# FPGA implementation of an efficient high-speed DVB-S2X block-interleaver

Youri Vladimirovitch Vassiliev

Master of Science in Electronics Submission date: July 2018 Supervisor: Kimmo Kansanen, IES

Norwegian University of Science and Technology Department of Electronic Systems

# Preface

This Master's Thesis was written during the spring of 2018 at the Norwegian University of Science and Technology (NTNU), located in Trondheim, in association with WideNorth, as part of an Erasmus+ exchange program form Ghent University. This project has been conducted under the supervision of Professor Dr. Kimmo Kansanen, Department of Electronic Systems and Bjarne Rislw from WideNorth

This thesis consists of 5 chapters. The first part is the introduction that talks about the overarching project that this thesis is a part of. The second chapter gives background information about the subject. The third chapter presents a theoretical design while the forth chapter puts the theory into practice. The final chapter concludes the Master's Thesis.

First and foremost I would like to thank my mother and father who have supported me during my exchange to Norway. Without their help, I would not have succeeded.

I would also like to thank WideNorth for giving me this Master's Thesis that has allowed me to realise my potential.

And finally, I would like to thank Kimmo Kansanen, he might not realise it, but his simple suggestions and tips have inspired many solution to all the problems that I faced in my design.

# Abstract

An overview of the DVB-S2 modem is given with the focus on the forward error correction block. The block-interleaver in the DVB-S2 and DVB-S2X standard is examined. Different interleaver configurations are evaluated. A suitable way to preform the interleaving process with one block of memory is found. The concept is proven with MATLAB models and implemented in VHDL. The entity has been verified and exceeds the desired performance.

# Table of Contents

| Pr  | eface   |                                       | 1  |

|-----|---------|---------------------------------------|----|

| Ab  | ostrac  | t                                     | 3  |

| Та  | ble of  | Contents                              | 6  |

| Li  | st of T | Tables                                | 7  |

| Lis | st of F | ligures                               | 10 |

| Ab  | obrevi  | ations                                | 11 |

| 1   | Intro   | oduction                              | 1  |

| 2   |         | rature Review                         | 3  |

|     | 2.1     | DVB-S2 modem                          | 3  |

|     | 2.2     | forward error correction              | 4  |

|     |         | 2.2.1 coding theory                   | 4  |

|     |         | 2.2.2 coding and decoding of frames   | 5  |

|     |         | 2.2.3 LDPC in more detail             | 5  |

|     | 2.3     | the block-interleaver                 | 7  |

|     |         | 2.3.1 purpose                         | 7  |

|     |         | 2.3.2 the DVB-S2 and DVB-S2X standard | 8  |

|     | 2.4     | existing block-interleaver designs    | 12 |

|     | 2.5     | Stratix 10 SX                         | 14 |

|     |         | 2.5.1 high level overview             | 14 |

|     |         | 2.5.2 Adaptive Logic Module           | 14 |

|     |         | 2.5.3 20-kilo-bit memory block        | 16 |

| 3   | Inte    | rleaver design                        | 19 |

|     | 3.1     | project description                   | 19 |

|     |         | 3.1.1 objective                       | 19 |

|    |        | 3.1.2    | performance goal                                              | 19 |

|----|--------|----------|---------------------------------------------------------------|----|

|    |        | 3.1.3    | design priorities                                             | 20 |

|    | 3.2    | testing  | methodology                                                   | 20 |

|    |        | 3.2.1    | modeling the interleaver as a permutation operation           | 20 |

|    |        | 3.2.2    | from model to hardware in steps                               | 21 |

|    |        | 3.2.3    | examples                                                      | 21 |

|    | 3.3    | block-i  | nterleaver models                                             | 21 |

|    |        | 3.3.1    | the block-interleaver as a matrix transposition               | 21 |

|    |        | 3.3.2    | memory block address generator as described in the literature | 23 |

|    |        | 3.3.3    | memory block address generator based on a linear congruential |    |

|    |        |          | generator                                                     | 25 |

|    |        | 3.3.4    | expanding from examples to real use cases                     | 28 |

|    | 3.4    | block-i  | nterleaver with only one memory block                         | 29 |

|    |        | 3.4.1    | One-memory-block design explained                             | 29 |

|    |        | 3.4.2    | permutation groups                                            | 31 |

|    |        | 3.4.3    | challenge in frame size scalability                           | 31 |

|    |        | 3.4.4    | possible compromise for large frames                          | 33 |

|    |        | 3.4.5    | solving the frame size scalability issue                      | 33 |

|    |        | 3.4.6    | uninterrupted interleaving for one configuration              | 37 |

|    |        | 3.4.7    | uninterrupted interleaving across all configurations          | 38 |

|    |        | 3.4.8    | scalability of the one-memory-block design                    | 40 |

|    | 3.5    |          | rleaving                                                      | 41 |

|    | 3.6    |          | sing multiple sequential bits at a time                       | 41 |

|    |        | 3.6.1    | subdividing the transposition operation                       | 41 |

|    |        | 3.6.2    | subdividing the interleaver                                   | 42 |

|    |        | 3.6.3    | row read order permutation                                    | 44 |

|    |        | 3.6.4    | challenge with indivisibility of words into columns           | 45 |

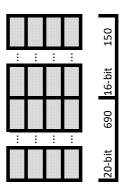

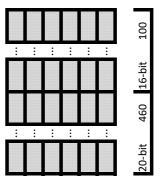

|    |        | 3.6.5    | allowing variable word sizes                                  | 47 |

|    | 3.7    | the fina | al design                                                     | 49 |

| 4  | imnl   | omonto   | tion and verification                                         | 51 |

| -  | 4.1    |          | erleaver implementation                                       | 51 |

|    | 4.2    |          | Sim simulation and verification                               | 53 |

|    | 4.3    |          | s timing and resource usage analysis                          | 61 |

|    | 4.5    | Quartu   |                                                               | 01 |

| 5  | Cone   | clusion  |                                                               | 65 |

| Bi | bliogr | aphy     |                                                               | 67 |

| Ар | pendi  | ix       |                                                               | 69 |

# List of Tables

| 2.1 | Block interleaver dimensions                                         | 9  |

|-----|----------------------------------------------------------------------|----|

| 2.2 | row read out order for small frames 1                                | 0  |

| 2.3 | row read out order for normal frames 1                               | 1  |

| 3.1 | permutation group element count for each interleaver configuration 3 | 2  |

| 3.2 | row-read-count pattern for all column sizes 4                        | 4  |

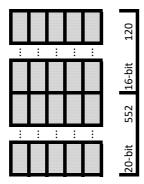

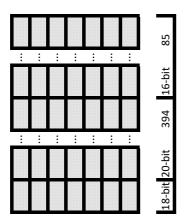

| 3.3 | column sizes when 16-bit words are used                              | 6  |

| 3.4 | column sizes when 20-bit words are used 4                            | 6  |

| 3.5 | column sizes when 18-bit words are used 4                            | .7 |

| 3.6 | column sizes when 30-bit words are used 4                            | .7 |

| 4.1 | big-interleaver maximum theoretical frequency                        | 1  |

| 4.2 | block resource usage                                                 | 1  |

| 4.3 | routing resource usage                                               |    |

# List of Figures

| 2.1  | functional block diagram of the DVB-S2 System                                 | 4  |

|------|-------------------------------------------------------------------------------|----|

| 2.2  | tanner graph representation of the parity check matrix                        | 6  |

| 2.3  | bit interleaved code modulation structure                                     | 8  |

| 2.4  | 8PSK bit interleaving of a normal frame                                       | 9  |

| 2.5  | 8PSK bit interleaving of a normal frame with coding rate of 3/5               | 10 |

| 2.6  | interleaver memory block structure                                            | 12 |

| 2.7  | address generators for WiMAX interleaver                                      | 13 |

| 2.8  | modified Finite State Machine (FSM)                                           | 13 |

| 2.9  | block diagram of the proposed interleaver/de-interleaver                      | 14 |

| 2.10 | configurable FIFO structure                                                   | 14 |

|      | Intel Stratix 10 FPGA architecture Block Diagram                              | 15 |

|      | Intel Stratix 10 FPGA ALM Block Diagram                                       | 15 |

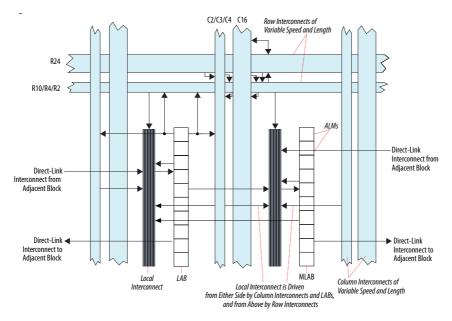

|      | Intel Stratix 10 LAB structure and interconnects overview                     | 16 |

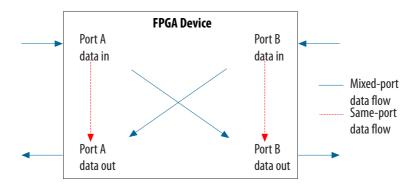

|      | read-during-write data flow                                                   | 17 |

| 2.15 | mixed-port read-during-write: old data mode                                   | 17 |

| 2.1  |                                                                               |    |

| 3.1  | alternative configuration for the address generator, 8 Phase-Shift Keying     | 24 |

| 2.2  | (PSK)                                                                         | 24 |

| 3.2  | Alternative configuration for the address generator, 16 Amplitude and Phase-  | 24 |

| 2.2  | Shift Keying (APSK)                                                           |    |

| 3.3  | block diagram of the simplified structure                                     | 26 |

| 3.4  | representation of the input range divided in two regions                      | 26 |

| 3.5  | example of a sequences created by an LCG based generator                      | 27 |

| 3.6  | representation of the input range divided in two regions after modification   | 27 |

| 3.7  | interleaver contents of example                                               | 30 |

| 3.8  | interleaver time efficiency                                                   | 33 |

| 3.9  | initial memory contents                                                       | 34 |

| 3.10 | · · <b>,</b> · · · · · · · · · · · · · · · · · · ·                            |    |

| 3.11 | unwrapping the memory contents with the second frame inside of it             | 35 |

| 3.12 | memory contents after the second frame is read and the third frame is written | 30 |

| 3.13 | unwrapping the memory contents with the third frame inside of it             | 36 |

|------|------------------------------------------------------------------------------|----|

| 3.14 | memory contents after the first frame is read and the second frame is writ-  |    |

|      | ten under a different configuration                                          | 39 |

| 3.15 | unwrapping the memory contents with the second frame inside of it under      |    |

|      | a different configuration                                                    | 39 |

| 3.16 | block interleaver in a 6 column configuration for normal frames              | 43 |

| 3.17 | first row of the big-interlear inside the small-interleaver                  | 43 |

|      | small-interleaver                                                            | 44 |

|      | contents of the small-interleaver after the columns have been written in the |    |

|      | sequence of the inverse row permutation                                      | 45 |

| 3.20 | interleaver in a 4 columns configuration for a normal frame                  | 46 |

| 3.21 | interleaver in a 3 column configuration for a word count of 3360             | 48 |

| 3.22 | interleaver in a 4 column configuration for a word count of 3360             | 48 |

| 3.23 | interleaver in a 5 column configuration for a word count of 3360             | 48 |

| 3.24 | interleaver in a 6 column configuration for a word count of 3360             | 48 |

| 3.25 | interleaver in a 7 column configuration for a word count of 3360             | 48 |

| 3.26 | interleaver in a 8 column configuration for a word count of 3360             | 48 |

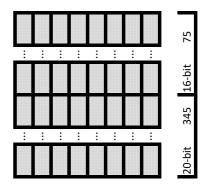

| 4.1  | overview of the full interleaving process of 12 normal frames                | 58 |

| 4.2  | overview of the full interleaving process of 12 small frames                 | 58 |

| 4.3  | start up behaviour for the small frame configuration                         | 59 |

| 4.4  | output small frame 0 and input small frame 1                                 | 59 |

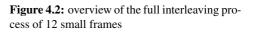

| 4.5  | output small frame 7 and input small frame 8                                 | 60 |

| 4.6  | output small frame 8 and input small frame 9                                 | 60 |

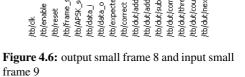

| 4.7  | big-interleaver implementation on the Field Programmable Gate Array          |    |

| •••  | (FPGA) fabric                                                                | 62 |

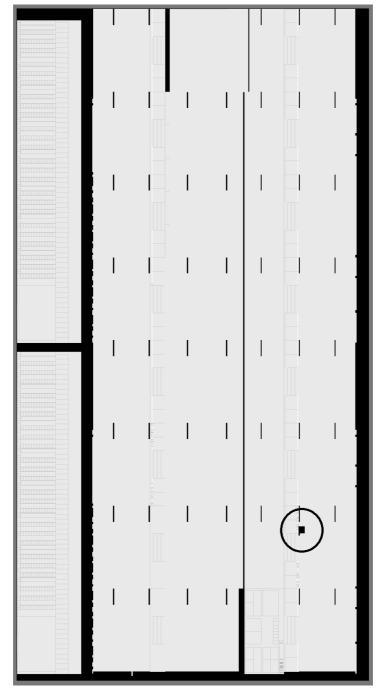

| 4.8  | the whole 1SX085HN3F43I3XG FPGA fabric                                       | 63 |

# Abbreviations

- ALM Adaptive Logic Module. 14, 16

- APSK Amplitude and Phase-Shift Keying. 19, 21, 22, 24, 38, 40, 42, 44, 47, 49, 51, 65

- AWGN Added White Noise Gaussian. 4

BCH Bose Chaudhuri Hocquenghem. 1, 3, 5

- BICM Bit-Interleaved Coded Modulation. 1, 7

- DAC Digital to Analogue Converters. 4

- DSP Digital Signal Processor. 20

- ESA European Space Agency. 1

- FEC Forward Error Correcting. 1, 3

- FIFO First In First Out. 12

- FPGA Field Programmable Gate Array. 14, 20, 61–63

- FSM Finite State Machine. 12, 13, 24, 27

- Gbps gigabit per second. 19

- Gs/s Giga-symbol-per-second. 1, 19

- LAB Logic Array Block. 14, 16, 61

- LCG Linear congruential Generator. 25, 27, 37

- LDPC Low-Density Parity-Check. 1, 3, 5, 7–9

- LUT Look-Up-Table. 14, 16, 29, 31, 32, 53, 61

- M20K Memory 20-Kilo-bit. 14, 16, 29, 46, 61

- MHz megahertz. 20, 38

- MLAB Memory Logic Array Block. 14, 16

- **PSK** Phase-Shift Keying. 19, 21, 22, 24, 27, 30, 34, 38, 42

- VHTS Very High Throughput Satellite. 1

- **VSAT** Very-small-aperture terminals. 1

# Chapter

# Introduction

The objective of this Master's Thesis is to design a DVB-S2X compliant block-interleaver, which will be used in a modem designed by WideNorth, for a research project commissioned by the European Space Agency (ESA). The purpose of this research project is to demonstrate a re-programmable wideband modem for Very High Throughput Satellite (VHTS) networks through ultra-wideband Very-small-aperture terminals (VSAT). The goal is to design a transmitter and receiver capable of handling a throughput of 1.4 Giga-symbol-per-second (Gs/s), which is around 3 to 4 times what current modems are capable of. The modem will be connected to various networks in a base station through an Ethernet interface. Wireless point-to-point and point-to-multipoint communication will be established through the existing VSAT satellite links that have a bent-pipe architecture.

The block-interleaver is only a part of the full Forward Error Correcting (FEC) block in the modem. Its purpose is to break the correlation caused by symbol mapping as it degrades the performance of the Low-Density Parity-Check (LDPC) decoder. The FEC block, which consists of Bose Chaudhuri Hocquenghem (BCH) encoding, LDPC encoding, and a block-interleaver, together with the constellation mapper form what is called a Bit-Interleaved Coded Modulation (BICM) structure. Chapter 2

# Literature Review

In this chapter a brief description will be given of the DVB-S2 modem. In this modem an overview is given of the FEC block. The function and importance of the block-interleaver in the FEC chain will be explained. Existing designs found in the literature will be presented. Because the block-interleaver is to be implemented on an Intel Stratix 10 FPGA its architecture will be studied.

# 2.1 DVB-S2 modem

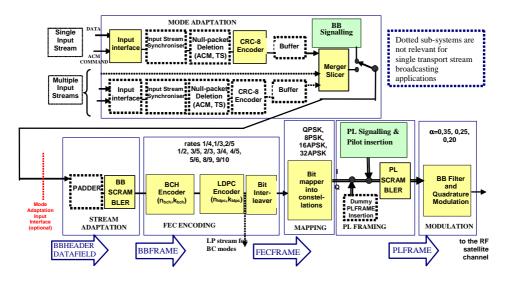

In order for a message to be transmitted it needs to pass through the modem consisting of the following modules[1]:

- Mode adaptation: This is the input stream interface. Here the data is synchronised, null-packet are deleted and the resulting stream is encoded with CRC-8 coding. Multiple streams are merged from multiple inputs and then sliced into data fields. A Base-Band Header is appended in front of the data field to notify the receiver of the input stream format and Mode Adaptation type.

- Stream adaptation: Zero padding is introduced when the available user data for transmission is insufficient to completely fill up a Base-Band Frame.

- Forward Error Correction Encoding: Each frame is first encoded with BCH code and then followed up by LDPC code. If the modulation scheme is either 8 PSK, 16 APSK or 32 APSK then the resulting message is interleaved in a block-interleaver.

- Mapping: The data-stream is then mapped into an I-Q data stream with the use of a constellation mapper.

- Physical layer framing: Dummy frames are transmitted when no useful data is ready to be sent. A slot is devoted to physical layer signalling such as start-of-Frame delimitation and transmission mode definition. A regular raster of pilot symbols is introduced to facilitate Carrier frequency recovery in the receivers.

- Quadrature Modulation Base-Band Filtering: The I-Q data is modulated into a waveform. This digital wave is filtered with a squared-root raised cosine filter that has a roll-off factor of either 0.35, 0.25 or 0.20.

- Digital to analogue conversion: WideNorth has made the design choice of doing all the filtering in the digital domain. By using state of the art high-speed Digital to Analogue Converters (DAC) the signal is put directly onto the L-band for transmission [2].

A detailed overview of the entire DVB-S2 modem for transmission is seen in Figure 2.1.

Figure 2.1: functional block diagram of the DVB-S2 System [1]

# 2.2 forward error correction

## 2.2.1 coding theory

In 1948 Claude Shannon established a theory that is now known as the noisy-channel coding theorem, but also referred to as the Shannon's theorem. It states that for any Added White Noise Gaussian (AWGN) channel, there exists a maximum rate for which data can be transmitted error-free with the use of error correcting codes [3]. The theorem, however, does not state what these error correcting codes are, only that such a code can exist. This opened up a new field in computer science. Since then, scientists and engineers have tried to come up with codes that reach this limit yet remain practical and feasible to implement. Practical means that the algorithm that is to be implemented, grows in polynomial complexity with respect to the message length.

## 2.2.2 coding and decoding of frames

In the DVB-S2 and DVB-S2X standard the message is encoded with BCH, afterwards it is encoded again with LDPC [1, 4]. LDPC is currently the best coding scheme available as it has the advantage of design flexibility, decoding simplicity, and a universally excellent error correction performance over various channel types [5]. In a soft-decision approach LDPC, encoded messages are decoded using a sum-product algorithm, also known as the belief propagation algorithm. This algorithm needs multiple iterations in order for the received data to converge to the most probable code-word. In certain cases, the maximum amount of iterations is exceeded, and the algorithm is halted prematurely. The resulting sub-optimal estimation is then passed through the BCH decoder. Here, the remaining errors are corrected in a reliable time-frame. It is shown that this combination of BCH and LDPC code provide excellent error correction performance and achieve an extremely low bit-error rate [6]. Since the error-correcting performance is improved compared to previous standards, it becomes possible to employ higher order modulation schemes to increase the spectral efficiency and maximal data rate [6].

## 2.2.3 LDPC in more detail

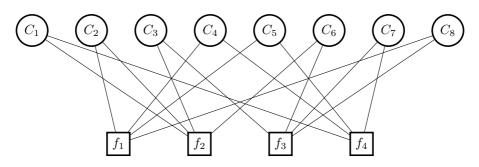

LDPC code preforms bad under certain circumstances. In order to understand what these circumstances are, a brief explanation is needed regarding the decoding process. The LDPC code is in essence a linear block code[7]. This means that data is encoded using a generator matrix and decoded using a parity check matrix. A property of this parity check matrix is that it has more zeroes then ones. This sparseness guarantees a linear increase in time complexity of decoding with increased block size [7, 8]. An example of such a parity check matrix is provided below [7].

$$H = \begin{pmatrix} 0 & 1 & 0 & 1 & 1 & 0 & 0 & 1 \\ 1 & 1 & 1 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 1 & 1 & 1 \\ 1 & 0 & 0 & 1 & 1 & 0 & 1 & 0 \end{pmatrix}$$

(2.1)

This LDPC decoder takes 8 bits of input and is constrained by 4 linear equations. These linear equations are:

$$\begin{cases} f_1 = C_2 + C_4 + C_5 + C_8 \pmod{2} = 0\\ f_2 = C_1 + C_2 + C_3 + C_6 \pmod{2} = 0\\ f_3 = C_3 + C_6 + C_7 + C_8 \pmod{2} = 0\\ f_4 = C_1 + C_4 + C_5 + C_7 \pmod{2} = 0 \end{cases}$$

(2.2)

Another way to represent this parity check matrix is by visualising it in a Tanner graph as seen in Figure 2.2. The C-nodes are the variable nodes that contain the received data. The f-nodes are the check nodes where each linear equation result is calculated. The edges represent an addition of the C-node in the f-node.

Figure 2.2: tanner graph representation of the parity check matrix [7]

$$C \cdot H^T = 0 \tag{2.3}$$

Consider C to be the received data. If equation 2.3 is satisfied, then the data contains no errors. Another way to phrase this is that for each linear equation in 2.2, the amount of bits that are 1 in each equations must be even. In other words, f1 through f4 must be 0. When a message contains an error, the condition in equation 2.3 is not satisfied, iterative decoding will takes place. For instance, lets assume that the received code-word from C1 through C8 is 10110100. The linear equations 2.2 become:

$$\begin{cases} f_1 = 0 + 1 + 0 + 0 \pmod{2} \\ f_2 = 1 + 0 + 1 + 1 \pmod{2} \\ f_3 = 1 + 1 + 0 + 0 \pmod{2} \\ f_4 = 1 + 1 + 0 + 0 \pmod{2} \end{cases} \iff \begin{cases} f_1 = 1 \\ f_2 = 1 \\ f_3 = 0 \\ f_4 = 0 \end{cases}$$

(2.4)

In this example the equations for f1 and f2 are not satisfied, therefore, the C-nodes in the Tenner graph, that are connected to both the check-nodes f1 and f2, must change. In this case  $C_2$  becomes 1. The final correct code-word then becomes 10110100. This is the essence of the bit-flipping algorithm. If multiple bits are wrong, then the bit-flipping process is repeated until equation 2.3 is satisfied. In bigger coding schemes, a C-node is flipped if the majority of the f-nodes it is connected to are 1. The Bit-flipping algorithm is essentially a message passing algorithm. The C-nodes broadcast their data to their fnodes. In turn the f-nodes broadcast their parity-check information back to their C-nodes. The C-nodes change their value based on majority consensus [8]. These steps are repeated until equation 2.3 is satisfied.

When a message is received, the symbols are de-mapped into a word consisting of bits that are all binary. This is called a hard-decision approach. A better approach would be to do a log-likelihood estimation and infer both the chance of bit x being a 1 and a 0. P(x = 1) is 1 - P(x = 0) so both probabilities can be described by a single value. This value is the logarithm of the proportion of P(x = 1) over P(x = 0) as per the following formula:

$$L(x) = \log\left(\frac{P(x=1)}{P(x=0)}\right)$$

(2.5)

This values is used as a metric to determine whether or not bit x is closer to being a 0 or a 1 [8].

The decoder will thus receive real-valued probabilities instead of bits. This approach is much more computationally heavy, but yields much better results. The best performing algorithm for this problem is the sum-product algorithm [3]. Just like the bit-flipping algorithm, the sum-product algorithm is also a message passing algorithm.

In the first part of the iteration the C-nodes broadcast their normalised probabilities to the f-nodes. The f-nodes sum up all the values they receive. In the second step these f-node broadcast their results back to the C-nodes. Each individual C-node subtracts its own contribution to the sums before multiplying everything they receive. The current values are replaced by the products. In order to verify if the message is error-free, the f-nodes threshold the incoming C-node values between step one and two. Anything smaller then 0.5 is considered to be a 0 and anything above is considered to be a 1. These values are then put through equations 2.3 and checked for parity. If the parity conditions are met then the message is done with the decoding process, if not, the algorithm proceeds to step two and loops back to step one. The probabilities themselves will eventually converge after multiple iterations. This process continues until the parity is satisfied or until the maximum allowed iterations is reached.

Both the soft-decision and hard-decision approach have something in common. If more then one received bit is wrong then the algorithm suddenly needs more iterations in order to successfully reconstruct the message. LDPC works therefor best in environments where errors are uncorrelated and the channel memory-less[6]. More information regarding the topic of decoding can be found here [3, 7, 8].

## 2.3 the block-interleaver

### 2.3.1 purpose

When information is transmitted, it is chopped into smaller messages where multiple bits are mapped into to one symbols. It stands to reason that when one symbol is incorrectly received, that multiple bits are affected by the distortion. In case of a soft-decision architecture, the individual bits that made up that symbol, receive a smaller certainty when the symbols are de-mapped. Grouping together of bits into symbols is a source of correlation. Where if one bit is affected then the surrounding bits are more likely to be affected as well.

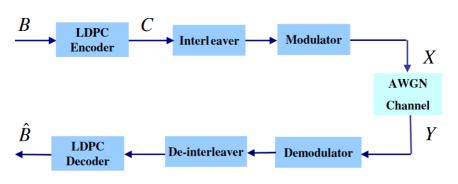

The purpose of an interleaver is to rearrange the bit ordering of a message, so that the bits that become correlated through symbol mapping, are spread out throughout the whole message. Whenever an error does occur, the surrounding bits will be uncorrelated and unaffected after the deinterleaving process. This makes the bit stream memory-less and uncorrelated [6]. An interleaver enhances the ability of the decoder to correct the errors in a message. A soft-decision LDPC decoder requires less iterations to correct multiple regions with small uncertainties, then one region with a big uncertainty. This is because the error is now dilute across multiple linear equations [6]. Bit-interleaving of LDPC code guarantees good performance [6]. A configuration that uses error correcting code together with an interleaver that covers its shortcomings is a BICM scheme. Such a configuration is shown in Figure 2.3.

Figure 2.3: bit interleaved code modulation structure [5]

Interleaving can also happen between different messages. Bits from multiple messages can be swapped between each other. These messages are then send across different channels. This makes transmissions more robust in scenarios where channel fading is an issue. In this process the correlation of data caused by transmission across an individual channel is broken up by sending the data across multiple channels and assembling the data back together at the destination. In case of DVB-S2 and DVB-S2X, this type of interleaving is not necessary as the sender and receiver will be stationary.

### 2.3.2 the DVB-S2 and DVB-S2X standard

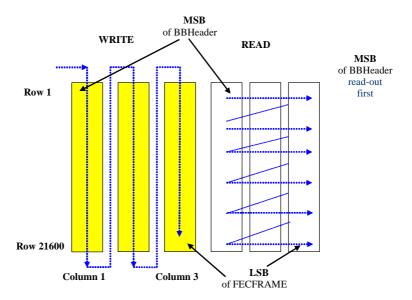

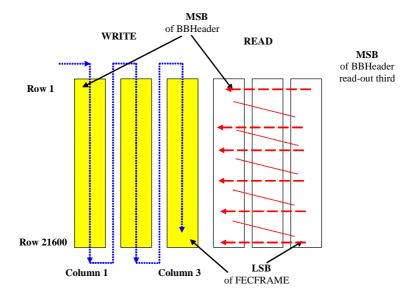

The interleaver that follows the LDPC encoder in the DVB-S2 and DVB-S2X standard is a Block-interleaver [1, 4]. There are two types of frames that need interleaving, a normal frame that is 64800 bits wide, and a short frame that is 16200 bits wide. There is also a medium frame that is 32400 bits wide, but that one doesn't need to be interleaved. Whether or not a normal or small frame needs to be interleaved, depends on the modulation scheme. In the DVB-S2 specification, normal and small frames that have to be transmitted over 8PSK, 16APSK and 32APSK need to be interleaved. In the DVB-S2X extension, additional modulation schemes for the normal frame have been added, for which interleaving also needs to take place. These modulation schemes are 64APSK, 128APSK, and 256APSK. The block interleaver is not a fixed implementation whereby every frame is subject to an identical operation. Different modulation schemes require different block dimensions. 8PSK, 16APSK 32APSK, 64APSK, 128APSK, and 256APSK respectively encode 3.4,5,6,7, and 8 bits of date. The amount of columns that are present in the blockinterleaver for each modulation scheme, is equal to the amount of bits each modulation scheme encodes. For example the block interleaver for 8PSK would have 3 deep columns while the block interleaver for 256APSK would have 8 shallower columns. The incoming data stream is written vertically, column-wise from top to bottom, starting with the leftmost column, and progressing from left to right. When the block is full, the data is read horizontally, row-wise from left to right, starting from the topmost row, and progressing from top to bottom. This process is visualised in Figure 2.4 in the case of 8PSK modulation. Because the column count is chosen to be the same size as the symbol bit size, whole rows can be taken to the constellation-mapper as they are.

Figure 2.4: 8PSK bit interleaving of a normal frame [1]

A summary of all the block-dimensions can be found in Table 2.1 for both the normal and the small frames.

| Modulation  | 8PSK  | 16APSK | 32APSK | 64APSK | 128APSK | 256APSK |

|-------------|-------|--------|--------|--------|---------|---------|

| column size | 3     | 4      | 5      | 6      | 7       | 8       |

| normal      | 21600 | 16200  | 12960  | 10800  | (9258)  | 8100    |

| small       | 5400  | 4050   | 3240   | N/A    | N/A     | N/A     |

Table 2.1: Block interleaver dimensions [1, 4]

When one tries to divide 64800 bits equally into 7 columns, he or she will find that the bit-size of each column becomes 9257,143. In the specification it is stated that for the case of 128APSK, an additional 6 bit padding is introduced after the LDPC encoder, in order to achieve an integer amount of symbols for the interleaver and constellation mapper [4].

Frames can be coded in a variety of coding rates. The ordering in which individual bits inside each row need to be read out, is tied to the coding rate. In the DVB-S2 standard, the read order of a row, for the case of 8PSK with a coding rate of 3/5, is reversed. This is depicted in Figure 2.5.

For the DVB-S2X standard the story is a bit more complicated as every coding rate comes with a custom read-order. All the read orders for the small frame and normal frame can be found in Table 2.2 and 2.3 respectively. As an example, the bit interleaver pattern 102 means that for each row, the middle entry (1) is read out first, followed by the leftmost entry (0), and finally the rightmost entry (2) [4].

Figure 2.5: 8PSK bit interleaving of a normal frame with coding rate of 3/5 [1]

| Modulation         | coding rate | read sequence |

|--------------------|-------------|---------------|

| 8PSK               | 7/15        | 102           |

| 8PSK               | 8/15        | 102           |

| 8PSK               | 26/45       | 102           |

| 8PSK               | 32/45       | 012           |

| 4+12APSK           | 7/15        | 2103          |

| 4+12APSK           | 8/15        | 2103          |

| 4+12APSK           | 26/45       | 2130          |

| 4+12APSK           | 3/5         | 3201          |

| 4+12APSK           | 32/45       | 0123          |

| 4+12+16rbAPSK APSK | 2/3         | 41230         |

| 4+12+16rbAPSK APSK | 32/45       | 10423         |

Table 2.2: row read out order for small frames [4]

| Modulation      | coding rate | read sequence |

|-----------------|-------------|---------------|

| 8PSK            | 23/36       | 012           |

| 8PSK            | 25/36       | 102           |

| 8PSK            | 13/18       | 102           |

| 4+12APSK        | 26/45       | 3201          |

| 4+12APSK        | 3/5         | 3210          |

| 8+8APSK         | 18/30       | 0123          |

| 4+12APSK        | 28/45       | 3012          |

| 4+12APSK        | 23/36       | 3021          |

| 8+8APSK         | 20/30       | 0123          |

| 4+12APSK        | 25/36       | 2310          |

| 4+12APSK        | 13/18       | 3021          |

| 4+12+16rbAPSK   | 2/3         | 21430         |

| 8+16+20+20APSK  | 7/9         | 201543        |

| 8+16+20+20APSK  | 4/5         | 124053        |

| 8+16+20+20APSK  | 5/6         | 421053        |

| 2+4+2APSK       | 100/180     | 012           |

| 2+4+2APSK       | 104/180     | 012           |

| 8+8APSK         | 90/180      | 3210          |

| 8+8APSK         | 96/180      | 2310          |

| 8+8APSK         | 100/180     | 2301          |

| 4+12APSK        | 140/180     | 3210          |

| 4+12APSK        | 154/180     | 0321          |

| 4+8+4+16APSK    | 128/180     | 40312         |

| 4+8+4+16APSK    | 132/180     | 40312         |

| 4+8+4+16APSK    | 140/180     | 40213         |

| 16+16+16+16APSK | 128/180     | 305214        |

| 4+12+20+28APSK  | 132/180     | 520143        |

| 128APSK         | 135/180     | 4250316       |

| 128APSK         | 140/180     | 4130256       |

| 256APSK         | 116/180     | 40372156      |

| 256APSK         | 20/30       | 01234567      |

| 256APSK         | 124/180     | 46320571      |

| 256APSK         | 128/180     | 75642301      |

| 256APSK         | 22/30       | 01234567      |

| 256APSK         | 135/180     | 50743612      |

Table 2.3: row read out order for normal frames [4]

## 2.4 existing block-interleaver designs

Before setting of on a journey to create an interleaver that will take over the world, some existing designs will be studied first.

In paper [9] a block-interleaver is created that can be used in both the WiMax and WLAN standard. In both cases a block of data is subject to two permutations as seen in equation 2.6 and 2.7.

$$M_k = \left(\frac{N}{d}\right) \times (k\%d) + \left\lfloor\frac{k}{d}\right\rfloor$$

(2.6)

$$J_k = s \times \left\lfloor \frac{M_k}{s} \right\rfloor + \left( \left( M_k + N - \left\lfloor d \times \frac{M_k}{N} \right\rfloor \right) \% s \right)$$

(2.7)

Here d represents the number of columns,  $M_k$  is the output of the first permutation while  $J_k$  is the output of the second permutation, both are indexed by k from 0 to N - 1in which N represents the message bit-size, and finally s is the maximum of 1 and N/2. Two memory blocs are used in this design. While data is written to the first block, the second block is being read from using the generated permutations as addresses, afterwards the roles reverse. A similar design is proposed in paper [10]. The memory block setup is depicted in Figure 2.6 taken from the paper.

Figure 2.6: interleaver memory block structure [10]

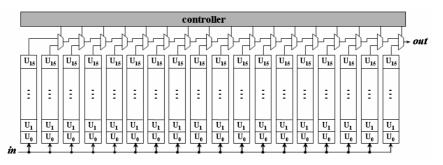

In this architecture the address is generated locally by a rather complicated circuit network, accompanied by a rather complicated FSM, as seen in Figure 2.7 and 2.8 respectively, taken from the paper.

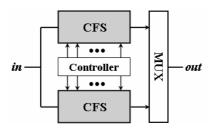

In paper [11] a similar block interleaver is designed, but instead of using memory blocks as a storage units, the author uses a First In First Out (FIFO) structure to store the data as depicted in Figure 2.9 and 2.10. This design is faster and more flexible but consumes more power [11].

Figure 2.7: address generators for WiMAX interleaver [9]

Figure 2.8: modified FSM [9]

Figure 2.9: block diagram of the proposed interleaver/de-interleaver [11]

Figure 2.10: configurable FIFO structure [11]

# 2.5 Stratix 10 SX

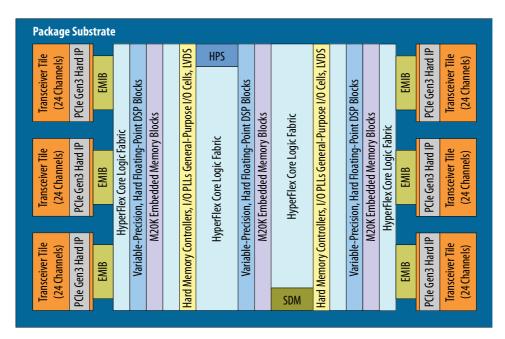

WideNorth hasn't fully decided yet on what FPGA will be used in the final product, but it will most likely be the Stratix 10 SX FPGA series from Intel. The interleaver that will be designed in this Master's thesis, will therefore be geared towards, and optimised for, this particular FPGA series. The resources available on the Stratix 10 SX series will now be discussed.

## 2.5.1 high level overview

A high level overview of the chip can be seen in Figure 2.11. Here the HPS is a Quad ARM Cortex-A53 Hard Processor System, the SDM is a Secure Device Manager, and the EMIB is an Embedded Multi-Die Interconnect Bridge [12].

The most important blocks for the interleaver design are the following: Adaptive Logic Module (ALM), Logic Array Block (LAB), Memory Logic Array Block (MLAB) and Memory 20-Kilo-bit (M20K) blocks. These will be discussed in more detail.

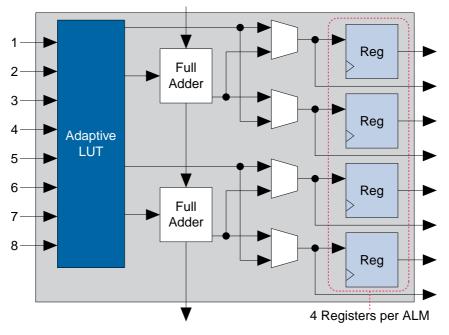

## 2.5.2 Adaptive Logic Module

The ALM is a block where combinatorial logic is realised. It contains two adaptive Look-Up-Table (LUT), two two-bit full adders, four multiplexers, and four latched outputs that can be bypassed. The structure of the ALM can be seen in Figure 2.12.

Figure 2.11: Intel Stratix 10 FPGA architecture Block Diagram [12]

Figure 2.12: Intel Stratix 10 FPGA ALM Block Diagram [12]

Figure 2.13: Intel Stratix 10 LAB structure and interconnects overview [13]

The ALMs are grouped together in groups of 10 into what is called a LAB [13]. The full structure can seen in Figure 2.13. This makes it easy to create fast and complex combinatorial structures, by feeding the output of one one ALM into the input of an adjacent ALM, through a dedicated local interconnect. Adjacent ALMs have their full-adder carry bit daisy-chained between each other to create ripple-adders of arbitrary length. Over a quarter of all LABs can be used as bit-addressable memory block that are of 640 bits in size. This structure is referred to as an MLAB. This is achieved by using modified LUTs as addressable storage space [13].

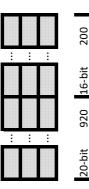

## 2.5.3 20-kilo-bit memory block

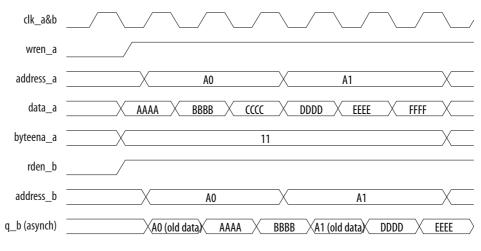

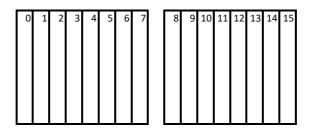

The M20K is a dedicated memory unit that can store 20,480 bits of data [14]. These blocks are flexible in how the input-size versus address space can be configured. The following options are possible: 512 x 40-bit, 1024 x 20-bit and 2048 x 10-bit. 8-bit, 16-bit, and 32-bit is not natively supported, this means that 20% of the total storage space will be wasted. Bigger address space or input size can be achieved by combining multiple M20K blocks together with multiplexers. M20K blocks can be configured as up to two true port and 4 simple port configuration. A true dual port allows one to read and write independently of each other, to two different addresses, on the same clock-cycle. On a simple dual port, one can read and the other one can write, but are excluded from both reading and both writing at the same time. On a four simple port configuration, only two reads and two writes are allowed each clock cycle.

It is possible to both read and write the same address during one clock-cycle. The behaviour however depends on whether or not a single port or a mixed dual port configuration is chosen [14]. If a single port solution is chosen, then the output of the read operation during a write, can be configured to output either the new data or don't care values on the next clock cycle. In a dual port, each port has its own output. In a mixed port configuration it is possible to cross the outputs. In essence, the read result of port B can be routed through the output of port A and vice versa. A mixed port configuration is visualised in Figure 2.14.

Figure 2.14: read-during-write data flow [14]

In this mixed port configuration, the output of a read during write to the same address, can now either be the newly written data, or the old data that is currently being overwritten [14]. In the latter configuration it is possible to take out stored data from memory, use it in the next block, and have it overwritten with new data, all in one clock cycle. This is comparable to a bit shift operation, but on a larger scale. This behaviour can be seen in the wave form in Figure 2.15.

Figure 2.15: mixed-port read-during-write: old data mode [14]

# Chapter 3

# Interleaver design

In this chapter the design goal is stated along with its constraints. The metrics that will be used to benchmark the performance of the interleaver will be specified. The design process begins with a mathematical model using MATLAB, that proves the correctness of a concept. In the final part of this chapter, the mathematical model is broken up into a sequence of smaller independent operations that can easily be implemented in hardware.

# 3.1 project description

# 3.1.1 objective

The objective consists of creating a DVB-S2 compliant block-interleaver that can handle normal and small frames that are destined for 8 PSK, 16 APSK, and 32 APSK modulation. An added bonus objective is to make it expandable to the DVB-S2X standard, where the interleaver would additionally have to support normal frames that are destined for 64 APSK, 128 APSK and 256 APSK modulation. Subsequent frames have no gaps in between them and each subsequent frame can be destined for a different modulation scheme, that in turn requires all frames to be interleaved under different interleaver configurations. This means that the interleaver must be capable of accepting frames as a never ending streaming data and be able to reconfigure itself on the fly. There is an exception when it comes to transitioning between frame types, from normal to small and vice versa. It is tolerable to delay the incoming frame in order to read out the current frame from the block of memory and reconfigure the interleaver for a different frame size.

# 3.1.2 performance goal

The goal of the research project is to create a DVB-S2 transmitter and receiver capable of handling 1.4 Gs/s. Each 32 APSK symbol encodes 4 bits. Therefore the target throughput should be  $1.4 \times 4 = 5.6$  gigabit per second (Gbps). The design choice has been made to process 16 bits in parallel every clock cycle at a clock-speed of 350 megahertz (MHz) to

reach this throughput. The addition of the DVB-S2X standard, that allows higher order modulation, would push the maximum throughput over that limit.

### 3.1.3 design priorities

The metrics that are important in this design are simplicity, engineering time and time to market. This means that code simplicity, design simplicity, human resource, and ease of integrating the module into the system is valued over FPGA resource use and energy usage to a certain degree so long as the performance goal is met.

## **3.2 testing methodology**

An analogy can be made in the way that the interleaver model is verified with the method by which a Digital Signal Processor (DSP)-system is verified. A DSP-system is tested by introducing a Dirac-impulse at the input and measuring the impulse response on the output. The reason for this is that the Dirac-impulse is a neutral element to the system. What flows out of the output is the function that identifies the operation done by the system. The tests that will be preformed on the mathematical models of the interleaver are similar in nature.

### **3.2.1** modeling the interleaver as a permutation operation

The operation done by the block-interleaver as described in section 2.3.2 can be described by a permutation. A vector will be used to represent a frame. A permutation that represents the interleaving process, is applied to this vector. The resulting vector represents the interleaved frame after the interleaving process. The neutral element of a permutation is the identity permutation.

The permutation that is preformed by the interleaver will from henceforth be denoted as  $\mathcal{P}$ , the identity permutation as 1, and the bit-size of the input as N. The normal frame has an N of 64800 and the short frame has an N of 16200. A permutation can be written in two ways. One of those is the Cauchy's two-line notation. Permutation  $\mathcal{P}$  and 1 can be seen in this notation in Equation 3.1 and 3.2 respectively.

$$\mathcal{P} = \begin{pmatrix} 0 & 1 & 2 & \dots & m-1 \\ \mathcal{P}(0) & \mathcal{P}(1) & \mathcal{P}(2) & \dots & \mathcal{P}(N-1) \end{pmatrix}$$

(3.1)

$$\mathbb{1} = \begin{pmatrix} 0 & 1 & 2 & \dots & N-1 \\ 0 & 1 & 2 & \dots & N-1 \end{pmatrix}$$

(3.2)

For this Master's Thesis a custom permutation notation will be used. This is for the sake of simplicity and because it corresponds to the output given by the MATLAB code. The custom notation is the Cauchy's two-line notation but without explicitly writing down the first row. Instead, the first row is always implied to go from 0 to N-1 and omitted from the notation. This notation can be seen in equation 3.3 and 3.4 for  $\mathcal{F}$  and  $\mathbb{1}$  respectively. Because the notation is essentially becomes a vector the permutations will henceforth be referred to as permutation vectors.

$$\mathcal{P} = [\mathcal{P}(0), \mathcal{P}(1), \mathcal{P}(2), \dots, \mathcal{P}(m-1)]$$

(3.3)

$$\mathbb{1} = [0, 1, 2, \dots, m-1] \tag{3.4}$$

#### **3.2.2** from model to hardware in steps

The first step of the design process is to create a high-level model that will serve as a definition of the interleaver operation. This model will be used to define the permutation vector  $\mathcal{P}$ . The next step is to break up the high-level model into a model that consists of a sequence of smaller operations that can easily be translated into hardware operations. The validity of this lower-level model can be verified by comparing it to the original high-level model that serves as the definition. Consider the following low level-model that realises a permutation  $\mathcal{F}$ .

$$1 \times \mathcal{P}_{sys} = \mathcal{P}_{out} \tag{3.5}$$

$$1 \times \mathcal{F}_{sys} = \mathcal{F}_{out} \tag{3.6}$$

These two models consisting of operation  $\mathcal{P}_{sys}$  and  $\mathcal{F}_{sys}$  are equal if and only if the outputs  $\mathcal{P}_{out}$  and  $\mathcal{F}_{out}$  from a neutral element are equal. This way of testing guarantees that the low-level model, destined for translation into hardware, is correctly implemented. This will serve as mathematical proof of correctness of the system.

The mathematical model can accept integers, but the eventual hardware will interleave binary data. In order to verify the correct implementation of the entity in hardware, the MATLAB model will generate an input frame using a random number generator. This frame is interleaved using the high level model that serves as the definition. In a test bench, the generated frame is fed to the input of the device. The output will then be compared to the expected output that was created by the high level model.

#### 3.2.3 examples

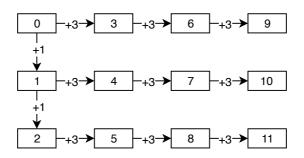

For the sake of simplicity, small examples will be given to demonstrate the different models and ideas. Later on, the concepts are extrapolated to larger structures that will serve as a basis for the hardware design. In these limited example the frame size N is 12 and the supported modulations are 8 PSK and 16 APSK. This means that the example interleaver has two configurations. For 8 PSK it is configured as a block consisting of 3 columns of size 4 and for 16 APSK it is configured as a block consisting of 4 columns of size 3.

# 3.3 block-interleaver models

### **3.3.1** the block-interleaver as a matrix transposition

The block-interleaver as described in section 2.3.2 can be seen as a matrix transposition. Data is written to the block from top to bottom and from left to right. The data is then read from left to right and from top to bottom. The relationship between the reading sequence and the writing sequence is that they are a transposition of each other. If the data inside the matrix is transposed then the reading sequence needs to be transposed as well to preserve the function. Transposing the reading sequence will result in it becoming equal to the writing sequence. Because the reading and writing sequence become equal they do not

contribute anymore to the permutation. The only operation left is the transposition of the data. This implies that the interleaving process can be translated to a transposition of the data. This is significant as the problem of implementing an interleaver has been translated in to the implementation of a transposition operation. The permutation of an interleaver is therefore equal to the permutation realised by a matrix transposition.

In reality no real transposition operation will happen inside the memory modules. What will happen instead is that the elements of the permutation vector will be used as an address. The memory will thus be accessed in a sequence defined by the permutation vector.

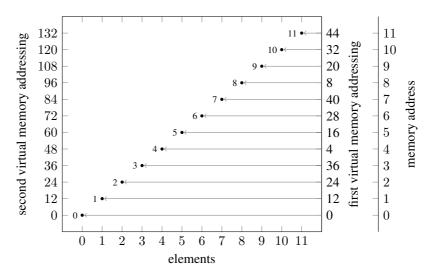

Consider the following neutral element in equation 3.7. This frame will be interleaved in both configurations of the interleaver. First the frame is written to the block as can be seen in equation 3.9 and 3.8 for the case of 8 PSK and APSK respectively. Afterwards the data is transposed as can be seen in equation 3.11 and 3.10. Afterwards the data is read and the results can be seen in equation 3.12 and 3.13.

$$\mathbb{1} = [0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 11] \tag{3.7}$$

$$Interleaver_{(8PSK)}(1) = \begin{bmatrix} 0 & 4 & 8 \\ 1 & 5 & 9 \\ 2 & 6 & 10 \\ 3 & 7 & 11 \end{bmatrix}$$

(3.8)

$$Interleaver_{(16APSK)}(\mathbb{1}) = \begin{bmatrix} 0 & 3 & 6 & 9 \\ 1 & 4 & 7 & 10 \\ 2 & 5 & 8 & 11 \end{bmatrix}$$

(3.9)

$$Interleaver_{(8PSK)}^{T}(\mathbb{1}) = \begin{bmatrix} 0 & 1 & 2 & 3\\ 4 & 5 & 6 & 7\\ 8 & 9 & 10 & 11 \end{bmatrix}$$

(3.10)

- 7

$$Interleaver_{(16APSK)}^{T}(1) = \begin{bmatrix} 0 & 1 & 2\\ 3 & 4 & 5\\ 6 & 7 & 8\\ 9 & 10 & 11 \end{bmatrix}$$

(3.11)

г.

$$\mathcal{P}_{(8PSK)} = [0, 4, 8, 1, 5, 9, 2, 6, 10, 3, 7, 11] \tag{3.12}$$

$$\mathcal{P}_{(16APSK)} = [0, 3, 6, 9, 1, 4, 7, 10, 2, 5, 8, 11] \tag{3.13}$$

The MATLAB code that was used to demonstrate these operations can be found in Listing 3.1.

Listing 3.1: MATLAB code that realises the interleaver as a transposition operation

```

1 frame_size = 12;

```

- 2  $column_count = 3;$

- 3 column\_size = frame\_size / column\_count;

- 4 input =  $0:(\text{frame_size} 1);$  %neutral element

```

5

6

Interleaver_A = reshape(input,[], column_count);

7

Interleaver_B = Interleaver_A';

8

ideal_permutation_vector = reshape(Interleaver_B, 1, []);

9

10

disp(input);

11

disp(Interleaver_A);

12

disp(Interleaver_B);

13

disp(ideal_permutation_vector);

```

Storing a full permutation vector for small frames is simple but expensive. The most straight forward solution for this problem is to recognise that there is a patter that can be exploited. This way it is possible to generate the addresses as they are needed.

#### **3.3.2** memory block address generator as described in the literature

One way of generating this permutation vector is by using equation 2.6 [9, 10, 11]. This equation has been modified a bit to suit the example.

$$\mathcal{P}_i = V \times (i\%H) + \left\lfloor \frac{i}{H} \right\rfloor \tag{3.14}$$

H stands for horizontal and represents the column count while V stands for vertical and represents the column depth. This permutation vector is generated by the use of a counter, this counter value is represented by i and goes from 0 to N. Equation 3.14 can be split into two parts along the sum operation. The first part iterates over the rows. This is done by moving in steps that are the size of a column width, which is achieved by the multiplication of the counter value i with V. The counter value i wraps around and continues back at the beginning of the row duo to the modulo operation. The second part determines what row is being accessed by providing an offset value. This is done by dividing the counter value by the column count and rounding it down. When the first part is finished traversing a row, the second part will increase the offset by one so that the first part will will start traversing the next row. The MATLAB code that puts this theory into action can be seen in Listing 3.2

Listing 3.2: MATLAB code that generate address with a modulo of an index

```

1

frame_size = 12:

2

column_count = 3:

3

column_size = frame_size / column_count;

4

input = 0:(frame_size -1); %neutral element

5

6

permutation = zeros(1, frame_size);

7

for i=0:(frame_size -1)

8

index = column_size * mod(i, column_count) + floor(i/

column_count);

9

permutation(i+1) = input(index+1);

10

end

11

12

disp(input)

```

Figure 3.1: alternative configuration for the address generator, 8 PSK

Figure 3.2: Alternative configuration for the address generator, 16 APSK

#### 13 **disp**(permutation)

This generator does its job well, but the multiplication and division operation are expensive to implement in hardware. The modulo operation on the other hand is simply not synthesizable unless it is a power of 2 or a custom implementation.

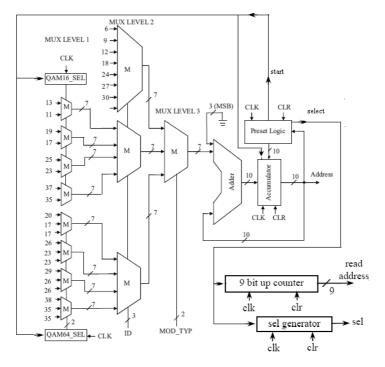

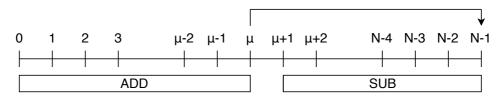

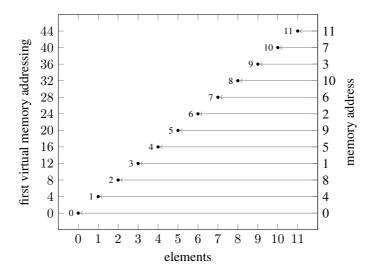

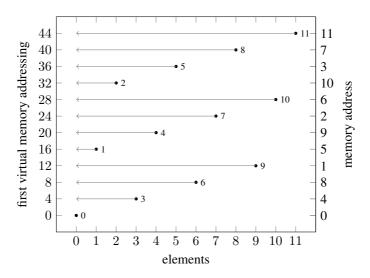

The same function, however, can be implemented using a counter, a full adder and a FSM for some needed intelligence. The counter will be used to offset the row. The adder copies the counter value and repeatedly adds the column size value to it in order to traverse the row. At the end of the row the counter is increased by one and serves as the next address. Afterwards the adder takes over the address generation. This continues until the counter reaches a threshold where it resets back to zero for the next frame. This operation is visualised in Figure 3.1 for the case of 8 PSK and in Figure 3.2 for the case of 16 APSK. To switch from one configuration to the next the, the only parameters that would have to change are the counter threshold and the column size value that is used in the addition.

## **3.3.3** memory block address generator based on a linear congruential generator

Another way to generate the addresses is by using a Linear congruential Generator (LCG) that recursively generates all the elements of the permutation. An LCG is usually used as a simple random number generator. In this case it will be appropriated to generate addresses in an orderly fashion by constructing what would generally be called a bad and predictable random number generator. The general formula has three parameters and looks as follows:

$$x_{n+1} = a \times X_n + b \mod m \tag{3.15}$$

Parameter a is set to one because no multiplication is needed to achieve the goal. Parameter b is set to the  $column\_size$  value in order to traverse the row. Parameter m is set to N-1. When the last element of the first row is accesses, the next address after the addition becomes N, the remainder after the modulo operation becomes 1. This serves as the offset for the next row and accumulates with other remainders as the generator progresses. After adjusting the formula in equation 3.15, the new formula now looks as follows:

$$\mathcal{P}_{i+1} = \mathcal{P}_i + column\_size \mod (N-1)$$

(3.16)

The permutation vector that this formula generates, however, is incomplete. This is because N-1, which is supposed to be the final value in the permutation, becomes a 0 duo to the modulo operation and ends the cycle one element short. It is therefore necessary to pause the sequence and hard-code the final address at the end of every sequence. Luckily this address is always the same regardless of the configuration of the interleaver. The MATLAB code that demonstrates this formula can be seen in Listing 3.3.

Listing 3.3: MATLAB code that generate addresses recursively

```

1

frame_size = 12;

2

column_count = 3;

3

column_size = frame_size / column_count;

4

input = 0:(frame_size -1); %neutral element

5

6 out = zeros(1, frame_size);

7

index = 0;

8

for i = 0: frame_size -1

9

out(i+1) = input(index+1);

index = mod((index + column_size)), frame_size -1);

10

11

end

12

out(frame_size) = input(frame_size);

13

14

disp(input)

15

disp(out)

```

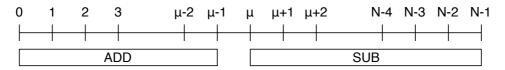

This recursive calculation consists of two operations, a sum operation and a modulo operation. The modulo operation can be simplified when taking into account the fact that the input range is always constrained to a certain interval. Consider the following case where  $\mathcal{P}_i \in [0, m-1]$  and  $column\_size \in [0, m-1]$ , in which m stands for the modulo value. The sum of both lies in the interval of [0, 2(m-1)]. A modulo operation can be realised as a conditional subtraction with m if the input is within the interval of [0, 2m-1]. Because the interval of the sum is a subset of the simplified modulo interval, it is possible to apply this simplification. The result of the subtraction of m from the sum would result in  $\mathcal{P}_{i+1}$  ending up in the interval of [0, m-2], which is a subset of the original input  $\mathcal{P}_i$ , meaning that the maximum value that the simplified modulo can accept, is never exceeded in all subsequent iterations of this formula. Keep in mind that the value of m is defined as N-1.

The next simplification that can be achieved is by combining the addition and conditional subtraction into a single operation. Instead of checking whether or not the sum is greater then or equal to modulo m, the input is compared with a value  $\mu$  which is defined as:

$$\mu = m - column\_size \tag{3.17}$$

$$= N - 1 - column\_size \tag{3.18}$$

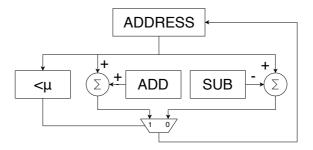

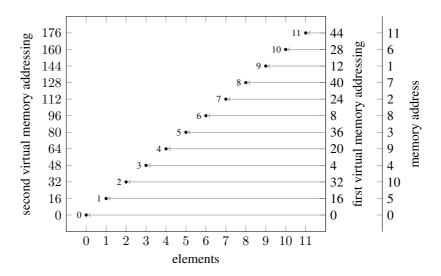

If the value of  $\mathcal{P}_i$  is smaller then  $\mu$ , then the result of the sum will be smaller then m. If  $\mathcal{P}_i$ , on the other hand, is greater than or equal to  $\mu$ , then an addition with *column\_size* followed by a subtraction of m is concatenated into a single subtraction of the value  $\mu$ . In other words, depending on whether or not the input value is smaller then  $\mu$ , the input will receive either an addition with the *column\_size* value or a subtraction with the  $\mu$  value. A block diagram of this construction can be seen in Figure 3.3 where the ADD register contains the value *column\_size* and the SUB register contains the same value as  $\mu$  that is defined in equation 3.17. Figure 3.4 gives an overview of the two different intervals and the arithmetic operation being done the each interval.

Figure 3.3: block diagram of the simplified structure

Figure 3.4: representation of the input range divided in two regions

As stated earlier, this generator can not generate the final address in the permutation vector that is needed to access the final element. Consider the simple example in the case

of 8 PSK modulation, for which the permutation vector is defined as equation 3.12. As it stands now, the way that the current LCG based generator creates the addresses is depicted in Figure 3.5 where the full lines represent the generated sequence. In this case the second

Figure 3.5: example of a sequences created by an LCG based generator

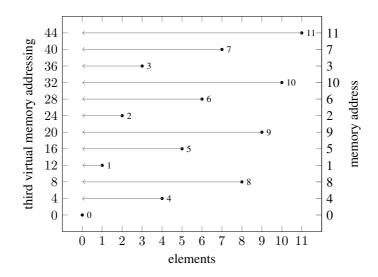

to last element, that is generated before going back to zero, is 7. In the ideal case it would have gone from node 7 to node 11 before going back to node 0 as depicted by the dotted lines in Figure 3.5. In order to achieve this, an intervention at the end of the cycle needs to happen. This can be done by applying the following trick. The subtraction is still done by  $\mu$ , but the input will not be compared with  $\mu$  anymore but with  $\mu + 1$ . The address  $\mu$  is the final address that is generated in the sequence and goes to 0 in the next iteration duo to it being subtracted with  $\mu$  itself. By offsetting the compare value by one, the address that is currently  $\mu$  will be summed with the *column\_size* value and become N - 1, which is the modulo value and the correct final address. Figure 3.6 shows how the intervals of the summation and subtraction have shifted.

Figure 3.6: representation of the input range divided in two regions after modification

The trouble now is that address 0 will be skipped. This is because the address that is now equal to N - 1, will be subjected to a subtraction of  $\mu$ , which will result in the second element of the permutation. By comparing the current address value with N - 1 it is possible to reset the address on that condition and force it to 0 to restart the sequence.

This design is much more simpler then the design suggested in section 3.2.3 because it contains no FSM. The address is generated deterministically based on the previous value. Because of this, the choice has been made to go forward with this design. Simplicity of course is not the only consideration, later on it will become clear why this design is so powerful.

#### 3.3.4 expanding from examples to real use cases

All the above designs have been explained using small examples. What follows now is MATLAB code that proves these concepts on the same scale of the application with real input sizes and real interleaver configurations. Each frame will be accompanied by two data fields. The first one is *frame\_select*, it will tell if the interleaver is dealing with a normal frame or a small frame. The second one is the APSK\_select, it tells the interleaver what modulation scheme will be used for the transmission of this frame. The column configuration of the interleaver depends on what modulation scheme sill be used as explained in section 2.3.2. A neutral element is is interleaved using the first high level model and compared to the two lower level models for all valid configurations. The exception is the 128APSK that needs to be verified separately in a separate MATLAB script because of the added zero padding that increases the input size to 64806 bits. The full MATLAB test script can be seen in Listing 3.4

Listing 3.4: MATLAB script that compares all the modles

```

close all; clear all; clc

1

2

max_disp_size = 9;

3 %% parameters

4

frame_select = 0;

5

% 0 -> 64800 bits

6

% 1 -> 16200 bits

7

APSK_select = 0;

8

% 0 -> 8 PSK

9

% 1 -> 16 APSK

10

% 2 -> 32 APSK

% 3 -> 64 APSK

11

% 4 -> 128 APSK

12

13

% 5 -> 256 APSK

14

%% constants

frame_size = [64800, 16200]; % 20 bit wide input

15

column_count = [3, 4, 5, 6, 7, 8];

16

column_size = [ [21600, 16200, 12960, 10800, 0, 8100],

17

18

[5400, 4050]

3240,

0.

0, 0

1 1:

19

frame_size = frame_size(frame_select+1);

20

column_count = column_count(APSK_select+1);

21

column_size = column_size(frame_select+1, APSK_select+1);

input = 0:(frame_size -1); % neutral element

22

23

%% High level model of the block interleaver using matrix

transposition.

24

Interleaver_A = reshape(input,[], column_count);

25

Interleaver_B = Interleaver_A';

26

ideal_permutation_vector = reshape(Interleaver_B, 1, []);

27

disp ("ideal_permutation_vector");

28

disp(ideal_permutation_vector(1: max_disp_size))

29

disp(ideal_permutation_vector(frame_size-max_disp_size+1:

frame_size))

30

%% for loop generation

31

```

```

32

for i=0:(frame_size -1)

33

index = column_size * mod(i, column_count) + floor(i/

column_count);

34

loop_permutation_vector(i+1) = input(index+1);

35

end

disp("loop_permutation_vector. Equal to ideal: "+isequal(

36

ideal_permutation_vector , loop_permutation_vector ) );

37

disp(loop_permutation_vector(1:max_disp_size))

38

disp (loop_permutation_vector (frame_size - max_disp_size +1: frame_size

))

%% Linear Congruent Generator (LCG) permuation model

39

40

LCG_permutation_vector = zeros(1, frame_size);

41

index = 0;

for i = 0: frame_size -1

42

43

LCG_permutation_vector(i+1) = input(index+1);

44

index = mod((index + column_size) , frame_size -1) ;

45

end

46

LCG_permutation_vector(frame_size) = input(frame_size);

47

disp("LCG_permutation_vector. Equal to ideal: "+isequal(

ideal_permutation_vector, LCG_permutation_vector));

48

disp(LCG_permutation_vector(1:min(max_disp_size, frame_size)))

49

disp(LCG_permutation_vector(frame_size - max_disp_size +1: frame_size)

)

```

### 3.4 block-interleaver with only one memory block

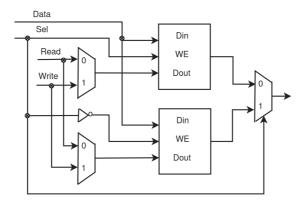

All the design so far have assumed that a double memory buffer is used. Such a configuration can be seen in Figure 2.6. With this configuration it is possible to interleave subsequent frames under different configurations. A frame can be read from one block with one configuration, afterwards the address generator switch to another set of register values using a LUT, and then reads the other frame in the other block under a different configuration. High performance interleaving has always being done by alternating two memory blocks, until now.

In this Master's thesis an attempt is made at creating an interleaver that uses one memory block for the interleaving process without sacrificing all the capabilities of a double memory block interleaver.

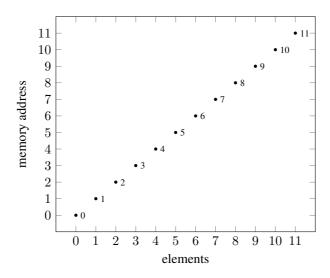

#### 3.4.1 One-memory-block design explained

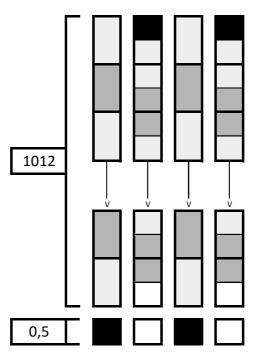

The inspiration of using only one memory block came from reading the Stratix 10 memory documentation [14]. As explained in section 2.5.3, the M20K modulo is capable of doing a concurrent read and write to the same address. The idea is to read out a piece of the current frame, while at the same time writing a piece of the new frame to the same address. In a larger sense, current frames are constantly swapped out with new frames, as if it was a giant shift register. As a demonstration, a 12 bit frame will be interleaved using a 4 by 3 block configuration for 8 PSK modulation. The contents of the interleaver in each step can

be seen in Figure 3.7. At first, the interleaver memory block is empty, this is visualised

| S   | tep | 0   | 1  | step | 1   |    | step | 2  |    | step | 3  | S   | tep | 4  | 5  | step | 5   |

|-----|-----|-----|----|------|-----|----|------|----|----|------|----|-----|-----|----|----|------|-----|

| [0] | Ō   | 0   | [0 | 4    | 8]  | [0 | 1    | 2] | [0 | 3    | 6] | [0] | 9   | 7] | [0 | 5    | 10] |

| 0   | 0   | 0   | 1  | 5    | 9   | 3  | 4    | 5  | 9  | 1    | 4  | 5   | 3   | 1  | 4  | 9    | 3   |

| 0   | 0   | 0   | 2  | 6    | 10  | 6  | 7    | 8  | 7  | 10   | 2  | 10  | 8   | 6  | 8  | 2    | 7   |

| 0   | 0   | 0   | 3  | 7    | 11  | 9  | 10   | 11 | 5  | 8    | 11 | 4   | 2   | 11 | 1  | 6    | 11  |

| Ē e | mpt | y Ī | fı | ram  | e 1 | f  | rame | 2  | f  | rame | 3  | fr  | ame | 4  | fı | rame | e 5 |

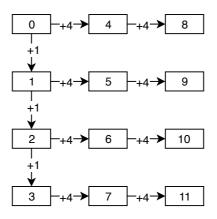

Figure 3.7: interleaver contents of example

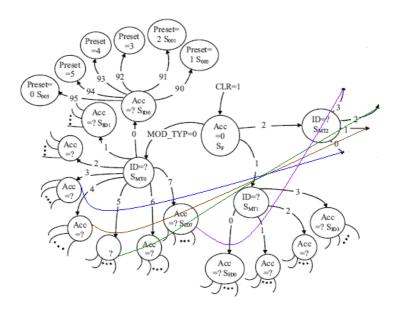

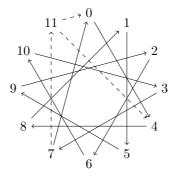

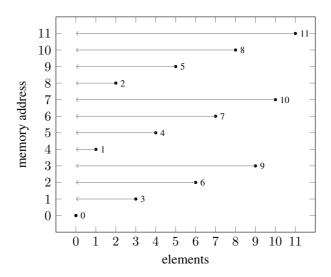

at step 0 with the memory block initialised to zero. The first frame, which is represented by a neutral element, is written sequentially into the memory. (Please note that the linear addressing of the matrix, in a sense what element is selected by a given address, coincides with the way that the neutral element is written to in step 1. In other words, accessing address 5 would return 5 at step 1.) The correct permutation vector to read and interleave frame 1 is given by equation 3.12. At the same time that frame 1 is read from memory, frame 2 will be stored to memory. Elements 0, 4 and 8 in the first row at step 1 are read, while at the same time, elements 0, 1 and 2 of frame 2 are stored in their place. The same goes for all the remaining elements of frames 1 and 2. Frame 1 is interleaved and frame 2 is now stored in memory, as can be seen in Figure 3.7 at step 2. Frame 2 is interleaved by reading addresses number 0, 5, and 10, which will access all the elements of the first row, while at the same time, elements 0, 1 and 2 of frame 3 are stored in their place. The same goes for all the remaining elements of frames 2 and 3. This cycle would ideally repeat indefinitely. In this case it does because reading out frame 5 in step 5, in the sequence of the unity permutation 1, while storing the next frame, would put the interleaver contents in the same state as step 1. There are some challenges that need to be overcome in order for this idea to work. The big question is: What permutation vector is needed to read out frame 2. The bigger question is: What permutation vector is needed to read out all the subsequent frames. The biggest question is: how would one generate these permutation vectors?

It has been confirmed that when writing a frame to memory in the sequence of 1, which is the unity permutation or in this case linear addressing, the frame can be interleaved by reading it in the sequence of  $\mathcal{P}$ . When a frame that has been written in the sequence of  $\mathcal{P}$ , like frame 2 in step 2, through experimentation with MATLAB it has been found that, it can be read and interleaved by reading it in the sequence of  $\mathcal{P} \times \mathcal{P} = \mathcal{P}^2$ . Frames that are written in a sequence of  $\mathcal{P}^2$  can be correctly interleaved by reading them in the sequence of  $\mathcal{P}^3$ . In general frames can be interleaved by writing them in the sequence of  $\mathcal{P}^n$  and reading them in the sequence of  $\mathcal{P}^{n+1}$

#### 3.4.2 permutation groups

The permutation vectors needed to read all the subsequent frames are listed below.

| 1 = [0]                                           | 1  | 2  | 3       | 4     | 5         | 6  | 7  | 8  | 9 | 10 | 11] | (3.19) |

|---------------------------------------------------|----|----|---------|-------|-----------|----|----|----|---|----|-----|--------|

| $\mathcal{P} = \begin{bmatrix} 0 \end{bmatrix}$   | 4  | 8  | 1       | 5     | 9         | 2  | 6  | 10 | 3 | 7  | 11] | (3.20) |

| $\mathcal{P}^2 = \begin{bmatrix} 0 \end{bmatrix}$ | 5  | 10 | 4       | 9     | 3         | 8  | 2  | 7  | 1 | 6  | 11] | (3.21) |

| $\mathcal{P}^3 = \begin{bmatrix} 0 \end{bmatrix}$ | 9  | 7  | 5       | 3     | 1         | 10 | 8  | 6  | 4 | 2  | 11] | (3.22) |

| $\mathcal{P}^4 = \begin{bmatrix} 0 \end{bmatrix}$ | 3  | 6  | 9       | 1     | 4         | 7  | 10 | 2  | 5 | 8  | 11] | (3.23) |

| $\mathcal{P}^5 = \mathbb{1}$                      |    |    |         |       |           |    |    |    |   |    |     | (3.24) |

| $\mathcal{P}^n = \mathcal{P}^n$                   | -5 | 1  | $n \in$ | [5, ] | $\infty[$ |    |    |    |   |    |     | (3.25) |

What has been stumbled upon is actually permutation group with a neutral element 1 and a seed element  $\mathcal{P}$ . As empirical evidence, one could manually read out the contents of the interleavers in Figure 3.7 by using the above mentioned permutation vector in order to interleave the individual frames and check the validity for themselves. Through experimentation with MATLAB it has been found that all the permutations in and of themselves can be generated using the same structure as described in section 3.3.3. The generator would now look as follows:

$$\mathcal{P}_{i+1}^n = \mathcal{P}_i^n + b(n) \mod (N-1) \tag{3.26}$$

$$b(n) = [1, 4, 5, 9, 3] \tag{3.27}$$

Vector b in equation 3.27 is a look up table that stores all the second elements of all the permutations in a LUT. The address generator that can be used is the same as the one depicted in Figure 3.3. If the current permutation vector is  $\mathcal{P}^n$  then in order to generate vector  $\mathcal{P}^{n+1}$ , b(n+1) is put into the ADD register, N - 1 - b(n+1) is put into the SUB register, N - 1 - b(n+1) + 1 is put into the  $\mu$  register, and the address is reset to zero.

#### 3.4.3 challenge in frame size scalability

The previous example has demonstrated the possibility of using the concurrent read and write operations, to interleaver subsequent frames with the use of only one memory block. The theory has been proven to work with small frames, where all the parameters needed to generate the full permutation group, can be stored in a small LUT. For larger frames, however, the permutation groups become larger, which in turn means that the LUT would have to store a significantly larger amount of parameters.

Because every permutation can be generated from the second element, it can therefore be used as a unique key, that identifies the full permutation vector. It is therefore possible to count all the permutation vectors in a group by comparing only the second elements. Counting all the elements is done by preforming permutations until the neutral element is encountered, which has a second element of 1. All the permutation group sizes for all the valid interleaver configurations can be seen in Table 3.1. They have been counted using the MATLAB code found in Listing: 3.5

| Modulation  | 8PSK  | 16APSK | 32APSK | 64APSK | 128APSK | 256APSK |

|-------------|-------|--------|--------|--------|---------|---------|

| column size | 3     | 4      | 5      | 6      | 7       | 8       |

| normal      | 27767 | 6941   | 27767  | 9255   | (995)   | 4627    |

| small       | 3983  | 1991   | 7967   | N/A    | N/A     | N/A     |

Table 3.1: permutation group element count for each interleaver configuration

Listing 3.5: MATLAB script that counts all the elements of all the used permutation groups

```

1

close all; clear all; clc

max_disp_size = 9;

2

3

%% parameters

4

frame_select = 0;

5

\% 0 \rightarrow 64800 bits, 1 \rightarrow 16200 bits

6

APSK_select = 1;

1 \rightarrow 8 PSK

7

% 0-> bypass

8

% 2 -> 16 APSK

3 \rightarrow 32 APSK

9

% 4 -> 64 APSK

5 -> 128 APSK

10

% 6 -> 256 APSK

11

%% constants

frame_size = [64800, 16200]; % 64806 in case of 128APSK

12

column_count = [3, 4, 5, 6, 7, 8];

13

column_size = [ [21600, 16200, 12960, 10800, 0, 8100],

14

15

[5400, 4050]

3240, 0,

0, 0 ] ];

16 frame_size = frame_size(frame_select+1);

17

column_count = column_count(APSK_select+1);

18

column_size = column_size(frame_select+1, APSK_select+1);

19

input = 0:(frame_size - 1); %neutral element

20 %% High level model of the block interleaver using matrix

transposition.

21

Interleaver_A = reshape(input,[], column_count);

Interleaver_B = Interleaver_A ';

22

23

ideal_permutation_vector = reshape(Interleaver_B, 1, []);

24 disp("ideal_permutation_vector");

25

disp(ideal_permutation_vector(1:max_disp_size))

26 %% counting the permutation group elements

27

count = 0;

28

element = ideal_permutation_vector;

29

while (element (2) = 1)

30

element=element(ideal_permutation_vector+1);

31

count = count + 1;

32

end

disp(element(1:max_disp_size))

33

34

disp(count);

```

To do uninterrupted interleaving for all configurations, a total of 91293 parameters of 16 bit need to be saved in a LUT, which comes down to 1460688 bits of data, which is around the size of 22.54 normal frame. Storing this much data would defeat the initial purpose of cutting down on memory usage.

#### 3.4.4 possible compromise for large frames

One way that this design can be salvaged is by breaking off after the first few iterations and reset the interleaver. This will slightly lower the maximum throughput but would otherwise make for an excellent low cost interleaver that can handle data in bursts.

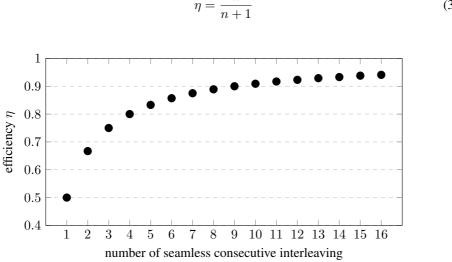

It takes a full time-frame for a frame to be both written to and read from memory. When only one frame is interleaved, the time efficiency drops to 50% as only one frame is processed every two time-frames. Traditional block-interleavers would therefor use two memory block in order to a achieve a full throughput. Interleaving consecutive frames using the above mentioned design will net a higher time efficiency because it takes n + 1time-frames to process n frames. The formula for efficiency can be seen in equation 3.28 along with the graph of the first 16 values of n in Figure 3.8.

$$=\frac{n}{n+1}$$

(3.28)

Figure 3.8: interleaver time efficiency

The efficiency has a diminishing return, but it is possible to achieve a maximum throughput of 94.1% with only 16 values for each configuration. In order for this interleaver to work continuously, however, a buffer at the input and output is needed to smooth out the inconsistencies duo to the need for a periodic reset. This again defeats the purpose of cutting down on memory usage, if it means that multiple buffers must be introduced.