# GNU Debugger for Single-ISA Heterogeneous MAny-Core System (SHMAC)

Bjørn Christian Seime

Master of Science in Computer ScienceSubmission date:June 2014Supervisor:Lasse Natvig, IDICo-supervisor:Asbjørn Djupdal, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

SHMAC is an FPGA-based multicore prototype developed in a research project within the Energy Efficient Computing Systems (EECS) strategic research area. SHMAC is planned to be an evaluation platform for research on heterogeneous multicore systems. The goal of the SHMAC project is to propose software and hardware solutions for future power-limited, heterogeneous systems. The main goal of this master thesis project is to implement debugging support for SHMAC. The first part is to implement general support for GDB by developing a GDB stub for SHMAC and necessary host driver support. The second part is to facilitate kernel debugging of Barrelfish on SHMAC. If time permits, the student should also implement and document

- debugging support for multiple SHMAC cores.

- debugging support for user space programs on Barrelfish.

- debugging support for Linux kernel on SHMAC.

- more advanced debugger support of multiple cores with some form of visualisation of core usage and communication.

Supervisor: Lasse Natvig and Asbjørn Djupdal.

# Abstract

Processors have historically attained performance improvements primarily by increasing frequency and the number of transistors. As the transistor density increases, keeping the power density constant gets harder. As a result, future processors will not be able to power all transistors simultaneously without exceeding the power budget. This phenomenon is coined *Dark Silicon*, referring to the part of the silicon that must be left unpowered. The issue with dark silicon can be mitigated by building heterogeneous computing systems. Such systems consist of several specialised components, each highly efficient in performing a specific task and workload.

The SHMAC project was initiated by NTNU to investigate the challenges in designing heterogeneous computing systems. The output of the project is a heterogenous processor called SHMAC, which has an architecture consisting of a grid of computing tiles. One of the available computing tile is an ARMv3 compliant CPU core. The current software for SHMAC is primarily using this tile as the target CPU.

This thesis presents the first functional debugger for SHMAC. The debugger is based on the *GNU Debugger* (GDB), a popular open-source debugger maintained by the *Free Software Foundation*. Future software development on SHMAC will greatly benefit from having a proper tool for debugging. Another contribution is the integration of the debugger with Barrelfish, the first functional operating system for SHMAC. The integration facilitates kernel debugging and debugging of user programs running on Barrelfish.

# Sammendrag

Prosessorer har historisk sett oppnådd forbedringer i ytelse ved å øke frekvensen og antall transistorer. Etter hvert som transistor-tettheten øker blir det vanskeligere å holde energiforbruket per areal konstant. Resultatet er at fremtidens prosessorer ikke vil kunne bruke alle transistorer samtidig uten å overskride tillatt effektnivå. Denne trenden blir kalt for *Dark Silicon*, som refererer til den del av silisiumet som må være avskrudd. Problemene med *dark silicon* kan delvis løses ved utvikling heterogene datamaskiner. Slike maskiner består av flere spesialiserte komponenter, der hver komponent er effektiv i å løse en spesifik oppgave av en gitt størrelse.

SHMAC-prosjektet ble startet av NTNU for å undersøke utfordringene rundt utvikling av heterogene datamaskiner. En heterogen prosessor kalt SHMAC er et resultat av dette prosjektet. Denne prosessoren har en arkitektur som består av et gitter av beregningsenheter. En av de tilgjengelige beregningsenhetene er en ARMv3-kompatibel CPU-kjerne. Nåværende programvare for SHMAC er primært laget for denne beregningsenheten.

Denne hovedoppgaven presenterer den første fungerende debuggeren for SHMAC. Debuggeren er basert på *GNU Debugger* (GDB), en velkjent debugger fra *Free Software Foundation*. Fremtidig programvareutvikling for SHMAC vil ha stor nytte av å ha et skikkelig verktøy for feilsøking. Et annet bidrag er integrasjon av debuggeren mot Barrelfish, det første funksjonelle operativsystemet for SHMAC. Denne integrasjonen forenkler feilsøking av operativsystemkjernen og programmer som kjører på Barrelfish.

# Preface

This report is submitted to the Norwegian University of Science and Technology in fulfillment of the requirements for master thesis.

This work has been performed at the Department of Computer and Information Science, NTNU, with Prof. Lasse Natvig as the supervisor, and Asbjørn Djupdal as co-supervisor.

# Acknowledgments

Thanks to Benjamin Bjørnseth for providing outstanding technical assistance with the ARM toolchain, SHMAC and Barrelfish.

Thanks to Asbjørn Djupdal for producing an enhanced ABP tile for the only purpose of aiding this project.

Thanks to Håkon Amundsen and Joakim Andersson for providing me with their ARMv3 version of the Amber CPU core.

# Contents

| Li            | st of | Figure | es                                    | xi       |

|---------------|-------|--------|---------------------------------------|----------|

| $\mathbf{Li}$ | st of | Tables | 3                                     | xiii     |

| $\mathbf{Li}$ | st of | Abbre  | eviations                             | xv       |

| 1             | Intr  | oducti | on                                    | 1        |

|               | 1.1   | Trends | s in Computer Architecture            | 1        |

|               | 1.2   | The S  | HMAC Project                          | 2        |

|               | 1.3   | Barrel | fish for SHMAC                        | 2        |

|               | 1.4   | Debug  | ging on SHMAC                         | 2        |

|               | 1.5   | Assign | ment Interpretation                   | 3        |

|               | 1.6   | Contri | butions                               | 4        |

|               | 1.7   | Thesis | Organization                          | 4        |

| <b>2</b>      | Bac   | kgroui | nd                                    | <b>5</b> |

|               | 2.1   | Debug  | $\operatorname{ging}$                 | 5        |

|               |       | 2.1.1  | Debugger                              | 5        |

|               |       | 2.1.2  | Black Box Debugging                   | 6        |

|               |       | 2.1.3  | Remote Debugging                      | 6        |

|               |       | 2.1.4  | Debugging Techniques without Debugger | 7        |

|               |       | 2.1.5  | Debugging Techniques using Debugger   | 8        |

|               | 2.2   | GNU I  | Debugger                              | 9        |

|               |       | 2.2.1  | Debugging Target                      | 9        |

|               |       | 2.2.2  | Remote Target                         | 9        |

|               |       | 2.2.3  | GDB Remote Serial Protocol            | 11       |

|               |       | 2.2.4  | GDB for ARM                           | 14       |

|               | 2.3   | The S  | HMAC Platform                         | 14       |

|               |       | 2.3.1  | Test platforms                        | 15       |

|               |       | 2.3.2  | Processor Tile                        | 17       |

|               |       | 2.3.3  | ARMv3 ISA                             | 17       |

|               | 2.4   | Barrel | fish                                  | 21       |

|   |               | 2.4.1 The Multikernel Model                                                                  |

|---|---------------|----------------------------------------------------------------------------------------------|

|   |               | 2.4.2 Barrelfish Architecture                                                                |

|   |               | 2.4.3 The SHMAC Port                                                                         |

|   | 2.5           | Related work 25                                                                              |

| 3 | $\mathbf{GD}$ | B for Bare-Metal Programs 25                                                                 |

|   | 3.1           | Specification                                                                                |

|   | 3.2           | Existing Work                                                                                |

|   | 3.3           | Development Process                                                                          |

|   | 3.4           | Debugger Setup                                                                               |

|   | 3.5           | Implementation                                                                               |

|   |               | 3.5.1 Stub Overview                                                                          |

|   |               | 3.5.2 Debugger Initialization                                                                |

|   |               | 3.5.3 Exception Handler $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 30$  |

|   |               | 3.5.4 Host Communication $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 32$ |

|   |               | 3.5.5 Breakpoints                                                                            |

|   |               | 3.5.6 Single Stepping                                                                        |

|   |               | 3.5.7 GDB Interrupts                                                                         |

|   |               | 3.5.8 Disabling the Debugger 38                                                              |

|   | 3.6           | Performance Enhancements                                                                     |

|   |               | 3.6.1 Range Stepping                                                                         |

|   |               | 3.6.2 Packet Compression                                                                     |

|   |               | 3.6.3 Binary Transfer Packet 39                                                              |

|   |               | 3.6.4 Disabling Irrelevant Packets                                                           |

|   |               | 3.6.5 Extended Stop Reply 40                                                                 |

|   | 3.7           | Multicore support                                                                            |

|   |               | 3.7.1 Analysis of Implementation Alternatives                                                |

|   |               | 3.7.2 Implementation                                                                         |

| 4 | GD            | B for Barrelfish 45                                                                          |

|   | 4.1           | Motivation                                                                                   |

|   | 4.2           | Specification                                                                                |

|   | 4.3           | Implementation                                                                               |

|   |               | 4.3.1 Overview                                                                               |

|   |               | 4.3.2 Multiprocess Mode                                                                      |

|   |               | 4.3.3 Barrelfish Hooks                                                                       |

|   |               | 4.3.4 Listing Available Processes                                                            |

|   |               | 4.3.5 Attaching a Process                                                                    |

|   |               | 4.3.6 Obtaining the Currently Executing Process                                              |

|   |               | 4.3.7 Providing Debug Symbols                                                                |

|   |               |                                                                                              |

|    | 5.1   | Testing Methodology                                            | 53       |

|----|-------|----------------------------------------------------------------|----------|

|    |       | 5.1.1 GDB for Bare-Metal Programs                              | 53       |

|    |       | 5.1.2 GDB for Barrelfish                                       | 54       |

|    | 5.2   | Test Plan                                                      | 55       |

|    |       | 5.2.1 GDB for Bare-Metal Programs                              | 55       |

|    |       | 5.2.2 GDB for Barrelfish                                       | 57       |

|    | 5.3   | Test Results                                                   | 58       |

|    |       | 5.3.1 GDB for Bare-Metal Programs                              | 58       |

|    |       | 5.3.2 GDB for Barrelfish                                       | 58       |

| 6  | Eva   | luation                                                        | 59       |

| U  | 6.1   | Performance Enhancements                                       | 59       |

|    | 6.2   | Limitations                                                    | 59       |

|    | 0.2   | 6.2.1 Limitations with the Single Stepping Implementation      | 59       |

|    |       | 6.2.2 Using Breakpoints in Multicore Programs                  | 60       |

|    |       | 6.2.3 GDB Interrupts                                           | 61       |

|    | 6.3   | The SHMAC Platform                                             | 61       |

|    | 0.0   | 6.3.1 Benefits of ARMv3                                        | 61       |

|    |       | 6.3.2   Benefits of Multiple TTY Channels                      | 61       |

|    | 6.4   | Comparing the Implementation with The Specification            | 62       |

|    | 0.4   | 6.4.1 GDB for Bare-Metal Programs                              | 62<br>62 |

|    |       | 6.4.1     GDB for Barelfish       6.4.2     GDB for Barrelfish | 63       |

|    | 6.5   | Evaluating Assignment Tasks                                    | 63       |

|    | 0.5   |                                                                | 05       |

| 7  | Fut   | ure Work                                                       | 65       |

|    | 7.1   | Adding ARMv4 Support                                           | 65       |

|    | 7.2   | Adding Debugging Capabilities to SHMAC CPU Core                | 65       |

|    |       | 7.2.1 Breakpoints and Single Stepping                          | 65       |

|    |       | 7.2.2 Range Stepping                                           | 66       |

|    |       | 7.2.3 Dedicated Debug Interface                                | 66       |

| 8  | Con   | clusion                                                        | 67       |

| Re | efere | nces                                                           | 69       |

| Aı | open  | dices                                                          |          |

|    |       | rce code overview                                              | 73       |

| 11 | A.1   | GDB for Bare-Metal Programs                                    | 73       |

|    | A.2   | GDB for Barcelish                                              | 74       |

| -  |       |                                                                |          |

| В  |       | r Guide: Debugging Programs on SHMAC                           | 75       |

|    | B.1   | Install GDB 7.7 for ARM                                        | 75       |

|    | B.2   | Setup ser2net on SHMAC Host Controller                         | 75       |

|              | B.3 | 3 Compile the GDB Stub                      |    |  |

|--------------|-----|---------------------------------------------|----|--|

|              | B.4 | Integrate GDB Stub with Program             | 77 |  |

|              |     | B.4.1 Insert Interrupt Hooks                | 77 |  |

|              |     | B.4.2 Insert Call to gdb_init               | 78 |  |

|              |     | B.4.3 Insert the Initial Static Breakpoint  | 78 |  |

|              |     | B.4.4 Compile the Program with the GDB Stub | 78 |  |

|              | B.5 | Starting a Debugging Session                | 79 |  |

|              | B.6 | Using the Debugger                          | 79 |  |

|              |     | B.6.1 Interrupting the Program              | 79 |  |

|              |     | B.6.2 Static Breakpoints                    | 79 |  |

|              |     | B.6.3 Disabling the Debugger                | 79 |  |

|              |     | B.6.4 Printing the SPSR Register            | 79 |  |

| $\mathbf{C}$ | Use | r guide: Debugging Barrelfish on SHMAC      | 81 |  |

|              | C.1 | Enabling and Disabling Debugging            | 81 |  |

|              | C.2 |                                             | 81 |  |

|              | C.3 |                                             | 82 |  |

|              | C.4 |                                             | 82 |  |

|              |     |                                             | 82 |  |

|              |     |                                             | 82 |  |

# List of Figures

| 2.1  | Screenshot of Winpdb, a debugger for Python.          | 6  |

|------|-------------------------------------------------------|----|

| 2.2  | Screenshot of GDB while debugging a program on SHMAC. | 7  |

| 2.3  | Debugging a local program.                            | 10 |

| 2.4  | Debugging a remote program using GDBServer.           | 10 |

| 2.5  | Debugging a remote program using a GDB stub           | 11 |

| 2.6  | Debugging with GDB over the JTAG interface            | 15 |

| 2.7  | Overview of the SHMAC architecture                    | 16 |

| 2.8  | SHMAC synthesized on RealView development system      | 17 |

| 2.9  | Overview of the ARMv3 instruction set                 | 18 |

| 2.10 | Layout of register file.                              | 19 |

| 2.11 | Format of Program Status Registers                    | 20 |

| 2.12 | The multikernel model.                                | 22 |

| 2.13 | The Barrelfish architecture.                          | 23 |

| 3.1  | Overview of the debugging setup for SHMAC             | 28 |

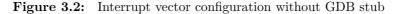

| 3.2  | Interrupt vector configuration without GDB stub       | 29 |

| 3.3  | Interrupt vector configuration with GDB stub          | 29 |

| 3.4  | The finite state machine for GDB IRQ handler.         | 37 |

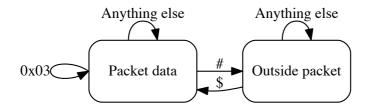

| 3.5  | Range stepping finite state machine.                  | 39 |

| 4.1  | Overview of the GDB setup in Barrelfish.              | 46 |

| 4.2  | The handle_gdb_syscall function.                      | 48 |

# List of Tables

| 2.1 | Obligatory packets for a GDB stub.                            | 13 |

|-----|---------------------------------------------------------------|----|

| 2.2 | SHMAC utility programs                                        | 17 |

| 2.3 | The interrupt vector                                          | 21 |

| 3.1 | Instructions supported by the single step instruction decoder | 36 |

| 5.1 | Unit tests for instruction decoder.                           | 57 |

# List of Abbreviations

**APB** Advanced Peripheral Bus.

**CLI** Command Line Interface.

**CPSR** Current Program Status Register.

**CPU** Central Processing Unit.

FIQ Fast Interrupt.

FPGA Field Programmable Gate Array.

${\bf FSM}\,$  Finite-State Machine.

${\bf GCC}\,$  GNU Compiler Collection.

**GDB** GNU Debugger.

**GNU** GNU's not UNIX.

**ILP** Instruction Level Parallelism.

**IRQ** Interrupt Request.

${\bf ISA}\,$  Instruction Set Architecture.

LR Link Register.

**OS** Operating System.

**PC** Program Counter.

**POSIX** Portable Operating System Interface.

${\bf RAM}\,$  Random Access Memory.

**RISC** Reduced Instruction Set Computing.

**SHMAC** Single ISA Heterogeneous MAny-core Computer.

${\bf SPSR}\,$  Saved Program Status Register.

SVC Supervisor Call.

${\bf SWI}$  Software Interrupt.

$\mathbf{TTY}$  TeleTY pewriter.

**UND** Undefined.

# Chapter Introduction

# 1.1 Trends in Computer Architecture

The processor has seen an impressive increase in performance since its conception. Most of the performance gains has been achieved by increasing the Instruction Level Parallelism (ILP). Increasing the ILP benefits the single core performance, but requires the use of more transistors. The result is that the number of transistors per processor has increased by an exponential rate. This trend is known as *Moore's Law*, named after the Intel co-founder who described the trend in a paper from 1965  $[M^+65]$ .

The performance increase through ILP and frequency scaling stagnated in the early 2000s. The power consumption and the core temperature reached the limit of what cooling systems could handle. The single core designs had become so complex that any increase in ILP would require a substantial increase of transistor usage and power consumption [BC11]. Higher performance had to be gained through other means. The multicore design was the answer to this issue. Multicore processors were designed by placing multiple homogenous processor cores on a single chip.

Processor designs have also relied on *Dennard scaling*, a law related to Moore's Law. Dennard scaling states that power density stays constant as transistors gets smaller  $[DGR^+74]$ . As the transistor dimension shrinks, it becomes harder to keep reducing the power consumption per transistor, leading to the failure of Dennard scaling. The result is that an exponential increase in number of transistors leads to an exponential increase in total power consumption. Thus only parts of a processor can be powered on at a given time to ensure that the chip does not overheat. This phenomenon is called *Dark Silicon* [EBSA<sup>+</sup>11].

A potential strategy for mitigating this problem is heterogeneous computing [Tay12]. Instead of making homogenous multicore processors, future multicore processor may consist of several specialized components, each highly efficient in performing a

#### 2 1. INTRODUCTION

specific task and workload. In theory, such processors may have only the most efficient component enabled at a time, yielding higher performance and power efficiency than traditional, general-purpose processors.

# 1.2 The SHMAC Project

The SHMAC project is a research project initiated by the Energy Efficient Computing Systems (EECS) group at NTNU [EECb]. EECS is a joint research initiative by the Department of Electronics and Telecommunications and the Department of Computer and Information Science [EECa]. The primary focus is to investigate the challenges in designing heterogeneous computing systems. A subproject of this research initiative is the Single-ISA Heterogeneous MAny-Core System (SHMAC). It is a generic architecture for implementing single-ISA heterogeneous multicore systems. The architecture consists of a grid of computing tiles, each implementing a specific routing interface. The most prominent tile available is an ARMv3 compliant CPU core. The current software for SHMAC is primarily using this tile as the target CPU.

# 1.3 Barrelfish for SHMAC

Barrelfish is an experimental operating system designed for future multi- and manycore systems [Zü, BBD<sup>+</sup>09]. It is developed by ETH Zürich with collaboration from Microsoft. The motivation behind Barrelfish is the current trend in hardware design where the number of cores and hardware diversity increases. The architecture of Barrelfish is designed after the *multikernel model* which treats the machine as a network of independent cores. The machine is modelled a distributed system; there is no intercore sharing and the cores communicate solely through message passing. Benchmarks on manycore systems have demonstrated that Barrelfish scales better than conventional operating systems such as Linux and Windows.

An initial port of Barrelfish to SHMAC was developed as a result of a student project in fall 2013 [BS13]. The port proved to run stable on SHMAC, although only utilizing a single core. Barrelfish became the first stable operating system for SHMAC. The development of the port continued in spring 2014 with the target goal of adding multicore support [Bj014].

# 1.4 Debugging on SHMAC

The report from the Barrelfish porting project stated that the lack of a debugger was a serious limitation with the SHMAC platform. Diagnosing errors was a challenging task that was time consuming and hard to carry out. Debugging was performed by examining the output from inserted print statements and the content of memory dumps taken during execution. These two techniques are far from ideal. Inserting print statements may accidentally alter the semantics of the program and requires recompilation whenever a new print statement is inserted. Examining memory dumps is a complicated task that requires detailed knowledge about how a program is laid out in memory.

A proper debugger will simplify software development on SHMAC. Locating bugs will be easier and less time consuming, enabling software developers to focus on implementing functionality rather than spending time on fixing bugs.

Terje Schjelderup investigated the debugging capabilities of SHMAC in a report from fall 2013 [Sch13]. The report states why having a debugger for SHMAC is important, and it also briefly describe how to add GDB support to SHMAC without having to perform any larger modifications to the SHMAC hardware.

# 1.5 Assignment Interpretation

The following tasks were extracted from the assignment text:

# Mandatory:

- **T1** Add support for debugging with the GNU Debugger (GDB) on SHMAC. This step includes the development of a GDB remote stub and any host drivers required to enable GDB debugging.

- T2 Facilitate debugging of the Barrelfish kernel using the software developed in T1.

# **Optional:**

- T3 Extend the debugger implementation in T1 and T2 to enable debugging of multiple SHMAC CPU cores simultaneously.

- ${\bf T4}\,$  Extend the debugger implementation in  ${\bf T2}$  to facilitate debugging of user programs in Barrelfish.

- ${f T5}$  Extend the debugger implementation in T1 to enable debugging of the Linux kernel.

- T6 Implement a software providing visualisation of core usage and communication.

Most effort will likely be spent on T1. The other tasks are dependent on the output of this task. T2 is the dependent on the success of T1, and cannot be started until the software in T1 has reached a stable state. T3 is defined as a separate task from T1

#### 4 1. INTRODUCTION

as it is believed to be technically challenging and time consuming. It is the highest prioritized task among the optional tasks since debugging multicore programs are an essential feature on SHMAC. T4 provides an extension of the software in T2. This task is believed to be a relatively simple once kernel debugging of Barrelfish is finished. T5 is related to a master thesis working on porting Linux to SHMAC [AA14]. This task will be initiated if they are in great need of a debugger and if time permits. T6 is not directly related to the other tasks, although it provides SHMAC with monitoring capabilities which can be useful when debugging.

# 1.6 Contributions

This thesis provides the SHMAC project with a fully functional debugger. The main contribution is support for the GNU Debugger (GDB), an open-source debugger developed and maintained by the Free Software Foundation. This thesis describes the implementation of a GDB remote stub, a small software component, which linked to a SHMAC program, enables debugging using GDB.

This thesis does also provide GDB support for the Barrelfish operating system. The GDB integration enables debugging of the OS kernel and system processes.

# 1.7 Thesis Organization

- Chapter 1: Introduction presents the motivation and goals of the Master Thesis.

- **Chapter 2: Background** presents an overview of common debugging concepts, the SHMAC platform, GNU Debugger (GDB) and the Barrelfish operating system.

- Chapter 3: GDB for Bare-Metal Programs describes the implementation of the GDB debugger for SHMAC.

- Chapter 4: GDB for Barrelfish describes how the debugger was integrated into Barrelfish.

- Chapter 5: Testing the debugger describes how the debugger was tested and verified.

- **Chapter 6: Evaluation** evaluates the debugger. Limitations with the current implementation are presented.

- Chapter 7: Future work suggests the direction for any future work.

- Chapter 8: Conclusion contains the concluding remarks for this project.

# 2.1 Debugging

Debugging is the process of discovering and eliminating defects in a computer program. Software defects and anomalies are more commonly known as *bugs*. Debugging is an essential part of software development, as it is hard to write fault-free code on a first attempt, and finding the bugs can be challenging. Static analysis and code reviews will identify some bugs, while other bugs are not discovered until testing or running the program live. Some debugging techniques involves inspecting the state of the system after the program has finished.

# 2.1.1 Debugger

A debugger is a tool used to facilitate debugging of a program. A debugger provides operations for examining and modifying the program state. In addition, the debugger may control the program execution. The program might be stopped at location, and then later resumed. The program being debugged is usually compiled with a special debug flag. The flag tells the compiler to include *debug symbols*. Debug symbols provides the debugger with details about the source code. This enables the debugger to determine the location of variables in memory, and to map each instruction to lines in the source code.

Some debuggers provide a graphical interface. An example is Winpdb [Aid], which is a debugger for the Python programming language. A screenshot of Winpdb is depicted in Figure 2.1. The upper right corner of the window presents the source code of the program being debugged. The line 4637 is highlighted as it indicates the current position in the program (which is currently paused). At the upper left corner is a list containing symbols, variables and functions, local to the source file. Each symbol is presented with its current value. The call stack is shown in the bottom left corner.

#### 6 2. BACKGROUND

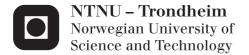

Other debuggers, like GDB [Fre], are controlled through a command line interface. Figure 2.2 shows GDB debugging SHMAC, using the software components produced as part of this master thesis. The debugger is controlled by typing in commands.

| Eile Breakpoints Control Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| II 🕨 이가 (가) 🧕 (가 😐 🗲 Filter: Medium 🛛 Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | g: auto Synchronicity: True                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Namespace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Source /data/sys/bin/winpdb-1.3.6/winpdb.py                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Name         Spe         Repr           Isocals         Globals         Exception           Name         Type         Repr           Image from b function         -function image from base64 at 0x1ees50s           Image from b function         -function image from base64 at 0x1ees50s           Istmix         medule           -main         -function image from base64 at 0x1ees50s           Istmix         medule           -main         -function image from /usr/lib64/python2.5/k/           -main         -main           -dass         None Type | 4522       def min ():       #         4523       frpdbl.get_vermin() (= "BDRE_l_6";       #         4524       if npdbl.get_vermin() (= "BDRE_l_6";       #         4525       rpdbl.grint(STE_DSDGE_INTEGE_ONSATTERLITY % ("BDRE_l_6"; npdbl.get_ve       #         4526       return       #       #         4527       return %D2.main(StartClient)       #       #         4528       def get_vermin():       #       #         4529       if |  |  |  |

| Threads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4648 · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| TID Name State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Console                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 45974534127920 HamThread waiting at break point Stack Frame Filename Line Function Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EPDB - The Remote Python Debugger, version PDE8_2_3_6,<br>Copyright (2) 2005-2008 Nin kides.<br>Type "help", "copyright", "license", "credits" for more information.<br>"" Stating of CTME." for auto completion in the following commands: launch,<br>"" eval and exec.<br>"" Pannoword has been met to a random pannword.<br>"" Stating debugger"                                                                                                |  |  |  |

| 0 winpdb.py 4637 <module> /data/sys/bin/winpdb-1.3.6</module>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | *** Attaching to debuggee *** Debug Channel is NOT encrypted.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 1         rpdb2.py         13767         StartServer         /data/sys/bin/winpdb-1.3.6           2         rpdb2.py         14015         main         /data/sys/bin/winpdb-1.3.6           3         rpdb2.py         14044 <module>         /data/sys/bin/winpdb-1.3.6</module>                                                                                                                                                                                                                                                                                 | *** Succemptilly attached to '/data/gw/bin/vingdb-1.3.6/vingdb.py'. *** Debuggee in waiting at break point for further commands.                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ; Command:                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | State: WAITING AT BREAK POINT                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

Figure 2.1: Screenshot of Winpdb, a debugger for the Python programming language. Source: Wikimedia [Wik].

# 2.1.2 Black Box Debugging

It's difficult to debug programs where its inner working is unknown or not available for inspection. A technique called *black box debugging* is employed in those cases [WT03]. Black box debugging collects useful information from sources external to the program. Many bugs can be diagnosed by observing the data that flows between the program and its dependencies. Relevant sources are for instance network traffic, system calls and file operations.

# 2.1.3 Remote Debugging

Remote debugging is debugging a program where the debugger runs on a different system than the program. The system running the debugger is called the *host*, while the system running the program is called the *target*. The host will usually connect

Figure 2.2: Screenshot of GDB while debugging a program on SHMAC.

to the target over a network, for instance over a serial line or using an IP connection. Remote debugging is used when debugging a system which cannot run the debugger itself, typically because the system has limited processing capabilities.

# 2.1.4 Debugging Techniques without Debugger

#### **Print Debugging**

Print debugging is a primitive form of debugging. Print statements are used to output the program's state at different locations during the program execution. One strategy is to print all relevant local and global variables at specific locations, to verify that their values are correct. The print statements are usually removed once the debug session is finished. This strategy is easy to understand, but requires modifications to the source code. Modifying the source code is undesired, as the process might introduce new bugs. The print output can be stored in a log file if standard output is not available.

#### 8 2. BACKGROUND

#### Analyse Core Dumps

A memory dump, sometimes called core dump, consists of the recorded state of the system at a specific time. A core dump of a program will usually contain the snapshot of the main memory and the values of the CPU registers. This information represents the state of the system at specific time. If the core dump was created at the time of a crash, it can be used to determine the cause.

# 2.1.5 Debugging Techniques using Debugger

#### Breakpoints

Breakpoints are used to stop the program execution at specific locations. The location can be a line in the source code or a memory location. The debugger is given control over the system when the program hits a breakpoint. The program's state may then be easily inspected as the program is paused. Breakpoints are usually managed by the debugger; the debugger insert and remove breakpoints during a debugging session. More advanced breakpoints exist in form of conditional breakpoints. Conditional breakpoints will only halt the program if certain conditions are met. The condition is usually specified as a boolean expression which includes program variables. Breakpoints are either implemented in software or in hardware.

#### Hardware Breakpoint

Some architectures provide support for hardware breakpoints. The breakpoint location is written to a special register file when it is inserted into the program. The processor will generate a trap when it tries to execute the instruction where the breakpoint is located. A processor will usually have a limited capacity for storing hardware breakpoints. So it is not uncommon for a debugger to use both hardware and software breakpoints simultaneously. The Intel x86 ISA has for instance only capacity for 4 hardware breakpoints [Int86].

#### Software Breakpoint

Software breakpoints are implemented using instructions that traps the processor when executed. The original instruction is substituted for a trap instruction when a breakpoint is inserted. Many architectures have a special trap instruction dedicated for breakpoints. The int3 instruction in Intel x86 will explicitly call the breakpoint exception handler [Int86]. The ARMv5 ISA introduced the BKPT breakpoint instructions, which triggers a prefetch abort on execution [ARM01]. Some architectures, for instance earlier ARM versions, do not provide a dedicated breakpoint instruction. The common solution is to either use a *software interrupt instruction* (SWI) or an *undefined instruction* for breakpoints. Both instructions are good candidates as they will generate a trap which will be handled by a dedicated exception handler.

#### Single Stepping

It is sometimes useful to execute only a single instruction or line of code while debugging. Variables can be examined after each step to verify that the previous operation was correctly executed. In addition, single stepping can be used to determine the actual program flow during execution. Implementations of single stepping in both software and hardware exists. One way of achieving single stepping is by inserting a breakpoint at the next instruction to be executed. Like with breakpoints, Intel x86 does also provide hardware support for single stepping. Setting the TP (trap flag) bit in the system register will force the CPU to generate an exception after executing a single instruction [Int86].

#### Watchpoints

A watchpoint halts the program when the values of an expression or variable changes. Watchpoint are sometimes called data breakpoint. The Intel x86 architecture provides hardware support; the CPU can be programmed to trap when the data at a memory location is modified [Int86].

# 2.2 GNU Debugger

GDB, shorthand for GNU Debugger, is an open-source debugger [RSea14]. It was originally developed by Richard Stallman, now managed by Free Software Foundation. GDB supports a large variety of architectures like x86, ARM and PowerPC. Language support is provided for C, C++, D, Go, Objective-C, Fortran, Java, OpenCL C, Pascal, Modula-2, Ada and several assembly dialects. GDB is still under active development, with multiple releases every year. The latest version as of March 2014, is GDB 7.7, which was released in February 6th, 2014.

# 2.2.1 Debugging Target

A target is a term used to describe the program being debugged. The typical use case is to run GDB side-by-side with the target, for instance running the debugger and the program on the same machine as depicted in Figure 2.3. The debugging session is initiated by attaching GDB to an existing process, or by specifying an executable file which GDB will launch and attach to. GDB also supports debugging of recorded sessions, for instance core dumps.

# 2.2.2 Remote Target

GDB can debug programs running on a remote machine. This is typically the case when debugging on a platform that does not have the necessary operating system support for running GDB directly.

Figure 2.3: Debugging a local program.

A host machine runs GDB, launched with the path of the program file as argument. The host connects to the remote target using either a serial port or a TCP connection. The remote target is either GDBServer instance or a remote stub. The host and the remote target communicates using a text based protocol named *GDB Remote Serial Protocol*. This protocol will be described in more detail in subsection 2.2.3.

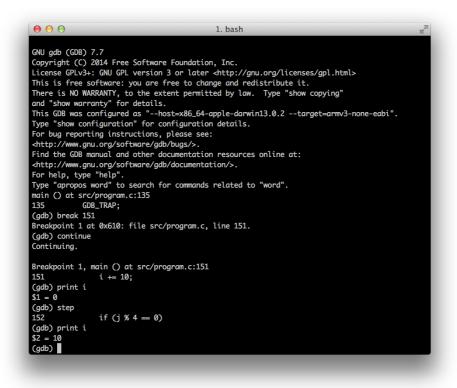

# GDBServer

GDBServer is a *debug server* running on the remote machine. It appears as a server program which other GDB instances may connect to. The GDB instances debugs the program running on the remote machine through GDBServer. Figure 2.4 illustrates a remote target in combination with GDBServer. GDBServer requires the same operating system facilities as standard GDB program. Its main advantage over GDB is its size. The codebase of GDBServer is smaller, which makes it simpler to add new architecture support. A small program size is also beneficial when running the debugger on a memory-constrained system.

Figure 2.4: Debugging a remote program using GDBServer.

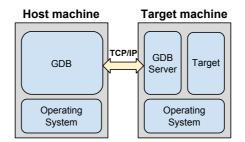

# GDB Remote Stub

Another way of debugging a remote program is using a remote stub. The remote stub is a small software component that is linked with the program. It uses the same remote protocol as GDBServer. A remote stub does not require an operating system as opposed to GDBServer. It is commonly used when debugging embedded systems or when debugging the operating system itself. KGDB, the Linux kernel debugger, is an example of a remote stub. Figure 2.5 illustrates a remote target being debugged over a serial line using a remote stub.

Figure 2.5: Debugging a remote program using a GDB stub.

# 2.2.3 GDB Remote Serial Protocol

The GDB host communicates with a remote target using the *GDB Remote Serial Protocol*. Data is transferred between host and target as *packets*. A packet has the following structure:

```

1  packet-data#checksum

```

A packet starts with a \$ character and ends with a # character followed by a two-letter checksum. The packet data is usually in ASCII text to support transmissions over mediums that only support 7-bit characters. The receiver of a packet verifies the checksum and sends an acknowledgement with result. An acknowledgement is sent as a single character, not as a packet. The character + is replied if the checksum matches the packet data, - if not. A negative acknowledgement will usually result in a retransmission of the original packet. The *Remote Serial Protocol* is a request-reply protocol. The host sends packets in form of *commands*, which are replied by the remote with a *response*. Note that *protocol commands* are different from the GDB CLI<sup>1</sup> commands. A CLI command will usually result in several protocol command packets.

# Packets

The GDB Remote Serial Protocol defines several commands with associated responses. The type of a command is determined by the first letters in the packet data. These

<sup>&</sup>lt;sup>1</sup>Command Line Interface

#### 12 2. BACKGROUND

letters represents the name of packet. The packet may contain any number of parameters. The parameters are usually separated from each other using either a semi-colon (;), comma (,) or colon (:). An example of a command with response from remote is shown below:

```

1 host: $m5cc,4#c8

2 remote: +$0030a0e1#ea

3 host: +

```

The host sends the read memory packet, m, requesting 4 bytes from address 0x5cc. The remote first acknowledges the packet with a +, then sends the response to the host. The response contains the 4 bytes requested, each encoded as a two-letter hexadecimal number. The bytes 0x00, 0x30, 0x30 and 0xE1 are returned to the host.

The stub is required to return an empty response for commands which it does not support. The older packets have single letter names, while newer packets typically have longer names. All multiletter names are prefixed with one of the letters q, Q or v.

Packet starting with a lower-case q are categorized as general query packets. An example is qC, which queries the target for the identifier of the current thread. A prefixed upper-case Q is used for general set packets; packets which modifies the remote's state. The prefix v is used for all other multiletter packets which do not fit any of the aforementioned categories.

The target sends the host a *stop reply packet* when the program halts. The stop reply packet informs the host of the reason for the halt, e.g. if the program hit a breakpoint or was killed. The stop reason is encoded as a Unix signal; **SIGTRAP** is for instance reported when program traps on a breakpoint.

# **Obligatory Packets**

A remote stub is only required to support a small subset of the available commands. These packet are shown in Table 2.1. Most of the debugging management will in that case be taken care of by the GDB instance running on the host. The host will for instance have to insert and remove breakpoints using the memory access packet if the stub does not support any of the breakpoint packets. Since the stub can support an arbitrary set of packets in addition to the minimum required, the host has to probe the stub for supported packets. Two techniques are used; the host can send the packet to stub and see if an empty response is replied, or query the stub for supported commands using the qSupported packet.

| Packet format    | Description                                                                                                                                                      | Reply                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| g                | Read general registers.                                                                                                                                          | XX<br>Each byte of register data<br>is described by two hex dig-<br>its. The bytes with the reg-<br>ister are transmitted in tar-<br>get byte order. |

| G XX             | Write general registers. Data<br>is in the same format as for <b>g</b><br>packet.                                                                                | ОК                                                                                                                                                   |

| m addr,length    | Read <i>length</i> bytes of memory starting at address <i>addr</i> .                                                                                             | XX<br>Memory contents; each<br>byte is transmitted as<br>a two-digit hexadecimal<br>number.                                                          |

| M addr,length:XX | Write <i>length</i> bytes of memory<br>starting at address <i>addr. XX</i><br>is the data; each byte is trans-<br>mitted as a two-digit hexadeci-<br>mal number. | ОК                                                                                                                                                   |

| s [addr]         | Single step. $addr$ is the address<br>at which to resume. If $addr$ is<br>omitted, resume at current ad-<br>dress.                                               | Stop reply packet when targets halts.                                                                                                                |

| c [addr]         | Continue. $addr$ is address to resume. If $addr$ is omitted, resume at current address.                                                                          | Stop reply packet when targets halts.                                                                                                                |

Table 2.1: Obligatory packets for a GDB stub. Source: [RSea14, Appendix E].

# Interrupt Mechanism

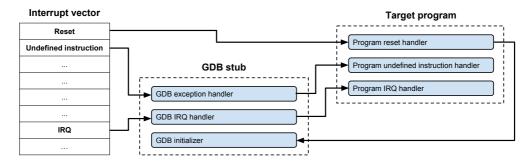

GDB has a mechanism for interrupting a program while its running. This mechanism is triggered if the user press Ctrl+C in the GDB command prompt. The interrupt signal is transferred to the remote as the byte 0x03. The byte does only represent an interrupt if it is not part of packet data. When the remote receives the byte, it stops the program execution and transfers the control over to the debugger. The remote will then send a *stop reply packet* to notify GDB that the program has stopped.

# Multithreading Support

GDB supports debugging of multithreaded programs. Several of the packets accepts a thread identifier to specify the thread of operation. A thread identifier is represented

#### 14 2. BACKGROUND

as a positive number. An example is the vCont packet, where the host can specify to single step a single thread while halting the others:

host: vCont; s:1; c#c1

The argument s:1 tells the stub to single step thread #1. The next argument c tells the stub to continue execution for the other threads.

There are two modes of controlling execution of the debugger in a multithreaded environment. The default mode is the *all-stop mode*. A more advanced alternative called *non-stop mode* was added in 2009 [GDB09]. The major difference between the modes is that in *all-stop mode*, all threads halt whenever one thread is halted. It is not possible to inspect a single thread while the others are running simultaneously. This limitation is removed in *non-stop mode*, at a cost of a substantially higher complexity, both in semantics and implementation.

#### Multiprocess Mode

*Multiprocess mode* enables GDB to attach and detach several processes during one session. This differs from normal behaviour which only supports debugging a single process during a session. The remote protocol supports packets for attaching, detaching and querying processes when in *multiprocess mode*.

# 2.2.4 GDB for ARM

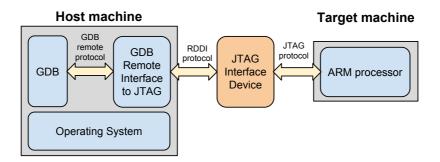

Most modern ARM microcontrollers provides a dedicated debug port named TAP (Test Access Port), which is part of the JTAG standard [JC09]. This interface talks directly to hardware, eliminating any need for debugging software running on the target. A debugger setup using GDB and JTAG is depicted in Figure 2.6. As a dedicated hardware port is common for most architectures today, there are only a few official remote stubs available. The GDB source code comes with stubs for only 6 architectures; none of which support ARM.

# 2.3 The SHMAC Platform

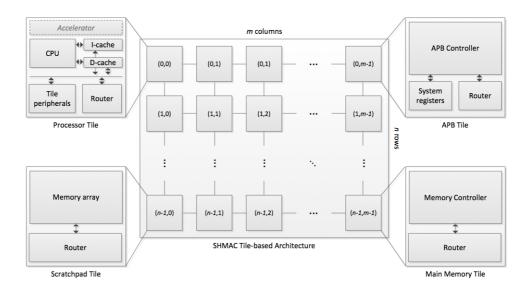

The SHMAC platform is a generic architecture for implementing single-ISA heterogeneous multicore systems. It is a tile-based architecture, meaning that the system consists of a set of tiles, connected to a two-dimensional grid interconnect. Each tiles implements a communication interface, supporting communication with up to 4 neighbors. As the grid is implemented as a mesh network, tiles are required to forward all packets to their destinations. The SHMAC architecture is depicted in Figure 2.7.

Figure 2.6: Debugging with GDB over the JTAG interface.

The current prototype is synthesized on FPGA development systems. The tile setup on SHMAC can be configured when synthesizing. All configurations consist of at least one processor tile, an APB tile and a memory tile.

The following tiles are available:

#### APB tile

This tile provides communication channels to the FPGA host controller. It implements the ARM AMBA Advanced Peripheral Bus (APB) protocol.

#### Processor tile

The processor tile consists of a single ARMv3 CPU core.

#### Main memory tile

The main memory tile provides access to off-chip RAM. The amount of RAM available depends on the development system.

#### Scratchpad tile

The scratchpad tile provides access to block RAM available on the FPGA chip.

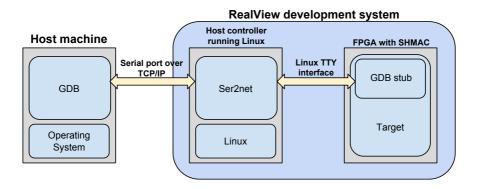

#### 2.3.1 Test platforms

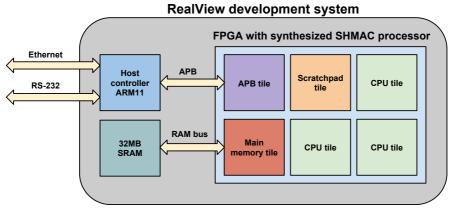

There are currently two SHMAC test platforms available. The first test platform is based on a RealView PB11MPCore development system, depicted in Figure 2.8. It features an ARM11-based host controller and 32MB SRAM. The test platform is synthesized with a SHMAC processor consisting of 3 CPU tiles, 1 APB tile, 1 main memory tile and 1 scratchpad tiles.

The second test platform is based on the Versatile Express development system. This system features a larger FPGA chip, making it possible to synthesize SHMAC chips

#### 16 2. BACKGROUND

Figure 2.7: Overview of the SHMAC architecture. Source: [EECb].

with several more tiles than the older RealView system. The Versatile system provides 4GB of DDR RAM and features an ARM Cortex A9 quad core host controller. It is synthesized with a SHMAC processor consisting of 8 CPU tiles, 1 APB tile, 1 main memory tile and 1 scratchpad tile.

Both test platforms run a Linux based operating system on their host controllers. The host controller acts as a gateway between the FPGA and the world outside. Communication with the system is available through ethernet connection and RS-232 serial port. Terminal access is possible by connecting to a SSH server installed on the host controller.

#### SHMAC Communication

The Linux installation communicates with SHMAC using a TTY device driver and set of utility programs. There are a total of 16 TTY devices available, which enable serial communication with the SHMAC. The TTY devices uses the APB tile as its underlying channel.

The utilities are listed in Table 2.2.

Figure 2.8: SHMAC synthesized on RealView development system.

Table 2.2:

SHMAC utility programs

| Name          | Description                         |

|---------------|-------------------------------------|

| shmac_reset   | Resets the SHMAC processor          |

| shmac_program | Writes data to the SHMAC's memory   |

| shmac_dump    | Dumps a SHMAC memory region to file |

## 2.3.2 Processor Tile

The processor tile is based on the open-source Amber 25 CPU core [Ope13], which is an 32-bit RISC processor implementing the ARMv2a instruction set. The Amber project is hosted at OpenCores, an open-source hardware community [Ope]. It features a 5-stage pipeline together with separate data and instruction cache.

Amundsen and Andersson [AA14] enhanced the CPU tile to support a newer ARM ISA version during their master thesis. Their goal were to port the Linux 3.12 kernel to SHMAC. As ARMv2a support was removed in Linux 2.6 version, migrating the CPU core to a newer ARM ISA became a necessity. Their work had positive implications for the debugger project, as the ARMv3 ISA was a crucial requirement for some of the debugger functionality. The benefits of ARMv3 will be outlined in subsection 6.3.1.

## 2.3.3 ARMv3 ISA

The ARMv3 ISA is a 32-bit RISC instruction set. All instructions are 4 bytes long. Only the load and store instructions can access main memory. Every instruction is prefixed with a 4 bit condition code. An instruction is only executed if the

#### 18 2. BACKGROUND

condition code agrees with the condition code flags in the program status register. This functionality enables conditional execution without using branching, which is beneficial as branching is an expensive operation. An overview of the instruction set is presented in Figure 2.9.

| 31 28 | 27 26 25 | 24 | 23  | 22                                      | 2  | 1 20 | 19 16    | 15 12                                  | 11 8                       | 7 5                | 4                    | 3 0                             | _                     |

|-------|----------|----|-----|-----------------------------------------|----|------|----------|----------------------------------------|----------------------------|--------------------|----------------------|---------------------------------|-----------------------|

| Cond  | 001      |    | Ор  | cod                                     | le | s    | Rn       | Rd Operand 2                           |                            | nd 2               |                      | Data Processing<br>PSR Transfer |                       |

| Cond  | 000      | 0  | 0 0 |                                         | A  | s    | Rd       | Rn                                     | Rn Rs 1001 Rm              |                    | Multiply             |                                 |                       |

| Cond  | 000      | 1  | 0   | в                                       |    | 0 0  | Rn       | Rn Rd 0000 1001 Rm S                   |                            | Single Data Swap   |                      |                                 |                       |

| Cond  | 0 1 I    | Ρ  | U   | в                                       | v  | / L  | Rn       | Rd                                     |                            | offset             |                      |                                 | Single Data Transfer  |

| Cond  | 011      |    |     |                                         |    |      | XXXXXXXX | XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX |                            |                    |                      |                                 |                       |

| Cond  | 100      | Ρ  | U   | s                                       | v  | / L  | Rn       | Rn Register List Block Data Transfer   |                            |                    |                      |                                 | Block Data Transfer   |

| Cond  | 101      | L  |     |                                         |    |      |          | offset Branch                          |                            |                    |                      |                                 |                       |

| Cond  | 110      | Ρ  | U   | N                                       | v  | / L  | Rn       | CRd CP# offset                         |                            |                    | Coproc Data Transfer |                                 |                       |

| Cond  | 111      | 0  |     | СР                                      | Op | C    | CRn      | CRn CRd CP# CP 0 CRm                   |                            |                    |                      |                                 | Coproc Data Operation |

| Cond  | 111      | 0  | С   | PC                                      | рс | L    | CRn      | Rd                                     | Rd CP# CP 1 CRm Coproc Reg |                    |                      | Coproc Register Transfer        |                       |

| Cond  | 111      | 1  |     | ignored by processor Software Interrupt |    |      |          |                                        |                            | Software Interrupt |                      |                                 |                       |

Figure 2.9: Overview of the ARMv3 instruction set. Source: [ARM94].

#### Modes

The ARMv3 ISA support six modes of operation. The processor may change mode because of several reasons. A mode change takes place when an exception arise, either triggered by an instruction or by an external interrupt. The processor may also be forced into a specific mode by modifying the program status register using the msr instruction.

A mode is either privileged or non-privileged. Code running in non-privileged mode is not allowed to execute certain instructions. Some instructions have different semantics in non-privileged mode.

The operating modes are described below:

#### User mode (usr)

The normal program execution state. It is the only non-privileged mode.

#### FIQ mode (fiq)

Entered on fast interrupt. Designed to support a data transfer or channel process.

#### IRQ mode (irq)

Entered on normal interrupt. Typically used for general purpose interrupt handling.

#### Supervisor mode (svc)

Mode typically used by the operating system code.

#### Abort mode (abt)

Entered on prefetch and data abort.

#### Undefined mode (und)

Entered when an undefined instruction is executed.

| USER | FIQ  | รเ | JPERVISC | R | ABORT |  | IRQ  | U | NDEFINED |

|------|------|----|----------|---|-------|--|------|---|----------|

| R0   | R0   | ]  | R0       |   | R0    |  | R0   |   | R0       |

| R1   | R1   | 1  | R1       |   | R1    |  | R1   |   | R1       |

| R2   | R2   | 1  | R2       |   | R2    |  | R2   |   | R2       |

| R3   | R3   | 1  | R3       |   | R3    |  | R3   |   | R3       |

| R4   | R4   | 1  | R4       |   | R4    |  | R4   |   | R4       |

| R5   | R5   |    | R5       |   | R5    |  | R5   |   | R5       |

| R6   | R6   |    | R6       |   | R6    |  | R6   |   | R6       |

| R7   | R7   |    | R7       |   | R7    |  | R7   |   | R7       |

| R8   | R8   |    | R8       |   | R8    |  | R8   |   | R8       |

| R9   | R9   | 1  | R9       |   | R9    |  | R9   |   | R9       |

| R10  | R10  | 1  | R10      |   | R10   |  | R10  |   | R10      |

| R11  | R11  |    | R11      |   | R11   |  | R11  |   | R11      |

| R12  | R12  |    | R12      |   | R12   |  | R12  |   | R12      |

| SP   | SP   |    | SP       |   | SP    |  | SP   |   | SP       |

| LR   | LR   |    | LR       |   | LR    |  | LR   |   | LR       |

| PC   | PC   |    | PC       |   | PC    |  | PC   |   | PC       |

|      |      |    |          |   |       |  |      |   |          |

| CPSR | CPSR |    | CPSR     |   | CPSR  |  | CPSR |   | CPSR     |

|      | SPSR |    | SPSR     |   | SPSR  |  | SPSR |   | SPSR     |

Figure 2.10: Layout of register file.

#### Registers

ARMv3 has 37 registers, of which 31 are general 32-bit registers and 6 are status registers. Only 16 of the general registers are visible at any time, which 16 depends on the current operating mode. The CPSR (Current Program Status Register) register is visible in all modes. All privileged modes has its own SPSR (Saved Program Status

#### 20 2. BACKGROUND

Registers) register, used to store the old value of CPSR on mode change. A register that is only visible in a single mode is a *banked register*. Figure 2.10 presents the register layout for each mode. Note that cells with gray background represents *banked registers*.

Some of the general registers have a special purpose. The register R15 is the program counter (PC). The banked register R14, also called LR, is the link register. It receives the old value of PC when executing a branch-and-link register or when an exception handler is invoked. Another special register is R13 (SP), a banked register which stores the stack pointer for each mode.

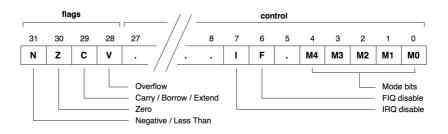

The layout of the program status registers is presented in Figure 2.11. The condition code flags consists of the N, Z, C and V bits. The bits MO-M4 are the mode bits, which determines the current operating mode. The I and F bits disables IRQ and FIQ respectively when set high.

Figure 2.11: Format of Program Status Registers. Source: [ARM94].

#### Exceptions

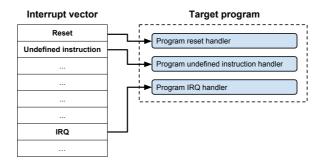

Certain registers are backed up automatically on exception. The old PC and CPSR values are copied into the LR and SPSR respectively. PC is set to a location in the interrupt vector defined by the type of exception. The mode bits in CPSR are set to the new mode. Interrupts are disabled when entering the exception handler to prevent unmanageable nesting of exceptions.

The interrupt vector is located at address 0 in memory. It contains 8 entries, one for each type of exception. The layout of the interrupt vector is shown in Table 2.3. An entry is stored as a *branch-and-link instruction*, where the branch offset is the location of the respective interrupt handler.

The CPU starts executing at address 0 on reset, effectively invoking the reset handler.

| Address    | Exception             | Mode on entry    |  |  |  |

|------------|-----------------------|------------------|--|--|--|

| 0x00000000 | Reset                 | Supervisor (svc) |  |  |  |

| 0x00000004 | Undefined instruction | Undefined (und)  |  |  |  |

| 0x0000008  | Software interrupt    | Supervisor (svc) |  |  |  |

| 0x0000000C | Abort (prefetch)      | Abort (abt)      |  |  |  |

| 0x00000010 | Abort (data)          | Abort (abt)      |  |  |  |

| 0x00000014 | Reserved              | -                |  |  |  |

| 0x00000018 | IRQ                   | IRQ (irq)        |  |  |  |

| 0x0000001C | $\operatorname{FIQ}$  | FIQ (fiq)        |  |  |  |

Table 2.3:

The interrupt vector

## 2.4 Barrelfish

Barrelfish is an experimental operating system developed by ETH Zürich, with collaboration from Microsoft Research [Zü, BBD+09]. Its architecture is designed for future multicore and manycore systems. The motivation behind Barrelfish is the increasing diversity in computer hardware and the growing number of cores. Todays operating systems are designed for the common case, homogenous architectures, while cores in newer systems are getting increasingly diverse. A single system can consist of multiple cores with different performance characteristics, power profiles and ISA. As the number of cores increase, cache coherency becomes more expensive, making shared memory less viable for intercore communication. Barrelfish does not rely on shared memory, and uses solely message passing for communication between cores. It is design to run on multicore system where cores are heterogeneous on ISAs level, for instance systems consisting of both ARM and x86 processors. Most of todays operating systems are designed after the *shared-memory single-kernel model*, where the operating system expects that all cores exposes the same ISA.

Barrelfish is ported to several different architectures. The official distribution supports the most common architectures such as Intel x86 and ARM. Several unofficial ports to more experimental architectures have also been developed. One example is the port to the Intel Single-Chip Cloud Computer [PSMR11], which is an experimental processor consisting of 48 x86 cores [HK10].

#### 2.4.1 The Multikernel Model

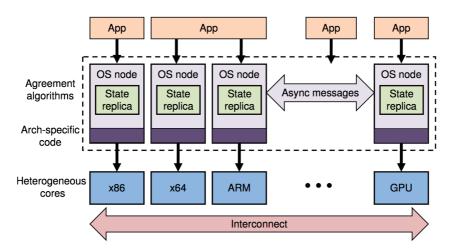

Barrelfish's architecture is designed after the multikernel model, which is depicted in Figure 2.12. The multikernel model structures the operating systems as a distributed system of cores.

#### 22 2. BACKGROUND

The multikernel is guided by three design principles:

- 1. Make all intercore communication explicit.

- 2. Make OS structure hardware-neutral.

- 3. View state as replicated instead of shared.

Each OS node communicates only through message passing. There is no shared state, each node has its own state replica. Replica consistency is maintained by exchanging messages. The hardware specific parts are separated out from the hardware-neutral codebase, which makes it easier to add support for new architectures.

Figure 2.12: The multikernel model. Source: [BBD<sup>+</sup>09].

## 2.4.2 Barrelfish Architecture

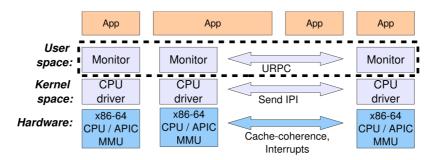

The Barrelfish implementation of the multikernel model is depicted in Figure 2.13.

Each CPU core has a *CPU driver* running in privileged mode. The CPU driver is responsible managing hardware resources and timeslicing processes, similar to a microkernel. It shares no state with other cores which simplifies its design.

A distinguished user process called *monitor* runs on top of each CPU driver. The *monitors* coordinate systemwide state and updates the data structures inside each local CPU driver, e.g. the memory allocation table, which has to be kept consistent across cores. All intercore coordination is performed by the monitor processes.

Figure 2.13: The Barrelfish architecture. Source: [BBD+09].

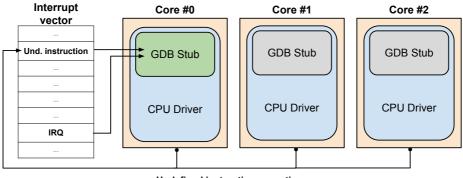

#### **Process Structure**