# Power Profiling: From Measurements to Simulation Models

Stian Hvatum Terje Runde

Master of Science in Computer ScienceSubmission date:June 2014Supervisor:Gunnar Tufte, IDICo-supervisor:Asbjørn Djupdal, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

# Abstract

Energy efficiency is currently one of the biggest challenges in modern computer design. High power density limits further performance growth, and energy efficiency affects both the power bill for supercomputers and battery lifetime for embedded devices. A better understanding of energy efficiency during the design stage eases development of better architectures. In this thesis, we investigate energy consumption and architectural properties of an ARM Cortex-A9 processor. Further, this information is used to create a tool for estimating its power consumption through simulation.

Instruction level energy consumption is determined through measurements and experiments on real hardware, which are further mapped to certain architectural events found in the gem5 simulator. The tool utilizes these events together with a simulator trace log and outputs a representation of energy consumption over time.

This method can be applied during the development process at the simulator level, while traditional methods typically involves hardware synthesis. The results show that this tool can estimate energy consumption with margin of error of 5 % on general workloads, and is able to identify power consumption trends throughout a program.

# Sammendrag

Energieffektivitet er en av de største utfordringene i moderne datamaskindesign. Videre ytelsesøkning begrenses av høy strømtetthet, i tillegg har energieffektivitet stor betydning i alt fra strømregningen på superdatamaskiner til batterlevetid for små innebygde enheter. Bedre forståelse for energieffektivitet vil gjøre det lettere å utvikle bedre arkitekturer. I denne masteroppgaven ser vi nærmere på arkitekturen og energiforbruket til en ARM Cortex-A9. Vi lager deretter et verktøy for å forutsi dens strømforbruk gjennom simulering.

Gjennom målinger og eksperimenter gjort på ekte maskinvare bestemmes strømforbruk på instruksjonsnivå. Videre blir dette koblet til bestemte hendelser i den samme arkitekturen modelert i gem5-simulatoren. Verktøyet vårt benytter så disse hendelsene, sammen med loggfiler fra simulatoren, til å lage en representasjon av prosessorens strømforbruk over tid.

Vår metode kan benyttes i prosessorutvikling allerede i simulatorfasen, mens tradisjonelle metoder ikke virker før maskinvaren er ferdig syntetisert. Resultatene viser at verktøyet vårt kan estimere strømforbruk innenfor 5 % feilmargin på normale arbeidslaster. Det kan også identifisere positive og negative utviklinger i strømforbruket gjennom kjøringen av et program.

# Preface

This report is submitted to the Norwegian University of Science and Technology in fulfillment of the requirements for master thesis. This work has been performed at the Department of Computer and Information Science, NTNU, with Associate Professor Gunnar Tufte as supervisor, and Asbjørn Djupdal as co-supervisor.

Thanks to Gunnar Tufte and Asbjørn Djupdal for all help with the technical work and the report. Also thanks to Kenneth Sivertsvik, Håkon Øye Amundsen and Joakim Andersson for help with proofreading the thesis.

| Title:    | Power Profiling: From Measurements to Simulation Models |

|-----------|---------------------------------------------------------|

| Students: | Terje Runde & Stian Hvatum                              |

**Problem description:** The SHMAC prototype is an ongoing research project within the Energy Efficient Computing Systems (EECS) strategic research area. SHMAC is planned to run in an FPGA and be an evaluation platform for research on heterogeneous multi-core systems. Due to the Dark silicon effect, future computing systems are expected to be power limited. The goal of the SHMAC project is to propose software and hardware solutions for future power-limited heterogeneous systems.

The micro architecture level is an implementation of the Instruction Set Architecture (ISA). Energy efficiency of an ISA is as such given by the chosen micro architecture. To be able to take the "right" design choice to optimize for energy efficiency, knowledge of energy and power for instruction types, e.g., instructions of type float, nop, copy, are needed.

The goal of this sub-project within the SHMAC platform is to gain knowledge of energy/power consumption of different instruction types to be able to extract information that can be used to improve the micro architecture design of SHMACcores. This project will take a twofold approach; 1) Investigate the power/energy consumption of simple benchmark programs on real hardware, i.e. create benchmark programs and evaluate performance by measurements. 2) Investigate the same benchmark programs in simulations as to ensure a good understanding of the relation between measurements and simulated results.

The project will include:

- Devising small benchmark programs, e.g., C or assembly, that isolate specific functions at the micro architecture level.

- Run test on real hardware to collect data.

- Run tests in simulation to relate measurements to simulation results.

An ARM processor is going to be the target ISA for measurements and simulations.

Supervisor:Gunnar Tufte, IDICo-supervisor:Asbjørn Djupdal, IDI

# Contents

| 1        | Intr | oduction                                        | 1        |  |

|----------|------|-------------------------------------------------|----------|--|

|          | 1.1  | Historical Perspective                          | 2        |  |

|          | 1.2  | Demand for Energy Efficiency                    | 2        |  |

|          | 1.3  | Optimizing for Energy Efficiency                | 3        |  |

|          | 1.4  | Assignment Interpretation                       | 3        |  |

|          | 1.5  | Report Organization                             | 4        |  |

| <b>2</b> | Bac  | cground                                         | <b>5</b> |  |

|          | 2.1  | Energy Consumption in CPUs                      | 5        |  |

|          | 2.2  | Instruction Level Energy Measurements           | 5        |  |

|          | 2.3  | Hardware Platform                               | 7        |  |

|          | 2.4  | Hardware Simulators                             | 9        |  |

|          |      | 2.4.1 A Brief Comparison of Hardware Simulators | 10       |  |

|          |      | 2.4.2 The gem5 Simulator                        | 11       |  |

|          | 2.5  | Global Optimization                             | 11       |  |

|          | 2.6  | SHMAC                                           | 14       |  |

| 3        | Bui  | ding a Power Estimation Tool                    | 15       |  |

|          | 3.1  | What is PET?                                    | 15       |  |

|          | 3.2  |                                                 |          |  |

|          |      |                                                 | 16       |  |

|          |      |                                                 | 17       |  |

|          | 3.3  | Input                                           | 18       |  |

|          |      | 3.3.1 gem5 Trace Logs                           | 18       |  |

|          |      |                                                 | 19       |  |

|          |      |                                                 | 20       |  |

|          | 3.4  | 0                                               | 23       |  |

|          |      |                                                 | 23       |  |

|          |      | 3.4.2 Examples of Output Data                   | 24       |  |

|          | 3.5  |                                                 | 24       |  |

|          |      |                                                 | 25       |  |

|          |      | 3.5.2 Argument Parsing and Program Options      | 26       |  |

|    |       | 3.5.3             | Reading Trace Logs                             | 27 |

|----|-------|-------------------|------------------------------------------------|----|

|    |       | 3.5.4             | String to Event Mapping and Power Accumulation | 27 |

|    |       | 3.5.5             | Data Reduction                                 | 28 |

|    |       | 3.5.6             | Output Production and Annotations              | 29 |

|    |       | 3.5.7             | Unit Tests                                     | 29 |

| 4  | PEI   | Γ Perfo           | ormance Tuning                                 | 31 |

|    | 4.1   |                   | ring a Real World Processor                    | 31 |

|    | 4.2   |                   | tor Environment                                | 31 |

|    |       | 4.2.1             | gem5 CPU configuration                         | 32 |

|    |       | 4.2.2             | gem5 Memory Model                              | 33 |

|    | 4.3   | Multi-            | objective Weight Optimization                  | 33 |

|    | 4.4   | Choosi            | ing Workloads                                  | 36 |

|    | 4.5   |                   | 。。<br>S...................................     | 37 |

|    |       | 4.5.1             | gem5 CPU Model Accuracy                        | 37 |

|    |       | 4.5.2             | Optimization using $1 + \lambda$               | 38 |

| 5  | Exp   | erimer            | nts and Results                                | 43 |

|    | 5.1   |                   | nvironment                                     | 43 |

|    | 5.2   |                   | Estimation Challenges                          | 44 |

|    | 5.3   |                   | s and Discussion                               | 44 |

|    |       | 5.3.1             | Presentation of Test Sets                      | 44 |

|    |       | 5.3.2             | Explanations and Errors                        | 46 |

|    |       | 5.3.3             | PET Processing Performance                     | 47 |

| 6  | Con   | clusio            | and Further Work                               | 49 |

|    | 6.1   | Conclu            | sion                                           | 49 |

|    | 6.2   | Furthe            | r Work                                         | 50 |

| Re | efere | nces              |                                                | 51 |

| ۸  | non   | dices             |                                                |    |

| -  | -     |                   |                                                |    |

| Α  | TD    | Г4501:            | Exploring Instruction Level Energy Efficiency  | 57 |

| в  |       |                   | ons to gem5                                    | 67 |

|    | B.1   | -                 | s/common/Exynos_4412P.py                       | 67 |

|    | B.2   |                   | s/example/se.py                                | 71 |

|    | B.3   | -                 | s/common/CacheConfig.py                        | 72 |

|    | B.4   | -                 | s/common/CpuConfig.py                          | 73 |

|    | B.5   |                   | ch/arm/linux/process.cc                        | 73 |

|    | B.6   | $\mathrm{scr/me}$ | em/SimpleDRAM.py                               | 74 |

# Chapter Introduction

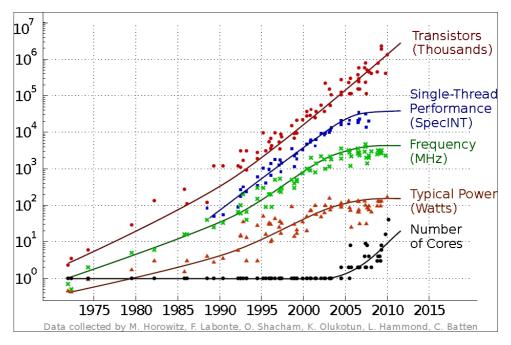

The steep increase in single-threaded performance during the last few decades seems to have come to an end. Figure 1.1 shows how Moore's law is continuing [1, 2]; the transistor count on-die is still increasing exponentially. As we have seen the end of Dennard scaling [3, 4], power density increases as more transistors are crammed together. Too much power on a tiny area leads to more heat than conventional cooling solutions can dissipate. Today, computer designers are striving to achieve higher performance without further increase in power density.

Figure 1.1: Historical trends in CPU performance, from [5].

#### 2 1. INTRODUCTION

# 1.1 Historical Perspective

Computers have emerged in many roles in our society, and the demand for greater computer resources is ever increasing. Throughout the '80s and '90s, the increasing demand for performance was met by increasing the clock frequency. Shortening the critical path and exploiting instruction level parallelism allowed the CPU to run at higher clock speeds to improve throughput [2]. Consequently, processor manufacturers were able to double single-threaded performance approximately every 18th month [1]. The tradeoff, however, was an increased amount of complex logic added to the processor core. Techniques such as pipelining, superscalarity and out-of-order execution all improved performance by leveraging the increased number of transistors [6]. For a long time, new process technologies allowed for smaller and less energy consuming transistors, but as we approached the end of Dennard scaling [3, 4], the amount of gates required to accommodate speedups could not fit on the die due to thermal constraints. Heat generation on-chip became overwhelming; one could no longer add more logic and increase the frequency to gain additional performance.

# **1.2** Demand for Energy Efficiency

We are now at the beginning of an era where energy efficiency and performance are tightly coupled. When improving performance, one must take care not to exceed the physical limitation of power dissipation. Thus, energy efficiency is key to additional performance gain; performance per Watt must be emphasized.

Heat is not the only motivating factor to keep energy consumption down. Processors targeting laptops, cellphones and other mobile devices have always been energy-constrained due to their use of batteries. Lower energy consumption would allow for longer battery life and/or heavier applications. More recently, mobile processors have become increasingly popular in alternative domains, such as supercomputing. Their low cost and high performance per Watt ratio makes them attractive for massively parallel problems, which is currently done on large and expensive supercomputers. These machines have huge energy budgets and are taken out of service after just a couple of years, being replaced by new machines that offer better performance for less power. Building data centers from low-cost embedded processors is believed to have a huge potential and could change the landscape of supercomputing in the future [7].

Not only data centers benefit from the use of mobile processors. The SHMAC research project at NTNU aims to build a single-ISA heterogeneous computing platform with processing cores specialized for energy efficiency. Using the most efficient processor or hardware accelerator – in terms of both energy and performance – is the key to success for such platforms.

There are several reasons to minimize a processors energy consumption. Batteries would last longer, applications become richer and it will enable processor performance growth to continue. Energy efficiency has become crucial; performance alone is no longer the single most important attribute of processors.

# **1.3** Optimizing for Energy Efficiency

Given the availability of advanced hardware design tools, it is possible to model and simulate performance of an unimplemented architecture with decent accuracy. However, modeling power consumption is a more elaborate process: current techniques works on a low level and uses circuit-level models to obtain energy metrics. This method makes them accurate, but also heavy and time consuming. Being able to rapidly prototype and visualize how changes in the microarchitecture affects energy performance is an advantage when designing energy efficient hardware. Some solutions already exists [8, 9], but most of them inspect energy consumption at a fine granularity and requires ASIC synthesis of HDL code. During the design process, there is a great need for tools that help developers predict the changes in power consumption when new features are implemented.

The immediate lack of a system that is easy to use and set up motivates the creation of a new high-level tool. We introduce PET; a tool that is able to estimate power usage over time for a given workload on a given architecture. It will use an energy metric profile together with a simulator trace log to calculate energy usage. Using this approach, PET will be able to detect if hardware modifications done to the simulation level model will be beneficial in the realized hardware. PET will also tell if a processor implementation is more energy efficient than another given a specific workload. Thus, it can help building workload optimized tiles for the SHMAC project [10]. Using PET, one can also adjust the energy metric profile and simulate power usage with one component cheaper or more expensive to use in terms of energy. This will enable hardware designers to understand which optimizations are most beneficial and identify possible routes of exploration in their journey of processor energy optimization.

# 1.4 Assignment Interpretation

Based on the assignment description text, the following main tasks were identified.

- **Task 1:** Quantify the exact cost of executing specific instructions on a modern out-of-order CPU core.

- **Task 2:** Create a software suite that accentuate energy consumption during software execution on various hardware.

#### 4 1. INTRODUCTION

Task 1 involves performing energy measurements on hardware components to obtain numbers of a processors energy characteristics. Task 2 depends on the results from the former and can only be solved after the completion of Task 1.

Task 1 was solved as a part of the specialization project (TDT4501) during the fall of 2013, and the final report in its entirety is attached in Appendix A. The review of Task 2 is the main emphasis of this master's thesis. In order to solve it, a simulation environment must be created and combined with a method for power estimation.

# 1.5 Report Organization

- **Chapter 1: Introduction** provides a historical perspective to the trends in processor design and motivates the need for energy efficient hardware.

- **Chapter 2: Background** contains supportive material on subjects used throughout this thesis, as well as explanations that justify decisions made later in the report.

- Chapter 3: Building a Power Estimation Tool is the main piece of our problem solution. It contains an in-detail review of what PET does and how it is built.

- **Chapter 4: PET Performance Tuning** describes considerations needed when porting the use of PET to support new hardware configurations.

- Chapter 5: Experiments and Results presents the tests used to evaluate PET, along with accuracy and performance data.

- Chapter 6: Conclusion and Further Work provides the concluding remarks on the work described in this thesis and suggests possible areas of interest for further research.

This thesis touches subjects such as artificial intelligence, computer architecture and electronics. Some background information on the most important subjects is provided in this chapter.

# 2.1 Energy Consumption in CPUs

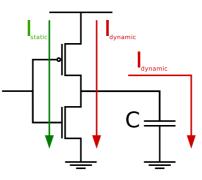

Two sources of energy consumption in a CPU can be distinguished: static and dynamic. Static energy consumption is caused by a small current continuously leaking through the transistors, while dynamic is due to charges being moved towards ground when transistors are toggling [11]. Figure 2.1 shows how current flows through a NOT gate at the transistor level. The green arrow indicates where static leakage occurs and the two red arrows shows where charges escapes when switching. As feature size decreases, a significant part of overall energy consumption is due to static leakage [12]. This means that simply powering the chip without any toggling generates a significant amount of heat [13, 14]. Static power consumption origins from transistor size and layout, while dynamic power consumption depends on the amount of transistor switching. From an architectural point of view, the dynamic power consumption is easier to influence.

# 2.2 Instruction Level Energy Measurements

High precision instruction level energy models can be derived for pipelined processors by monitoring the instantaneous current drawn by the processor at each clock cycle, as explained in [15]. Modern processors commonly operate at a few GHz, and the Nyquist-Shannon sampling theorem [16] states that the sampling frequency must be at least twice the frequency of the signal being measured. The signal sampled from the processor might change at least once per clock cycle, so obtaining accurate measurements would require use of very expensive instruments.

#### 6 2. BACKGROUND

Figure 2.1: Static and dynamic power through a NOT gate.

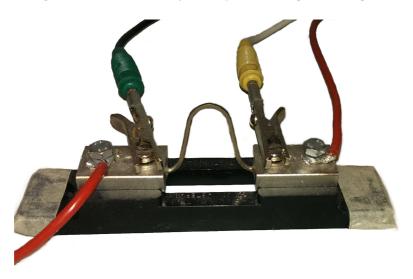

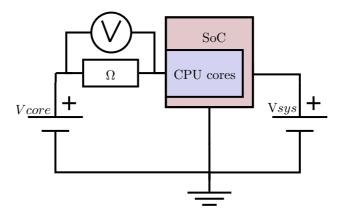

Figure 2.2: The shunt resistor used in our experiments.

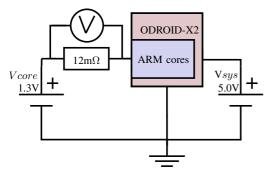

In [17], single instructions were measured by exploiting fast-loop-mode [18] and looping over a group of equal instructions. A bench multimeter was used to measure the voltage drop over a shunt resistor as seen in Figure 2.2, set up as illustrated in Figure 2.3. From this, the current flowing from the  $V_{core}$  power rail and through the processor core was inferred. The peripherals were isolated and excluded from the measurements. The shunt resistor was chosen such that the voltage drop over it resided in the range 0 – 100 mV. According to the datasheet [19], the voltage readings would then have 0.003 % margin of error.

The use of a shunt resistor to infer current is equivalent to how ammeters work internally. However, the internal shunt resistor is not scaled for the dynamic range of a specific target. Also, a too large resistor would drop the voltage relative to the impedance in the load, and in the case of a processor this can give unpredictable

Figure 2.3: Experiment setup for measuring single instruction current drain.

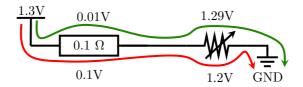

results. Figure 2.4 illustrates two scenarios where voltage drops over a 0.1  $\Omega$  shunt resistor and a variable load (e.g., the CPU core). There is a trade-off between accuracy in measurements and voltage variations across the circuit. If the shunt resistor is too small, the voltage drop diminishes and is difficult to measure.

Figure 2.4: The red and green lines represents two snapshots in time with different variable loads. A higher current drain through the circuit changes the ratio of voltage drop between the two loads.

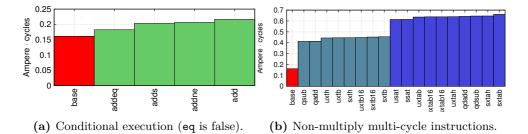

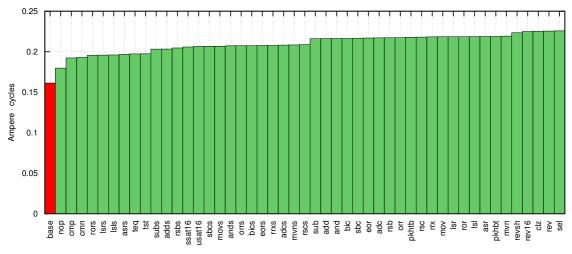

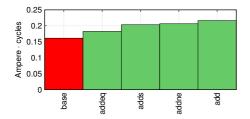

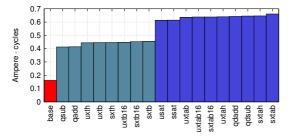

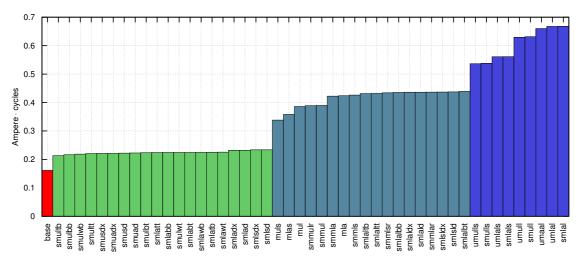

Figure 2.5 presents results from [17], and shows how different instructions use different amounts of energy. This indicates that the architecture impacts how efficient each instruction is. *base* refers to the cheapest instruction in the ISA and roughly corresponds to the static power consumption.

# 2.3 Hardware Platform

The ODROID-X2 developer platform [20] was used as the reference hardware for all experiments in this thesis. An image of the platform is shown in Figure 2.6. Its core voltage is accessible on an attached daughter board beneath the heat sink, making it easy to conduct power measurements. The board is equipped with a Samsung Exynos 4412 "Prime" [21], a modern SoC ("System-on-Chip") featuring four ARM Cortex-A9 [18] CPU cores, a Mali-400 GPU and 2 GB of on-chip DRAM. The Cortex-A9 is

Figure 2.5: Figures from [17] showing the results of measuring the current drain through the CPU core while running isolated instructions in a loop. The values are measured current drain multiplied by the average number of cycles used.

Figure 2.6: Image of the Hardkernel ODROID-X2 from the Hardkernel ODROID-X2 product page [20].

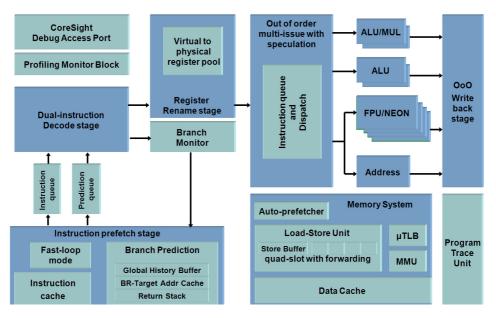

one of ARM's mid-to-high-range application processors. It features an out-of-order dual-issue speculative RISC core, and it seems to be designed with emphasis on energy efficiency. This processor is primarily found in low-powered embedded devices with a modest demand for performance, such as smartphones and tablets.

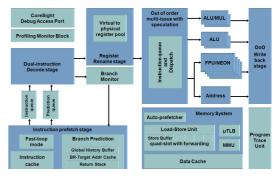

Figure 2.7 shows an overview of the ARM Cortex-A9 architectural structure. It features an out-of-order multi-issue module after the decode stage. This module can do speculative issue and schedules two arithmetic operations per cycle. It also features a multiplexed lane for address operations and floating point operations (the *NEON* FPU). In this experiment, a 4-core variant of the processor was used, but 3 of the cores were disabled to ease both the measurement and the simulation process. Table 2.1 enumerates the most important properties of the SoC.

Figure 2.7: An overview of the Cortex-A9 Pipeline, figure taken from the ARM Cortex-A9 White paper [18].

| Manufacturer         | Hardkernel                                                        |

|----------------------|-------------------------------------------------------------------|

| Platform             | ODROID-X2                                                         |

| $\operatorname{SoC}$ | Samsung Exynos 4412 "Prime"                                       |

| CPU Core             | ARM Cortex-A9 (r3p0)                                              |

| Number of Cores      | 4                                                                 |

| Clock Frequency      | $1.7 \mathrm{GHz}$                                                |

| Core Voltage         | 1.3 V                                                             |

| L1 Cache             | Dual 32 KB                                                        |

| L2 Cache             | 1 MB                                                              |

| Main Memory          | $2~\mathrm{GB}~\mathrm{LP}\text{-}\mathrm{DDR2}~880~\mathrm{MHz}$ |

Table 2.1: Hardware specifications ODROID-X2.

# 2.4 Hardware Simulators

As computer architecture development meets more challenging demands, a versatile set of software tools have been developed to help the designers. In this collection of tools lies a set of computer architecture simulators meant to evaluate processors at the architectural level. They provide the ability to model hardware at a higher abstraction layer than what is expressed by the underlying circuit.

## 2.4.1 A Brief Comparison of Hardware Simulators

To support our power estimation tool, a simulator front-end must provide a good picture of events that occur in a hardware implementation of the architecture. The out-of-order property significantly increases the level of complexity which the simulator must handle. The following simulators were considered:

#### Sniper

Sniper is a high-speed, multicore, multi-threaded and cycle-accurate computer architecture simulator [22, 23, 24]. It already integrates with McPAT [25, 26] and it is open source. Sniper only works with x86 targets, and is therefore not applicable for simulation of ARM-based architectures.

#### SimpleScalar

SimpleScalar is a popular commercial architectural simulator that comes with a free academic license providing full source code [27, 28, 29]. SimpleScalar supports the ARM instruction set among many others, and looks like a decent simulator for advanced out-of-order core simulation. SimpleScalar is also the simulator used by the Wattch-project [30]. However, the SimpleScalar project seems to be in a state of abandonment. The source code for SimpleScalar v3 is still available and received patches in 2003.

#### QEMU

QEMU is a generic open source machine emulator which enables near real-time performance on architectures like ARM, even on x86 host machines [31, 32, 33]. However, QEMU is a machine emulator rather than an architectural simulator. Despite its great performance of running ARM-binaries, it will not produce CPU and memory event trace logs, and is not suitable for this project.

#### gem5

gem5 is a merger between the M5 simulator [34] and the GEMS simulator project [35]. gem5 includes ARM-support with out-of-order execution and provides cycle-accurate trace logs which are appropriate for this project [36]. Its core is written in C++ and has a highly modular interface that allows users to specify simulator targets through Python scripts. Many of the maintainers are employees of ARM Corp., and the activity on the mailing lists suggests high project activity [37].

Provided this comparison of simulators, and given that NTNU has previous experience with gem5, gem5 was the natural winner and our choice of an architectural simulator.

# 2.4.2 The gem5 Simulator

The gem5 project [38] merges the best features of M5 [34] and GEMS [35] and includes a wide range of CPU and memory models [39].

The gem5 simulator comes bundled with different CPU models ranging from in-order models without timing constraints, such as AtomicSimpleCPU, to detailed out-of-order cores such as O3CPU. During the merge between M5 and GEMS, two memory systems emerged: M5's simple memory system and the more advanced Ruby Memory System from the GEMS project. M5's memory system is simple, and works by settings delays to each memory request, depending on how they hit in the memory hierarchy. Ruby is a more complete memory system simulation tool, and can be used to model new types of memory systems. The Ruby memory system is currently unsupported for ARM architectures.

The simulator has two main execution modes: *Syscall Emulation* (SE) or *Full System* (FS). In SE mode, the simulator runs without any real operating system. gem5 traps system calls from the executable and emulates them, often by passing them to the host operating system. In FS mode, the simulator can load an entire operating system, e.g., a GNU/Linux distribution, and run applications within the OS. gem5 supports many architectures; it can run binaries compiled for ALPHA, SPARC, MIPS, ARM, x86 and POWER architectures.

During simulation, gem5 keeps track of hundreds of different events related to the CPU core and memory system. In-detail statistics, similar to performance counters on real hardware, are then dumped for subsequent inspection. gem5 is also able to output a trace log while it runs, originally intended for debugging of gem5. A trace log contains user-selected events that happens within the simulated hardware. These trace logs grow quickly in size, easily tens of gigabytes, but provides useful insights of the simulated execution. In particular, they describes CPU activity down to the microarchitecture level and outputs simulated processor activity.

# 2.5 Global Optimization

Optimization is a field of applied mathematics that deals with finding the best set of parameters to optimize an objective function. A problem with N variables  $\{n_0, \ldots, n_{N-1}\}$  in range  $n_i \in \{0, \ldots, k-1\}$  will have a search space with  $k^N$  possible solutions. Each solution can be evaluated by applying the objective function to it, to obtain the solutions *fitness*. The fitness is a measure of how good the solution is and it is used to assist the selection of candidate solutions for evaluation.

The solution space can be thought of as a (N+1)-dimensional space that directly relates to the number of variables in the solution, plus one axis for the fitness value.

#### 12 2. BACKGROUND

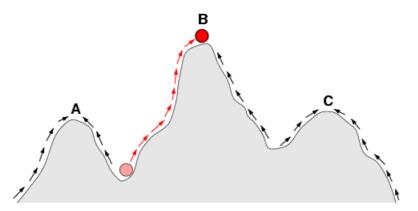

E.g., when a problem contains a single variable, its solution space might look like Figure 2.8 where the X-axis is the value of the single variable and the Y-axis is the fitness of this solution. Problems with more variables will have more axes. The optimization algorithms can be thought of as methods for exploring and finding the highest or lowest point in of the fitness-axis.

As k and N grow large, it becomes infeasible to search through and evaluate the vast amount of permutations and other techniques must be employed. Finding an arbitrary local optimum is often straight forward using classical *local* optimization methods such as a simple hill climbing algorithm. However, these methods cannot always be used to find a *global* optimum. A wide range of algorithms to search through a subset of the solution space exists, each with different approaches and properties. Many of these are described in detail in [40].

**Figure 2.8:** A one-dimensional fitness landscape. The arrows indicate the preferred flow of a population on the landscape, and the points A and C are local optima. The red ball indicates a population that moves from a very low fitness value to the top of a peak. Borrowed from [41].

In general terms, optimization algorithms can be divided into deterministic and non-deterministic approaches. The deterministic approaches can be thought of as a single path in the solution space that starts at a defined but most likely suboptimal solution and ends at the best solution. The non-deterministic approaches usually selects one or more paths at random such that each run might yield a different outcome. Deterministic algorithms will always find the same solution, but if the search space is large this might be extremely time consuming. Non-deterministic algorithms tend to have an explorative behavior [42]; each computation of the next state includes some form of randomness. E.g., simulated annealing will do the same as the hill climbing algorithm, but will have some chance of moving downhill, thus it will be less prone to be stuck in a local optimum. A brief overview of algorithms considered for this thesis is provided below.

- **Regression** is described as a study of dependence between properties [43]. When data set contains values from at least two properties, regression can be used to find one value as a function of the other. An example of a regression technique is the least square method. This method will try to find a linear function,  $y = a_1x_1 + a_2x_2 + ... + a_nx_n + b$ , that minimizes the least square error. Implementations of linear regression solvers often formulate the problem as a system of linear equations [44], which can be solved by Gaussian elimination. More advanced forms for regressions can be used when the problem cannot be well mapped with a linear function, such as the Gauss-Newton algorithm [45].

- Simulated Annealing is a technique that belongs to the field of stochastic optimization and metaheuristics, inspired by the process of annealing in metallurgy [46]. It starts in a random state s, and for each iteration it probabilistically decides between moving the system to a neighboring state s' or staying in state s. To avoid ending up in a local optimum, the probability starts high, but decreases over time. Hence, simulated annealing can quickly consider the most important parts of the state if configured adequately.

- **Evolutionary Algorithms** is a term that refers to computational methods inspired by the process and mechanisms of biological evolution [47]. They differ from conventional algorithms by selecting the best-fit individuals in a population for reproduction and applying crossover and mutation to produce offspring. Only the best fit individuals go on to the next generation [48].

Global optimization problems are a well studied research area and there are countless ways to solve them. It can be difficult to know in advance which methods will provide the most rewarding results. Also, multiple approaches can be combined in efforts to extract the best properties from several branches, or to speed up convergence.

In this thesis, we have chosen to use an evolutionary approach called  $1 + \lambda$ , with  $\lambda = 4$ . It includes the following steps:

- 1. Generate  $\lambda$  random individuals.

- 2. Evaluate population.

- 3. Select the best individual.

- 4. Mutate  $\lambda$  new individuals from the best-fit individual.

- 5. Repeat step 2 through 4 for each generation.

In addition, we have borrowed ideas from simulated annealing by letting the probability of mutation decrease as fitness improves.

#### 14 2. BACKGROUND

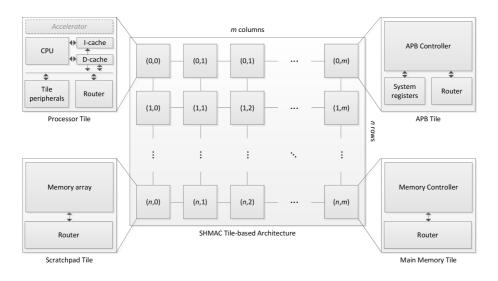

Figure 2.9: The SHMAC architecture. The figure shows how different kind of tiles are combined together and form a complete architecture. From [10].

# 2.6 SHMAC

SHMAC is a hardware prototype of a Single-ISA Heterogeneous MAny-core Computer [49, 10, 50]. It is an ongoing research project within the Energy Efficient Computing Systems (EECS) research area at the Department of Computer and Information Science, and Department of Electronics and Telecommunications at NTNU. The SHMAC project is driven by the *dark silicon effect*: as transistors become smaller, only parts of a chip can be powered simultaneously [4]. SHMAC implements two main strategies to mitigate the dark silicon effect, heterogeneity and specialization.

The SHMAC architecture is tile-based. Processing elements are laid out in a rectangular grid with connections to their nearest neighbor, as depicted in Figure 2.9. A router device present in all SHMAC tiles handles communication and data flow between tiles. In SHMAC, different kinds of specialized tiles/accelerators can be composed as desired, to form a computer tailored to the application. With the ability to evaluate different tiles with respect to energy and performance, the most advantageous core composition can be chosen.

# Chapter

# **Building a Power Estimation Tool**

The ultimate goal for this project is to model and estimate energy consumption for not yet implemented computer architectures. This allows new ideas to be prototyped and evaluated with respect to energy efficiency already at the design stage, easing the process of building energy efficient hardware. These evaluations can only serve as estimates and will doubtedly be truly accurate. Nevertheless, it can be used to test specific workloads and applications on specific processor configurations and evaluate ideas rapidly during the design phase.

As we are already supplied with a computer architecture simulator capable of tracing all sorts of hardware events, the next step is to extract power information from these event logs. In this chapter we introduce PET, a Power Estimation Tool. PET provides guided information about power usage for computer architectures and represents a major piece of our problem solution.

PET is implemented in C++ using the Boost Library [51]. The source code for PET and the rest of this project can be found Github:

git clone https://github.com/terjr/thesis.git

# 3.1 What is PET?

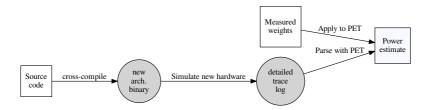

PET is a tool for power estimation of new as well as old architectures. It is built by measuring existing hardware with great detail, capturing discrete events and assigning each event a certain energy cost. When selected events have been weighted, one can run test programs through a simulator which is configured to act as the target hardware, as depicted in Figure 3.1. The simulator will generate a trace log containing the weighted events, which is then processed by PET. From this workflow, PET can produce a data set containing power consumption distributed over the simulation lifetime – a power profile of the program execution.

#### 16 3. BUILDING A POWER ESTIMATION TOOL

Figure 3.1: Example usage of the PET program.

When estimating power for an unimplemented hardware platform, the new hardware will be weighted similar to an existing implementation. As a consequence, this method requires a certain similarity between old and new hardware. We claim that in general, all modern computer architectures are built from comparable principles, and thus mappable to each other.

The accuracy will indeed suffer the more the model deviates from the reference hardware. PET's primary use is to identify *variations* between two implementations of the same instruction set architecture. For instance, one can experiment with a larger L2 cache to see how it affects energy usage and performance. The additional energy used by a larger L2 cache can be derived from existing implementations.

# 3.2 Approach

There are many considerations to take before creating a tool that should pretend to understand the implementation of hardware and the implications of features regarding energy efficiency. Through the next sections, we a model to be used in PET is developed and its inputs are defined.

#### 3.2.1 Energy Modeling

Song et. al [52] identifies three major approaches to processor power modeling used in the past, and introduces an instruction-based energy estimation model that can be used for energy simulation at high speed. Their proposed method is expressed through the following equation, and includes the desired features of previous energy models.

$$P_{core}(t) = \frac{E_{unit} \cdot A_{datapath} \cdot w(t) + E_{static}}{T_{sampling}}$$

(3.1)

This method has two dependencies. First, one must have sufficient details of the processor in order to identify datapath components to form the  $A_{datapath}$  matrix. The entries in  $A_{datapath}$  are the invocation counts of physical components in the datapath with respect to the workload metric w(t). w(t) is typically comprised of instruction types or key operational parameters such as cache miss, ratio, pipeline stall cycles and number of executed instructions. Secondly, the energy unit vector  $E_{unit}$ , a vector enumerating the per-access energy cost, requires circuit-level knowledge of the target processor to calculate.  $A_{datapath}$  can often be found by reverse engineering and benchmarking. The  $E_{unit}$ , however, is rarely available for commercial processors.

When building the model for PET, the model from [52] is simplified by combining  $A_{datapath}$  and  $E_{unit}$  to form a vector of weights that directly corresponds to the cost of an event. We call this vector C. Power for each core over time,  $P_{core}(t)$ , is then modeled by the following formula.

$$P_{core}(t) = \frac{C \cdot w(t) + E_{static}}{T_{sampling}}$$

(3.2)

Here, C represents the global cost vector – a matrix enumerating the cost for all event types. Note that it is global and do not depend on time.  $T_{sampling}$  represents the sampling period and  $E_{static}$  the static energy consumption.

#### 3.2.2 Power Consuming Events

Choosing which events should be tracked and which workloads that would give good metrics is an important part of our method. We account for two main groups of events; CPU instruction events and memory activity events. The events in these groups are listed in Table 3.1. It is desirable to estimate energy consumption on literally all types of computing systems, ranging from large-size clusters to embedded systems. To provide this flexibility it was decided that PET should parse log files from the simulators rather than being built-in on a specific simulator. Most active and working architectural simulators supports this sort of trace logs. Even if they are formatted differently, the effort of adjusting to a new format is a lot less than the effort of building this tool within a simulator.

The trace logs contains information about everything that goes on within the fictional computer. Such a piece of information is defined in PET as a *simulator event*. A simulator event can be thought of as a unit of work that uses a specified amount of energy. When PET finds such an event, it increases the modeled energy consumption at the correct point in time where the event took place.

#### 18 3. BUILDING A POWER ESTIMATION TOOL

| IntAlu        | Basic integer ALU operation           |

|---------------|---------------------------------------|

| IntMult       | Integer multiply ALU operation        |

| MemRead       | Memory Read issued, triggers LS unit  |

| MemWrite      | Memory Write issued, triggers LS unit |

| SimdFloatMisc | NEON unit activated                   |

| (a) CPU core events. |                             |

|----------------------|-----------------------------|

| L1IR                 | L1 instruction cache, read  |

| L1IW                 | L1 instruction cache, write |

| L1DR                 | L1 data cache, read         |

| L1DW                 | L1 data cache, write        |

| L2R                  | L2 cache, read              |

| L2W                  | L2 cache, write             |

| PhysR                | Main memory, read           |

| PhysW                | Main memory, write          |

(b) Memory events.

Table 3.1: Power consuming events.

The events described in Table 3.1 are the ones currently recognized by PET, but adding more (or removing) events is trivial. These events are selected mainly based on the information which is easily extracted from a gem5-formatted trace log, but also adjusted according to what could be checked with performance counters on the target hardware. Most of this information is available from [17], where different instruction loops were measured with both ammeter and performance counters. This is then correlated with the properties of the pipeline (as seen in Figure 2.7).

#### 3.3 Input

PET needs two types of data in order to model power; a simulator trace log and event-type weights. Optionally, PET can also read an annotation file and display function calls in the output.

#### 3.3.1 gem5 Trace Logs

In order to create the simulator trace log with the information required by PET, gem5 must be run with a specific set of parameters. By executing gem5 with --debug-flags=Bus,Cache,MemoryAccess,Exec, gem5 will output trace files that look like Listing 3.1.

| $\begin{array}{c} 1 \\ 2 \\ 3 \\ 4 \end{array}$ | 3021: system.physmem: Write of size 8 on address 0x82fe0 data 0xe1a0f00eee1d0f70<br>3021: system.cpu.icache: access for ReadReq address 9c0 size 64<br>3021: system.cpu.icache: ReadReq (ifetch) 9c0 miss- |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5                                               | 3432: system.cpu.dcache: Block addr $81$ f0 moving from state 0 to state:7 valid: 1                                                                                                                        |

| 6                                               | 3432: system.cpu.dcache: Leaving recvTimingResp with ReadResp for address 81f00                                                                                                                            |

| 7                                               | 3432: system.tol2bus.respLayer1: The bus is now busy from tick $234320$ to $236376$                                                                                                                        |

| 8                                               | 1642: system.cpu T0 : 0x89d4.0 : ldr r1, [sp] #4 : MemRead : D=0x00000000                                                                                                                                  |

| 9                                               | 1642: system.cpu T0 : 0x89d4.1 : addi_uop sp, sp, #4 : IntAlu : D=0x00000000b                                                                                                                              |

| 10                                              | 1701: system.cpu T0 : 0x89d8 : mov r2, sp : IntAlu : D=0x00000000b                                                                                                                                         |

| 11                                              | [1701: system.cpu T0 : 0x89dc.0 : str r2, [sp, #-4]! : MemWrite : D=0x00000000                                                                                                                             |

| 12                                              | 1760: system.cpu T0 : 0x89dc.1 : subi_uop sp, sp, #4 : IntAlu : D=0x00000000b                                                                                                                              |

| 13                                              | 1760: system.cpu T0 : $0x89e0.0$ : str r0, $[sp, #-4]!$ : MemWrite : D= $0x0000000$                                                                                                                        |

| 14                                              | 4000: system.membus: recvTimingResp: src system.membus.master[0] ReadResp 0x1640                                                                                                                           |

| 15                                              | 4000: system.l2: Handling response to ReadResp for address $1640$                                                                                                                                          |

| 16                                              | 4000: system.l2: Block for addr $1640$ being updated in Cache                                                                                                                                              |

|                                                 |                                                                                                                                                                                                            |

Listing 3.1: gem5 trace log.

Each line in Listing 3.1 represents an event that happens in the simulated hardware. Line 1 tells that a write access to physical memory has happened. Line 2 is the event of instruction cache access, while Line 3 shows that this request failed. During this simulation, there is also events like Line 5 which represents that the data cache updates some content. The discrete instructions running through the CPU is also logged, e.g., Line 8 shows a load instruction and Line 9 shows an add instruction.

The trace log input can be opened as a file or read from a Unix pipe. Discrete events are extracted from the trace log and power consumption is accumulated in equally sized timeslots in PET. Internally, these time steps are called buckets and its size is parameter controlled. Often, it is more practical to specify the number of buckets in the output rather then specifying the number of simulator ticks in each bucket. PET is able to estimate the bucket size by peeking at the last tick of a trace file. This is not possible when reading from a pipe, i.e., stdin. The trace file is not necessarily in tick order, but close enough to set a reasonable bucket size. The bucket size estimation algorithm is shown in Algorithm 3.1.

Listing 3.1 shows that the events in the trace log is not necessarily in their correct order. This means that PET must accumulate power consumption to the entire timeline at all times. Consequently, it is not possible to produce a continuous output flow. The results are stored in memory and written out when the entire input is parsed.

# 3.3.2 PET Weight Files

Equally important as finding the correct events is assigning each event the correct amount of power consumption. As each event will count differently depending on the architecture, PET will read a weight file along with the gem5 trace log. A sample

#### Algorithm 3.1 Bucket size detection algorithm.

```

function numTicks( traceFile ):

1

\mathbf{2}

# Find file size

3

eof_pos = traceFile.getSize()

4

5

# Seek almost to end, avoid last newline

traceFile.seek( eof_pos - 3 )

6

7

# Trace from back of file to second last newline

8

9

while not traceFile.currentChar is '\n':

10

traceFile.seek_backwards

11

# File stream position is now at beginning of last line

12

# Parse this line

13

14

simulatorEvent = parseLine( traceFile.getLine() )

15

# Return the tick of the retreived event

16

17

return simulatorEvent.getTick()

```

weight file is shown in Listing 3.2. As the timeslots are specified in simulator ticks instead of CPU cycles, the values have been chosen to match a 2 GHz processor, i.e., one CPU cycle per 500 simulator ticks <sup>1</sup>. If this method was to be applied to a processor with a different clock speed than 2 GHz, the weights would have to be scaled proportionally. This is not the case for the static power drain, as it is added to each timeslot, and not scaled in accordance with bucket size. It is also important to understand that the weight is applied once for each event, so events that naturally takes a number of cycles will have a high weight, which is in reality distributed over many ticks. This will not be accurate if an expensive event is applied at the border of a bucket. It is assumed that accuracy at this level is not important enough to increase the complexity of PET.

The weights displayed in Listing 3.2 are accumulated each time PET discovers a recognizable event in the log file. A simplified version of this algorithm can be found in Algorithm 3.2

# 3.3.3 Program annotation files

PET has the ability to annotate its output using a map from PC to function name (or rather, symbol name). The simulated binary itself is not an input to PET, instead PET comes bundled with an annotation tool: scripts/annotate.sh. This tool extracts symbols from the binary file, compiled with debugging symbols, to a text file in the format seen in Listing 3.3. The left column represents the address where the function is found, and the right column is the function name. PET will tag

<sup>&</sup>lt;sup>1</sup>This is the default gem5 simulation granularity.

```

1

# This file contains weights for the ARM Cortex-A9 embedded within

\mathbf{2}

# Samsung Exynos 4412 Prime meassured on an Odroid X2. Details in

3

# Runde & Hvatum 2013 "Exploring Instruction Level Energy Efficiency"

4

\mathbf{5}

# CPU Core Activity

6

IntAlu 170

7

IntMult 300

MemRead 80

8

9

MemWrite 50

10

SimdFloatMisc 400

11

12

# Memory related activity

13

L1IR

230

14

L1IW

340

15

L1DR

230

16

L1DW

340

17

L2R

1100

18

L2W

1300

PhysR 2600

19

PhysW 2800

20

21

# Static power

22

23

Static 70

```

Listing 3.2: Weight file example.

#### Algorithm 3.2 Power accumulation algorithm.

```

1

# map of accumulated power for each time step

2

map < time, power > output

3

# input is all trace log lines, elements in weight file and

4

# the determined bucket size (number of simulator ticks in

5

# each bucket)

6

7

function assignWeights( traceLogLines, weightMap, bucketSize )

8

9

# run through each line

for each line in traceLogLines:

10

# extract event parameters from line

11

12

simulatorEvent = parseLine( line )

13

14

# get the assigned weight from weight file

eventWeight = weightMap[simulatorEvent.getEventType()]

15

16

17

# add this weight to the output map

18

output[simulatorEvent.getTick()/bucketSize] += eventWeight

19

return output

```

```

1

00008120 read_int

\mathbf{2}

00008194 group_number

3

00008680 strip

4

00008734 read_int

\mathbf{5}

000087a4 group_number

000089bc fini

6

7

00008a08 call_weak_fn

8

00008a2c deregister_tm_clones

9

00008a64 register_tm_clones

10

00008aec frame_dummy

00008b44 main

11

12

00008f40 check_one_fd

13

00009420 abort

14

000097ac exit

15

000099ec rand

16

00009ed0 flush_cleanup

17

00009ff0 save_for_backup

18

0000bd44 malloc_init_state

19

0000bda4 ptmalloc_unlock_all2

20

0000be3c mem2mem_check

21

0000beb8 mem2chunk_check

22

0000c128 ptmalloc_lock_all

23

0000c318 new_heap

```

Listing 3.3: Annotation File Example.

each bucket with the last seen symbol within that bucket. scripts/annotate.sh is constructed using objdump and is shown in Listing 3.4.

```

#!/bin/sh

1

\mathbf{2}

BINARY = $1

3

OBJDUMP=$(which arm-linux-gnueabi-objdump)

4

if [ -z "$OBJDUMP" ]

then

5

6

OBJDUMP=$(find / -name 'arm-*-objdump' -print -quit 2>/dev/null )

7

fi

8

9

$OBJDUMP -S $BINARY | grep '<.*>:' | grep -v '<_' | tr -d '<>:'

```

Listing 3.4: scripts/annotate.sh: Script to extract symbols from a binary.

It should be mentioned that a program compiled with debugging symbols contains hundreds, if not thousands of symbols. Often, many of these symbols are called in clusters, while long periods of the program are spent in loops that are not using any symbols at all. This often renders a graphical representation of the power log with complete annotation as a complete mess. We recommend creating the annotation file using the mentioned tools, but manually filtering out only the symbols of interest.

### 3.4 Output

When a log file is consumed by PET, the output should be usable for many applications. In early stages of the design phase, or when great differences are expected, a sparse annotated graphical output might be the best way of visualizing power consumption. As the project evolves and more subtle changes are evaluated, a textual output will be easier to compare. PET supports three different output options:

#### graph

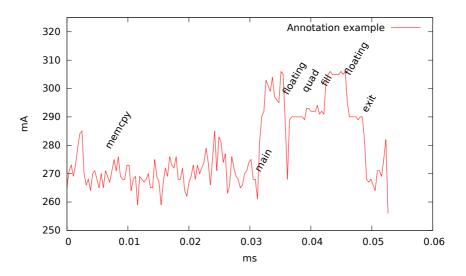

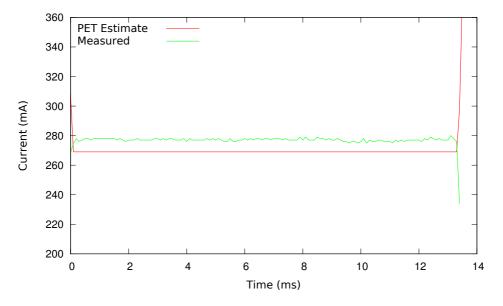

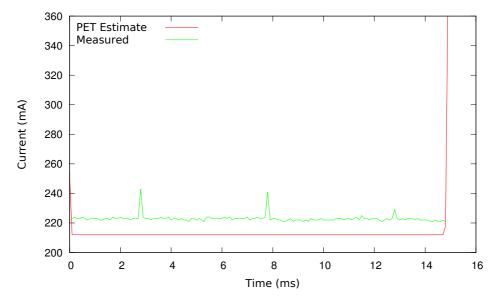

This format is the default, and provides an overview of the entire program in an easily digestible format. An example of such a graph is printed in Figure 3.2.

#### plain

The example in Listing 3.5 shows the *plain* format, which is intended to be used for further machine processing.

#### table

The table format, with an example shown in Listing 3.6, shows a terminalprintable output which is easier to read. It might come in handy as the default format might be hard to read when you are looking for specific information.

#### 3.4.1 Units

The output format is understood as timeslots in which the architecture has a certain current drain, which should be multiplied with applied voltage to get consumed energy. The values are given as milliamperes, equal to milliwatt if voltage is 1 V. Milliamperes are used as it is easier to find current drain rather than wattage with the setup used in this project, as described in section 2.2. When power is estimated for a new architecture, the resistance of the circuit is difficult to deduce, and voltage might also be an unknown factor. Given Ohms law in Equation 3.3 and the definition of electric power in Equation 3.4

$$I = \frac{U}{R} \tag{3.3}$$

$$P = U \cdot I \tag{3.4}$$

it can be found that power equals current squared times resistance

$U=R\cdot I$

#### 24 3. BUILDING A POWER ESTIMATION TOOL

$$P = (R \cdot I) \cdot I$$

$$P = I^2 \cdot R \tag{3.5}$$

and that power equals voltage squared divided by resistance

$$P = U \cdot \frac{U}{R}$$

$$P = \frac{U^2}{R}$$

(3.6)

Thus, estimating only the current drain means that the power at each point will be unknown without knowing resistance or voltage. Further, energy consumption cannot be estimated unless the new architecture is similar in terms of voltage and resistance to a chip where these numbers are available. Even the current drain might not be representable at all; if resistance or voltage is unequal to the levels found in the reference chip, the final numbers will be far off.

Equation 3.5 and Equation 3.6 states how voltage and current is important for energy consumption. The current is, from Equation 3.3, dependent on resistance as well as voltage. With this in mind, and knowing that power in a complex environment is a delicate matter, the most important application for PET is to point in the right direction. PET will never give accurate power estimations for new chips, but will provide useful information for seeing if a new feature or architectural fix will render the final architecture more energy efficient or not.

# 3.4.2 Examples of Output Data

Visualization is often a good thing when inspecting old or trying to understand new problems. Figure 3.2 shows an example of PET graph output format, with annotations.

Example of the **plain** output format can be seen in Listing 3.5. The left column is the bucket number, while the right column is instant current draw from the modeled architecture.

When reading the output directly from console, a more descriptive output format is the table format. An example using this option is rendered in Listing 3.6.

# 3.5 Architecture

The trace logs read by PET can easily grow to 10s of gigabytes. Due to memory constraints on commonly available computers, it is not feasible to read the entire log

Figure 3.2: PET graphical output. This example contains annotations, each label represents the entrance of a function.

0 120 memcpy 1 113 start 2 150 main 3 123 main 4 133 fun1 5 117 main

Listing 3.5: PET plain output with function annotations.

file into memory and then start parsing. One of PET's major design goals is to be user friendly and convenient to use, and as a consequence it must be reasonably fast. To gain speed, the PET core is built around a parallel pattern similar to MapReduce [53].

#### 3.5.1 Overview

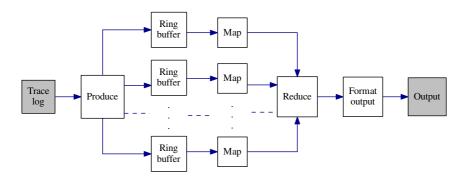

In order to obtain acceptable performance, we have looked at different ways of digesting large data sets. The final implementation of PET follows a scheme borrowing ideas from the producer-consumer pattern as explained by Gamma et. al. in [54] and the MapReduce algorithm. As depicted in Figure 3.3, this scheme makes it rather easy to let a producer (sequentially) read the lines from the log file into ring buffers (produce) and let multiple consumers pick from their ring buffer (consume). Each consumer parses the log lines they pick, and apply the weight of each read event to

| 1 |        |            |       |        | > |

|---|--------|------------|-------|--------|---|

|   | Bucket | milliAmps  |       | Symbol |   |

|   |        |            | -   - |        |   |

|   | 0      | 120.000000 | 1     | memcpy | 1 |

|   | 1      | 113.000000 | 1     | start  | 1 |

|   | 2      | 150.000000 | 1     | main   | 1 |

|   | 3      | 123.000000 | 1     | main   | 1 |

|   | 4      | 133.000000 | 1     | fun1   | 1 |

|   | 5      | 117.000000 | 1     | main   | 1 |

| \ |        |            |       |        | / |

Listing 3.6: PET table output with function annotations.

Figure 3.3: How PET works.

their result vector (map). When all lines are read and parsed, the result vectors are merged (reduce) and idle-task power and static power consumption is added. This combination of algorithms allows PET to take advantage of all available cores.

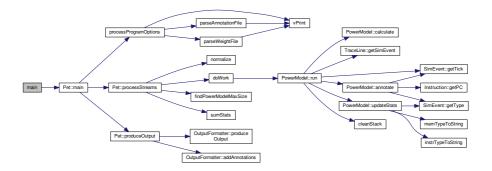

The next subsections will describe in detail the most important parts of the workflow, in sequential order. For further understanding of the program flow, a call graph is seen in Figure 3.4.

## 3.5.2 Argument Parsing and Program Options

As any other non-trivial programs, PET has to adapt to input options given from the command line or from a settings file. PET makes extensive use of the Boost library and utilize Boost::Program\_options for parsing the command line. This allows easy extraction of program options, both with long (--option=value) and short (-o value) option style.

Figure 3.4: Call graph.

### 3.5.3 Reading Trace Logs

When arguments are parsed and a trace log has been specified, either by path or as stdin, a single thread is kicked off reading each line of the log file into a C++ string container. This happens in the Pet::processStreams class member function seen in Figure 3.4. The string container is then inserted into one of many circular buffers. The circular buffers are implemented with boost::lockfree::spsc\_queue, a lock-free single producer, single consumer queue. The property of being lock-free is explained by Tim Blechmann in [55]:

Data structures are *lock-free*, if some concurrent operations are guaranteed to be finished in a finite number of steps. While it is in theory possible that some operations never make any progress, it is very unlikely to happen in practical applications.

In PET, this queue has a fixed size of 8192 elements, but dynamic size is also available in the library implementation. Which buffer the string is inserted into is determined by a simple circular algorithm; the next ring buffer is selected when the current one is full. When the buffers are small, each are filled fast enough to keep all workers occupied. We observed that this method avoids locking better than using a single ring buffer shared by all worker threads. The number of threads and the size of the ring buffers are tightly coupled with how fast the host computer is able to feed PET with the log files.

#### 3.5.4 String to Event Mapping and Power Accumulation

String parsing and mapping are the most compute-intensive parts of PET. PET spawns multiple worker threads as specified by the user. As the producer fills the

#### 28 3. BUILDING A POWER ESTIMATION TOOL

ring buffers for each of the workers, the workers pick strings from their pool. The strings are popped from the ring buffer, thus making space for new elements right away. Each string is parsed by the **TraceLine** class, which looks for patterns in the strings containing known event types. When connecting PET with gem5, the trace logs as previously seen Listing 3.1 contains an event type designation in the second colon-separated column. The **TraceLine** class extracts this part by string trimming.

The event types are instantiated as objects of their parent type (Instruction- or Memory-event). The right parameters are found from progressive string parsing. If the event is unrecognized, a dummy object of type UnknownEvent is returned. This type has zero cost later in the reduce phase. Each event object is able to figure out its own weight as written in the *weights*-file. After the event has been parsed, the weight is added to the power model at the corresponding time step.

In order to reduce the time used for disposal of the string objects after they are parsed, they are placed in a static-size array. When this array is full, or the ring buffer is empty, the worker frees all the string data. This helps keeping the memory footprint low while avoiding unnecessary calls to free(). This optimization does not have a massive impact on performance, but as can be seen from [56], the free() implementation contains enough pointer arithmetic to make a difference in a tight loop.

#### 3.5.5 Data Reduction

When all lines from the trace log have been consumed by the workers, the threads are joined and their data is returned as standard C++ vectors. These vectors are further wrapped in yet another standard C++ vector. The inner vectors are then combined; the value from the corresponding buckets in each vector is added together and put in a result vector. This reduction happens as the last part of Pet::processStreams, as seen in Figure 3.4.

After this reduction, the number of idle cycles is estimated by subtracting recorded events from the maximum number of events in a bucket. This is done more simplistic than accurate using Equation 3.8. eventsInWorkerBucket is the number of events recorded in each vector at each bucket, and each event is pinned to the cycle where it originated. Note that N is the number of worker threads, not the number of buckets.

$$eventsInBucket = \sum_{n=1}^{N} eventsInWorkerBucket_n$$

(3.7)

$$idleEvents = \frac{ticksInBucket}{ticksInCycle} - eventsInBucket$$

(3.8)

It should also be noted that even though this method might work well in a single-cycle in-order CPU, the out-of-order nature of the Cortex-A9 makes it hard to tell how many idle cycles actually occurred. E.g., a single cycle may fill the pipeline with four events, then idle the three next cycles; this would be calculated as no idle time. When the approximate numbers of **idleEvents** have been estimated, that number is multiplied by the *Idle*-weight and added to the sum in the result vector. Finally, the entire vector is normalized according to bucket size and then static current drain is added.

## 3.5.6 Output Production and Annotations

After the result vector has been completely accumulated, annotation is added to a new vector in the same manner as the data reduction. With the new, merged annotation map containing all last matches between a symbol and the program counter within each measure point, this map is fed to the OutputProducer object as seen in Figure 3.4. The OutputProducer is responsible for generating output as defined by the input arguments. Its options have already been described in section 3.4, and its implementation is a simple nested if-else-clause that calls internal functions for each output type. The graphical output is produced using a wrapper around gnuplot, while the textual outputs are created by printf-statements.

#### 3.5.7 Unit Tests

All internal string parsing is verified by unit tests. The unit tests are written with help from the Boost Test Library [57].

The test library generates a new binary with the same program content, except the main function, thus the program flow is different. The test binary will run through the listed functions with a certain input, and if the output is unexpected, the test binary will print to the console an error message containing a description of what went wrong.

## Chapter

# **PET Performance Tuning**

Several factors affect the PET model accuracy. We now consider the steps needed to adapt the use of PET on a new architecture. First, one must create a CPU model using gem5's Python interface, resembling the modeled hardware. Then, finding proper weights is formulated as a global optimization problem and matched up against existing hardware.

#### 4.1 Measuring a Real World Processor

The results contributed in this work relies on the existence of a method to isolate and measure core voltage on a hardware implemented reference CPU. This is possible due to the  $V_{core}$  separation on the development kit, as mentioned in section 2.3.

In [17], we conducted experiments to quantify the energy cost of an instruction executing on a modern out-of-order mobile processor. We were able to do this by completely bypassing the memory hierarchy utilizing special hardware (*fast-loop mode*) and sampling a running average. Voltage drop over a shunt resistor set in series with the ODROID-X2 development board was measured. This voltage drop was used to calculate energy used in the processor core. The results obtained are further used to tune PET towards this architecture.

### 4.2 Simulator Environment

PET relies heavily on a front-end that can execute a binary on a simulator and output (*time, event*) tuples as a trace of execution. In this thesis, we are using the gem5 simulator, but technically PET could be modified to support any simulator front-end. The power profile generated by PET are derived from the weight configuration given as input and the simulation trace, so it is important that the simulator trace is similar to a hardware execution.

#### 32 4. PET PERFORMANCE TUNING

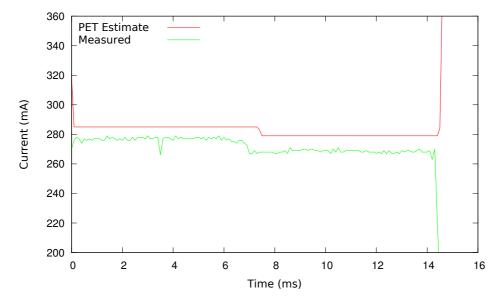

Butko et al. [58] reports gem5 *runtime* accuracy to vary from 1.39 % to 17.94 %, with the most accurate results coming from programs with low memory usage. The benchmarks used represents a wide variety of scientific workloads, as well as media applications and memory intensive synthetic benchmarks. The benchmarks used has a high degree of instruction diversity, so they get away with having a simple CPU model. The real program flow gets diluted and accurate timings are obtained simply by setting the correct CPI value. In fact, they used an in-order model to simulate an out-of-order core.

We claim that the key to obtain high precision power estimates is an architectural simulator with great accuracy. The simulator must exhibit similar timing characteristics as the target hardware under all workloads considered, such that the simulated execution resembles the hardware execution as close as possible. This means that accurate power estimation needs these discrete events to happen, and they must happen with a realistic timing related to their triggering cause. Without a simulator capable of providing decent accuracy over system events, power estimation using methods as suggested in this report will fail. We will now explain how gem5 can be configured to improve simulator accuracy for a particular CPU core, as well as pointing out difficulties with this approach.

## 4.2.1 gem5 CPU configuration

The gem5 simulator is bundled with an out-of-order core implementing the ARMv7 ISA. It serves as a basis for the evolution of our custom core meant to model a Cortex-A9 on the Exynos 4412 SoC. ARM cores can be configured with caches of varying sizes decided by the implementing vendor and will have varying performance accordingly. Thus, it is important to tune all CPU parameters so that it matches the modeled SoC. It is not publicly known which SoC the default configuration attempts to model, but according to the gem5 mailing list it is neither Cortex-A9 nor Cortex-A15 [59]. However, the fact that it is made for the ARMv7 instruction set and is out-of-order leads us to think that minor modifications will make it a decent Cortex-A9 model.

The model gem5 uses in its simulations can easily be configured using a Python interface. We started with gem5 changeset aaf017eaad7d and added a new CPU configuration file for the Exynos 4412; gem5/configs/common/Exynos\_4412P.py. A few other files were edited to accommodate the new processor definition. Please refer to Appendix B to see all patches applied in these experiments.

We found many sources of information claiming to know implementation details of the Cortex-A9, including [58, 60, 61, 62, 63, 64, 65, 66].

Combining this information helps us build a gem5 model for the Exynos SoC, but

it is still not trivial. We found the simulator to perform different from the physical hardware, even though the system parameters were set equal. We claim that this is due to the abstraction the simulator provides us; the simulator is not a complete model of the hardware. Gibson et. al. [67] have done a similar experiment using different simulators and concluded that bugs and omissions in system simulators may render accuracy tuning difficult.

To improve our results, we adjusted the model specification such that it *performed* similar to the hardware, i.e., programs executed in about the same number of clock cycles. Even if the processor implementation would have been completely transparent, it would still be hard to leverage the use of a multi-architecture computer simulator. Features such as fast-loop mode found in certain ARM cores must have a corresponding implementation in the simulator for complete correctness; it would be infeasible to include such details in a general simulator.

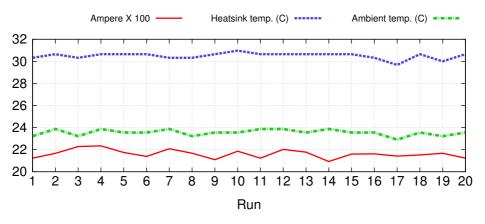

We scripted the simulator to run a wide variety of configurations, about 50 in total. We evaluated their performance by comparing simulated execution time to execution time on real hardware. Real execution time was inferred by measuring power during program executions and identifying when the CPU was working. The final CPU configuration is shown in its entirety in section B.1.

## 4.2.2 gem5 Memory Model

The memory system is an important part of a system simulator when doing performance estimations. At the time of writing, gem5 will not easily work with an out-of-order CPU model together with the GEMS Ruby memory system. Lacking other methods and considering our resources, the simple memory system will provide events that PET can use to determine memory and memory bus communications. The simple memory model was tuned as shown in section B.6.

## 4.3 Multi-objective Weight Optimization

With an accurate CPU model, the event weights used by PET must now be tuned to match measured power consumption on real hardware. We formulated this as a multi-objective optimization problem.

We started by creating a set of training workloads, essentially computer programs designed to hold certain characteristics compiled to a native  $ARMv7^1$  binary. The design and selection of these will be elaborated in the next subsection. We executed the binaries in the gem5 simulator with the CPU model from last section to obtain

<sup>&</sup>lt;sup>1</sup>ARMv7 is the instruction set architecture supported by ARM Cortex-A9.

Algorithm 4.1 Algorithm used to evolve a set of event weights.

```

1

individuals = createIndividuals()

\mathbf{2}

generations = 6000

3

4

best = None

5

for 1 to generations:

for ind in individuals:

6

7

evaluate(ind)

if ind betterthan best:

8

9

best = ind

10

individuals = mutate(ind)

11

12

print best

```

a file containing (time, event) tuples from the (modeled) execution, just like in Listing 3.1. The next challenge was to assign each of these events a cost.

We attack this problem by running a multi-objective optimization algorithm. We picked a subset of event types that is believed to impact energy consumption, as we described in subsection 3.2.2. Choosing too many events could give us overfitting issues, but taking too few out could lead to lack of detail in our model. We experimented with dozens of optimization algorithms and ended up combining a  $1 + \lambda$  evolutionary strategy with simulated annealing. The evolutionary part would make sure that our algorithm was explorative enough (i.e., it covered large parts of the candidate solution space), while the simulated annealing part made the algorithm more aggressive to start with. Using DEAP [68], a Python framework for evolutionary algorithms, we were able to prototype our ideas rapidly. Algorithm 4.1 describes the final algorithm.

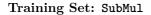

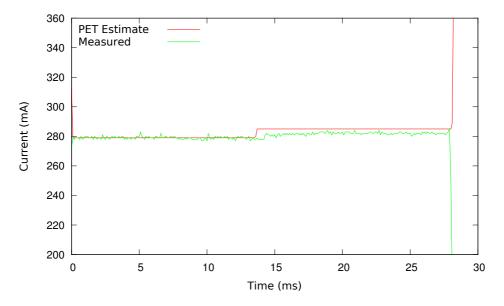

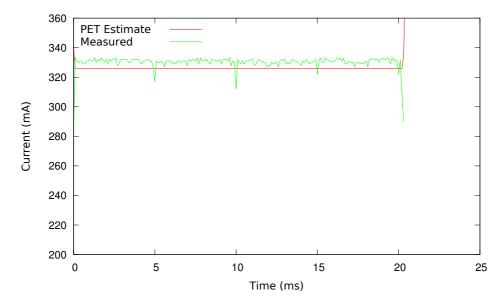

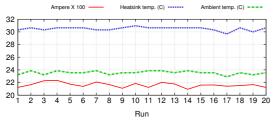

|        | IntAlu | IntMult | MemRead | •••   | PhysW  |