# Linux for SHMAC

# Håkon Furre Amundsen Joakim Erik Christopher Andersson

Master of Science in Computer ScienceSubmission date:June 2014Supervisor:Lasse Natvig, IDICo-supervisor:Asbjørn Djupdal, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

# Abstract

For several years it has been possible to improve processor performance by taking advantage of the ever increasing transistor density. Recently, the power demand of processors has exceeded their power budget, so it is no longer possible to utilize all parts of the processor at the same time. The heterogeneous processor architecture is suggested in order to circumvent this effect. By containing specialized processor cores that are optimized for certain types of tasks, the single thread performance can still be increased while staying within the power budget.

The SHMAC project provides a research framework for heterogeneous architectures, in which different hardware components acts as interchangeable tiles. Currently, the only processor tile available in the SHMAC project is the ARMv2a ISA compliant Amber processor tile.

The only operating systems currently available for SHMAC is the experimental research operating system Barrelfish. Hence, most software written for SHMAC runs without an operating system, directly above the hardware. As the SHMAC hardware is frequently modified, maintaining compatibility between software and hardware is a tedious job, imposing limitations on the efficiency for SHMAC software development.

This thesis presents the process of porting the Linux kernel to SHMAC. The Linux kernel provides a powerful abstraction layer which allows the researchers to be more efficient when writing software to SHMAC.

The Amber processor tile was upgraded to support the ARMv4T ISA before porting. Once Linux was ported to this new processor tile, a toolchain was generated and a large set of user applications was built.

The final result of this project is a familiar Linux environment with over 200 UNIX applications made available through a standard UNIX shell.

# Sammendrag

I flere år har det vært mulig å forbedre prossessorytelsen ved å ta i bruk den stadig økende transistortettheten. I de siste årene har strømkravet til prosessorene overgått strømbudsjettet deres, så det er ikke lenger mulig å benytte alle delene av prosessoren samtidig. Den heterogene prossesorarkitekturen er foreslått for å overkomme dette problemet.

SHMAC-prosjektet tilbyr et forskningsrammeverk for heterogene prosessorarkitekturer, hvor forskjellige maskinkomponenter fungerer som utskiftbare moduler. For tiden er den ARMv2a kompatible Amber kjernen den eneste prosessormodulen tilgjengelig.

Det eneste operativsystemet tilgjengelig for SHMAC er det eksperimentelle forskningsoperativsystemet Barrelfish. Som et resultat av dette kjører mesteparten av koden skrevet for SHMAC uten noe operativsystem, direkte på maskinvaren. Siden maskinvaren til SHMAC ofte blir byttet ut vil jobben med å holde programvaren kjørbar være tidkrevende, og gjøre programvareutviklingen til SHMAC mindre effektiv.

Denne rapporten presenterer arbeidet gjort for å tilpasse Linux-kjernen til å kjøre på SHMAC. Linux kjernen gir programvare et kraftig abstraksjonslag som lar utviklerne være mer effektive når de skriver programvare til SHMAC.

Amber prosessormodulen ble oppgradert til å støtte ARMv4T instruksjonssettarkitekturen før Linux-kjernen ble modifisert. Da Linux var modifisert til å kunne kjøre på denne nye prosessormodulen ble det laget et verktøysett for å lage kjørbare programmer, samt et stort sett med brukerprogrammer.

Det endelige resultatet av dette prosjektet er et kjent Linux-miljø med over 200 UNIX programmer, tilgjengeliggjort gjennom et standard UNIX-skall.

# Preface

This report is submitted to the Norwegian University of Science and Technology in fulfillment of the requirements for master thesis.

This work has been performed at the Department of Computer and Information Science, NTNU, with Prof. Lasse Natvig as the supervisor, and Asbjørn Djupdal as co-supervisor.

# Acknowledgments

Thanks to Lasse Natvig and Asbjørn Djupdal for all help with the technical work and the report. Thanks to Anders Akre and Sebastian Bøe for help with reusing the testbench from the Amber project, for providing us with an improved multiply unit, and for giving us an accelerated processor tile that could be used when performing the benchmarking necessary for this project. Thanks to Stian Hvatum and Terje Runde for help with proofreading the thesis. Also thanks to Benjamin Bjørnseth for technical assistance.

Hello Tobias!

# **Problem Description**

SHMAC is an FPGA-based multicore prototype developed in a research project within the Energy Efficient Computing Systems (EECS) strategic research area. SHMAC is planned to be an evaluation platform for research on heterogeneous multi-core systems. The goal of the SHMAC project is to propose software and hardware solutions for future power-limited heterogeneous systems.

The main goal of this master thesis project is to port a recent version of Linux to run on SHMAC. As discovered in the autumn project conducted by Håkon Amundsen and Joakim Andersson, the SHMAC hardware needs some modifications to support Linux v2.6 and later. This project will therefore involve both Verilog design and Linux kernel programming.

Main tasks included in the project are:

- Implement support for the ARM v3 ISA in the Amber SHMAC CPU tile.

- Create a Linux port for the new CPU tile.

- Test and benchmark individual components and the finished system

If time permits, the students can also:

- Enable multiprocessor support.

- Investigate possibilities for mass storage support through the SHMAC host driver.

# Contents

| Co       | onter               | $\mathbf{ts}$ |                                          | ix       |  |

|----------|---------------------|---------------|------------------------------------------|----------|--|

| Li       | List of Tables xiii |               |                                          |          |  |

| Li       | st of               | Figure        | es                                       | xv       |  |

| A        | bbrev               | viation       | s                                        | xvii     |  |

| 1        | Intr                | oducti        | on                                       | 1        |  |

|          | 1.1                 |               | uter Architecture Trends                 |          |  |

|          | 1.2                 | SHMA          | m C                                      | 2        |  |

|          | 1.3                 | SHMA          | C Operating System Project               |          |  |

|          | 1.4                 | Assign        | ument Interpretation                     | 3        |  |

|          | 1.5                 | Contri        | butions                                  | 4        |  |

|          | 1.6                 | Report        | t Outline                                | 4        |  |

| <b>2</b> | Bac                 | kgrour        | ıd                                       | <b>5</b> |  |

|          | 2.1                 | SHMA          | m AC                                     | 5        |  |

|          |                     | 2.1.1         | SHMAC Architecture                       | 5        |  |

|          |                     | 2.1.2         | Amber Processor Tile                     | 6        |  |

|          |                     | 2.1.3         | SHMAC Development Environment            | 7        |  |

|          | 2.2                 | ARM           | Instruction Set Architecture             | 7        |  |

|          |                     | 2.2.1         | Comparing the ARMv2a and ARMv3 ISA       | 8        |  |

|          |                     | 2.2.2         | Comparing the ARMv3 and ARMv4 ISA        |          |  |

|          |                     | 2.2.3         | ARMv4T Extension                         | 12       |  |

|          |                     | 2.2.4         | ARM Architecture Procedure Call Standard | 12       |  |

|          | 2.3                 | Amber         | r                                        | 13       |  |

|          |                     | 2.3.1         | Amber Core                               | 14       |  |

|          |                     | 2.3.2         | Test Framework                           |          |  |

|          | 2.4                 | Opera         | ting Systems                             | 16       |  |

|          |                     | 2.4.1         | Operating System Definition              | 16       |  |

|          |                     | 2.4.2         | Terminology Used in this Thesis          | 16       |  |

|          | 2.5                 | Linux         |                                          |          |  |

|          |                     | 2.5.1         | Linux Distribution Overview              |          |  |

|          |                     | 2.5.2         | Linux Kernel Overview                    | 17       |  |

|          |                     | 2.5.3         | Porting Linux                            | 18       |  |

|   |      | 2.5.4 Writing Software for Linux                      | 0 |

|---|------|-------------------------------------------------------|---|

|   | 2.6  | The uClinux Project                                   | 1 |

|   | 2.7  | GNU Operating System                                  | 1 |

|   | 2.8  | BusyBox                                               | 2 |

|   | 2.9  | Toolchains                                            | 2 |

|   |      | 2.9.1 Standard C Library 2                            | 3 |

|   | 2.10 | Multicore Operating Systems                           | 4 |

|   |      | 2.10.1 Symmetric Multiprocessing                      | 4 |

|   |      | 2.10.2 Locking Primitives                             | 4 |

|   |      | 2.10.3 SMP in Linux                                   | 5 |

| • | ъ    |                                                       | _ |

| 3 | Rav  |                                                       |   |

|   | 3.1  | Motivation                                            |   |

|   | 3.2  | Execution Stage Schematic                             |   |

|   | 3.3  | Implementing Rav with ARMv3 Support                   |   |

|   |      | 3.3.1 Program Status Registers                        |   |

|   |      | 3.3.2 New Processor Modes                             |   |

|   |      | 3.3.3 Program Status Register Transfer Instructions 3 |   |

|   | ~ .  | 3.3.4 Execution Context                               |   |

|   | 3.4  | Implementing Rav with ARMv4T support                  |   |

|   |      | 3.4.1 System Mode                                     |   |

|   |      | 3.4.2 Long Multiplication                             |   |

|   |      | 3.4.3 Halfword Load and Store                         |   |

|   |      | 3.4.4 Branch and Exchange 3                           |   |

|   | 3.5  | Testing Rav                                           |   |

|   |      | 3.5.1 Instruction Tests                               |   |

|   |      | 3.5.2 System Testing                                  |   |

|   |      | 3.5.3 Performance                                     | 8 |

| 4 | Port | ting Linux to SHMAC 4                                 | 1 |

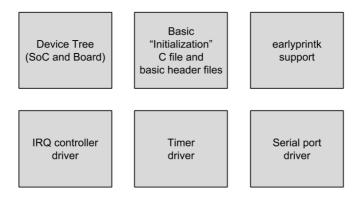

| - | 4.1  | Porting Steps                                         |   |

|   | 4.2  | Linux Device Tree                                     |   |

|   | 4.3  | Basic Setup                                           |   |

|   | 1.0  | 4.3.1 SoC Initialization                              |   |

|   |      | 4.3.2 Early Kernel Messages                           |   |

|   |      | 4.3.3 Starting the Kernel                             |   |

|   | 4.4  | Interrupt Controller Driver                           |   |

|   | 4.5  | Timer Driver                                          |   |

|   | 1.0  | 4.5.1 Clockevent Device                               |   |

|   |      | 4.5.2 Clocksource Device                              |   |

|   | 4.6  | Serial Driver                                         |   |

|   | 1.0  | 4.6.1 Driver Registration                             |   |

|   |      | 4.6.2 Console                                         |   |

|   |      | 4.6.3 Serial Port                                     |   |

|   |      | 4.6.4 UART Callback Functions                         |   |

|   |      |                                                       | 1 |

|   |      |                                                       | т |

|    |      | 4.6.6 UART Reception                                                                                                                      |

|----|------|-------------------------------------------------------------------------------------------------------------------------------------------|

|    | 4.7  | Adding Multicore Support to Linux                                                                                                         |

|    |      | 4.7.1 Adding Kernel Support 54                                                                                                            |

|    |      | 4.7.2 Adding Hardware Support                                                                                                             |

|    | 4.8  | Testing Linux                                                                                                                             |

|    | 1.0  | 4.8.1 Interrupts                                                                                                                          |

|    |      | 4.8.2 Timer                                                                                                                               |

|    |      | 4.8.3         Serial Communication         56                                                                                             |

|    |      |                                                                                                                                           |

|    |      | 4.8.4 System Calls                                                                                                                        |

| 5  | Use  | land Toolchain 61                                                                                                                         |

| 0  | 5.1  | Userland Toolchain Requirements                                                                                                           |

|    | 5.2  | Challenges Encountered                                                                                                                    |

|    | 0.2  | 5.2.1 libgcc                                                                                                                              |

|    |      | 5.2.1 $nlgee \dots $                |

|    |      |                                                                                                                                           |

|    |      |                                                                                                                                           |

|    | 5 0  | $5.2.4 \text{ elf2flt} \dots \dots$ |

|    | 5.3  | The Final Toolchain                                                                                                                       |

|    | 5.4  | Testing the Toolchain                                                                                                                     |

| 6  | Buil | ding a Linux Distribution 65                                                                                                              |

| U  | 6.1  | Creating a Userspace Environment                                                                                                          |

|    | 6.2  |                                                                                                                                           |

|    |      |                                                                                                                                           |

|    | 6.3  | Using SHMAC Linux                                                                                                                         |

| 7  | Ben  | chmarking 69                                                                                                                              |

| •  | 7.1  | Benchmark Set                                                                                                                             |

|    | 7.2  | Comparing Benchmark Results on Linux and Bare Bones 69                                                                                    |

|    | 7.3  | Comparing Performance Increase Achieved on Linux and Bare Bones 70                                                                        |

|    | 1.5  | Comparing renormance increase Achieved on Linux and Dare Dones 70                                                                         |

| 8  | Disc | ussion 73                                                                                                                                 |

|    | 8.1  | Performing a Bottom Up Project                                                                                                            |

|    | 8.2  | Top Down Verification   73                                                                                                                |

|    | 8.3  | Building a Toolchain in Parallel                                                                                                          |

|    | 8.4  | Design Choices                                                                                                                            |

|    | 0.1  | 8.4.1 Supporting ARMv4T                                                                                                                   |

|    |      | 8.4.2 Including an FPGA Specific Multiplier                                                                                               |

|    |      | 8.4.3       Building BusyBox for SHMAC       75                                                                                           |

|    | 0 5  |                                                                                                                                           |

|    | 8.5  | Results                                                                                                                                   |

| 9  | Con  | clusion 79                                                                                                                                |

| 10 | Furt | her Work 81                                                                                                                               |

| TO |      | Memory Management Unit                                                                                                                    |

|    |      |                                                                                                                                           |

|    | 10.2 | Upgrade Serial Port Driver for new Single-ISA Heterogeneous MAny-                                                                         |

|    |      | core Computer (SHMAC) Implementation                                                                                                      |

|              | 10.3  | Enable Mass Storage Support                            | 81 |

|--------------|-------|--------------------------------------------------------|----|

|              | 10.4  | Symmetric Multiprocessing (SMP) Support in SHMAC Linux | 82 |

|              | 10.5  | Upgrading Rav                                          | 82 |

| Bi           | bliog | graphy                                                 | 83 |

| $\mathbf{A}$ | Con   | npile and Run Linux                                    | 85 |

|              | A.1   | Setup Enviroment Variables                             | 85 |

|              | A.2   | Toolchain                                              | 85 |

|              | A.3   | BusyBox                                                | 85 |

|              | A.4   | Linux Kernel                                           | 86 |

|              | A.5   | Run                                                    | 86 |

|              | A.6   | Building Userland Applications                         | 87 |

|              | A.7   | Miscellaneous                                          | 88 |

| в            | Тоо   | lchain Guide                                           | 89 |

|              | B.1   | Kernel Toolchain                                       | 89 |

|              | B.2   | Userland Toolchain                                     | 89 |

|              |       | B.2.1 Setup                                            | 89 |

|              |       | B.2.2 Setup uClibc                                     | 90 |

|              |       | B.2.3 Configuration uClibe                             | 90 |

|              |       | B.2.4 Setup Crosstool-NG                               | 91 |

|              |       | B.2.5 Configuration Crosstool-NG                       | 92 |

|              |       | B.2.6 Building the Toolchain                           | 93 |

| $\mathbf{C}$ | Inst  | ruction Test Cycle Comparison                          | 95 |

# List of Tables

| 2.1 | ARMv2a status flags.                                                | 8  |

|-----|---------------------------------------------------------------------|----|

| 2.2 | ARMv2a processor mode bits                                          | 9  |

| 2.3 | AAPCS register convention                                           | 13 |

| 3.1 | ARMv3 processor mode bits.                                          | 29 |

| 4.1 | Linux atomic interface                                              | 55 |

| 4.2 | Verifying process system calls.                                     | 58 |

| 4.3 | Verifying security system calls                                     | 59 |

| 4.4 | Verifying memory system calls                                       | 60 |

| 4.5 | Verifying files and folders system calls                            | 60 |

| 7.1 | Comparing benchmark results from Linux and bare metal               | 70 |

| 7.2 | Performance increase measured when executing benchmark on top of    |    |

|     | Linux                                                               | 71 |

| 7.3 | Performance increase measured when executing benchmark on top of    |    |

|     | bare metal                                                          | 71 |

| 7.4 | Percentage difference between executing benchmark on Linux and bare |    |

|     | metal                                                               | 72 |

|     |                                                                     |    |

# List of Figures

| 2.1  | SHMAC tile architecture overview                                         |

|------|--------------------------------------------------------------------------|

| 2.2  | Architecture of a generic SHMAC tile                                     |

| 2.3  | SHMAC memory map                                                         |

| 2.4  | The 26-bit PC scheme of ARMv2a                                           |

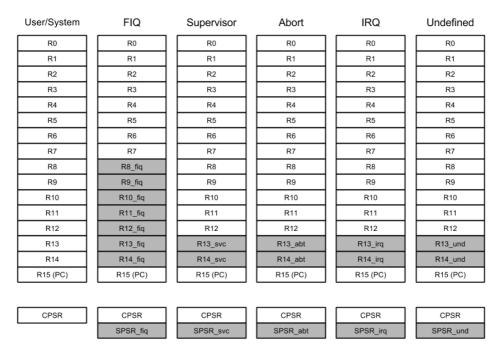

| 2.5  | Banked register overview                                                 |

| 2.6  | Examples of PC usage in ARMv2a 10                                        |

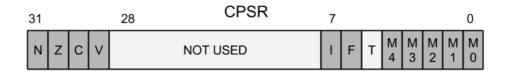

| 2.7  | The CPSR scheme of ARMv3                                                 |

| 2.8  | Sign extending values represented as two's complement                    |

| 2.9  | Amber system overview.13                                                 |

| 2.10 | Conceptual placement of register bank in execute stage                   |

| 2.11 | Linux distribution layers. (From [29]) 17                                |

| 2.12 | Linux kernel components. (From [29]) 18                                  |

| 2.13 | Operating system hardware touch points                                   |

| 2.14 | Example of hardware specific code                                        |

|      | Operating system driver interface illustration                           |

| 3.1  | Rav schematic execution stage                                            |

| 3.2  | Program status register format. (From [18].)                             |

| 3.3  | ARMv3 and ARMv4T register bank. (From [18].)                             |

| 3.4  | Going from three register read support (left) in ARMv3, to four register |

|      | read support (right) in ARMv4                                            |

| 3.5  | The program status register format in ARMv4T                             |

| 3.6  | Excerpt from an instruction test for the add instruction                 |

| 3.7  | Setting up the stack pointers of various execution modes for Rav 38      |

| 4.1  | ARM SoC porting steps. (From [6].)                                       |

| 4.2  | SHMAC Linux Device Tree (LDT) definition                                 |

| 4.3  | Linux SoC kernel configuration                                           |

| 4.4  | SHMAC early printk implementation                                        |

| 4.5  | Simplified version of the bootloader                                     |

| 4.6  | SHMAC timer driver exporting compatible flags to the LDT 47              |

| 4.7  | Function for reading the value of the SHMAC system clock register. 48    |

| 4.8  | Console write function in SHMAC serial driver                            |

| 4.9  | SHMAC serial driver UART transmit function                               |

| 4.10 |                                                                          |

| 4.11 | Excerpt from Linux SMP code for ARM                                      |

|      | 1                                                                        |

|     | Excerpt from Linux kernel configuration for ARM |    |

|-----|-------------------------------------------------|----|

| 5.1 | Components included in the userland toolchain   | 62 |

|     | Example of initramfs configure list             |    |

| 8.1 | Top down verification                           | 74 |

# Abbreviations

**AAPCS** ARM Architecture Procedure Call Standard.

**ABI** Application Binary Interface.

AIC Amber Interrupt Controller.

ALU Arithmetic Logic Unit.

**CPSR** Current Program Status Register.

**FIQ** Fast Interrupt Request.

FPGA Field Programmable Gate Array.

${\bf ILP}\,$  Instruction Level Parallellism.

**IRQ** Interrupt Request.

**ISA** Instruction Set Architecture.

${\bf LDT}\,$  Linux Device Tree.

MMU Memory Management Unit.

$\mathbf{MPU}\xspace$  Memory Protection Unit.

PC Program Counter.

**PSR** Program Status Register.

SHMAC Single-ISA Heterogeneous MAny-core Computer.

**SMP** Symmetric Multiprocessing.

SoC System on Chip.

SPSR Saved Program Status Register.

**TLP** Thread Level Parallellism.

# Chapter Introduction

During the lifespan of the computer processor, various techniques have been used to increase its performance. These techniques have helped improved the performance of the processor 25,000 fold [22]. As the processor evolves, some of these techniques stop being efficient, and new limitations are discovered. This provides the computer architects with ever new challenges. In recent years, the biggest problem facing the computer architects has been related to power consumption.

# 1.1 Computer Architecture Trends

From the introduction of the RISC architecture in the early '80s to the late '90s, the most important fields of improvement for processors has been Instruction Level Parallellism (ILP) and memory system techniques [22].

ILP refers to the potential overlap among machine level instructions. There are several ways of exploiting this overlap. Processor pipelining, out of order execution, branch prediction and superscalar execution are all techniques that increase processor performance by exploiting the ILP in the intsruction stream [25, 22]. Memory system techniques aim to decrease the latency and increase the bandwidth of instructions and data from memory to the processor. These two fields of improvement have worked hand in hand with Moores Law, which states that the number of transistors available for a processor doubles every 18 to 24 months [22]. This allows the researchers to simply add wider buses, more registers, longer pipelines, more advanced branch predictors and generally making the processor more complex.

In the early 2000s, extracting any more ILP from the instruction stream reached a point of diminishing returns. The processors had become too complex, and their power consumption was too much for the available cooling systems to handle. In 2004, Intel canceled all of its high-performance uniprocessor projects as a result of this. They decided to focus all attention on the new architecture trend, multiple processor cores per chip [22].

The multiprocessor architectures exploit the Thread Level Parallellism (TLP) in the instruction stream. By looking at typical workloads for a processor, it is

#### 2 1. INTRODUCTION

evident that several of the execution threads are independent of each other. These independent threads can be executed in parallel on two or more separate processing units, allowing an increase in performance. TLP was exploited by including several processor cores on a single chip.

One of the reasons why it was now possible to have multiple processor cores on a single chip, was the increase in transistor density. This scheme relied not only on Moores Law, but also on Dennard Scaling, which states that as number of transistors per unit area increase, the power consumption remains constant [20]. Unfortunately, the Dennard Scaling stopped applying, while Moores law continued [21]. The power usage per unit area increased as the transistor density increased, making it difficult to keep the processor temperature at an acceptable level. Consequently, it was no longer possible to utilize all parts of the processor at the same time. This effect is known as "dark silicon".

One of the suggested strategies for mitigating this effect is the use of heterogeneous multicore processor architectures, which contains several processing elements with different performance and power characteristics.

# 1.2 SHMAC

The SHMAC project is an effort from NTNUs Energy Efficient Computing Systems (EECS) strategic research area to investigate challenges posed by heterogeneous computer architectures [12]. It proposes a tile based architecture of generic computing units connected in a network. There exists different types of computing units. At the time of writing there exists processor tiles, memory tiles and communication tiles. The current processor tile is a slightly modified version of the open source Amber processor core, which supports the ARMv2a Instruction Set Architecture (ISA). This ISA was used in the Acorn computers during the late 80s and early 90s [1, 2, 3, 4]. Using an ISA this old impose restrictions to what software can be compiled and run on SHMAC. A Field Programmable Gate Array (FPGA) prototype of this architecture has been developed [26].

# 1.3 SHMAC Operating System Project

This master thesis builds on the work described in the report "SHMAC Operating System" [17]. The project was an effort to port an operating system to run on the SHMAC hardware. It investigated several candidates for porting before deciding that Linux should be the target operating system. The 2.4.28 version of the Linux kernel was ported.

The ported kernel executed on one core, and was able to boot, mount the root filesystem and execute a single userland application with a limited set of working system calls.

The Amber core used in this project supported the ARMv2a ISA, this project faced several problems as a consequence. During this project, it was found that this ISA was not supported in any recent versions of the Linux kernel. Linux 2.4 was the last kernel version to include support for the ARMv2a ISA, which is why this was the Linux version used. The main research field in the SHMAC project is multicore architectures, however it was found that the Linux 2.4 kernel did not scale to multicore environments. The ARMv2a support in the Linux kernel was in such a state that performing ports to systems with this architecture was cumbersome. The toolchain used in this project had several shortcomings and put severe restrictions on software compatibility.

The proposition of the project was to modify the Amber processor tile to support a more recent version of the ARM ISA, allowing more recent Linux versions to be ported.

# 1.4 Assignment Interpretation

The following tasks were interpreted from the assignment text:

#### Mandatory:

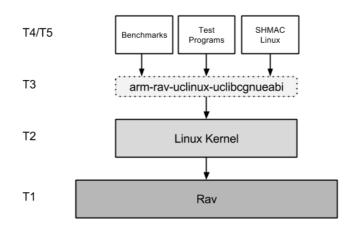

T1 Modify the Amber processor tile so that it supports the ARMv3 ISA.

T2 Port a recent version of the Linux kernel to this new processor tile.

${\bf T3}\,$  Provide a tool chain which is compliant with the ported version of the Linux kernel.

${\bf T4}\,$  Test and Benchmark the new processor tile and the ported version of the Linux kernel.

#### **Optional:**

T5 Build a minimal Linux distribution capable of user interaction.

T6 Enable multicore support in the ported Linux kernel.

**T7** Investigate the possibility of mass storage through the SHMAC host controller.

The tasks **T1** and **T2** have been directly extracted from the assignment text. The task **T3** has been interpreted from the assignment text and made mandatory since, although user applications are not part of the Linux kernel, a Linux kernel without the ability to run user applications would not be a usable system. Also, a Linux version without the ability to run user applications would be very hard to test. The task **T5** has been added as an optional task to increase the productivity of SHMAC developers by providing a familiar environment to run applications in.

#### 4 1. INTRODUCTION

This makes it easier to run programs in an interactive environment and to run a set of applications on different hardware configurations. The tasks **T6** and **T7** are optional and something to be looked at when the Linux port was considered to be working correctly.

# 1.5 Contributions

This project provides the SHMAC project with a new processor tile, Rav, compatible with the ARMv4T ISA. The Linux 3.12.13 kernel has been ported to support SHMAC running a single ARMv4T compatible processor tile. A toolchain which is fully compliant with the ported Linux kernel is provided, alongside a large set of applications which has been built using this toolchain. A complete Linux distribution containing a large set of standard UNIX tools and an interactive shell has been built to provide a familiar Linux experience. Tools and documentation are provided to make it easy to install and run Linux on SHMAC.

# 1.6 Report Outline

**Chapter 1: Introduction** gives an introduction to the motivation behind heterogeneous computer architectures. It presents the SHMAC project, assignment interpretation and a summary of contributions.

Chapter 2: Background introduces concepts related to this project.

**Chapter 3: Rav** gives a detailed description of the process of modifying the Amber processor tile to support the ARMv4T instruction set architecture.

**Chapter 4: Porting Linux to SHMAC** describes the process of porting the Linux 3.12.13 kernel to SHMAC.

**Chapter 5: Userland Toolchain** presents the process of building a toolchain for the ported Linux kernel.

**Chapter 6: Building a Linux Distribution** describes the process of integrating BusyBox with the ported Linux kernel in order to provide a complete Linux distribution.

Chapter 7: Benchmarking contains a set of benchmark results.

**Chapter 8: Discussion** presents a detailed discussion about the project process, the choices made and the results achieved.

Chapter 9: Conclusion provides concluding remarks.

**Chapter 10: Further Work** gives a set of suggestions for further work on this project.

This chapter introduces information required to understand the work done in this project.

# 2.1 SHMAC

SHMAC is a hardware prototype of a Single-ISA Heterogeneous MAny-core Computer [12]. It is an ongoing research project within the Energy Efficient Computing Systems (EECS) research area at the Department of Computer and Information Science, and Department of Electronics and Telecommunications at NTNU. The goal of the SHMAC project is to propose hardware and software solutions for future computer systems in order to tackle the Dark Silicon effect.

### 2.1.1 SHMAC Architecture

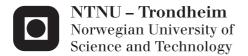

The SHMAC architecture specifies a grid of generic computing tiles, as seen in Figure 2.1. The tiles are connected in a 2D mesh network topology.

Figure 2.1: SHMAC tile architecture overview.

#### 6 2. BACKGROUND

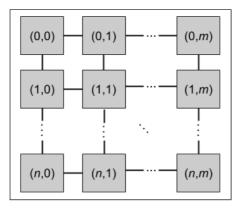

It is required that all of the tiles are able to forward packets to other tiles. This forwarding is performed by a router which is included in all SHMAC tiles, see Figure 2.2

Figure 2.2: Architecture of a generic SHMAC tile.

As previously stated, each of the tiles can be made out of different hardware. Currently, the following tile types are available:

- Communication tile.

- Block RAM, 16 kB.

- External RAM, 32 MB.

- Amber25 processor tile.

The communication tile deals with the serial communication with the host. The block RAM provides memory which is implemented on the FPGA, whereas the external ram tile integrates a larger, slower, off chip memory. The block RAM is small and fast while the external RAM is large and slow.

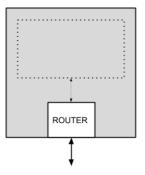

The SHMAC architecture uses a 32-bit address space to provide access to the its various components, as seen in Figure 2.3. It should be noted that only a subset of the available addresses is mapped to actual devices.

### 2.1.2 Amber Processor Tile

The Amber processor tile is based on the five stage pipeline version of the Amber Core, described in section 2.3. The Amber core is slightly modified to be compatible with the SHMAC architecture. Since the Amber project is optimized for synthesis, it does not include a reset signal. This is added to the SHMAC version. The interrupt controller has been updated into using a generic bus for its sources, not one line for each source as was the case for the original Amber core.

Figure 2.3: SHMAC memory map.

#### 2.1.3 SHMAC Development Environment

The SHMAC prototype is implemented on a Xilinx Virtex 5 XV5VSX330 FPGA located on an ARM RealView Versatile platform. This platform contains an FPGA and a host controller. This host controller runs a Linux distribution, and provides the developers with an interface to the SHMAC hardware through a set of kernel modules, described below.

shmac\_program write a file to SHMAC memory.

shmac\_dump dump SHMAC memory to a file.

shmac\_reset reset the SHMAC hardware.

**shmac\_ko** exposes a serial device for communication with the SHMAC hardware.

# 2.2 ARM Instruction Set Architecture

An Instruction Set Architecture (ISA) defines the interface between the hardware and the lowest-level of software [25]. Since its first use in the Acorn computers introduced in the '80s, the ARM Instruction Set Architecture has seen widespread use throughout different markets segments [5]. Over the years the architecture has been upgraded several times. This section will present the changes in two of the upgrades of the ARM ISA, from ARMv2a to ARMv3 and from ARMv3 to ARMv4.

#### 2.2.1 Comparing the ARMv2a and ARMv3 ISA

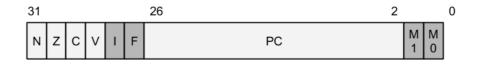

The ARMv2a ISA was used in the ARM2 and ARM3 family of processors which was used by Acorn Computers in their Archimedes line of computers [23]. The ARMv2a ISA is a load store architecture with 16 general purpose 32-bit registers. One of these registers is the Program Counter (PC) register. The program counter value is the memory address of the next instruction to be executed, and is incremented each cycle or modified by instructions. In addition to containing the program counter, the PC register also keeps track of the execution state of the processor, as seen in Figure 2.4. This execution state consist of 8 bits, leaving 24 bits for the program counter value. The program counter is word aligned, this implies that the program counter has a 26-bit address space. The 8 bits used for execution state is 4 bits for status flags, 2 bits for the current execution mode, and 2 bits for interrupt masking.

Figure 2.4: The 26-bit PC scheme of ARMv2a.

The status flags are described in Table 2.1. These are set by the Arithmetic Logic Unit (ALU) output only when the executed instruction explicitly states that the status bits should be updated.

| Identifier | Meaning           |

|------------|-------------------|

| N          | Not Equals        |

| Z          | $\mathbf{Z}$ ero  |

| С          | $\mathbf{C}$ arry |

| V          | oVerflow          |

Table 2.1:ARMv2a status flags.

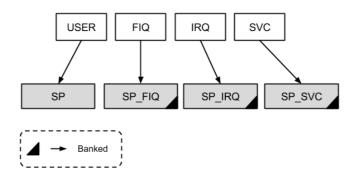

ARMv2a has 4 execution modes: supervisor, interrupt, fast interrupt and user. User mode is the only non-privileged execution mode. The other modes are exception modes and are privileged. The current mode is stored using the two least significant bits of the PC register, M1 and M0, as seen in Figure 2.4, using the values from Table 2.2. Each privileged mode have their own banked link register and stack pointer. This means that the value read when loading the link register or stack pointer differs for each of the modes, as shown in Figure 2.5.

The interrupt mask bits makes it possible to disable/enable interrupts at any given time. Privileged modes are able to freely change mode and interrupt masks while user mode is prevented from this. The interrupt mask bits are also updated by the processor itself when context switches takes place. As an example, when an Interrupt Request (IRQ) is triggered, the IRQ mask is set to 1 automatically, ensuring that no other interrupts take place while the current interrupt is being handled.

| <b>M</b> [1:0] | Mode                         |

|----------------|------------------------------|

| 00             | User                         |

| 01             | Fast Interrupt Request (FIQ) |

| 10             | IRQ                          |

| 11             | Supervisor                   |

Table 2.2:

ARMv2a processor mode bits.

Figure 2.5: Banked register overview.

In order to modify the status bits, the tstp and teqp instructions are used. These instructions perform an AND or XOR compare operation, respectively, and store the status bits in the PC register. An example of this can be seen in Figure 2.6, where the mode is changed, the mask bits are set, and the condition flags are controlled.

The 26-bit program counter scheme puts some restrictions upon further development. Having 26 bits for addressing instructions limits the program counter to only address 64 MB of memory. Also, increasing the amount of bits used for storing the current execution mode, status bits, or interrupt mask bits would decrease size of the program counter.

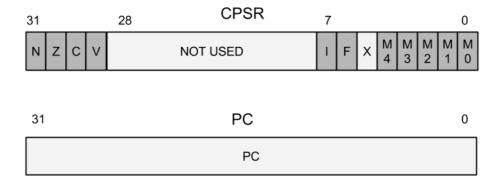

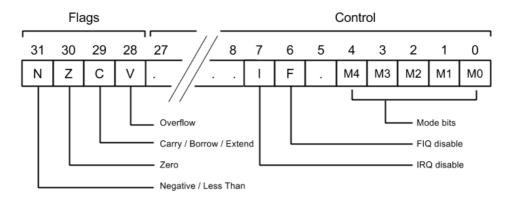

When ARM designed ARMv3 they split the 26-bit PC scheme into a 32-bit PC register and a separate Current Program Status Register (CPSR) used for storing the status bits, as seen in Figure 2.7.

In addition they added a Saved Program Status Register (SPSR) which saves the CPSR when the processor performs a context change. The SPSR register is banked for each exception mode. These registers are not general purpose and can only be accessed by the new instructions **mrs** and **msr**, provided for reading and writing

```

1 /* Switch to IRQ Mode */

2

mov

r0, #0x0000002

3

teqp

pc, r0

4

5

. . .

6

/* Switch to User Mode */

7

/* and unset interrupt mask bits */

8

r0, #0x0000000

9

mov

10 teqp

pc, r0

11

12

. . .

13

14 /* Check that the condition flags are still 0xf */

15 mov

r4, pc

r7, r4, #0xfc00000

16 and

r7, #0x08000000

17 Cmp

18 movne

r10, #70

19 bne

testfail

```

Figure 2.6: Examples of PC usage in ARMv2a.

Figure 2.7: The CPSR scheme of ARMv3.

the status bits registers. ARMv3 also adds two new exception modes: "abort" and "undefined".

#### The Address Exception

The address bus in ARMv2a is 26 bits wide [23]. When calculating memory addresses, it is therefore important to take care not to produce illegal addresses in which one of the top six bits is non-zero. This will trigger an Address Exception.

In the case of ARMv3, any 32-bit value is a legal memory address, hence there exists no Address Exception in ARMv3 or later ARM ISAs.

#### 2.2.2 Comparing the ARMv3 and ARMv4 ISA

ARMv4 extended ARMv3 with half word data transfer, signed data transfer, long multiply and a new execution mode.

#### Half Word Data Transfer

Since high level programming languages use data structures of different sizes, it is desirable to be able to provide instructions which allows you to fetch the correct amount of bits from memory. The default behavior in the ARM architecture is to fetch an entire word (32 bits). ARMv2a and ARMv3 also supports byte transfer (8 bits). ARMv4 adds support for half word (16 bits) data transfer. This is made possible by the ldrh instruction for loading a halfword from memory, and strh for writing a halfword to memory.

#### Signed Data Transfer

When loading a half word sized or byte sized value from memory, it will be placed in a 32 bit register. This has implications for the transfer of signed values, since they need to be sign extended in order to retain their value. ARM represents signed values as two's complement. In the two's complement scheme, the most significant bit is used to tell if the value is positive or negative. When extending a value represented as two's complement, the most significant bit needs to be repeated in the extra bits, as seen in Figure 2.8

```

/* Signed representation of the value

10000 using two's complement using 16 bits*/

2

0010 0111 0001 0000

4

/* Sign extended representation of the value

5

6

10000 using 32 bits */

0000 0000 0000 0000 0010 0111 0001 0000

7

8

9

/* Two's complement representation of the

value -10000 */

11 1101 1000 1111 0000

12

13 /* Sign extended representation of the value

14 -10000 using 32 bits */

15 1111 1111 1111 1111 1101 1000 1111 0000

```

Figure 2.8: Sign extending values represented as two's complement.

ARMv4 adds two new instruction, ldrsb and ldrsh, to automate this process for byte values and half word values respectively.

#### 12 2. BACKGROUND

# Long Multiply

Both ARMv2a and ARMv3 supports multiplying the 32-bit values of two registers. The result of such a multiplication will often be bigger than what it is possible to represent using 32 bits. In the case of ARMv2a and ARMv3 the result is stored in a single 32-bit register. If the result is bigger than what it is possible to represent with 32 bits the value is truncated.

ARMv4 provides long multiplication in which the result is stored in two separate 32-bit registers, making it possible to store the result of any 32-bit multiplication.

#### System Mode

ARMv4 adds the new privileged execution mode, "system". While the other privileged modes all have banked registers, the system mode share all of its registers with the user mode. The only difference between the unprivileged user mode and the privileged system mode is that system mode is able to change the current execution mode.

# 2.2.3 ARMv4T Extension

The T-extension to ARMv4 adds the 16-bit Thumb execution state. This execution state implements a subset of the ARM instruction set using 16-bit representation. A new instruction, bx (Branch and Exchange), is added in T-variants of ARMv4, and is used to switch between regular 32-bit execution state and the 16-bit Thumb execution state.

# 2.2.4 ARM Architecture Procedure Call Standard

When a procedure calls another procedure, they need to agree on how the arguments will be transferred, how the result of the called procedure will be stored, and what state the called procedure should leave the system in when it is done.

Arguments can be transferred in several ways, using the stack or by using the registers. In order to make it possible for separately compiled and assembled code to work together, a standard for transferring arguments needs to be defined, this is the ARM Architecture Procedure Call Standard (AAPCS) [19].

The AAPCS defines how registers are used during a procedure call, as seen in Table 2.3. It also defines how to return from a procedure call.

#### The Role of Branch Exchange in AAPCS

The AAPCS states that the bx instruction should be used when returning from a procedure [[19],p.21]. bx takes a register as argument, and jumps to the address specified by that register. If the last bit of that address is 1, the processor should change to Thumb execution state (16-bit instruction width). Even though this

| Register | Purpose                                                                                                                                                                 |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r0-r3    | Holds the arguments passed to a sub procedure. r0 also holds the result from the subroutine.                                                                            |

| r4-r11   | Holds local variables. These registers needs to be retained during<br>the procedure call, which is done by storing them on the stack<br>while the procedure is ongoing. |

| r12      | The Intra-Procedure-Call scratch register.                                                                                                                              |

| r13      | The stack pointer.                                                                                                                                                      |

| r14      | The link register.                                                                                                                                                      |

| r15      | The program counter.                                                                                                                                                    |

Table 2.3:

AAPCS register convention.

instruction is heavily associated with the Thumb instruction set, it is also used on processors without support for Thumb instructions. In the case of ARMv4, which does not support the bx instruction, a GCC flag, fixv4bx, is provided in order to change all of the bx calls into equivalent mov calls. ARMv4 is therefore incompatible with the AAPCS. In ARMv5 or later, trying to change to Thumb execution state when this is not supported will trigger an undefined exception.

# 2.3 Amber

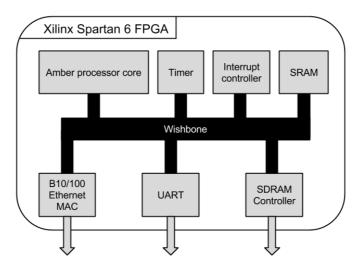

Amber is an open source project which contains a complete embedded computing system. This system consists of the Amber processor core, hereby called the "Amber core", and a set of peripherals as shown in Figure 2.9.

Figure 2.9: Amber system overview.

#### 14 2. BACKGROUND

The Amber project focuses on FPGA synthesis rather than hardware implementations. An example of this is that the Amber cores does not have any reset logic, since this is not necessary in an FPGA environment. The peripherals makes it possible for the user to interact with the system, and to execute applications of a relatively large size. A brief explanation of the peripherals most relevant for this project is given below.

**UART** deals with communication with the users of the system.

Timer generates timed interrupts.

**Interrupt Controller** is a general purpose interrupt controller which is able to send interrupts from various modules.

SDRAM Controller contains the memory of the system.

#### 2.3.1 Amber Core

The Amber project contains two versions of the Amber core: one with a three stage pipeline and one with a five stage pipeline, called A23 and A25 respectively. The Amber processor tile contains a modified version of the five stage pipeline, A25.

#### Pipeline Design

The Amber core is a scalar, in-order processor core with a classical five stage RISC pipeline [22]. The pipeline stages are fetch, decode, execute, memory and write-back.

**Fetch** reads the instruction to be executed from memory and forwards it to the decode stage.

**Decode** looks at the instruction, and decides what needs to be done in the remaining pipeline stages to perform the tasks requested by the instruction. This is arguably the most complex of the five stages, as it needs to be able to parse all legal instructions, and set all of the requested control signals.

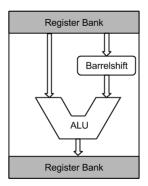

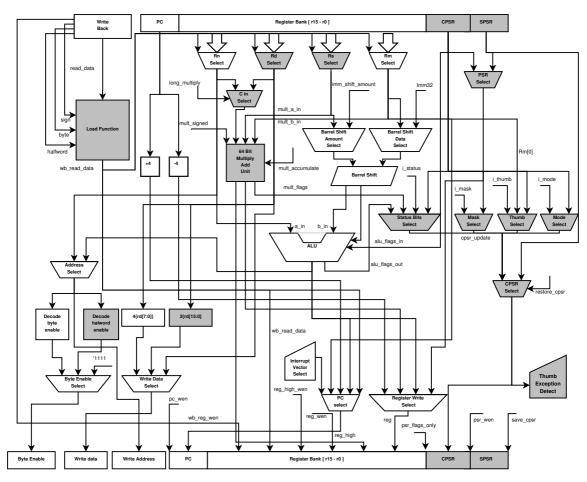

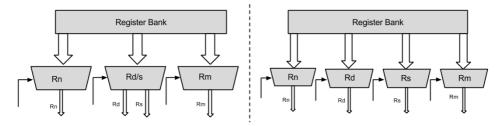

**Execute** performs the actions which is required to change the register values according to the instruction being executed. It is controlled by the decode stage, and is also used for calculating addresses which is sent to the memory stage. In the case of the Amber core, the execute stage contains the register bank. This implies that the register values are updated at the end of the execute stage. Since most instructions read some value from a register, the output from the register bank is wired to the input of the execute stage, creating a circular data flow, seen in Figure 2.10

Memory reads data from or writes data to the memory.

Write-Back saves the data read from memory to the register bank.

Figure 2.10: Conceptual placement of register bank in execute stage.

#### Instruction Set Architecture

The Amber core supports the ARMv2a instruction set architecture. This makes the Amber core compatible with the GNU toolset, and old versions of Linux (ARMv2a support was removed in version 2.6).

### 2.3.2 Test Framework

When designing hardware it is important to perform testing early in the development process. Once the design has been placed on an FPGA it is cumbersome to execute tests and verify the result, hence it is preferred to tests the design in a simulator. In a simulator, the state of the entire system is accessible.

#### Instruction Tests

An instruction test is a test that verifies that the processor behaves correctly for a single assembly instruction. The Amber project contains 59 instruction tests. The tests are executed using the Xilinx ISE simulation tool. Xilinx tools are also used for compiling the Amber system and initializing the memory to be used during the tests.

The test framework is able to execute the same set of code as the FPGA implementation of the Amber system. This is achieved by using a top level design which is developed specifically for simulation.

The test framework contains several scripts which makes it simple to execute a set of tests. These scripts also makes it easy to extend the existing test framework with new tests.

#### System Tests

In addition to the above-mentioned instruction tests, the Amber project contains a set of system tests.

The biggest system test contained within the Amber project is a ported version of the Linux 2.4.28 kernel, which is compatible with the Amber core. When verifying a processor design, it is not enough to verify each of the supported instructions in an isolated environment. Some bugs might not be triggered unless the processor is in a specific state which might only be triggered by a specific sequence of instructions. It is hard, if not impossible, to cover all possible code sequences using a set of small test programs. However, by running an application as big as the Linux kernel the confidence in the correctness of the design is increased.

# 2.4 Operating Systems

The operating system has been an important part of computers since its inception. The variation of complexity and size between operating systems, 45 million lines of code in Windows XP against 16,500 in FreeRTOS, suggests that the term "operating system" is a vague definition.

# 2.4.1 Operating System Definition

An operating system is a layer of software whose job is to "provide user programs with a better, simpler, cleaner, model of the computer and to handle managing all the resources..." [29]. In other words, an operating system is not required to interact with the user of the system, but with the user programs. However the term operating system is often used to describe system that do interact with the user, e.g Microsoft Windows and Apple OS X.

The motivation behind an operating system is twofold. It manages hardware complexity by providing applications with a simpler and cleaner interface. It also handles resource sharing in the system, allowing several programs to execute simultaneously on the same system.

#### 2.4.2 Terminology Used in this Thesis

In the thesis, the terms "Linux", "Linux kernel" and "Linux operating system" are used to refer to the Linux kernel. The term "userland" refers to all code that runs outside of the kernel. The term "Linux distribution" refers to a system with the Linux kernel and a set of userland applications which enables direct user interaction.

# 2.5 Linux

Linux is an open source operating system kernel which has been ported to a large set of computer architectures. It is used in various computing domains, with its highest popularity in the web server and supercomputer domains [13, 15].

## 2.5.1 Linux Distribution Overview

The Linux kernel provides abstractions and services to user *applications*. The term Linux, however, is often used to describe a Linux distribution. A Linux distribution is the Linux kernel together with a set of applications and tools that provides abstractions and services to the *user*.

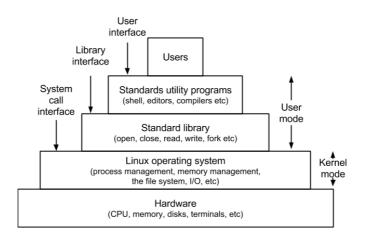

A Linux distribution is a layered system where each layer provides services to the layers above it while relaying on the services provided by the layer below it, as seen in Figure 2.11. The Linux kernel runs on top of the hardware, and is the only piece of software which runs in privileged mode. The library layer runs on top of the kernel and provides access to the kernel system call by wrapping system calls in library procedures. This enables applications to call system calls as if they were regular library routines. Which applications are included in a Linux distribution varies between distributions, from only a shell and some basic utilities to full fledged GUI systems for use with personal computers.

Figure 2.11: Linux distribution layers. (From [29])

## 2.5.2 Linux Kernel Overview

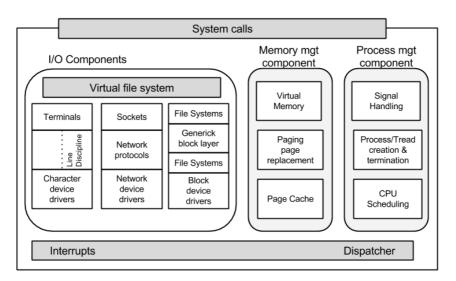

The kernels job is to manage the hardware resources in the system and expose access to these resources through a simplified interface. The simplified interface that the kernel exposes is the system call interface. Internally, the kernel is divided into three major components, as seen in Figure 2.12. The memory management component is responsible for managing the memory available in the system by providing virtual memory and paging functionality. The process management component is responsible for providing the process abstraction, scheduling which process should run and handling interprocess communication with signals. The I/O component manages access to all the input output devices in the system through a unified virtual file system known as the root file system. Resources are made available as files in the root file system.

Figure 2.12: Linux kernel components. (From [29])

# 2.5.3 Porting Linux

The initial versions of Linux were not portable [30]. However, during its lifetime, Linux has come to be one of the most portable and ported operating systems.

For an operating system to be portable, the job of modifying it so that it is able to execute on a previously unsupported computer architecture should be as simple as possible. There are two perspectives one can use when talking about portability.

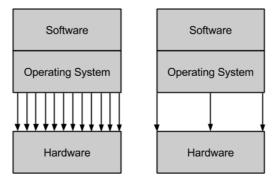

The first of these two perspectives is that of *hardware specific code*. The number of places where hardware specific code is found should be limited to a bare minimum, as Figure 2.13 shows.

The code in Figure 2.14 is an example of hardware specific code. This code excerpt shows the function used for turning off a single interrupt within an interrupt controller. The offset from the memory base of the interrupt controller to the control signal used for clearing interrupts, IRQ\_ENABLE\_CLEAR, would vary between different interrupt controller chips. The base address used for the interrupt controller device could vary between two architectures that used the same interrupt controller device.

Figure 2.13: Operating system hardware touch points.

```

1

#define IRQ_ENABLE_CLEAR 0x0c

2

3

/* Mask (turn off) an interrupt */

static void irq_mask(struct irq_data *d)

4

5

ſ

/* Find the HW-IRQ-nr by looking at the domain */

6

unsigned int irq = irqd_to_hwirq(d);

7

8

9

unsigned int pos = ffs(irq)-1;

/* Write to IRQ control register to mask interrupt */

writel((1 << pos),base + IRQ_ENABLE_CLEAR);</pre>

13 }

```

Figure 2.14: Example of hardware specific code.

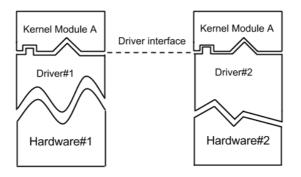

In addition to the hardware specific code perspective, the *upward interface* from the hardware specific code is important. This interface decides how the other operating system components interact with the hardware specific code. By making sure that this interface is well defined, it is possible to use a single implementation of a higher level module with any implementation of this interface, Figure 2.15 illustrates this.

Porting an operating system quickly becomes cumbersome if care is not taken when designing it. Linux is highly portable, it has a layered design which ensures that hardware specific code is limited to the device drivers, and as long as they are compliant with the standard driver interface, no change is required in any higher level modules.

## Linux Device Drivers

When performing a port, a task that needs to be performed no matter how portable the operating system, is to write drivers for all unsupported hardware. Linux

Figure 2.15: Operating system driver interface illustration.

provides a standard interface for most domains of hardware devices.

It is not required for a driver to implement all of the functions in the interface. What functions needs to be implemented is determined by the configuration of the kernel. What drivers should be compiled and included in the kernel is also set in the kernel configuration. To choose which drivers that should be used during execution, and how these should be configured, Linux provides a functionality called *Linux Device Tree*.

## Linux Device Tree

The Linux Device Tree (LDT) is a hardware description format used in the Linux kernel. The introduction of the LDT simplified the porting process. It also made it easier to build kernel binaries which were compatible with a set of hardware platforms instead of only one.

The LDT describes which hardware components are included in a specific architecture. The LDT information is separated from the kernel, so it is possible to modify this information without having to recompile the kernel. The only time one would have to recompile the kernel is to add support for new hardware.

The LDT is given to the kernel by the bootloader. As the Linux kernel initializes, it parses the entry in the LDT that corresponds to the architecture type it has discovered. Once the LDT has been parsed, a set of compatibility flags and required device drivers has been found. These are mapped against the drivers contained within the kernel, and the drivers which matches are loaded and initialized.

## 2.5.4 Writing Software for Linux

The services provided by an operating system are made available by the system call interface. In the case of the Linux kernel, there exists 380 system calls. To

utilize these system calls, a *toolchain* that is compliant with the target Linux version is required. Briefly explained, a toolchain is a set of tools which is used when transforming source code to executable files. In cases where the target architecture, the architecture that will execute the program, differs from the host, the one on which the code is being written and compiled, a *cross compiler* is required as a part of the toolchain.

Once equipped with a toolchain that is compatible with the target Linux version, it is possible to compile code that utilizes the Linux system calls. In addition to containing the header definitions of the Linux system calls, the toolchain needs to generate code which is compatible with the Application Binary Interface (ABI) supported by the target Linux version.

ABI is the interface between the operating system and the applications at the machine code level. It specifies the binary format of applications, the procedure call standard, and how system calls are performed.

# 2.6 The uClinux Project

Several embedded computing systems lack a Memory Management Unit (MMU), and can only use physical addresses directly in their code. This has major implications for the programming model. The uClinux project provided support for MMU-less system in the Linux kernel.

The uClinux project provided a set of patch files which made the Linux kernel portable to MMU-less systems. The two projects existed in parallel for a few years before the uClinux project was merged into mainline Linux.

In addition to the patch files for the Linux kernel, the uClinux project also contained tools for adapting userland applications to work on MMU-less architectures. The uClinux project also contained a standard C library implementation, uClibc, which was built specifically for MMU-less Linux systems with limited memory resources.

# 2.7 GNU Operating System

GNU was launched in 1983 and set out to offer a completely free UNIX-compatible operating system. Many computer users today run a modified version of the GNU system without even realizing it. This is because what many users consider to be "Linux" is in fact the Linux kernel together with the free GNU system. By the time that Linux was released the GNU project had put together almost a complete operating system. What they still lacked was a UNIX-like kernel. When the Linux kernel was released, the GNU project was combined with the Linux kernel to build a complete operating system known as GNU/Linux. The GNU project is still working on an operating system kernel while the combined system GNU/Linux has achieved major success.

# 2.8 BusyBox

While GNU/Linux is a popular operating system for desktop computers Busy-Box/Linux is a good alternative for embedded systems. BusyBox combines tiny versions of the most common UNIX utilities into a single executable. The implementations of these utilities usually has less features than their GNU counterparts while still providing a very similar behavior. Since BusyBox targets embedded systems, it has been written with size-optimization and small memory footprint in mind. It is also customizable, and it is possible to configure which features should be included at compile time. BusyBox also support running on Linux without MMU support.

BusyBox provides both a shell and an entire execution environment, which enhances the Linux kernel with powerful user interaction that makes a system behave like a regular PC with the GNU/Linux terminal.

# 2.9 Toolchains

A toolchain is a set of software components used for building applications. A typical toolchain contains a compiler, a linker, binary utilities and an assembler. Libraries are often included to simplify the job of the software developers using the toolchain. The binary utilities contained within the toolchains provide helpful tools when working with binary files. With these tools, it is possible to transform high level language source code to executable files.

In the embedded world, the *target* architecture is often different from the *host* architecture. That is: the processor for which the application is written has a different architecture than the computer generating the executable application files. It is often necessary to build a toolchain specifically for a single system environment.

Building an entire toolchain can be a cumbersome process. There are often dependencies between the various components, restrictions as to what configurations they might have, and which versions that are compatible with each other. When building the toolchain, it is important that the components are configured such that they are compatible with each other, and with the ABI of the target system. There exists several build systems for simplifying the toolchain building process.

These build systems simplify the building and configuration process by providing a single configuration interface, and automating the build process. Most build systems also ensures that no dependencies are violated during the configuration of the toolchain. What these build systems provide varies, a brief description of some popular build systems is given below.

## Buildroot

In addition to being able to generate toolchains, Buildroot has the capability of building operating system images, bootloader images, root file systems and applications for the target architecture [8]. This is done using a set of build scripts and configurations for the GNU *make* utility. Buildroot does not have support for ARM architectures without an MMU [7].

## PTXdist

The most feature rich build system evaluated for this project is PTXdist. PTXdist largely supports the same features as Buildroot, and uses the same tools to achieve this. Compared to Buildroot, PTXdist provides a simpler interface, and has support for MMU-less ARM architectures. PTXdist also lets the user provide patch files to apply to the Linux kernel before compiling, which is often necessary in the embedded world.

## Crosstool NG

This is the simplest build system of the three evaluated. Crosstool NG only targets toolchain generation, and does not provide functionality for building Linux or bootloaders like Buildroot and PTXdist. It is simpler to use than both Buildroot and PTXdist. As with PTXdist, it supports MMU-less ARM architectures.

# 2.9.1 Standard C Library

In software development, a library is a collection of function implementations made available to the developer through a well defined interface. One of the most important C libraries is the *standard C library*. This library defines a set of functions expanding the basic C functionality. It contains functions that "... provide input and output, string handling, storage management, mathematical routines, and a variety of other services for C programs" [24].

Developing useful applications in C without using the standard C library could be difficult. For a C program to be able to utilize the functionality offered by the standard C library, the toolchain used when building the application must include an implementation of it. There exists several implementations of the standard C library.

The ANSI definition only specifies the standard C library interface and functionality, not its implementation. Depending on the hardware support on the target architecture, it might not be possible for a standard C library implementation to provide all functions specified in the standard C library interface. The features supported by a standard C library implementation can also depend on operating system support.

## Standard C Library on Bare Bones Platforms

The term "bare metal" refers to a platform which does not have an operating system. Standard C Library implementations for use with bare metal target architectures are implemented using only standard C. One example of a bare metal implementation of the standard C library is *newlib* [10].

## Standard C Library on Platforms with Operating Systems

Once a system is equipped with an operating system, the platforms interface towards any software executing on top of it will be enriched by the operating systems system calls. In the case of Linux, this means support for threads, processes, files, time, concurrency, kernel modules, devices and much more.

Standard C library implementations which utilizes system calls are tightly coupled with the operating system on which they execute, placing strict requirements to any toolchain that wishes to generate executable code.

An example of a standard C library implementation that can be connected to the Linux system calls is uClibc [14]. uClibc specializes in embedded platforms, and supports MMU-less Linux.

# 2.10 Multicore Operating Systems

Since the introduction of the multicore processors, operating systems have been adapted to fully utilize the processing power offered by a multicore architecture. Designing an operating system for a multicore architecture requires several design features not required for a single core operating system.

# 2.10.1 Symmetric Multiprocessing

The cores in the SHMAC architecture all support the same ISA and have shared memory. This makes it possible to use the SMP model. The SMP model places the operating system in shared memory, and allows for any core to run it [29]. Allowing all of the cores to access the operating system introduces synchronization problems. What is the result when two cores attempts to update the same variable simultaneously? This problem can be solved with inter core synchronization.

## 2.10.2 Locking Primitives

There are several ways to implement inter core synchronization, locking is a necessity for most of them. A lock protects an entity, and ensures that only one actor (core, computer or thread) can access this protected entity at a time. This entity could be anything from a piece of critical code, code which only one core can execute simultaneously, to an entire device, such as the hard drive. For this to be possible, it is important that the locking mechanism is *atomic*. This means that when an actor locks an entity, the system behaves as if it was an instantaneous operation. A lock such as the one described above, which can be either in locked or unlocked state, is known as a *mutex* [29].

Consider the situation in which several actors requires access to a locked entity. If they cannot get exclusive access, they will go to sleep, and try to get access again after some time. In a situation like this, it would be desirable to maintain a list of actors that want access to the locked entity, and wake them up explicitly once it's their turn. A single mutex is only capable of ensuring exclusive access, not maintaining a queue such as this. The solution is to introduce a counter which can be atomically read, incremented and decremented. A counter like this is known as a *semaphore* [29].

### 2.10.3 SMP in Linux

Linux provides multicore support through SMP. A problem with using locks as a synchronization mechanism is that the entities under protection of a single lock can not be simultaneously accessed once that lock is taken. Hence it is desirable that the entity which a lock protects is as small as possible, while still ensuring correct execution with multiple cores. As described in [17], it was not until Linux version 2.6 that the size of the entities protected by the SMP locks was reduced to a scalable level.

This chapter describes in detail the changes made to the ARMv2a compliant Amber core in order to make it ARMv4T compliant. The new core was named Rav - the Norwegian word for Amber.

# 3.1 Motivation

Upgrading the Amber core to support a more recent ISA would result in better support in software tools, simplifying the development process for SHMAC software. ARMv2a used a 26-bit program counter scheme, requiring special handling in any software package that was to support it. This was needed since the architecture had a 32-bit ALU and a 32-bit PC register of which only 24 bits is the program counter. Given that only a handful of computers actually used ARMv2a ISA, it becomes clear that it is unattractive to add support for this ISA in modern software projects.

ARMv3 was the first ARM ISA to move away from the 26-bit PC scheme, resulting in increased support by software tools. However, the AAPCS is not supported by ARMv3.

To make Rav compatible with the AAPCS, the target ISA was chosen to be ARMv4T without Thumb support.

# 3.2 Execution Stage Schematic