# Postings List Compression and Decompression on Mobile Devices

Lars Martin S Pedersen

Master of Science in Computer ScienceSubmission date:December 2013Supervisor:Anne Cathrine Elster, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

# **Problem Description**

Mobile devices such as iPads or iPhones have a relatively little amount of RAM, but a comparably powerful CPU and increasing amounts of low-latency flash memory storage (128 GiB on the last generation iPad). Increased computational power and storage, combined with progressively more energy efficient devices, allows one to pursuit new areas of research including exploiting available hardware in unique ways.

The Trondheim-based company "Atbrox" are involved with an EU project focusing on search on mobile devices. An important component of search is the representation of the inverted index, and within, the per term postings list – a compressed list of URIs, where each URI represents a document containing the search term. Compression and decompression of the posting list can be handled in a number of different ways.

This thesis will focus on implementation, tuning (e.g. chunk size) and benchmarking of Variable byte encoding, a simple but efficient way to store the posting list. A survey of additional algorithms such as Elias gamma coding will also be included.

The work carried out in this project should provide insight to the performance of reading and writing from an SSD on a mobile device, streaming data and random access, and the balance between SSD and CPU utilization.

This work will be implemented in Objective-C, utilizing acceleration frameworks provided on the iOS platform.

## Abstract

Recent years has seen a tremendous increase in both the performance of handheld devices and the use cases they are required to fullfil. Indeed, operations previously reserved for handling on personal computers have begun being executed on smart phones and tablets instead. This revolutionary development allows one to exploit handheld device hardware in novel applications.

Trondheim-based start-up "Atbrox" is engaged in an EU project where Atbrox' focus is search on mobile devices. An important component of search is the inverted index, and within, the per term postings list – an encoded list of Unified Resource Identifiers (URI). Decoding of a postings list must be fast in order to not comprimise the user experience, but is also required to hold a small storage footprint. As the first to our knowledge, this thesis attempts to identify the properties of postings list encoding and decoding on handheld devices.

*Variable-byte coding, Group Varint coding,* and *Elias*  $\gamma$  *coding* are implemented in Objective-C. Performance is surveyed by benchmarking three devices out of Apple: A 5th generation iPod, a 4th generation iPad, and an iPad Air. Executions are run from disk-to-disk, *i.e.* by reading a block of data, applying either encoding or decoding, and writing the result to permanent storage. Block sizes are varied. In addition, multithreading is applied during both encoding and decoding and compared to serial executions in an attempt to identify the properties under which each coding scheme performs best.

This thesis provides valueable insight to the properties of coding schemes on handheld devices. Among its findings is the varying degree of performance and compression ratio between coding schemes: Group Varint proves to outperform the two others in terms of speed, however, is lacking in terms of compression. Elias  $\gamma$  code provides the best compression ratio, but is the slowest in both encoding and decoding. Results also prove a strong correspondance between block size and performance, although a point of saturation is reached at 512 KiB. Additionally, block sizes below 512 KiB display an inability to take advantage of multithreading.

# Sammendrag

De senere årende har sett en rivende utvikling innen ytelsen i håndholdte enheter og deres bruksområder. Gjøremål tidligere reservert for PC har blitt flyttet over til smarttelefoner og nettbrett. Denne revolusjonerende utviklingen tillater utnyttelse av tilgjengelig maskinvare på nye, spennende måter.

Det Trondheims-baserte selskapet "Atbrox" er engasjert i et EU-prosjekt, der Atbrox fokuserer på søk på mobile enheter. En viktig komponent i søk er den inverterte indeksen, med tilhørende postings-liste – en komprimert liste av Unified Resource Identifier-er (URI). Dekomprimering av postings-listen må være rask for ikke å forkludre brukerfølelsen, men samtidig tilordne seg lite lagringsplass. Til vår kjennskap er denne masteroppgaven det første forsøket på å kartlegge en postingslistes egenskaper på mobile enheter.

*Variable-byte-*, *Group Varint-* og *Elias*  $\gamma$ -komprimering er implementert i Objective-C. Ytelsen er kartlagt ved å benytte følgende enheter fra Apple: En femtegenerasjons iPod Touch, en fjerdegenerasjons iPad og en iPad Air. Kjøringer er gjort ved å lese en datablokk, anvende komprimering eller dekomprimering på datablokken og skrive resultatet til disk. Blokkstørrelser varieres mellom kjøringer. Flere tråder er benyttet under både komprimering og dekomprimering og sammenlignet med serielle kjøringer.

Masteroppgaven gir verdifull kunnskap om egenskapene ved de nevnte komprimeringsmetodene på håndholdte enheter. Blant funnene er variasjonen i ytelse og komprimeringsgrad metodene i mellom. Group Varint gir best ytelse sett i forhold til hastighet, men betaler med dårligst komprimeringsgrad, mens Elias  $\gamma$  har egenskaper invertert av disse. Resultatene viser også en sterk sammenheng mellom hastighet og blokkstørrelse. Et metningspunkt oppstår dog ved 512 KiB. I tillegg virker applikering av flere tråder mot sin hensikt for blokkstørrelser under 512 KiB.

# Contents

| Pr  | oblen   | n Description                  | iii  |

|-----|---------|--------------------------------|------|

| Ab  | strac   | t                              | v    |

| Sa  | mme     | ndrag                          | vii  |

| Со  | nten    | is                             | ix   |

| Lis | st of F | igures                         | xi   |

| Lis | st of T | ables                          | xiii |

| 1   | Intr    | oduction                       | 1    |

|     | 1.1     | Project Context                | 2    |

|     | 1.2     | Project Contributions          | 2    |

|     | 1.3     | Thesis Outline                 | 2    |

| 2   | Han     | dheld Devices and Development  | 5    |

|     | 2.1     | Central Processing Unit        | 5    |

|     | 2.2     | Storage                        | 7    |

|     | 2.3     | Memory                         | 7    |

|     | 2.4     | Apple Devices                  | 8    |

|     | 2.5     | Mac OS X and iOS Development   | 11   |

| 3   | Mul     | ti-core and Parallel Computing | 17   |

|     | 3.1     | Parallel Programming           | 17   |

|     | 3.2     | Parallel Scaling               | 18   |

| 4   | Post    | ings Lists in Inverted Indexes | 23   |

#### CONTENTS

|    | 4.1    | Structure                                        | 23  |

|----|--------|--------------------------------------------------|-----|

|    | 4.2    | Compression and Decompression                    | 25  |

|    | 4.3    | Related Work                                     | 30  |

| 5  | Post   | ings List Coding on Mobile Devices               | 33  |

|    | 5.1    | Flash Memory Performance                         | 33  |

|    | 5.2    | Encode and Decode Performance                    | 37  |

|    | 5.3    | Benchmark Execution                              | 49  |

| 6  | Resu   | ılts and Discussion                              | 53  |

|    | 6.1    | Coding Scheme Properties                         | 53  |

|    | 6.2    | Flash Memory Performance                         | 55  |

|    | 6.3    | Performance Critical Applications in Objective-C | 66  |

|    | 6.4    | Variable-byte Coding Performance                 | 67  |

|    | 6.5    | Group Varint Code                                | 79  |

|    | 6.6    | Elias $\gamma$ Code                              | 87  |

|    | 6.7    | Summary                                          | 97  |

|    | 6.8    | Critique                                         | 98  |

| 7  | Con    | clusion and Future Work                          | 101 |

|    | 7.1    | Future Work                                      | 103 |

| Bi | bliogi | aphy                                             | 105 |

| A  | Bun    | dled Scripts and Applications                    | 113 |

| B  | Exec   | cuting SSDPerformanceMapping                     | 115 |

|    | B.1    | Preparations                                     | 115 |

| С  | Exec   | cuting PostingListApp                            | 117 |

|    | C.1    | Preparations                                     | 117 |

|    | C.2    | Caveats During Execution                         | 118 |

х

# **List of Figures**

| 5.1  | The User Interface of the Flash Memory benchmark app                     | 35 |

|------|--------------------------------------------------------------------------|----|

| 5.2  | The user interface of the encoding and decoding benchmark app            | 37 |

| 5.3  | The user is presented the results of an execution in the encoding and    |    |

|      | decoding benchmark app.                                                  | 38 |

| 5.4  | An illustration of the encoding/decoding pipeline                        | 40 |

|      |                                                                          |    |

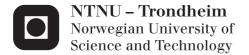

| 6.1  | Results of flash memory benchmark on a 5th generation iPod Touch         | 56 |

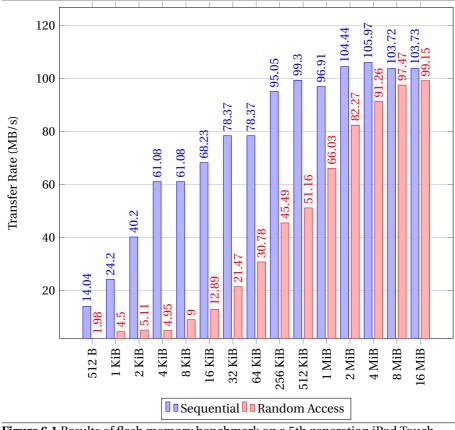

| 6.2  | Results of flash memory benchmark on a 5th generation iPod Touch         | 57 |

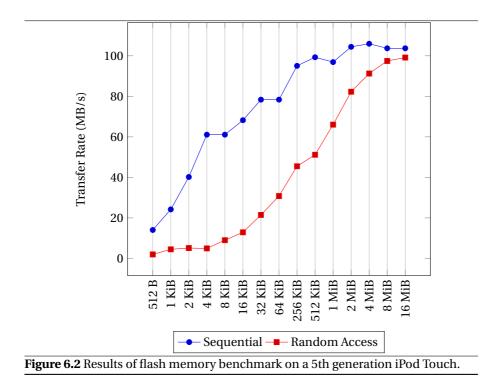

| 6.3  | Results of flash memory benchmark on a 4th generation iPad               | 59 |

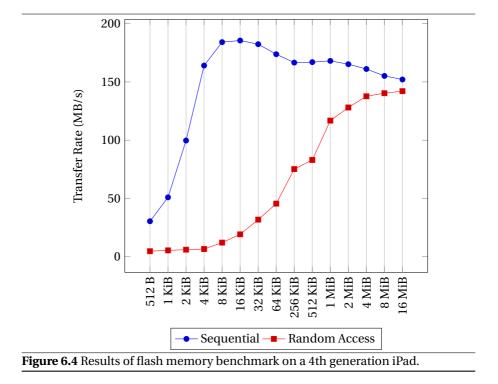

| 6.4  | Results of flash memory benchmark on a 4th generation iPad               | 60 |

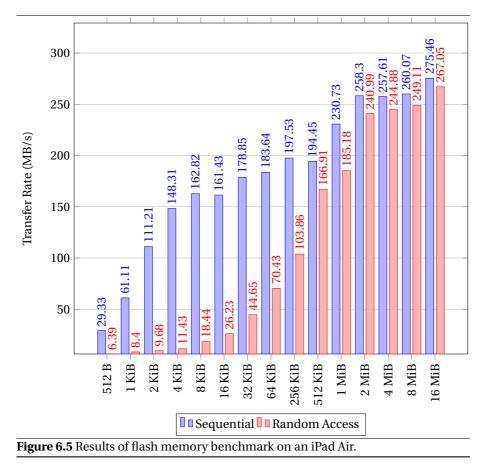

| 6.5  | Results of flash memory benchmark on an iPad Air.                        | 61 |

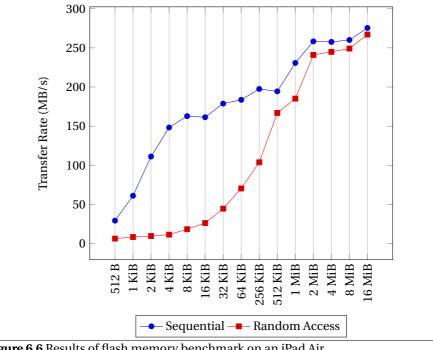

| 6.6  | Results of flash memory benchmark on an iPad Air.                        | 62 |

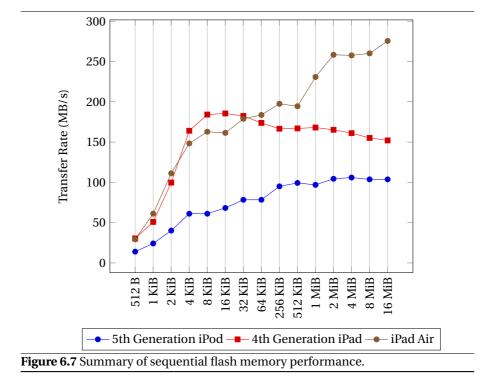

| 6.7  | Summary of sequential flash memory performance                           | 64 |

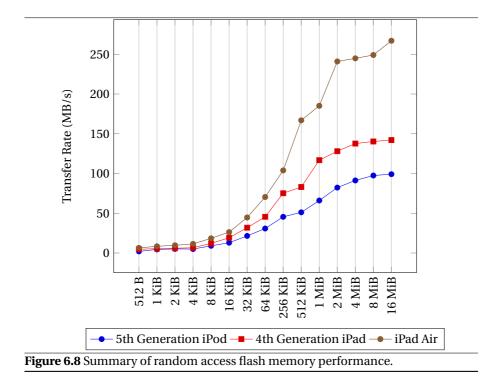

| 6.8  | Summary of random access flash memory performance                        | 65 |

| 6.9  | Disk-to-disk Variable-byte decoding before and after Objective-C opti-   |    |

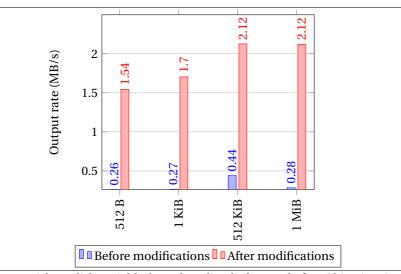

|      | mizations                                                                | 66 |

| 6.10 | Disk-to-disk Variable-byte encoding for configurations of single thread, |    |

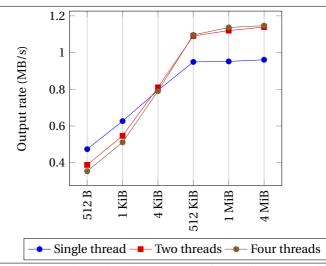

|      | two threads, and four threads on a 5th generation iPod                   | 68 |

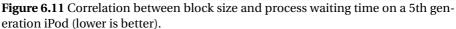

| 6.11 | Correlation between block size and process waiting time on a 5th gen-    |    |

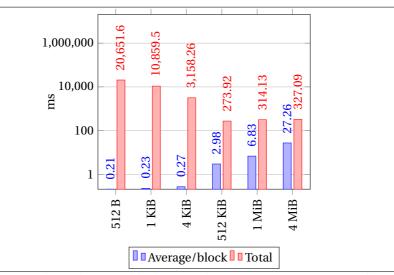

|      | eration iPod (lower is better).                                          | 69 |

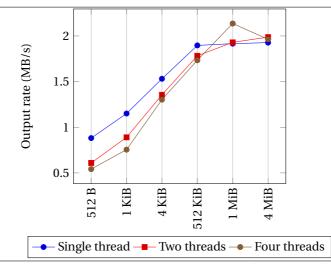

| 6.12 | Disk-to-disk Variable-byte encoding for configurations of single thread, |    |

|      | two threads, and four threads on a 4th generation iPad.                  | 70 |

| 6.13 | Disk-to-disk Variable-byte encoding for configurations of single thread, |    |

|      | two threads, and four threads on an iPad Air.                            | 71 |

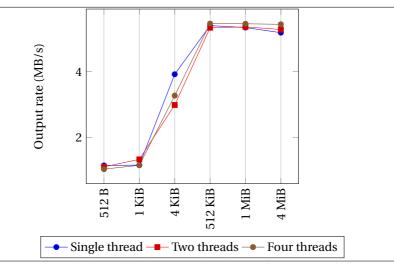

| 6.14 | Variable-byte encoding performance of the three devices tested.          | 73 |

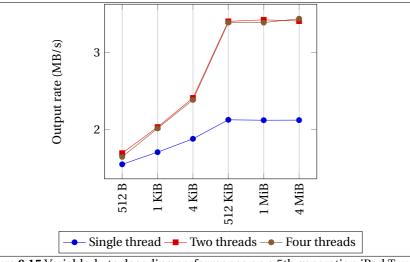

|      | Variable-byte decoding performance on a 5th generation iPod Touch.       | 74 |

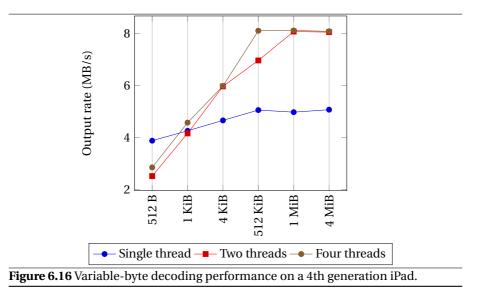

|      | Variable-byte decoding performance on a 4th generation iPad              | 76 |

| 5.15 |                                                                          |    |

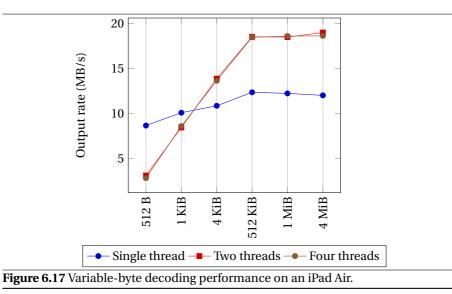

| 6.17 | Variable-byte decoding performance on an iPad Air                           | 77 |

|------|-----------------------------------------------------------------------------|----|

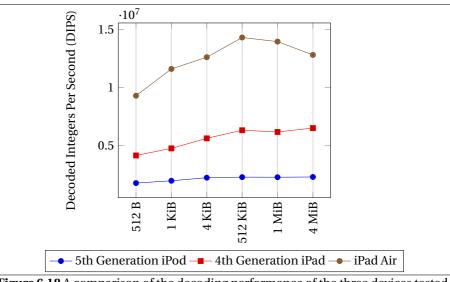

| 6.18 | A comparison of the decoding performance of the three devices tested.       | 78 |

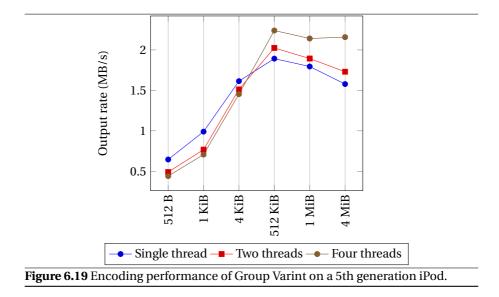

| 6.19 | Encoding performance of Group Varint on a 5th generation iPod               | 80 |

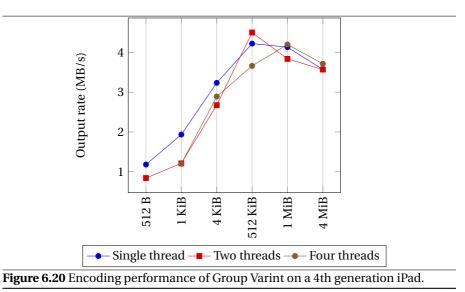

| 6.20 | Encoding performance of Group Varint on a 4th generation iPad               | 81 |

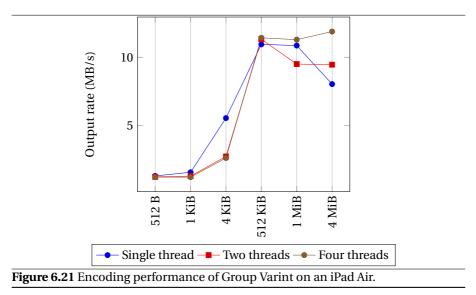

| 6.21 | Encoding performance of Group Varint on an iPad Air.                        | 82 |

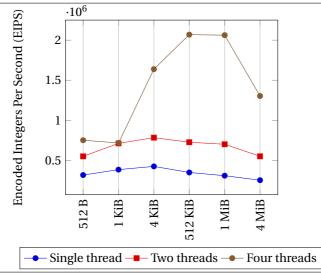

| 6.22 | Comparison of Group Varint encoding performance on the devices tested.      | 83 |

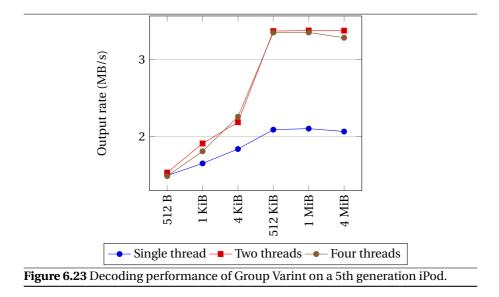

| 6.23 | Decoding performance of Group Varint on a 5th generation iPod               | 84 |

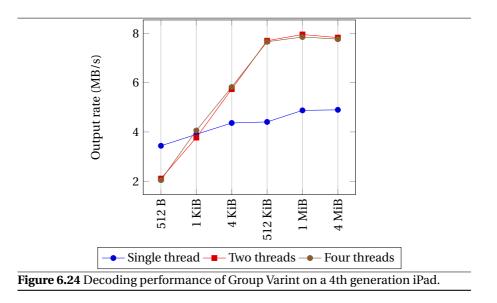

|      | Decoding performance of Group Varint on a 4th generation iPad               | 85 |

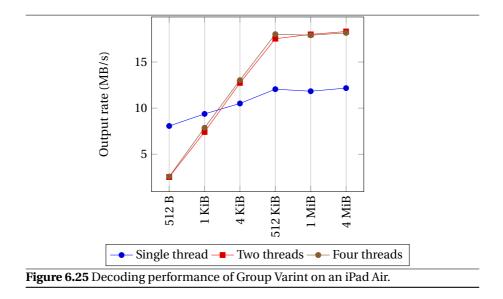

|      | Decoding performance of Group Varint on an iPad Air.                        | 86 |

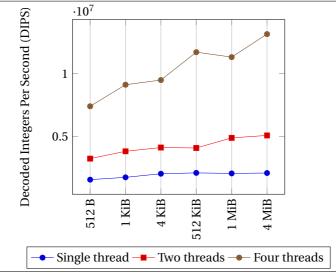

|      | Comparison of Group Varint decoding performance on the devices tested.      | 87 |

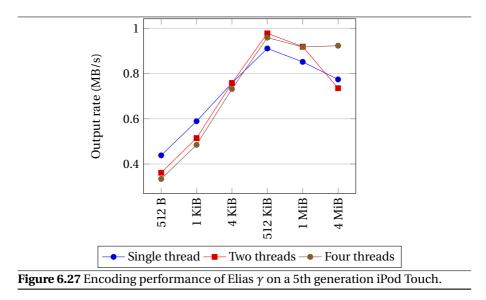

|      | Encoding performance of Elias $\gamma$ on a 5th generation iPod Touch       | 88 |

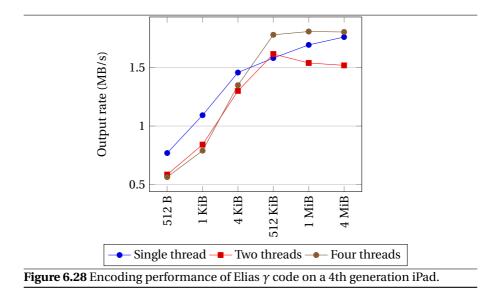

|      | Encoding performance of Elias $\gamma$ code on a 4th generation iPad        | 90 |

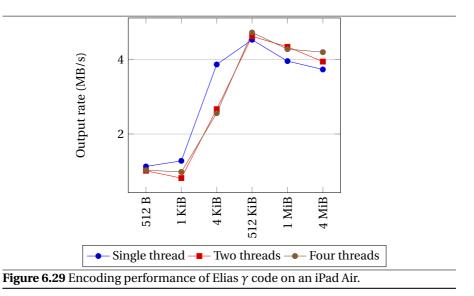

| 6.29 | Encoding performance of Elias $\gamma$ code on an iPad Air                  | 91 |

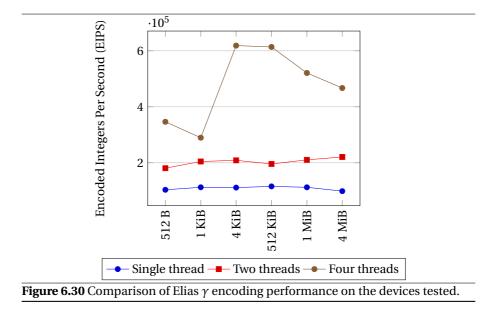

| 6.30 | Comparison of Elias $\gamma$ encoding performance on the devices tested     | 92 |

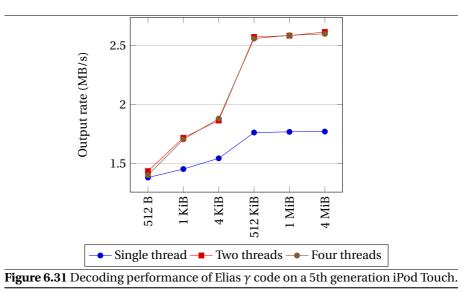

| 6.31 | Decoding performance of Elias $\gamma$ code on a 5th generation iPod Touch. | 93 |

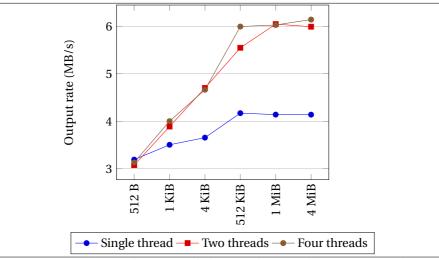

| 6.32 | Decoding performance of Elias $\gamma$ code on a 4th generation iPad        | 94 |

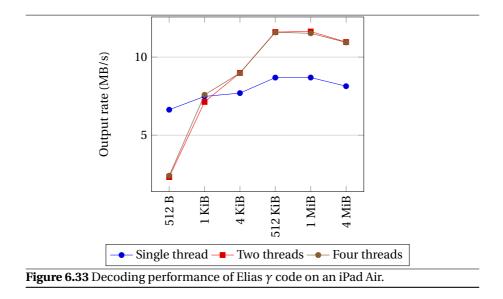

|      | Decoding performance of Elias $\gamma$ code on an iPad Air                  | 96 |

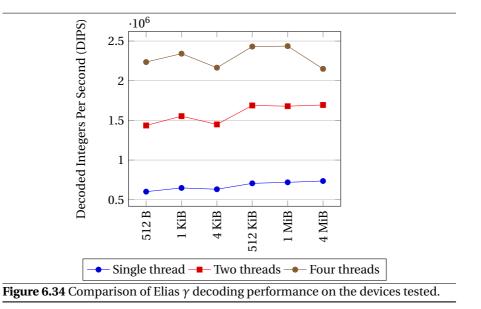

| 6.34 | Comparison of Elias $\gamma$ decoding performance on the devices tested     | 97 |

|      |                                                                             |    |

xii

# List of Tables

| 2.1 | Core specifications of common ARM processors.                            | 6  |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | Specifications of iPod Touch devices.                                    | 8  |

| 2.3 | Specifications of iPhone devices.                                        | 9  |

| 2.4 | Specifications of iPad devices.                                          | 9  |

| 2.5 | Properties of the different generations of A-series System on Chips      | 10 |

| 4.1 | Example of Variable-byte coded integers. The continuation bit is high-   |    |

|     | lighted in bold.                                                         | 27 |

| 4.2 | Example of Elias $\gamma$ encoded integers                               | 29 |

| 5.1 | Concrete specifications of the devices employed during benchmarking.     | 49 |

| 6.1 | Comparison of the time spent encoding the test data set                  | 54 |

| 6.2 | Comparison of the time spent decoding the test data set                  | 54 |

| 6.3 | Comparison of compression ratio on the test data set                     | 54 |

| 6.4 | Comparison of the time spent decoding the test data set without prior    |    |

|     | delta encoding.                                                          | 55 |

| 6.5 | Detailed comparison of a single threaded Variable-byte encoding and      |    |

|     | dual threaded Variable-byte encoding on a 5th generation iPod            | 68 |

| 6.6 | Detailed comparison of a single threaded Variable-byte encoding and      |    |

|     | dual threaded Variable-byte encoding on a 4th generation iPad 4          | 70 |

| 6.7 | Detailed comparison of a single threaded Variable-byte encoding run      |    |

|     | and a dual threaded Variable-byte encoding run on an iPad Air.           | 72 |

| 6.8 | Correlation between block size and process wait time on the three tested |    |

|     | devices (lower is better).                                               | 72 |

| 6.9 | Detailed comparison of a single threaded Variable-byte decoding run      |    |

|     | and a dual threaded Variable-byte decoding run on a 4th generation       |    |

|     | iPad 4                                                                   | 76 |

| 6.10 | Detailed statistics of an execution with two threads and block sizes of         |    |

|------|---------------------------------------------------------------------------------|----|

|      | 512 KiB, 1 MiB, and 4 MiB                                                       | 77 |

| 6.11 | Detailed statistics of a single threaded and dual threaded execution of         |    |

|      | Group Varint encoding on a 4th generation iPad 4, with 1 MiB block size.        | 81 |

| 6.12 | Detailed statistics of an execution on a 5th generation iPod with two           |    |

|      | threads and block sizes of 512 KiB, 1 MiB, and 4 MiB.                           | 89 |

| 6.13 | Detailed statistics of a serial execution on an iPad Air with block sizes of    |    |

|      | 512 B, 1 KiB, and 4 KiB                                                         | 91 |

| 6.14 | Detailed comparison of a single threaded Elias $\gamma$ decoding and a four     |    |

|      | threaded Elias $\gamma$ decoding with a block size of 4 MiB on a 4th generation |    |

|      | iPad                                                                            | 95 |

|      |                                                                                 |    |

xiv

### **Chapter 1**

# Introduction

Recent years has seen a tremendous increase in both the performance of handheld devices and the use cases they are required to fullfil. Indeed, operations previously reserved for handling on personal computers have begun being executed on smart phones and tablets instead. This revolutionary development allows one to exploit handheld device hardware in novel applications. In addition, while handheld devices have become increasingly faster in terms of computation, they have also received storage space on par with Solid State Drive (SSD) based notebooks. The recent iPad Mini and iPad Air out of Apple each hold storage capacities of 128 GiB. With flash memory as the storage technology, such devices promise high Input/ Output (I/O) performance.

Trondheim-based technology start-up "Atbrox" specialize in search technologies and novel applications of search. They are currently engaged in an on-going EU project where Atbrox' focus is on search on mobile devices. An important component of search is the inverted index, and within, the per term postings list – an encoded list of Unified Resource Identifiers (URI), each identifying a document in the document storage system. Decoding of a postings list must be fast in order to not comprimise the user experience, but is also required to hold a small storage footprint as the device storage space is shared with numerous other applications.

This thesis is motivated by recent hardware developments in the handheld device market, with a major potential for utilizing the available performance in unique ways. Three different coding schemes commonly used in encoding and decoding postings lists will presented and implemented: *Variable-byte coding, Group Varint coding,* and *Elias*  $\gamma$  *coding.* Each coding will be applied using a 5th generation iPod, a 4th generation iPad, and an iPad Air, with the performance of each being

recorded. In addition, tests with a varying block size will be conducted, and multithreading will be attempted in order to investigate the potential for parallel encoding and decoding.

#### 1.1 Project Context

This master's thesis is the end product of a five year Master of Science (M.Sc.) education in Computer Science conducted at the Norwegian University of Science and Technology (NTNU). It is one of several projects organized by the High Performance Computing (HPC) group at the Department of Computer and Information Science (IDI) [16]. Further, the project is under advisement from Dr. Anne C. Elster from NTNU<sup>1</sup>, and Dr. Amund Tveit on behalf of atbrox<sup>2</sup>.

#### 1.2 Project Contributions

While novel ways of coding or structuring postings lists are not part in the this projects contributions, it provides valuable insight to the behaviour of coding schemes on mobile platforms, the performance, and optimal ways of use. In addition, problems related to blocked reading of data to encode or encoded data are assessed and handled. These are situations that have not been found described in other litterature. Implicitly, the relative performance between devices is also measured, both in terms of CPU performance and disk performance.

#### 1.3 Thesis Outline

The remainder of this thesis is structured as follows:

- **Chapter 2:** Contains an introduction to the current handheld device market, as well as a more thorough presentation of Apple *i*-series of devices and the hardware found within. In addition, a quick walkthrough of developing on the iOS platform will be given.

- **Chapter 3:** Gives a review of parallel concepts such as multi-core, parallel data models, and theoretical models of parallelization.

<sup>&</sup>lt;sup>1</sup>http://www.idi.ntnu.no/~elster/

<sup>&</sup>lt;sup>2</sup>http://www.atbrox.com

#### 1.3. THESIS OUTLINE

- **Chapter 4:** Presents the concept of a postings list in general, how they are commonly organized, as well as encoding and decoding methods relevant to postings lists. The chapter will end with a review of work related to this thesis.

- **Chapter 5:** Discloses the implementation details of the work performed, with information on the work flow of created applications and the processing of data from disk into encoded or decoded form. Additionally, the internals of implemented coding schemes are presented. Towards the end, a description on how benchmarks were executed is given.

- **Chapter 6:** Begins with an overview of the performance and compression ratio of implemented coding schemes. At the same time, a comparison with generalized compression methods is made. Following, results of the flash memory reading benchmarks are presented. The remainder of the chapter is dedicated to presenting and discussing results found testing each coding scheme under various parameters on the benchmarked devices. In the end, results are summarized and given a critical review.

- **Chapter 7:** Contains a recap of the findings in the thesis, an assessment of these findings, and conclusions that have been made. Suggestions for future work is presented at the end.

### **Chapter 2**

# Handheld Devices and Development

This chapter will introduce the reader to the handheld device market, and development on such devices. First off, common hardware configurations and their properties are presented. Further, Apple's *i*-series, *i.e.* the iPod Touch, iPhone, and iPads, are given a more thorough introduction. Due to Atbrox' involvement in iOS, important contributors and large hardware manufacturers such as Samsung, HTC, and LG, have not been covered in this thesis.

Towards the end, a walkthrough of development on iOS will be given, introducing the Objective-C programming language and important programming frameworks.

#### 2.1 Central Processing Unit

While limitations in power consumption, generation of heat and physical die space are all factors hampering the performance of a Central Processing Unit (CPU) running on a desktop computer, compromises made on mobile platforms are more rigorous. Consumers demand high performance coupled with maximized battery life. In addition, the tight body of mobile devices force manufactures to shrink the CPU's die and forego active cooling solutions such as fans. Indeed, even passive cooling solutions must be trimmed to fit within the shell of a handheld device. An increased awareness of battery life, the absense of active cooling and less real estate for the CPU have forced a new market of mobile CPU manufacturing with roots in the embedded market.

#### 2.1.1 ARM Architecture

ARM's embedded past and early initiative with low-powered Graphics Processing Units (GPUs) have made them a dominant entity in the handheld chip market. Their list of Intellectual Property (IP) licensee's include manufacturers such as Apple, Qualcomm, Samsung and others [10].

The architecture has been designed to be small and simple, allowing for a low power consumption. In essence, it follows the design of a Reduced Instruction Set Computer (RISC), incorporating several typical RISC features such as a *load/store*-centric architecture and a large uniform register file. Coupled with additional enhancements to the traditional RISC architecture, particularly towards the use of the Arithmetic Logic Unit (ALU), ARM processors achieve a good balance between performance, power consumption and die size [50]. ARM's first 64 bit processor was introduced in 2011.

ARM has been present in the handheld market since the early 1990s, first introduced with the Apple Newton [23]. Since then, the company has become a dominant actor within the handheld chip market. In 2006, research estimated an ARM designed core was present in 98 % of all mobile phones [40]. Table 2.1 list common ARM processors and their features found in current mobile phones and tablets [7– 9].

| 1                |                 | 1                       |                         |

|------------------|-----------------|-------------------------|-------------------------|

|                  | Cortex-A8       | Cortex-A9               | Cortex-A15              |

| Clock Frequency: | 600 MHz – 1 GHz | 800 MHz – 2 GHz         | 1.0 GHz - 2.5 GHz       |

| # Cores:         | 1               | 1 - 4                   | 1 - 4                   |

| L1 Cache (I/D):  | 32 KiB /32 KiB  | 32 KiB /32 KiB per core | 32 KiB /32 KiB per core |

| L2 Cache:        | -               | 128 KiB – 8 MiB         | 128 KiB – 8 MiB         |

| 64 bit:          | -               | -                       | -                       |

| SIMD Extensions: | NEON            | NEON                    | NEON                    |

Table 2.1 Core specifications of common ARM processors.

#### 2.1.2 IA-32/Intel x86-64 Architecture

Intel's IA–32 and x86–64 architectures are architectures based on and backwards compatible with Intel's x86 architecture. In comparison to the previously mentioned ARM architecture, x86 is a Complex Instruction Set Computer (CISC) architecture. A characteristic of CISC is the inherit complexity of instructions, enabling them to perform several operations per instruction, for instance loading a value from memory and dispatching it to the ALU. Later generations of x86 introduced

#### 2.2. STORAGE

a decoding step and a RISC-like core in the processor. X86/CISC instructions are decoded into *micro-operations* and executed in a RISC-like manner [33, 57].

In handheld devices, Intel's *Atom* series of processors has been the most prevalent x86-based CPU. Intel Atom is a family of Ultra-Low-Voltage (ULV) processors, created to establish Intel in the embedded and handheld device market [32, 34]. As with ARM, Intel Atom sports a notably lower clock frequency compared to processors designed for desktop and server use. In addition, the physical size of the chip is significantly less than its desktop counterparts.

#### 2.2 Storage

In order to keep device size at a minimum, but still provide sufficient storage, handheld devices resort to the use of flash memory instead of traditional, mechanical hard drives.

#### 2.2.1 Flash Memory

Flash memory is a type of non-volatile electronic storage medium, commonly found within hardware devices such as mobile phones, tablets and Solid State Drives (SSD). The technology promises significant performance gains, while being more dense and power efficient. However, flash memory does not come without idiosyncrasies. It is known to be less durable, as well as having data integrity issues [20]. Indeed, the current most common type of flash memory, Negated AND (NAND) memory, has been predicted a bleak future since both the increase in performance and reliability have stagnated as the density has risen [21]. Despite mentioned idiosyncrasies, flash memory's low power consumption and performance compared to that of mechanical hard drives makes it a favourable candidate when choosing the storage medium for a device. Being both electric and non-volatile, flash memory combines the properties of technology found in use as main memory, *i.e.* high random access performance, without data loss when the memory is unpowered. In addition, some issues, such as wear-leveling and integrity, may be countered through the use of an intelligent flash controller or a flash translation layer.

#### 2.3 Memory

With the advent of more and more mobile devices, with a higher demand for prolonged battery life as well as less device real estate, a new type of Random Access Memory (RAM) was introduced: Low Power Double Data Rate RAM (LPDDR) or Mobile DRAM (mDDR). LPDDR was first standardized by JEDEC<sup>1</sup> in 2007, then as a minor modification to the existing DDR standard, specifying lower operating voltage, a new deep power down mode as well as a smaller physical size [38]. Devices such as the first generation of iPad and Samsung Galaxy Tab adopted the new type of memory [19].

As new devices have been released, so has the LPDDR standard. JEDEC announced LPDDR2 in 2009, further lowering the operating voltage in addition to representing a more dramatic change from conventional DDR [36, 53]. LPDDR2 was quickly adopted by the industry, and is represented in devices such as the iPhone 5 and Samsung Galaxy S3 [30, 51]. LPDDR3 was announced in May 2012, promising a higher data rate, improved bandwidth and power efficiency, as well as higher memory densities than its predecessor [37, 54].

#### 2.4 Apple Devices

Apple released their first modern, handheld *i*-device in 2007 with the introduction of the iPhone<sup>2</sup> [25]. Since inception, the devices have had a strong emphasis on preserving battery life. Indeed, an emphasis to the extent that processors within *i*-devices have been underclocked<sup>3</sup>. Each generation of devices from Apple have possessed the previously mentioned hardware characteristics: An ARM based CPU, flash drive for storage and a variant of Low Power DDR RAM. Table 2.2, Table 2.3, and Table 2.4 lists the different generations, as well as key hardware components.

|                      | System on Chip            | Memory  | Storage         |

|----------------------|---------------------------|---------|-----------------|

| 1st gen. iPod Touch: | Samsung S5L8900 (412 MHz) | 128 MiB | 8 GiB – 32 GiB  |

| 2nd gen. iPod Touch: | Samsung S5L8720 (533 MHz) | 128 MiB | 8 GiB – 32 GiB  |

| 3rd gen. iPod Touch: | Samsung S5L8920 (600 MHz) | 128 MiB | 32 GiB – 64 GiB |

| 4th gen. iPod Touch: | Apple A4 (800 MHz)        | 256 MiB | 8 GiB – 64 GiB  |

| 5th gen. iPod Touch: | Apple A5 (1 GHz)          | 512 MiB | 16 GiB – 64 GiB |

<sup>&</sup>lt;sup>1</sup>JEDEC is a standardization body and independant semiconductor trade organization. The DDR SDRAM standards are a product of JEDEC. More information is available at http://www.jedec.org.

<sup>&</sup>lt;sup>2</sup>Only generations of iPod running iOS are considered in this project, that is, the iPod Touch-series of devices.

<sup>&</sup>lt;sup>3</sup>Running a CPU on a clock frequency lower than specified. As opposed to overclocking, where the clock frequency is increased beyond specification., iphone2008underclocked, iphone2009underclocked

|             | System on Chip            | Memory         | Storage         |

|-------------|---------------------------|----------------|-----------------|

| iPhone:     | Samsung S5L8900 (412 MHz) | 128 MiB LPDDR  | 4 GiB – 16 GiB  |

| Phone 3G:   | Samsung S5L8900 (412 MHz) | 128 MiB LPDDR  | 8 GiB – 16 GiB  |

| iPhone 3GS: | Samsung S5PC100 (600 MHz) | 256 MiB LPDDR  | 8 GiB – 32 GiB  |

| iPhone 4:   | Apple A4 (800 MHz)        | 512 MiB LPDDR2 | 8 GiB – 32 GiB  |

| iPhone 4s:  | Apple A5 (800 MHz)        | 512 MiB LPDDR2 | 8 GiB – 64 GiB  |

| iPhone 5:   | Apple A6 (1.3 GHz)        | 1 GiB LPDDR2   | 16 GiB – 64 GiB |

| iPhone 5C:  | Apple A6 (1.3 GHz)        | 1 GiB LPDDR2   | 16 GiB – 32 GiB |

| iPhone 5S:  | Apple A7 (1.3 GHz)        | 1 GiB LPDDR3   | 16 GiB – 64 GiB |

.... . . . • • C 1 D 1 .

| Table 2.4 Specifications of i | iPad devices. |

|-------------------------------|---------------|

|-------------------------------|---------------|

| System on Chip      | Memory                                                                                                                     | Storage                                                                                                                                                                             |

|---------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Apple A4 (1 GHz)    | 256 MiB LPDDR                                                                                                              | 16 GiB – 64 GiB                                                                                                                                                                     |

| Apple A5 (1 GHz)    | 512 MiB LPDDR2                                                                                                             | 16 GiB – 64 GiB                                                                                                                                                                     |

| Apple A5X (1 GHz)   | 1 GiB LPDDR2                                                                                                               | 16 GiB – 64 GiB                                                                                                                                                                     |

| Apple A6X (1.4 GHz) | 1 GiB LPDDR2                                                                                                               | 16 GiB – 128 GiB                                                                                                                                                                    |

| Apple A5 (1 GHz)    | 512 MiB LPDDR2                                                                                                             | 16 GiB – 64 GiB                                                                                                                                                                     |

| Apple A7 (1.3 GHz)  | 1 GiB LPDDR3                                                                                                               | 16 GiB – 128 GiB                                                                                                                                                                    |

| Apple A7 (1.4 GHz)  | 1 GiB LPDDR3                                                                                                               | 16 GiB – 128 GiB                                                                                                                                                                    |

|                     | Apple A4 (1 GHz)<br>Apple A5 (1 GHz)<br>Apple A5X (1 GHz)<br>Apple A6X (1.4 GHz)<br>Apple A5 (1 GHz)<br>Apple A7 (1.3 GHz) | Apple A4 (1 GHz)256 MiB LPDDRApple A5 (1 GHz)512 MiB LPDDR2Apple A5X (1 GHz)1 GiB LPDDR2Apple A6X (1.4 GHz)1 GiB LPDDR2Apple A5 (1 GHz)512 MiB LPDDR2Apple A7 (1.3 GHz)1 GiB LPDDR3 |

An interesting observation to make is the close relationship between hardware configurations in generations of iPod and iPhone.

#### 2.4.1 Apple A-Series System on Chip

The A-series family of System on Chips (SoC) integrate one or several ARM-based CPU cores, an arbitrary GPU, cache memory and additional electronic equipment required for mobile computing functions. Its first official debute was in the release of Apple's *iPad*, then represented by the Apple A4. Apple themselves design the package, while manufacturing is out-sourced to external contractors such as Samsung [56]. A-series SoCs are found in nearly all electronic equipment produced by Apple; iPad, iPod Touch, iPhone as well as the Apple TV.

As mentioned, Apple A4 first introduced the series. Then followed the Apple A5 and A5X the consecutive year and lastly Apple A6 and Apple A6X. In 2013, Apple released its first 64 bit mobile SoC aptly named A7. Properties of each generation is summarized in Table 2.5 [41, 43-45, 56].

|            | Apple A4   | Apple A5  | Apple<br>A5X | Apple A6 | Apple<br>A6X | Apple A7   |

|------------|------------|-----------|--------------|----------|--------------|------------|

| Proces-    | ARM        | ARM       | ARM          | Apple    | Apple        | Apple      |

| sor:       | Cortex-A8  | Cortex-A9 | Cortex-A9    | Swift    | Swift        | Cyclone    |

| Clock Fre- | 800 MHz    | 800 MHz   | 1 GHz        | 1.3 GHz  | 1.4 GHz      | 1.3 GHz –  |

| quency:    | – 1 GHz    | – 1 GHz   |              |          |              | 1.4 GHz    |

| # Cores:   | 1          | 1 - 2     | 2            | 2        | 2            | 2          |

| L1 Cache   | 32 KiB /32 | 32 KiB    | 32 KiB       | 32 KiB   | 32 KiB       | 64 KiB /64 |

| (I/D):     | KiB        | /32 KiB   | /32 KiB      | /32 KiB  | /32 KiB      | KiB        |

| L2 Cache:  | 512 KiB    | 1 MiB     | 1 MiB        | 1 MiB    | 1 MiB        | 1 MiB      |

| 64 bit:    | -          | -         | -            | -        | -            | Yes        |

| GPU:       | PowerVR    | PowerVR   | PowerVR      | PowerVR  | PowerVR      | PowerVR    |

|            | SGX 535    | SGX543    | SGX543       | SGX543   | SGX554       | G6430      |

Table 2.5 Properties of the different generations of A-series System on Chips.

Apple recently made a move from making use of ARM designed cores, to cores designed by Apple themselves, *i.e.* the Apple Swift found in Apple's A6 and A6X and Apple Cyclone found in A7.

#### 2.4.2 Storage

The amount of available storage on devices made by Apple varies from generation to generation. From the first iPhone having options between 4 and 16 Gigabytes (GB), to the latest iPhone 5S having been made available with 16, 32 or 64 GB of storage. Common to all is the use of NAND flash Memory as the electronic storage medium. It is unknown whether Apple employ the use of an additional Input/ Output (I/O) controller to facilitate access to the flash memory or if the CPU has direct access. Several investigations into the internals of *i*-devices make no mention of a controller [27–29, 31]. Indeed, reverse engineering attempts show atleast earlier versions of iPhone make use of dynamic wear leveling implemented in software as a proprietary flash translation layer (FTL) [35]. However, in 2012 Apple acquired Anobit Technologies, Ltd, an Israeli flash memory controller manufacturer [52]. Articles commenting on the acquisition mention Anobit technology as already present in iPhones and iPads [17].

#### 2.5. MAC OS X AND IOS DEVELOPMENT

#### 2.4.3 Memory

Main memory in Apple's devices is not bundled alongside the CPU and GPU on the same SoC, but rather attached as a Package on Package (PoP). That is, RAM and SoC are stacked and unified through a standard routing interface. Apple makes use of one of the standards of Low Power DDR RAM (LPDDR), a physically smaller type of DDR RAM operating on lower than normal voltages. The original LPDDR was used up until the release of the second generation iPad (iPad 2) and iPhone 4, providing bandwidths up to 1600 Megabytes per second (MB/s) depending on memory clock rate and width of the memory bus. iPad 2, iPhone 4 and later generations of the two use LPDDR2, achieving theoretical bandwidths up to 12800 MB/s. In iPhone 5S, the Apple A7 is packaged with LPDDR3, further pushing the theoretical bandwidth limit.

#### 2.5 Mac OS X and iOS Development

The following sections will introduce the programming languages and tools available for development on Apple's platforms.

#### 2.5.1 Programming Languages

Three different, although related, programming languages are available when developing for Mac OS X and iOS: *C*, *C*++, and *Objective-C*, with the latter being the primary language of use.

#### **Objective-C**

Objective-C is the primary programming language of use when developing software for Mac OS X and iOS. It is a strict superset of the C programming language, defining several powerful extensions. Among these are Object-oriented capabilities by adopting Smalltalk-like messaging and a dynamic runtime [2, About Objective-C].

**Syntax** Being a thin layer on top of C, any Objective-C compiler is able to compile a C program. In addition, a developer is permitted to freely include C code in an Objective-C class. It follows Smalltalk's syntax for sending messages, *i.e.* calling an object's method or function. Syntax for associating variables with values, arithmetics, conditional constructs, and other non-object oriented behaviour follows the same convention as C.

**Classes and Objects** As with other object-oriented languages, objects in Objective-C are made to encapsulate and package related data. A class is a description of an object. It acts as a blueprint, defining properties and behaviour of objects that belong to this specific class. For instance, an array object may contain functionality for storing, expanding, and contracting data. However, one does not need to know the interals of such an object, as described in the class, only how one is expected to interact with the object and how the object will respond [2, Defining Classes].

Class inheritance is an important feature of an object-oriented design, and Objective-C is no exception. Although not required, almost all classes used in relation to Mac OS X or iOS inherit from NSObject. NSObject corresponds to Java's Object class or Python's object class. That is, a root class<sup>4</sup> with a basic interface to the runtime system, enabling child classes to behave as objects of their respective programming languages.

**Interface** An important focus in Objective-C is to define the behaviour of objects of a class, and hide implementation details. To facilitate such an architecture, classes are required to define public methods and properties in what is called an *in*terface. Listing 2.1 illustrate a bare class interface definition named MyPersonClass, inheriting methods and properties from NSObject.

Listing 2.1 An example of an Objective-C class interface definition.

```

#import <Foundation.h>

1

3

@interface MyPersonClass : NSObject

@end

```

In Objective-C, the properties of a class are public class instance variables. These are variables that should be easily referenced and require no additional source when accessed, other than setting or getting their value. For instance, consider if one was to extend the class created in Listing 2.1 to contain information to better describe a person. This could be achieved by creating properties to contain a person's name and birth date as demonstrated in Listing 2.2. Note the asterisk preceding the variable names. This is due to NSString and NSDate being Objective-C objects and the language's thin layer around C: objects must be represented by their pointers [2, Defining Classes].

2

4

5

<sup>&</sup>lt;sup>4</sup>A class which inherits from no other class and defines a common interface shared by all objects in the hierarchy below it.

```

Listing 2.2 Creating properties to contain information abouth a specific person.

```

```

1 #import <Foundation.h>

2

3 @interface MyPersonClass : NSObject

4

5 @property NSString *firstName;

6 @property NSString *lastName;

7 @property NSDate *birthDate;

8

9 @end

```

As mentioned earlier, objects primarily communicate with each other through messages. These messages are defined through method declarations. While the concept is similar to how one would assume C method declarations to behave, the syntax is quite different, as demonstrated in Listing 2.3a and Listing 2.3b. In Listing 2.3b, first and second are the variable names that must be referred to in the implementation of the method, while anotherParameter is a descriptive name of the parameter. It is important to note, however, that Objective-C does not support named parameters, as for instance Python does. Both the order of parameters and the descriptive name is part of the method declaration and must match when the method is called or is to be implemented. In other words, the declaration in Listing 2.3b is not the same as the one displayed in Listing 2.3c [2, Defining Classes]. In general, a method declaration in Objective-C follows the following pattern:

- (ReturnType)methodName:(FirstParameterType)firstParameter nextParameterDescription:(NextParameterType)nextParameter

The leading – (dash) creates an instance method. Replacing it with a + (plus) will create a class method.

**Implementation** With the properties and methods defined in an interface, the implementation of a class' behaviour is written inside an implementation directive. As illustrated in Listing 2.4, this is done by importing the header file containg the interface declaration and writing the implementation for each defined method in the interface. Here, the interface example from earlier has been extended with an additional method, secondsSinceBirthDate:(NSDate \*)date [2, Defining Classes].

Listing 2.3 Comparison of method definitions in C and Objective-C.

| 1<br>2 | <pre>void someMethod(int first, 1</pre>                                   | <pre>- (void)someMethod:(int)first anotherParameter:(int)second;</pre> |

|--------|---------------------------------------------------------------------------|------------------------------------------------------------------------|

|        | (a) Method definition in C.                                               | <b>(b)</b> Method definition in Objective-C.                           |

| 1<br>2 | <pre>- (void)someMethod:(int)first     secondParameter:(int)second;</pre> |                                                                        |

(c) A second method definition in Objective-C.

#### 2.5.2 Fundamental Frameworks and APIs

When developing with Objective-C for Mac OS X or iOS, there are a set of essential frameworks and Application Programming Interfaces (API). These are the Foundation framework and Cocoa and Cocoa Touch APIs.

#### Foundation

Foundation is a framework providing a base layer of primitive object classes and utility classes that are not covered by the Objective-C language. Among these are NSString, NSArray, NSDictionary and the previously referenced NSDate. Each of these are defined in separate header files. However, they can all be included by importing Foundation's primary header file, Foundation.h [5]:

#import <Foundation.h>

#### **Cocoa and Cocoa Touch**

Cocoa and Cocoa Touch are Apple's native object-oriented APIs for Mac OS X and iOS, respectively. Developers are encouraged to use Apple's Xcode Integrated Development Environment (IDE) when interfacing with Cocoa Touch, as the IDE tightly incorporates both APIs [3, 4].

Cocoa includes the previously introduced Foundation framework, in addition to the AppKit framework [3]. The latter includes classes for handling a program's User Interface (UI), as well as handling events when a user interacts with UI components. Cocoa Touch is based on Cocoa, with a an AppKit modified to suit iOS as well as additions for handling touch gestures and an animation framework [4].

```

Listing 2.4 Example of a defined interface and its implementation.

```

```

#import <Foundation.h>

1

2

@interface MyPersonClass : NSObject

3

4

@property NSString *firstName;

5

@property NSString *lastName;

6

@property NSDate *birthDate;

7

8

- (float)secondsSinceBirthDate:(NSDate *)date;

9

10

@end

11

```

(a) Interface for MyPersonClass.

```

#import "MyPersonClass.h"

1

2

3

@implementation MyPersonClass

4

- (float)secondsSinceBirthDate:(NSDate *)date {

5

float seconds = [date timeIntervalSinceDate:self.birthDate];

6

7

return seconds;

}

8

9

10

@end

```

(b) Implementation of MyPersonClass

Common to both is the use of the Model-View-Controller (MVC) development pattern for coupling user engaged events in the UI and corresponding data [3, 4].

### **Chapter 3**

# **Multi-core and Parallel Computing**

This chapter is a summary of the litterature studied at the beginning of the process leading up to this thesis. Within, the principles, technologies and hardware that define and set the bounds of the project is presented.

#### 3.1 Parallel Programming

This section will give a quick overview of the architectures and memory models of parallel programming.

#### 3.1.1 Architectural Definitions

Two different models are commonly used to define parallel architectures. The first uses the relationship between memory and compute units to describe its modes, while the other, often identified as Flynn's taxonomy, describe the relationship between instruction and data stream.

The former defines three different architectures:

**Shared Memory:** In shared memory, every compute unit shares the same unified memory location. This allows for relatively easy development and for fast communication between compute units. However, this architecture does generally not scale well because of race conditions. In addition, memory is often cached locally by compute units, which in turn raises a cache-coherency issue.

- **Distributed Memory:** Distributed memory describes an architecture where each compute unit has its own private memory. This makes computation on local data very fast. However, computation on external data enforces communication between compute units beforehand, which in turn results the need for some interconnect and message passing interface between each compute unit. Distributed memory eliminates race conditions.

- **Distributed Shared Memory:** In distributed shared memory, the memory is not shared among compute units, but it is addressed logically as it was shared. This means that the extra communication between compute units in distributed memory is abstracted away from the programmer.

Flynn's taxonomy defines four different models:

- **Single Instruction, Single Data (SISD):** A single instruction is executed which does not exploit any data parallelism, either in the instruction or in the data.

- **Single Instruction, Multiple Data (SIMD):** A single instruction which exploits multiple data streams. This is typical for graphics processing units (GPU).

- Multiple Instruction, Single Data (MISD): Multiple instructions operate on a single data stream. This architecture is fairly uncommon.

- **Multiple Instruction, Multiple Data (MIMD):** Multiple instructions simultaneously execute on multiple data streams. This architecture is typical for distributed systems, either organized as a shared memory system or a distributed memory system.

#### 3.2 Parallel Scaling

It is important to note that the speedup gained by exploiting the parallelism in a program is highly dependent on the properties of each individual program, *i.e.* the fraction of the program's execution which is parallelizable. This rather pessimistic assumption is stated in Amdahl's law [1], and has later been revised by Mark D. Hill and Micheal R. Marty [24].

Parallel speedup is defined as the quotient after dividing the sequential execution time of an algorithm,  $T_1$ , by the parallel execution time of the algorithm, executed with p processors,  $T_p$  [39]:

$$S_P = \frac{T_1}{T_p}$$

#### 3.2. PARALLEL SCALING

Further, Amdahl's law states that if 90% of your program is sequential and the remaining 10% is parallelizable, the minimum execution time can not be lower than the 90% spent in the sequential part of the program. In other words, if *P* is the proportion of the program that can be made parallel, and 1 - P) is the remaining serial proportion, the maximum speedup given *N* processors is given by the following equation [1]:

$$S(N) = \frac{1}{(1-P) + \frac{P}{N}}$$

John L. Gustafson and Edwin H. Barsis later reevaluated Amdahl's assertion in what has been known as "Gustafson's law" or "Gustafson-Barsis' law" [22]. Gustafson's law has a more optimistic take on parallel computing, stating that computations involving arbitrary large datasets can efficiently be parallelized. This has made Gustafson's statement a counter-part to Amdahl's law, which presents an upper bound for fixed size datasets. Gustafson's assumption was that software developers set the problem size based on the available hardware. Therefore, if more parallel hardware and powerful hardware is available, the problem size would increase. Inherently, as the problem size increases, the ratio of parallel-to-serial tasks also sees change. That is, the serial portion will become smaller in proportion to the total execution. Gustafson called his metric "scaled speedup" and defined it as such [22]:

$$S(P) = P - \alpha \times (1 - P)$$

Where *S* is the speedup, *P* is the number of processors and  $\alpha$  is the serial fraction of any parallel process.

With the advent of multi-core processors, Mark D. Hill and Michael R. Marty revised Amdahl's law in 2008, providing new insight to how multi-core processors should be designed in relation to Amdahl's law [24]. The authors deduced three equations for three different types of models:

#### 3.2.1 Symmetric Multi-core Chips

Every core on a chip has equal cost, *i.e.* exploit the same amount of Base Core Equivalents (BCE)<sup>1</sup>. For instance, a symmetric multi-core with a budget of n = 16 BCEs and r = 1 BCE per core would give a 16 core symmetric, multi-core chip. In general, the number of cores is decided by the quotient of  $\frac{n}{r}$ , *i.e.* the BCE budget and number of BCEs per core. In addition, Hill and Marty defined a parameter *per* f(r), which is equivalent to the performance of a core with r BCEs.

<sup>&</sup>lt;sup>1</sup>A generic unit of cost depending on context, *e.g.* power, design effort or money.

The symmetric multi-core architecture uses one core to execute the serial part, with performance perf(r), and applies all  $\frac{n}{r}$  cores to execute the parallel part. As a result, the speedup is given by the formulae:

$$S_{symmetric}(f, n, r) = \frac{1}{\frac{1-f}{perf(r)} + \frac{f \times r}{perf(r) \times n}}$$

#### 3.2.2 Asymmetric Multi-core Chips

The second architecture explored by Hill and Marty is that of the asymmetric multicore chip. Here, the relation between BCEs and cores is not linear. Instead, several BCEs are combined into one large, more powerful core, while the remainder is divided among a set of smaller, less powerful cores. For instance, an asymmetric multi-core chip could have a budget of n = 16 BCEs at its disposal. Of these, four could be combined into one large, single core, with 12 small cores with one BCE each. In general, an asymmetric chip can have 1 + n - r cores. The large core allocates *r* BCEs, while the remainder, n - r, is distributed to the rest of the cores.

In the asymmetric architecture, the serial part is executed on the powerful core, and every core executes the parallel part. The speedup is modelled by the equation:

$$S_{asymmetric}(f, n, r) = \frac{1}{\frac{1-f}{perf(r)} + \frac{f}{perf(r)+n-r}}$$

With the advent of General Purpose Programming on GPUs (GPGPU), this architecture has become increasingly more relevant lately. If one thinks of a Central Processing Unit (CPU) as the large core, performing the serial portion of the program, the GPU can be thought of as the set of smaller, less performant cores, executing the parallel portion of the program. The result is a heterogeneous architecture.

#### 3.2.3 Dynamic Multi-core Chips

The third and last architecture is that of dynamic multi-core chips. In this architecture, resources are dynamically allocated depending on where they are needed. When a program executes its serial fraction, all of the BCEs are combined into one large core. During the parallel execution of a program, the BCEs are distributed evenly among all cores, utilizing all base cores. This behaviour is modelled by:

$$S_{dynamic}(f, n, r) = \frac{1}{\frac{1-f}{perf(r)} + \frac{f}{n}}$$

#### 3.2. PARALLEL SCALING

For a more thorough explanation of the three architectures, and a modelled review of their performance, the reader is urged to investigate Hill and Marty's paper from 2008, "Amdahl's Law in the Multi-core Era" [24].

## **Chapter 4**

# **Postings Lists in Inverted Indexes**

This chapter will start with a description of the most common structure a postings list is given. Following sections will introduce techniques commonly employed to reduce the storage footprint. Due to the postings list often being organized as a list of sorted integers, more effective methods than generalized compression, such as Bzip2 and Zlib, have been developed. Coding schemes included ahead are *Variable-byte coding, Group Varint coding,* and *Elias*  $\gamma$  *coding.*

The chapter will end with an overview of work related to what has been performed in this thesis.

#### 4.1 Structure

An inverted index is an index data structure used to map between arbitrary content, such as words or terms, to locations in a database or document storage. It is conventionally used in search engines to provide fast full text search, at the cost of expensive processing when the database or document storage system is updated. A common structure of an inverted index is to keep a *dictionary* of terms and pair each term with the individual IDs of documents the term occurs in. The resulting list of such IDs, or *postings*, is described as a *postings list* [46, p. 6]. Listing 4.1 displays a simple inverted index for the following sentences:

- 1. Hakuna Matata.

- 2. It is our motto.

- 3. What is a motto?

4. Nothing. What is a motto with you?

Below, terms occur on the left hand side, while separate postings lists are encapsulated in curly braces on the right hand side.

**Listing 4.1** An inverted index for the four sentences above. Each number in the postings list represents the sentence a term occurs in.

{3, 4} a: 1 hakuna: {1} 2 {2, 3, 4} 3 is: **{**2**}** 4 it: matata: {1} 5 motto: {2, 3, 4} 6 nothing: {4} 7 our: **{**2**}** 8 {3, 4} 9 what: **{**4**}** 10 with: **{**4**}** 11 you:

In its simplest form, a postings list constitute a number of Uniform Resource Identifiers (URI), sorted in ascending order. Each URI identifies a location in an arbitrary document storage system. Listing 4.2 illustrates one of form a postings list can take, a comma delimited series of sorted integers.

**Listing 4.2** A simple example of a postings list for the term "motto" in the previously listed sentences.

1 motto: {2, 3, 4}

1

A common addition to storing the URI is to also bundle the location of a word in each document together with the number of occurences. Again for the term "motto", a postings list more rich in information is demonstrated in Listing 4.3.

**Listing 4.3** A postings list also containing the location of the word "motto" in each sentence, where the location is the *n*th position of the first character in "motto" in the sentence (whitespace included).

motto: {<2, 11>, <3, 11>, <4, 20>}

24

#### 4.2 Compression and Decompression

With an increasingly larger abundance of information being generated and indexed [18], the necessity of efficient schemes to minimize an inverted index' storage footprint is paramount. In addition, such schemes must enable fast retrieval of data stored in an index. Search engines implement a number of optimizations to reduce index size and provide better indexing and retrieval of data. Among these are specialized handling of extremely common terms which incur little benefit in providing a better search experience, so called "stop words" [46, p. 27], but also compression of the postings list. In addition to reducing the disk space, compression provides two additional benefits [46, p. 85]: *a*) Increased use of cache, as common terms can be stored in memory, rather than read from disk; and *b*) faster transfer between disk and memory. Indeed, compression schemes are known to have an efficiency level that surpass the time to transfer uncompressed data from disk to memory [46, p. 85].

A third, more subtle benefit is the ability to cache more data in memory, as an inverted index' size is decreased. For an uncompressed index, the cost of retrieval is equal to the sum of locating, *i.e.* seeking, for the index on disk, transferring it to main memory, and further caching it on the CPU. In order to deem a compression scheme successful, the reduction in retrieval time plus the time spent decompressing retrieved data, should not surpass the time cost of an uncompressed index [49].

The following sections will introduce techniques which facilitate the process of index minimization, each with a different granularity on their representation. Only *lossless* compression schemes that are effective for integer compression are presented.

#### **4.2.1** $\Delta$ -Coding

$\Delta$ -*Coding* is the process of recording the difference or *delta* between sequential data, rather than the data values themselves. Algorithm 4.1 and 4.2 illustrate a serial, naive approach to encoding and decoding.

1: function DELTA(A: array[1..n]) 2:  $D \leftarrow array[1..n]$ 3:  $D[1] \leftarrow A[1]$ 4: for  $i \leftarrow 2$  to n do

▷ Allocate result matrix D

```

5: D[i] \leftarrow A[i] - A[i-1]

```

6: return D

Algorithm 4.1 Serial, naive approach to  $\Delta$ -encoding.

1: function SUM(D: array[1..n]) 2:  $A \leftarrow array[1..n]$   $\triangleright$  Allocate result matrix **A** 3:  $A[1] \leftarrow D[1]$ 4: for  $i \leftarrow 1$  to n - 1 do 5:  $A[i+1] \leftarrow A[i] + D[i+1]$ 6: return DAlgorithm 4.2 Serial, naive approach to  $\Delta$ -decoding.

The effectiveness of the technique is influenced by the nature of data at hand. For an unsorted data set,  $\Delta$ -encoding may yield little to no compression. However, for an evenly distributed data set of sorted values, results of compression may be significant. The difference in compression ratio is best demonstrated by an example: Consider the list of integers displayed in Listing 4.4. Assuming the result of encoding is stored as *ASCII* characters, Listing 4.5 and 4.6 illustrate the difference in length after encoding the list as unsorted data and sorted data. It can be seen that the former achieves a compression ratio of  $\frac{40}{35} = 1.14$ , while the latter achieves a compression ratio of  $\frac{40}{22} = 1.89$ .

#### Listing 4.4 An unsorted list of integers.

1 **[**177, 152, 171, 155, 170, 128, 163, 133, 143, 139**]**

#### **Listing 4.5** List after $\Delta$ -encoding it without sorting.

1 [177, -25, 19, -16, 15, -42, 35, -30, 10, -4]

**Listing 4.6** List after  $\Delta$ -encoding it with sorting.

1 [128, 5, 6, 4, 9, 3, 8, 7, 1, 6]

#### 4.2.2 Variable-byte Coding

As the name suggests, *Variable-byte Coding*, or *vByte*, is a byte-oriented coding scheme. It is popular in Information Retrieval (IR) systems because of its simplicity and balanced trade-off between speed and compression ratio [46, p. 96]. Variable-byte coding uses as an integral number of bits in a byte (7) to encode an integer's value (the *payload*), while the first bit (the *continuation bit*) denotes if a byte is the last byte of an encoded number. That is, the continuation bit is set to 1 if this is the last byte of an encoded number, otherwise it is set to 0 [46, p. 96]. Table 4.1 displays four integers and their respective binary representations after being encoded with Variable-byte coding.

**Table 4.1** Example of Variable-byte coded integers. The continuation bit is highlighted in bold.

| Integer | Encoded Bit String                |

|---------|-----------------------------------|

| 1       | 10000001                          |

| 7       | 10000111                          |

| 9       | 10001001                          |

| 259     | <b>0</b> 0000010 <b>1</b> 0000011 |

Decoding is done by reading a bytestream until the continuation bit is equal to 1. Payloads are then extracted from read bytes and concatenated into the resulting, decoded number [46, p. 96]. Algorithm 4.3 and Algorithm 4.4 illustrate the pseudo-code for encoding and decoding, respectively. Decoding of variable-byte encoded numbers lends itself well to optimizations, as one is able to minimize the number of CPU cycles by use of bit shifts [12, p. 206].

During a keynote talk in 2009, Senior Google Fellow Jeff Dean introduced Google's modified variant of Variable-byte encoding, *Group VarInt*. A problem with traditional Variable-byte encoding is branch mispredictions. During decoding, the decoder must inspect every continuation bit and decide whether to continue decoding or concate the currently collected results and skip to the next set of data to decode. The decision is made via a branch instruction, and as such, a branch misprediction may occur. Group VarInt circumvents this by replacing the continuation bit with a two bit representation of an encoded posting's length. This allows for the

use of a lookup table or arithmetics to determine the number of bits to read for the posting currently being decoded [14]. Listing 4.7 illustrates the four previous values encoded with Group Varint. The vertical separator and the space between each encoded integer is present for readability only and not part of the encoded format.

**Listing 4.7** An example of four integers encoded with Group Varint. Note that the length of the last encoded integer is first in bit mask representing the length of each encoded integer.

```

1: function ENCODE(numbers: array[1..n])

bytestream \leftarrow array[]

▷ Allocate result array bytestream

2:

3:

for i ← 1 to n do

bytes \leftarrow array[]

4:

n \leftarrow numbers[i]

5:

while true do

6:

bytes \leftarrow [n \mod 128: bytes] \triangleright Prepend the result of n \mod 128 to

7:

bytes

if n > 128 then

8:

9:

break

n \leftarrow n \, div \, 128

10:

bytes[len(bytes)] \leftarrow bytes[len(bytes)] + 128

11:

bytestream ← [bytestream: bytes] ▷ Extend bytestream with bytes

12:

array

return bytestream

13:

```

Algorithm 4.3 Encoding a list of numbers with Variable-byte encoding.

1

```

1: function DECODE(bytestream: array[1..n])

numbers \leftarrow array[]

▷ Allocate result array numbers

2:

n \leftarrow 0

3:

for i ← 1 to n do

4:

if bytestream[i] < 128 then

5:

n \leftarrow 128 \times n + bytestream[i]

6:

7:

else

8:

n \leftarrow 128 \times n + (bytestream[i] - 128)

9:

numbers \leftarrow [numbers:n] \triangleright Append decoded number to numbers

array.

n \leftarrow 0

10:

11:

return numbers

Algorithm 4.4 Decoding a bytestream of Variable-byte encoded numbers.

```

#### **4.2.3** Elias $\gamma$ Coding

Elias  $\gamma$  Coding is one of the first non-trivial coding schemes for positive integers, first described by Elias in 1975 [15, p. 193]. It is bit-oriented, dividing each encoded number into two components: *1*) the *selector*, a *unary* representation of the *body's* length; and *2*) the *body*, an integer's binary representation [12, p. 193]. Table 4.2 lists the encoded values of integers 1, 7, 9 and 21.

| <b>Table 4.2</b> Example of Elias $\gamma$ encoded integers. |         |          |       |  |  |  |  |

|--------------------------------------------------------------|---------|----------|-------|--|--|--|--|

|                                                              | Integer | Selector | Body  |  |  |  |  |

|                                                              | 1       | 1        | 1     |  |  |  |  |

|                                                              | 7       | 110      | 111   |  |  |  |  |

|                                                              | 9       | 1110     | 1001  |  |  |  |  |

|                                                              | 21      | 11110    | 10101 |  |  |  |  |

With the unary segment of the encoded value having length  $1 + \lfloor \log_2 x \rfloor$  and the binary representation having the same length, an integer encoded with Elias  $\gamma$  encoding will inhabit  $2 \times \lfloor \log_2 x \rfloor + 2$  bits of space. By inverting the unary code, it can be observed that one is able to decrease the consumption of space, as the 1 bit between between the unary encoding and the integers binary representation is common. This is established from the fact that for an integer k with selector(k) = j,  $2^{j-1} \le k < 2^j$  is true. As such, the j-th least significant bit in k's binary representation, which happens to be the first bit in the encoded value's body, must be 1. With

this information in hand, the first bit in every encoded number's body is redundant and one can omit one bit per posting. The resulting storage foot print for an Elias  $\gamma$  encoded integer is thus  $2 \times \lfloor \log_2 x \rfloor + 1$ . [12, p. 193].

Elias  $\gamma$  coding is most effective when used together with postings lists of predominantly small gaps. However, for lists consisting of large gaps, it can be quite wasteful [12, p. 193]. Elias  $\delta$  Coding is an attempt to improve the efficiency for larger values. Here, the length of the integer value, *i.e.* the values previously encoded in unary, is instead encoded using Elias  $\gamma$  encoding. This way of compression manages to represent an integer in  $\lfloor \log_2 x \rfloor + 2 \times \lfloor \log_2(\lfloor \log_2 x \rfloor + 1) \rfloor + 1$  bits [15]. However, Elias  $\delta$  coding suffers from inefficiencies when encoding large values [49].

#### 4.2.4 SIMD Accelerated Coding

The previously presented compression schemes are not trivially translated to SIMD instructions and accelerated in such a manner. This is in essence due to the variable nature of each codeword generated by the different techniques. For both Variable-byte coding and Elias  $\gamma$  coding, the byte position of an encoded value is unknown until the preceding codeword is decoded.

With some modifications to Elias' initial algorithm and storage format, Schlegel *et al.* are able to parallelize and produce a SIMD accelerated Elias  $\gamma$  coding scheme; *k*- $\gamma$  coding [48].

Stepanov *et al.* use Variable-byte coding as a basis in their paper "SIMD-Based Decoding of Posting Lists", presenting SIMD accelerated compression techniques for variations of traditional Variable-byte coding, as well as the previously mentioned Group Varint.

Due to the unavailability of core SIMD instructions used in the implementation of the mentioned articles and time constraints, an implementation for ARM utilizing the NEON SIMD extensions have not been pursued.

#### 4.3 Related Work

Research into how one can minimize a postings list's storage footprint, and compression of data in general, is a thorougly researched area. Common techniques for compressing an inverted index are found in book literature by Ian H. Witten *et al.* [58], as well as text books from Manning *et al.* [46] and Büttcher *et al.* [12]. Such techniques have further been revised and optimized, for instance by Falk Scholer *et al.* in "Compression of Inverted Indexes For Fast Query Evaluation" [49]. However, these authors are not concerned with the underlying hardware of the inverted in-

#### 4.3. RELATED WORK

dex. "Fast integer compression using SIMD instructions" considers using Single Instruction Multiple Data (SIMD) instructions for a performance increase in integer compression and decompression, but does not address the storage medium [48].

Ahmed A. Aqrawi and Anne C. Elster considered compression performance in regards to SSD storage in 2011 [6]. However, their paper was concerned with the compression of seismic images and minimizing the size of data transferred across the bus between CPU and GPU. Microsoft, represented by Bojun Huang and Zenglin Xia attempted the use of flash memory as a replacement of expensive DRAM for caching frequently accessed data structures in a search engine [26].

To the best of this thesis' knowledge, none have previously investigated the nature of postings list encoding and decoding on a flash memory based storage medium in detail, and in addition, employed ultra-low-powered, *i.e.* handheld, hardware in the process.

## **Chapter 5**

# Postings List Coding on Mobile Devices

In order to perform the experiments required, two iOS applications have been created. The first is a tool to identify the flash memory read performance of benchmarked devices with a varied read buffer size. This was implemented due to an unavailability of similar applications for the platform. The first sections will be dedicated to the description of this.

The second is an application where one selects the compression scheme and buffer size, and measures the performance of a full disk-to-disk read-*encode*-write or read-*decode*-write. Below, test data, internal details of the application's implementation, concerns with developing for an embedded environment, and which coding schemes that have been implemented and the internals of these is disclosed. Problems one must handle when data is read blockwise and runs the risk of reading incomplete data is also described, together with how these problems have been solved.

Towards the end, details on how benchmarks are executed will be given.

#### 5.1 Flash Memory Performance

Flash memory read performance is measured using a iOS application identified as "SSDPerformanceMapping". Via its User Interface (UI), displayed in Figure 5.1, a user is able to set the number of iterations for a performance measurement test, as well as the size of each block to be read and whether or not data should be read in a random access manner. During execution, a user will receive visual feedback on the

status of the benchmark through two progress bars. After a successful execution, data from the run may be saved by pushing the "Save Log" button. Data from the benchmark is then stored on the device and must be retrieved through iTunes. A sample log file is illustrated in Listing 5.1.

| iPod 🗢      | 10:05                     | * 💼        | + |  |

|-------------|---------------------------|------------|---|--|

| Iterations: |                           | 100        |   |  |

| Block Size: |                           | 16777216   |   |  |

| Random Acc  | ess:                      |            |   |  |

| Running     | g Sav                     | ve log     |   |  |

| Read 7130   | 10 / 100<br>03168 / 10485 | 7600 bytes |   |  |

|             |                           |            |   |  |

|             | Total progress            | 5:         |   |  |

|             |                           |            |   |  |

Figure 5.1 The User Interface of the Flash Memory benchmark app.

Listing 5.1 A sample of the output generated from a test run of the benchmark.

- 1 Test start: 2013-11-08 10:34:47 +0000

- 2 Test end: 2013-11-08 10:37:42 +0000.

- 3 Was Random: O

- 4 Iterations: 10.

- 5 Total duration: 71.25 s.

- 6 Average iteration duration: 7.12 s.

- 7 Average transfer rate: 14.04 MB/s

#### 5.1.1 Benchmark Details

A 100 Mebibytes (MiB) file of random data is bundled with the application<sup>1</sup>. The data file is read in blocks as configured by the executor, with each read block being discarded immediately. The time to read each block is summarized, with an average being calculated at the end, together with an estimate of the transfer rate.

If the benchmark is executed with several iterations one runs the risk of not achieving accurate results due to data being kept in cache. Restarting the device to clear memory is tedious and also prone to inaccurate results, and flushing the memory by reading another large file will cause the operating system to kill the application due to memory consumption. To counter caching of the data file, each iteration starts with moving and renaming the file. Tests have shown this to be a viable option for achieving accurate results.

If one is measuring random access performance, each read location, *i.e.* the jumps in the data file, are also randomized before each iteration.

<sup>&</sup>lt;sup>1</sup>The file was generated by reading data from /dev/urandom as such: dd if=/dev/urandom of=data.random bs=1024 count=\\$((100\*1024)). The file size will be read as 105 MB ( $1 \times 10^6$ ), but is equal to 100 MiB ( $1 \times 2^{20}$ ).

#### 5.2 Encode and Decode Performance