# Improving Energy Efficiency with Special-Purpose Accelerators

Alexandru Fiodorov

Embedded Computing Systems Submission date: June 2013 Supervisor: Magnus Jahre, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

#### Abstract

The number of transistors per chip and their speed grows exponentially, but the power dissipation per transistor is decreased slightly with each process generation. This leads to increased power density and heat generation, meaning that only a fraction of the chip can be active at any given time. To attack this problem, heterogeneous systems-on-chip are developed. They consist of multiple specialized cores, each optimized to perform a particular set of tasks. Delegating parts of the application to run on specific, energy-efficient cores, allows more computations to execute within the given power budget, increasing the overall performance of the system.

This thesis proposes a methodology for developing a special-purpose accelerator for a given application to create an energy-efficient heterogeneous system-on-chip based on the Xilinx Zynq platform. This work introduces the Xilinx tool suite used during development and defines the complete design work flow for implementing the accelerator and running the application on the accelerated system. This work evaluates the optimization techniques which lead to the most energy-efficient implementation. The simulations show that pipelining, separate ports for reading and writing data and a small, fast, local memory improves the performance of the accelerator by a factor of 44.4x and the energy-efficiency by 379x.

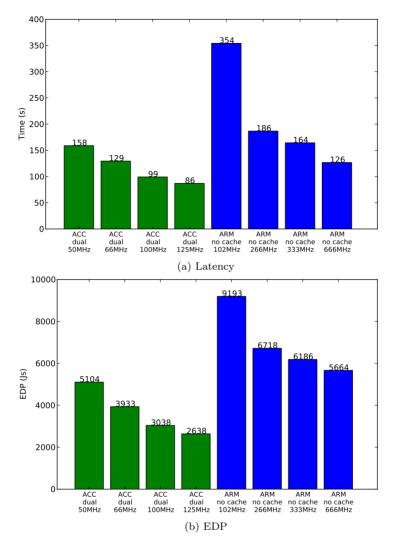

The accelerator is physically implemented on the Xilinx Zynq SoC and acts as a co-processor for the ARM CPU available on the system. This work proposes a methodology for evaluating the physical power consumption and performance of various configurations of the system. For the given application, the system with the accelerator running at 125 MHz is 1.5x faster and 2.15x more energy-efficient compared to the application executing only on the CPU at 666 MHz. If the clock frequencies are matched at 100 MHz, the accelerated system is 3.6x faster and 3x more energy-efficient.

### Contents

| Li       | st of | Figures                                  | 4         |

|----------|-------|------------------------------------------|-----------|

| Li       | st of | Tables                                   | <b>5</b>  |

| Li       | st of | Acronyms                                 | 7         |

| 1        | Intr  | oduction                                 | 11        |

|          | 1.1   | Motivation                               | 11        |

|          | 1.2   | Research Questions                       | 12        |

|          | 1.3   | Accelerating Applications on Xilinx Zynq | 13        |

|          | 1.4   | Contributions                            | 15        |

|          | 1.5   | Thesis Organization                      | 15        |

| <b>2</b> | Bac   | ground                                   | 17        |

|          | 2.1   | Accelerating for Energy-Efficiency       | 17        |

|          | 2.2   | Berkeley Dwarves                         | 19        |

|          | 2.3   | Xilinx Zynq-7000 System-on-Chip          | 22        |

| 3        | Imp   | lementation                              | <b>25</b> |

|          | 3.1   | Preparing the Application                | 26        |

|          | 3.2   | Pre-synthesis Validation                 | 27        |

|          | 3.3   | High-Level Synthesis (HLS)               | 28        |

|          |       | 3.3.1 Interface Synthesis                | 29        |

|          |       | 3.3.2 Specifying the Bus Interfaces      | 33        |

|          |       | 3.3.3 Default Accelerator                | 33        |

|          |       | 3.3.3.1 AXI Master Interface             | 34        |

|          |       | 3.3.3.2 AXI Slave Interface              | 35        |

|          |       | 3.3.3.3 First Optimization               | 35        |

|          |       | 3.3.3.4 Synthesising the Accelerator     | 36        |

|          |       | 3.3.4 Optimized Accelerator              | 38        |

|          |       | 3.3.5 Dual-Port Accelerator              | 39        |

|          | 3.4   | Post-synthesis Verification              | 40        |

|          | 3.5   | Hardware Design                          |           |

|          |       | 3.5.1 The BRAM Implementation            | 42        |

|          |                          | 3.5.2 Accessing DDR with High-Performance Slave Ports 4                           | 3                                |

|----------|--------------------------|-----------------------------------------------------------------------------------|----------------------------------|

|          |                          | 3.5.3 Accessing DDR with Accelerator Coherency Port 4                             | 5                                |

|          | 3.6                      | Software Design                                                                   | 7                                |

| 4        | Met                      | hodology 4                                                                        | -                                |

|          | 4.1                      | Power Measurements                                                                | 9                                |

|          |                          | 4.1.1 Measurement Setup                                                           | 9                                |

|          |                          | 4.1.2 Measuring Idle Power                                                        | $\mathbf{i}1$                    |

|          |                          | 4.1.3 Measuring Application Power                                                 |                                  |

|          | 4.2                      | Running on Different Hardware                                                     |                                  |

|          | 4.3                      | Tweaking Energy-Efficiency                                                        |                                  |

| <b>5</b> | $\mathbf{Res}$           | llts 5                                                                            | 7                                |

|          |                          |                                                                                   |                                  |

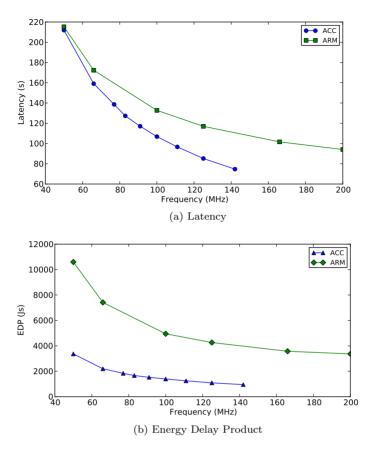

|          | 5.1                      | Accelerator Implementations                                                       | -                                |

|          | $5.1 \\ 5.2$             | Accelerator Implementations       5         LBM Running on ARM       6            | 68                               |

|          | • • •                    | LBM Running on ARM 6                                                              | 58<br>50                         |

|          | 5.2                      | LBM Running on ARM                                                                | 58<br>50<br>52                   |

|          | $5.2 \\ 5.3$             | LBM Running on ARM 6                                                              | 58<br>50<br>52<br>55             |

| 6        | 5.2<br>5.3<br>5.4<br>5.5 | LBM Running on ARM6LBM Running on ACC6LBM with Data in BRAM6                      | 58<br>50<br>52<br>55<br>56       |

| 6        | 5.2<br>5.3<br>5.4<br>5.5 | LBM Running on ARM6LBM Running on ACC6LBM with Data in BRAM6LBM with Data in DDR6 | 58<br>50<br>55<br>56<br><b>9</b> |

# List of Figures

| 1.1 | Dark silicon increase with technology scaling [3]   | 12 |

|-----|-----------------------------------------------------|----|

| 1.2 | Design work flow                                    | 13 |

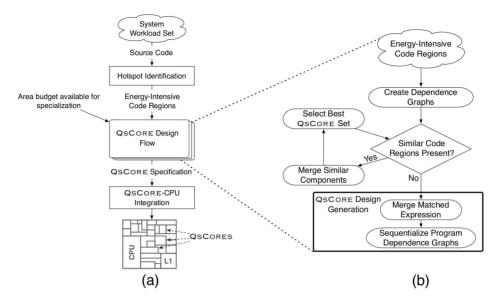

| 2.1 | Automatic synthesis and compilation of c-cores [22] | 18 |

| 2.2 | Overview of QsCore-enabled system [23]              | 19 |

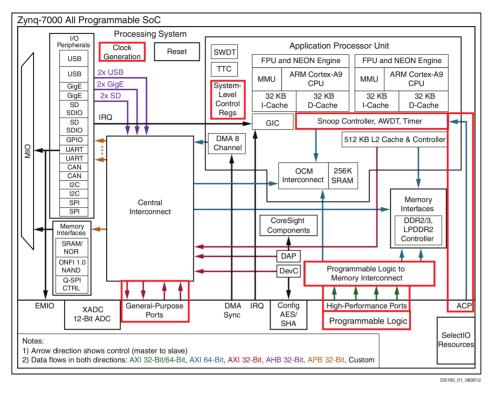

| 2.3 | Xilinx Zynq-7000 SoC overview [32]                  | 22 |

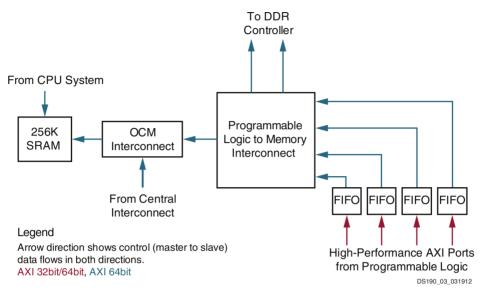

| 2.4 | PL Interface to PS Memory Subsystem [32]            | 23 |

| 3.1 | Data type and interface synthesis support [28]      | 29 |

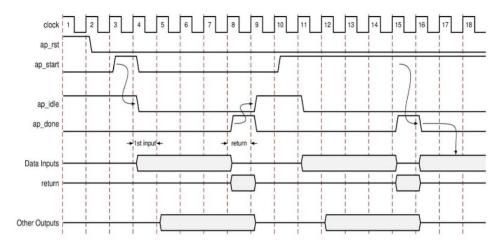

| 3.2 | Behaviour of ap_ctrl_hs interface [28]              | 32 |

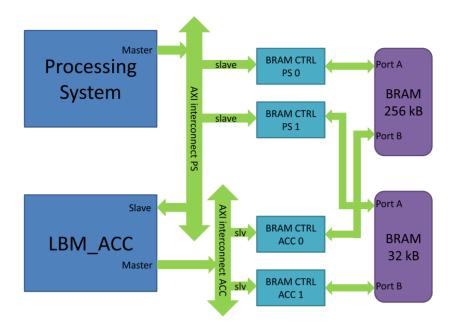

| 3.3 | System architecture using BRAM                      | 42 |

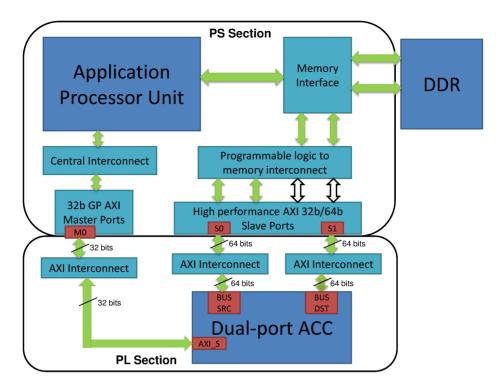

| 3.4 | System architecture using HP                        | 43 |

| 3.5 | ChipScope waveforms for AXI CDMA                    | 44 |

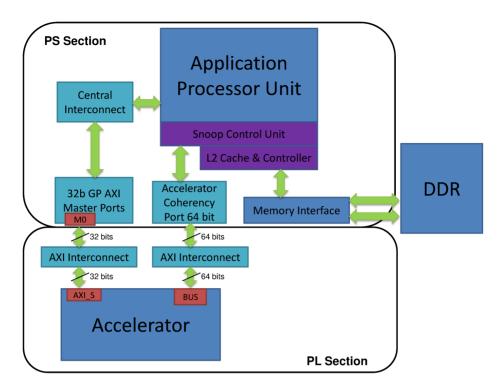

| 3.6 | System architecture using ACP                       | 45 |

| 4.1 | Power measurement setup                             | 50 |

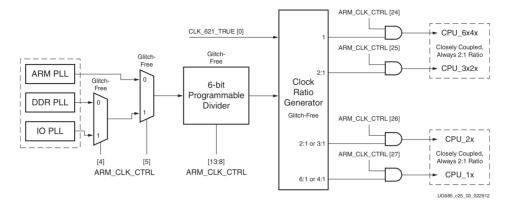

| 4.2 | CPU clock generation and domains [33]               | 54 |

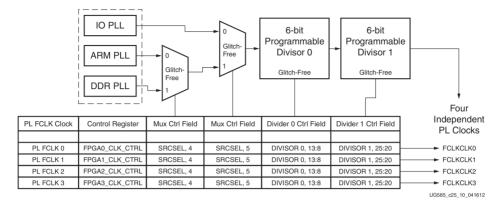

| 4.3 | PL clock generation [33]                            | 55 |

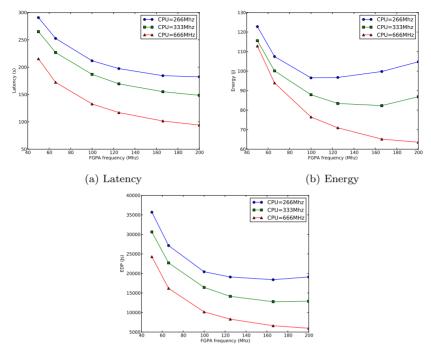

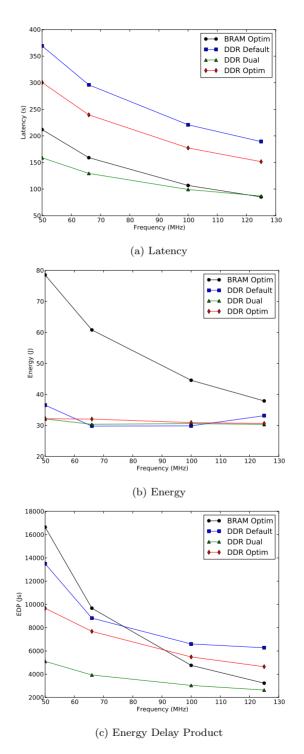

| 5.1 | Results for CPU with data in BRAM                   | 60 |

| 5.2 | Results for CPU with data in BRAM or DDR            | 61 |

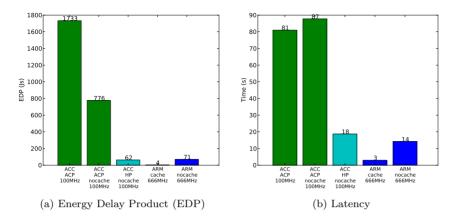

| 5.3 | Results for ACC using the ACP                       | 62 |

| 5.4 | Results for different ACC implementations           | 63 |

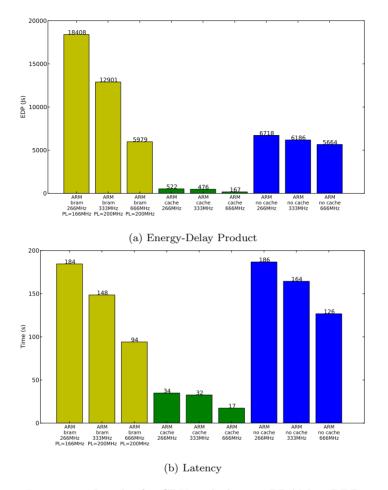

| 5.5 | Results for LBM with data in BRAM                   | 65 |

| 5.6 | Results for LBM with data in DDR                    | 66 |

### List of Tables

| 2.1 | The 13 Berkeley Dwarves                                                                       | 20 |

|-----|-----------------------------------------------------------------------------------------------|----|

|     | Description of interface protocols supported in Vivado HLS RTL port to bus interface mappings |    |

| 5.1 | Characteristics of different ACC implementations                                              | 58 |

## List of Acronyms

| ACC   | Accelerator                                            |

|-------|--------------------------------------------------------|

| ACP   | Accelerator Coherency Port                             |

| ASIC  | Application-Specific Integrated Circuit                |

| ASIP  | Application-Specific Instruction-set Processor         |

| ASSP  | Application-Specific Standard Product                  |

| BRAM  | Block RAM                                              |

| BSP   | Board Support Package                                  |

| DRC   | Design Rule Check                                      |

| EDP   | Energy Delay Product                                   |

| ED2P  | Energy Delay Squared Product                           |

| EEMBO | ${\tt C}$ Embedded Microprocessor Benchmark Consortium |

| FPGA  | Field-Programmable Gate Array                          |

| FSM   | Finite-State Machine                                   |

| HLS   | High-Level Synthesis                                   |

| HP    | High-Performance slave port                            |

| IP    | Intellectual Property                                  |

| LBM   | Lattice Boltzmann methods                              |

| ОСМ   | On-Chip Memory                                         |

| PL    | Programmable Logic                                     |

| PLL   | Phase Lock Loops                                       |

| PS    | Processing System                                      |

|       |                                                        |

- **RTL** Register-Transfer Level

- **SCPI** Standard Commands for Portable Instruments

- SCU Snoop-Control Unit

- **SDK** Software Development Kit

- **SLCR** System Level Control Registers

- **SoC** System-on-Chip

- **SPEC** Standard Performance Evaluation Corporation

- Tcl Tool Command Language

- **VHLS** Vivado HLS

- **XPS** Xilinx Platform Studio

10

### Chapter 1

### Introduction

### 1.1 Motivation

Modern computing is largely influenced by power limitations. Following Moore's Law [16], the number of transistors per chip and their speed continues to increase. However, the per-transistor switching power cannot be decreased by the same factor any more, due to the limits of threshold voltage scaling [22]. The result is the increased power density and heat generation, which cooling systems fail to remove completely.

With fixed power and area budget, integrating more transistors on a die results in need for under-clocking or under-utilizing a part of the chip. Ahn et al. [1] introduced the term *utilization wall* to refer to the limit on the fraction of the chip that can be used at full speed at any time. The remaining, passive silicon areas are referred to as *dark silicon* [13].

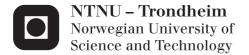

Figure 1.1 illustrates the problem of the utilization wall. It is an example of the current-generation 45nm-scale chip, which would shrink to a quarter size at 22nm and a sixteenth at 11nm. These chips would consume the same power for 22nm with 60% increase in peak frequency, and even drawing 40% less power with 2.4 times the original frequency. Future microcontrollers would be more efficient in terms of performance, power and area. Keeping the original area constant, one could pack 4 times the transistors at 22nm and 16 times at 11nm, thus increasing the processing power. However the power constraint of the original 45nm chip limits the 22nm and 11nm chips to use only 25% and 10% respectively. This means that at any given time, up to 90% of the silicon will be "dark".

Recently, a number of researches [7, 22, 23] showed that developing heterogeneous multi-core Systems-on-Chip (SoCs), containing specialized hardware, is an effective solution to the problem of using the area budget to improve performance. Choosing a heterogeneous architecture is driven by the fact that in most embedded systems, there are a number of computationally intensive algorithms that can be easily mapped to an individual processor that is highly tuned to running that one particular type of algorithm. Such processors are generally referred to as

Figure 1.1: Dark silicon increase with technology scaling [3]

Application-Specific Instruction-set Processors (ASIPs), co-processors or accelerators. Instead of running the whole application on a single, big, general-purpose core, different parts of the workload are delegated to specific co-processors. These hardware units optimize per-computation power requirements, allowing more computations to execute within the given power envelope [23]. The energy-efficiency of these accelerators improve the overall performance of the system without violating the power constraint. The main challenge with such systems is the software application, which should be aware of the heterogeneous nature of the underlying hardware and partition its code accordingly.

### 1.2 Research Questions

This thesis addresses one of the most discussed problems in modern computing:

"How to improve the energy-efficiency of the system?"

It tries to experimentally discuss one of the aspects of this issue:

"Does moving to heterogeneous multicore systems improve energy-efficiency?"

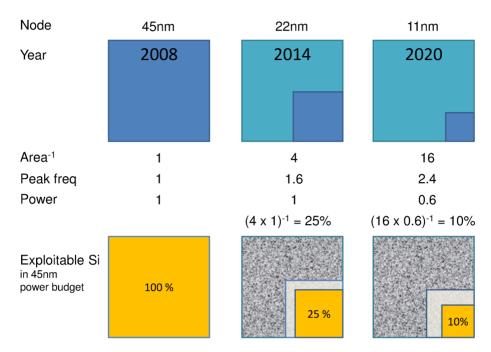

Figure 1.2: Design work flow

For this purpose a specialized accelerator is designed. During its development the following questions arise:

- 1. How can Xilinx tools assist in developing a energy-efficient hardware accelerator?

- 2. How can different optimization and architectural choices affect the performance and energy-efficiency of the accelerator?

- 3. How can the performance and energy-efficiency be evaluated on Zynq?

- 4. How can the custom accelerator improve the energy-efficiency of the complete system?

### 1.3 Accelerating Applications on Xilinx Zynq

This work presents the process of designing a hardware accelerator to improve the energy-efficiency of a given application. It explores the effects of different architectural techniques, like pipelining, caches and dynamic clock gating, to achieve the optimal balance between performance, area and power consumption, which leads to the most energy-efficient solution. This work also introduces a methodology for measuring power and performance, deriving metrics for energy-efficiency and comparing those for different system architectures.

The complete design flow is illustrated in Figure 1.2. It is based on High-Level Synthesis (HLS) – an automatic process of creating a Register-Transfer Level (RTL)

hardware representation of an algorithm, given its behavioural description. The behavioural specifications are generally represented by a synthesisable subset of ANSI C, C++ and SystemC programming languages. The first steps in the design flow are choosing the right application and identifying the so called *hot* regions – the most computationally intensive blocks of code, which will serve as input to the HLS process. These code segments will then pass the pre-synthesis validation, to make sure that all the constructs can be synthesised into a hardware representation. After running the synthesis process, the resulting hardware description is verified against the initial source code, to make sure it correctly implements the expected behaviour. The work flow then continues with *logic synthesis* – a process of transforming the RTL representation into a design implementation in terms of logic gates. The accelerator is prototyped on a Field-Programmable Gate Array (FPGA) platform, so the logic synthesis actually outputs a bitstream to program the device. Finally, the application's source code is adapted to make use of the hardware accelerator.

In order to find a suitable candidate for acceleration, I referred to the "Berkeley Dwarves" classification, by Asanovic et al. [6]. Dwarves are equivalence classes of applications that are believed to be the common computational patters of current and future scientific computing [6]. This makes the result of current work applicable for important, real-world scenarios. I chose the target application from the "Structured Grids" dwarf.

In the applications belonging to the "Structured Grids" dwarf, data is arranged in a regular multidimensional grid (most commonly 2D or 3D, sometime 4D, but rarely higher). Computation is a sequence of grid update steps. In each iteration, every node is updated using the values from a small neighbourhood. This algorithm is highly vectorizable. The points can be visited in an order that provides spatial locality to make good use of long cache lines and temporal locality to allow cache reuse. Due to high spatial locality and predictable addressing pattern, hardware or software pre-fetching can be used effectively. Temporal locality is limited and depends on the size of the neighbourhood, as each data value is accessed once by each neighbourhood that contains it [10].

In my previous paper [14] I identified the SPEC2006 implementation of Lattice Boltzmann methods (LBM) to be the best candidate for acceleration out of all Standard Performance Evaluation Corporation (SPEC) benchmark members of the Structured Grids dwarf. Its method performStreamCollide takes more than 99% of the execution time. Due to its structured data organization, spatial and temporal locality, application's performance can potentially benefit from hardware acceleration.

The accelerator is developed on a Xilinx Zynq System-on-Chip [31]. Zynq is composed of a dual-core ARM-A9 CPU and a Field Programmable Gate Array (FPGA), tightly integrated on a single die. The FPGA provides a flexible and powerful environment for rapid prototyping and exploring different design decisions. Coupled with the ARM cores, it creates a system well-suited for developing highperformance accelerator applications.

### 1.4 Contributions

This thesis proposes improving the system's energy-efficiency by implementing the most computationally intensive part of an application as a hardware accelerator. In the process of developing the accelerator the following is achieved:

- 1. The complete tool suite for developing a hardware module, given the behavioural description of a program in C is defined (Chapter 3).

- 2. Different optimization techniques to improve accelerator's energy-efficiency are evaluated (Section 3.3).

- 3. The specific details of developing such an accelerator on Xilinx Zynq are explained (Section 3.5).

- 4. The methodology for measuring power and latency is defined. These metrics are used to compute system's energy-efficiency (Chapter 4).

- 5. The results of the experiments are presented and analysed (Chapter 5).

### 1.5 Thesis Organization

The current thesis starts with Chapter 1, that presents the motivation, research questions and contributions. Chapter 2 presents the background on energy-efficient hardware accelerators, the Berkeley Dwarves and the Xilinx Zynq. Chapter 3 describes the design flow for implementing the accelerator, followed by Chapter 4 which presents the methodology for power measurements and describes how to configure the system to explore the energy-efficiency of different setups. Chapter 5 summarizes the results of the experiments. Chapter 6 draws the conclusions and discusses the future work. The Appendix lists the design files attached to this work.

CHAPTER 1. INTRODUCTION

### Chapter 2

### Background

### 2.1 Accelerating for Energy-Efficiency

At first, accelerators were concerned only about increasing the performance of the system. Most of them are strongly application-specific and cover domains such as cryptography [25], signal processing [11], vector processing [2] and computer graphics [17]. However, of particular interest for this paper are the works of Venkatesh et al. that focus on improving the energy-efficiency, while keeping the performance constant [22,23] or increasing it [18]. In contrast to the above mentioned examples, their approach is general and can target different applications. These papers are discussed in more detail in the following.

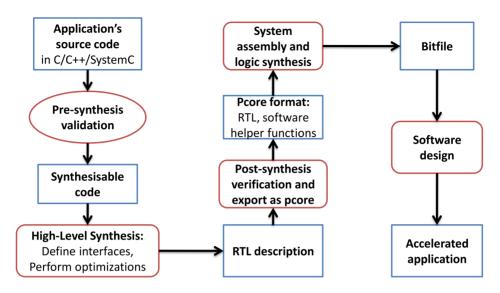

To attack the *utilization wall*, Venkatesh et al. [22] present the *conservation* cores or *c*-cores. C-cores have a different purpose than conventional accelerators and focus primarily on energy reduction rather than performance. Conservation cores that achieve a better performance are also possible, but the paper describes those with similar performance. The focus on energy-efficiency allows the c-cores to address a broader range of applications. Codes with large amounts of parallelism and predictable memory access patterns map naturally to conventional accelerators. On the other hand, their results show that irregular applications with little parallelism and very poor memory behaviour are excellent candidates for conservation cores. Their paper describes the tool chain for automatically synthesising c-cores for any given C code base (Figure 2.1). First the tool analyses the input C code and generates a set of c-cores. The custom compiler uses the descriptions of the c-cores available on the chip and produces assembler code that utilizes them. This means the C code should not be adapted to use the c-cores. The conservation cores support load-time reconfigurability using *patches*. These introduce a limited amount of flexibility, hence the applications should experience a high level of maturity to be accelerated using c-cores. The results show an improvement in energy-efficiency between 3.3x and 16.0x for targeted functions and up to 2.1x for the full application.

Figure 2.1: Automatic synthesis and compilation of c-cores [22]

The next paper by Venkatesh et al. [23] describes the Quasi-specific Cores (Qs-Cores), specialized processors capable of executing several general-purpose computations, optimized for energy-efficiency. When carefully implemented, a relatively small number of QsCores can potentially support a significant part of the computation. The design flow (Figure 2.2) is based on the observation that similar code patterns exist within and across applications. QsCores exploit this similarity to reduce the hardware redundancy of specialized cores by implementing a generalized functionality which is customized by parametrization. The authors develop heuristics that analyse the energy-area trade-off to ensure that the QsCores fit the area budget while providing a high degree of energy-efficiency. They evaluate their solution by implementing the main operator functions, find, insert, delete of commonly used data structures like linked-list, binary and AA trees, hash table etc. Using just 4 QsCores, they achieve 13.5x energy savings. On a general-purpose workload consisting of different benchmarks, the energy-efficiency is improved by a factor of 18.4x while reducing the number of specialized cores by 50% and area by 25% compared to fully-specialized implementation. At the system level, the energy-delay product is improved by 46% compared to general-purpose processors.

In the last paper [18], the authors optimize their earlier solution of c-cores with two techniques to improve performance and energy-efficiency even further, Selective Depipelining (SDP) and Cachelets. These enhanced c-cores are called *Efficient Complex Operation Cores* (ECOcores). SDP is a novel pipelining technique that reduces both unnecessary clock power and time wasted due to poorly aligned operators within cycles. Several operations, including dependent memory accesses can be performed in a single logical clock cycle. Selective depipelining exploits the fact that datapath and memory operations have different needs. The datapath is inexpensive to replicate by adding more functional units, while the memory accesses are centralized around a single bus. SDP allows the memory to run at a much higher

Figure 2.2: **Overview of QsCore-enabled system** The figure overviews the high-level design flow of a QsCore-enabled system (a) as well as the design flow for generating QsCores (b) (Source: [23])

clock rate, which effectively replicates the memory interface *in time*. Slowing down the datapath clock saves power and leverages ILP by replicating the computation *in space*. The second technique, *cachelets* is a type of small, distributed, coherent L0 cache that optimizes common load-store operations to reduce the memory latency by up to 83%. Cachelets provide sub-cycle memory accesses, 6x faster than L1 cache. Each cachelet serves a particular set of static operations. ECOcores achieve a reduction of 2x for Energy Delay Product (EDP) and 35% for area relative to c-cores. Compared to an efficient MIPS processor, they achieve on average a speed-up of 1.5x for targeted functions and 1.3x for the whole application, with EDP reduction of 7.1x and 2.9x respectively.

### 2.2 Berkeley Dwarves

For many years the evaluation of architectural innovations was based on benchmark suites like Standard Performance Evaluation Corporation (SPEC) and Embedded Microprocessor Benchmark Consortium (EEMBC) [12, 20]. These are very well suited for uni-processor systems, but there are no such standard benchmarks for evaluating parallel applications on multi- and many-core architectures, hence a higher level of abstraction is needed.

Researchers at Berkeley came up with the idea of "dwarves", algorithmic methods that capture a pattern of computation and communication [6]. The initial "Seven Dwarves" are based on the work of Phil Colella [8], who identified seven numerical methods that he believed will be important for science and engineering for at least the next decade. Later, six more dwarves were identified. Table 2.1 is adopted from [6,10] and presents a brief description of the 13 Berkeley Dwarves.

"Dwarves are equivalence classes, where membership is defined by the similarity in computation or data movement." [6]. Dwarves define a higher level of abstraction for a broad range of applications. Asanovic et al. believe that "although implementation of these programs may vary, the underlying patterns have persisted through generations of changes and will remain important in the future." [6]

Members of the dwarf "Structured Grids" are good candidates for acceleration, due to their structured data organization, spatial and temporal locality. The accelerator implementation described in this thesis targets one of the members of this dwarf – the SPEC2006 implementation of Lattice Boltzmann methods algorithm.

| Name                     | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dense linear<br>algebra  | Data are dense matrices or vectors, having little zero values,<br>typically laid out as a contiguous array. Computations are<br>performed on elements, rows, columns or partitions of matrices,<br>usually addition and multiplication.                                                                                                                                                                                 |

| Sparse linear<br>algebra | Data sets include vectors and matrices with few non-zero val-<br>ues. To reduce space and computation, they are stored in a<br>compressed form, as indexed lists.                                                                                                                                                                                                                                                       |

| Spectral methods         | Data is operated on in the spectral domain, often transformed<br>from either a temporal or spatial domain. During a transfor-<br>mation, spectral methods typically use multiple stages, where<br>the dependencies within a stage for a set of butterfly patterns.<br>Each butterfly operation has two inputs and two outputs (each<br>typically a complex number) and perform a set of multiply and<br>add operations. |

| N-body<br>methods        | Depends on interactions between many discrete points. Varia-<br>tions include particle-particle methods, where every point de-<br>pends on all others, leading to an $O(N^2)$ calculation, and hier-<br>archical particle methods, which combine forces or potentials<br>from multiple points to reduce the computational complexity<br>to $O(N \log N)$ or $O(N)$ .                                                    |

| Structured<br>grids      | Data is arranged in a regular multidimensional grid. Computa-<br>tion proceeds as a sequence of grid update steps. At each step,<br>all points are updated using values from a small neighbour-<br>hood around each point. These codes have a high degree of<br>parallelism, and data access patterns are regular and statically<br>determinable.                                                                       |

Table 2.1: The 13 Berkeley Dwarves

Continued on next page

|                                       | Table $2.1$ – continued from previous page                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Unstructured<br>grids                 | An irregular grid where data locations are selected, usually by<br>underlying characteristics of the application. Data point loca-<br>tion and connectivity of neighbouring points must be explicit<br>The points on the grid are conceptually updated together. Up-<br>dates typically involve multiple levels of memory reference indi-<br>rection, as an update to any point requires first determining a<br>list of neighbouring points, and then loading values from those<br>points. |

| MapReduce<br>(Monte Carlo)            | This dwarf was originally called "Monte Carlo", after the tech-<br>nique of using statistical methods based on repeated ran-<br>dom trials. The patterns defined by the programming mode<br>MapReduce are a more general version of the same idea: re-<br>peated independent execution of a function, with results aggre-<br>gated at the end. Nearly no communication is required between<br>processes.                                                                                   |

| Combinational<br>Logic                | exploits bit-level parallelism to achieve high throughput<br>Workloads dominated by combinational logic computations<br>generally involve performing simple operations on very large<br>amounts of data.                                                                                                                                                                                                                                                                                   |

| Graph<br>Traversal                    | Visits many nodes in a graph by following successive edges<br>These applications typically involve many levels of indirection<br>and a relatively small amount of computation.                                                                                                                                                                                                                                                                                                             |

| Dynamic<br>Programming                | is an algorithmic technique that computation.<br>simpler overlapping subproblems. It is particularly applicable<br>for optimization problems where the optimal result for a prob-<br>lem is built up from the optimal result for the subproblems.                                                                                                                                                                                                                                          |

| Backtrack and<br>Branch-and-<br>Bound | These algorithms work by the divide-and-conquer principle<br>the search space is subdivided into smaller subregions (thi<br>subdivision is referred to as branching), and bounds are found<br>on all the solutions contained in each subregion under consid<br>eration. Suboptimal solutions are discarded.                                                                                                                                                                                |

| Graphical<br>Models                   | A graphical model is a graph in which nodes represent variables, and edges represent conditional probabilities. Graphica models include Bayesian networks (also known as belief net works, probabilistic networks, causal network, and knowledg maps). Hidden Markov models and neural networks are also graphical models.                                                                                                                                                                 |

| Finite<br>State<br>Machine            | capture a system whose behaviour is defined by states, transitions defined by inputs and the current state, and events associated with transitions or states. These applications are mostly sequential.                                                                                                                                                                                                                                                                                    |

Table 2.1 – continued from previous page

Figure 2.3: Xilinx Zynq-7000 SoC overview [32]

#### 2.3 Xilinx Zynq-7000 System-on-Chip

Zynq-7000 is a family of SoC platforms composed of a powerful dual-core ARM<sup>®</sup> Cortex<sup>TM</sup> A9 MPCore<sup>TM</sup> based Processing System (PS) and a 28nm Xilinx Programmable Logic (PL) on a single die. The PS also includes on-chip memory, external memory interfaces and a variety of peripherals (Figure 2.3). The system offers the scalability and flexibility of an FPGA, while providing performance, power and ease of use typically associated with Application-Specific Integrated Circuits (ASICs) and Application-Specific Standard Products (ASSPs) [32]. The use of a powerful general-purpose processor allows developing both bare-metal and Linux applications.

Tightly integrated on the same die is the PL part, which is used to extend the PS. It is based on 28nm Artix-7 or Kintex-7 FPGA fabrics and comes in different sizes to accommodate the needs of various use-cases and applications. Artix-7 devices offer lower power and lower cost, targeting high-volume applications, while the Kintex-7 ones are used for high-performance and high I/O throughput [31].

The Zynq architecture enables software programmability in the PS and implementation of custom logic in the PL. The software updates and the hardware customization – whether static or dynamic, partial of full reconfiguration – can

Figure 2.4: PL Interface to PS Memory Subsystem [32]

be accomplished under control of the ARM processing system [31]. This opens a broad range of possibilities for hardware-software co-design. The integration of the PS with the PL allows levels of performance that the two-chip solutions (e.g. an ASSP with an FPGA) cannot match due to their limited I/O bandwidth, latency and power budgets [32].

Figure 2.3 highlights the parts of the system that are used for configuring and communicating with the custom logic implemented in the PL. Zynq is a processorcentric system, with the CPU coordinating the work of all peripherals. Zynq adopted the AMBA bus with AXI interface as the primary means of communication between the PS and the modules implemented in PL. The PS features two 32-bit general-purpose (GP) AXI Master ports to access the AXI Slave peripherals in PL. Usually these peripherals contain a set of internal configuration and status registers which are memory mapped to CPU's address space.

Zynq features the ability to share processor memory (internal and external) with the programmable logic, achieving high bandwidth with low latency. The peripherals that implement the AXI Master interface can access processor memory using the following ports [32]:

- Two 32-bit AXI Slave interfaces

- Four 64-bit/32-bit configurable, buffered AXI Slave interfaces with direct access to DDR memory and On-Chip Memory (OCM), referred to as High-Performance slave ports (HP).

- One 64-bit Slave Accelerator Coherency Port (ACP) for coherent access to CPU memory.

The two highest performance interfaces between PS and PL are the HP and the ACP. The HP interfaces connect the PL to the memory interconnect via a FIFO controller. Two of the three output ports go to the DDR memory controller and the third goes to the dual-ported OCM (Figure 2.4). The Accelerator Coherency Port (ACP) provides connectivity between the CPU and a potential accelerator function in the PL. It directly connects to the Snoop-Control Unit (SCU) of the ARM Cortex-A9 processors, enabling cache-coherent access to CPU data in the L1 and L2 caches [32].

Zynq allows fine tuning of the system power consumption via dynamic clock gating. The different clocks in the system can be configured from software by modifying the System Level Control Registers (SLCR) (Figure 2.3). The PL and PS are on separate power domains, allowing to shut down the PL completely, when not in use. The PL needs to be reconfigured after each power-on. The user should take PL configuration time into consideration when using this power saving mode. The PS cannot be turned off, but can be clocked down to 20 MHz. If the CPU delegates a very time-consuming task to the accelerator, it can go to a low-power sleep mode and be woken up by an interrupt, when the accelerator is finished. Furthermore, for single-threaded applications it makes sense to disable one of the cores to save energy.

# Chapter 3 Implementation

This work explores the techniques and tools which are used to improve the system's energy-efficiency. My approach selects a particular application and develops a special-purpose accelerator which offloads the CPU by implementing the most computationally intensive part of the algorithm in hardware. The accelerator is developed with the main focus on energy-efficiency, which in addition may or may not improve the performance.

The purpose of this chapter is to present the complete design flow in detail (see Figure 1.2 on page 13) and tools used for implementing the hardware accelerator. Since the target device is a Xilinx Zynq platform, the Xilinx tool-chain is used. It is composed of Vivado HLS (VHLS), for designing the accelerator, PlanAhead with Xilinx Platform Studio (XPS) and ChipScope, for assembling and configuring the target device, and the Xilinx Software Development Kit (SDK) for modifying the original software to work on the accelerated system.

The first step of the design flow (Figure 1.2) is described in my previous paper [14]. That work analysed the Standard Performance Evaluation Corporation (SPEC) benchmark suite to identify the SPEC2006 implementation of the Lattice Boltzmann methods (LBM) algorithm as the best candidate for acceleration. LBM is a class of computational fluid dynamics (CFD) methods for fluid simulation [24]. It is the computationally most important part of a larger code which is used in the field of material science to simulate the behaviour of fluids with free surfaces, in particular the formation and movement of gas bubbles in metal foams [21].

The most computationally intensive part of the algorithm is the *performStream-Collide* method. This method maps very well onto a hardware implementation, because it is self-contained, *i.e.* does not call other methods, and consumes more than 99% of algorithm's total execution time.

This chapter describes the steps of the design flow (Figure 1.2) that start after the function to develop a hardware accelerator for is chosen:

- Pre-synthesis validation (Section 3.2)

- High-Level Synthesis (HLS) (Section 3.3)

- Post-synthesis verification (Section 3.4)

- System assembly and logic synthesis (Section 3.5)

- Software design (Section 3.6)

The High-Level Synthesis (HLS) process uses the function's source code to generate the RTL representation of the algorithm. The input to HLS should be adapted to pass the pre-synthesis validation, to make sure it does not contain constructs that cannot be synthesised, like recursive functions, dynamic memory allocation, system calls, etc. During the HLS phase, the tool is instructed to perform certain optimizations on the resulting RTL, like pipelining and loop unrolling, as well as defines accelerator's interface for communication with other modules in the system. The resulting hardware description then passes the post-synthesis verification against the source code, to prove it correctly implements the desired behaviour.

The complete system, containing the accelerator and all the necessary modules and connections is assembled and fed into the *logic synthesis* tool, which generates the bitfile to program the target FPGA device. Having the hardware system powered by the accelerator, the source code of the LBM algorithm is changed to use the accelerator for computing the performStreamCollide function.

### 3.1 Preparing the Application

The default data type for input and output arguments, used in SPEC2006 implementation of LBM, is a four-dimensional grid, 100x100x130x20 of double precision floating point numbers. In addition, the algorithm needs some margin space around the grid to be allocated, which makes the total size for one grid about 205MB. The method performStreamCollide operates on two grids, one source and one destination, which makes a total of 410 MB of memory needs to be allocated.

At first, I could not figure out how to access the DDR memory from the accelerator, so Block RAM (BRAM) was used to store the data. This architectural choice limited the size of the initial input set of application, because the maximum size of BRAM that can fit on Xilinx Zynq is only 560 kB, part of which is used internally by the accelerator. This restriction can be met using various techniques, like prefetching or double buffering, but these come with the additional difficulties when tracing the data movement in the algorithm.

Due to time constraints I decided to use a simpler method. The problem size has been scaled to  $10 \times 10 \times 13 \times 20$  of *single* precision floating point numbers, which resulted in a total memory requirement of 266 kB. However the output of single precision computation is different when running on the CPU compared to floating Listing 3.1: Remove dynamic memory allocation

```

1 /* dynamic memory allocation cannot be synthesised */

2 // char* foo = (char*)malloc(128 * sizeof(char));

3

4 /* use static memory allocation instead */

5 char _foo[128];

6 /* pointer in the original design using malloc should not be rewritten,

7 * make it point to the existing static resource */

8 char* foo = &_foo[0];

```

point cores used in the accelerator. This mismatch prevented proper verification of the design, so I reverted back to double precision with a 10x10x5x20 grid. It resulted in a memory consumption of 281 kB. The maximum size of a BRAM module for Zynq is 256 kB, so I used two modules to store the grids.

Later in the design phase, I managed to access the DDR from the accelerator, but still kept the reduced size of the input set, to be able to evaluate how different memory systems affect performance and energy-efficiency.

### 3.2 Pre-synthesis Validation

Prior to synthesis, the C code should be validated by a test bench, which is nothing but a normal C program, containing all the functions above the synthesised one and a main function. The test bench should be self-checking, *i.e.* it should compare the output of the function to be synthesised with a "golden" result. It returns zero in case of success and a non-zero value, in case the outputs mismatch.

It is a good design practice to keep the functions used by the test bench in separate files from the functions to be synthesised. If a file contains both, it should be added to the project twice, once as a source file and once as a test bench file. All the input and output files used by the test bench should also be added to the project as test bench files.

Not every C/C++ function can be synthesised in VHLS. To be *synthesisable*, the function and all other functions it calls should contain the entire functionality of the design, avoiding system calls to the operating system. All its constructs should be unambiguous and of bounded size. The following is a list of constructs that cannot be synthesised:

- System calls cannot be synthesised, because they invoke OS routines which cannot be part of the final hardware design. For example printf(), scanf(), sleep(), time(), etc. should be removed from the functions to be synthesised. Also functions that handle files are not allowed, because there will be no concept of a file system in the final design. Access to external data should be performed via top-level function parameters or global variables.

- **Dynamic memory and functions.** To be able to synthesise a hardware implementation, the design must be self-contained, specifying all the required

Listing 3.2: Implementing unsupported casts

```

1

union udouble {

2

double d

3

u64 u:

4

};

\mathbf{5}

union udouble ud;

6

7

u64 double2int(double d) {

8

ud.d = d;

9

return ud.u;

10

}

11

12

double int2double(u64 u) {

ud.u = u;

13

14

return ud.d;

15

}

```

resources with fixed sizes. Dynamic memory allocation violates this constraint. Code that uses calls to malloc(), calloc(), free(), etc. should be adapted to use static allocation (see Listing 3.1). The same stands for virtual functions in C++, which cannot be used because the actual function to be executed is decided at runtime.

- General Pointer Casting Pointer casting is not supported in general case, only between native C types. The LBM algorithm uses unsupported casting between double and long int. This casting is implemented using unions (see Listing 3.2).

- **Pointer Arrays** Arrays of pointers are supported for synthesis if each pointer points to a scalar or an array of scalars.

- **Recursive Functions** Recursive functions cannot be synthesised. This refers to functions which can form endless recursion as well as tail recursions, with a finite number of calls.

### 3.3 High-Level Synthesis (HLS)

High-Level Synthesis (HLS), also called behavioural or architectural-level synthesis, is an automated design process which generates RTL designs from behavioural specifications. These specifications are generally defined using a synthesisable subset of ANSI C, C++ and SystemC languages. The HLS tools also allow to define a cost function and a set of design constraints for area, performance, power consumption, etc. The goal is to generate a RTL design that implements the specified behaviour while satisfying the design constraints and optimizing the given cost function.

The RTL design of the LBM accelerator is built using the Xilinx Vivado HLS (VHLS) tool. It takes a C/C++ function as input and produces the equivalent

| Argument                                                            | Variable<br>Pass-by- value |                 | Pointer<br>Variable<br>Pass-by-reference |   |    | Array<br>Pass-by-reference |   |    | Reference<br>Variable<br>Pass-by-reference |   |    |   |

|---------------------------------------------------------------------|----------------------------|-----------------|------------------------------------------|---|----|----------------------------|---|----|--------------------------------------------|---|----|---|

| Туре                                                                |                            |                 |                                          |   |    |                            |   |    |                                            |   |    |   |

| Interface Type                                                      | I                          | 10 <sup>2</sup> | 0 <sup>2</sup>                           | I | IO | 0                          | I | IO | 0                                          | I | IO | 0 |

| ap_none                                                             | D                          |                 |                                          | D |    |                            |   |    |                                            | D |    |   |

| ap_stable                                                           |                            |                 |                                          |   |    |                            |   |    |                                            |   |    |   |

| ap_ack                                                              |                            |                 |                                          |   |    |                            |   |    |                                            |   |    |   |

| ap_vld                                                              |                            |                 |                                          |   |    | D                          |   |    |                                            |   |    | D |

| ap_ovld <sup>3</sup>                                                |                            |                 |                                          |   | D  |                            |   |    |                                            |   | D  |   |

| ap_hs                                                               |                            |                 |                                          |   |    |                            |   |    |                                            |   |    |   |

| ap_memory                                                           |                            |                 |                                          |   |    |                            | D | D  | D                                          |   |    |   |

| ap_fifo                                                             |                            |                 |                                          |   |    |                            |   |    |                                            |   |    |   |

| ap_bus                                                              |                            |                 |                                          |   |    |                            |   |    |                                            |   |    |   |

| ap_ctrl_none⁴                                                       |                            |                 |                                          |   |    |                            |   |    |                                            |   |    |   |

| ap_ctrl_hs⁴                                                         |                            |                 | D                                        |   |    |                            |   |    |                                            |   |    |   |

| Kev:<br>I : input<br>IO : inout<br>O : output<br>D : Default Interf |                            | Unsup           | orted<br>rface<br>ported<br>rface        |   |    |                            |   |    |                                            |   |    |   |

Figure 3.1: Data type and interface synthesis support [28]

Verilog code, that implements the same logic in hardware. This particular function is considered the top module and all the functions it calls are implemented as submodules. To avoid compatibility issues between different tools of the suite, the name of the top module should be in *lower case* characters. Otherwise, during logic-synthesis the PlanAhead tool produces an error that tells nothing about the cause of the problem and is it hard to figure out that the name of the module was the reason of failure.

The following sections describe different types of interface protocols and bus interface implementations that Vivado HLS can synthesise for a given module. Later the implementation details of three versions of the accelerator are presented, DEFAULT, OPTIM and DUAL.

#### 3.3.1 Interface Synthesis

When the method's source code is synthesised into an RTL module, the method's arguments are synthesised into RTL data ports. Interface synthesis is used to automatically add an interface protocol to the RTL data ports. The interface

protocol could be as simple as an output valid signal indicating when an output is ready or it could include all the ports required to interface a BRAM [28].

The type of interface depends on the C argument. For example, the array arguments are the only ones that support a random access memory interface. This interface is used to directly connect to memory elements. If the memory is accessed via a bus interface, the argument should be a C pointer or a C++ reference variable. Figure 3.1 summarizes the types of interfaces which are supported for each type of C function argument. If no interface type or an unsupported type is specified for a port, the default one will be implemented as detailed in Figure 3.1.

The notes in Figure 3.1 are explained as follows [28]:

- 1. The concept of inputs and outputs is somewhat different between the C functions and RTL blocks. The following convention is used here for the purposes of explaining interface synthesis:

- A function argument which is read and never written to, like an RTL input port, is referred to as an input (I)

- A function argument which is both read and written to, like an RTL inout port, is referred to as inout (IO)

- A function argument which is written and never read, like an RTL output port, is referred to as an output (O)

- 2. A standard pass-by-value argument cannot be used to output a value to the calling function. The value of an argument such as this can only be returned (or output from the function) by the function return statement.

- Any pass-by-value function argument which is written to but never read, like an RTL output port, will be synthesised as an RTL input port with no fanout.

- Any pass-by-value function argument which is written to and read, like an RTL inout port, will be synthesised as an RTL input port only.

- 3. The ap\_ovld interface type is only valid for output ports.

- 4. The interface types ap\_ctrl\_none and ap\_ctrl\_hs are used to control the synthesis of function level interface protocols. These interface types are specified on the function itself (all other interface types are specified on the function arguments).

Table 3.1 summarizes the available interface protocols. There are two types of interface synthesis, the one that is performed on C function arguments and the one that is applied at the function or block level.

| Interface                  | Description                                                                                                                                                                                                                                                                                                      |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ap_none                    | The simplest interface with no associated control signals. The producer<br>blocks are required to provide data to the input port at the correct time<br>or hold it for the length of the transaction. The consumer blocks should<br>read the output ports at the correct time.                                   |

| ap_stable                  | Like ap_none it does not add any interface control ports to the design. The ap_stable informs the High-Level Synthesis (HLS) that the data applied to this port will remain stable during normal operation, but is not a constant value which could be optimized, and the port is not required to be registered. |

| ap_ack                     | Provides an acknowledge signal to say when data is consumed.                                                                                                                                                                                                                                                     |

| ap_vld                     | Provides a valid signal to indicate when the data is valid.                                                                                                                                                                                                                                                      |

| ap_ovld                    | The same as ap_vld, but can only be specified on output ports. This is<br>a useful type for ensuring pointers which are both read from and written<br>to, will only be implemented with an output valid port (and the input<br>half will default to type ap_none)                                                |

| ap_hs                      | This interface provides both an acknowledge and a valid signal. It is a superset of the ap_ack, ap_vld and ap_ovld interfaces.                                                                                                                                                                                   |

| ap_memory                  | Used to communicate with memory elements (RAMs, ROMs) when the implementation requires random accesses to memory locations. The memory interface cannot be stalled by external signals. It provides an indication of when output data is valid.                                                                  |

| ap_fifo                    | Used when the access is performed only in a sequential manner. This<br>interface allows the port to be connected to a FIFO, supports full two-<br>way empty-full communication.                                                                                                                                  |

| ap_bus                     | Used to communicate with a bus-bridge. The interface does not adhere<br>to any specific bus standard but is generic enough to be used with a bus<br>bridge which in-turn arbitrates with the bus system and is responsible to<br>cache all burst writes. It supports standard and burst modes of operation.      |

| ap_ctrl_none<br>ap_ctrl_hs | Used to specify if the RTL is implemented with block-level handshake<br>signals or not. These signals specify when the design can start to perform<br>its standard operation and when that operation ends.                                                                                                       |

Table 3.1: Description of interface protocols supported in Vivado HLS

Standard port level interface synthesis is specified for each function argument. A function argument which is both read from and written to is synthesised in the following manner [28]:

- ap\_none, ap\_stable, ap\_ack, ap\_vld, ap\_ovld, ap\_hs separate input and output ports. For example, if function argument arg1 was both read from and written to, it would be synthesised as RTL input data port arg1\_i and output data port arg1\_o and any specified or default IO protocol is applied to each port individually.

- ap\_memory, ap\_bus a single interface is created. Both these RTL ports support read and write.

- ap\_fifo read and write are not supported. There must be two separate function arguments for reading and writing.

Figure 3.2: Behaviour of ap\_ctrl\_hs interface [28]

Interface modes ap\_ctrl\_hs and ap\_ctrl\_none are applied on the function or function return value to specify if the RTL is implemented with block-level handshake signals or not. These signals control when the block can begin execution, when it is ready for new data and when it completes. By default these signals are made external to the module, but could be as well made accessible through an internal control register.

The behaviour of the handshake signals created by the ap\_ctrl\_hs protocol is illustrated in Figure 3.2 and presented in the following [28]:

- After reset, the block will wait for ap\_start to go high before it begins operation.

- Output ap\_idle goes low when ap\_start is sampled high.

- Data can now be read on the input ports. The first input data may be sampled on the first clock edge after ap\_idle goes low.

- When the block completes all operations, any return value will be written to port ap\_return. If there was no function return, there will be no ap\_return port on the RTL block. Other outputs may be written to at any time until the block completes and are independent of this IO protocol.

- Output ap\_done goes high when the block completes operation. If there is an ap\_return port, the data on this port will be valid when the ap\_done is high. The ap\_done signal can therefore be used to show when the function return value is valid.

- The ap\_idle signal goes high one cycle after ap\_done and remains high until the next time ap\_start is sampled high, indicating the block should once again begin operation.

- If the ap\_start signal is high when ap\_done goes high: the ap\_idle signal will remain low, the block will immediately start its execution (or next transaction), the next input may be read on the next clock edge.

| RTL Interface<br>Protocol                          |                       |                |                |                     |                      |     |     |

|----------------------------------------------------|-----------------------|----------------|----------------|---------------------|----------------------|-----|-----|

|                                                    | AXI4<br>Lite<br>Slave | AXI4<br>Master | AXI4<br>Stream | PLB<br>4.6<br>Slave | PLB<br>4.6<br>Master | FSL | NPI |

| ap_bus                                             | -                     | Х              | -              | -                   | Х                    | -   | -   |

| ap_fifo                                            | -                     | -              | Х              | -                   | -                    | Х   | -   |

| ap_ctrl_hs<br>ap_none<br>ap_vld<br>ap_ack<br>ap_hs | Х                     | -              | -              | Х                   | -                    | -   | -   |

| ap_ovld<br>ap_memory                               | -                     | -              | -              | -                   | -                    | -   | -   |

Table 3.2: RTL port to bus interface mappings

Listing 3.3: *performStreamCollide* initial interface

void performStreamCollide(double[SIZE] srcGrid, double[SIZE] dstGrid);

#### 3.3.2 Specifying the Bus Interfaces

In addition to standard interfaces described in the previous section, VHLS can also automatically add bus interfaces to the RTL design. The bus interfaces are added to the design during the "Export RTL" process, so they are not present in the RTL written after synthesis and do not appear in the synthesis reports.

The type of the bus interface depends on the protocol of the RTL port it is applied to. Table 3.2 is adopted from Vivado User Guide [28] and shows the list of the RTL interface ports and the available bus interfaces which can be connected to them. The **ap\_memory** interface does not require a bus interface and can be directly connected to memories (BRAM). Any port with **ap\_ovld** interface should be modified to be one of the supported types, for example **ap\_hs**, or it cannot be connected to a bus interface.

#### 3.3.3 Default Accelerator

The initial interface of the method performStreamCollide is shown in Listing 3.3. The method arguments are two arrays of double floating point numbers, representing the source and destination grids. By default, arrays are synthesised into memory ports (Figure 3.1). Their size should be fixed at compile time, otherwise the function cannot be synthesised. Connecting an external memory with fixed size directly to these ports results in a tight coupling of the system components and makes the system less flexible. To achieve a modularized and extensible architecture, the memory will be accessed via the bus. The address and location of the grids will be stored in internal configuration registers.

```

Listing 3.4: performStreamCollide with wrapper

```

```

1

void performStreamCollide(volatile double *p_srcGrid, volatile double *p_dstGrid) {

2

3

}

4

void lbm_acc(volatile double *bus,

5

volatile u32 *srcAddr, volatile u32 *dstAddr) {

6

7

/* make sure the addresses are aligned */

8

9

if (*srcAddr % sizeof(double) != 0 || *dstAddr % sizeof(double) != 0) return;

10

performStreamCollide(bus + (*srcAddr)/sizeof(double),

11

12

bus + (*dstAddr)/sizeof(double));

13

}

14

}

```

Xilinx Zynq SoC is using the AMBA AXI bus interface for communication between modules in the system. The accelerator implements two AXI interfaces, an AXI master to access the memory and the AXI slave to give CPU access to its configuration registers.

#### 3.3.3.1 AXI Master Interface

Using the master interface, the Accelerator (ACC) accesses the memory controllers to keep the data. The unified bus standard allows to attach different memory controllers to the ACC, provided they all implement an AXI slave interface. This allows a flexible design, in which the memory system could be replaced, without modifying the ACC architecture.

In the current implementation of the system, the ACC will keep the data either in BRAM or in the DDR. In the former case, the ACC accesses the AXI slave BRAM controllers which in turn connect to the BRAM modules in the Programmable Logic (PL). The second option is to connect the ACC to the AXI slave ports of the Processing System (PS), which provide access to the DDR Controller.

The initial interface of the performStreamCollide (Listing 3.3) cannot be mapped to a ap\_bus port. Figure 3.1 suggests that to implement a bus protocol, the function argument should be a pointer. This will allow both reading and writing to it. Vivado HLS (VHLS) requires the pointer to be declared volatile if it will be accessed multiple times. Thus, the first modification is to convert the *array* into a *volatile pointer* type (Listing 3.4 line 1). The modified interface remains compatible with the initial one.

In the C program, the pointer values of srcGrid and dstGrid are the memory locations of the source and destination grids respectively. However, when these arguments are mapped to bus ports, in the resulting RTL there is no information about the addresses of the grids. Both bus interfaces are implemented to have a base address of zero. This means the actual addresses of the grids should be explicitly added as an offset to srcGrid and dstGrid variables. The ACC accesses the memory through a single bus interface. This requires changing the existing interface of performStreamCollide. To keep a clean coding style and ensure backward compatibility, the original interface is left unaltered, instead a wrapper lbm\_acc is build around the original function (Listing 3.4). The volatile double \*bus variable represents the master port of the ACC. The offsets specifying the addresses of source and destination grids are added to the bus variable and the results are passed as arguments to the performStreamCollide.

#### 3.3.3.2 AXI Slave Interface

The slave interface is used by the Processing System (PS) to set up and control the Accelerator (ACC). As previously discussed, the wrapper function should at least contain three arguments, the bus variable representing the master port and two pointer variables srcAddr and dstAddr that would contain the addresses of the source and destination grids respectively (Listing 3.4). Note that the value referenced by the pointer contains the actual data.

The address variables implement the **ap\_hs** protocol, that provides both a valid and an acknowledge signal. By default each of them will be synthesised as separate AXI slave ports. To save pins and simplify the design, all configuration variables are bundled into a single AXI slave port. ACC stores these variables in internal registers, that can be accessed by the slave interface, specifying the address of the register.

The accelerator implements the so called "function level hand-shake protocol". The behaviour of this protocol is detailed in Figure 3.2. It specifies three signals, which describe the status of accelerator's Finite-State Machine (FSM). These signals are used by the PS to control when the ACC can start execution and to be notified when the operation has finished. By default, these signals are synthesised as external inputs and outputs. By specifying the register option on the ap\_ctrl\_hs protocol, the control signals can be accessed using the accelerator's status register, which is also mapped to the AXI Slave interface. The control signals are:

- ap\_start input signal. When set to "high", accelerator starts its execution.

- ap\_idle output signal. Is kept "low" during accelerator's execution and "high" when it is idle.

- ap\_done output signal. Becomes "high" when the accelerator has finished its execution. Cleared on read.

#### 3.3.3.3 First Optimization

In the original SPEC implementation of LBM, the performStreamCollide is called multiple times in a loop, swapping the source and destination grids after each iteration (Listing 3.5). The call to performStreamCollide at line 11 is replaced by the call to the accelerator (Listing 3.6). To reduce the overhead of setting up

Listing 3.5: LBM original implementation

```

1

void LBM_swapGrids( LBM_GridPtr* grid1, LBM_GridPtr* grid2 ) {

LBM_GridPtr aux = *grid1;

2

3

*grid1 = *grid2;

4

*grid2 = aux;

}

\mathbf{5}

6

7

int main() {

8

. . .

9

int t:

for( t = 1; t <= param.nTimeSteps; t++ ) {</pre>

10

11

performStreamCollide(*srcGrid, *dstGrid);

12

LBM_swapGrids( &srcGrid, &dstGrid );

}

13

14

. . .

15

}

```

#### Listing 3.6: Calling the accelerator

```

1 XLbm_acc_SetP_srcgrid(&acc, srcAddr);

```

```

2 XLbm_acc_SetP_dstgrid(&acc, dstAddr);

```

```

3 XLbm_acc_SetNsteps(&acc, param.nTimeSteps);

```

```

4 XLbm_acc_Start(&acc);

```

```

5 while (!XLbm_acc_IsDone(&acc));

```

and calling the accelerator in every iteration, the loop is moved inside the wrapper and the number of iterations is passed as an argument.

Notice that the swapping is done in a "hardware-friendly" way (Listing 3.7). Normally in software this is achieved by simply swapping the values of the variables (see LBM\_swapGrids in Listing 3.5), but VHLS erroneously interprets it and "optimizes the unnecessary" swapping by just assigning one variable to another. The srcAddr and dstAddr are merged as if pointing to the same memory location, which is not the expected behaviour. Instead, the swapping is done explicitly, by changing the source and destination grid addresses every odd iteration (Listing 3.7) lines 12-18).

#### 3.3.3.4 Synthesising the Accelerator

Vivado HLS (VHLS) uses special directives to set up the synthesis process. They annotate function's parameters, to specify the module's interface, and pieces of code, to implement loop unrolling, pipelining and other optimization features. The VHLS directives can be specified in the source code, using **#pragma** pre-processor directives, or in the **directives.tcl** file of the solution. The Tcl file should normally be modified using the GUI, but one could as well directly create his own directives file and include it in the main **script.tcl** file of the solution.

Listing 3.8 presents the Tool Command Language (Tcl) script to configure the

Listing 3.7: Moving the main loop inside the wrapper

```

void performStreamCollide(volatile double *p_srcGrid, volatile double *p_dstGrid) {

1

\mathbf{2}

3

r

4

5

void lbm_acc(volatile double *bus,

6

volatile u32 *srcAddr, volatile u32 *dstAddr, u32* nsteps) {

7

int i;

/* make sure the addresses are aligned */

8

if (*srcAddr % sizeof(double) != 0 || *dstAddr % sizeof(double) != 0) return;

9

for (i = 0; i < *nsteps; i++) {</pre>

10

/* do the swap */

11

12

if (i % 2 == 0) {

13

performStreamCollide(bus + (*srcAddr)/sizeof(double),

14

bus + (*dstAddr)/sizeof(double));

15

} else {

16

performStreamCollide(bus + (*dstAddr)/sizeof(double),

17

bus + (*srcAddr)/sizeof(double));

18

}

}

19

}

20

```

```

Listing 3.8: Tcl configuration script

```

```

1

# implement the function level protocol for lbm_acc

\mathbf{2}

# and create a status register for the signals.

3

set_directive_interface -mode ap_ctrl_hs -register "lbm_acc"

# map the status register to the AXI Slave port

4

set_directive_resource -core AXI4LiteS "lbm_acc" return

5

6

# the "bus" parameter should implement the bus interface

\overline{7}

# and specifically the AXI Master.

set_directive_interface -mode ap_bus -depth 36000 "lbm_acc" bus

8

9

set_directive_resource -core AXI4M "lbm_acc" bus

10

# the other parameters are mapped to AXI Slave

11

set_directive_interface -mode ap_hs "lbm_acc" srcAddr

set_directive_resource -core AXI4LiteS "lbm_acc" srcAddr

12

13

set_directive_interface -mode ap_hs "lbm_acc" dstAddr

set_directive_resource -core AXI4LiteS "lbm_acc" dstAddr

14

```

15 # ... other accelerator's parameters are mapped in a similar way