# SHMACsim

A Cycle-accurate Simulation Infrastructure for the Heterogeneous SHMAC Multi-Core Prototype

# Yaman Umuroglu

Embedded Computing Systems Submission date: July 2013 Supervisor: Magnus Jahre, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

# **Problem Description**

#### A Cycle-accurate Simulation Infrastructure for the Heterogeneous SHMAC Multi-Core Prototype

Current multi-core processors are constrained by energy. Consequently, it is not possible to improve performance further without increasing energy efficiency. A promising option for making increasingly energy efficient CMPs is to include processors with different capabilities. This improvement in energy efficiency can then be used to increase performance or lower energy consumption.

Currently, it is unclear how system software should be developed for heterogeneous multi-core processors. A main challenge is that little heterogeneous hardware exists. It is possible to use simulators, but their performance overhead is a significant limitation. An alternative strategy that offers to achieve the best of both worlds is to leverage reconfigurable logic to instantiate various heterogeneous computer architectures. These architectures are fast enough to be useful for investigating systems software implementation strategies. At the same time, the reconfigurable logic offers the flexibility to explore a large part of the heterogeneous processor design space.

The Single-ISA Heterogeneous MAny-core Computer (SHMAC) project aims to develop an infrastructure for instantiating diverse heterogeneous architectures on FPGAs. A prototype has already been developed, but an important remaining challenge is to design a flexible memory system while retaining high performance. This and other architectural trade-offs are best evaluated in a simulator. With simulation, it is possible to evaluate a large number of policies without an excessive implementation effort.

The task in this assignment is to develop a simulator for the SHMAC prototype. In addition, the student should implement a set of micro-benchmarks that stress important aspects of the architecture. If time permits, the student should propose improvements and evaluate the performance impact of these improvements.

Supervisor: Assoc. Prof. Magnus Jahre, IDI

#### Abstract

The fast-paced development trend in microprocessor performance characterized by Moore's Law can no longer continue unperturbed. Shrinking semiconductor node size still translates into increasing transistor count but not directly into performance, since thermal and power constraints are limiting the amount of transistors that can be used simultaneously. One way of exploiting this "dark silicon" is building heterogeneous systems containing specialized accelerators and cores. The SHMAC project aims to provide a research platform for heterogeneous systems research. An FPGA prototype has been constructed for the SHMAC, but to have a rapid implement-evaluate cycle for system policies, software simulation is needed.

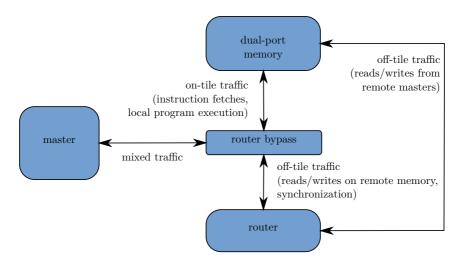

This thesis covers the design and implementation of a cycle-accurate simulation infrastructure for the SHMAC. Additionally, the current state of the architecture is evaluated with a set of micro-benchmarks and several improvements are proposed. The constructed infrastructure offers a highly configurable, cycle-accurate simulation of the SHMAC FPGA prototype. A micro-benchmark-based analysis of the current state of the architecture exposes the router hop latency and throughput as the greatest bottlenecks. To address this a dual-port RAM slave with router bypass is implemented, resulting in  $3.5 \times$  instruction fetch speedup and contributing to overall system performance. Improvements contributing traffic independent clock counting and bootstrapping functionality, and a network packet lifetime instrumentation method are also described.

# Preface

This thesis is submitted to the Norwegian University of Science and Technology in partial fulfilment of the requirements for the European Master in Embedded Computer Systems (EMECS) degree.

This work has been performed at the Department of Computer and Information Science, NTNU, Trondheim, with Assoc. Prof. Magnus Jahre as the supervisor.

## Acknowledgements

I would like to extend my gratitude to my supervisor Magnus Jahre for his extensive support throughout the entire process and for enabling me to start a research career on heterogeneous multi-core platforms, to Håkon Marthinsen for his extensive moral support as well as invaluable help on  $L^{AT}EX$  and Inkscape, and to all my instructors and friends at the Erasmus Mundus in Embedded Computing Systems programme for a fantastic two years.

The "Virtual Heterogeneous Multicorn" logo is built upon the work of Dee Dreslough with post-processing by Karl Johan Heimark and myself.

# Contents

| Pr  | oblen                | n Description                                                                             | i             |

|-----|----------------------|-------------------------------------------------------------------------------------------|---------------|

| Pr  | eface                |                                                                                           | iv            |

| Lis | t of                 | Figures                                                                                   | viii          |

| Lis | t of                 | Tables                                                                                    | ix            |

| Lis | t of                 | Abbreviations                                                                             | x             |

| 1.  | 1.1.                 | oduction<br>Historical Trends in Computing Power                                          | <b>1</b><br>1 |

|     | 1.2.<br>1.3.         | Era of Multi-Cores: Symmetric, Asymmetric and Heterogeneous<br>EECS and the SHMAC project | $\frac{3}{5}$ |

|     | 1.4.<br>1.5.<br>1.6. | Assignment Interpretation          Contributions          Report Organization             | 5 7 7         |

| 2.  | Bac                  | kground                                                                                   | 9             |

|     | 2.1.                 | The Motivation for Heterogeneous Multi-Cores                                              | 9             |

|     | 2.2.                 | Hardware for Heterogeneous Multi-core Processors                                          | 11            |

|     |                      |                                                                                           | 11            |

|     |                      |                                                                                           | 12            |

|     |                      |                                                                                           | 14            |

|     | 2.3.                 |                                                                                           | 15            |

|     | 2.4.                 | 1                                                                                         | 18            |

|     |                      | 0                                                                                         | 19            |

|     |                      |                                                                                           | 20<br>21      |

|     |                      | 2.4.2.1. The genis simulator                                                              | 41            |

|     |                      |                                                                                           | 22            |

|     |                      |                                                                                           | 23            |

| 3. | The  | SHMAC Simulator In      | frastructure                         | 25         |

|----|------|-------------------------|--------------------------------------|------------|

|    | 3.1. | Methodology             |                                      | 25         |

|    |      | 3.1.1. Development E    | asis                                 | 25         |

|    |      | 3.1.2. Choice of Abst   | raction Levels                       | 26         |

|    |      | 3.1.3. Choice of Exte   | rnal Tools and Modules               | 27         |

|    |      | 3.1.3.1. Simul          | ation Framework                      | 28         |

|    |      | 3.1.3.2. Proce          | ssor Core Generation                 | 29         |

|    | 3.2. | Design                  |                                      | 29         |

|    |      | 3.2.1. Processor Core   | s                                    | 30         |

|    |      | 9                       | cation with SHMAC Memory Interface . | 31         |

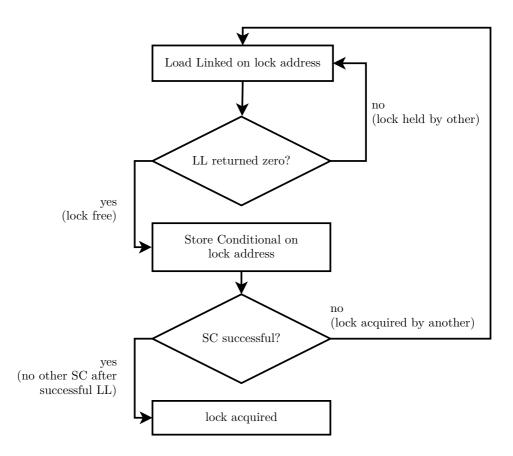

|    |      | 3.2.1.2. Imple          | mentation of $LL/SC$ Instructions    | 32         |

|    |      | 3.2.2. Memory Units     |                                      | 33         |

|    |      |                         | Slave Unit                           | 33         |

|    |      |                         | L/SC Slave Unit                      | 34         |

|    |      | 3.2.2.3. Other          | Slave Units                          | 35         |

|    |      |                         |                                      | 35         |

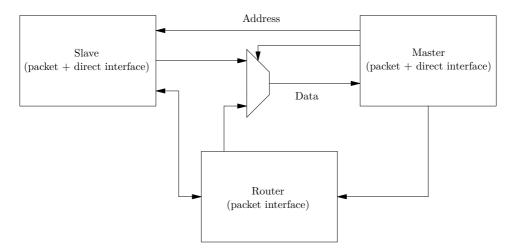

|    |      |                         | ork Packets and Memory Interface     | 35         |

|    |      |                         | er Interface                         | 36         |

|    |      | •                       | -Accurate Router Implementation      | 36         |

|    |      |                         | ork Construction                     | 38         |

|    | 3.3. |                         |                                      | 38         |

|    |      |                         |                                      | 38         |

|    |      | _                       |                                      | 39         |

|    |      |                         | guration                             | 40         |

|    | 3.4. |                         | 5                                    | 40         |

|    | 3.5. | Testing and Verificatio | m                                    | 41         |

| 4. | Eval | uating the SHMAC: N     | Aicro-benchmarks                     | 43         |

|    | 4.1. | -                       | and Notation                         | 43         |

|    | 4.2. |                         |                                      | 46         |

|    | 4.3. |                         |                                      |            |

|    | 4.4. |                         | Performance                          |            |

|    |      |                         |                                      |            |

|    |      | 0                       | ers                                  | 53         |

|    | 4.5. | -                       | cal Fetch                            | 54         |

|    | 4.6. | -                       | ·····                                | 56         |

| F  | lass | waving the SUMAC        |                                      | 60         |

| э. |      | roving the SHMAC        | Poutor Burbass                       | <b>6</b> 0 |

|    | 0.1. |                         | Router Bypass                        |            |

|    |      | J.I.I. Description .    |                                      | 61         |

|     |        | 5.1.2.  | Evaluation and Results                                | 62 |

|-----|--------|---------|-------------------------------------------------------|----|

|     | 5.2.   | System  | Register File                                         | 64 |

|     |        | 5.2.1.  | Description                                           | 64 |

|     |        | 5.2.2.  | Evaluation and Results                                | 66 |

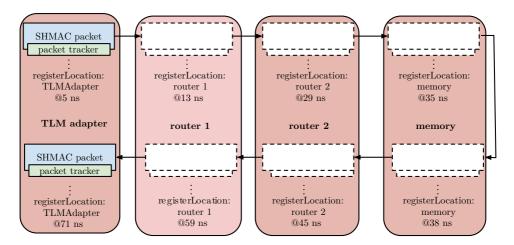

|     | 5.3.   | Packet  | Tracking                                              | 67 |

|     |        | 5.3.1.  | Description                                           | 67 |

|     |        | 5.3.2.  | Results                                               | 68 |

| 6.  | Con    | clusion | and Future Work                                       | 70 |

|     | 6.1.   | Conclu  | sion                                                  | 70 |

|     | 6.2.   | Future  | Work                                                  | 71 |

|     |        | 6.2.1.  | Power Modelling                                       | 71 |

|     |        | 6.2.2.  | ELF Parsing                                           | 72 |

|     |        | 6.2.3.  | GDB Support                                           | 73 |

|     |        | 6.2.4.  | Dynamic Model Switching                               | 73 |

|     |        | 6.2.5.  | Packet Tracking                                       | 74 |

|     |        | 6.2.6.  | Improvements to the SHMAC Architecture                | 75 |

|     |        |         | 6.2.6.1.~ A Faster, Pipelined Router Implementation . | 75 |

|     |        |         | 6.2.6.2. Integrating a System-Wide Bus                | 75 |

|     |        |         | 6.2.6.3. Core Diversity and Accelerators              | 76 |

| Bil | oliogr | aphy    |                                                       | 78 |

| Α. | Appendices                                              | 84 |

|----|---------------------------------------------------------|----|

|    | A.1. SHMACsim Utility Scripts                           | 84 |

|    | A.1.1. shmacsim-archc-compile                           | 84 |

|    | A.1.2. shmacsim-archc-allcompile                        | 85 |

|    | A.1.3. shmacsim-run-benchmarks                          | 86 |

|    | A.2. Micro-benchmark Listings                           | 87 |

|    | A.2.1. Clock Tile Access Time                           | 87 |

|    | A.2.2. Tile Start-Up Delays                             | 89 |

|    | A.2.3. Pure Memory R/W Performance - Single Master      |    |

|    | A.2.4. Pure Memory R/W Performance - Multiple Masters . | 93 |

|    | A.2.5. Remote Impact on Local Fetch                     | 95 |

|    | A.2.6. Lock Time Acquisition                            |    |

# List of Figures

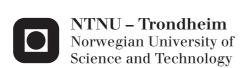

| 1.1.  | History of single-threaded integer performance .        | <br>• | · | • | • | • | 2  |

|-------|---------------------------------------------------------|-------|---|---|---|---|----|

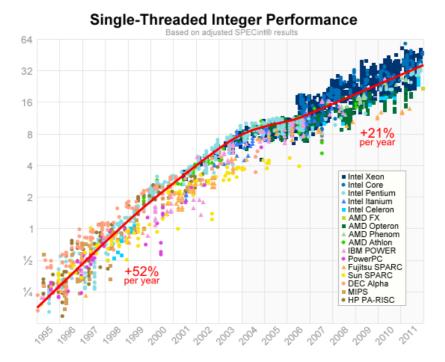

| 2.1.  | Comparison of multi-cores                               |       |   |   |   |   | 10 |

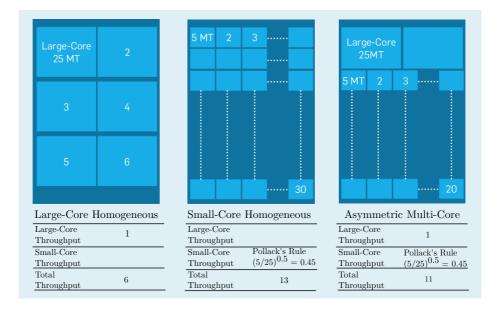

| 2.2.  | Bus versus Network-on-Chip                              |       |   |   |   |   | 13 |

| 2.3.  | ARM big.LITTLE memory hierarchy                         |       |   |   |   |   | 15 |

| 2.4.  | High-level SHMAC overview                               |       |   |   |   |   | 16 |

| 2.5.  | SHMAC Memory Layout                                     |       |   |   |   |   | 16 |

| 2.6.  | Modelling abstraction terminology                       |       |   |   |   |   | 20 |

| 2.7.  | gem5 speed vs accuracy spectrum                         |       |   |   |   |   | 21 |

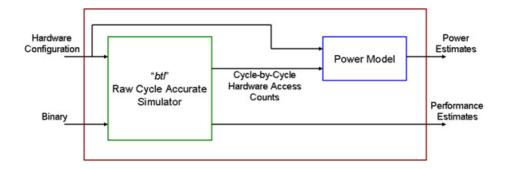

| 2.8.  | Graphite high-level architecture                        |       |   |   |   |   | 23 |

| 3.1.  | SHMACsim overview                                       |       |   |   |   |   | 30 |

| 3.2.  | SHMACMaster components                                  |       |   |   |   |   | 31 |

| 3.3.  | Routing steps                                           |       |   |   |   |   | 37 |

| 3.4.  | Configuration System                                    | <br>• | • | • | • | • | 39 |

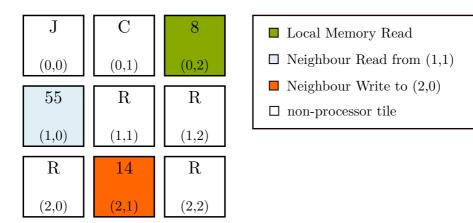

| 4.1.  | Benchmark notation                                      |       |   |   |   |   | 45 |

| 4.2.  | Clock tile access time benchmark configuration .        |       | • |   | • | • | 46 |

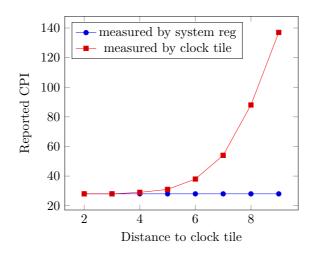

| 4.3.  | Clock measurement skew                                  |       | • |   | • | • | 47 |

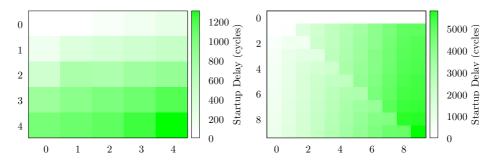

| 4.4.  | Startup delays in $5 \times 5$ and $10 \times 10$ grids |       |   | • |   |   | 48 |

| 4.5.  | Pure mem R-W performance benchmark                      |       |   |   |   |   | 50 |

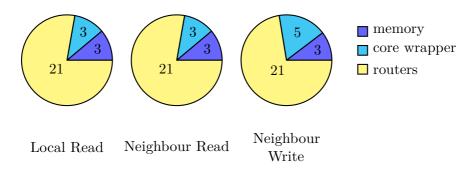

| 4.6.  | Instruction fetch breakdown                             |       | • | • | • | • | 52 |

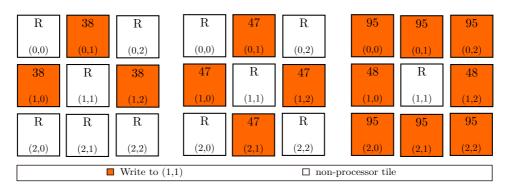

| 4.7.  | Multiple master read micro-benchmark                    |       | • |   | • | • | 53 |

| 4.8.  | Multiple master write micro-benchmark $\ldots$ .        |       |   | • | • | • | 53 |

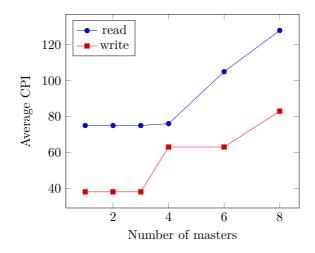

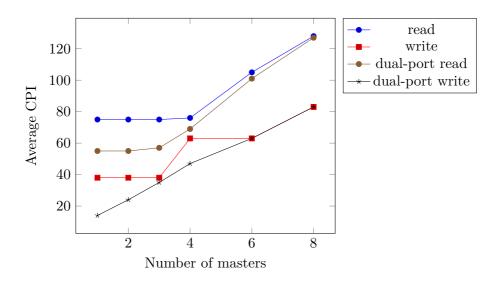

| 4.9.  | Multiple master read-write comparison                   |       |   |   |   |   | 54 |

|       | Remote Read Impact on Local Fetch 1-2-4                 |       |   |   |   |   | 55 |

|       | Remote Write Impact on Local Fetch 1-2-4                |       |   |   |   |   | 55 |

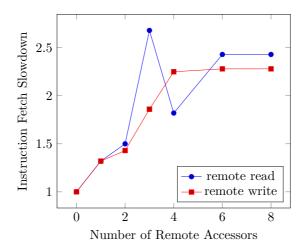

|       | RILF slowdown                                           |       |   |   |   |   | 56 |

| 4.13. | LL/SC lock acquisition flow                             |       | • | • | • | • | 57 |

|       | Lock Acquisition Time Measurement Configuration         |       |   |   |   |   | 58 |

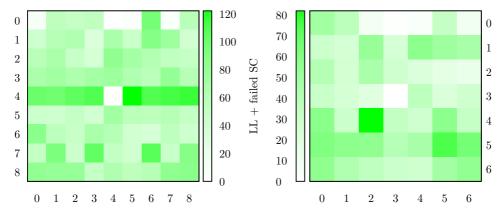

| 4.15. | Heat map of LL/SC failures                              | <br>· | • | • | • | • | 59 |

| 5.1.  | Dual-Port RAM overview                                  |       |   | • |   |   | 61 |

| 5.2. | Example router bypass implementation                     | 62 |

|------|----------------------------------------------------------|----|

| 5.3. | Single Master Pure Memory Read-Write with dual-port RAM  | 63 |

| 5.4. | Comparison of multiple master read-write with single and |    |

|      | dual-port RAM                                            | 63 |

| 5.5. | System Register File                                     | 65 |

| 5.6. | Packet tracking                                          | 67 |

| 5.7. | Example packet trace                                     | 69 |

| 6.1. | TileWattch concept                                       | 72 |

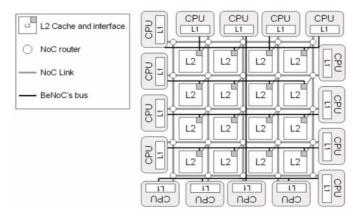

| 6.2. | Overview of a BENoC-based CMP system                     | 76 |

# List of Tables

| 1.1. | List of Contributions                        |

|------|----------------------------------------------|

| 2.1. | TI OMAP4470 cores                            |

| 2.2. | SHMAC prototype tile types 17                |

| 3.1. | Chosen abstraction levels                    |

| 3.2. | Notation and symbols for Simulator Design 31 |

| 3.3. | Implemented tile types                       |

| 4.1. | Overview of implemented micro-benchmarks     |

| 4.2. | micro-benchmark kernel descriptions          |

| 4.3. | Pure memory R/W results                      |

| 4.4. | Pure memory R/W CPI breakdown 51             |

| 5.1. | System registers                             |

# List of Abbreviations

**AMP** Asymmetric Multi-Core Processor **AT** Approximately Timed **BFM** Bus Functional Model **CA** Cycle Accurate **CPI** Cycles Per Instruction **CPU** Central Processing Unit **DSP** digital signal processor **EECS** Energy Efficient Computing Systems **ELF** Executable and Linkable Format **FPGA** Field-Programmable Gate Array **FPU** Floating Point Unit **GCC** GNU Compiler Collection **GDB** GNU Debugger **GPGPU** General-Purpose Graphics Processing Unit **HDL** Hardware Description Language **HMP** Heterogeneous Multi-Core Processor **ILP** instruction-level parallelism **ISA** Instruction Set Architecture LL Load Linked LL/SC Load Linked/Store Conditional LT Loosely Timed

**NUMA** Non-Uniform Memory Access

OS Operating System RILF Remote Impact on Local Fetch RTL Register Transfer Level SAM System Architectural Model SC Store Conditional SHMAC Single-ISA Heterogeneous Many-core Computer SHMACsim SHMAC Simulator SIMD Single Instruction Multiple Data SMP Symmetric Multi-Core Processor SoC System on a Chip TLM Transaction-Level Modelling TLP task-level parallelism TSV Through-Silicon Via U-core unconventional core

**UT** Untimed

# 1. Introduction

Since the birth of computers, the electronics and computer industries have strived forward to construct devices with more computing power. The capability to integrate an ever increasing number of transistors onto the same area, commonly referred to as "Moore's Law" [56], has led to dramatic improvements in terms of computing power. However, taking advantage of this increase in transistor count to deliver more performance is becoming increasingly difficult. In order to understand the need for heterogeneous computing, it is necessary to understand the historical trend in the development of computing power, and why the same trend is unlikely to continue.

### 1.1. Historical Trends in Computing Power

Central Processing Units (CPUs) have come a long way since their invention. As can be observed in Figure 1.1, the period 1995–2004 saw a doubling of single-threaded integer operation performance every two years. The increase in the number of transistors was utilized by processor designers to allow faster execution in a single processor core. Transistors that could run faster and deep pipelines with many stages, which could run at higher clock frequencies, were the driving forces behind this trend [13]. More transistors in the core made it possible to construct complicated hardware such as instruction reordering engines to exploit instruction-level parallelism, and branch predictors to avoid pipeline flushing penalties.

However, also visible in Figure 1.1 is a drop in the increase of performance after 2004. Sutter [59] attributes this to problems arising from the physical nature of shrinking transistor technology, namely power consumption and high heat production. Indeed, the increase in transistor density (as predicted by Moore's Law) does not translate to performance gains if the transistors cannot be powered. The lower power requirements of downscaled transistors (also known as "Dennard scaling") described by Dennard et al. [20] has made it possible to power the increasing number of transistors while keeping the energy and cooling budgets fixed. Unfortunately, the sub-130 nm transistor

Figure 1.1.: Historical trend of single-threaded integer operation performance. Reproduced from [49]

dimensions have brought an end to Dennard scaling [35]. Further scaling down of the transistor dimensions and threshold voltage causes increased leak current, whose impact on power becomes even larger due to exponentially increasing transistor count. This means it is no longer possible to power more transistors without either increasing the power budget or leaving parts of the chip unpowered (called the "dark silicon" [22] effect).

It is undesirable to increase the power budget seeing that data centers accounted for 1.1-1.5 % of global power usage in 2010 [34] and the impact of ICT on the environment is already significant [47]. Another reason would be the energy sensitivity of the mobile computing devices such as smartphones and tablets, which are becoming more popular [24] – a mobile device consuming several watts of power would suffer from overheating and have a rather short battery life. Borkar and Chien [13] predict that energy will be the key limiter of performance for the next 20 years, and point to large-scale parallelism and heterogeneous computing for the solution.

# 1.2. Era of Multi-Cores: Symmetric, Asymmetric and Heterogeneous

The limitations brought by power and heat ushered the trend of multi-core processors. Intel Corporation [62] name heat production, power, memory latency and RC delay to explain their move to multi-core architectures. Another motivation for the move to multi-cores is the limited amount of instruction-level parallelism (ILP) available in typical applications. Wall [65] reports the median parallelism for a mix of real-life programs and benchmarks that can be exploited with practical hardware as 5; investing further resources into single-core CPUs capable of more ILP would have limited performance benefits. Instead, integrating N processor cores onto the same die can offer a theoretical N times increase in computing power, provided that the applications are able to exploit task-level parallelism (TLP) by the way of either using multiple threads, or running multiple applications simultaneously. Replicating an existing core multiple times to form a more powerful processing unit is also appealing in terms of reusing engineering resources. The name Symmetric Multi-Core Processor (SMP) [23] reflects the identical nature of each processing core on this type of processor.

The energy-sensitive nature of mobile computing devices such as smartphones and tablets has given rise to another type of multi-core processor, the Asymmetric Multi-Core Processor (AMP) [23]. These processors typically include some simple cores for performing computationally non-intensive tasks and some powerful cores for tasks with high performance requirements. This mapping of tasks to cores has the potential to increase energy efficiency without sacrificing performance.

However, while the move to symmetric multi-cores has helped to uphold the performance growth demands and asymmetric multi-cores promise more energy efficiency, the problem of dark silicon still lurks on the horizon. Esmaeilzadeh et al. [22] argue that the failure of Dennard scaling will continue to plague multi-core designs, forcing 21 % of the transistors in a fixed-size 22 nm chip to be powered off, regardless of core asymmetry and topology. Therefore, in order to keep utilizing the increase in transistor count for higher computational power, it is of utmost importance to achieve better energy efficiency.

This is where *Heterogeneous Multi-Core Processors (HMPs)* have the potential to carry the flag further. Similar to an asymmetric multi-core, a heterogeneous multi-core processor can contain regular cores of different sizes, but it can also so-called *unconventional cores (U-cores)* [16]. These U-cores can range from vector processors to application-specific accelerators, General-Purpose Graphics Processing Units (GPGPUs) or programmable logic such as Field-Programmable Gate Arrays (FPGAs). The primary advantages of such a mix of hardware in the face of dark silicon challenges are twofold:

- Different cores and accelerators can be powered on or off according to the processing requirements of the current task. This selective powering can ameliorate the dark silicon limitations.

- Customized U-cores can perform specific types of computation with higher energy efficiency than pure software solutions running on general purpose cores [64] which can contribute significantly to the overall energy efficiency of the system.

Chung et al. [16] conclude that U-cores are very likely to find their way into future processors. Indeed, heterogeneous system-on-a-chip solutions in the form of mobile application processors and microcontrollers are already quite widespread in the embedded systems market and demonstrate the energy efficiency potential [30, 37, 50].

## 1.3. EECS and the SHMAC project

Established with the goal of improving energy efficiency in computing at different levels of abstraction, the Energy Efficient Computing Systems (EECS) strategic research area at the Norwegian University of Science and Technology has heterogeneous computer architectures as one of its primary research foci. Despite the rising popularity of the topic in the computer architecture community, two primary research questions still remain unanswered:

Heterogeneous Hardware: How should a heterogeneous processor architecture be designed in terms of core composition, accelerators, interconnect and memory system?

Heterogeneous Software: Given a heterogeneous processor architecture, how should application and system software be designed to obtain maximum energy efficiency?

The SHMAC project was initiated by the EECS to help discover the answers to these questions. The goal of the project is to develop a heterogeneous architecture which in turn will be utilized for heterogeneous software research. Important aspects of the architecture are covered in Section 2.3. A prototype for the SHMAC using reconfigurable logic has already been developed by Rusten and Sortland [54]. However, while the FPGA prototype remains a valuable tool for evaluation, the heterogeneous design space is too large to be quickly explorable by such an approach, since it is necessary to model each desired component in an Hardware Description Language (HDL). This is why SHMAC Simulator (SHMACsim) is also necessary for the SHMAC project; simulators are much more suitable for evaluating a large number of coarse-grained policies, which then can be evaluated in detail by the FPGA implementation.

## 1.4. Assignment Interpretation

Based on the assignment description text, the following main tasks were identified:

**Task 1:** *(mandatory)* Create a cycle-accurate simulation infrastructure that reflects the SHMAC architecture

**Task 2:** *(mandatory)* Implement a set of micro-benchmarks that stress the important aspects of the architecture, and interpret the results

Task 3: *(optional)* Suggest and evaluate improvements to the SHMAC architecture

Fulfilling these tasks will in turn help answer the following research questions:

- ${\bf RQ1}~{\rm How}$  should the SHMAC architecture be modelled in a software simulator?

- **RQ2** What sort of benchmark programs can be utilized to identify major bottlenecks in the SHMAC architecture?

- ${\bf RQ3} \quad {\rm How \ can \ the \ shortcomings \ of \ the \ SHMAC \ architecture \ and \ the \ current \ implementation \ be \ remedied?}$

As the infrastructure to be provided as part of Task 1 is intended to serve as a research tool for continued investigations of the EECS into heterogeneous multi-core architectures, requirements and design guidelines have been further elaborated via discussions with the research group. These are summarized below.

- Cycle Accuracy: SHMACsim must be able to accurately reflect the complex interactions between multiple cores. The difference in cycle-based performance statistics should be less than 10 % between the simulator and the FPGA prototype. High simulation performance is not a primary goal at this point and sacrificing simulated performance for higher accuracy is deemed acceptable.

- **Configurability:** SHMACsim should be structured in a way that allows easy creation and evaluation of desired heterogeneous models via a flexible configuration system.

- Modelling capabilities on multiple abstraction levels: EECS aims to improve the energy efficiency of computing systems at all abstraction layers of a computing system. Therefore, flexible tools that are not bound to a particular layer of abstraction are desirable.

- Maintainability and extensibility: As the beginnings of a research tool, it is important that SHMACsim is easy to maintain and extend for future research. Clean interfaces, modular structure and well-commented code are important towards this.

It is worth mentioning here that the SHMAC is a dynamic research project, and development continued in parallel with SHMACsim. SHMACsim as presented in this report is not intended to and does not reflect the state-of-the-art SHMAC architecture, but rather the FPGA prototype. For instance,

the cores in SHMAC have been changed from MIPS to ARM Instruction Set Architecture (ISA) while SHMACsim was still in development, which could not be reflected in the simulator due to time constraints.

## 1.5. Contributions

This work makes contributions to the SHMAC project in three main areas, in connection with the three tasks defined in the assignment text. A complete list of contributions is provided in Table 1.1.

## 1.6. Report Organization

The organization of the report into individual chapters is briefly described for the reader's convenience:

- Chapter 1: Introduction gives a brief introduction to the trends in processor design and describes the motivations behind the SHMAC and SHMACsim.

- Chapter 2: Background describes the main concepts in heterogeneous processor and simulator design, as well as related work on these subjects by other authors.

- Chapter 3: The SHMAC Simulator Infrastructure goes into the details of SHMACsim's design and the influencing factors on design decisions, and how it was tested and verified against the FPGA prototype.

- Chapter 4: Evaluating the SHMAC: Micro-benchmarks introduces a description of implemented benchmarks and the results obtained from their execution.

- Chapter 5: Improving the SHMAC contains a set of proposed improvements based on this discussion, and their performance impact.

- Chapter 6: Conclusion and Future Work provides the concluding remarks and propositions for future work on carrying SHMACsim further.

| Task | $\mathbf{Section}(\mathbf{s})$ | Description                                                                                   |

|------|--------------------------------|-----------------------------------------------------------------------------------------------|

| T1   | 3.2                            | A SystemC/C++ model of the SHMAC, cycle ac curate to within 5% of the FPGA prototype          |

| T1   | 3.2.1                          | An ArchC-generated MIPS core model extended with LL/SC instructions                           |

| T1   | 3.2.1.1                        | A TLM adapter for ArchC core integration into<br>SHMAC tiles                                  |

| T1   | 3.4                            | A set of utilities to compile C applications for a given tile coordinate for ArchC MIPS cores |

| T1   | 3.3.1                          | A centralized system for defining and constructing tile types                                 |

| T1   | 3.3                            | A configuration system for tile layout and runtime parameters                                 |

| Τ2   | 4.3                            | A micro-benchmark to measure start-up delays due to the jump tile                             |

| Τ2   | 4.2                            | A micro-benchmark to measure effects of traffic or clock tile-based timing                    |

| Τ2   | 4.4.2                          | A micro-benchmark to measure the effects of sharing<br>a RAM tile between multiple masters    |

| Τ2   | 4.5                            | A micro-benchmark to measure performance impact<br>of remote memory accesses on local cores   |

| Τ2   | 4.6                            | A micro-benchmark to test synchronization of large grids with the LL/SC tile $$               |

| Τ3   | 5.1                            | A dual-port RAM implementation in software to increase local memory performance               |

| Т3   | 5.2                            | A system register file implementation to provide<br>per-tile bootstrapping and clock counting |

| Τ3   | 5.3                            | A packet tracker implementation to instrument<br>memory packet route information in time      |

Table 1.1.: A list of contributions provided by this work, in relation to the corresponding tasks from 1.4.

# 2. Background

The design of HMPs is a broad field encompassing a number of different subfields including the design of processing cores, interconnect and the memory system. In order to have a better understanding of the heterogeneous nature of the SHMAC, it is beneficial to examine these sub-fields to some extent.

In this chapter, the reader is provided with an overview of the background concepts and related work surrounding HMP design. A summary of the SHMAC architecture is also presented. This is followed by a section on computer architecture simulators, introducing the simulation technology background SHMACsim draws on.

## 2.1. The Motivation for Heterogeneous Multi-Cores

As explained in Chapter 1, the primary motivation for the move to HMPs is their potential for higher energy efficiency in the face of dark silicon challenges, while still offering improved performance. This section aims to provide some insight into the analytical models and empirical examples justifying these claims regarding heterogeneous multi-cores.

As HMPs can be thought of as asymmetric multi-cores with U-cores, one can start by looking at the analytical foundations for AMPs. These can be based on three so-called "laws":

- Amdahl's Law describes the maximum theoretical possible speed-up limit obtainable for an application via parallel execution given its parallelizable portion [3]. It draws the primary conclusion that massively parallel execution of applications is of limited benefit, since inherent sequential portions in the application limit the performance improvement.

- *Gustafson's Law* is essentially a reinterpretation of the same relationship Amdahl's Law describes. However, Gustafson [27] pointed out that despite the limitations imposed by serial portions, the speed-ups

Figure 2.1.: Comparison of 150 million transistors integrated into three different multi-core layouts. Adapted from [13]

brought by massively parallel execution can also be utilized to attack larger problem sizes, which otherwise would be impractical due to long execution times.

• *Pollack's Rule* theorizes that there is a direct proportion between performance improvements from a microprocessor and the square root of the amount of transistors used for improving that processor's micro-architecture [48]. Thus, one can make a rough estimate the total available computing power given a number of transistors and how they are to be allocated into different cores.

Figure 2.1 presents an comparison of three possible multi-core configurations given 150 million transistors, with the throughput of each core estimated using Pollack's Rule. Although the small-core homogeneous layout has greater total throughput than the others, the limited degree of parallelism available in most applications (as suggested by Amdahl) will limit the possible speedup. The AMP is able to offer a better compromise thanks to its mix of core types. Fedorova et al. [23] suggest that an AMP system can offer better performance and minimize power usage by executing the sequential and parallel phases of the application on large and small cores, respectively.

In addition to the benefits of AMPs, HMPs have the advantage of containing specialized U-cores. These specialized cores and accelerators can have up to two orders of magnitude higher energy efficiency [16, 57] and can be selectively powered on or off depending on the task at hand. This selective powering allows an HMP to trade dark silicon area for increased performance and energy efficiency. Borkar and Chien [13] refer to this as the "Rise of 10x10 Optimization": operating the chip with 90 % of the transistors inactive, and a different 10 % active at each point in time.

## 2.2. Hardware for Heterogeneous Multi-core Processors

#### 2.2.1. Core Types and Accelerators

The types and features of processor cores and accelerators to be included on an HMP is a major determinant in the system's final capabilities. Many different processor cores and accelerators have been designed over the history of computing, and an HMP's ability to combine several of them into a single system increases the size of the design space to vast proportions. The question of which cores and accelerators to use is to some extent answerable within a given application area, but is much tougher for general purpose HMPs.

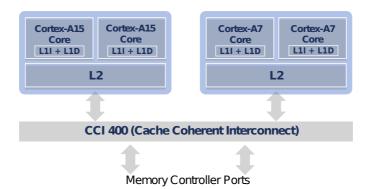

In terms of asymmetric general-purpose core mixes, both Kumar et al. [36] and Van Craeynest & Eeckhout [63] argue that two core sizes provide most benefits from heterogeneity. This mix of cores (usually referring to core types as "big/powerful" and "small/simple") can also be found in the industry; both ARM's big.LITTLE [26] (depicted in 2.3) and NVIDIA's Kal-El [45] are such examples.

Besides general-purpose cores, two rising trends in HMP design in the industry are the inclusion of media processing elements and GPGPUs for parallel processing. The Texas Instruments OMAP4470 System on a Chip (SoC) whose the range of computing elements is displayed in Table 2.1 is such an example. This range of core types can offer the benefits of asymmetric multi-cores in terms of general purpose computing, as well as energy efficient multimedia processing with the DSP and accelerator hardware. Similar HMPs are widely used in power sensitive computing devices such as smartphones and tablets [50, 55].

| Name           | Core Type                          | Core Count |

|----------------|------------------------------------|------------|

| ARM Cortex A9  | general purpose (high performance) | 2          |

| ARM Cortex M3  | general purpose (energy efficient) | 2          |

| PowerVR SGX544 | graphics processing unit           | 4          |

| IVA-HD         | still image and video accelerator  | 1          |

| mini-C64x+     | digital signal processor           | 1          |

Table 2.1.: List of cores in a Texas Instruments OMAP4470 SoC [30]

Beyond these core types, there has also been research on including less conventional cores and hardware accelerators onto HMP dies. These include energy-efficient conservation cores [64] auto-synthesized from application source code, database indexing accelerators [32] and hardware web browsing [7], among others. Last but not least, there is substantial work on reconfigurable computing where FPGAs or similar reconfigurable hardware is utilized to dynamically create datapaths suited for the task at hand [28]. Chung et al. [16] suggest that such hardware is broadly useful if energy efficiency is a primary goal and is likely to be part of future HMP designs.

#### 2.2.2. Interconnect

Interconnect has a critical role in HMP system design. For instance, many modern personal computers also contain heterogeneous processing elements such as GPUs, but the external nature of the GPU and the bus that connects it to the rest of the system gives rise to large delays while copying data from/to these units, creating bottlenecks. In contrast, an HMP contains the computing units and the interconnect on the same chip, allowing higher-speed communication between them.

The traditional bus is based around the idea of connecting multiple devices to a global shared medium. However, semiconductor technology scaling has brought severe limitations to this approach: global synchronization problems, deep submicron effects and power/thermal management [6]. Additionally, the increasingly larger number of devices connected to a global bus introduces additional verification difficulties. The proposed solution to shared-medium bus problems is one inspired from network engineering: a *Network on Chip*. A traditional bus-based interconnect and a NoC are illustrated in Figure

Figure 2.2.: A shared bus based multi-core on the left, and one organized as a mesh-based NoC on the right. Adapted from [67].

2.2, where processing elements (PE) in the NoC are connected by routers and network links, and data is transferred in the form of network packets. By exposing a common high-level interface to all connected units, the NoC can offer a well-structured system with increased productivity and scalability, while still being able to maintain a high-performance communication infrastructure. The TILE64 processor [1] utilizes such networks to connect modular tiles and scale up to 64 cores.

The design and implementation of such a network is an active research area [5, 19] and a complex topic involving design decisions on many levels. Bjerregaard and Shankar [10] investigate these issues with a layered approach in their survey of NoC research and practices, which are briefly summarized below:

- The **Application Level** is concerned with the decoupling of nodes from the network, which allows a modular design approach by abstracting away the details of communication.

- The **Network Level** covers issues dealing with the structure of the network and the movement of data packets inside, such as:

- Topology, the layout of the network with routers and nodes. 2D grid topologies are by far the most popular.

- Protocol, the strategy of moving data through the NoC. Store and forward, virtual cut-through and wormhole routing are widely known, with wormhole routing being the most popular [10].

- Flow control, the mechanism determining packet movement along a network path. Virtual channels (VCs) are widely utilized to avoid deadlock.

- Other features. Quality of Service (QoS) may be offered for realtime guarantees, broadcast/multicast for mass communication, or more complex operations such as test-and-set for synchronization.

- The **Link Level** regards to node-to-node links and covers a wide range of issues including cross-clock-domain synchronization, pipelining long channels, low-swing drivers to optimize power consumption, and reliable encoding schemes.

#### 2.2.3. Memory

The location of data with respect to a given processing unit that desires to access this data is a major performance determinant – without sufficiently fast data access, a set of heterogeneous computing elements will be of little benefit. Two principal approaches to the design of a multi-core memory system are *shared memory* (coupling all cores to a shared/central memory) and *distributed memory* (coupling each core with its own memory unit), although hybrid approaches are common as well. A body of research on memory system designs for multiple computing units was produced in the late 1980s – albeit for multi-chip (as opposed to multi-core on a single chip) systems, some of the results also apply to multi-core designs since the underlying ideas are similar.

Nitzberg and Lo [44] mention that the primary advantage of a shared memory system is the relative straightforwardness of its design and programmability. However, it has a serious scalability drawback due to the serialization point brought by the common access bus. Distributed memory can offer much higher total bandwidth and does not suffer from this bottleneck, which make it better suited to multi-core systems. In turn, distributed memory is not as straightforward to program as a shared memory architecture.

While using a NoC as described in Subsection 2.2.2 helps address the design challenges for distributed memory, the programming difficulties require additional undertakings. This is commonly addressed by building a shared memory abstraction on top of distributed memory. Referred to as *distributed shared memory*, it entails constructing a coherence mechanism in either

Figure 2.3.: Memory hierarchy in ARM's big.LITTLE AMP solution, with per-cluster L2 cache and per-core L1 cache. Adapted from [26].

hardware or software, and exposing a consistency model to the programmer [44].

Memory systems in many multi-cores today, both in the academy [25, 61] and the industry [1, 26], utilize a hybrid model where distributed memory is mostly found in the form of private caches. Such caches deliver bandwidth with higher scalability to multiple cores, although their performance is bound by memory reference locality. With the developments in 3D integration and Through-Silicon Via (TSV) techniques, efficient and large on-chip distributed memory implementations [38] are becoming possible. This may be important for keeping up with the bandwidth and latency demands of memory-hungry many-core chips.

## 2.3. The SHMAC Architecture

As the SHMAC architecture constitutes the base for the construction of SHMACsim, it is important to give an overview of the architecture in order to have a better understanding of SHMACsim. A one-sentence description of the architecture would be *heterogeneous computing elements and distributed memory organized into tiles with a mesh NoC interconnect.* This high-level description has been elaborated by Rusten and Sortland [54] to create the initial FPGA-based prototype, and the rest of this section will be a summary of their work, on which SHMACsim is also based.

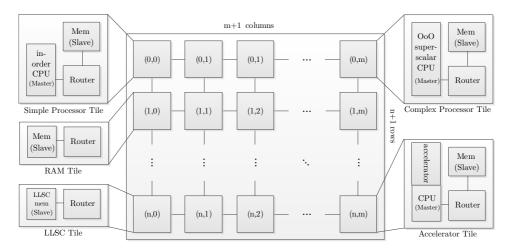

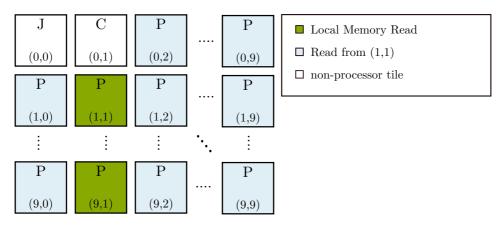

Tile internal organization: Each tile contains a router, and can contain master and/or slave units, as illustrated in Figure 2.4. A master unit is

Figure 2.4.: An overview of a SHMAC mesh with a variety of tile types. Tile types and placement are solely for purposes of illustration and do not necessarily reflect a realistic scenario.

| (0,0)      | (0,1)        | (0,m)                                                    | (1,0)          | (n,m)        |  |

|------------|--------------|----------------------------------------------------------|----------------|--------------|--|

| 0x00000000 | 0 - 0 x01000 | $ \begin{array}{c}                                     $ | 0000 0 0 10000 | 000 0 xnm000 |  |

Figure 2.5.: The SHMAC global memory layout, showing the address space partitions for each tile. The most significant 16 bits represent the tile coordinate, whereas the remaining 24 bits act as the local address. Reproduced from [54].

defined as a unit initiating memory requests, and a slave unit is similarly defined as a unit handling memory requests. CPU cores and memory would be typical examples for master and slave units, respectively. The router is responsible for communication between the master and slave units, as well as other tiles. An overview of implemented tile types for the prototype can be found in Table 2.2.

**Memory:** The global address space is partitioned according to tile coordinates, and each tile's slave unit (if any) is mapped to one, as shown in Figure 2.5. No memory protection is implemented and tiles have free access to each other's address spaces. For tiles containing processors, the program to be executed is loaded into the local tile memory. The prototype does not include any cache memory, making the performance highly sensitive to access patterns.

| Tile Type                     | Master        | Slave                       | Purpose                                           |

|-------------------------------|---------------|-----------------------------|---------------------------------------------------|

| Integer Processor Tile        | mlite         | RAM                         | general purpose, integer computations             |

| Floating Point Processor Tile | mlite<br>+FPU | RAM                         | general purpose, float-<br>ing point computations |

| RAM Tile                      | none          | RAM                         | random access memory                              |

| LL/SC Tile                    | none          | LL/SC unit                  | synchronization                                   |

| Jump Tile                     | none          | jump<br>unit                | bootstrapping proces-<br>sors                     |

| Clock Tile                    | none          | $\operatorname{clock}$ unit | measuring execution times                         |

| LED Tile                      | none          | LED<br>control<br>unit      | LED output                                        |

| UART Tile                     | none          | UART<br>unit                | communicating with<br>the external world          |

Table 2.2.: Tile types implemented in [54]

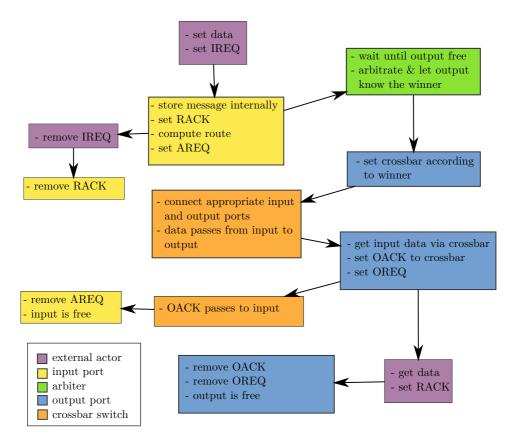

**Interconnect:** The interconnect is responsible for carrying memory requests and responses across units and tiles. A packet-switched NoC is used, with each memory response or request encapsulated into a network packet. The packet format contains information about the nature of the memory operation (request or response), read/write and interrupt/sync flags, the initiator and target of the memory request, and any associated data. The utilized router model is non-pipelined with per-output-port round robin arbitration, and uses dimension order routing. The reader is referred to sections 4.1 and 4.2.3 of [54] for further details.

**Processor cores and ISA:** The SHMAC FPGA prototype used the mlite core [52] configured with a two-stage pipeline, which uses the MIPS-I ISA. In order to support synchronization, the ISA was extended with the Load Linked (LL) and Store Conditional (SC) instructions. Additionally, a version of the mlite core extended with a floating point unit was provided. The cores were wrapped into a state machine for integration with the SHMAC network interface. This state machine allows a single outstanding memory request; the core is stalled for read requests or LL/SC instructions, but not for write requests.

## 2.4. Computer Architecture Simulators

Having introduced some of the background concepts in heterogeneous multicore architectures, it is also interesting to examine the role simulators in exploring HMP design. Computer architecture simulators allow the exploration of the architectural design space and evaluation of design decisions at a relatively low cost. Their primary advantage comes from the ability to create abstract models of the desired architecture and execute this model in a controlled environment. This modelling and execution environment is usually completely in software, although FPGA-accelerated simulation (discussed in 2.4.3) is also gaining momentum.

A brief overview of the underlying concepts in computer architecture simulation and related work will be presented here. Throughout the rest of this section the term *target* refers to the machine being simulated, while *host* refers to the machine running the simulation, which is common terminology for computer architecture simulators [43, 60].

#### 2.4.1. Categorization of Simulators

A number of simulators are used in computer architecture research and related fields, and it can be useful to generalize some aspects of these simulators into categories in order to have a better understanding.

**Scope:** The simulation targets can vary widely in scope, from the microarchitecture of a single core to multiple interconnected cores and memory units. Full-system simulators capable of booting an Operating System (OS) also exist [8, 39].

Workload type: Simulators can accept different types of input, the two main types being *trace-driven simulators* which run on pre-recorded or generated streams of events, and *execution-driven simulators* which allow execution of software. Trace-driving has the advantage of offering a greater degree of control but the inputs first have to be generated and may be very large in size. Execution-driven simulation has a size advantage, and generating new workloads is faster since the target programs may already exist. Additionally, execution-driven simulation can capture dynamic interactions between instruction streams in multiple processors [18].

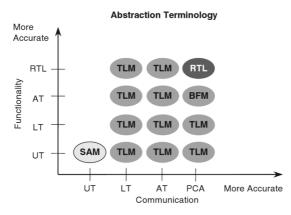

Level of detail: All simulators use a model of the simulation target. The level of detail of this model is the most defining characteristic of a simulator, with great impact on the performance and accuracy of the simulation. While it is difficult to precisely specify the level of detail/abstraction for a model, the degree to which elapsed simulation time is modelled is a helpful classification. The IEEE 1666 standard [29] defines the following:

- **Untimed (UT)**: The notion of simulation time is unused. UT models are used for the construction of *purely functional* models.

- Loosely Timed (LT): Each transaction has two timing points; the start and the end. Simulated processes may be temporally decoupled from simulation time.

- Approximately Timed (AT): Each transaction has multiple timing points, simulated processes typically run in lockstep with simulation time.

- Cycle Accurate (CA), also called Pin and Cycle Accurate (PCA): Simulation time is modelled with cycle-level accuracy.

Going down the list, these abstraction levels offer increasing level of detail while sacrificing performance. This trade-off is inevitable since the amount

Figure 2.6.: A classification of abstraction terminology for system models. Reproduced from [11].

of necessary computation increases significantly with increasing level of detail. To find an appropriate fit for the simulation requirements, it may be necessary to mix multiple abstraction levels.

For complex system-level designs with a substantial amount of data exchange between components, it is beneficial to separate the communication domain from the functionality domain. Different abstraction levels can be mixed and matched for the two different domains, which is known as *Transaction-Level Modelling (TLM)*. Figure 2.6 presents an overview of abstraction terminology including TLM, System Architectural Model (SAM), Bus Functional Model (BFM) and Register Transfer Level (RTL) model. As the complexity of processors increase, simulators created with a mix of well-defined levels of abstraction will become important to productivity [11].

#### 2.4.2. Multi-core Simulation

The processor development trends mentioned in Chapter 1 are reflected in simulators. Before the advent of the multi-core era, most simulators were focused on the microarchitecture of a single core to develop faster processors. However, the move to multi-cores required tools to evaluate and validate design decisions and implementations. Simulators today are required to have a wider scope, covering multiple cores, complex memory hierarchies and interconnects.

| Proc          | essor       | Memory System |        |               |  |  |

|---------------|-------------|---------------|--------|---------------|--|--|

| CPU Model     |             | <i>a</i>      | Ruby   |               |  |  |

| CPU Model     | System Mode | Classic       | Simple | Garnet        |  |  |

| A             | SE          | High Speed    |        |               |  |  |

| Atomic Simple | FS          |               |        |               |  |  |

| <b>m</b> :    | SE          |               | <      |               |  |  |

| Timing Simple | FS          |               |        |               |  |  |

| In-Order      | SE          |               |        |               |  |  |

| In-Order      | FS          |               |        |               |  |  |

| O3 (Out of    | SE          | ]             |        |               |  |  |

| Order)        | FS          |               |        | High Accuracy |  |  |

Figure 2.7.: Various processor and memory system models in gem5 with the speed versus accuracy spectrum. Reproduced from [8].

A wide range of computer architecture simulators, both from the industry and the academia, exist today [9, 15, 39, 41, 46]. To give a better understanding of the field in general, two multi-core simulators are briefly discussed below.

#### 2.4.2.1. The gem5 Simulator

A merger of the M5 [9] and GEMS [41] simulators, the gem5 is a simulator widely used for computer architecture research [8]. Since it is not bound to a particular architecture and can instantiate simulations based on different configurations, it is more appropriately called a *simulation framework*. The unmodified Linux kernel can be booted on full-system mode using the ARM, ALPHA and x86 ISAs.

gem5 has a flexible, modular system capable of combining different CPUs, system modes and memory system models to create an appropriate configuration in terms of accuracy and speed, as illustrated in Figure 2.7. The object-oriented nature of the system makes it easy to instantiate multiple cores and there are no inherent limitations on the simulated core count except simulation speed.

- **CPU Model:** Refers to the level of detail for the core model, which can range from *AtomicSimple* always executing an instruction per cycle to *O3*, a detailed out-of-order model.

- System Mode can be either System-call Emulation (SE), which avoids the need for peripheral device models, or Full System (FS) to model an entire system which can run an OS.

- Memory System: refers to the model of memory request-response system, including the fast and easily configurable classic M5 model as well as completely customizable models. For instance, the Garnet [2] models a NoC including router microarchitecture.

- **ISA:** Most commercial ISAs (ARM, ALPHA, MIPS, Power, SPARC, and x86) are supported.

Although gem5 does not inherently target HMPs, there are gem5-based projects [42, 66] targeting heterogeneous systems. These projects make some constraining assumptions regarding the target architecture and seem to be mostly tailored towards CPU+GPGPU systems.

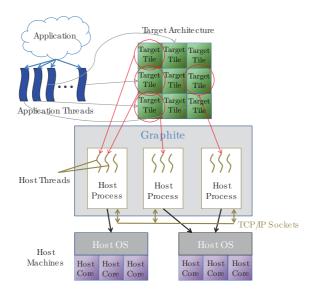

#### 2.4.2.2. Graphite: Distributed Parallel Multi-core Simulation

The origin of the Graphite simulation infrastructure [43] lies in the multi-core simulator scalability problem. The simulation of future processor architectures containing hundreds or thousands of cores will require an enormous amount of computational resources. However, most simulators today are not capable of tackling this task since they have sequential implementations. To address this issue, Graphite provides a parallel, distributed simulation infrastructure that allows functional and performance modelling for cores, on-chip networks and memory systems include coherent cache hierarchies. It is not cycle accurate, but provides good estimates through the use of a collection of models and techniques. A high-level overview of the simulator architecture is presented in Figure 2.8.

As with any kind of parallel application, synchronization is a major problem in multi-core simulation. Even though simulating the multiple cores themselves may appear trivial to parallelise, the need for synchronization arises when these cores interact with each other or with shared resources. Graphite addresses this problem by offering a *lax synchronization* scheme, where synchronization between tiles happens only on explicit events such as application-level locks/barriers, inter-tile message passing and thread spawns/joins. Together with other techniques, this allows almost linear speedup as more host resources are added.

Graphite uses a tile-based target architecture model, where a tile consists of a compute core, a network switch and a part of the memory system (cache and/or DRAM controller). This definition allows for heterogeneity in tiles. Threads on the target application are mapped to tiles and distributed to

Figure 2.8.: High-level architecture of Graphite. Reproduced from [43].

host machine threads. The host threads themselves can be running on a multi-core machine and/or distributed to several machines across a network.

#### 2.4.3. FPGA Accelerated Simulation

Although software-based simulation has carried computer architecture research a long way, their ability to quickly evaluate points in design space may be deteriorating. Tan et al. [60] argue the move to multi-cores has hampered the performance of pure software-based simulators, since multi-core simulation targets exhibit complex timing-dependent non-deterministic behaviour. Such behaviour needs detailed cycle-level simulation, which in turn requires cycle-by-cycle synchronization. Unfortunately this is notoriously difficult to parallelize (to take advantage of multi-core host machines), and as a result simulator performance has suffered.

This "simulation gap" led to *FPGA Accelerated Model Execution (FAME)* techniques, where the desired target architecture is mapped to an FPGA for evaluation [60]. The FPGA's highly parallel, programmable execution substrate is suitable for the nature of multi-core simulation, and can provide an average speedup of 263x over pure software simulators for detailed models. It is important to note here that FAME techniques do not necessarily run the

target hardware RTL description on an FPGA directly; rather, the FPGA executes a model of the target system, so it may take multiple FPGA clock cycles to execute a single target clock cycle.

# 3. The SHMAC Simulator Infrastructure

SHMACsim intends to provide a simulation infrastructure for the SHMAC architecture described in Section 2.3, and reflect the FPGA prototype created by Sorten and Rustland [54] with cycle-accuracy. Its construction is the primary task in this assignment, and forms a basis for evaluating microbenchmarks in Chapter 4 and potential improvements in Chapter 5.

This chapter will provide information about the design of SHMACsim, describing the methodology and reasoning behind development, followed by the structural and behavioural details of the design.

# 3.1. Methodology

#### 3.1.1. Development Basis

The first step in SHMACsim's development was to decide whether it would be built using an existing simulator as a basis or written from scratch. Three alternatives were considered, summarized below with an overview of advantages and disadvantages.

- 1. Customizing an existing simulator would involve taking an existing simulator or simulation framework, such as gem5 [8], and tailoring it to meet SHMACsim's requirements by modifications and additions.

- + A solid, proven basis for work immediately available

- + Reuse of features, modules

- Requires a good understanding of existing simulator structure

- Potentially large amount of unnecessary features/overheads

- 2. Creating a simulator from scratch implies designing SHMACsim completely from the ground-up, without using any external modules.

- + Complete control over simulator structure and features

- + The entire development timeframe can be used on implementation instead of studying existing modules and functionality

- Can take an extensive amount of time to get results

- "Reinventing the wheel", existing components may be already perfectly suitable for SHMACsim's needs

- 3. Limited use of existing components is a "best-of-both-worlds" approach, where some existing modules or libraries would be utilized, and the remaining functionality implemented from scratch.

- + A reasonable degree of control over structure and features

- + The most time-consuming or difficult implementations can be imported as pre-made modules

- Suitable modules must be found

- May need adapter logic to make everything work together

In light of the simulation infrastructure requirements and the advantages/disadvantages of each approach, the third was deemed most suitable. SHMACsim is built mostly from scratch to reflect the nature of the SHMAC accurately, while making use of suitable existing components and libraries.

#### 3.1.2. Choice of Abstraction Levels

As described in Chapter 2, an HMP consists of a number of interacting subsystems, and SHMACsim aims to model these subsystems for the SHMAC architecture. Each subsystem has a different inherent complexity and impact on the overall system performance, which must be taken into account while modelling.

Table 3.1 lists the level of abstraction each subsystem is modelled in, while the rest of this section provides reasoning on the abstraction level choices.

The interconnect is a resource utilized by the entire system and highly parallel in nature, which can give rise to complicated traffic interleaving and resource contention situations. Without an extensive and time-consuming mathematical analysis of the router, simplified models are likely to miss potentially important details. Additionally,

| Subsystem       | Abstraction level   |

|-----------------|---------------------|

| Processor cores | Loosely Timed       |

| Memory          | Approximately Timed |

| Interconnect    | Cycle-Accurate      |

Table 3.1.: Chosen abstraction levels for individual SHMACsim subsystems.Please refer to 2.4.1 details on each abstraction level.

Rusten and Sortland [54] mention the interconnect as the major bottleneck in the SHMAC prototype design. Therefore, a cycle-accurate model of the interconnect is used.

The memory units does not exhibit parallel access characteristics, since each slave unit is only directly accessible by its router. However, the wrapper state machines (which stall the processor cores and convert between SHMAC network packets and memory operations) cause delays that can influence the access patterns in the system. Thus, the memory units are modelled on an approximately timed abstraction level.

**Processor cores** in SHMAC are relatively simple with only a single outstanding memory request allowed, thus a loosely timed model is used for them. This is also appropriate, since as stated in Section 1.4 future SHMAC cores will not be MIPS cores; creating complex models can be a waste of resources.

Considering the cycle-accurate communication model and the loosely timed computation model utilized, SHMACsim could be considered a TLM model bordering on BFM according to the categorization presented in Section 2.4.1.

#### 3.1.3. Choice of External Tools and Modules

Taking into account the decisions on development methodology and abstraction levels, the next step in the design of SHMACsim was to select the set of external tools and modules to be utilized.

The following subsections will describe the selections with regard to their properties and how they correspond to SHMACsim's requirements.

#### 3.1.3.1. Simulation Framework

A software-based simulation kernel or framework that provides the necessary capabilities to model generic hardware is a powerful tool, and a prime candidate for accelerating SHMACsim's development. Indeed, Skadron et al. [58] mention that the manual mapping from the concurrent, structural nature of a computer architecture to the sequential, procedural nature of a programming language such as C or C++ is a complex, ad-hoc and error-prone process.

SystemC, the IEEE standard for system-level modelling [11], was chosen as the SHMACsim simulation infrastructure for the following reasons:

Language of implementation: The Open SystemC Initiative provides an open source reference implementation in C++, meaning that the regular language constructs in C++ are readily available alongside those provided by SystemC. This means that external C++ models can also be integrated with ease. An example would be components from gem5 [8].

**Concurrency and Time:** Hardware is inherently concurrent and operates at a well-defined rate, thus the ability to model concurrency and time is important for cycle accurate hardware simulation. SystemC offers an event-driven simulation kernel with explicit concepts of passage of time and concurrency.

Abstraction Level of Modelling: SystemC and the associated TLM standard do not enforce a particular level of abstraction for modelling system components, allowing the modelling of different parts of the system with varying levels of detail. The developer is then free to choose the level of modelling for each component in accordance with speed or accuracy requirements of the simulation. On the low-end of the modelling scale, SystemC offers RTL-like language constructs inspired by hardware design languages. One particular advantage of using this level of modelling is the possibility to translate code back and forth between SystemC and HDLs with minimal effort. On the other end of the modelling scale, it is possible to use any abstraction C++ is capable of, thus an instruction decoder could be implemented as a *switch()* statement, or random-access memory modelled with an array. These capabilities correspond to the mixed abstraction level decisions in Section 3.1.2.

#### 3.1.3.2. Processor Core Generation

The construction and verification of processor core models is a potentially lengthy process, which marks it as a strong candidate for utilizing an external module instead of writing from scratch. Since the standard MIPS ISA is utilized in the FPGA prototype, it is relatively easy to find an appropriate pre-made model.

SHMACsim uses an ArchC-generated SystemC model for processor cores. ArchC is a Processor Description Language which can generate SystemC processor models from an ISA behavioural description. Mature models capable of running the SPEC2000 benchmark suite are provided for MIPS-I, PowerPC, SPARC V8, ARMv5 and the Intel 8051 ISAs [4]. Other advantages of using ArchC-generated models are syscall emulation support, TLM memory port support for connecting external memory models, and GNU bintools generation for the models.

This set of features, especially the SystemC model generation, the availability of a mature loosely-timed MIPS-I model and an external memory port, were the reasons for the choice of ArchC. The multiple ISAs supported is also beneficial for future work where a different ISA is desired for the SHMAC.

# 3.2. Design

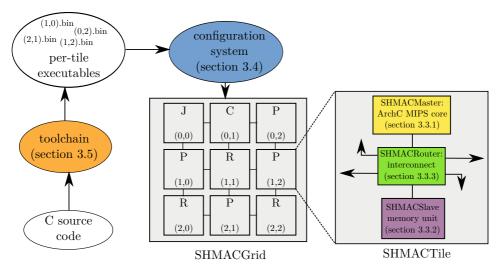

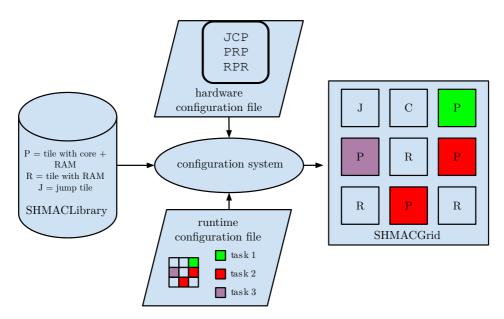

Having described the development basis, choice of abstraction levels and external modules, the design details of SHMACsim will be provided in this section. The constructed infrastructure is capable of instantiating desired SHMAC grids and running applications on them. An illustration of the high-level workflow in the system can be found in 3.1. The simulated SHMAC system itself comprises three core subsystems: the processor cores, the memory system, and the interconnect. These are organized into SHMACTiles which form a SHMACGrid. There is an additional configuration subsystem which is responsible for instantiating and configuring the desired grid, and a toolchain for compiling applications for the architecture is also provided.

The following sections describe these subsystems in some detail. The notation used to refer to design elements throughout the rest of the chapter is given in Table 3.2.

Figure 3.1.: An overview of the simulator core subsystems and helper subsystems in SHMACsim

#### 3.2.1. Processor Cores

SHMACsim utilizes loosely-timed MIPS-I core models generated by ArchC, similar to the Plasma MIPS-I cores used in the FPGA prototype. The model introduces a one clock cycle delay between instruction executions, and although it lacks the two-stage pipeline found in the prototype, the overall system performance was found to be very similar within SHMACsim's scope as indicated by the results in Section 3.5.

The generated cores are configured without any built-in cache or memory except the register file. Instead, memory requests are sent to the on-tile router via the TLM port as described in Subsection 3.2.1.1. Additionally, two extra instructions are implemented from the MIPS-II ISA to support multi-core synchronization, which is described in Subsection 3.2.1.2.

It is worth noting here that only one processor core model is supplied with SHMACsim. The "complex core" enhanced with a Floating Point Unit (FPU) in the FPGA prototype is not implemented since floating point computations can be trivially performed by the host computer in simulation. If desired, individual cores can be made faster or slower by changing the inter-instruction delay in the current loosely timed model, thus providing core diversity. This has not been explored in this report since the assignment does not focus

| Type                            | Notation Example(s)               |  |  |

|---------------------------------|-----------------------------------|--|--|

| Class names                     | SHMACTLMAdapter, shmacsim::packet |  |  |

| Function names                  | receiveMessage                    |  |  |

| Shell scripts                   | $shmacsim\-archc\-all compile$    |  |  |

| Active objects <sup>1</sup>     | С                                 |  |  |

| Input-Output Ports <sup>1</sup> |                                   |  |  |

Table 3.2.: Notation and symbols used in the simulator design description

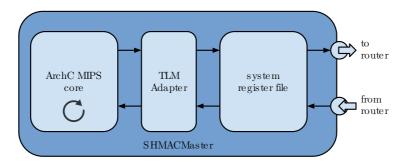

Figure 3.2.: The internal structure of a SHMACMaster, showing the ArchC MIPS core and the TLM adapter.

on effects of core diversity, but rather the construction of an infrastructure capable of supporting this diversity.

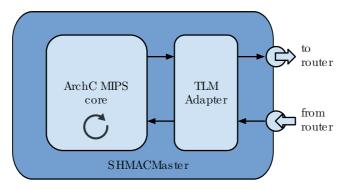

#### 3.2.1.1. Integration with SHMAC Memory Interface

ArchC-generated cores provide an optional TLM port for accessing memory devices. This port is utilized in SHMACsim to integrate the ArchC-generated cores with the network-based memory interface. An adapter is necessary for this integration, since ArchC uses a bidirectional blocking interface and SHMACsim uses double unidirectional blocking interfaces (described in Section 3.2.2). The SHMACTLMAdapter class provides this adaptation by

<sup>&</sup>lt;sup>1</sup>Active objects contain SC\_THREAD or SC\_METHODs, and all ports are implemented as SystemC ports. Please refer to [29] or [11] for details on SystemC processes and ports.

translating back and forth between ArchC TLM transport calls and SHMAC network packets. This process works as follows:

- 1. The ArchC-generated core calls the *transport* function on the **SHMACTLMAdapter** with a memory request

- 2. The adapter creates a SHMAC network packet corresponding to the ArchC memory request, and sends out this packet to the local router port

- 3. The core is stalled by a SystemC *wait* call by the adapter while the adapter waits for the reply

- 4. Upon receiving the corresponding reply packet for this request, the adapter converts the reply into the response format expected by ArchC and returns from the *transport* function call

- 5. The core's memory request has been served and it can continue execution

It can be observed that SHMACTLMAdapter has a similar purpose to the state machine wrapper for the processor cores in the SHMAC prototype - both stall the processor core while waiting on memory requests. The delays introduced by the state machine wrapper are also annotated on SHMACTLMAdapter to have a more accurate model of the prototype. Finally, the adapter is also a key part of SHMACsim's LL/SC instruction implementation, as described in 3.2.1.2.

Reflecting the master-slave terminology in the SHMAC architecture, the ArchC-generated cores and the TLM adapter are packed into a SHMACMaster class with inbound and outbound memory ports as shown in Figure 3.2.

#### 3.2.1.2. Implementation of LL/SC Instructions