Jan Christian Meyer

## Performance Modeling of Heterogeneous Systems

Thesis for the degree of Philosophiae Doctor

Trondheim, November 2012

Norwegian University of Science and Technology Faculty of Information Technology, Mathematics and Electrical Engineering Department of Computer and Information Science

NTNU – Trondheim Norwegian University of Science and Technology

#### NTNU

Norwegian University of Science and Technology

Thesis for the degree of Philosophiae Doctor

Faculty of Information Technology, Mathematics and Electrical Engineering Department of Computer and Information Science

© Jan Christian Meyer

ISBN 978-82-471-4015-4 (printed ver.) ISBN 978-82-471-4016-1 (electronic ver.) ISSN 1503-8181

Doctoral theses at NTNU, 2012:344

Printed by NTNU-trykk

For Adrien and Martin Manó, my beloved family who keep me synchronized.

### Abstract

As the complexity of parallel computers grows, constraints posed by the construction of larger systems require both greater, and increasingly non-linear, parameter sets to model their behavior realistically. These heterogeneous characteristics create a trade-off between the complexity and accuracy of performance models, creating challenges in utilizing them for design decisions.

In this thesis, we take a bottom-up approach to realistically model software and hardware interactions, by composing system models from simpler, linear models, which allow parts of the analysis to be automated. We associate empirically benchmarked platform performance metrics with the core elements in a variant of bulk-synchronous execution, aiming to quantify application performance, and associated potential for computation and communication overlap on SMP clusters.

The original bulk-synchronous performance model is introduced, and we identify areas of computation and communication where its abstractions impede realistic models of contemporary hardware. These are addressed independently, using experimental evidence to develop a representation collecting computation kernel characteristics and pairwise communications in matrices, to combine into a system model. As bulk-synchronous execution strongly depends on periodic, global synchronization, we develop a cost model for it by combining latency measurements with a parametric representation of signalling patterns, and experimentally verify the resulting predictions for three common algorithms.

We describe a design to implement the BSPLib programming interface, combining threads and message-passing parallelism to achieve overlap on commodity cluster platforms, implementing its one-sided communication primitives using out-of-band control messages. We augment and validate the cost model of one adapted synchronization algorithm with the corresponding bandwidth requirement, completing a framework for modeling BSPLib program performance.

Finally, we test the utility of this framework as a proof-of-concept for guiding software performance adaptations, using two cases. First, we use the latency terms to automatically generate synchronization operations, using model predictions to generate customized patterns with respect to platform topology, showing that the resulting algorithms equal or outperform the system defaults. Second, the strong scaling characteristics of a 5-point stencil code is compared for three implementations. Experiments show the performance overhead of our implementation, but also its capability for predicting program cost, including parameter values to optimize for balanced overlapping of computation and communication.

<u>ii</u>

## Preface

This thesis is submitted to Norwegian University of Science and Technology (NTNU) in partial fulfillment of the requirements for the degree Philosophiæ Doctor.

The work herein was performed at the Department of Computer and Information Science, NTNU, Trondheim, under the supervision of Associate Professor Anne C. Elster.

The work was financed by the Faculty of Information Technology, Mathematics and Electrical Engineering.

## Acknowledgements

Pursuing a single project for such an extended period is a rare opportunity. First and foremost I wish to thank my advisor, Anne C. Elster, for affording me the possibility, and for all her tireless work in helping me through it. I also extend my gratitude to co-advisors Lasse Natvig and Jørn Aslak Amundsen, who have offered very helpful feedback and advice along the way.

Many heartfelt thanks go to fellow Ph.D. students Thorvald Natvig, Rune Erlend Jensen, Magnus Jahre, Asbjørn Djupdal, Marius Grannæs, Dragana Laketić, Nils Grimsmo and Truls Amundsen Bjørklund, and everyone else along the corridor, who made it a memorable time for reasons beyond research work.

Magnus Lie Hetland and Peter Henry Hughes both deserve my sincere thanks, for pointing me directly to key insights, at particular times when I was all out of ideas.

Finally, I am most deeply grateful to the near and dear: Adrien and our son Martin Manó, our parents Sissel and Jan, Marika and Vince, my brother Bjørn, and my incomparable friend Egil Albertsen. You have all patiently and thoughtfully suffered my absence, supported, listened, discussed, commented, sympathized, sacrificed, inspired, and forgiven a thousand broken promises. Here you have what kept me for so long.

Jan Christian Meyer Trondheim, November 2012 iv

# Contents

| Lis             | st of <b>T</b> | ables     |                                                              | ix |

|-----------------|----------------|-----------|--------------------------------------------------------------|----|

| List of Figures |                | xi        |                                                              |    |

| 1               |                | oductio   |                                                              | 1  |

|                 | 1.1            |           | ing Challenges And Scope                                     | 2  |

|                 | 1.2            |           | work Outline                                                 | 4  |

|                 | 1.3            |           | ch Questions                                                 | 5  |

|                 | 1.4            | butions   | 7                                                            |    |

|                 |                | 1.4.1     | A Bulk-Synchronous Programming Tool                          | 7  |

|                 |                | 1.4.2     | A Modeling Framework to Capture Overlap Using Linear Systems | 7  |

|                 |                | 1.4.3     | Benchmarks for Commodity SMP Clusters                        | 7  |

|                 |                | 1.4.4     | A Method for Automatic Barrier Adaptation                    | 8  |

|                 |                | 1.4.5     | A Method for Determining Application Overlap                 | 8  |

|                 | 1.5            | Structu   | re of the Thesis                                             | 8  |

| 2               | Scala          | ability a | and Heterogeneity                                            | 11 |

|                 | 2.1            | Termin    | ology                                                        | 11 |

|                 |                | 2.1.1     | Architectural Scalability                                    | 11 |

|                 |                | 2.1.2     | Architectural Heterogeneity                                  | 12 |

|                 |                | 2.1.3     | Programmatic Scalability                                     | 12 |

|                 |                | 2.1.4     | Programmatic Heterogeneity                                   | 13 |

|                 | 2.2            | Archite   | ectural Map                                                  | 13 |

|                 |                | 2.2.1     | Multi-core and Many-core Systems                             | 14 |

|                 |                | 2.2.2     | GPGPU and Special Purpose Accelerators                       | 15 |

|                 |                | 2.2.3     | Distributed Shared Memory Systems                            | 16 |

|                 |                | 2.2.4     | Distributed Memory Systems                                   | 17 |

|                 |                | 2.2.5     | Grids                                                        | 18 |

|                 | 2.3            | Progra    | mming Model Map                                              | 19 |

|                 |                | 2.3.1     | Thread Parallelism                                           | 20 |

|                 |                | 2.3.2     | Stream Parallelism                                           | 21 |

|                 |                | 2.3.3     | Message Passing                                              | 22 |

|                 |                | 2.3.4     | Hybrid Models and Job-level Parallelism                      | 23 |

|                 | 2.4            | Resear    | ch Context                                                   | 24 |

| 3 | Modeling Framework                                        | 27       |

|---|-----------------------------------------------------------|----------|

|   |                                                           | 27       |

|   |                                                           | 31       |

|   |                                                           | 34       |

|   |                                                           | 36       |

|   | 6                                                         | 37       |

|   |                                                           | 57       |

| 4 | 1                                                         | 39       |

|   | 4.1 Impact of Variations in Time                          | 39       |

|   | 4.2 Impact of Variation in Memory Footprint               | 46       |

|   |                                                           | 49       |

| 5 | Communication Latency                                     | 51       |

| J | e                                                         | 51       |

|   | 1 5                                                       | 53       |

|   |                                                           | 55<br>54 |

|   | 5                                                         |          |

|   |                                                           | 55       |

|   | i e                                                       | 56       |

|   | 1                                                         | 59       |

|   |                                                           | 59       |

|   | e                                                         | 60       |

|   | 5.6.3 Benchmark Statistics                                | 62       |

|   | 5.6.4 Benchmark Validation                                | 62       |

|   | 5.6.5 Barrier Cost Model                                  | 63       |

|   | 5.6.6 Test Cases: 8x2x4 and 12x2x6 cluster configurations | 64       |

| 6 | Run-time System and Performance Model                     | 77       |

| v | •                                                         | <br>77   |

|   |                                                           | 79       |

|   |                                                           | 81       |

|   | 8                                                         |          |

|   |                                                           | 82       |

|   |                                                           | 83       |

|   | 6.6 Empirical Validation                                  | 87       |

| 7 | Case Study I:                                             |          |

|   |                                                           | 91       |

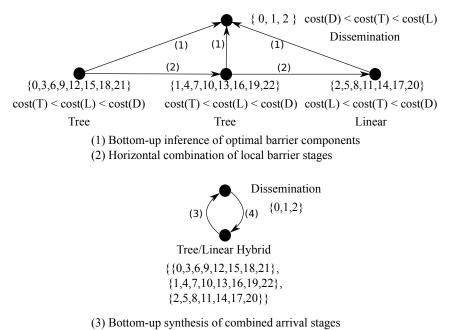

|   | 7.1 Barrier Combination                                   | 91       |

|   | 7.2 Determining Subset Sizes                              | 93       |

|   |                                                           | 97       |

|   |                                                           | 99       |

|   |                                                           | 02       |

| Q | Case Study II: Lonlogian Stancil                          | 05       |

| 8 |                                                           | 05<br>06 |

|   |                                                           | 06       |

|   | 1 1                                                       | 07       |

|   | 8.3 Implementation Details                                | 09       |

vi

|   |                   | 8.3.1 BSP implementation                                                                                                                                                                                          | 100                                                                                                                |

|---|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|   |                   |                                                                                                                                                                                                                   |                                                                                                                    |

|   |                   | I                                                                                                                                                                                                                 |                                                                                                                    |

|   |                   |                                                                                                                                                                                                                   | 111                                                                                                                |

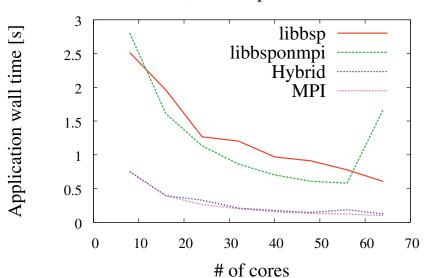

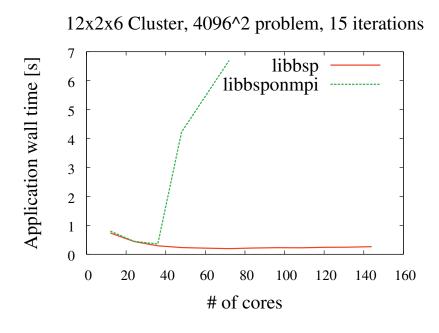

|   | 8.4               | Comparisons of Strong Scalability                                                                                                                                                                                 | 112                                                                                                                |

|   |                   | 8.4.1 Comparison of All Implementations                                                                                                                                                                           | 112                                                                                                                |

|   | 8.5               |                                                                                                                                                                                                                   | 119                                                                                                                |

|   |                   | 8.5.1 Experimental Methodology                                                                                                                                                                                    | 121                                                                                                                |

|   |                   | 8.5.2 Results And Discussion                                                                                                                                                                                      | 121                                                                                                                |

|   | 8.6               | Model-driven Optimization                                                                                                                                                                                         | 128                                                                                                                |

|   |                   |                                                                                                                                                                                                                   |                                                                                                                    |

| • | 0                 |                                                                                                                                                                                                                   |                                                                                                                    |

| 9 | Con               | clusions and Future Work                                                                                                                                                                                          | 133                                                                                                                |

| 9 | <b>Con</b><br>9.1 |                                                                                                                                                                                                                   |                                                                                                                    |

| 9 |                   | Process and Publications                                                                                                                                                                                          | 134                                                                                                                |

| 9 | 9.1               | Process and Publications                                                                                                                                                                                          | 134<br>135                                                                                                         |

| 9 | 9.1               | Process and Publications                                                                                                                                                                                          | 134<br>135<br>135                                                                                                  |

| 9 | 9.1               | Process and Publications                                                                                                                                                                                          | 134<br>135<br>135<br>136                                                                                           |

| 9 | 9.1               | Process and Publications                                                                                                                                                                                          | 134<br>135<br>135<br>136<br>136                                                                                    |

| 9 | 9.1               | Process and Publications         Future Work         9.2.1       Profiling Extensions         9.2.2       On-Line Adaptivity         9.2.3       Range Of Applications                                            | 134<br>135<br>135<br>136<br>136                                                                                    |

| - | 9.1               | Process and PublicationsFuture Work9.2.1Profiling Extensions9.2.2On-Line Adaptivity9.2.3Range Of Applications9.2.4Range Of Interconnects                                                                          | <ol> <li>133</li> <li>134</li> <li>135</li> <li>135</li> <li>136</li> <li>136</li> <li>137</li> <li>139</li> </ol> |

| - | 9.1<br>9.2        | Process and Publications         Future Work         9.2.1       Profiling Extensions         9.2.2       On-Line Adaptivity         9.2.3       Range Of Applications         9.2.4       Range Of Interconnects | 134<br>135<br>135<br>136<br>136<br>137                                                                             |

viii

# **List of Tables**

| 3.1 | BSPBench parameter values for 8-way 2x4 core cluster                                                                                 | 29 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.1 | BSPlib programming primitives                                                                                                        | 78 |

|     | Output of 60-process SSS clustering on 8x2x4 node configuration<br>Output of 115-process SSS clustering on 10x2x6 node configuration |    |

|     | Experimental Configurations                                                                                                          |    |

<u>x</u>\_\_\_\_\_

# **List of Figures**

| 1.1<br>1.2<br>1.3                      | Aspects of the BSP model                                                                                                                                                                                                                                                                                                                 | 3<br>4<br>6                                                          |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 2.1<br>2.2                             | Map of architectural scalability and heterogeneity                                                                                                                                                                                                                                                                                       | 14<br>19                                                             |

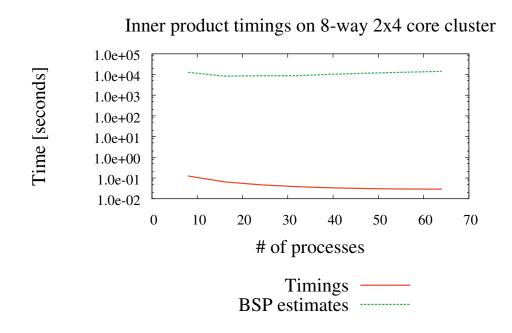

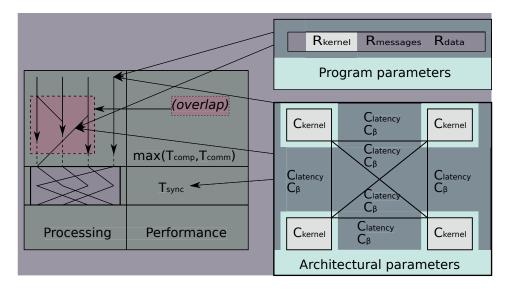

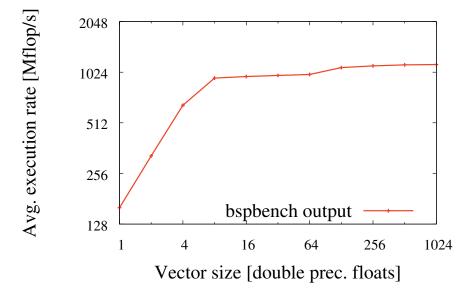

| 3.1<br>3.2<br>3.3                      | Relationship between component BSP modelsInner product comparison on 8-way 2x4-core clusterRelationship between revised models                                                                                                                                                                                                           | 28<br>30<br>32                                                       |

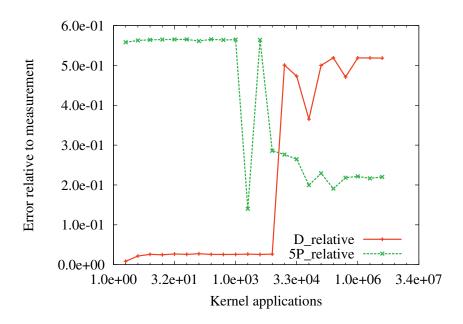

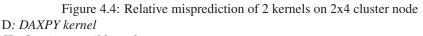

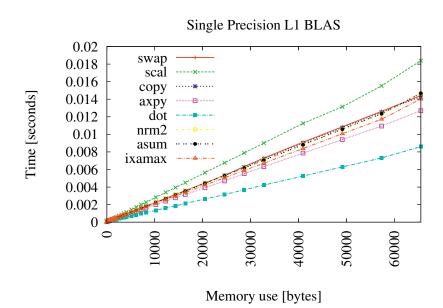

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Architectural and program parameters of computational ratebspbench computation rates on 2x4 cluster nodeRates and predictions of 2 kernels on 2x4 cluster nodeRelative misprediction of 2 kernels on 2x4 cluster nodeL1 BLAS performance, in-cache problem sizes on Athlon X2L1 BLAS performance, 64K-element problem sizes on Athlon X2 | 40<br>41<br>44<br>45<br>47<br>48                                     |

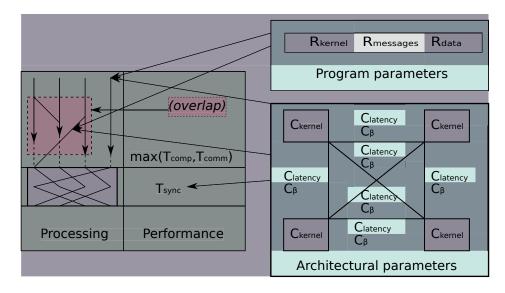

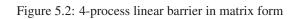

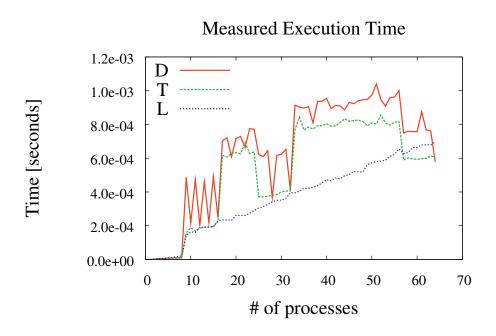

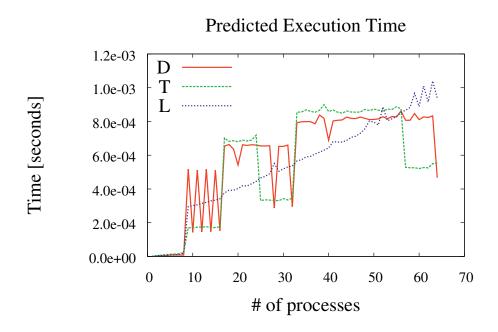

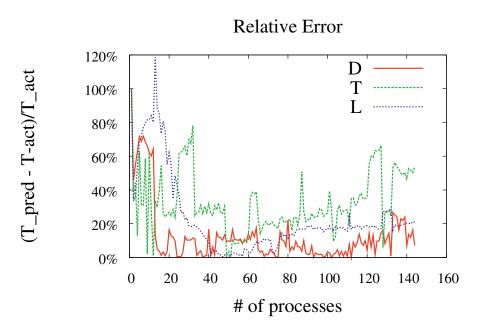

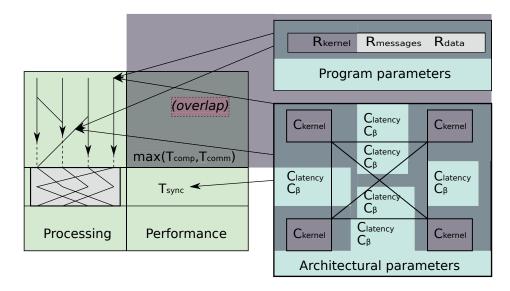

| 5.12                                   | Architectural and program parameters of communication latency 4-process linear barrier in matrix form                                                                                                                                                                                                                                    | 52<br>57<br>57<br>60<br>65<br>66<br>68<br>69<br>70<br>71<br>72<br>73 |

| 6.1                                    | Relation of communication parameters to processing and performance models                                                                                                                                                                                                                                                                | 84                                                                   |

| 6.2  | Recursive Critical Path Search                                        | 85  |

|------|-----------------------------------------------------------------------|-----|

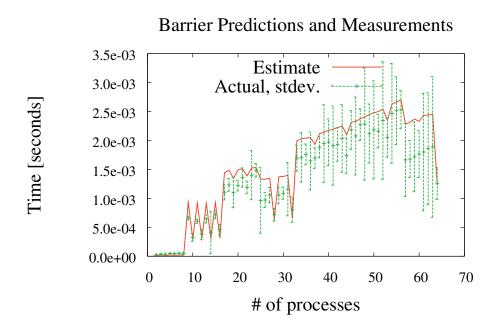

| 6.3  | Measured barrier timings and estimate on 8x2x4 cluster                | 88  |

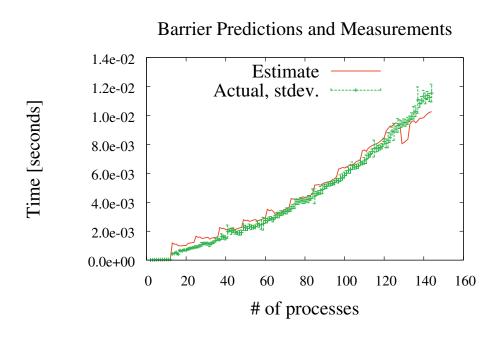

| 6.4  | Measured barrier timings and estimate on 12x2x6 cluster               | 89  |

| 7.1  | Model components of synchronization cost                              | 92  |

| 7.2  | Hierarchical hybrid barrier with marked subsets                       | 93  |

| 7.3  | Greedy construction of a hierarchically clustered, customized barrier | 97  |

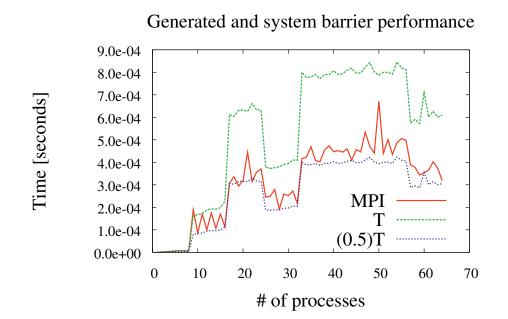

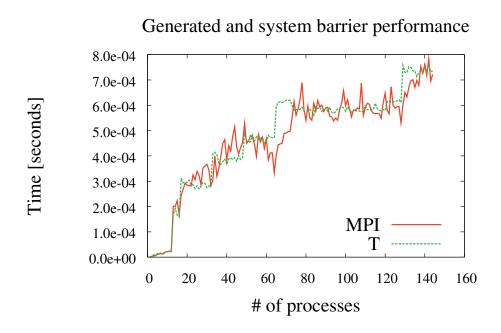

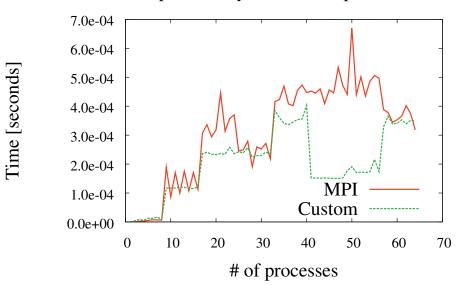

| 7.4  | Barrier performance on 8-way 2x4-core cluster                         | 100 |

| 7.5  | Barrier performance on 12-way 2x6-core cluster                        | 101 |

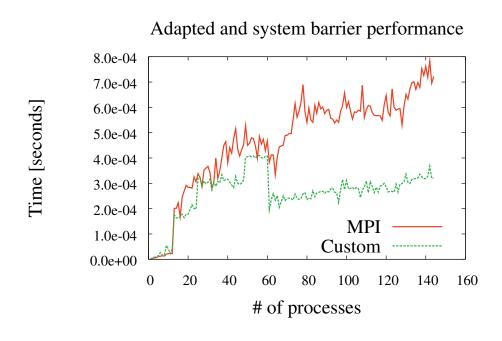

| 7.6  | Adapted barrier performance on 8-way 2x4-core cluster                 | 102 |

| 7.7  | Adapted barrier performance on 12-way 2x6-core cluster                | 103 |

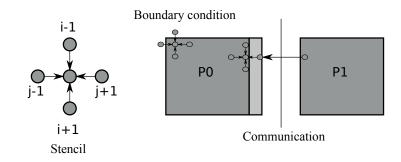

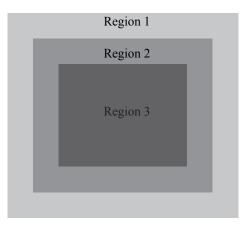

| 8.1  | Boundaries and Ghost Area in 5-point Stencil Computation              | 108 |

| 8.2  | 17 Regions in BSP implementation                                      | 110 |

| 8.3  |                                                                       | 111 |

| 8.4  | 2-Stage Border Exchange in MPI Implementation                         | 111 |

|      | A1: All Implementations                                               | 114 |

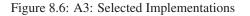

| 8.5  | A2: BSP Implementations Only                                          |     |

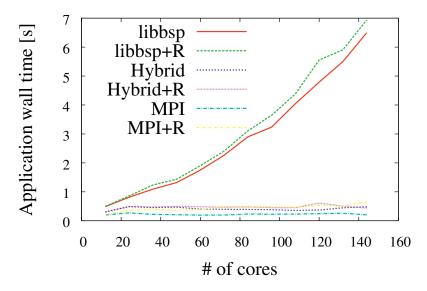

| 8.6  | A3: Selected Implementations                                          | 117 |

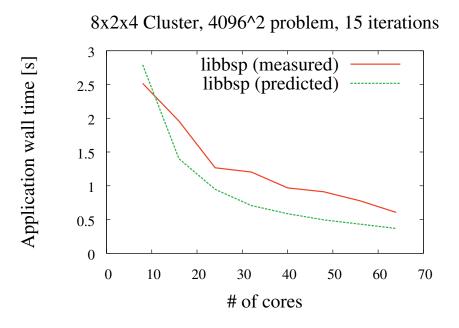

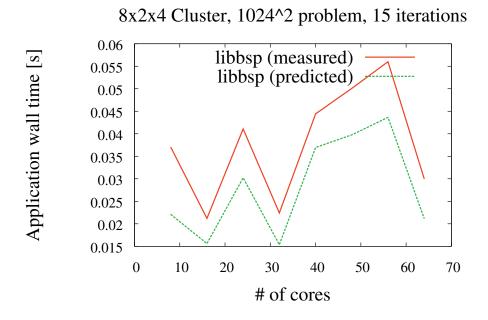

| 8.7  | A4: Selected Implementations                                          | 118 |

| 8.8  | Application-specific Matrix Setup                                     | 120 |

| 8.9  | Predictor Program                                                     | 120 |

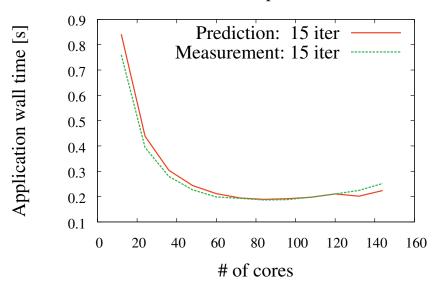

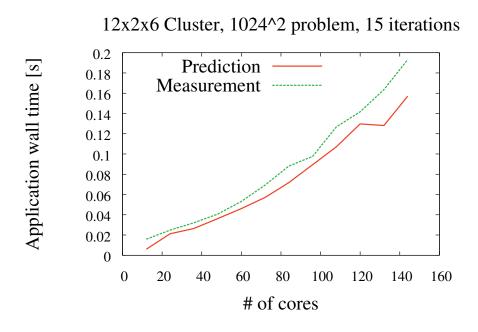

|      | B1: Prediction vs. Measurement, Large Problem                         | 122 |

|      | B2: Prediction vs. Measurement, Small Problem                         | 123 |

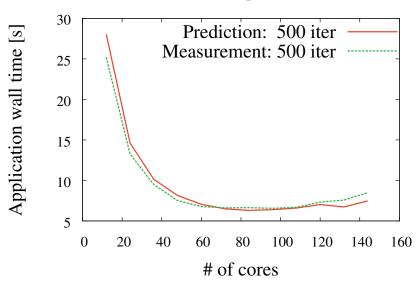

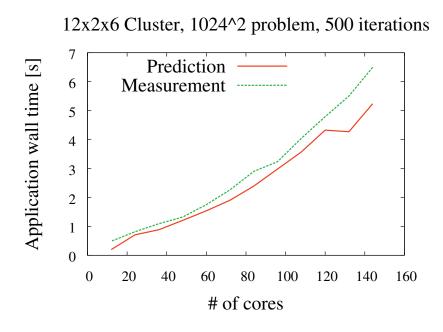

|      | B3: Prediction vs. Measurement, Large Problem                         | 124 |

|      | B4: Prediction vs. Measurement, Small Problem                         | 125 |

|      | B5: Prediction vs. Measurement, Large Problem                         | 126 |

|      | B6: Prediction vs. Measurement, Small Problem                         | 127 |

|      | Shadow Cell Regions In A Local Subproblem                             | 129 |

|      | Adapted Superstep Prediction                                          | 130 |

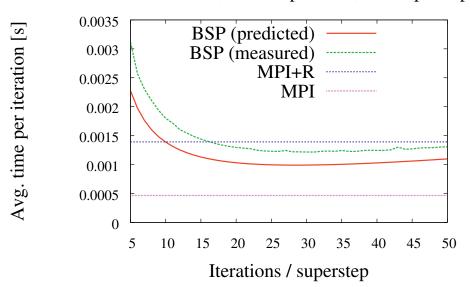

| 8.18 | C1: Predicted vs. Measured Iteration Time                             | 132 |

## **Chapter 1**

## Introduction

The main aim of this thesis is to derive performance models of complex program and platform interactions which admit automated support for performance tuning. Recent generations of parallel computers are composed of subsystems with highly variable, nonlinear performance properties, which make them challenging to model accurately. Maintaining an illusion of a large memory with uniform access cost is already impossible in most cases, and the communication costs of distributed memory systems are influenced by many factors. The sustainable computational rate of a processor is tied to the memory access patterns of programs, making it variable even on systems composed of identical processors. Models expressed as small sets of linear parameters do not reflect these heterogeneous characteristics, but increasing the level of model detail detracts from both clarity and generality.

In order to maximize the efficiency of parallel programs, it is necessary to chart the sustainable load of component subsystems, leading to the consideration of how far communication and computation can be overlapped. Because the cost of communication is fundamentally dependent on the distance between the communicating parties, balancing the two is essential in order to permit system scale to grow without diminishing the utility of the added computational resources.

The method described in this thesis approaches system model complexity based on the existence of effective linear models of individual subsystems. Assuming the distribution of a known, finite workload onto these subsystems, the composition of overall system behavior from a heterogeneous collection of subsystems can be automated. This permits system models to incorporate a great number of parameter values without requiring an analyst to manually manipulate them all.

## 1.1 Modeling Challenges And Scope

Ideally, a performance model should be simple, general, and provide strong predictions. These objectives conflict with the need to capture system complexity, as it requires structural information about both system and program to be taken into account. The resulting trade-offs make it unrealistic to search for a single, correct approach to all systems. This section outlines the choices we make to produce a usable framework for deriving performance models for systems with heterogeneous performance parameters.

In this thesis, we have chosen to model heterogeneous systems by extending the Bulk-Synchronous Parallel (BSP) model [95]. Its purpose is to form a *bridging* model, combining aspects of parallel computation from several levels of abstraction.

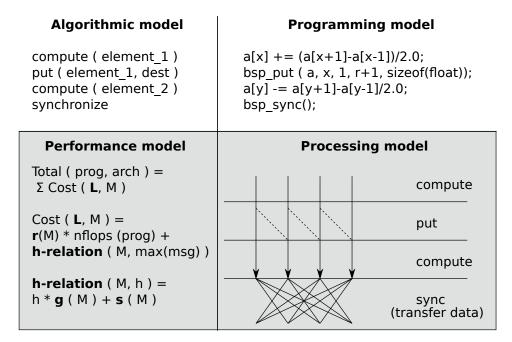

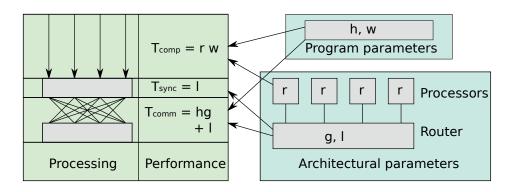

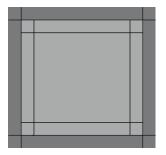

Figure 1.1 illustrates how BSP unifies algorithmic, programmatic, processing and performance models in terms of a few, global concepts. In order to adapt it to heterogeneous systems, we adjust the processing model to permit performance models of greater detail. BSP is chosen because it makes it possible to exchange these parts without violating the semantics of the algorithmic and programmatic components, allowing this thesis to utilize and complement existing programs and algorithms in the body of related work.

Our objective is to keep component models sufficiently simple, so that they can be represented in a uniform manner programmatically. Linear models of subsystems are appropriate for this purpose, because of the relative simplicity of manipulating large systems of linear equations in software. Such an approach carries two significant limitations. One is that it requires a bound on the time interval for which the model should be valid, in order to derive the amount of work delegated to each subsystem. The other lies in the assumption that a piecewise linear description of global behavior can be obtained from a subsystem decomposition.

Bulk-synchronous execution inherently partitions computation into bounded intervals, restricting our scope of study to synchronized or loosely synchronized algorithms. A 1996 technical report by Fox [36] estimates that this accounts for 90% of parallelized problems in scientific computing. Assessing the accuracy of that number is beyond the scope of this thesis, but we argue that synchronized computation is an important area of study, while noting that our approach is poorly suited to asynchronous algorithms.

Nonlinear subsystem models are not addressed in this thesis because composing an overall system of nonlinear equations greatly complicates automatic manipulation, detracting from its effectiveness for hiding model complexity. Computation rate is nonlinearly related to the data traffic caused by problem specific properties. This is approached by treating such functions as piecewise linear, and decomposing them into a discontinuous set of linear models. While this works in the practical cases investigated here, it increases the amount of manual labor involved in modeling.

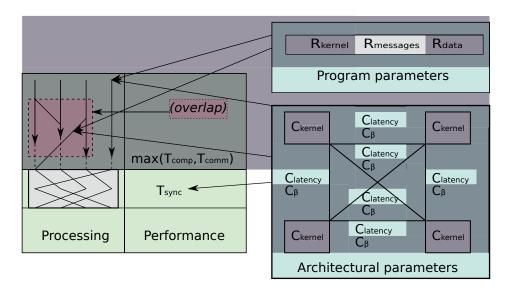

#### Figure 1.1: Aspects of the BSP model

Algorithmic and programming models represent the abstractions presented for program design purposes, as a set of fundamental operations and their corresponding programming language support. The processing model shows a synchronized superstep where communication is effected by a total exchange at the end. It serves as a shared abstraction to both software and hardware architecture. The **performance** model attaches cost functions to key elements of programs and platforms. Specifically, L is the periodicity of the program, h is the maximal amount of data communicated between a pair of parallel processes, r is the rate of computation, g is the throughput of the communication infrastructure, and s is the latency. L is written as a function of the program, to reflect variations in the amount of work in a given superstep. M is not explicitly acknowledged in the original notation, but is introduced here to acknowledge the platform-dependency of cost functions. This notation will be significantly altered with our model refinements, but is stated here to clarify connections with related work.

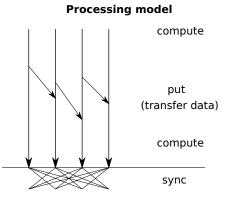

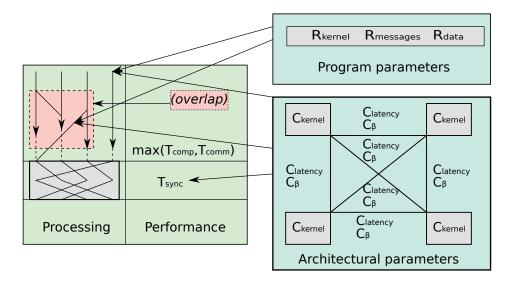

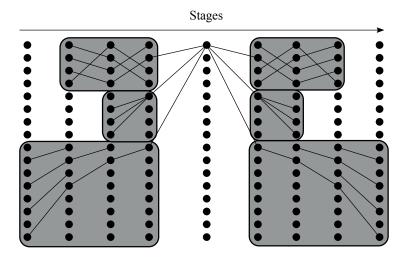

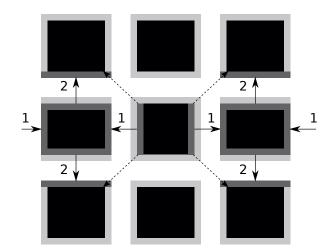

Figure 1.2: Alternative processing model

### **1.2 Framework Outline**

Figure 1.2 illustrates our modified processing model, which retains the BSP semantics that effects of communication are not observed until after synchronization/total exchange. The change amounts to initiating communication as early as permissible, decoupling the cost of communication from synchronization. This reduces the amount of communication required at synchronization time, and holds the potential for mitigating interconnect contention, as communication may happen at the individual process' discretion when the message is ready.

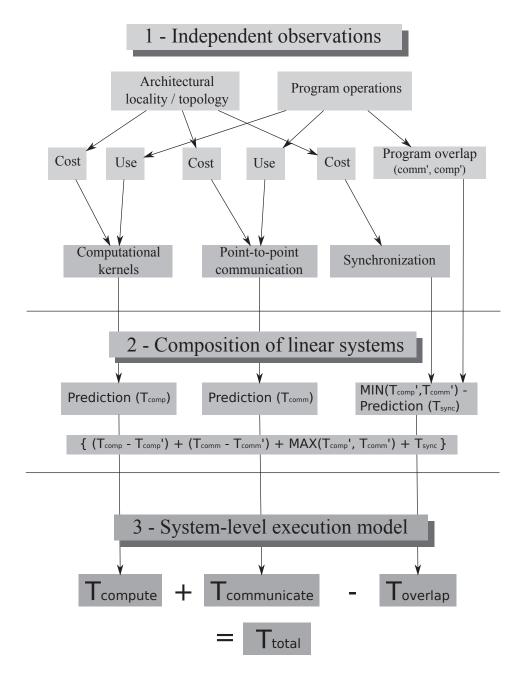

Accounting for background communication, as well as a heterogeneous performance model, Figure 1.3 shows an overview of our approach for modeling application behavior at the system level. It is structured according to what Barker *et al.* [14] name the "fundamental equation of modeling", given in Equation 1.1.

$$T_{total} = T_{compute} + T_{communicate} - T_{overlap}$$

(1.1)

Selecting the computational *superstep* [95] as the model unit of work implies a division of computation and communication time totals into non-maskable and maskable parts. Equations 1.2 and 1.3 express the non-maskable time as the difference of total requirement T and a maskable part T'.

$$T_{comm-nonmaskable} = T_{comm} - T'_{comm}$$

(1.2)

$$T_{comp-nonmaskable} = T_{comp} - T'_{comp} \tag{1.3}$$

This allows the right hand side of Equation 1.1 to be restated as Equation 1.4, with total time representing the superstep cost.

$$T_{total} = (T_{comp} - T'_{comp}) + (T_{comm} - T'_{comm}) + \max(T'_{comp}, T'_{comm}) + T_{sync}$$

(1.4)

This formulation indicates that a *superstep* consists of some sequentially dependent work, some which can be overlapped (bounding total time to the greatest requirement), and the synchronization cost of a semantic fence to mark the completion of both.

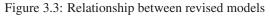

The approach proceeds bottom-up, in the 3 stages shown in Figure 1.3:

- 1. Approximate  $T_{comp}$ ,  $T_{comm}$  and  $T_{sync}$  separately

- 2. Combine the approximations in a linear system which describes collective behavior

- 3. Derive a system-level model of execution

Details concerning each of these stages are developed in subsequent chapters of this thesis. The underlying goal is to manage the complexity of the resulting system-level model by selecting simplifications to facilitate automatic model manipulation. Thus, the point of modeling system behavior as (potentially large) linear systems in Stage 2 is to admit heterogeneous collections of subsystem performance characteristics.

An important feature to note in Figure 1.3 is that the starting point of Stage 1 is a separation of program and platform characteristics. The purpose of initially considering these in isolation is to consider their representation as parameters by Stage 2, so that a model of one may be applied to several instances of the other. In particular, there is strong focus on keeping the topology of the communication infrastructure parametric. This requires coupling the physical locality of a process to its position in the logical layout of a program. Locality is observed to be an important factor in determining the cost of communication, implying that accurate modeling requires its impact to be kept under strict control.

## **1.3 Research Questions**

The main research question of this thesis is

How can automation support the analysis of interactions between a parallel algorithm and the executing platform when both show heterogeneous performance characteristics?

Addressing this question breaks into more specific research questions, which pertain to the requirements of adapting the approach in Figure 1.3 to a particular system:

- RQ1 How can the computation and communication requirements of a program be coupled to an independent profile of the executing platform?

- RQ2 How can the impact of synchronization on program performance be determined?

- RQ3 Which constraints govern the accuracy of performance predictions produced using the developed framework?

- RQ4 How suitable is the framework for the purposes of automatic application performance tuning?

Figure 1.3: Outline of the Proposed Framework

## **1.4 Contributions**

Several variations over models found in the body of related work are employed throughout this thesis. Its novelty lies in coupling application modeling techniques for pairwise communication, collective behavior, and computation rates with programming and processing models adapted from a more theoretical approach. Strong focus on experimental validation is maintained throughout, to ensure that the developed framework is practically applicable. The remainder of this section gives further details of our contributions.

#### 1.4.1 A Bulk-Synchronous Programming Tool

The BSP model is already endowed with a programming interface specification. The work presented in this thesis constructs an implementation of this interface, modifying the processing model to employ asynchronous communication. The corresponding experimental work provides evidence that the combination is a simple and effective means to identify and exploit an algorithm's potential for computation/communication overlap, to the extent made feasible by the target platform.

#### 1.4.2 A Modeling Framework to Capture Overlap Using Linear Systems

The tradition of modeling homogeneous parallel systems in terms of constants or piecewise linear functions grows in complexity when applied to systems where performance parameters are greater in number and range. The presented framework approaches the composition of subsystems by expanding these into matrices containing individual or pairwise performance parameters, and deriving overlap as a collective property of the resulting linear systems.

This approach retains the favorable property of aggregating system models by composition of subsystems, without concealing all structural information. It is shows robustness in the face of parameter values varying by several orders of magnitude.

#### 1.4.3 Benchmarks for Commodity SMP Clusters

To validate the framework on COTS systems of multi-chip, multi-core compute nodes, it is tested on commodity Linux clusters with variable topology and configuration. Because the model relies on empirical data in order to characterize the performance impact of deploying an algorithm on a given platform, these clusters are benchmarked to produce their key parameters. The method of obtaining these benchmarks is described, as great care must be taken in order to give the stability and accuracy necessary for validation.

#### 1.4.4 A Method for Automatic Barrier Adaptation

Because synchronization costs are central to the framework, a detailed cost model of barrier synchronization is developed, including a general matrix representation of arbitrary barrier communication patterns. Since our predictions are shown through experiments to be very accurate, they can be used to produce customized barrier implementations of superior performance to those provided by available system libraries.

#### 1.4.5 A Method for Determining Application Overlap

A system's ability to mask communication by simultaneous computation is of great and growing significance to sustained, scalable performance. Its magnitude is, however, composed of both algorithmic dependencies and the architectural facilities for exploiting it. The implementation and instrumentation necessary to realize this potential and estimate its effectiveness, can require a significant amount of application restructuring. Bulk-synchronous execution semantics allow overlap to be automatically exploited by following the simple programming rule of committing communication as early as possible. The effectiveness of a model derived from our framework is illustrated by its correct identification of parameter values for optimal overlap in a simple application.

### **1.5** Structure of the Thesis

The structure of this thesis follows the stages of Figure 1.3, through development, testing, and application of a corresponding programming library and performance model. After initial considerations of computation speed, communication model terms are approached with a view to vertical integration. Communication cost is first estimated as a function of topological distance, to estimate synchronization cost. Communication patterns of several synchronization strategies are encoded as application requirements in a reduced model without cost functions for computation and synchronization. This is developed into a synchronization cost function which can be integrated with computation, and the implementation of a corresponding run-time library is described. Finally, the model is applied to automatic analysis of synchronization patterns and a small application program. Results demonstrate that the independent components can be integrated in a model which supports program optimization.

The remaining chapters are structured as follows:

Chapter 2 surveys a spectrum of parallel platforms and programming models with respect to heterogeneity and scale, to establish terminology and place the test system class in a greater context.

Chapter 3 introduces the background to motivate the framework's construction, and presents its basic terms, with emphasis on the relationship between bulk synchronicity and the fundamental equation of modeling.

Chapter 4 describes the challenges posed to stable metrics of computational rate imposed by the memory hierarchy of contemporary platforms, and shows the assumptions and methods applied to the test systems.

Chapter 5 describes the expression of the model's communication startup cost components, which provide accurate performance predictions for the cost of several synchronization algorithms applicable to the test systems.

Chapter 6 describes the techniques employed to create an implementation of the *BSPlib* programming interface which utilizes an application's potential for overlap, and exposes its magnitude on a given target platform. Attention is focused on a particular synchronization algorithm, extending its cost function to include a minimal data payload. This allows it to function as a special case of a total exchange collective, which establishes the synchronization cost estimate required by the framework.

Chapter 7 demonstrates the applicability of the framework to fully automate the construction of generic synchronization algorithms, by examining the model's prediction of their interaction with independently captured architectural profiles.

Chapter 8 introduces a simple finite difference application, and compares performance expectations to the results obtained by studying it with the developed model.

Chapter 9 draws conclusions, and outlines the potential for exploring the framework approach as a tool for guiding manual and automatic performance tuning.

## Chapter 2

## **Scalability and Heterogeneity**

Much of the complexity and diversity of parallel computing is due to how the requirements scaling solutions to ever greater problems conflict with those of implementing such solutions using a uniform set of resources. The resulting trade-offs manifest themselves both in hardware and software design. In order to provide an appropriate context for our research, this chapter presents a brief, qualitative survey of how this relationship is reflected in a range of systems.

Section 2.1 defines the distinguishing characteristics of scalability and heterogeneity for the purposes of this discussion. Section 2.2 applies these characteristics to classes of parallel hardware, while Section 2.3 addresses characteristics of programming model classes. Finally, Section 2.4 describes the context of our work, including how other models have contributed influential points.

## 2.1 Terminology

Since no commonly accepted definitions of heterogeneity and scalability exist, the scope of both terms are defined in the following sections, where they will be related to both the construction of parallel computer platforms, as well as programming models.

#### 2.1.1 Architectural Scalability

According to Hennessy and Patterson[43], scalability was long considered a property which could be built into an architectural design. Their further discussion of multiprocessor systems offers no succinct updated view, but it indicates that difficulties stem from increased requirements to grow interprocessor communication networks. Hwang and Xu[49] divide scalability into *resource*, *application* and *technology* scalability, further specified in

terms of various properties such as machine size, software scalability and heterogeneity scalability. They list of four design principles for scalability, which are

- 1. The principle of independence

- 2. The principle of balanced design

- 3. The principle of design for scalability

- 4. The principle of latency hiding

Parallel hardware scalability will be discussed in terms of these four principles. The principle of independence states that dependencies between system components should be minimized. The principle of balanced design states that any performance bottleneck should be minimized. The principle of design for scalability states that scalability should be acknowledged from the beginning of a design process, reflected in *overdesign*, *i.e.* features which anticipate future extensions, and *backward compatibility* for the sake of downscaling. The principle of latency hiding refers to exposing the potential for exploiting simultaneous execution and communication, to conceal startup cost. Patterson's treatment of the topic [82] states that "In the time that bandwidth doubles, latency improves by no more than a factor of 1.2 to 1.4", and reasons that this trend can be expected to continue. Accordingly, future designs should invent further techniques like caching, replication and prediction, to reduce the impact of latency at the expense of other resources.

#### 2.1.2 Architectural Heterogeneity

Our classification of architectural heterogeneity will take the high-level view that the defining characteristics of parallel computers are the processing and communication facilities, with the latter encompassing the effects of hierarchical memory subsystems. The sources of heterogeneity in a parallel architecture are thus the degree of variability in the range of their processing element designs, and in the elements which are employed to transport data to and from them.

#### 2.1.3 Programmatic Scalability

McCool's survey of scalable programming models [67] focuses on the conceptual mapping between architectural and programming model aspects. It makes an essential point by discriminating between processing and programming models, in order to separate issues of programmability and execution efficiency. Programming models are defined as a programmer's abstract view of software logic, whereas processing models are the associated cost considerations by which performance trade-offs can be evaluated. He identifies three central characteristics of a scalable programming model:

- 1. Simplicity

- 2. Expressiveness

- 3. Safety

*Simplicity* is the property of affording common programming tasks with little programming effort. *Expressiveness* is the property of allowing succinct statements of solutions within a problem domain. *Safety* refers to facilities which protect programmers from making common mistakes. It is interesting to note that the utility of these properties is not to provide efficient execution, but to restrict program complexity. Our discussion of programmatic scalability will adopt these three parameters as evaluation criteria for programming models, leaving efficiency to be considered as an aspect of program interaction with architectural parameters.

#### 2.1.4 Programmatic Heterogeneity

Classifying heterogeneity exclusively with respect to programming models is prone to become a statement of subjective opinion. The term is often used either with respect to hardware only, or when considering systems which integrate hardware and software. This may stem from the fact that different programming models feature different concepts, making it difficult to compare them systematically. Moreover, programmers' mental model of the operations at their disposal is highly subjective, *e.g.* it is a well known problem that programs which are obvious to their author can be incomprehensible to another reader, making it difficult to reach any consensus on how many levels of abstraction it involves. Still, addressing the heterogeneity of programming has some merit, witnessed by how heterogeneous architectures inspire programmers to develop multi-model solutions [31, 85].

Although the number of abstractions or entities identified in a programming model is not a perfect map of every idea the model may present to a programmer, it enables structured reasoning on how many concepts are considered independent in its specification. The number of *available* abstractions is obviously not in direct relation to the number actually utilized in any given program. However, our discussion of programmatic heterogeneity will use it as a measure of the potential for variability in application behavior, in order to provide an ordered relation between different models.

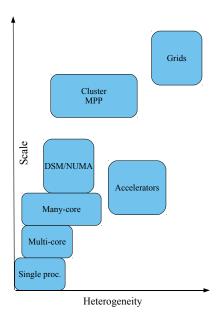

## 2.2 Architectural Map

Figure 2.1 gives an overview of several kinds of systems, related to each other by the criteria identified in Sections 2.1.1 and 2.1.2. Since creating an exhaustive, fine-grained taxonomy of parallel systems is vulnerable to rapid technology changes, systems are grouped into approximate categories. Section 2.2.1 discusses many-core systems. Section 2.2.2 discusses systems augmented with special-purpose accelerators, Section 2.2.3 discusses distributed shared memory systems, Section 2.2.4 discusses distributed memory systems, and finally, Section 2.2.5 discusses computational grids.

Figure 2.1: Map of architectural scalability and heterogeneity

#### 2.2.1 Multi-core and Many-core Systems

Multi-core processors of autonomous units have yet to reach the same scale as large systems, but core counts are rapidly growing. Asanovic *et al.* [11] introduce the term *manycore* as an extension of this development, noting that the number of cores per chip can be expected to double with each silicon generation. Accordingly, we place the *multi-core* category in the low range of scalability, referring to the present generation of processors with relatively small numbers of processing cores. The computational cores of these processors are typically identical, but their overall performance becomes heterogeneous due to variable access cost and contention effects observable on a chip level [72].

Beyond mass-market processors, the literature describes systems which warrant discussion as many-core designs. The Niagara processor [56] provides 8 units capable of 4-way thread execution. While the cost of numerical operations render this design less interesting for scientific computing purposes, we note that its degree of heterogeneity is reflected in the attention devoted to thread scheduling. The Larrabee architecture [88] promised up to 48 processing units on a chip. The architectural description argues its general programmability, as cores are based on x86 designs. Brief treatment is given to applications in physics as well as video processing, but applied benchmarks primarily address gaming applications and graphics rendering. While the Larrabee architecture has been put aside, a more recent Intel press release [50] indicates that processors of similar on-chip parallelism and core design may target high-performance computing. These systems are designed primarily for scalability, driven by the exploitation of chip area as replicated cores. As witnessed by the application sensitive design decisions made with Sun's Niagara and Intel's Larrabee, however, the balance of these designs is obviously biased towards restricting application dependent bottlenecks. Replicating cores mandates a uniform interface, so core internals must be encapsulated, corresponding to the principle of independent design. Achieving latency hiding still requires careful programming or specialized workloads.

Towards increased heterogeneity, Kumar et al. [59] point out that system-on-chip (SoC) designs apply increased transistor counts to make single-chip computing platforms from a mixture of integrated devices, but that these systems mostly allocate distinct tasks for the various subsystems. Deciding on the complexity of the replicated core in a multi-core processor is a trade-off not only because of variable application requirements, but also because of similar variability in the requirements between phases of a single application. Thus, general-purpose chip multiprocessors have both power and throughput advantages to gain from heterogeneous design. Amdahl's historic contribution [8] calls for improvements in parallel processing to be matched by a corresponding improvement in sequential processing. Woo and Lee [101] examine this with respect to many-core computing, comparing constant power budget configurations of a small number of large cores, a large number of small cores, and a large core coupled with a greater number of small ones. Their analytical model indicates that the latter combination is more energy efficient, indicating that chip-level heterogeneity may mitigate the effect of Amdahl's law. The Cell BE [42, 58] represents a commercially available heterogeneous on-chip multiprocessor with general purpose processing capabilities, consisting of a modified Power4 core, and eight synergistic processing elements, which are optimized for executing single-precision floating point operations using 128-bit wide vector instructions.

With tightly coupled cores, the heterogeneous features of the communications subsystem are limited in such systems. Although the heterogeneity of application-specific designs will be dependent on the nature of the application, both the Cell and the projections of Woo and Lee consider designs composed from at most two core designs. While the rapid growth in number of cores per die may lead to designs of more variable on-chip components, contemporary systems remain in the low range of architectural heterogeneity.

#### 2.2.2 GPGPU and Special Purpose Accelerators

Improvements in scalability on the single system level invites application-specific accelerator designs which leverage the potential increase in core count to integrate large numbers of simplified cores on a chip. Such accelerators include recent generations of graphics processors featuring in the hundreds of reduced cores [78], with improvements in general programmability. Designs like the HC-1 [24] utilize FPGA units to let users specify application-specific core capabilities. McCool[67] surveys programming models with a view towards scaling into massive parallelism on chip using graphics processing units, arguing that these are the consumer processors which currently feature the greatest amount of explicit parallelism, and that general purpose processors are likely to follow their development. Without assessing the accuracy of that prediction, the present generation of accelerated systems carries the distinction that the co-processors are designed quite differently from their host processors. While damaging to subsystem independence, this clearly caters to the principles of balance and design for scalability. Furthermore, modern graphics processors integrate scheduling hardware specialized to facilitate latency hiding by context switches. The manner in which these systems achieve scalability is tightly linked to their wider range of core designs, making them an excellent example of the trade-off between the two aspects.

#### 2.2.3 Distributed Shared Memory Systems

Laudon and Lenoski [63] argue that the scalability of the design they describe is chiefly based on the modularity of its architecture. They also present latency measurements, and descriptions of data and process migration mechanisms to maintain low communication overheads. This work appears to address scalability by arguing that it is embedded in the design, as it includes considerations of how this single, modular architecture can be applied across a range of system sizes, providing a tailored entry price point for dedicated systems with known performance parameters. The first three scalability principles in Section 2.1.1 are evidently considered, and the requirements on interconnection technology are mentioned in a section which bounds total system size to 1024 processors. Two points about this work deserve particular attention, to illuminate later discussion. The first is that the mention of "ccNUMA" in the title acknowledges the significance of a heterogeneous system property, i.e. the cost of memory access. The second is that the distributed directory scheme which implements this nonuniform communication may inherently restrict the number of processors which can be added. In their discussion of cache coherency by distributed directories, Hennessy and Patterson[43] state that the amount of information required by a straightforward directory implementation is proportional to the product of the number of memory blocks and the number of processors, and that this becomes a significant overhead for processor counts around 200. Some suggestions are made regarding how this limitation can be reduced by restricting the information stored in the directory, such as tagging a memory block as relevant for a *group* of processors. In the general case, this would imply a hierarchical approach, which is likely to increase the heterogeneity of memory access costs.

Anderson *et al.*[9] describe the CRAY T3E, another distributed shared memory architecture which makes claims to scalability. This article devotes much attention to programming techniques, but communication facilities are also described, and the principle of latency hiding features prominently in the discussion of how remote memory access has extensive support for pipelining and prefetching. Large-scale installations are described as a torus topology of up to 2048 processors. Remote memory access is facilitated through a large number of registers which bypass local memory cache to request transfer from remote locations in a given range of the shared address space. Latency figures for remote load operations are given as a small range of values, indicating that global memory access is non-uniform on this architecture as well, even though effort is made to describe how this effect can be masked by software. Common to these architectures is that the operating frequency of their processors is relatively low compared to contemporary units. According to Lusk and Chan, "the fastest machines now virtually all consist of multi-core nodes connected by a high speed network" [66], which shows that the significance of memory access cost has grown since the design of these systems. The limits of distributed shared memory architecture scalability are still of of interest, witnessed by the existence of projects like Blue Waters [34], but as such systems are exceptional cases, and exceedingly challenging to construct, we consider distributed shared memory platforms in the low thousands of processing units here.

Distributed shared memory systems are not commonly discussed in the context of heterogeneity, although considerable attention is devoted to the non-uniform cost of memory access. Performance-wise, heterogeneity is limited to similar nonuniform access costs of hierarchical memory as with multi-core systems, but with a greater number of stages leading to greater variability. With communication being the only source of heterogeneity, this class is placed in the low end of the heterogeneity spectrum.

#### 2.2.4 Distributed Memory Systems

The present generation of supercomputers is dominated by architectures featuring distributed memory and supporting the message-passing paradigm of software design. The June 2012 top 500 supercomputer list [94] sorted by architecture share shows that compute clusters and MPP architectures together compose the entire list.

Given the common creation of compute clusters from components-off-the-shelf (COTS), architectural descriptions tend to be scarce. The architecture of the cluster as such is of little academic interest beyond the description of its components. Nevertheless, some constructions like the PACS-CS [21] are documented, due to a measure of novelty in board-level construction and interconnect design. This design aims to leverage the cost-efficiency of COTS while addressing shortcomings of conventional clusters by introducing tailored solutions to improve bisection bandwidth and sustained performance figures. The use of COTS requires independent component designs, and consideration of the growing network bandwidth matches the principles of balance and design for scalability, showing that this system observes the first 3 principles. It is built to a scale of 2560 processing cores.

Although similar to clusters in the sense of supporting parallelism as the joint operation of compute units without shared resources, MPP systems feature more integrated designs between the computational units and the interconnection network. This caters more to the principles of balance and design for scalability than to independence. A prime example from this system class is the Blue Gene/L architecture [6], which features dual-processor computational nodes in a torus topology. One processor is mainly intended to cater to communication operations, but can also be explicitly programmed to perform computation. The processors operate at a relatively low frequency for the sake of power efficiency. With an appropriate interconnection network, the design can scale to 65536 computational nodes.

A more recent example is Roadrunner [13], which was the first system to achieve sustained petaflop performance with standard benchmarks. The composition of this platform breaks

down into 17 *compute units*, which are each in turn composed from 180 triblade *compute nodes*, consisting of one blade of two dual-core Opteron processors and two blades of two PowerXCell 8i processors, a version of the Cell BE with extended support for double-precision floating point operations. The full system thus contains a mixture of processing elements on the order of tens of thousands in number, with a variety of interconnection technologies on the various levels of locality. Quoting Barker *et al.* [13], "An implication of Roadrunner's deep communication hierarchy [...] is that the performance of a hybrid application is critically dependent upon the application's ability to exploit spatial and temporal locality". While the architecture's hierarchical decomposition indicates a modular design built for scalability, this limitation suggests an imbalance in the relative costs of computation and communication, as well as challenges in latency hiding.

The heterogeneity of distributed memory systems spans a great range in our classification, reflecting that it is a function both of the variability in the interconnection between component subsystems, and the heterogeneity of their internal architecture.

At the low end of the range, a common class of cluster systems is composed from multicore processors, or even multiple such processors interconnected on multiprocessor boards, creating the same amount of heterogeneity as distributed shared memory systems, with one or more additional stages of interconnection. In the middle of the range we find systems which are classified as heterogeneous cluster systems due to being composed of component systems of variable processing capacity, as well as a nonuniform interconnection network [77]. At the high end, we find systems which differ in the mixture of processing elements within each component subsystem, but to a lesser extent in the variability of these subsystems [13].

#### 2.2.5 Grids

At the far end of the architectural scalability spectrum, we find *computational grids*. These grids aim to interconnect computational resources on an abstraction level which transcends single systems, in order to provide computation as a transparent service independent of the site of program execution.

According to Foster and Kesselman [35], the scale of a computational grid should be considered along with its intended application, *e.g.* grids for distributed supercomputing are likely to be differently dimensioned compared to throughput-oriented grids which aim to increase the utilization of otherwise idle computers.

Both of these categories still contain some of the world's largest computational resources. In the case of distributed supercomputing, the Enabling Grid for E-sciencE grid infrastructure provides access to a number of processors in the hundreds-of-thousands order of magnitude [104]. The Folding@Home network is a loosely coupled system for harvesting spare computational power from the idle time of generic desktop computers. At the time of writing, the number of active donor processors also number in the hundreds of thousands [60].

While the largest grid applications are massively parallel, they also bear the distinguishing

Figure 2.2: Map of programming model scalability and heterogeneity

characteristic that they are mostly programmed using job-level parallelism, reducing the programmatic difficulty of exploiting the available resources to a pure scheduling problem. An exception to this can be found in the work of Allen *et al.* [5], which details the application of grid-enabled communication libraries to obtain performance measurements on a combination of one 1024-processor, one 256-processor and two 128-processor systems. Although this configuration is restricted to a resource consumption two orders of magnitude smaller than the greater challenges tackled in a grid context, it is interesting with respect to the principles of scalability to note that the experiences collected pay meticulous attention to the issues of load balance and masking communication cost in order to achieve the reported performance.

As computational grids cannot be restricted to any particular category of component subsystems or interconnection technology, it is difficult to discuss them in terms of their architectural properties. In light of the above examples, however, it is fitting to categorize them as extreme cases of both scalability and heterogeneity.

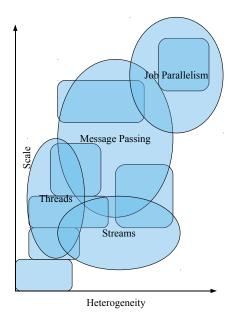

## 2.3 Programming Model Map

Based on the criteria identified in Sections 2.1.3 and 2.1.4, a high-level taxonomy of programming models can be identified in a manner similar to that of architectures. A division of programming models into *thread*, *stream*, *message passing* and *job parallelism* categories is shown in Figure 2.2, superimposed on the architectural map from Figure 2.1. This section argues their placement, beginning with threaded models in Section 2.3.1. The discussion then proceeds in order of scalability, covering stream parallelism in Section 2.3.2, and message passing in Section 2.3.3, before discussing the corner cases of hybrid models and job level parallelism in Section 2.3.4.

#### 2.3.1 Thread Parallelism

Quoting Akhter and Roberts [3], "Scalability is the challenge of making efficient use of a larger number of threads when software is run on more-capable systems". This definition is too thread-centric to generically capture scalability, even within high-performance programming, but it reflects a common perception of the challenges which come with many-core general processors. A variety of threading models are available, some are language neutral such as POSIX threads [3] or OpenMP [100], while others are related to specific environments such as *e.g.* Java or Perl. All facilitate multiple concurrent instruction streams using a shared address space, restricting threads to shared memory systems.

Explicit threading provides detailed control of fine-grained synchronization. Common model features are either mutual exclusion primitives in the form of locks and semaphores, or language extensions for marking critical sections. While utilizing such features makes programming simpler than using explicit locking, this type of synchronization is still contains a number of pitfalls which lead to common programming mistakes. In this sense, explicit threading is neither simple nor safe. Expressiveness is naturally tied to the facilities of the language featuring the threading model, but the management of synchronization leads to at least some programming unrelated to the problem domain.

OpenMP provides a simple set of directives which can be applied to imperative programming constructs such as loops and sequential blocks. These allow the programmer to guarantee that sections are free of dependencies, automating thread management and identification of synchronization requirements. This improves simplicity and safety of threading with little interference in expressiveness. However, hiding the cost of thread management from the programmer conceals performance parameters which are critical to scalability.

The class of architectures supporting threaded programs spans a wide range of scales, encompassing installations from single-core *hyperthreading* processors with limited support for concurrency, to large systems with distributed shared memory, which may execute thousands of threads. This large footprint in the architectural landscape makes threading a convenient model for inclusion in hybrid programming approaches, such as those described by Rabenseifner [85] and Barker *et al.* [13].

Thread programming is a lightweight approach to parallelism, as threads have only a small local workspace within a shared program state. The shared program state provides implicit communication, as any thread can read values modified by another, requiring concurrent execution to control cases where it results in nondeterminism. Thus, thread control can be provided by a small set of constructs, placing it low in the heterogeneity spectrum.

The POSIX thread interface focuses on synchronization primitives, providing mutual exclusion by explicit locking of memory locations, signal delivery between threads, and waiting for thread completion. Collective operations include barrier synchronization primitives and broadcast signals, but higher-order operations require explicit programming. OpenMP also provides mutual exclusion, but at a higher level of abstraction, as critical sections can be marked in the code without explicit locking procedures. Like POSIX threads, OpenMP also provides signalling and barrier synchronization, and collective operations are extended to include reductions. The task of spawning threads is abstracted almost completely, with brief mnemonics to indicate independent program sections. Finally, some scheduling parameters can be controlled, and a high-resolution timer is provided for profiling. This raises level of abstraction relative to POSIX thread programs, but also complicates cost analysis, *e.g.* by introducing barriers which are implicit in the code.

#### 2.3.2 Stream Parallelism

*Streaming* models are connected to systems which integrate accelerators and commodity processors. Large computational demands are divided into independent data streams, and the computation is expressed as a *kernel*, which is a small algorithm for processing a segment at the head of a stream. This choice of program unit is similar to a thread, by representing a light-weight invocation of a function on a small amount of data. However, kernels have restricted communication and synchronization facilities. The performance gap between memory access and computation requires a level of *numerical intensity*, *i.e.*, each element fetched must undergo a number of computational operations in order to amortize the cost of fetching it.

Extensions of traditional paradigms require that functions can address program global state: if the programming model does not express this, it requires automatic detection of the data set a function acts on. Detecting this requires complex data-flow analysis [2], and the exploitable benefit must be conservative, even when successful. Without guarantees on locality of reference, program translation leads to bursts of read-modify-write sequences [67], which is bad for pipelining and numerical intensity.

Stream processing explicitly recognizes that a kernel consumes a restricted number of data elements. This comes at the expense of some amount of programmability, leading to streams often being embedded in conventional languages. An early example of this approach can be found in the software system of the Imagine stream processor[52], which separates the *StreamC* and *KernelC* extensions to the C programming language to take advantage of a dedicated processor architecture. Approaches which leverage graphics processors for general purpose computation are presently undergoing rapid development. Starting from a library approach using OpenGL, Adinetz [1] summarizes how its inconvenience for general computations led to a wealth of higher-level approaches, such as CUDA [78], Cg and Sh [67]. Developments like the Imagine architecture have led to similar ideas also in the embedded applications space [86]. Less GPU-centric approaches such as the programming toolchain of the Cell Broadband Engine [58] and OpenCL [41] also exist.

The specific designs of such approaches change quickly, as seen from the 2006 press re-

lease regarding the AMD Close-to-Metal technology [7] and its subsequent abandonment in 2008 [97]. For the purposes our discussion, the defining characteristic of all these approaches is the emphasis on computational kernels, and that with the exception of OpenCL, they address problems of a scale which is solvable on a small number of processing units each featuring a high number of parallel components.

Programming models which couple existing languages with architecture-specific extensions go far with respect to expressiveness, assuming their use within appropriate application domains. Simplicity and safety are improved by the move from adapting problem descriptions for graphics pipelines to more general tools. Still, programming these models still requires special training even for trained programmers, indicating that performance concerns still receive more attention than simplicity and safety so far.

The necessity of expressing statements about streams makes these models more heterogeneous than threading models. As an example, NVIDIAs CUDA model [78] features not only synchronization and the stream abstraction, but also has facilities for event handling, management of various kinds of memory corresponding to the type of processor, and distinguishes between graphics devices and host processors. Taken to an extreme, the two languages of the Imagine system [52] separates statements regarding the computation of a kernel and the scheduling of streams unto execution devices into two disjoint language extensions. Although this approach is less common in other models, it provides a poignant example of the need for varied constructs in a stream programming context.

#### 2.3.3 Message Passing

Message passing found utility before the emergence of true concurrency in commodity computing: computation as an exchange of messages is central to the SmallTalk and Erlang languages, amongst others. According to Kay [53], it was motivated by a desire to "find a better module scheme for complex systems[...]". This not only for improves simplicity and expressiveness, but also fits the modularity principle of scalable design.

Erlang originates as a control language for distributed systems in telecommunications, where operating a large number of devices is business critical. Armstrong summarizes scalability as the requirement that "adding a new machine should be a simple operation that does not require large changes to the application architecture" [10], emphasizing encapsulation over performance. A different perspective is offered by Gropp, Lusk and Skjellum in their description of MPI: "Scalability analysis is the estimation of the computation and communication requirements of a particular problem and the mathematical study of how these requirements change as the problem size and/or number of processes changes" [40].