# Prototyping a Reconfigurable Architecture suitable for Multitasking

Kjetil Wathne Oftedal

Master of Science in Computer Science Submission date: July 2010 Supervisor: Gunnar Tufte, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

# **Problem Description**

Reconfigurable computers offers a large speed-up compared to traditional processor based computers. The speed-up in such machines is a result of including customized hardware for time consuming computation. Although reconfigurable computers offer a considerable speed-up when the reconfigurable parts are configured to a specific computation, the concept requires that the reconfigurable parts of the machine change when the problem changes. In most of today's computers a multitasking approach is taken to utilize the computation power. To include reconfigurable hardware in a multitasking machine the reconfigurable parts must be able to change according to the requirement of each task. Such change of configuration requires effective switching between configurations.

In "Multitasking on a reconfigurable computing system" an architecture for a system capable of integrating reconfigurable computation with a multitasking system was proposed. To further investigate the proposed concept it is required to take the abstract description to a detailed level that can produce a working prototype. To be able to move to a detailed level that can be modeled and implemented in existing FPGA technology the computational reconfigurable building blocks must be defined together with logic that can meet the requirement for reconfiguration in a multitasking environment.

The goal of this thesis is to propose computational building blocks together with a reconfiguration system that can support the architecture proposed in "Multitasking on a reconfigurable computing system" at a level that can be prototyped and modeled.

Assignment given: 18. January 2010 Supervisor: Gunnar Tufte, IDI

### Abstract

Integrating reconfigurable computing hardware into general purpose computers offers promise of performance improvement. General purpose computers allows for a large amount of multitasking, as such, the reconfigurable hardware integrated into such a system should also support multitasking. This requires a low overhead reconfiguration method that supports preemption of tasks running on reconfigurable hardware. To investigate methods that can integrate reconfigurable hardware into a multitasking machine an architecture for a reconfigurable device is proposed. In this work the proposed architecture is taken to prototype level. This includes a definition of the computational properties of the basic reconfigurable blocks, a reconfiguration method that can fit within the requirements of multitasking, a configuration format that allows for backwards binary compatibility, and support for rudimentary control flow. The resulting prototype system has been tested and evaluated.

## Preface

This thesis was written at the Department of Computer and Information Science, Norwegian university of Science and Technology. I would like to thank my supervisor Dr. Gunnar Tufte for his advice and support. I would also like to thank my friends in the Computer Architecture group at IDI, especially those whom I have shared an office with for the past year.

# Contents

| 1        | Intr | oducti | ion                                    | 1        |

|----------|------|--------|----------------------------------------|----------|

|          | 1.1  | Thesis | s outline                              | 4        |

| <b>2</b> | Bac  | kgrour |                                        | <b>5</b> |

|          | 2.1  | Histor | y                                      | 5        |

|          |      | 2.1.1  | Fixed+Variable Computer                | 5        |

|          |      | 2.1.2  | Reconfigurable Computing               | 6        |

|          | 2.2  | Coupli | ing                                    | 7        |

|          | 2.3  | Granu  | larity                                 | 8        |

|          | 2.4  | Multit | asking                                 | 9        |

|          | 2.5  | Relate | ed technology and architectures        | 12       |

|          |      | 2.5.1  | FPGA                                   | 12       |

|          |      | 2.5.2  | Piperench                              | 13       |

|          |      | 2.5.3  | Wavefront array processor              | 15       |

|          |      | 2.5.4  | RISC processors                        | 17       |

| 3        | Syst | tem ov | verview                                | 19       |

|          | 3.1  |        |                                        | 19       |

|          | 3.2  | Device | e overview and properties              | 20       |

|          |      | 3.2.1  |                                        | 20       |

|          |      | 3.2.2  |                                        | 22       |

|          |      | 3.2.3  |                                        | 23       |

|          |      | 3.2.4  |                                        | 26       |

|          |      | 3.2.5  | - ·                                    | 27       |

|          | 3.3  | Cell a |                                        | 29       |

|          |      | 3.3.1  | Reconfiguration issues and granularity | 29       |

|          |      | 3.3.2  |                                        | 30       |

|          |      | 3.3.3  | Branching                              | 31       |

|          | 3.4  | Recon  | figuration system                      | 34       |

|          |      | 3.4.1  | - ·                                    | 34       |

|          |      | 3.4.2  | Grid interconnect                      | 35       |

|          |      | 3.4.3  |                                        | 37       |

| <b>4</b> | Imp | lementation: Device version 1                                                                                  | <b>39</b> |

|----------|-----|----------------------------------------------------------------------------------------------------------------|-----------|

|          | 4.1 | Grid                                                                                                           | 39        |

|          |     | 4.1.1 Asynchronous                                                                                             | 39        |

|          |     | 4.1.2 Synchronous                                                                                              | 40        |

|          | 4.2 | Cell                                                                                                           | 41        |

|          |     | 4.2.1 Internal dataflow management                                                                             | 43        |

|          |     | 4.2.2 ALU                                                                                                      | 43        |

|          |     | 4.2.3 Multiplication and division                                                                              | 44        |

|          | 4.3 | Reconfiguration system                                                                                         | 44        |

|          |     | 4.3.1 Reconfiguration master                                                                                   | 45        |

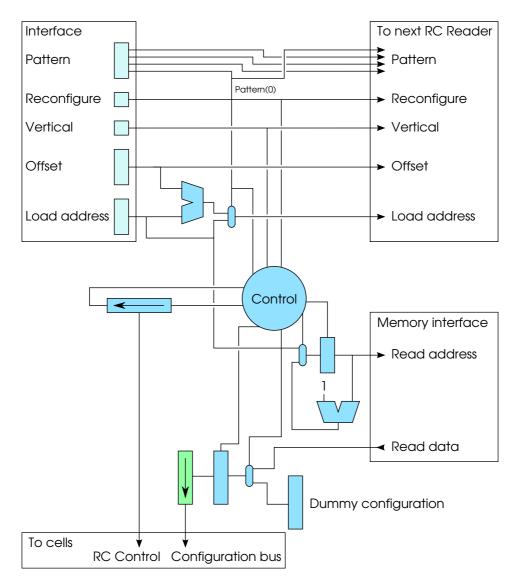

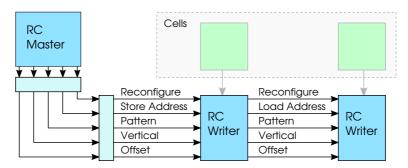

|          |     | 4.3.2 Reconfiguration reader                                                                                   | 50        |

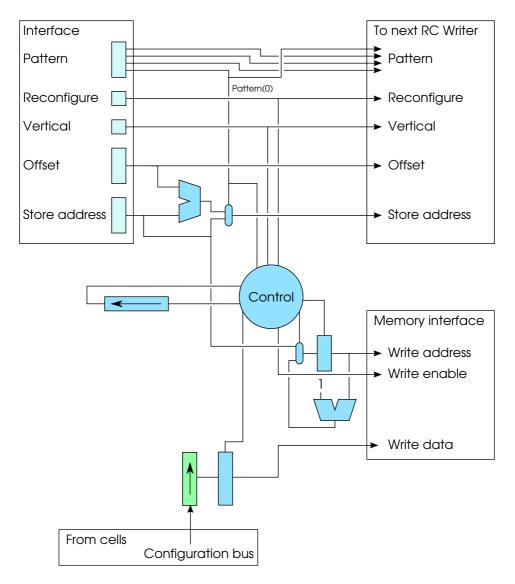

|          |     | 4.3.3 Reconfiguration writer                                                                                   | 55        |

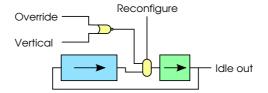

|          |     | 4.3.4 Reconfiguration register                                                                                 | 58        |

|          | 4.4 | Runtime manager                                                                                                | 60        |

| <b>5</b> | Imp | lementation: Device version 2                                                                                  | 63        |

|          | 5.1 | Cell version 2                                                                                                 | 63        |

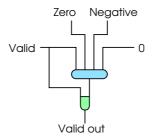

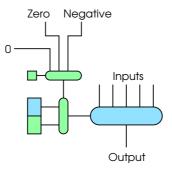

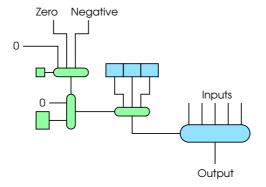

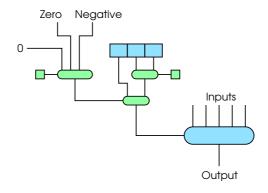

|          |     | 5.1.1 Output valid                                                                                             | 64        |

|          |     | 5.1.2 Output switching                                                                                         | 65        |

|          |     | 5.1.3 Input selection                                                                                          | 68        |

|          |     | 5.1.4 State write policy                                                                                       | 69        |

|          |     | 5.1.5 Cell version 2 architecture                                                                              | 70        |

|          | 5.2 | Reconfiguration system version 2                                                                               | 70        |

|          |     | 5.2.1 Reconfiguration master                                                                                   | 70        |

|          |     | 5.2.2 Reconfiguration reader                                                                                   | 73        |

|          |     | 5.2.3 Reconfiguration writer                                                                                   | 75        |

|          |     | 5.2.4 Reconfiguration register                                                                                 | 75        |

| 6        | Imp | lementation: Other                                                                                             | 79        |

|          | 6.1 | Assembler                                                                                                      | 79        |

|          |     | 6.1.1 Language                                                                                                 | 79        |

|          |     | 6.1.2 Software architecture                                                                                    | 86        |

| 7        | Res | ilts and testing                                                                                               | 91        |

|          | 7.1 | Testing                                                                                                        | 91        |

|          |     | 7.1.1 Component testing $\ldots \ldots \ldots$  | 91        |

|          |     | 7.1.2 Device testing $\ldots$ | 92        |

|          | 7.2 | Synthesis results                                                                                              | 95        |

|          |     | 7.2.1 Size version 1                                                                                           | 95        |

|          |     | 7.2.2 Clock speed version $1 \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                   | 95        |

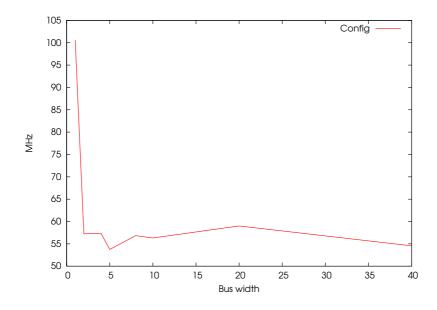

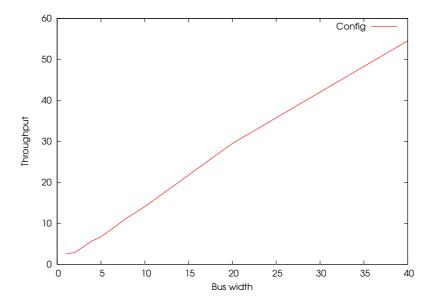

|          |     | 7.2.3 Reconfiguration bus speed exploration                                                                    | 97        |

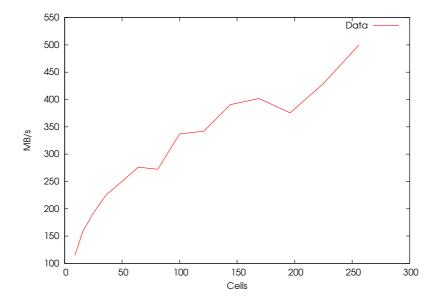

|          |     | 7.2.4 Data consumption development                                                                             | 101       |

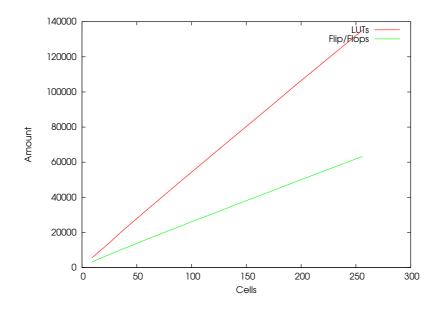

|          |     | 7.2.5 Size version 2                                                                                           | 101       |

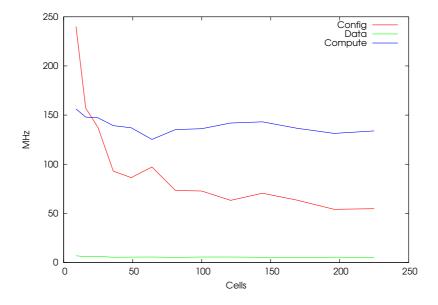

|          |     | 7.2.6 Clock speed version 2                                                                                    | 102       |

|          |     | 7.2.7 Speed comparison                                                                                         | 102       |

|          | 7.3 | Other results                                                                                                  | 104       |

|              |      | 7.3.1    | Configuration size          |       | ••• |     | • | • • | • | ••• | • • | · | • • | • | • | · | • | • • | . 104 |

|--------------|------|----------|-----------------------------|-------|-----|-----|---|-----|---|-----|-----|---|-----|---|---|---|---|-----|-------|

| 8            | Disc | cussion  | and conclusion              |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     | 107   |

|              | 8.1  | Device   | performance                 |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     | . 107 |

|              | 8.2  | Comp     | utational properties        |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     | . 109 |

|              | 8.3  | -        | l branching                 |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

|              | 8.4  | Config   | uration scaling             |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     | . 111 |

|              | 8.5  |          | uration compatibility       |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

|              | 8.6  | Recont   | figuration system .         |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     | . 113 |

|              | 8.7  | Conclu   | ision                       |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     | . 114 |

|              | 8.8  | Future   | e work                      |       |     |     |   |     | • |     |     |   |     | • |   | • |   |     | . 115 |

| Δ            | Mul  | ltiplica | tion and division           |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     | 121   |

|              | A.1  |          | blication algorithm .       |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

|              | A.2  |          | on algorithm                |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

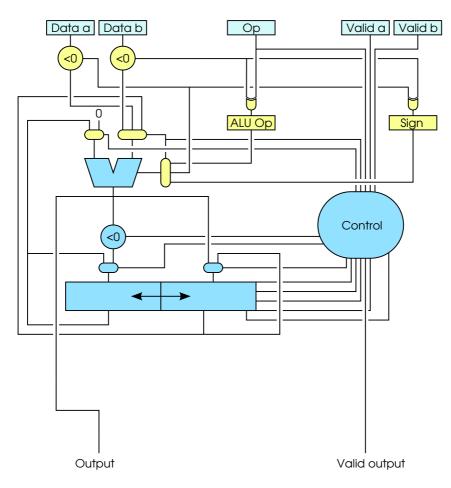

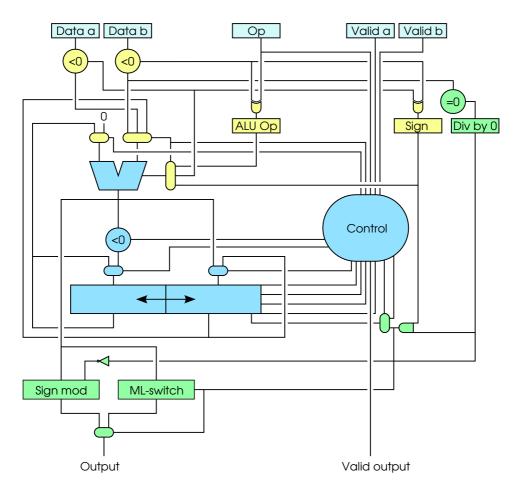

|              | A.3  |          | are implementation          |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

|              |      | A.3.1    |                             |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

|              |      | A.3.2    | Signed operation .          |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

|              |      | A.3.3    | Division by zero .          |       |     |     |   |     | • |     |     |   |     | • |   |   |   |     | . 130 |

| в            | Reg  | ister a  | nd configuration l          | avout | F   |     |   |     |   |     |     |   |     |   |   |   |   |     | 135   |

| D            | B.1  |          | n interface                 |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

|              | D.1  | B.1.1    | Status register             |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

|              |      | B.1.2    | 0                           |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

|              |      | B.1.3    | Auxiliary control re        |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

|              | B.2  | Config   | $uration$ $\ldots$ $\ldots$ |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

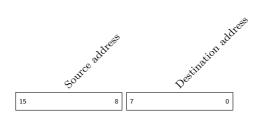

|              |      | B.2.1    | Header                      |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

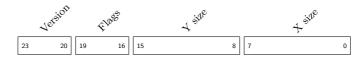

|              |      | B.2.2    | Configuration versio        |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

|              |      | B.2.3    | Configuration version       |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

| $\mathbf{C}$ | Ass  | embler   | Grammar                     |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     | 143   |

| Б            | -    |          |                             |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

| D            |      | overv    |                             |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     | 145   |

|              |      |          | n independent compo         |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

|              |      |          | n 1 components              |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     |       |

|              | D.3  | Versio   | n 2 components              |       | • • | • • | • |     | • | ••• | • • | · | • • | • | • | · | • | • • | . 152 |

| $\mathbf{E}$ | Cod  | le       |                             |       |     |     |   |     |   |     |     |   |     |   |   |   |   |     | 155   |

# List of Figures

| 2.1  | Simple logic block                | 6  |

|------|-----------------------------------|----|

| 2.2  | Coupling                          | 8  |

| 2.3  | Granularity                       | 9  |

| 2.4  | Multitasking                      | 10 |

| 2.5  | Field Programmable Gate Array     | 12 |

| 2.6  | Piperench reconfiguration         | 14 |

| 2.7  | Wavefront array processor         | 16 |

| 3.1  |                                   | 20 |

| 3.2  | Nearest neighbor dataflow         | 21 |

| 3.3  | Reconfiguration wave              | 22 |

| 3.4  | Grouped scaling                   | 24 |

| 3.5  | 1 0                               | 25 |

| 3.6  | 0                                 | 27 |

| 3.7  | Branching                         | 31 |

| 3.8  | Branch-based load                 | 32 |

| 3.9  | Cells load capability             | 33 |

| 3.10 | Reconfiguration system overview   | 34 |

| 3.11 | Reconfiguration interconnect      | 35 |

| 3.12 | Cell reconfiguration interconnect | 36 |

| 3.13 | Storage formats                   | 37 |

| 4.1  |                                   | 42 |

| 4.2  | 0                                 | 46 |

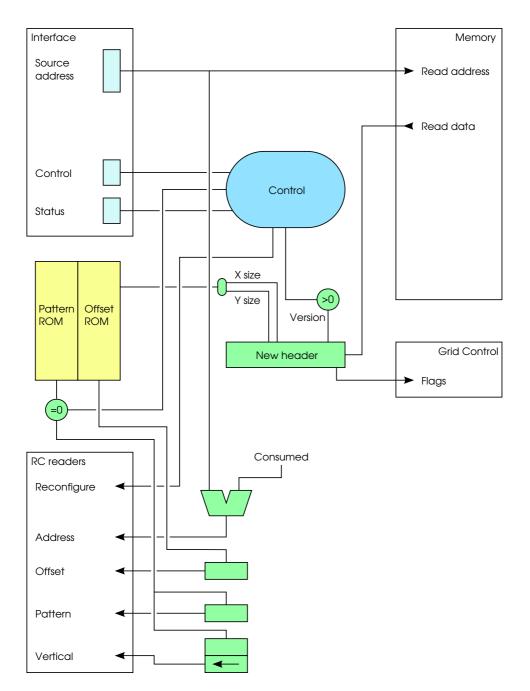

| 4.3  | 0                                 | 48 |

| 4.4  | 0                                 | 51 |

| 4.5  |                                   | 52 |

| 4.6  | 0                                 | 53 |

| 4.7  | 0                                 | 55 |

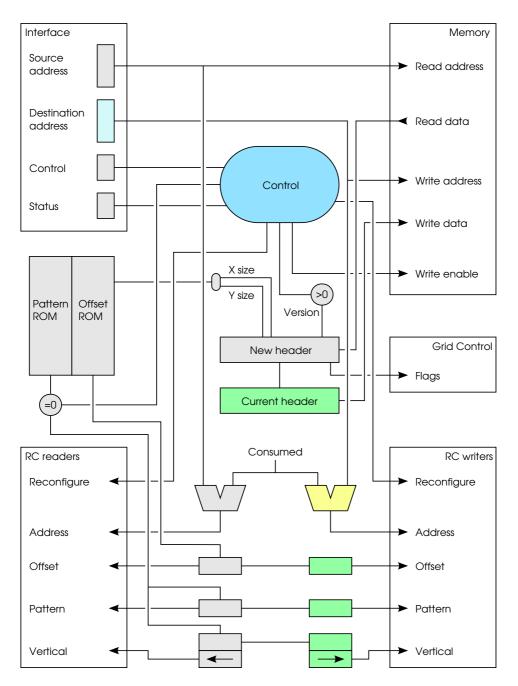

| 4.8  | Reconfiguration writer            | 57 |

| 4.9  | Reconfiguration register          | 59 |

| 4.10 | Runtime manager                   | 60 |

| 5.1  | 1                                 | 64 |

| 5.2  | Conditional output switch         | 65 |

| 5.3        | Conditional output switch                                                                                                                                                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.4        | Conditional output switch                                                                                                                                                |

| 5.5        | Conditional output switch                                                                                                                                                |

| 5.6        | Input selection                                                                                                                                                          |

| 5.7        | Write policy selection                                                                                                                                                   |

| 5.8        | Cell version 2                                                                                                                                                           |

| 5.9        | Reconfiguration master version 2                                                                                                                                         |

| 5.10       | Reconfiguration reader version 2                                                                                                                                         |

| 5.11       | Reconfiguration writer version 2                                                                                                                                         |

|            | Reconfiguration register version 2                                                                                                                                       |

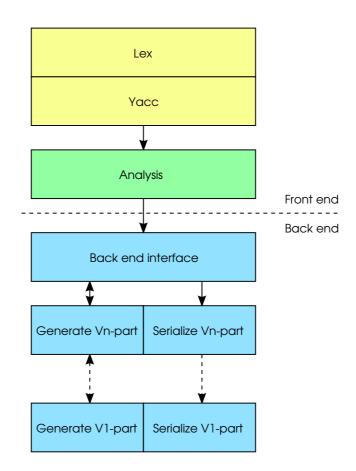

| 6.1        | Assembler architecture                                                                                                                                                   |

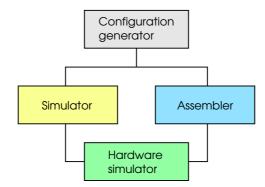

| 7.1        | System simulator based implementation testing                                                                                                                            |

| 7.2        | Configuration generation                                                                                                                                                 |

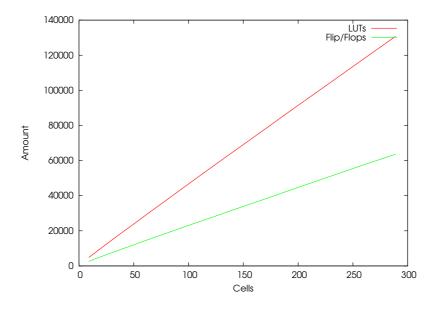

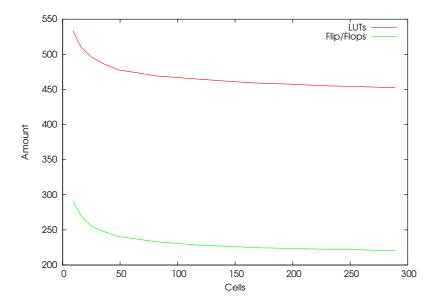

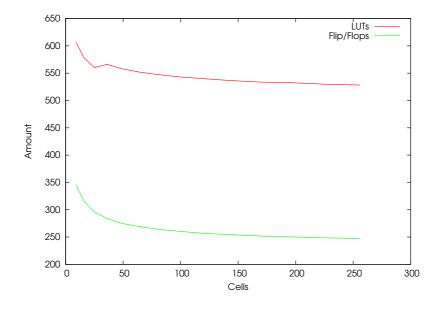

| 7.3        | Resource utilization (version 1)                                                                                                                                         |

| 7.4        | Normalized resource utilization (version 1)                                                                                                                              |

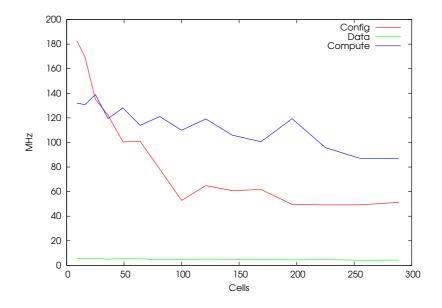

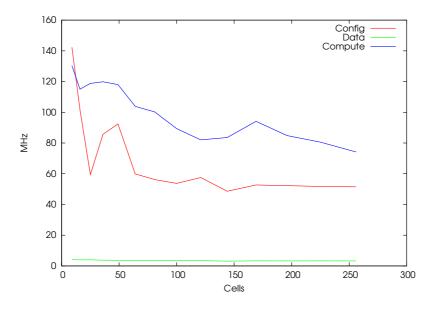

| 7.5        | Clock speed estimates (version 1)                                                                                                                                        |

| 7.6        | Clock speed estimates with cell hierarchy (version 1)                                                                                                                    |

| 7.7        | Clock speed optimized results                                                                                                                                            |

| 7.8        | Reconfiguration bus speed                                                                                                                                                |

| 7.9        | Reconfiguration bus throughput                                                                                                                                           |

| 7.10       | Data consumption development                                                                                                                                             |

| 7.11       | Resource utilization (version 2)                                                                                                                                         |

| 7.12       | Normalized resource utilization (version 2)                                                                                                                              |

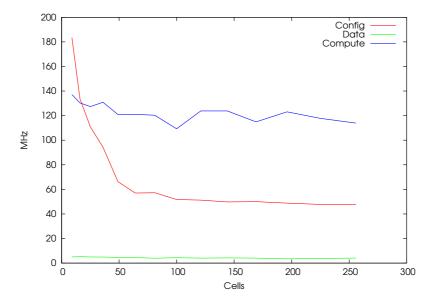

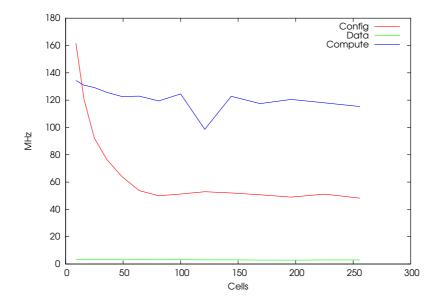

|            | Clock speed estimates (version 2) $\ldots \ldots \ldots$ |

| 7.14       | Clock speed estimates with cell hierarchy (version 2) 103                                                                                                                |

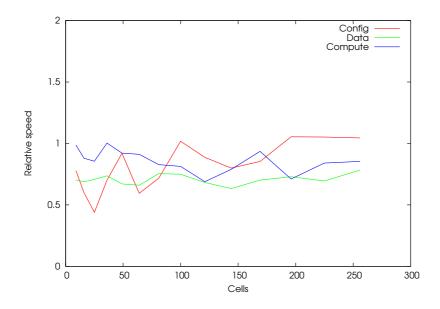

|            | Relative speed change                                                                                                                                                    |

| 7.16       | Cell configuration size development                                                                                                                                      |

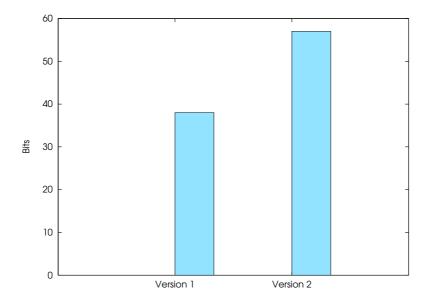

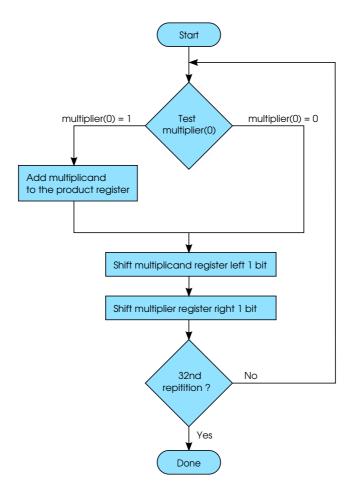

| A.1        | Multiply operation flowchart                                                                                                                                             |

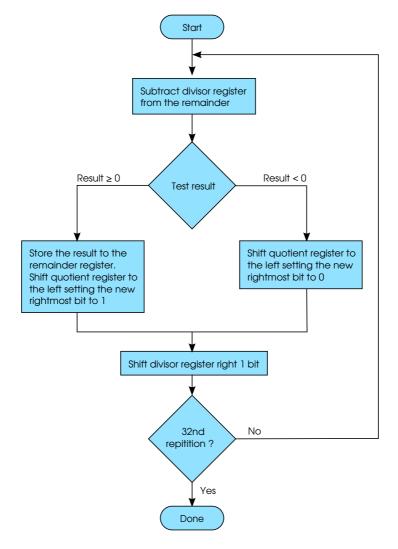

| A.1<br>A.2 | Divide operation flowchart                                                                                                                                               |

|            |                                                                                                                                                                          |

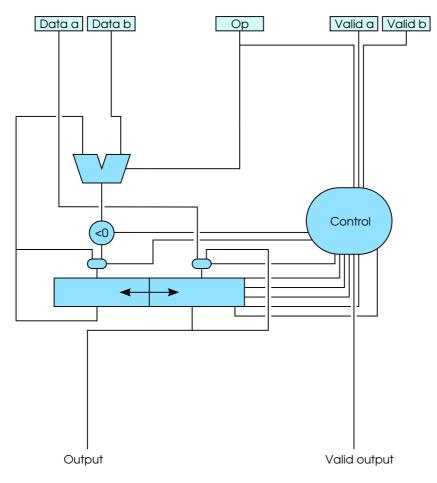

| A.3        | Unsigned multiplier and divider                                                                                                                                          |

| A.4        | Signed multiplier and divider $\dots \dots \dots$                        |

| A.5        | Complete multiplier and divider                                                                                                                                          |

| B.1        | Status register                                                                                                                                                          |

| B.2        | Control register                                                                                                                                                         |

| B.3        | Auxiliary control register                                                                                                                                               |

| B.4        | Header layout                                                                                                                                                            |

| B.5        | Flags field                                                                                                                                                              |

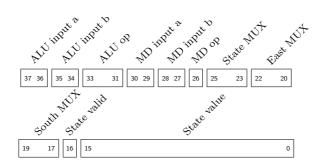

| B.6        | Configuration version 1                                                                                                                                                  |

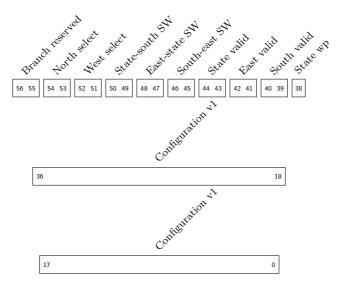

| B.7        | Configuration version 2                                                                                                                                                  |

# List of Tables

| 3.1        | Instruction listing            |

|------------|--------------------------------|

| B.1        | ALU MUX encoding               |

| B.2        | ALU opcode encoding            |

| B.3        | MD MUX encoding                |

| B.4        | State/output MUX encoding      |

| B.5        | Input select policy encoding   |

| B.6        | Switch policy encoding         |

| B.7        | Valid policy encoding          |

| B.8        | State write policy encoding    |

| D.1        | Addersubtracter                |

| D.1<br>D.2 | Addersubfracter                |

| D.2<br>D.3 | Multiplydivide         140     |

| D.4        | MUX                            |

| D.4<br>D.5 | Shifter                        |

| D.6        | Shift register                 |

| D.7        | Cell                           |

| D.8        | Reconfiguration master         |

| D.9        | Reconfiguration reader         |

| D.10       | Reconfiguration writer         |

|            | Reconfiguration register       |

|            | Reconfigurable processing unit |

|            | Cell                           |

| D.14       | Reconfiguration master         |

| D.15       | Reconfiguration reader         |

| D.16       | Reconfiguration writer         |

| D.17       | Reconfiguration register       |

| D.18       | Reconfigurable processing unit |

### List of abbreviations

ALU Arithmetic Logic Unit

ASIC Application-specific integrated circuit

${\bf BNF}$  Backus-Naur Form

CAL Configurable Array Logic

**CISC** Complex Instruction Set Computing

**CLB** Configurable Logic Block

**CPU** Central Processing Unit

**DMA** Direct Memory Access

**DSP** Digital Signal Processing

FIFO First In First Out

FPGA Field Programmable Gate Array

FLEX Fast Lexical Analyzer

FF Flip Flop

**IO** Input/Output

LSB Least Significant Bit

${\bf LUT}$ LookUp Table

MAC Multiply ACcumulate

**MD** Multiply Divide

**MIPS** Microprocessor without Interlocked Pipeline Stages

MSB Most Significant Bit

MUX Multiplexer

**PE** Processing Element

${\bf RAM}\,$  Random Access Memory

$\mathbf{RC}$  Reconfigurable Computing

**ROM** Read-Only Memory

${\bf RPU}$  Reconfigurable Processing Unit

**RISC** Reduced Instruction Set Computing

**SPARC** Scalable Processor ARChitecture

${\bf SRAM}$  Static Random Access Memory

${\bf VHDL}~{\rm VHSIC}$  Hardware Description Language

**VHSIC** Very High Speed Integrated Circuits

**WAP** Wavefront Array Processor

YACC Yet Another Compiler-Compiler

# Chapter 1 Introduction

Reconfigurable hardware allows for the potential speedup of applications, as the hardware can be tailored to increase the execution speed of specific operations the application performs. This is referred to as reconfigurable computing. The speedup is achieved by removing generality in the hardware used to perform the computational intensive parts of the application.

Less general circuitry can employ several techniques to outperform a conventional general purpose processor. It can perform operations that operates on data widths that better suit a specific application. Constants can be integrated into the circuitry to increase the speed of said circuitry, in addition to reducing the required hardware resources. Application specific pipelines of considerable depth can be implemented which would increase the throughput of the hardware.

On the other hand it is hard to implement an entire application in hardware. Hence, the computational intensive parts should be mapped to reconfigurable hardware, and the parts that is dominated by control flow should be run on a conventional general purpose processor. Further, it must be decided how reconfigurable hardware should be allocated to applications.

Adding reconfigurable hardware for each application that can utilize such hardware to a computing system might be an option. However, this is unlikely to be effective in terms of cost and area consumption. It is therefore appealing to reuse the same hardware resources between applications. This requires that the hardware is dynamically reconfigurable, which is the ability to reconfigure hardware after it has been initialized with a default configuration. Another requirement is that the reconfigurable hardware is general enough to support the computations the different applications want to execute.

Allocating the reconfigurable hardware to a single application at the time is a simple solution that allows hardware reuse. Unfortunately, this matches the usage patterns of modern computing systems poorly. When an application is allocated the reconfigurable hardware, and will perform a large amounts of computations with it, the hardware will be monopolized by a single application for extended periods of time. In a multitasking environment, other applications might then be forced to wait until this application terminates. This is unacceptable as this wait period might eliminate any performance that could be gained by running on reconfigurable hardware.

Performing multitasking in a manner that resembles the general purpose processor approach is appealing. This would require that the state of the reconfigurable hardware is stored in memory, and then reconfiguring the hardware to suit the needs of another application. Unfortunately, this is not feasible. The reason for this is that the time required for reconfiguration the most common reconfigurable hardware, that is the Field Programmable Gate Array (FPGA), is prohibitively high. This is summarized in the following quote:

Studies estimate that, in some cases, reconfiguration time alone occupies approximately 25 to 98 present of the the total execution time of a reconfigurable computing application.

- Reconfigurable Computing: The theory and practice of FPGA-based computing [HD07]

There is also no standard method for retrieving and restoring state of such a device. A method for retrieving and restoring the state of a FPGA was attempted by examining the configuration stream of a FPGA in *Preemptive Multitasking on FPGAs* [LMSS00]. The idea was to filter out the state of the readback bitstream from an FPGA, and inserting this state in the configuration bitstream when the task was to be resumed. The problem with this is that the state filtering and configuration splicing would require knowledge of the FPGA configuration format. This format is unlikely to be the same between FPGA families. In addition the filtering and splicing operation would consume computational resources and could increase the already prohibitively long configuration time.

Another possibility is dividing the available reconfigurable hardware into smaller configurable regions, and allocating these regions to applications. The applications would then be able to use the reconfigurable hardware in parallel, and in effect achieve true multitasking. These smaller regions will also impact the configuration time. As a smaller region contains less hardware resources the configuration time would be reduced. The cost of this is not surprisingly that the available area for a single configuration is smaller.

If an application cannot fit all the desired computations within one region, it must use several. Then the problem that this method was trying to avoid might reassert itself, as a single application might require all the available regions. A similar problem might also occur if there are more applications trying to use reconfigurable hardware than there are regions available. Then it would still be required that a the reconfigurable hardware support retrieving and restoring the state of a running configuration if equal access to the hardware resources is to be achieved.

Hence, to achieve multitasking on reconfigurable hardware it is important that a low overhead reconfiguration method is utilized. One such method is presented in *A Time-Multiplexed FPGA*. Several configuration is stored on-chip. These configurations a distributed throughout the reconfigurable hardware in such a manner that the active configuration can be switched instantaneously. However, the extra storage required reduces the amount of hardware that contributes to computation. When there are more applications requiring the use of reconfigurable hardware than there are room for on-chip, additional challenges occur. The period required for a reconfiguration is still high. However, in terms of hardware utilization this can be masked, as a configuration can be loaded into one an inactive storage area, while another configuration performs computation.

These existing approaches are general in nature, and can be used in any hardware system. However, if the reconfigurable hardware is integrated into a general purpose computer, some additional considerations can be made. General purpose processors perform multitasking by allocating time slots to different tasks. This gives the tasks some amount of equality in terms of computation time available to each task.

However, letting a task occupy the entire time slot that has been allocated to it might reduce processor utilization. The cause of this is usage of virtual memory systems, and Input/Output (IO) operations performed against slower storage units. The processor is much faster than the storage unit. As such, the processor would sit idle whenever a task performs IO operations.

Switching task when an IO operation is performed is likely to increase processor utilization, as another task can use the processor while the IO operation is being performed. The utilization reduction caused by virtual memory system is very similar. This is caused by page misses, which occurs when some task tries to access a memory page that has been moved to secondary storage. In fact, this also causes IO operations to be performed, when this page is retrieved from secondary storage.

This problem is not exclusive to general purpose processors in a conventional computing system. If reconfigurable hardware that operates on memory is integrated into computer, that uses a virtual memory system, this hardware would also be affected. A low overhead reconfiguration technique can therefore increase the utilization of reconfigurable hardware, as other tasks can be allowed to use the hardware, when the current task triggers an IO operation.

Increasing the hardware utilization alone might not be enough. Using the same time slot approach as general purpose processors on reconfigurable hardware will also give more predictable response times for the tasks utilizing such hardware. The effect of this is the harmonization of scheduling on general purpose processors and reconfigurable hardware. As such, the existing scheduling principles that have been developed for general purpose processors could be used with reconfigurable hardware to some extent.

The problem of multi-tasking in a dynamically reconfigurable RC context is largely unsolved.

- High-Performance Embedded Architecture and Compilation Roadmap 2007  $[\mathrm{BLM}^+07]$

The preceding quote illustrates that this harmonization might not be trivial, as the multitasking part of reconfigurable computing is unresolved. Some approaches to this multitasking has been presented already. These approaches have strengths and weaknesses, and the basis for them is the reconfiguration overhead that exist in reconfigurable hardware.

None of these approaches have taken the characteristics of existing computer architecture into account in the design. This thesis will present a low overhead reconfiguration technique that relies on overlapping the computation of two tasks. The hope is that this low overhead technique will allow for multitasking on reconfigurable hardware integrated into a mainstream computer architecture.

It has been attempted to implement the support hardware required for this reconfiguration technique, to prove that it is a feasible solution. An example reconfigurable hardware core that utilizes this reconfigurable technique has been implemented. This hardware core operates as semi-autonomous processing unit, that supports a range of computational operation combinations. One of the more interesting ones being a form of limited control flow. That is the ability to perform rudimentary branches.

As the design target is integration into a existing computer system, preserving some of the characteristics of computer programs has been attempted. The most notable is binary compatibility between device revisions.

### 1.1 Thesis outline

- **Chapter 2:** This chapter contains important background material and a brief presentation of concepts parts of the resulting architecture can be related to or is based upon.

- **Chapter 3:** Here the architecture and considerations around the implementation features is presented.

- **Chapter 4:** The implementation of the device has been performed in two stages, to demonstrate binary compatibility. This chapter presents the first system version.

- **Chapter 5:** Here the second system version is presented. The first version is extended with the ability to perform rudimentary branching.

- Chapter 6: Support software is presented in this chapter.

- **Chapter 7:** Here the testing procedures is outlined. In addition the results of synthesizing the hardware are illustrated.

- **Chapter 8:** This chapter contains a discussion of the implemented hardware and concepts. Additionally the conclusion and future work is presented.

- **Appendix A:** This appendix describes the hardware implementation of a combined multiplication and division unit.

- **Appendix B:** This appendix contains detailed data of the configuration bitstream used, and layout of important system interfaces.

- Appendix C: Here the grammar for the system assembler is shown.

- **Appendix D:** This appendix contains an overview of the tests performed.

- Appendix E: This appendix contains the code required for system reproduction.

### Chapter 2

## Background

### 2.1 History

#### 2.1.1 Fixed+Variable Computer

In the late 1950s/early 1960s, Gerald Estrin observed that even though faster computers were being built, the number of discovered problems that could not be solved were increasing. The limiting factor being the amount of time required to solve the problem. This time limitation was caused by several factors; the cost of using a computer for an extended amount of time could be too high compared to the value of the solution. If there was some sort of real-time demand on solving the problem, the solution might not be valid or useful, when the computation was eventually completed. Another problem emerges if the computation requires a larger amount of time than the computer's mean time between component failure [Est60].

To overcome these problems, special-purpose hardware could be built that achieved significantly higher performance than that of a general purpose computer. With this in mind, Gerald Estrin formulated the following goal for the *Fixed+Variable Computer*:

To permit computations which are beyond the capabilities of present systems by providing an inventory of high speed substructures and rules for interconnecting them such that the entire system may be temporarily distorted into a problem oriented special purpose computer. - Gerald Estrin [Est60]

The *Fixed+Variable Computer*, as the name suggest, consists of two parts: a fixed and a variable part. The fixed part would typically be a general purpose computer. This would handle IO in addition to providing a stable programming interface, so computer scientists would not be discouraged from developing complex programs by a continuously changing intruction set.

The variable part would be a collection of various components optimized for certain operations. The interconnection between these components and the fixed part of the system would be decided by a set of rules. These rules would be problem specific. The resulting structure would increase performance when solving certain problems defined by the currently used interconnection.

An attempt at realization of such a computer was described in *Parallel processing in a restructurable computer system* [EBTB63]. Restructuring based upon electric switching and physical reconnection was considered. Electrical switching did not allow for physical relocation of components, and was limited with regard to the interconnect changes that can be made. Therefore physical reconnection of components was chosen. Physical reconnection was implemented by the use of printed circuits and a module based system.

Although the *Fixed+Variable Computer* could achieve performance improvements the rapid increase in computational power of general purpose computers hampered the development. The idea on the other hand would live on in the research field of reconfigurable computing.

#### 2.1.2 Reconfigurable Computing

Reconfigurable computing gained momentum by the use of technologies derived from FPGAs [CH02]. The FPGA was commercialized by Xilinx in the 1980s. The purpose of the FPGA was to be a electrically programmed device, that had the ability to perform complex computations internally. As the FPGA are generally reconfigured by the use of electronic switching they are a child of the development path originally dismissed as being too limiting by Gerald Estrin [EBTB63].

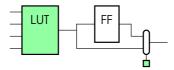

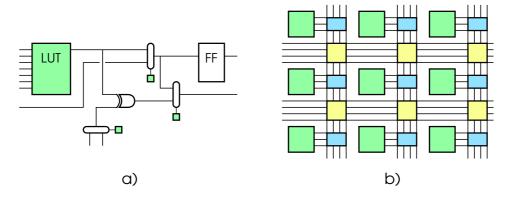

Figure 2.1: Simple logic block

In figure 2.1 a simplified version of a FPGA building block is shown. The block consists of a LookUp Table (LUT), a Flip Flop (FF) and a by-pass Multiplexer (MUX). The LUT is primarily used to emulate logic function. The FF can be used to store the result of this logic emulation. The by-pass MUX allows the result of the logic emulation to pass directly to the output of the logic block. This output can be used as an input in a different logic block and thus be used to implement logic functions that will not fit in a single LUT.

FPGA reconfiguration is often performed by changing internal Static Random Access Memory (SRAM). This internal SRAM is shown in green in figure 2.1. When the SRAM is changed the logic function emulated by the LUT is changed. In addition the interconnection network in the FPGA is changed, as represented by the MUX in figure 2.1.

Even though the early FPGAs became popular with the reconfigurable computing researchers, the FPGAs were severely limited in the amount of logic gate emulation that could be performed in a single FPGA [HD07]. The computational power of general purpose computers were also increasing at a rapid rate. This caused research to be focused on constructing systems with multiple FPGAs and problems that could not be efficiently solved with word-oriented general purpose processors.

Spatial computing is one of the reconfigurable computing approaches to solving problems faster than general purpose processors. General purpose processors rely on reusing the same execution units. Whenever a new instruction is to be executed the computation performed by a execution unit is changed, to suit this instruction. As the execution units is reused in time, this referred to as temporal computing.

Spatial computing on the other hand has execution units with fixed functionality at fixed location in space. As data flows through these units computations are performed. One of the simplest implementations of this is pipelining of operations. As each stage perform different operations on the data as it pass through the pipeline.

One of the more interesting devices of this era was the Configurable Array Logic (CAL), which was later developed into the Xilinx XC6200. This FPGA consisted of rather simple logic cells, however each logic cell could be dynamically reconfigured. This is the process where an individual cell can be reconfigured while the FPGA is operating. The ability to do this did require that the users of such features get complete access to the device configuration specification, and specification of the internal structure of the device.

Such information was usually kept secret by the FPGA manufacturers, as they feared that cheap clones of the chip could be manufactured. The information available about the XC6200, and the backing provided by Xilinx, made it popular in the reconfigurable computing research community. The available information gave the research community the ability to experiment with new applications and tools for reconfigurable devices.

### 2.2 Coupling

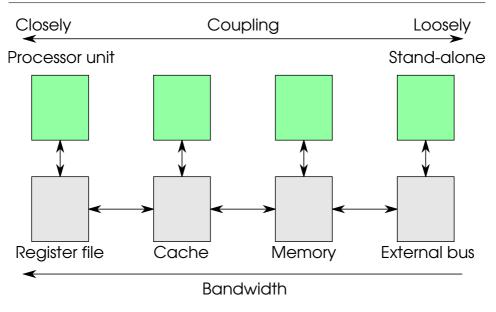

When a Reconfigurable Computing (RC) unit is to be integrated into an ordinary microprocessor based computing system, the point of connection must be decided. Where in the system the connection is made in relation to the microprocessor is referred to as coupling. In figure 2.2 some possible connection points are shown in relation to the existing memory hierarchy. The RC units are represented with green, and the existing computing system with gray.

When the RC unit is integrated as a part of the processor, or as a co-processor, the coupling in the system is referred to as close. With such a closely coupled system, large amounts of the existing memory system is shared between the microprocessor and the RC unit. The degree of sharing might be so high that even the microprocessor's register file is shared. In the other end of the coupling range is loosely coupled, in which the RC unit is connected to the system over an external bus.

The coupling degree determines several key parameters of the communication between the RC unit and microprocessor, such as communication speed, latency

Figure 2.2: Coupling

and control of the RC unit. At the bottom of figure 2.2 it is indicated that the bandwidth decreases when the degree of coupling decreases. It should be noted that this is the bandwidth between the microprocessor and the RC unit, not the RC unit's memory bandwidth as it might include a separate memory system. This might be required if the RC unit needs large amount of bandwidth, and the existing memory system is not optimized for the memory access pattern of the RC unit. However, this kind of coupling would decrease the amount of control the microprocessor can assert upon the RC unit as the information flow between them is limited by both bandwidth and latency.

### 2.3 Granularity

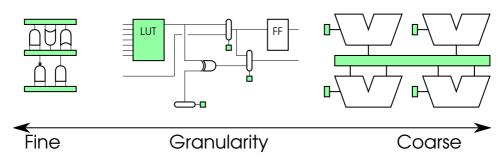

Granularity is an important property of a reconfigurable device. This refers to the operational width or rather the complexity of the reconfigurable logic blocks. The spectrum of granularity is shown in figure 2.3, with the part of the device that is reprogrammed during reconfiguration highlighted.

Fine granularity devices typically consists of basic logic gates with reconfigurable interconnect. The logic gates are often of NAND type, which can be used to implement all other binary logic functions. The major drawback of fine granularity devices is that the interconnect requirements are high compared to the implemented logic functions [MB07].

The logic blocks of a medium granularity device can perform logic operations with several inputs and outputs. As shown in the middle of figure 2.3, the logic block of a medium granularity device can consist of a LUT with several inputs

Figure 2.3: Granularity

which is connected through some reconfigurable interconnect to a FF or directly to the block output. Some basic gates are often added to the structure to speed up basic arithmetic operations.

Devices of coarse granularity contain logic blocks that can perform even more complex logical operations. These operations are often arithmetic or logic operations of a somewhat higher level, which are performed on several inputs in parallel. This allows for faster operation as the logic can be optimized for the supported operations. The amount of configuration data is also reduced as the operation that is to be performed only needs to be specified once for all the inputs to a logic block. The drawback of coarse granularity is that generality is lost as the number of implementable logic functions is reduced. Arithmetic Logic Unit (ALU), as shown in figure 2.3, is typical logic block in a coarse grained architecture. Only a small amount of configuration is needed for each ALU. The amount of configuration needed for the interconnect is also reduced. The reason for this is that multiple wires can be grouped together. The size of this group would equal the operational width of a ALU, and the group can then be routed by a small amount of bits.

Such a reduction in the configuration size might be beneficial for multitasking as the amount of configuration that must be loaded is reduced.

### 2.4 Multitasking

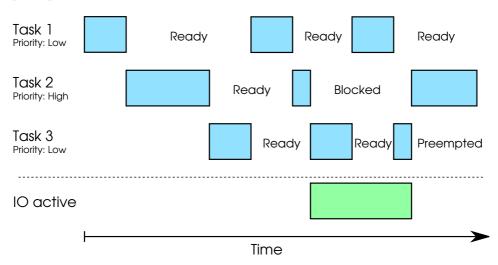

Multitasking on general purpose processors was conceived to allow multiple programs to share system resources and achieve higher system utilization. If a only a single program was allowed in a computer at any given time the Central Processing Unit (CPU) would be idle whenever IO was performed. Because IO is rather slow compared to CPU speeds, the CPU utilization would be low. By allowing several programs to be present in the system simultaneously the operating system could switch to another program when one program starts an IO operation. Hopefully one of the other programs will be ready to use the CPU, and thereby reducing the idle periods of it.

This approach would lead to higher utilization. However, if one program does not perform any IO, this one program would always be active and the other programs present in the system would never be able to use the CPU. This is referred to as starvation. To mitigate this problem, time sharing is used. All programs that can use the CPU are said to be in the *Ready* state. Programs waiting for IO are in the *Blocked* state. If more than one program is in the *Ready* state the CPU resources must be divided between them. The programs are given time slots on the CPU and a timer generates interrupts that invoke a scheduler that switches to the next program when the current time slot has ended.

Some programs might have higher priority than the rest and must be allocated a larger amount of CPU time. This can lead to situations were it is required that the current running program must yield to a higher priority program, that becomes *Ready* as a result of the completion of a IO operation. This form of multitasking is called preemptive multitasking, and the process that must yield is said to be preempted.

Figure 2.4: Multitasking

Figure 2.4 illustrates the multitasking process. Three tasks are present in the system, with various priorities. The blue blocks above the dotted line represent periods when the corresponding task is using the CPU. The green block below the dotted line represents activity in the IO system. Task 1 is the first task allowed to use the CPU. After a while a timer generates an interrupt and the current running task is switched to Task 2. This task has a higher priority and is allocated a larger amount of CPU time. After a period of time Task 3 is reactivated, and subsequently Task 1 is activated again, and so on.

During the second time slot allocated for Task 2, the running task performs an IO request. This task then enters the *Blocked* state and is deactivated, and the scheduler continues to Task 3. As Task 2 is *Blocked* it is not activated at all, and the running task switches between Task 1 and Task 3. After a while the IO operation started by Task 2 completes, and an interrupt is generated. At that time Task 3 is the current running task. Task 2 is now in the *Ready* state and has higher priority than the current running task. Based upon this information and the period from the last activation of Task 2 the scheduler deactivates Task 3 and reactivates Task 2.

Achieving multitasking by reusing the same hardware is also possible with reconfigurable hardware. The simplest approach to this is configuring a FPGA with the required configuration, and the running the task to completion. When the task has finished the FPGA is configured with the configuration required by the next task. Although simple, and hardware effective, it drastically increases latency of tasks not currently running, and can cause starvation.

The major problem with this approach is that the overhead of reconfiguration a FPGA is quite large. Loading a configuration onto a modern Xilinx Virtex 6 FPGA requires  $\sim 85 \text{ms}^{1}$ [Xil09].

A solution to this problem is partial reconfiguration of the reconfigurable hardware. Dividing the device into smaller regions and using these independently, reduces the amount of configuration that needs to be loaded. Although this reduces reconfiguration overhead it also reduces the size of configurations. If this approach is to be viable the reduction in reconfiguration overhead must be substantial.

To achieve this efficient overlapping computation and configuration has been attempted by several researchers [JTY<sup>+</sup>99], [QSN06], [RMC05], [RCG<sup>+</sup>08], [EAGEG09]. The idea is configuring an inactive region of the device, while others perform computation. The problem is deciding which configuration the inactive region should be configured with. In some cases the next required configuration will be decided by the result of a running configuration. The next configuration is not predetermined under these conditions. A solution would then be to guess which configuration will be required next, and speculative load this configuration. When the wrong configuration is loaded the system will have to reconfigure the region to the correct configuration. When this happens the reconfiguration overhead will be just as large as not speculating at the next configuration at all.

A different method of handling configurations can almost eliminate the reconfiguration overhead. This approach was presented in *A Time-Multiplexed FPGA* [TCJW97]. The reconfiguration overhead is reduced by storing several configurations on-chip. These configurations are spread throughout the reconfigurable fabric, in a manner that stores the part of a configuration near the unit that it will control. Instead of connecting the internal units directly to a configuration it is connected to a MUX. This MUX is in turn connected to several different configurations. The reconfiguration procedure is then reduced to simply switching witch configuration is connected to the internal units. This hardware structure is referred to as a multi-context FPGA.

The overhead of this reconfiguration in relation to time is very low. However, it does require storage for several configurations on-chip. The high speed reconfiguration is also limited to the configurations located on-chip. Combining this approach with the overlapping reconfiguration approach will alleviate this. As an inactive configuration can be switched out, when another is connected to the internal units.

The advantages of time sharing and preemptive multitasking should not be ignored in a reconfigurable hardware context. Such support does require that

<sup>&</sup>lt;sup>1</sup>Using a 16-bits configuration bus running at 30Mhz

the current state of a running configuration can be saved and restored. When reconfigurable hardware is used in a computing system that incorporates some slow secondary storage system, the state storage and reconfiguration overhead must be lower than the mean IO operation time, if the reconfigurable hardware utilization is to be increased by multitasking.

#### 2.5 Related technology and architectures

This section includes some related architectures and principles. Some of these approaches will find new use in the reconfigurable architecture presented in the next chapters.

#### 2.5.1 FPGA

Figure 2.5: Field Programmable Gate Array

FPGA is as mentioned on flavor of reconfigurable hardware. It is often used for logic prototyping, and has even found its way into commercial products due to a fall in chip cost.

In figure 2.5a, a simplified version of the basic reconfigurable block of a FPGA is shown. As previously mentioned this consists of a LUT used for logic emulation. This LUT is often implemented with SRAM in reprogrammable FPGAs. By changing the contents of the LUT the logic function emulated in the LUT is changed.

The LUT is often connected to a FF, which can be used to store the output value across clock ticks. These FFs can often function in a variety of ways. Such, being triggered by an enable signal, having an asynchronous clear and so forth.

In addition some complex gates used for arithmetic operations are often included into the device, to increase the speed of such operations. This is illustrated in figure 2.5a with an XOR-gate. The internal connection between these components is often controlled by MUXes. The setting of these MUXes is controlled by small SRAM cells, and can therefore be reconfigured in the same way as the LUT. Several such reconfigurable block are grouped together in a Configurable Logic Block (CLB). The internal blocks of a CLB are connected together in various ways. Many CLBs is present within a FPGA. These are illustrated with green, in figure 2.5b. The rest of figure 2.5b illustrate a simplified mesh-based interconnection scheme for a FPGA.

Each CLB is connected to the interconnect via a connection box, shown in blue. This connection box connects the IO ports of the CLB to various interconnection wires. These interconnection wires are connected to switch boxes, shown with yellow in figure 2.5b. In the switch boxes various vertical and horizontal wires are connected together. As such, connections between the connection boxes of different CLBs can be made. Both the connection boxes and the switch boxes are reconfigurable. In a real FPGA the interconnect is richer than the illustrated one. An example of this would be that neighboring CLBs can be connected together directly, without using routing resources. In addition, wire delay between two distant CLBs can be reduced by letting some wires run straight through the switch boxes.

One of the appealing possibilities of FPGA, is to partial reconfigure the device. As the name suggests, this is the possibility to load a configuration into a specified region of the FPGA. This requires that two independent configurations running in the same FPGA does not utilize the routing resources. This would be easy in the simplified illustrated interconnect. However, in a real FPGA the long wires running straight through the switch boxes can cause problems, as this can cause unintended connections between the two configurations.

The independent configurations must also not make use of the fixed hardware structures embedded into the device. These units are added to speed up complex operations, or provide more area efficient structures. Examples of these would be microprocessor cores, and Random Access Memory (RAM). Because of these resources FPGAs can be classified as a mix between coarse grained and medium grained devices. However, they are often referred to as fine granularity devices as they can perform bit wise operations.

#### 2.5.2 Piperench

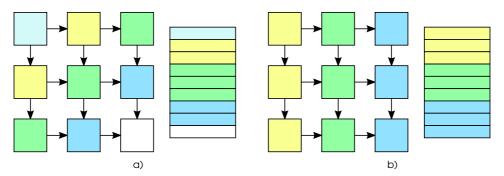

Piperench is a reconfigurable architecture presented by Seth Copen Goldstein et al. in *Piperench: A Reconfigurable Architecture and Compiler* [GSB+00]. The focus of the Piperench architecture is virtualization of hardware. This can be compared to virtual memory, where the amount of physical memory differs from the amount of virtual memory a program can access. Within reconfigurable hardware it refers to a similar mismatch between the size of the configuration and the amount of configuration the physical device can hold. Piperench uses pipelining to solve this problem. The application is divided into a number of virtual pipeline stages (v)that can be scheduled on a smaller number of physical pipeline stages (p).

One of the advantages of virtualization of reconfigurable hardware, as done in Piperench, is the ability to reuse the same configuration on larger devices as they become available. Traditionally FPGAs require resynthesizing of the design when switching to a larger FPGA. As long as no changes are made to the physical stages used in a Piperench processor it is able to load a configuration containing any number of virtual pipeline stages.

As devices containing larger amounts of physical pipeline stages become available, throughput will increase as a larger number of the virtual pipeline stages can be active at any time. This increase in throughput related to the number of physical pipeline stages has its limits, and will stop when the number of physical pipeline stages increases beyond the number of virtual pipeline stages.

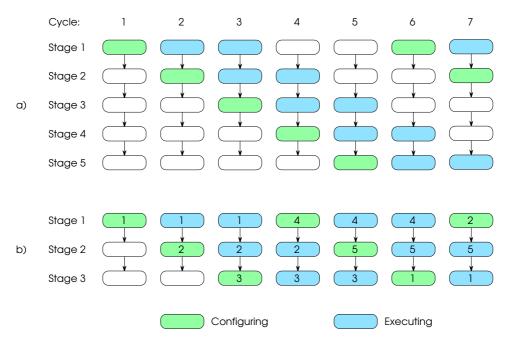

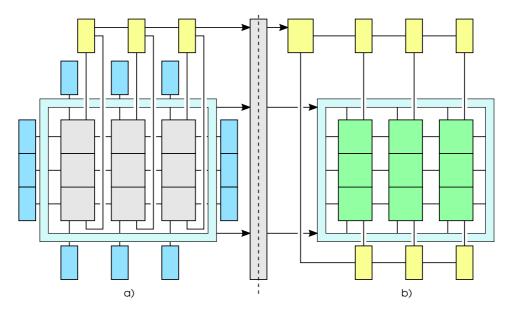

Figure 2.6: Pipelined reconfiguration (adapted from [GSB+00])

Piperench uses a pipelined reconfiguration technique described in *Pipelined re-configurable FPGAs* [SCMG00]. This process is illustrated in figure 2.6. Figure 2.6a shows the virtual pipeline, and figure 2.6b shows the physical pipeline. When a configuration containing more virtual than physical stages (v > p), it is not possible to have all the virtual pipeline stages active at the same time. Therefore run-time reconfiguration is used to simulate a larger device.

The first physical stage is configured with the first virtual stage. When the configuration is completed the first stage starts executing while the reconfiguration system starts configuring the second physical stage with the second virtual stage. The reconfiguration process must complete the configuration of a physical stage as fast as a pipeline stage can produce output to the next stage in the pipeline. In effect the reconfiguration always stays one step ahead of the data propagating through the pipeline. This requires that piperench is able to reconfigure a single stage as fast as computation is performed in a single stage. To achieve this a wide parallel bus is used change to configuration of a pipeline stage.

When there are no more unconfigured pipelined stages in the physical pipeline, the physical pipeline stage containing the oldest configuration is reconfigured with the next virtual pipeline stage. At this point no more data will enter the pipeline, as the first virtual stage will be disabled. Instead data already in the pipeline will continue through the virtual pipeline until reaching the end of the virtual pipeline. When the final virtual pipeline stage has been configured, the first pipeline stage will then be configured into the next physical pipeline stage, and data will again be able to enter the pipeline. It can be shown that this leads to a throughput proportional to  $\frac{(v-1)}{n}$  [GSB<sup>+</sup>00].

This style of reconfiguration has some requirements to the configuration and the underlying architecture. The state of a single stage must be the result of its own state and the state of the previous state in the pipeline. This leads to a requirement that all cyclic dependencies must fit within a single pipeline stage. In addition data can only flow between consecutive pipeline stages. However, it is possible to implement virtual connections between remote stages.

It is required that any virtual pipeline stage must be placeable on any physical pipeline stage. Therefore all physical stages must be identical and all physical pipeline stages must be able to be the first and last stage in the virtual pipeline. This is done to increase efficiency of the architecture, and leads to a requirement that all physical pipeline stages must have the ability to receive external data.

#### 2.5.3 Wavefront array processor

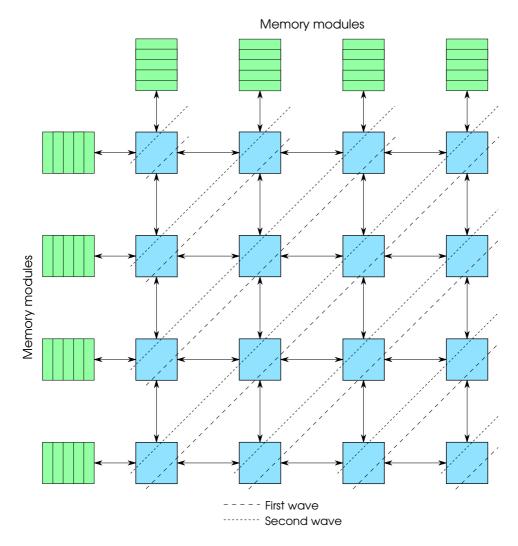

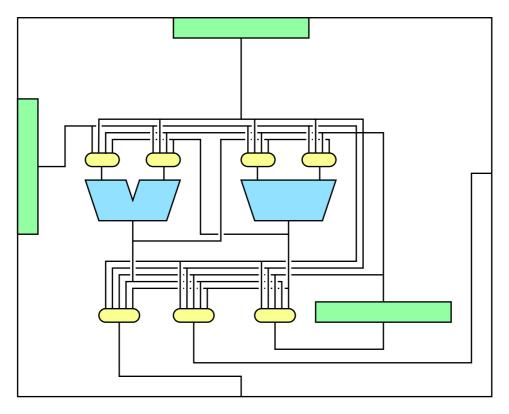

The Wavefront Array Processor (WAP) was described by Sun-Yuan Kung et al. in *Wavefront Array Processor: Language, Architecture and Applications* [Sun82]. This processor is designed for recursive algorithms with local data dependencies.

Such algorithms often present behavior which consists of repeated execution of simple operations with localized data flow in a homogeneous computing network[Sun82]. Localized data flow in this context means that communication in the computing network is limited to the nearest neighbors in this network. These algorithms running on a computing network can induce propagation of computational activity in a way that resembles physical wave propagation. This is called a computational wave. These computational waves can be pipelined by starting a new wave after the current wave have propagated away from the wave origin. This allows for parallel execution of recursion in an algorithm. The actual cause of this phenomenon is locality, regularity, recursivity and concurrency.

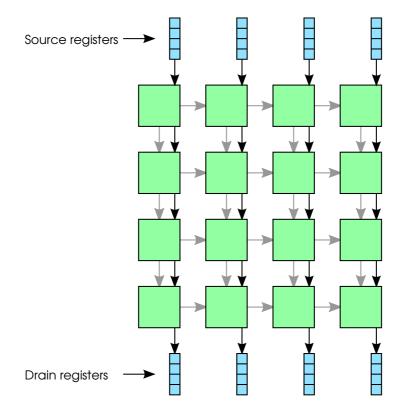

WAP is designed to take advantage of the computational wave. The structure of WAP is illustrated in figure 2.7. The processor is organized as a array containing Processing Element (PE)s, which are shown in blue. These PEs are restricted to local communication. A PE can only communicate with its nearest neighbors in the horizontal and vertical directions. The memory modules, shown in green in figure 2.7, are connected to the first row and first column of the PE grid. Therefore memory access is only possible through the PEs in the first column and the first row in the array. These PE are therefore different from the rest of the array. All the interior PE are identical. This is desirable as a regular structure is easier to produce.

Figure 2.7: Wavefront array processor (adapted from [Sun82])

The processing array does not have a global clock. As such, the need for a low skew clock network is eliminated. However, without a global clock to synchronize communication, the PEs need another form of synchronization during data exchange with neighboring PEs. A handshaking scheme is used to overcome the asynchrony of the PEs and allow them to communicate without risking data corruption. The handshake scheme allows PE to wait for data to arrive on their input ports, in addition to block further communication if the input buffer of a PE is full. Hence the processor is said to be data flow based. Deadlocks in the processing array are prevented by requiring all processing elements to initiate sends before receiving.

Two ways of programming the array was proposed. The PEs in the grid can be programmed individually or an entire wavefront can be programmed. Both programming methods can lead to differences in computation time between wavefronts. This difference in computation time can lead to a situation, where a faster wavefront catches up to a wavefront which has reached a slow stage in the computation. Collision between these two waves is prevented by the blocking handshake scheme.

#### 2.5.4 RISC processors

One traditional approach to improve performance was the usage of complex instructions that would cause a sequence of microinstructions to be executed. This approach is referred to as Complex Instruction Set Computing (CISC). The improvement in performance was caused by the relative difference in memory speed and processor speed. If a complex instruction could cause a large number of operations to be performed on the input data, this would improve performance as the number of instructions fetched from memory would decrease.

The available technology could implement high-speed Read-Only Memory (ROM)s. By storing commonly repeated instruction sequences as subroutines in a ROM, and using the instruction stream to call these, performance could improve. This approach did however require that sensible subroutines would be implemented, and that the gap in performance between processor and memory speed would continue.

However, these assumptions did not hold. As shown in [PD80], only a subset of the available instructions were used by the programs analyzed. Furthermore, a major proportion of the programs consisted of a even smaller subset of simple instructions. That is instructions that can be efficiently run directly on hardware. The cause of this might be found with compilers that were unable to utilize the complex instructions. Additionally, the increased use of caches also narrowed the gap between processor speed and memory speed.

Acknowledging this, several research projects into processor architecture led to a class of devices now known as Reduced Instruction Set Computing (RISC). The common factor for these processor was the elimination of the complex instruction translation. Simple instructions that were directly implementable in hardware was utilized.

Such simple instruction eliminated the need for a complex control unit, and a subroutine ROM. The Berkeley RISC I project went even further with simplifica-

tion of the processor [PS81], as the goal of the project was to create a single chip processor, with a reasonably sized on-chip cache.

The instruction formats should be of equal size. The instruction encoding is probably not the most size efficient. However, the fixed size instruction simplifies instruction fetch, as instruction will always be aligned in memory.

The resultant architecture should be able to execute one instruction per cycle, which puts a limit on instruction complexity. This does increase the size of programs as more complex operation must be implemented by the programmer. Nevertheless the resultant processor can have greater efficiency as the instructions are easier to decode.

Only load and store instruction should access memory. Hence, all other instructions should operate on registers. This was done to force the allocation of variables to registers, and not to memory addresses. When the variables are allocated to internal registers, and not to memory addresses the amount of memory accesses is reduced. The cause of this is that intermediate results are not stored back to memory, when they are likely to be accessed again soon.

The Berkeley RISC processor was eventually commercialized by Sun Microsystems under the name Scalable Processor ARChitecture (SPARC). Another notable RISC research project that was commercialized was the Microprocessor without Interlocked Pipeline Stages (MIPS) developed at Stanford university.

A major difference between the Berkeley RISC and the Standford MIPS was in their pipeline implementation. While Berkeley RISC relied on hardware to detect dependencies between instructions in the pipeline, and perform forwarding between pipeline stages. The MIPS relied upon compiler technology to reorder instructions and thereby remove hazardous dependencies [Pat85].

# Chapter 3

# System overview

In this chapter a brief overview of the implemented device will be given. First the integration point of the device is elaborated upon. Following this a wave based method for performing computation and reconfiguration, that allows for multitasking, is described. Then binary compatibility between device revision is elaborated upon. After this elaboration follows a description of a possible IO system for the device. A description of the computational properties of the device follows this. Finally an overview of a reconfiguration system that supports the low overhead reconfiguration method is given.

# 3.1 System coupling

During the design stages it was required to roughly specify the kind of coupling the finished system might use. If the device was designed as unit suitable for integration into a general processor it would be tied to the running task of that processor. This would probably reduce the utilization of a reconfigurable unit as not all tasks would make use of such hardware, and it would be left idle when such tasks were running.

Therefore the device was designed as a separate device that would take commands from a general purpose processor. This would allow for scheduling of the reconfigurable device to be performed by an operating system. This independence does come at a cost, which is the increased communication latency and reduced control over the device.

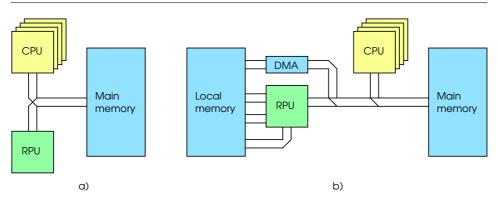

In figure 3.1 some possible interconnection schemes are shown. Figure 3.1a illustrates the simplest connection type. The Reconfigurable Processing Unit (RPU) is connected to the same bus as the regular CPUs and share the main memory. The CPUs can send commands directly to the RPU. Although simple to implement it requires that the existing memory system meet the bandwidth and latency requirements of the RPU without causing starvation in the CPUs.

If the existing memory system is unable to satisfy the memory system requirements imposed by the RPU, one could consider the approach shown in 3.1b. A

Figure 3.1: System overview

separate memory system, labeled *Local memory* in the figure, is implemented to suit the needs of the RPU. Data which the RPU is to perform computation on is explicitly copied into the devices private memory with a Direct Memory Access (DMA)like device. The command interface of the RPU is still connected to the existing infrastructure. However, one should acknowledge that this does not eliminate the bottleneck. It will either exists as a limit upon the maximum amount of memory the unit can perform computation on, or it will consume data faster than it can be loaded from main memory unless it reuses data elements already loaded.

# 3.2 Device overview and properties

Multitasking on a reconfigurable unit requires that the device be carefully designed to allow low overhead reconfiguration. In this section a interconnect style that allows for a high degree of overlap between tasks is introduced. In addition, solutions for backwards compatibility is presented, and the IO system of the device is elaborated upon.

## 3.2.1 Device dataflow

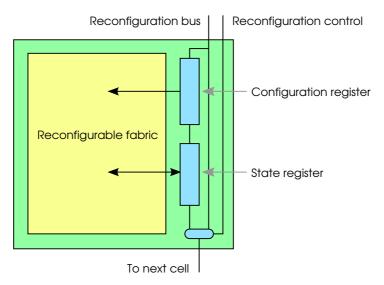

The RC device is first divided into subunits, called cells. A cell has some amount of inputs and some amount of outputs. The internals of a cell, will for now, be left as a black box that performs some computation on the input data. The result of this computation will be put on the cell output ports.

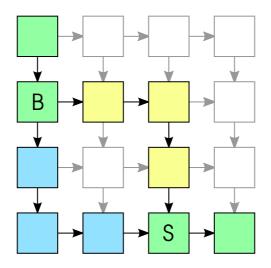

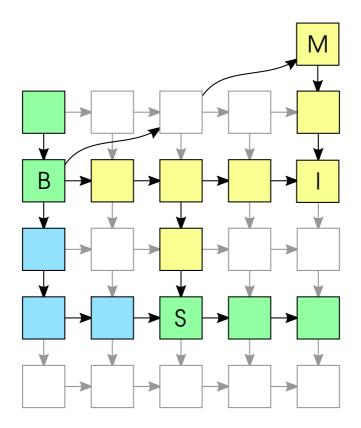

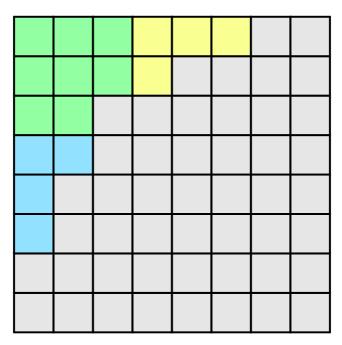

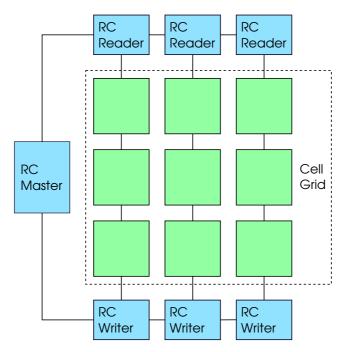

When the RC device is divided into cells, which perform some computation before passing data to other cells, there is a worst possible data dependency case. This worst possible case is when all the cells depend on input data from other cells. Only cells that solely rely on external input can start performing computation. When these cells are done with their computation and transfers data to their neighboring cells, all the neighbors that now have all their data dependencies met can start computation, in addition to the originating cells that now can receive more external data. This will cause computational activity to propagate through the RC device following the interconnection network. The computations performed on input data will be highly pipelined as the originating cells can start computation on their next data set as soon as data is transferred to neighboring cells, which also can start computation if all their data dependencies are now met.

Figure 3.2: Nearest neighbor dataflow

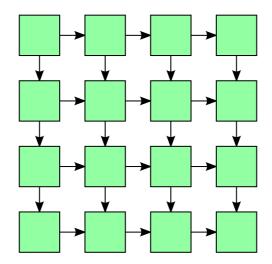

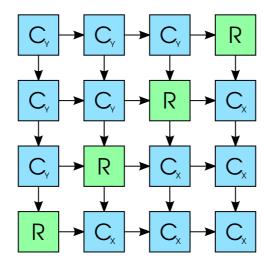

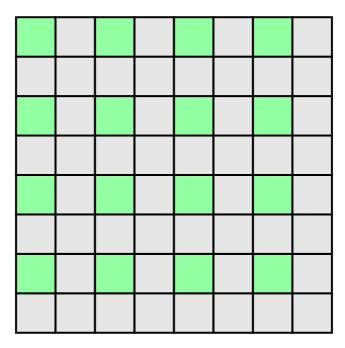

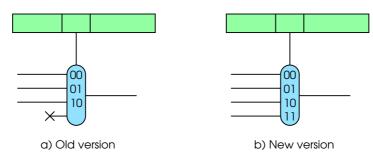

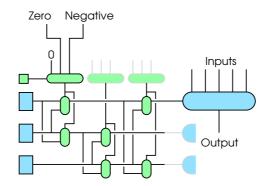

The multitasking approach proposed will be designed for this worst possible case. The basic RC device is divided into cells. Each cell have two input ports and two output ports. The cells are organized in a grid with nearest neighbor communication as shown in figure 3.2.

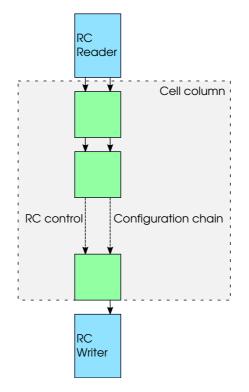

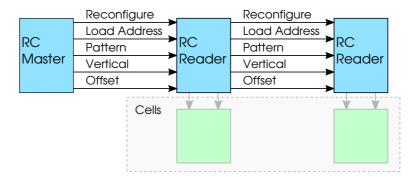

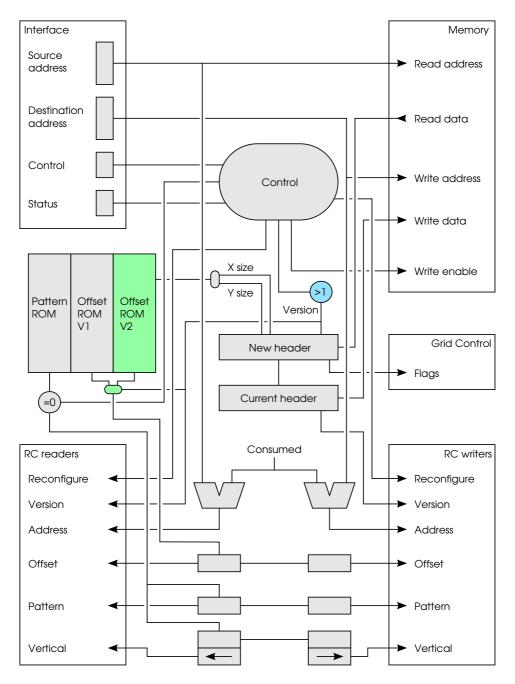

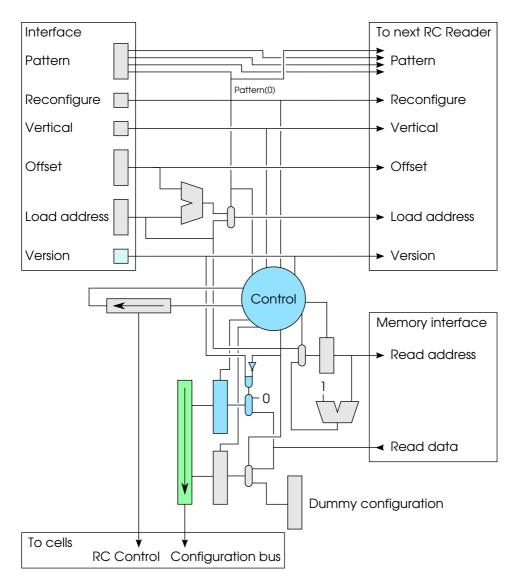

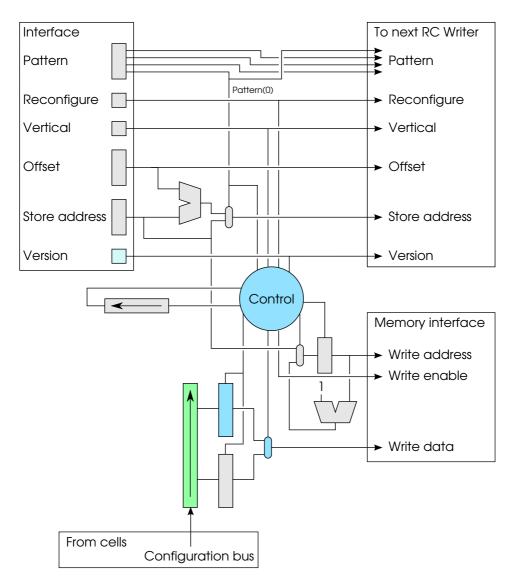

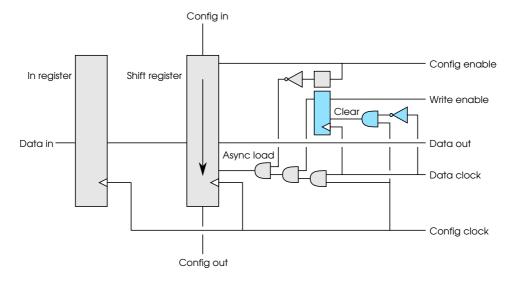

Cells along the edge of the structure can communicate with external units. This organization is somewhat similar to WAP. The main difference is that the communication is further restricted to be unidirectional, while WAP uses bidirectional communication. The unidirectional communication allow us to define a worst case data dependency case, that all other communication patterns allowed in the device must be a subset of. This is the worst possible case previously outlined.