## Abstract

This report gives a short introduction of the Norwegian wireless electronics company Chipcon AS, and goes on to account for the state of the art of small IP processor cores. It then describes the NanoRisc, a powerful processor developed in this project to replace hardware logic modules in future Chipcon designs. The architecture and a VHDL implementation of the NanoRisc is described and discussed, as well as an assembler and instruction set simulator developed for the NanoRisc. The results of this development work are promising; synthesis shows that the NanoRisc is capable of powerful 16-bit data moving and processing at 50 MHz in an 18nm process while requiring less than 4500 gates. The report concludes that the NanoRisc, and none of the existing IP cores studied, satisfies the requirements for hardware logic replacement in Chipcon transceivers.

## Preface

This report and the NanoRisc development work was made as part of a master's thesis for the Norwegian University of Science and Technology (NTNU). The project proposal was given by Chipcon AS, and the work has been performed in their offices.

### Acknowledgements

I would like to thank my mentors Jørgen Langfeldt, Robin Osa Hoel and Dag-Sverre Skjelbreid at Chipcon for their many hours of help and great inspiration.

I would like to thank Chipcon AS for supporting me and providing me with a desk, computer and all necessary tools.

I would like to thank Lasse Natvig and Morten Hartmann of NTNU for helpful guidance in writing this report.

### Outline

This report consists of three parts. Part I is an introduction to the project and accounts for the state of the art. An introduction to Chipcon and the motivation behind this project is given in chapter 2 followed by the requirements specification in chapter 3. An overview and discussion of available IP cores is given in chapter 4. Part I describes the NanoRisc and its tools. An overview of the NanoRisc architecture is given in chapter 5 followed by a description of its implementation in chapter 6. Chapter 7 describes the tools developed for NanoRisc. Part III contains the results and discussion. Chapter 8 describes the testing performed on the NanoRisc and chapter 9 describes the results achieved in synthesis. Chapter 10 is a discussion on some of the more interesting trade-offs made during the development of the NanoRisc.

## **Table of Contents**

| Abstract |                                        | 1  |

|----------|----------------------------------------|----|

| Preface  |                                        | 3  |

| Ackno    | wledgements                            | 3  |

| Outlin   | e                                      | 3  |

| Table of | Contents                               | 5  |

| Table of | Figures                                | 7  |

| Table of | Tables                                 | 7  |

| Part I   |                                        | 9  |

| 1 Intro  | oduction                               | 10 |

| 1.1      | Project Description                    | 10 |

| 2 Chi    | con and NanoRisc                       |    |

| 2.1      | Corporate and Organization             | 12 |

| 2.2      | Products                               |    |

| 2.3      | Motivation behind the NanoRisc Project | 12 |

| 3 Req    | uirement Specification                 |    |

| 4 Stat   | e of the Art                           | 16 |

| 4.1      | Design Reuse                           | 16 |

| 4.2      | Comparison of IP Processor Cores       | 17 |

| Part II  | 1                                      |    |

| 5 Arc    | hitecture Specification                |    |

| 5.1      | Nomenclature                           |    |

| 5.2      | Address Space Overview                 |    |

| 5.3      | Instruction Addressing Modes           |    |

| 5.4      | Constants                              |    |

| 5.5      | Instruction Fetch                      |    |

| 5.6      | General Registers                      |    |

| 5.7      | Special registers                      |    |

| 5.8      | Data Processing                        |    |

| 5.9      | I/O                                    |    |

| 5.10     | Memory                                 |    |

| 5.11     | Program Flow                           |    |

| 5.12     | Interrupt                              |    |

| 5.13     | 1                                      |    |

| 5.14     | Reset                                  |    |

| 5.15     | Interface                              |    |

| 5.16     | Instruction Set                        |    |

| 5.17     | The NanoRisc Assembly Language         |    |

|          | lementation                            |    |

| 6.1      | Тор                                    |    |

| 6.2      | ALU                                    |    |

| 6.3      | Fetch                                  |    |

| 6.4      | I/O                                    | -  |

| 6.5      | Mem                                    |    |

| 6.6      | Mul                                    |    |

| 0.0      |                                        | .0 |

| 6.7       | PCU                                | 48 |  |

|-----------|------------------------------------|----|--|

| 6.8       | Reg                                | 50 |  |

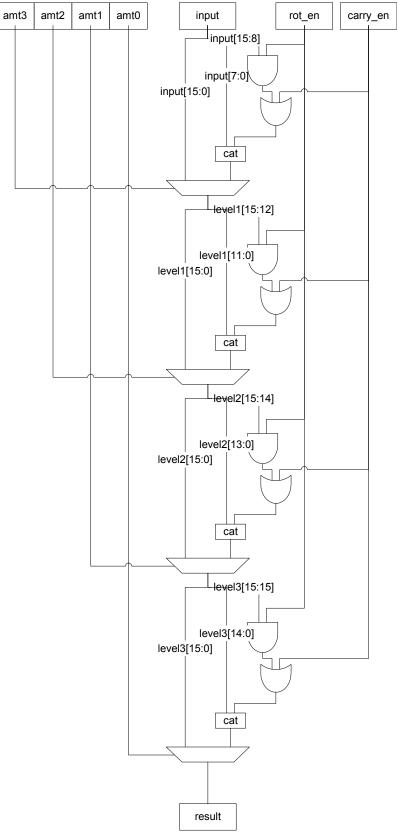

| 6.9       | Shift                              | 50 |  |

| 6.10      | Src                                | 52 |  |

| 7 Too     | ls                                 | 53 |  |

| 7.1       | Assembler                          | 53 |  |

| 7.2       | ISS                                | 57 |  |

| Part III  |                                    | 61 |  |

| 8 Tes     | t                                  | 62 |  |

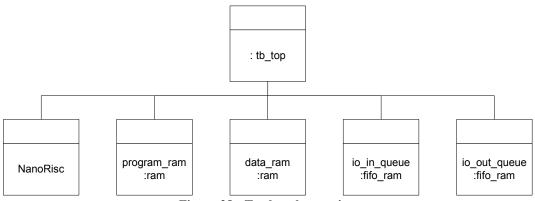

| 8.1       | Test Bench                         | 62 |  |

| 8.2       | Coverage program                   | 64 |  |

| 8.3       | Quicksort Program                  | 65 |  |

| 8.4       | CRC Program                        | 65 |  |

| 8.5       | 16-bit Multiplication              | 66 |  |

| 8.6       | SPI                                | 66 |  |

| 9 Res     | ults                               | 67 |  |

| 9.1       | Synthesis                          | 67 |  |

| 9.2       | Performance                        | 69 |  |

| 10 E      | Discussion                         | 72 |  |

| 10.1      | Instruction set                    | 72 |  |

| 10.2      | Architecture                       | 75 |  |

| 10.3      | Tools                              | 79 |  |

| 10.4      | Testing                            | 79 |  |

| 10.5      | Future Work                        | 79 |  |

| 10.6      | Summary of Requirements Conformity | 81 |  |

| 11 C      | onclusion                          | 83 |  |

| Bibliogra | Bibliography                       |    |  |

# Table of Figures

| Figure 1 - Code hierarchy                                | 19 |

|----------------------------------------------------------|----|

| Figure 2 - NanoRisc simple overview                      |    |

| Figure 3 - Logical register layout                       |    |

| Figure 4 - Stack use                                     | 27 |

| Figure 5 - Status register                               |    |

| Figure 6 - Program address                               |    |

| Figure 7 – Negate                                        | 29 |

| Figure 8 - Clear register                                | 30 |

| Figure 9 - I/O port layout                               | 31 |

| Figure 10 - Single memory solution                       |    |

| Figure 11 - Separate memories solution                   |    |

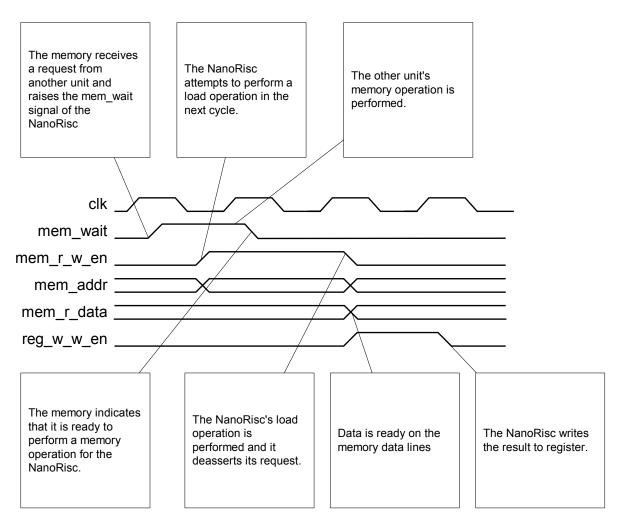

| Figure 12 - Memory wait timing diagram                   |    |

| Figure 13 - Interrupt sequence                           | 36 |

| Figure 14 - External interrupt module                    | 37 |

| Figure 15 - Top-level interface                          |    |

| Figure 16 - Instruction Encoding                         | 42 |

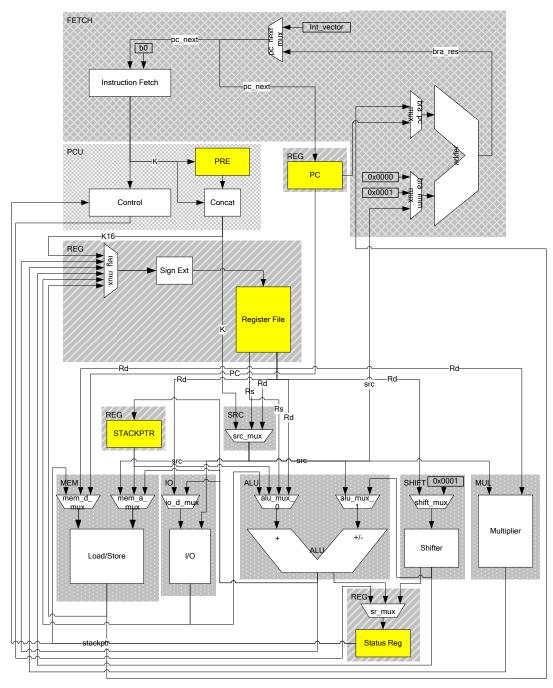

| Figure 17 - Data flow diagram                            | 45 |

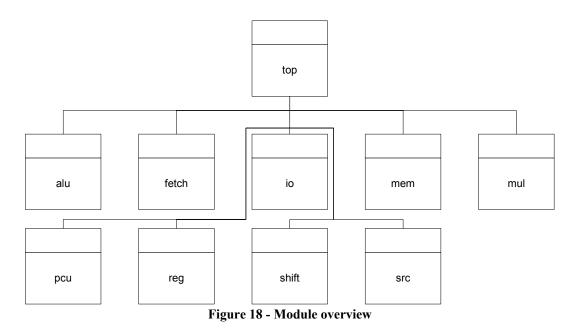

| Figure 18 - Module overview                              | 46 |

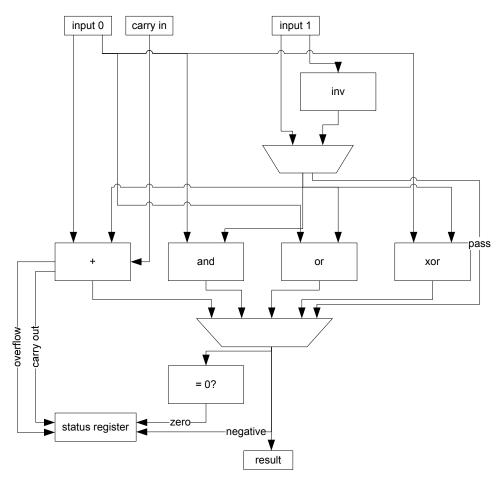

| Figure 19 - ALU overview                                 | 47 |

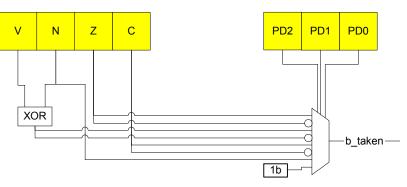

| Figure 20 - Branch control unit                          |    |

| Figure 21 - Left shifter                                 |    |

| Figure 22 - Label definition syntax                      |    |

| Figure 23 - Define syntax                                | 53 |

| Figure 24 - Include syntax                               | 54 |

| Figure 25 - Comment syntax                               | 55 |

| Figure 26 - Assembler command-line syntax                | 57 |

| Figure 28 – ISS screenshot during execution of quicksort | 58 |

| Figure 29 - Testbench overview                           | 62 |

| Figure 30 – Interrupt simulation                         |    |

| Figure 31 – Sleep functionality                          |    |

| Figure 32 - Example instruction test                     | 65 |

## **Table of Tables**

| 17 |

|----|

| 27 |

| 29 |

| 29 |

| 30 |

| 30 |

| 31 |

| 34 |

| 35 |

| 38 |

| 40 |

|    |

| Table 12 – Results overview | 67 |

|-----------------------------|----|

| Table 13 - Area             | 68 |

## Part I

## 1 Introduction

This chapter gives a short introduction to the project. Chipcon is a Norwegian company who designs low-cost, low-power wireless transceivers. The increasing complexity of the chips designed by Chipcon reveals a need for new design methods on their systems on chip (SoCs). One way to achieve this is through the use of an on-chip firmware processor. Contrary to the processors integrated in the Chipcon designs of today, an on-chip firmware processor would not be user programmable, but handle only internal control and data processing tasks.

The NanoRisc processor was developed for Chipcon as a part of this thesis. It is a compact and effective microcontroller core which can control complex processes and move and process data. It features 13 general 16-bit registers, a full 16-bit ALU, an 8x8 multiplier, a 16-bit barrel-shifter, and a load/store unit with auto-increment/decrement. Its up to 32 addressable I/O ports and interrupt handling contribute to its easy integration into any design. It is controlled by a compact and comprehensive set of 16-bit instructions, but is still capable of immediate 16-bit memory addressing without the use of paging. A complete implementation of the core requires less than 5K gates.

This report will show that the NanoRisc is more suited to Chipcon's firmware processor needs than the available intellectual property (IP) processor cores.

### 1.1 Project Description

The task as given by Chipcon is cited below:

Develop an ultra-low-complexity CPU core aimed at replacing hardwired finite state machines (FSMs) and custom logic in ASIC designs. A typical application is packet processing and protocol handling. A suggestion for CPU core features is:

- Ultra-low complexity (2-5 kgates maximum)

- 8/16-bit ALU/register width (e.g. sixteen 8-bit registers which can also be addressed as eight 16-bit registers)

- Simple, orthogonal, high-density instruction set. (preferably fixed size instructions)

- Common address space for code and data (12-16 bit). Separate memory busses for code and data allow the two to map to disjoint parts of the address space and be accessed simultaneously. All memory busses are compatible with synchronous SRAMs (synchronous read and write).

- *Load/store architecture.*

- Simple integrated interrupt controller.

- Parameterizable number of input/output ports.

- Low power consumption (< 25 uW/MHz in a 0.18 um process)

The goals of the thesis are:

• Detailed specification of CPU architecture / instruction set

- Develop cycle-accurate instruction set simulator (ISS) in C/C++ (preferably GUI-based).

- Develop assembler for the instruction set (Bison/Flex & C/C++).

- Implement core in synthesizable VHDL.

- Perform exhaustive testing of VHDL core against ISS.

- Perform test synthesis for a TSMC 0.18 um process to determine accurate gate count and power consumption.

## 2 Chipcon and NanoRisc

This chapter gives a brief overview of Chipcon, and accounts for the motivation behind the NanoRisc project. Chipcon is a Norwegian microelectronics company which specializes in the design of wireless transceivers. They operate in an international market, selling chips for applications ranging from wireless game pads and security systems to industrial systems.

### 2.1 Corporate and Organization

Chipcon started out as a specialized Application Specific Integrated Circuits (ASICs) design center in 1996, and has since changed strategy to become a leading international 'fabless' semiconductor company. It has a total of 103 employees where 17 are located in San Diego and 7 in sales offices around the world. The remaining 79 employees make up the headquarter and design center in Oslo where this project was undertaken [Chipcon].

The design center in Oslo handles

- Design of new chips

- Testing

- Support and applications development

- Development tools (HW/SW)

This thesis was written in close cooperation with the digital signal processing (DSP) and system-on-chip (SoC) groups.

Chipcon's largest owners today are Four Seasons Venture and the founders Geir Førre, Sverre Dale Moen and Svein Anders Tunheim.

### 2.2 Products

Today, most of Chipcon's revenue comes from Application Specific Standard Products (ASSPs) for short-range wireless communication. The application which represents the largest portion of the orders is game pads for systems such as Sony PlayStation [Sony] and Microsoft Xbox [Microsoft]. One of it's main competitors in the wireless game controllers and other wireless applications is Nordic Semiconductor [Nordic] located in Trondheim.

Currently, Chipcon works to promote the ZigBee standard which is a low power consumption and low bandwidth protocol for wireless communication between potentially a large number of devices. It is based on the IEEE802.15.4, and requires a software Media Access Control (MAC) module. See [ZigBee] for details.

### 2.3 Motivation behind the NanoRisc Project

While Chipcon maintains a range of cheap and simple wireless transceivers, they are also developing complex SoCs for wireless applications. Future Chipcon chips will require

rather complex protocol handling, packet processing and buffer control, which is what the motivation for the NanoRisc project springs from. The NanoRisc will be a general-purpose embedded processor providing a specific service in an application as described in [WongVa2004].

The task of designing a processor core as described in the original task had the aim of producing a controller that could replace some of the larger finite state machines (FSMs) currently used for hardware sequencing and protocol control in the Chipcon transceivers. Microprocessors and hardware modules both have the capability to implement most any digital logic function. There are, however, unique advantages and disadvantages to either approach.

- **Ease of implementation** It was thought that it would be easier to program an FSM as software rather than in a hardware description language (HDL). In terms of testing, it is not necessarily more work to verify a processor running a program than to verify the FSM implementing the same logic.

- Size When evaluating the implementation size of a processor versus a hardware module, it is important to count the memory requirements of microcontroller which grows with complexity. On the other hand, a processor re-uses its logic resources, while the need for logic resources in a hardware implementation increases with complexity. A processor with memory is not expected to be smaller than the hardware state-machine implementing the same logic.

- **Performance** The sequential execution of instructions in a processor entails a degradation of performance with increased complexity. A hardware module will not necessarily in the same way experience performance degradation with increased complexity because algorithms can be implemented in parallel. This leads to a faster but more expensive implementation. To counterpart to this in a software implementation would be to use several microcontrollers working in parallel to increase performance.

- Flexibilty A microcontroller implementation is more flexible and makes it easier to make changes and fix bugs after initial production. An error in a large hardware FSM causing incorrect behavior discovered after initial production can be very expensive. Fixing it would demand several man-months of work plus the full set of masks to be remade at considerable cost. Alternatively, a manual manipulation of the routing could be performed in some cases, but it is very difficult work. The advantage of using a processor is that its program memory can be changed by changing only one of the masks. Errors in its behavior can thus be changed easily and one can in some cases use the processor to make workarounds for errors elsewhere on the chip. In a larger perspective, a software program is easier to upgrade and to differentiate from a previous design.

An ideal approach is usually to have a microcontroller embedded on a chip where the complex, non-timing crucial control functions can be implemented on the microcontroller, while timing critical or data path functions are implemented in hardwired logic [Xilinx2004].

There are several processor cores on the market today designed for SoC integration, and re-use of such a module would have to be considered for an application such as those mentioned above. The Chipcon engineering group is familiar with design reuse. Both an implementation of the 8051 microcontroller and the Cambridge Consultants Xap1 processor has successfully been used as IP cores in Chipcon designs. The 8051 is found as a user programmable microcontroller chips such as CC1010 and CC2420, while the Xap1 processor was used as a controller in an ASIC project. A discussion of possible integration of a processor IP core is found in chapter 4.

## **3 Requirement Specification**

The requirements specification is based on the original task and a series of meetings with Chipcon representatives in January 2005. They represent what Chipcon believes the processor should be for it to be suitable for integration into a future Chipcon transceiver.

- 1. **Load/store architecture.** This requirement arose from the original task. It implies that data processing should only be done on data in registers.

- 2. **Simple, orthogonal, high density instruction set.** This requirement arose from the original task. It is understood that the instruction set can not be entirely orthogonal due to its load/store nature, but consistency should be strived for. Fixed size instructions are wanted, but other solutions could be explored.

- 3. **Data processing capabilities.** This requirement arose from the meetings. The processor should include an ALU with logical and arithmetic operations and should support some shift and rotate scheme.

- 4. **8x8 Multiplier.** This requirement arose from the meetings. An 8x8 hardware multiplier should be implemented.

- 5. **Stack.** This requirement arose from the meetings. A stack should be implemented in hardware or software to allow nested function calls and facilitate a C compiler.

- 6. **16-bit memory interface, no paging.** This requirement, decided in the meetings, is an extension of a requirement in the original task. The processor should be able to interface a 16-bit memory bus, and have a shared, byte addressable address space for data and program. Paging should not be used, as it complicates programming.

- 7. A parameterizeable sized I/O space with bit-operations. This requirement arose partly from the original task and was extended in the meetings. It is important the processor should be able to interface with peripherals without having to memory map these. This is to be implemented by the use of I/O ports, and the number and width of these ports should be parametrizeable. Efficient bit-operations such as "set", "clear" and "test" should be able to operate on these ports.

- 8. **Simple integrated interrupt controller.** This requirement arose from the original task. The processor should be able to respond promptly to external events by the use of interrupts.

- 9. Small footprint (2K-5K). Perhaps the most important requirement arose from the original task. As size directly influences production cost, the size of the controller should be kept at a minimum to keep it attractive compared to dedicated hardware solutions.

- 10. Power consumption of < 25 uW/MHz in the 0.18 um process excluding memories. This requirement arose from the original task.

## 4 State of the Art

This chapter will give an overview of the current small embedded processor in the market today. The discussion of examples will be limited to architectures available as intellectual property (IP) modules that can be licensed for use in ASIC/ASSP production.

### 4.1 Design Reuse

Reuse of hardware cores has become increasingly popular over the last few years. The need to close the gap between design sizes and engineer productivity has lead the ASIC industry to adopt the concept of design reuse from software development. A multitude of vendors selling intellectual IP modules for system integration has emerged.

The reuse of processor IP cores is well known and has been available for years through established vendors as ARM [ARM] and MIPS [MIPS] [Rosenberg1999]. Perhaps one of the main reasons behind the success of processor IP cores is the availability of tools. Developing a processor architecture from scratch requires that one also builds up an arsenal of tools for programming and debugging to make the processor usable in practice. Many processor IP vendors have avoided this by providing IP cores that are functionally equivalent to well known and established processor architectures, enabling the tools such as compilers, assemblers and simulators available for these architectures to be reused. Important in this respect is also the fact that the competency of the programmers can be reused when such an approach is chosen.

As hardware systems grow increasingly in complexity, the need to increase engineer productivity grows with it. [Bouldin] suggests that design reuse might save 70% of the design effort compared to the original development. This is a great motivation for design reuse.

Another motivation for design reuse is the brand-name recognition and consumer trust that has been built up by major IP vendors. It is harder to convince an engineer that his application would be easy to write, debug and run on your unknown processor than on the newest ARC supporting the Thumb2 instruction set for example. For Chipcon this becomes a big issue if the processor should ever be targeted for user programming. As long as it is an internal integrated firmware processor, the Chipcon-internal recognition of the processor is all that counts.

There are, however, certain pitfalls associated with hardware design reuse. One of the more obvious is to choose a design that does not turn out to satisfy specifications and constraints [Bolado2003]. Public information on IP cores, however is limited, and it can be difficult to find a processor that fulfills all requirements [Salminen2004]. An alternative is to modify an IP which is almost suited to fulfill all requirements. Most processor core IP's are delivered as soft IP cores, that is, they are described in a hardware definition language. As opposed to physical design, netlists or RTL models, this is the most easily modifiable IP format. The problem, however, is that according to [McCorquodale] verification represents at least 50% of the design cycle for IP components, and if modifications are made, the design will have to be re-verified. In this

respect, modified IP is not suited to close the gap between the vast amount of logic that can be put on a chip and the amount of logic an engineer can design [Rosenberg1999].

### 4.2 Comparison of IP Processor Cores

This section describes and evaluates a number of processor IP cores available in the market today. The cores selected for study are generally their vendor's smallest cores with an emphasis on low power consumption. As stated by [Salminen2004], however, IP comparisons are hard and tedious because public information is limited and product briefs are inaccurate and unclear. The IP cores to evaluate were found through conversations with engineers at Chipcon, using the search at design-reuse.com and searches on general-purpose search engines on the internet. Key numbers on these processors are summarized in Table 1.

| Table 1 - IP processor cores |               |                     |                        |                                  |                           |

|------------------------------|---------------|---------------------|------------------------|----------------------------------|---------------------------|

| Core                         | Data<br>Width | Area<br>[kilogates] | Max.<br>Freq.<br>[MHz] | Power<br>Consumption<br>[mW/MHz] | Performance<br>[MIPS/MHz] |

| Arc Classic86                | 16b           | 22                  | 80                     | -                                | 0.08                      |

| [ARCx86]                     |               |                     |                        |                                  |                           |

| ArcLite [ArcLite]            | 8b            | 3,5                 | 160                    | -                                | -                         |

| ARM Cortex-M3                | 32b           | 33                  | 100                    | 0.12                             | 1.2 (DMIPS)               |

| [ARMCortex-M3]               |               |                     |                        |                                  |                           |

| MC8051                       | 8b            | 10                  | 100                    | -                                | -                         |

| [Salminen2004]               |               |                     |                        |                                  |                           |

| OpenRISC 1200                | 32b           | 25                  | 150                    | -                                | -                         |

| [Salminen2004]               |               |                     |                        |                                  |                           |

| PicoBlaze                    | 8b            | -                   | -                      | -                                | -                         |

| [PicoBlaze]                  |               |                     |                        |                                  |                           |

| Xap1 [Xap1]                  | 16b           | 3                   | -                      | ~0.45                            | 0.18 (DMIPS)              |

| Xap2 [Xap2]                  | 16b           | 12                  | 100                    | > 0.45                           | 0.37 (DMIPS)              |

### 4.2.1 Performance

Most of these processors use pipelining to some extent. Pipelining is the splitting of instructions into steps that are executed on one clock cycle each. It enables the processor to greatly increase its throughput because it can run at higher clock speeds and in most cases complete one instruction each cycle. Several instructions are being executed at one time, and it requires logic to handle precise interrupts, minimize branch penalties, data dependency stalls etc. In addition it requires registers to store results between each stage of the pipeline [Hennesy1996]. This logic may account much of the area consumed by some of these processors, but on the other hand it is what enables for example the OpenRISC to obtain such high operating frequencies.

The measure of relative performance of microprocessors is difficult. Measures like MHz, MIPS or benchmarks do not necessarily reflect how a processor would perform doing your task. The user is referred to [Hennesy1996] for a thorough discussion on the metrics

of processor performance. In practice, however, for small processor cores, the Dhrystone benchmark is the most commonly used measurement of performance. The Dhrystone benchmark is a synthetic benchmark, invented in 1984 which contains no floating point operations. The output from the benchmark is the number of Dhrystones per second (number of iterations of the main code loop per second), but the most frequently used metric is the Dhrystone MIPS (DMIPS). It is a measure of the Dhrystone processor relative to the Dhrystone performance of a DEC VAX processor [Weiss2002]. DMIPS are generally seen as being proportional to the clock speed, and the more useful measure of DMIPS/MHz is usually reported. There were, however, no specific requirements as to performance for this project, so no processors are excluded based on it.

### 4.2.2 Area

Based on the requirements put forth in the task for this thesis, most of the above mentioned processors can be ruled out for this application based on simple metrics. One of the requirements is that an implementation of the processor core should be less than 5000 gates. This requirement has a great impact on the cost of the solution, as the gate count is directly proportional to die area and the die area to the fourth power is proportional to the cost of the chip [Hennesy1996]. Even though the ARM Coretex-M processor can compete with many 8-bit architectures in terms of size, the stringent size requirement for this project rules out all the 32-bit processors [Wong2004]. The Xilinx PicoBlaze is a small 8-bit controller especially designed to achieve a small footprint in the Xilinx field programmable gate arrays (FPGA), but its size when implemented in a 18nm ASIC process has not been found. This leaves the 8-bit ArcLite and the 16-bit Xap1 for consideration.

When considering the area consumed by a particular processor, it is also important to consider the size of the required program memory i.e. the code size. Small code size has been an important selling point for the AVR architecture for example. The size of each instruction word and the number of instruction words to implement a program is important. The size of the instruction word is usually bounded from below by the number of instructions needed and the size of the immediate values necessary. Many CISC architectures use a variable-size instruction word to allow large immediate values while avoiding a general increase in instruction word size. The RISC architecture of the Xap2, however, uses a "PREFIX" instruction to load a part of an immediate value into a temporary register which is used to extend the immediate field of the next instruction. Its effect is similar to that of a variable-size instruction word, but with a simpler instruction set.

### 4.2.3 Power Consumption

Power consumption is very important in Chipcon products. Due to their wireless nature, they are often used in battery driven applications. Power consumption is measured in watts, but it is highly dependent on the frequency of operation, so it is common to find the power consumption of a processor in mW/MHz. The requirement for power consumption of < 25 uW/MHz given in the task is for the processor core without memory. In practice, however, for an architecture which demands large amounts of memory or frequent memory accesses, the power consumption of the memory surpasses

that of the core. It is therefore important that a low-power design also has sufficient registers to avoid frequent memory accesses. The power consumption of an architecture varies with the process in which it is implemented. For the processors where the power consumption was reported, the process was not always mentioned, and it will be assumed that the numbers are for the popular 18um process. The power consumption of the Xap1 processor is reported as 2.25 mW [Xap1]. Interestingly enough, the frequency of operation is not reported, and assuming a frequency of operation of 50 MHz, this gives 45 uW/MHz, which exceeds the specified value. In addition, the Xap1 only has 4 16-bit registers available in an accumulator architecture, which requires frequent memory accesses. The Xap1 must therefore be ruled out based on power consumption.

### 4.2.4 Ease of Programming

An important but unspecific criteria for a processor is that that it is easy to program. The availability of good compilers for high-level languages as for example "C" is important when writing large programs. All the above mentioned processors except the PicoBlaze implement architectures for which "C" compilers are available. For small control applications where code-size and speed is crucial, it is often necessary to program the processor in assembly language. Assembly language is a programming language in which each instruction generally corresponds to one machine language instruction on the architecture which the assembly language is for. In contrast to higher level languages, an assembly language reflects all the particularities of the ISA of the target machine. Assemblers are available for all the above mentioned architectures. The assembler is a computer program which translates a program written in assembly language to machine language. It is intended to close the semantic gap between the expressions that are close to the human way of representing statements, and the primitive operations of a processor [Clements]. The relationship between the above mentioned entities is described in Figure 1.

High Level Language -> Assembly Language -> Machine Language Compiler Assembler

#### Figure 1 - Code hierarchy

When programming a processor in assembly, it is important for the ease of coding that the architecture bit-width is greater or equal to the size of the data types being operated on. If the bit-width of the architecture is less than the size of the data, several instructions have to be used to perform an operation on the data, and the assembly programming becomes a complex task. This is a great disadvantage of the 8-bit architectures, and especially the PicoBlaze, as it has no high-level language compiler to hide this complexity.

Perhaps the greatest advantage of buying an IP core as opposed to developing a new solution is the availability of tools. In addition to the compilers, many of the above mentioned architectures have editors, debuggers and instruction set simulators available, which simplifies programming and debugging.

### 4.2.5 Architecture

One of the greatest disadvantages of the ArcLite is its interrupt handling. It implements interrupts by inserting an interrupt instruction into it's pipeline. The interrupt handling routine latency is the time from an external interrupt signal change until the first useful instruction of the interrupt routine is executed. For the ArcLite this time is 12 cycles in the worst case. In addition to this, high priority interrupts can not interrupt lower priority interrupt routine latency for a high priority interrupt is in fact 12 cycles plus the time it takes to finish a lower priority interrupt routine. This makes implementing control applications with any degree of real-time demands very difficult [ArcSupport].

One of the major disadvantages of the PicoBlaze is that it is only capable of addressing 1024 bytes of program memory, while a typical application for a firmware processor could easily be 4K bytes in size. This rules out the PicoBlaze.

## Part II

## Architecture Specification

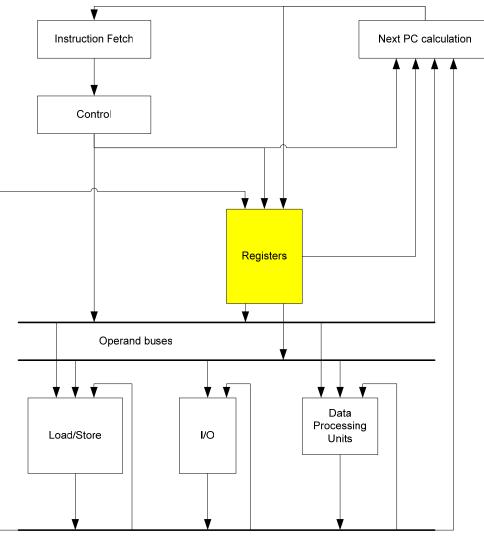

This chapter describes the processor from the perspective of the user, or the "Architecture" as described by Blaauw and Brooks [Blaauw1997]. This architecture specification was developed as a part of this project based on the requirements given in the task description (see section 1.1) and the subsequently developed requirements specification (see chapter 3). A discussion on many of the aspects of the NanoRisc design described in this chapter is found in chapter 10. The NanoRisc name was given as part of the task description and has become, as the name imposes, a relatively simple RISC processor. It features 13 16-bit general registers, a dedicated stack pointer, up to 32 I/O ports and a 16-bit memory interface. It features single cycle execution of all instructions that do not read from memory. It is a load/store architecture which means that logical and arithmetic operations can only be performed on data stored in the registers, however, efficient load/store and stack instructions makes moving data between memory and registers fast. A simple overview of the architecture is given in Figure 2.

Result bus

Figure 2 - NanoRisc simple overview

Before going into detail on the functionality of the processor, an overview of the nomenclature used will be given.

### 5.1 Nomenclature

Special registers:

SR: Status Register

- Halt: Halt Flag

- IRQ: Interrupt Request Flag

- IE: Interrupt Enabled Flag

- V: Two's complement overflow indicator

- N: Negative Flag

- Z: Zero Flag

- C: Carry Flag

PC: Program Counter SP: Stack Pointer

#### General 16-bit registers:

R0-R12: General registers

### Memory spaces

M: Data memory IO: I/O ports

#### **Bit change indications:**

"-": Not changed "\*": Changed "1": Set "0": Cleared

#### Instruction registers and operands:

Rd: Destination (and source) register in the Register File Rs Source register in the Register File K: Constant data k: Constant address

#### Bytes

LSB: Least significant byte MSB: Most significant byte

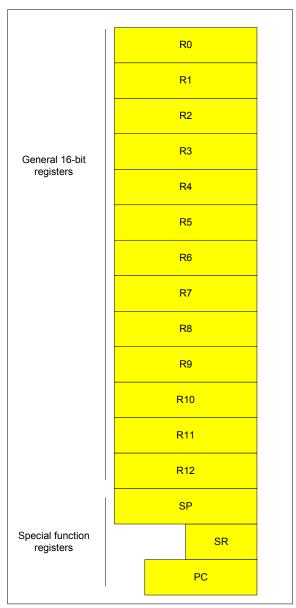

### 5.2 Address Space Overview

There are three different memory spaces in the NanoRisc. The first memory space is the register memory space. There are 16 addressable registers. The first 13 are general registers, followed by the 16-bit stack pointer, the 7-bit status register, and the up to 15-bit program counter (see Figure 3).

Figure 3 - Logical register layout

The second address space is the I/O address space. It is a 5-bit address space where the first 16 addresses are for input ports, and the last 16 addresses are for output ports. The third address space is the combined program and data memory space. It is a 16-bit memory space of which the user decides its composition of RAM and ROM. It is implemented in a manner that is impartial to the big endian/little endian problem. Only aligned word-accesses are allowed, and for byte operations, the byte read or written is read or written to and from the LSB of the register. The correct arrangement of bytes must be handled in an external module.

### 5.3 Instruction Addressing Modes

Due to the load/store nature of the architecture, the NanoRisc instruction set is not orthogonal when it comes to addressing modes. Each instruction supports only one addressing mode, and they are described for each instruction in Appendix A.

## 5.4 Constants

The constant field of the immediate instructions of the NanoRisc ranges from 2 to 8 bits while the architecture is 16-bits. To allow 16-bit immediate values in the branch, logical, arithmetic and load/store instructions, the "pre" instruction is included in the instruction set (see Appendix A). When the "pre" instruction precedes any of the above mentioned instructions that take a "pre" instruction, the constant field of the "pre" instruction is concatenated with the constant field of the instruction being executed to form a 16-bit constant field. The least significant bits of the "pre" instruction. The least significant bits of this constant is the immediate field of the instruction word of the current instruction.

## 5.5 Instruction Fetch

Instructions are fetched on each clock cycle with the exception of the first cycle of an instruction that reads from memory, or when waiting for a busy data memory. The instruction read from the instruction memory is executed in that same cycle. Which address to be loaded next is calculated and selected on each cycle, which voids the need for branch prediction.

## 5.6 General Registers

The NanoRisc contains 13 16-bit general registers without any dedicated role. These registers can be used in all operations where a source or destination register is required. There is no dedicated accumulator. The general registers are referenced in the assembler as R0 through R12, but aliases can be created for better clarity of code (see section 7.1.1.2).

## 5.7 Special registers

The special registers of the NanoRisc each have a dedicated role in the processor. They comprise the stack pointer (SP), status register (SR) and program counter (PC) and are referenced respectively as R13 through R15. These registers can be used in all operations where a source register is required, and with the exception of the program counter, they can also be used as destination registers. When a special register is used as destination register for an operation, this will override any other attempt to modify the contents of the register in that cycle. Note that for the registers that are not 16-bits, when used as a destination register, the result will be truncated.

### 5.7.1 SP

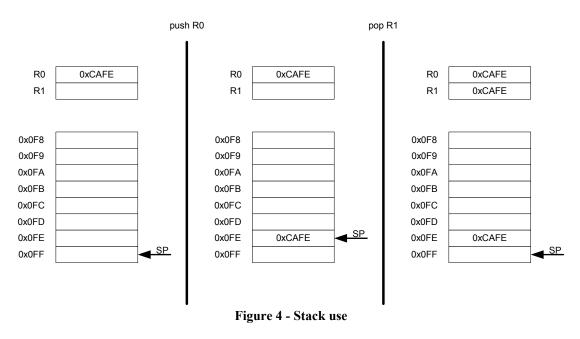

The stack pointer is a 16-bit register which points to the top of the top of the system stack located in the data memory. The stack pointer must be initialized to the desired address of the stack before it is used. Note that all stack operations are word operations, and that the stack pointer should then be initialized to an even address. Stack operations employ a

pre-decrement, post-increment scheme in which the stack pointer is decremented before writing a data object to its location (push) and incremented after reading an item from its location (pop). The operations that influence the stack are the following push/pop pairs:

- "push"/"pop"

- "call"/"ret"

- interrupt/"reti"

The instructions that operate on the stack pointer are summarized in Table 2.

| Table 2 - Stack instructions |                                                |  |  |

|------------------------------|------------------------------------------------|--|--|

| Mnemonic                     | Description                                    |  |  |

| call                         | Indirect Call                                  |  |  |

| calli                        | Push PC on the stack, jump to relative         |  |  |

| рор                          | Pop a value from the stack and put it in Rd    |  |  |

| push                         | Push the contents of Rd onto the stack         |  |  |

| ret                          | Jump to the PC popped from the stack + 2 bytes |  |  |

| reti                         | Jump to the PC popped from the stack           |  |  |

The stack can also be manipulated manually by using the stack pointer as the destination register of an operation, but it is then important to remember that the stack pointer should only point to even addresses. Figure 4 shows an example of stack use. The contents of the register R0 is pushed onto the stack, and then popped to register R1.

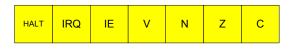

### 5.7.2 SR

The 8-bit status register contains the flags and status bits of the NanoRisc. The high nibble contains the bits that control various aspects of the processor while the lower nibble contains the flags that are set based on the result of a logical, arithmetic or shift operation. Which bits are affected by the different instruction is shown in Appendix A. Using the status register as destination register in an operation which writes to register

takes priority over the automatic updating of flags by the operation being executed. The register layout is shown in Figure 5, and the individual bits and their behavior when not written to as a register are described below.

Figure 5 - Status register

- HALT Halt execution. This bit is set when the processor should halt execution. No instructions are executed while this bit is set.

- IRQ Interrupt request. This bit is set on every clock cycle when the interrupt request line is held high, and cleared when it is low.

- IE Interrupt enable. When this bit is set, it masks out any interrupt request causing it not to be acknowledged.

- V Overflow. This bit is set when the result of an arithmetic operation overflows the signed variable range.

- N Negative. This bit is set whenever the result of an operation is negative.

- Z Zero. This bit is set whenever the result of an operation is zero.

- C Carry. This bit is set whenever an operation produces a carry.

### 5.7.3 PC

The program counter contains the program memory word address of the instruction currently being executed. Its width is fully configurable depending of the program memory size in the implementation. A zero is concatenated with the PC to make up the program memory byte address of the instruction (see Figure 6).

Figure 6 - Program address

The PC can not be more than 15-bits wide which would make a 16-bit byte address. A program memory address of 11-bits for example, enables the NanoRisc to address 2K instruction words, or 4K bytes of program memory. The PC is by default reset to -1, but the reset value can be changed by the user before synthesis and set to the address of the first instruction in the program minus one. The PC is written on each cycle of execution except when waiting for a memory operation (see 5.10). A manual write to PC by using it as the destination register of an operation is not allowed, however the "jmp" instruction provides much of the same functionality (see Appendix A).

## 5.8 Data Processing

The NanoRisc implements a comprehensive set of data processing instructions enabling the user to efficiently process data in the registers. In keeping with the load/store architecture philosophy, the data processing instructions all operate on values stored in the registers.

### 5.8.1 Arithmetic

The arithmetic instructions are provided to enable calculations on both signed and unsigned quantities stored in the registers. All arithmetic instructions set the flags in the status register as if a signed operation was performed. However, due to the principles of two's complement arithmetic, the same instruction can be used to calculate a valid result for both a signed operation and an unsigned operation. The distinction between signed and unsigned operations is made with the conditional branch instructions (see section 5.11). Table 3 gives an overview of the arithmetic instructions implemented in the NanoRisc.

#### Table 3 - Arithmetic instructions

| Mnemonic | Description                   |

|----------|-------------------------------|

| add      | Add                           |

| addc     | Add with Carry                |

| addci    | Add Immediate with Carry      |

| addi     | Add Immediate                 |

| cmp      | Compare                       |

| cmpi     | Compare Immediate             |

| sub      | Subtract                      |

| subc     | Subtract with Borrow          |

| subci    | Subtract Immediate with Carry |

| sxt      | Sign-extend LSB into MSB      |

| zxt      | Zero-extend LSB into MSB      |

|          |                               |

There is no instruction implemented to negate a register in one cycle, because it would require another multiplexer on the input to the ALU in addition to the control logic. Figure 7 shows how this can instead be done in two cycles employing the principle of two's complement.

inv RO addi RO, 1

Figure 7 – Negate

### 5.8.2 Logical

The logical instructions perform logical bitwise operations between the contents of two registers. They enable amongst other things the setting, clearing and toggling of individual bits. Table 4 gives an overview of the logical instructions of the NanoRisc.

Table 4 - Logical instructions

| Mnemonic | Description           |

|----------|-----------------------|

| and      | Logic AND             |

| andi     | Logic AND Immediate   |

| inv      | Invert Rd             |

| mov      | Copy register content |

| or       | Logic OR              |

| ori      | Logic OR Immediate    |

tstLogic TesttstiLogic Test ImmediatexorLogic XORxoriLogic XOR Immediate

The architecture does not have a dedicated function to clear the contents of a register. The same result can, however be produced by xor'ing the register with itself as shown in Figure 8. This will correctly set the zero flag of the status register.

xor R0, R0

Figure 8 - Clear register

### 5.8.3 Multiplication

The architecture is capable of single cycle 8x8 unsigned multiplication. The result is stored in one of the 16-bit registers. To achieve signed multiplication, the user must give the result the sign indicated by the xor of the sign bits of the multiplier and multiplicand. An overview of the NanoRisc multiplication instructions is given in Table 5.

#### **Table 5 - Multiplication instructions**

| Mnemonic | Description                              |

|----------|------------------------------------------|

| mul      | Unsigned Multiplication of LSB           |

| muli     | Unsigned Multiplication Immediate of LSB |

### 5.8.4 Shift and Rotate

The NanoRisc processor provides full shift and rotate functionality. Between 0 and 15 shifts can be performed in either direction in a single cycle, shifting in '0's, '1's, the value of the carry bit or the bits shifted out. A summary of the shift and rotate instructions is given in Table 6.

#### Table 6 - Shift and rotate instructions

| Mnemonic | Description            |

|----------|------------------------|

| rol      | Rotate left            |

| ror      | Rotate Right           |

| slc      | Carry Shift Left       |

| sll      | Logic Shift Left       |

| sra      | Arithmetic Shift Right |

| src      | Carry Shift Right      |

| srl      | Logic Shift Right      |

|          |                        |

The NanoRisc does not include a specific instruction to swap the LSB with the MSB of a register. This effect can instead be achieved by rotating the register 8 places to the left or to the right.

### 5.9 I/O

The NanoRisc Input/Output ports allow connection to peripherals or other NanoRisc processors, and resemble the external ports of the 8051 architecture. The advantage of keeping a separate set of I/O ports as opposed to memory mapped I/O is the possibility to perform single cycle bit-operations on output which is important when implementing bit-banging or timing critical control functions. Bit-banging is the action of transmitting data by emulating the protocol in software without the use of a task-specific hardware controller.

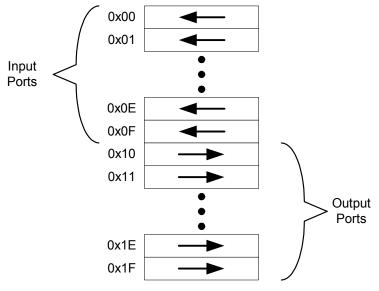

The processor contains a configurable number of addressable I/O ports. The width of the I/O ports is configurable from 1 to 16 bits. There are always equally many input ports as there are output ports with a maximum of 16 of each. The port layout with the maximum number of ports is described in Figure 9.

Figure 9 - I/O port layout

Read operations can be performed on either input or output ports. If the width of the I/O port is less than 16-bit, the value is zero-extended when read into a register. Operations that change the value of a port can only be performed on output ports. An attempt to change the value of an input port will be ignored by the processor. The NanoRisc I/O instructions are summarized in Table 7.

#### Table 7 - I/O instructions Mnemonic Description Clear bit in I/O out register iobc iobs Set bit in I/O out register Set bit in I/O out register to value of carry flag iosc Toggle bit in I/O in register iota Test bit in I/O in register iots rdio Read from I/O port Read from I/O port immediate address rdioi

| wrio  | Write to I/O port                   |

|-------|-------------------------------------|

| wrioi | Write to I/O port immediate address |

### 5.10 Memory

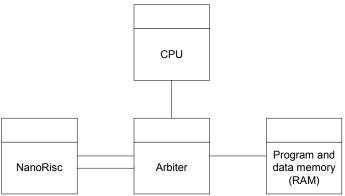

The program and data memories of the NanoRisc share address space, however they each have a separate memory bus going out of the NanoRisc (see 5.15). This enables the user to choose the most sensible solution for memory implementation depending of the demands of the application. A sensible solution in an application where the NanoRisc functions as a coprocessor to another microcontroller could be to implement the program and data memories in the same memory. This would require an arbiter between the program and data memory busses, the CPU and potentially other units using the same RAM (Random Access Memory) (see Figure 10). The CPU would then load the program data for the NanoRisc into it's RAM on startup. It is important that the NanoRisc program memory read would always be prioritized in such a setting.

Figure 10 - Single memory solution

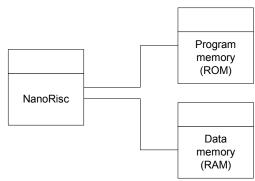

When the NanoRisc is used as a standalone implementation of a control function, it will in most cases be simpler and more economical to implement the program memory as a separate ROM (Read Only Memory) (see Figure 11). This configuration, however, does not allow the NanoRisc to read constants from its own program memory without an arbiter on the data bus with access to the ROM.

Figure 11 - Separate memories solution

Other configurations are along the same lines are of course possible. It should be noted, however, that the NanoRisc reads from program memory on practically every cycle and that these reads have to be prioritized.

### 5.10.1 Program Memory

The program memory contains the instruction words of the program. After a reset, the NanoRisc will always start reading from the "PC\_RESET\_VAL" address plus one word, so the program data should always be placed at this address. The memory is byte-addressed, and instruction words are always read from even addresses. Because a read instruction word is not registered internally before it is used, there are certain requirements as to the delivery of the program data. The program data must be a synchronous RAM or ROM. The access time (time after a rising clock edge before data is ready on the lines) should be relatively low in order to achieve a high operating frequency. If the program memory receives a read request from the NanoRisc which it can not fulfill on the next cylcle, it should deassert the "clk\_enable" signal to stall the processor for one cycle.

### 5.10.2 Data Memory

The data memory should be implemented in a synchronous RAM. The memory is byte addressed and there are operations to read and write both bytes and words. The LSB of a word is always on an even address. When reading a byte, the MSB of the result is ignored which gives freedom when implementing the memory. The physical memory unit in which the data memory is implemented can be shared with the program memory of the NanoRisc or other units. If, due to contention, a data memory request from the NanoRisc cannot be fulfilled on the next clock cycle, the memory wait signal (see section 5.15) should be asserted by the memory. This will cause the processor to wait until the signal is deasserted and the request has been fulfilled. The timing diagram in Figure 12 shows the sequence of events when the NanoRisc receives the memory wait signal at a load operation.

Figure 12 - Memory wait timing diagram

The instructions that operate on the data memory are summarized in Table 8.

#### Table 8 - Memory instructions

| Mnemonic | Description                  |

|----------|------------------------------|

| ld       | Load byte/word               |

| lda      | Load byte/word with inc/dec  |

| ldo      | Load byte/word with offset   |

| st       | Store byte/word              |

| sta      | Store byte/word with inc/dec |

| sto      | Store byte/word with offset  |

In addition to these, the stack operations described in 5.7.1 also operate on the data memory.

### 5.11 Program Flow

The default program flow is to execute next the instruction located after the current instruction in the program memory. This default flow can be overridden by either of two separate events; acknowledging an interrupt or change of flow by an instruction, where

the interrupt takes priority. A description of the interrupt handling is given in section 5.12. Change of flow by instruction is a single cycle operation, and this voids the need for branch prediction. Table 9 describes the instructions that potentially change the flow of the program execution.

#### Table 9 - Change-of-flow instructions

| Table 7 - Cha | Table 7 - Change-of-now instructions           |  |

|---------------|------------------------------------------------|--|

| Mnemonic      | Description                                    |  |

| beq           | Branch if zero flag is set                     |  |

| bges          | Branch if greater than or equal signed         |  |

| bgeu          | Branch if greater than or equal unsigned       |  |

| blts          | Branch if less than signed                     |  |

| bltu          | Branch if less than unsigned                   |  |

| bn            | Branch if negative                             |  |

| bne           | Branch if zero flag is not set                 |  |

| call          | Indirect Call                                  |  |

| calli         | Push PC on the stack, jump to relative         |  |

| jmp           | Indirect jump                                  |  |

| jmpi          | Unconditional branch                           |  |

| ret           | Jump to the PC popped from the stack + 2 bytes |  |

| reti          | Jump to the PC popped from the stack           |  |

|               |                                                |  |

### 5.12 Interrupt

The interrupt functionality allows the NanoRisc to respond promptly to external asynchronous events without having to poll continuously for them. This means that the processor is free to perform other useful work while it is waiting for an external event. An interrupt is triggered by an interrupt request (IRQ) signaled by the assertion of the "irq" input line on the NanoRisc (see section 5.15). This signal is sampled on each rising clock to set the "IRQ" flag in the status register. The interrupt will be considered for acknowledgement if the "interrupt enable" (IE) flag of the status register is set. There is no rollback functionality in the NanoRisc, so all instructions have to be executed atomically. This means that an interrupt will neither be acknowledged while a load instruction is waiting for the result, nor between the execution of a "pre" instruction and the instruction that is to use the "pre" value.

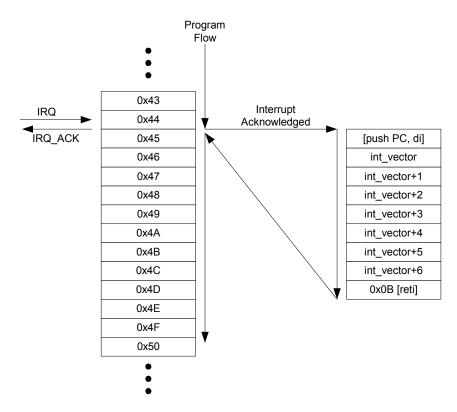

When an interrupt is acknowledged, the instruction read from memory on that cycle is not executed, instead the PC is pushed onto the stack and the next instruction to be loaded is the instruction at address of the interrupt vector (see Figure 13). The interrupt vector is an input to the NanoRisc(see section 5.15).

Figure 13 - Interrupt sequence

The maximum time between the rise of the IRQ line and the execution of the first instruction of the interrupt handler is two cycles. Usually the first instruction of the interrupt handler should be to push the status register to the stack in order to preserve the state at which the interrupt was acknowledged. When an interrupt is acknowledged, the "irq\_ack" signal is set high for one clock cycle, and the interrupt enable (IE) flag of the status register is cleared to avoid unwanted nesting of interrupts. To enable nested interrupts, the "ie" instruction should be run by the interrupt handler. Nested interrupts means that an interrupt handling routine can be interrupted to start another interrupt handling routine. The "reti" instruction will atomically return to the instruction which was about to be executed when the interrupt was acknowledged and enable interrupts by setting the IE flag of the status register. In some rare cases one might want to use an interrupt routine to disable interrupts. In this case one can replace the "reti" instruction by a decrement of the PC on the stack followed by a "ret" instruction which does not enable interrupts.

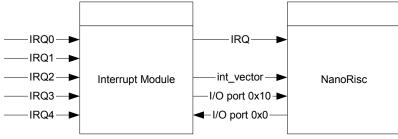

Two levels of priorities for interrupts may be achieved in the NanoRisc by the use of the "ie" instruction. The nature of the interrupt should be determined by software, and if it is a low priority interrupt, the "ie" instruction should be run to enable a high priority interrupt to interrupt the routine. This simple interrupt handling will be insufficient for some applications. In those cases, an external interrupt module such as a programmable interrupt controller (PIC) [Bolado2003] can be used to provide extended interrupt functionality as described in Figure 14.

Figure 14 - External interrupt module

Several interrupt request lines may be connected to the interrupt module. The module prioritizes the interrupts and forwards an IRQ to the NanoRisc. The NanoRisc will, as one of the first operations of the interrupt handler, read the identity of the current interrupt from the I/O lines. Interrupt priorities may be changed dynamically by the NanoRisc by communicating with the interrupt module over the I/O lines. Alternatively, the interrupt module can dynamically set the interrupt vector depending on the identity of the interrupt.

The architecture of the NanoRisc also allows software interrupts or "traps". A trap can be implemented by manually setting the "IRQ" flag of the status register, for example by using the emulated raise interrupt ("ri") instruction (see Appendix A). Please note that the NanoRisc does not make a distinction between software and hardware interrupts, and that a software interrupt is also acknowledged using the external "irq\_ack" line.

# 5.13 Halt

The halt functionality of the NanoRisc enables it to be entered into a power-saving mode. The "sleep" input line (see 5.13) is sampled on every rising clock edge into the "halt" bit of the status register. When the halt bit is set, the state of the processor is frozen, and no more instructions are performed. The "halt" bit also drives the "is\_sleeping" output line. When the "is\_sleeping" signal goes hight, the "clk\_en" signal can be driven low, causing the registers of the NanoRisc to stop sampling, further reducing the power consumption. To wake the NanoRisc, the "clk\_en" signal must be driven high, and an IRQ must be signaled. The processor will then continue execution where it left off or handle the interrupt if the interrupt enable bit of the status register is set. Another alternative for waking the processor is to reset it, in which case the state of the processor is reset and execution starts from address 0 (see section 5.14).

# 5.14 Reset

A reset of the processor is performed by holding the "reset\_n" line low for at least one clock cycle (see section 5.15). A reset will set the status register to 0, which means among other things that interrupt is initially disabled. The PC is by default reset to -1, but the reset value can be changed by the user before synthesis and set to the address of the first instruction in the program minus one. The program memory read lines "p\_rdata" should be reset to 0. The I/O output registers are reset to 0. The other registers of the NanoRisc are not affected by a reset.

## 5.15 Interface

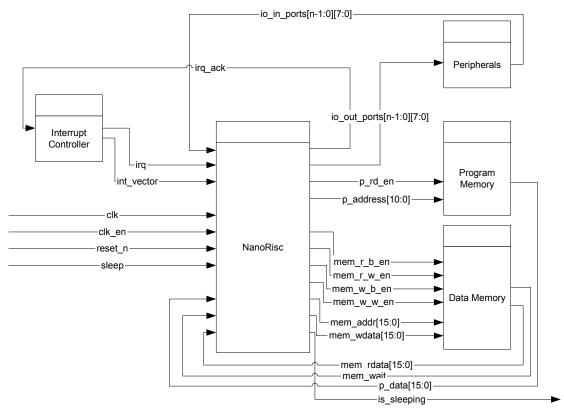

Figure 15 - Top-level interface

An overview of the top-level interface signals to the NanoRisc is shown in Figure 15. A detailed description of each signal is given in Table 10.

| Table 10 - Top-level int | terrace s | ignal descriptions                                                                                                                                                 |

|--------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| io_in_ports              | in        | I/O input ports. It consists of n ports of byte width. Valid                                                                                                       |

| [n-1:0][7-0]             |           | data should be present on these lines when reading from the corresponding I/O port.                                                                                |

| irq                      | in        | <b>Interrupt request line.</b> Sampled on each rising clock to set the IRQ flag in the status register. Should be deasserted as soon as the "irq_ack" is asserted. |

| int_vector               | in        | <b>Interrupt vector.</b> These lines contain the address of the interrupt handler.                                                                                 |

| clk                      | in        | <b>Clock input.</b> All elements of the NanoRisc CPU are clocked from the rising edge of this signal.                                                              |

| clk_en                   | in        | <b>Clock enable signal.</b> This signal gates the clock signal to all registers and should be deasserted when the processor is sleeping to save power.             |

| reset_n                  | in        | <b>Reset.</b> This signal is active low and should be deasserted for at least one clock cycle. It resets the CPU to the state described in section 5.14.           |

| sleep                    | in        | Sleep. This signal will when asserted for at least one clock                                                                                                       |

#### Table 10 - Top-level interface signal descriptions

| p_rdata[15:0]                | in  | cycle cause the "halt" flag of the status register to be<br>asserted and the processor to enter the sleep state.<br><b>Program data.</b> The valid instruction word corresponding to<br>the address on the "p_address" lines should be present on<br>these lines after each positive clock edge where "p_rd_en"<br>has been asserted. See section 5.2 for maximum allowable<br>delay. |

|------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mem_wait                     | in  | <b>Memory wait.</b> This signal should be asserted whenever the data memory is busy and will be unable to fulfill a request                                                                                                                                                                                                                                                           |

| mem_rdata[15:0]              | in  | from the NanoRisc processor on the next clock cycle.<br><b>Data memory read data.</b> This signal should contain the<br>data as indicated by the address on the "mem_addr" on the<br>cycle after one of the "mem_r_b_en" or "mem_r_w_en"<br>signals are asserted.                                                                                                                     |

| irq_ack                      | out | <b>Interrupt request acknowledge.</b> This signal is asserted as soon as an interrupt request has been acknowledged. See section 5.12 for a description of the event sequence.                                                                                                                                                                                                        |

| io_out_ports<br>[n-1:0][7:0] | out | <b>I/O output ports.</b> It consists of n ports of byte width. These ports always reflect the contents of the output registers of the processor, and can be read at any time.                                                                                                                                                                                                         |

| p_rd_en                      | out | <b>Program memory read enable.</b> This signal is asserted whenever a word should be read from the program memory.                                                                                                                                                                                                                                                                    |

| p_address[10:0]              | out | <b>Program memory address.</b> This byte address indicates which word which is to be read from the program memory.                                                                                                                                                                                                                                                                    |

| mem_r_b_en                   | out | <b>Data memory read byte enable.</b> This signal is asserted<br>whenever a byte should be read from the data memory.                                                                                                                                                                                                                                                                  |

| mem_r_w_en                   | out | <b>Data memory read word enable.</b> This signal is asserted whenever a word should be read from the data memory.                                                                                                                                                                                                                                                                     |

| mem_w_b_en                   | out | <b>Data memory write byte enable.</b> This signal is asserted whenever the LSB should be written from the "mem wdata" lines to the data memory.                                                                                                                                                                                                                                       |

| mem_w_w_en                   | out | <b>Data memory write word enable.</b> This signal is asserted whenever a word should be written from the "mem_wdata" lines to the data memory.                                                                                                                                                                                                                                        |

| mem_addr[15:0]               | out | <b>Data memory address.</b> This byte address indicates which part of the data memory should be read or written.                                                                                                                                                                                                                                                                      |

| mem_wdata[15:0]              | out | <b>Data memory write data.</b> This signal contains valid data to be written to memory whenever the "mem_w_b_en" or the                                                                                                                                                                                                                                                               |

| is_sleeping                  | out | "mem_w_w_en" signals are asserted.<br><b>Is sleeping.</b> When this signal is asserted, the processor has<br>entered the sleep mode and will not execute any new<br>instructions until an interrupt request is received.                                                                                                                                                              |

# 5.16 Instruction Set

The machine code instruction set of the NanoRisc consists of 63 16-bit instructions. A summary of the instruction set showing how many cycles of execution is required for each instruction and a brief description of each is given in Table 11.

#### Table 11 - Instruction set summary

|       |     | Description                                        |

|-------|-----|----------------------------------------------------|

| add   | 1   | Add                                                |

| addc  | 1   | Add with Carry                                     |

| addci | 1   | Add Immediate with Carry                           |

| addi  | 1   | Add Immediate                                      |

| and   | 1   | Logic AND                                          |

| andi  | 1   | Logic AND Immediate                                |

| beq   | 1   | Branch if zero flag is set                         |

| bges  | . 1 | Branch if greater than or equal signed             |

| bgeu  | 1   | Branch if greater than or equal unsigned           |

| blts  | 1   | Branch if less than signed                         |

| bltu  | 1   | Branch if less than unsigned                       |

| bn    | 1   | Branch if negative                                 |

| bne   | 1   | Branch if zero flag is not set                     |

| call  | 1   | Indirect Call                                      |

| calli | 1   | Push PC on the stack, jump to relative             |

| cmp   | 1   | Compare                                            |

| cmpi  | 1   | Compare Immediate                                  |

| inv   | 1   | Invert Rd                                          |

| iobc  | 1   | Clear bit in I/O out register                      |

| iobs  | 1   | Set bit in I/O out register                        |

| iosc  | 1   | Set bit in I/O out register to value of carry flag |

| iotg  | 1   | Toggle bit in I/O in register                      |

| iots  | 1   | Test bit in I/O in register                        |

| jmp   | 1   | Indirect jump                                      |

| jmpi  | 1   | Unconditional branch                               |

| ld    | 2   | Load byte/word                                     |

| lda   | 2   | Load byte/word with inc/dec                        |

| ldi   | 1   | Load Immediate                                     |

| ldo   | 2   | Load byte/word with offset                         |

| mov   | 1   | Copy register content                              |

| mul   | 1   | Unsigned Multiplication of LSB                     |

| muli  | 1   | Unsigned Multiplication Immediate of LSB           |

| nop   | 1   | No-operation                                       |

| or    | 1   | Logic OR                                           |

| ori   | 1   | Logic OR Immediate                                 |

| рор   | 2   | Pop a value from the stack and put it in Rd        |

| pre   | 1   | Load 10-bit PRE register                           |

| push  | 1   | Push the contents of Rd onto the stack             |

| rdio  | 1   | Input                                              |

| rdioi | 1   | Read from I/O port                                 |

| ret   | 2   | Jump to the PC popped from the stack               |

| reti  | 2   | Jump to the PC popped from the stack               |

| rol   | 1 | Rotate left                   |

|-------|---|-------------------------------|

| -     | • |                               |

| ror   | 1 | Rotate Right                  |

| slc   | 1 | Carry Shift Left              |

| sll   | 1 | Logic Shift Left              |

| sra   | 1 | Arithmetic Shift Right        |

| SrC   | 1 | Carry Shift Right             |

| srl   | 1 | Logic Shift Right             |

| st    | 1 | Store byte/word               |

| sta   | 1 | Store byte/word with inc/dec  |

| sto   | 1 | Store byte/word with offset   |

| sub   | 1 | Subtract                      |

| subc  | 1 | Subtract with Borrow          |

| subci | 1 | Subtract Immediate with Carry |

| sxt   | 1 | Sign-extend LSB into MSB      |

| tst   | 1 | Logic Test                    |

| tsti  | 1 | Logic Test Immediate          |

| wrio  | 1 | Output                        |

| wrioi | 1 | Write to I/O port             |

| xor   | 1 | Logic XOR                     |

| xori  | 1 | Logic XOR Immediate           |

| zxt   | 1 | Zero-extend LSB into MSB      |

|       |   |                               |

The encoding of the instruction words is shown in Figure 16.

|            | Bits |    |    |        |            |             |                  |     |                 |   |   |   |          |      |     |   |

|------------|------|----|----|--------|------------|-------------|------------------|-----|-----------------|---|---|---|----------|------|-----|---|

| Mnemonic   | 15   | 14 | 13 | 12     | 11         | 10          | 9                | 8   | 7               | 6 | 5 | 4 | 3        | 2    | 1   | 0 |

| nop        | 0    | 0  | 0  | 0      | 0          | 0           | 0                | 0   | 0               | 0 | 0 |   |          | SERV |     |   |

| ret        | 0    | 0  | 0  | 0      | 0          | 0           | 0                | 0   | 0               | 0 | 0 |   |          | SERV |     |   |