### Power Factor Correction for a Bidirectional On-Board Charger for Electric Vehicles and Plug-in Hybrid Electric Vehicles

A fundamental study of the bidirectional totem-pole PFC

#### Sondre Westby Johannessen

Master of Energy and Environmental Engineering Submission date: June 2018 Supervisor: Roy Nilsen, IEL Co-supervisor: Tore Undeland, IEL Torbjørn Sørsdahl, Valeo Siemens eAutomotive

Norwegian University of Science and Technology Department of Electric Power Engineering

## Abstract

With the beginning implementation of a "smart grid" in industrialized countries increasing the load flexibility of customers, as well as communication with the grid operators, a potential market for bidirectional on-board chargers (OBC) is emerging. The OBC is the electric vehicle charger located within the vehicle, operating as a link between the DC-voltage battery and the AC grid voltage in electricity sockets anywhere, thus working at a universal voltage range (85Vrms-265Vrms) with rated power in the range of 1.9kW to 3.5kW. To maximize the real power drawn by these OBCs, they are designed with power factor correction (PFC) converters at the AC grid interface, shaping the drawn AC current sinusoidally and in phase with the AC voltage, to maximize the power factor. Thus, a bidirectional OBC would necessarily require a bidirectional PFC. In this master's thesis, a simulation model is developed for a bidirectional totem-pole PFC, attempting to verify the use of this topology as the mentioned bidirectional OBC PFC. The work is focused on describing the basic bidirectional operation of the bidirectional totem-pole PFC, deriving expressions for currents, voltages and losses, as well as for the gate logic and control system. Average current mode control is used, with cascaded current and voltage control including PI controllers and Symmetrical optimum tuning. To verify the simulation model for the power levels and demands of an OBC, the main components are dimensioned to achieve 98% efficiency at 230Vrms, 3.5kW and 90kHz switching frequency, implementing GaN eHEMTs in the fast-switching leg of the totem-pole. At last, simulations are performed, showing that the PFC is able to achieve a power factor of 0.998 and a THD of 5% in both G2V and V2G, without a DM filter on the AC side.

## Sammendrag

Etter hvert som implementeringen av "smarte nett" er i ferd med å skyte fart i industrialiserte land, med økt lastfleksibilitet på kundesiden og økt kommunikasjon mot nettoperatørene, begynner det å åpne seg et marked for bidireksjonelle såkalte "on-board chargers" (OBC-er). En OBC er elbilladeren som er plasserte inne i elbilen og fungerer som en link mellom elbilbatteriet - som krever DC-spenning og AC-spenningen i strømuttaket, hvilket betyr at den må designes for å operere ved universell AC-spenning (85Vrms-265Vrms) og nominelle effektnivåer mellom 1.9kW og 3.5kW. For å maksimere den reelle effekten trukket av OBC-en, er de designet med såkalte "power factor corretion"-omformere (PFC-er) på AC-siden ut mot nettet. Denne kontrollerer AC-strømmen som trekkes til å være formet som en sinus og i fase med AC-spenningen på nettet, for på den måten å maksimere effektfaktoren. Av den grunn, vil nødvendigvis en bidireksjonell OBC behøve en bidireksjonell PFC. I denne masteravhandlingen vil det bli utviklet en såkalt bidireksjonell "totem-pole PFC", mens det forsøkes å verifisere hvorvidt dennetopologien egner seg for bruk i en bidireksjonell PFC for en OBC. Hovedfokus for oppgaven vil ligge i å beskrive hvordan en bidireksjonell totem-pole PFC fungerer grunnleggende, mens det vil utledes uttrykk for strømmer, spenninger og tap i omformeren, samt gate-logikken og kontrollsystemet. "Average current mode" brukes i kontrollsystemet, med dobbel kontrollsløyfe med strøm- og spenningskontroll, begge to med PI-regulatorer dimensjonert med Symmetrisk optimum. For å verifisere simuleringsmodellen for de aktuelle spennings- og effektnivåene, dimensjoneres de viktigste komponentene til å opnå 98% virkningsgrad ved 230Vrms, 3,5kW og 90kHz switchefrekvens, med GaN eHEMT-er implementert i det hurtigswitchende totem-pole-benet. Til slutt ble det utført simuleringer av modellen, og disse viser at den bidireksjonelle totem-pole PFC-en oppnår en effektfaktor på 0.998 og en THD på 5% både under G2V og V2G, uten filter på AC-siden.

## Preface

This master's thesis is conducted during the spring 2018, and it is the finishing work of a master's degree in Energy and Environmental Engineering at the Norwegian University of Science and Technology (NTNU), Department of Electric Power Engineering. The thesis focuses on power electronics, and it is a continuation of a specialization project performed during the autumn 2017, both of which have been announced and guided by Valeo Siemens eAutomotive.

I would like to thank my supervisor, Roy Nilsen, for his valuable guidance and support through numerous guidance sessions throughout the year, and co-supervisor, Tore M. Undeland, for his expert advice. My sincere gratitude goes to Torbjørn Sørsdahl at Valeo Siemens for his effort, advice and guidance throughout the year. Thanks also to the rest of the staff at Valeo Siemens in Drammen who were ready to answer any of my questions without hesitation, during my stays there through the year.

Finally, I would like to place a warm thanks to my family for their loving support, and to my favourite Ingunn for letting me know when it is time to go home for the night.

## Table of Contents

| Ab | ostrac  | t                                               | i    |

|----|---------|-------------------------------------------------|------|

| Sa | mme     | ndrag                                           | ii   |

| Pr | eface   |                                                 | iii  |

| Та | ble of  | Contents                                        | viii |

| Li | st of ] | <b>Fables</b>                                   | ix   |

| Li | st of I | ligures                                         | xiii |

| Ac | rony    | ns                                              | xiv  |

| 1  | Intr    | oduction                                        | 1    |

|    | 1.1     | Motivation                                      | 2    |

|    | 1.2     | The Bidirectional On-Board Charger              | 4    |

|    | 1.3     | The bidirectional PFC                           | 7    |

|    | 1.4     | Scope of work                                   | 10   |

| 2  | Basi    | c operation of the bidirectional totem-pole PFC | 13   |

|    | 2.1     | G2V operation                                   | 14   |

|    | 2.2     | V2G operation                                   | 16   |

|    | 2.3     | Boost inductor                                  | 18   |

|    |         | 2.3.1 Current waveforms and ripple              | 18   |

|   |      | 2.3.2   | Conduction losses                         | 20 |

|---|------|---------|-------------------------------------------|----|

|   | 2.4  | Transis | stors                                     | 22 |

|   |      | 2.4.1   | Current waveforms and ripple              | 22 |

|   |      | 2.4.2   | Conduction losses                         | 25 |

|   |      | 2.4.3   | Switching losses                          | 27 |

|   | 2.5  | DC-lin  | ık                                        | 30 |

|   |      | 2.5.1   | Current waveforms and ripple              | 30 |

|   |      | 2.5.2   | Conduction losses                         | 32 |

| 3 | Con  | nonent  | ts dimensioning                           | 35 |

| 0 | 3.1  |         | k capacitor                               | 36 |

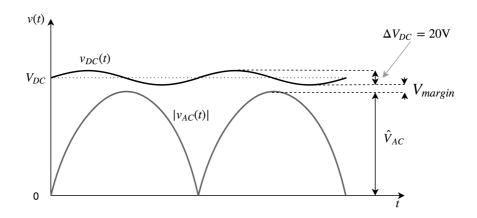

|   | 5.1  | 3.1.1   | DC-link rated voltage                     | 36 |

|   |      | 3.1.2   | DC-link rated current                     | 38 |

|   |      | 3.1.2   | DC-link capacitance value                 | 38 |

|   |      | 3.1.4   | Capacitor choice                          | 39 |

|   | 3.2  |         | stors                                     | 41 |

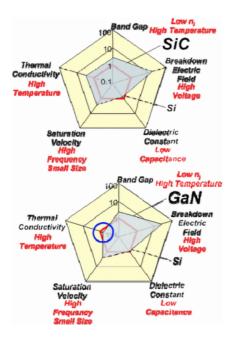

|   | 5.2  | 3.2.1   | Choice of transistor technology           | 41 |

|   |      | 3.2.2   | Guesstimating component loss distribution | 43 |

|   |      | 3.2.3   | Totem-leg transistors                     | 45 |

|   |      | 3.2.4   | Switching frequency                       | 47 |

|   |      | 3.2.5   | Comparison to state-of-the-art MOSFETs    | 48 |

|   |      | 3.2.6   | Rectifier-leg transistors                 | 49 |

|   | 3.3  | Boost   | inductor                                  | 51 |

|   |      | 3.3.1   | Boost inductance value                    | 51 |

|   |      | 3.3.2   | RMS current rating                        | 52 |

|   |      | 3.3.3   | Saturation current rating                 | 52 |

|   |      | 3.3.4   | Choice of inductor                        | 53 |

| 4 | Driv | e and c | ontrol                                    | 55 |

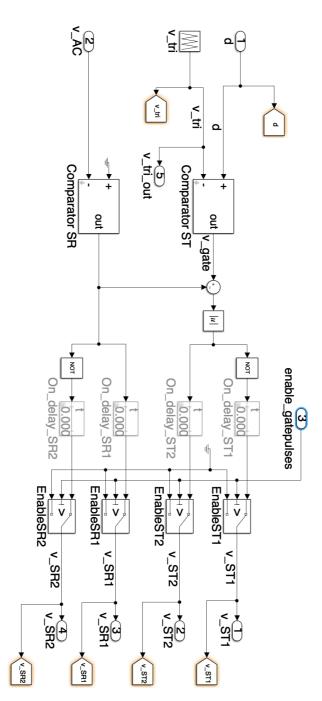

|   | 4.1  |         | rive logic                                | 56 |

|   |      | 4.1.1   | Rectifier leg                             | 56 |

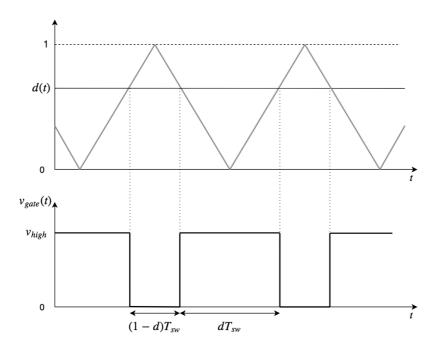

|   |      | 4.1.2   | Totem leg                                 | 58 |

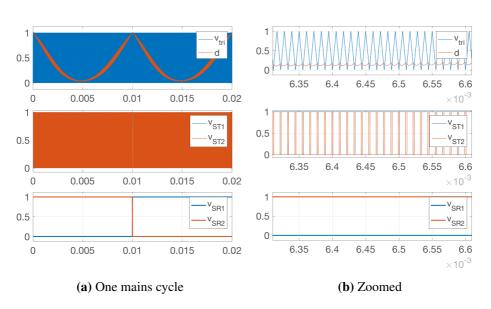

|   |      | 4.1.3   | Waveforms                                 | 61 |

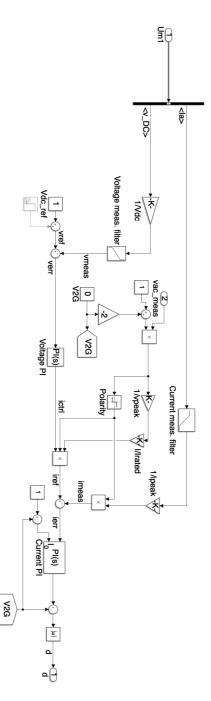

|   | 4.2  |         | ol system                                 | 63 |

|   |      | 4.2.1   | Control logic                             | 65 |

|   |      | 4.2.2   | Current control loop                      | 70 |

|   |      |         | -                                         |    |

|    |             | 4.2.3         | Voltage control loop                                   | 78  |

|----|-------------|---------------|--------------------------------------------------------|-----|

| 5  | Syst        | em-leve       | l simulations                                          | 85  |

| 6  | Feas        | sibility o    | of the bidirectional totem-pole PFC                    | 89  |

|    | 6.1         | Model         | shortcomings                                           | 89  |

|    | 6.2         | Loss c        | omparison to a regular boost PFC                       | 91  |

|    |             | 6.2.1         | Comparison at worst-case operating temperature         | 93  |

|    |             | 6.2.2         | Comparison at normal operating conditions              | 94  |

|    |             | 6.2.3         | Comparison at 120Vrms                                  | 95  |

| 7  | Con         | clusion       | and Further Work                                       | 97  |

|    | 7.1         | Conclu        | ision                                                  | 97  |

|    | 7.2         | Furthe        | r Work                                                 | 99  |

| Bi | bliogi      | raphy         |                                                        | 101 |

| Ap | pend        | lices         |                                                        | 109 |

| A  | Vale        | o Sieme       | ens bidirectional OBC specifications                   | 111 |

| B  | Lite        | rature 1      | review on power factor correction converters           | 121 |

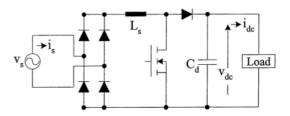

|    | <b>B</b> .1 | Power         | factor correction AC-DC converter                      | 121 |

|    |             | <b>B</b> .1.1 | Conventional PFC                                       | 122 |

|    |             | B.1.2         | Bidirectional PFC                                      | 124 |

| С  | Pap         | er on G       | aN HEMTs and bidirectional PFCs                        | 129 |

| D  |             |               |                                                        | 137 |

|    | D.1         | Modul         | us Optimum in current loop                             | 137 |

|    |             | D.1.1         | PI controller parameters                               | 137 |

|    |             | D.1.2         | Current measurement filter design with Modulus optimum | 138 |

|    |             | D.1.3         | Simulations                                            | 139 |

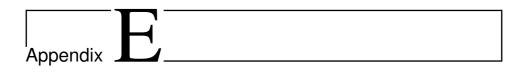

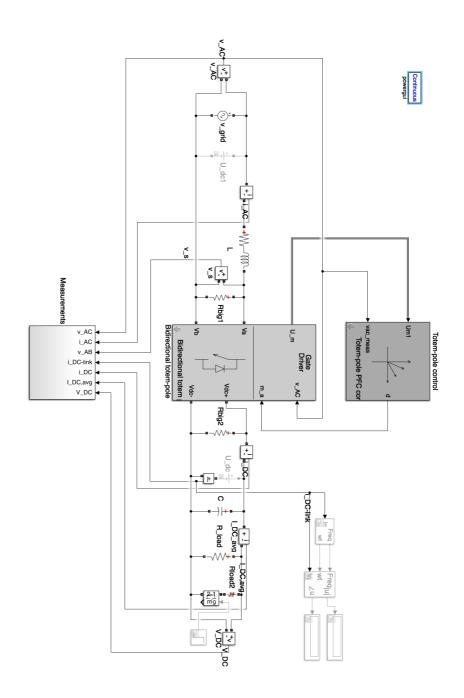

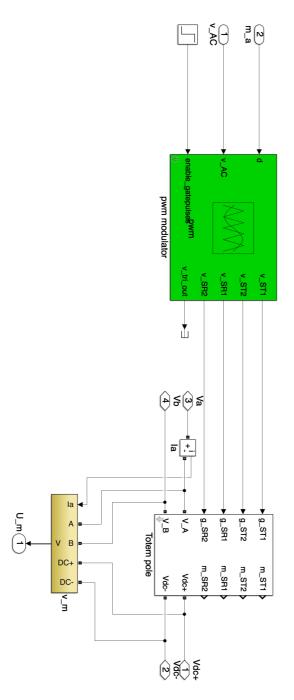

| E  | Imp         | lemente       | ed Simulink model                                      | 141 |

| F  | MA          | ГLAB с        | ode                                                    | 145 |

|    | F.1         | Contro        | ller tuning script                                     | 145 |

| G | Syste | em-level simulations    | 153 |

|---|-------|-------------------------|-----|

|   | F.2   | Filter graphical solver | 149 |

# List of Tables

| 1.1 | Demands and specifications for the bidirectional universal OBC,    |    |

|-----|--------------------------------------------------------------------|----|

|     | from [1]                                                           | 11 |

| 1.2 | PFC-specific demands and specifications                            | 12 |

| 3.1 | Key parameters for the relevant electrolytic capacitor used by Va- |    |

|     | leo Siemens today. [1]                                             | 39 |

| 3.2 | Guesstimated design rule losses distribution in the bidirectional  |    |

|     | totem-pole PFC.                                                    | 45 |

| 3.3 | Some key parameters and rated values of the GaN Systems eHEMTs     |    |

|     | at $T_{case} = 25^{\circ}$ C.                                      | 46 |

| 3.4 | Calculated conduction losses of the eHEMT models                   | 47 |

| 3.5 | Estimated switching energy, losses and frequency of GS66516        | 47 |

| 3.6 | Some key parameters and rated values of MOSFET IPW60R045CPA        |    |

|     | at $T_{case} = 25^{\circ}$ C.                                      | 50 |

| 3.7 | Estimated inductor parameters based on technology used by Valeo    |    |

|     | Siemens today.[1]                                                  | 53 |

|     |                                                                    |    |

# List of Figures

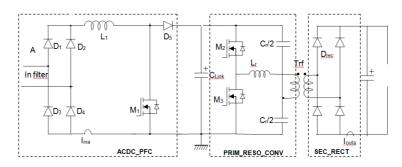

| 1.1  | A sketch of the current Valeo Siemens OBC topology [1]               | 4  |

|------|----------------------------------------------------------------------|----|

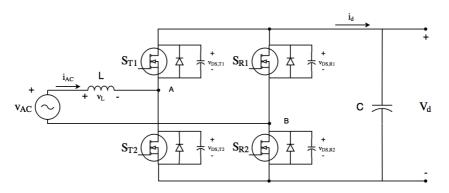

| 1.2  | The basic bidirectional PFC topology                                 | 8  |

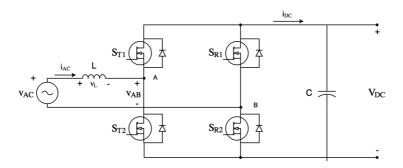

| 2.1  | The basic bidirectional totem-pole topology                          | 13 |

| 2.2  | The G2V operation of the bidirectional totem-pole PFC                | 15 |

| 2.3  | The V2G operation of the bidirectional totem-pole PFC                | 17 |

| 2.4  | CCM $i_L$ and $v_L$ ripple over one switching period                 | 18 |

| 2.5  | Boost CCM $\Delta i_L$ vs duty cycle                                 | 19 |

| 2.6  | The inductor current compared to the AC mains voltage through-       |    |

|      | out one mains cycle.                                                 | 20 |

| 2.7  | The rectifier-leg transistor drain-source currents throughout one    |    |

|      | mains cycle during G2V.                                              | 22 |

| 2.8  | The current ripple of the totem-leg switches during positive mains   |    |

|      | half cycle in G2V operation.                                         | 23 |

| 2.9  | The totem-leg transistor drain-source currents throughout one mains  |    |

|      | cycle during G2V                                                     | 25 |

| 2.10 | Approximation of the switching characteristics of a MOSFET           | 28 |

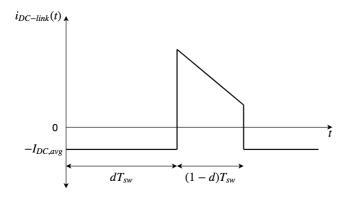

| 2.11 | Illustration of he DC-link capacitor, voltage and currents           | 30 |

| 2.12 | The current through the DC-link capacitor over one totem-leg switch- |    |

|      | ing period                                                           | 31 |

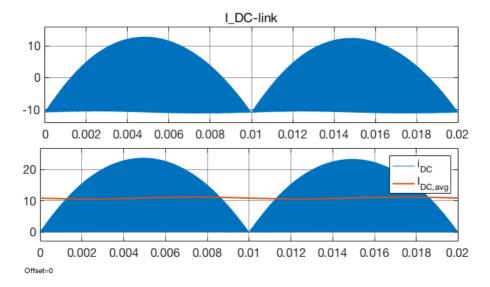

| 2.13 | The DC-side currents throughout one mains cycle during G2V           | 31 |

| 3.1  | DC-link voltage design requirements compared to AC mains voltage.    | 37 |

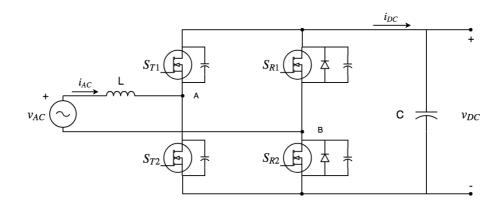

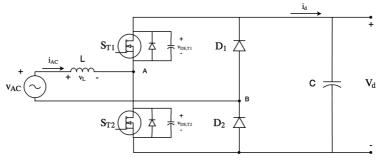

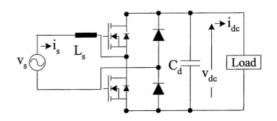

| 3.2               | The bidirectional totem pole topology with GaN eHEMTs in the                                                                                                                                                                                                                                                                                       |                          |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|                   | totem leg and MOSFETs in the rectifier leg                                                                                                                                                                                                                                                                                                         | 44                       |

| 4.1               | A screenshot of the PWM system implemented in Simulink                                                                                                                                                                                                                                                                                             | 57                       |

| 4.2               | Illustration of the pulse width modulation used in this                                                                                                                                                                                                                                                                                            | 59                       |

| 4.3               | Duty cycle and gate drive signals over one mains cycle and zoomed                                                                                                                                                                                                                                                                                  |                          |

|                   | in on a few switching cycles.                                                                                                                                                                                                                                                                                                                      | 62                       |

| 4.4               | Current and Voltage control systems implemented in Simulink                                                                                                                                                                                                                                                                                        | 64                       |

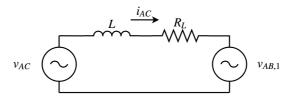

| 4.5               | The fundamental-frequency equivalent totem-pole PFC                                                                                                                                                                                                                                                                                                | 65                       |

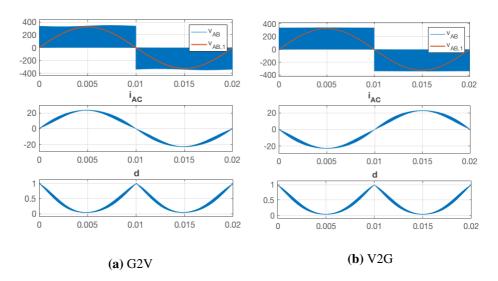

| 4.6               | Some selected waveforms over one mains cycle in G2V and V2G                                                                                                                                                                                                                                                                                        |                          |

|                   | operation.                                                                                                                                                                                                                                                                                                                                         | 68                       |

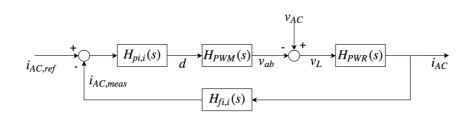

| 4.7               | The inner current control loop                                                                                                                                                                                                                                                                                                                     | 70                       |

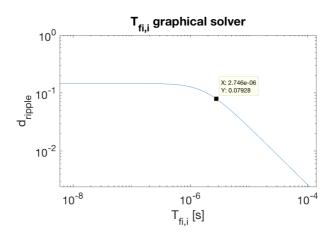

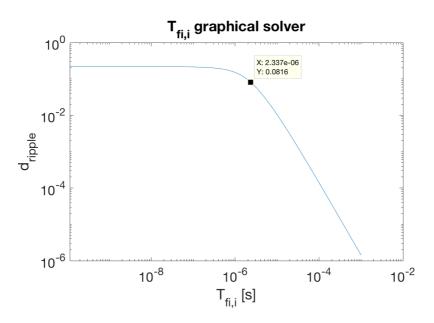

| 4.8               | Graphical solution of (4.27) to find $T_{fi,i}$                                                                                                                                                                                                                                                                                                    | 75                       |

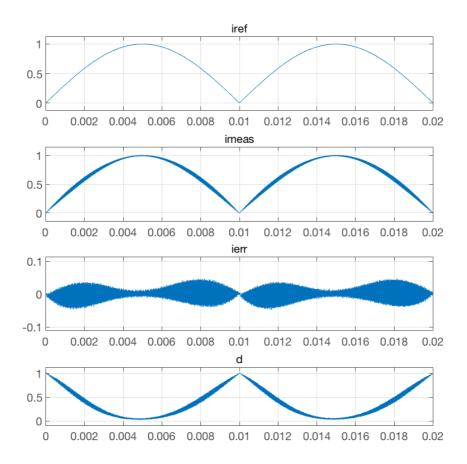

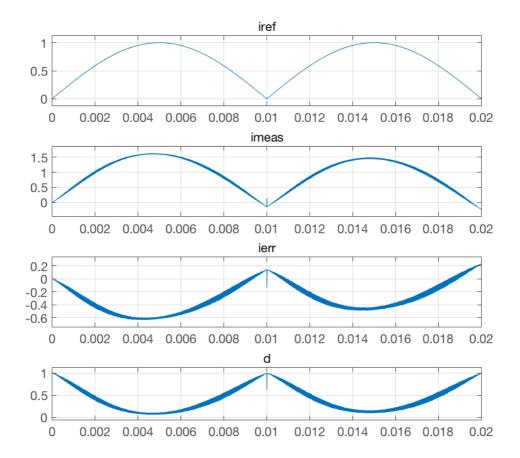

| 4.9               | Simulation of current controller waveforms during one mains period.                                                                                                                                                                                                                                                                                | 76                       |

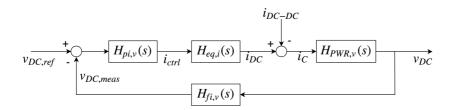

| 4.10              | A block diagram of the voltage control loop                                                                                                                                                                                                                                                                                                        | 78                       |

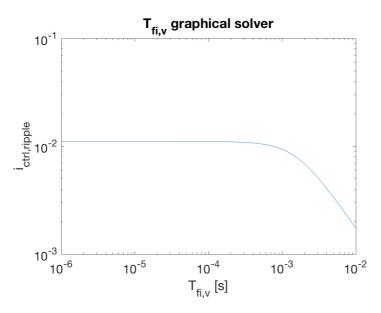

| 4.11              | Grapical solution to (4.36), with $\omega_c = 2\pi \cdot 500$ rad/s                                                                                                                                                                                                                                                                                | 81                       |

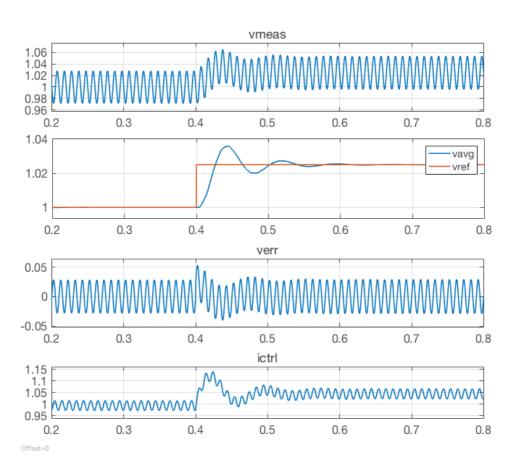

| 4.12              | Voltage controller step response to a 10V leap in voltage reference.                                                                                                                                                                                                                                                                               | 82                       |

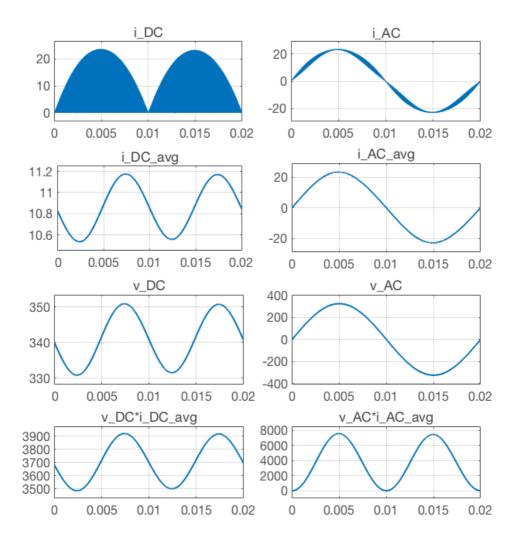

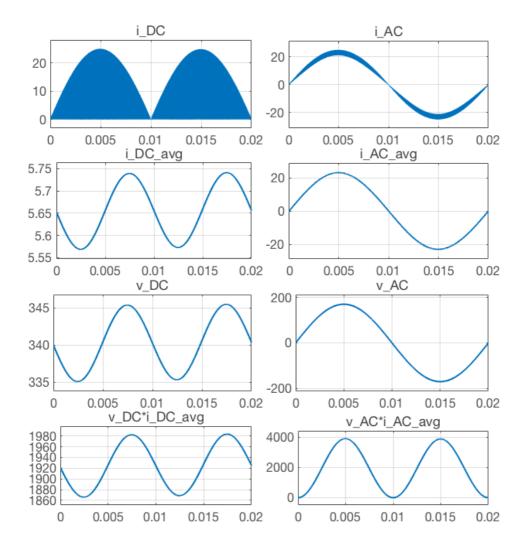

| 5.1               | System-level simulation results at 230Vrms G2V operation                                                                                                                                                                                                                                                                                           | 87                       |

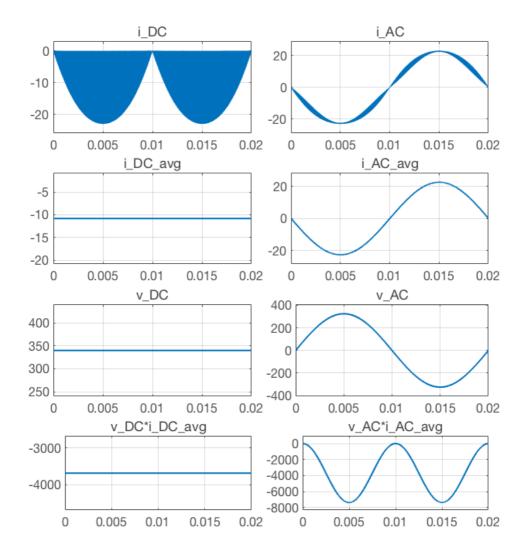

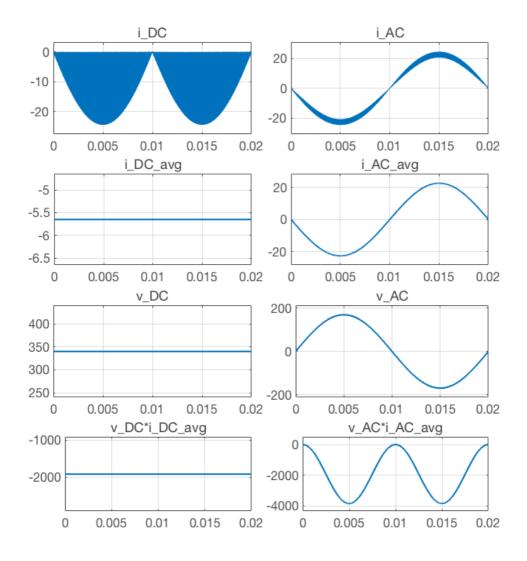

| 5.2               | System-level simulation results at 230Vrms V2G operation                                                                                                                                                                                                                                                                                           | 88                       |

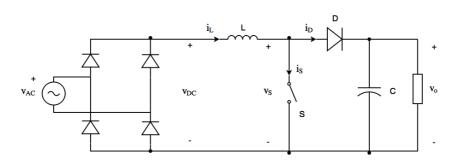

| <b>B</b> .1       | The topology of a conventional boost PFC converter                                                                                                                                                                                                                                                                                                 | 122                      |

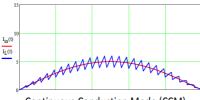

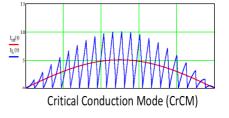

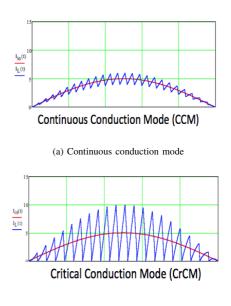

| B.2               | The current waveforms of a boost PFC, as found in [2]                                                                                                                                                                                                                                                                                              | 123                      |

| B.3               | Bridgeless PFC topologies                                                                                                                                                                                                                                                                                                                          | 125                      |

| B.4               | The basic bidirectional PFC topology                                                                                                                                                                                                                                                                                                               | 105                      |

|                   |                                                                                                                                                                                                                                                                                                                                                    | 125                      |

| B.5               | MOSFET switching dynamics with extended reverse conduction                                                                                                                                                                                                                                                                                         | 125                      |

| B.5               | MOSFET switching dynamics with extended reverse conduction                                                                                                                                                                                                                                                                                         | 125<br>127               |

| B.5<br>D.1        | MOSFET switching dynamics with extended reverse conduction                                                                                                                                                                                                                                                                                         |                          |

|                   | MOSFET switching dynamics with extended reverse conduction<br>time, as found in [3]                                                                                                                                                                                                                                                                |                          |

|                   | MOSFET switching dynamics with extended reverse conduction<br>time, as found in [3]                                                                                                                                                                                                                                                                | 127                      |

| D.1               | MOSFET switching dynamics with extended reverse conductiontime, as found in [3].Graphical solution of current filter time constant $T_{fi,i}$ with Modulus optimum.Current controller waveforms over one mains period with Modulus                                                                                                                 | 127                      |

| D.1               | MOSFET switching dynamics with extended reverse conductiontime, as found in [3].Graphical solution of current filter time constant $T_{fi,i}$ with Modulus optimum.Current controller waveforms over one mains period with Modulus optimum.                                                                                                        | 127<br>139               |

| D.1<br>D.2        | MOSFET switching dynamics with extended reverse conduction<br>time, as found in [3].Graphical solution of current filter time constant $T_{fi,i}$ with Modulus<br>optimum.Current controller waveforms over one mains period with Modulus<br>optimum .The complete totem pole converter implemented in Simulink.                                   | 127<br>139<br>140        |

| D.1<br>D.2<br>E.1 | MOSFET switching dynamics with extended reverse conduction<br>time, as found in [3].Graphical solution of current filter time constant $T_{fi,i}$ with Modulus optimum.Current controller waveforms over one mains period with Modulus<br>optimum .The complete totem pole converter implemented in Simulink.The gate drive and totem-pole bridge. | 127<br>139<br>140<br>142 |

- G.1 System-level simulation results at 120Vrms G2V operation. . . . 154

- G.2 System-level simulation results at 120Vrms V2G operation. . . . 155

# Abbreviations

| AC:                                                                                    | Alternating Current                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCM:                                                                                   | Continuous Conduction Mode                                                                                                                                                                                                                                          |

| CrCM:                                                                                  | Critical Conduction Mode                                                                                                                                                                                                                                            |

| DAB:                                                                                   | Dual Active Bridge                                                                                                                                                                                                                                                  |

| DC:                                                                                    | Direct Current                                                                                                                                                                                                                                                      |

| DCM:                                                                                   | Discontinuous Conduction Mode                                                                                                                                                                                                                                       |

| DM:                                                                                    | Direct Mode                                                                                                                                                                                                                                                         |

| DSO:                                                                                   | Distribution System Operator                                                                                                                                                                                                                                        |

| EMI:                                                                                   | Electromagnetic Interference                                                                                                                                                                                                                                        |

| ESR:                                                                                   | Equivalent Series Resistance                                                                                                                                                                                                                                        |

| EV:                                                                                    | Electric Vehicle                                                                                                                                                                                                                                                    |

| G2V:                                                                                   | Grid-to-Vehicle                                                                                                                                                                                                                                                     |

| GaN:                                                                                   | Gallium Nitride                                                                                                                                                                                                                                                     |

| HEMT:                                                                                  | High Electron Mobility Transistor                                                                                                                                                                                                                                   |

|                                                                                        |                                                                                                                                                                                                                                                                     |

| MOSFET:                                                                                | Metal-Oxide-Semiconductor Field-Effect Transistor                                                                                                                                                                                                                   |

| MOSFET:<br>OBC:                                                                        | Metal-Oxide-Semiconductor Field-Effect Transistor<br>On-Board Charger                                                                                                                                                                                               |

|                                                                                        |                                                                                                                                                                                                                                                                     |

| OBC:                                                                                   | On-Board Charger                                                                                                                                                                                                                                                    |

| OBC:<br>PCB:                                                                           | On-Board Charger<br>Printed Circuit Board                                                                                                                                                                                                                           |

| OBC:<br>PCB:<br>PHEV:                                                                  | On-Board Charger<br>Printed Circuit Board<br>Plug-in Hybrid Electric Vehicle                                                                                                                                                                                        |

| OBC:<br>PCB:<br>PHEV:<br>PLL:                                                          | On-Board Charger<br>Printed Circuit Board<br>Plug-in Hybrid Electric Vehicle<br>Phase-Locked Loop                                                                                                                                                                   |

| OBC:<br>PCB:<br>PHEV:<br>PLL:<br>PWM:                                                  | On-Board Charger<br>Printed Circuit Board<br>Plug-in Hybrid Electric Vehicle<br>Phase-Locked Loop<br>Pulse Width Modulation                                                                                                                                         |

| OBC:<br>PCB:<br>PHEV:<br>PLL:<br>PWM:<br>RMS:                                          | On-Board Charger<br>Printed Circuit Board<br>Plug-in Hybrid Electric Vehicle<br>Phase-Locked Loop<br>Pulse Width Modulation<br>Root Mean Square                                                                                                                     |

| OBC:<br>PCB:<br>PHEV:<br>PLL:<br>PWM:<br>RMS:<br>SHBM:                                 | On-Board Charger<br>Printed Circuit Board<br>Plug-in Hybrid Electric Vehicle<br>Phase-Locked Loop<br>Pulse Width Modulation<br>Root Mean Square<br>Single H-Bridge Modulation                                                                                       |

| OBC:<br>PCB:<br>PHEV:<br>PLL:<br>PWM:<br>RMS:<br>SHBM:<br>SiC:                         | On-Board Charger<br>Printed Circuit Board<br>Plug-in Hybrid Electric Vehicle<br>Phase-Locked Loop<br>Pulse Width Modulation<br>Root Mean Square<br>Single H-Bridge Modulation<br>Silicon Carbide                                                                    |

| OBC:<br>PCB:<br>PHEV:<br>PLL:<br>PWM:<br>RMS:<br>SHBM:<br>SiC:<br>THD:                 | On-Board Charger<br>Printed Circuit Board<br>Plug-in Hybrid Electric Vehicle<br>Phase-Locked Loop<br>Pulse Width Modulation<br>Root Mean Square<br>Single H-Bridge Modulation<br>Silicon Carbide<br>Total Harmonic Distortion                                       |

| OBC:<br>PCB:<br>PHEV:<br>PLL:<br>PWM:<br>RMS:<br>SHBM:<br>SiC:<br>THD:<br>V2G:         | On-Board Charger<br>Printed Circuit Board<br>Plug-in Hybrid Electric Vehicle<br>Phase-Locked Loop<br>Pulse Width Modulation<br>Root Mean Square<br>Single H-Bridge Modulation<br>Silicon Carbide<br>Total Harmonic Distortion<br>Vehicle-to-Grid                    |

| OBC:<br>PCB:<br>PHEV:<br>PLL:<br>PWM:<br>RMS:<br>SHBM:<br>SiC:<br>THD:<br>V2G:<br>V2H: | On-Board Charger<br>Printed Circuit Board<br>Plug-in Hybrid Electric Vehicle<br>Phase-Locked Loop<br>Pulse Width Modulation<br>Root Mean Square<br>Single H-Bridge Modulation<br>Silicon Carbide<br>Total Harmonic Distortion<br>Vehicle-to-Grid<br>Vehicle-to-Home |

Chapter 1

## Introduction

This master's thesis is a continuation of a specialization project work performed on the same topic.[4] For that reason, some of the work described in this thesis is based on some of the work performed and described in the specialization project report. The following figures are retrieved from the specialization project report:

- Figure 1.1

- Figure 2.1

- Figure 2.2

- Figure 2.3

Furthermore, the following sections contain large portions of text reproduction from the abovementioned specialization project report:

- Section 1.1

- Section 1.2

- Section 2.1

- Section 2.2

#### 1.1 Motivation

In the quest of securing a more sustainable and renewable electric energy supply in industrialized countries, the implementation of a "smart grid" is picking up pace. The smart grid concept incentivizes more distributed renewable electricity production and increased consumption flexibility for the customer.[5] This development is exemplified by the extensive roll-out of advanced electricity consumption measurement systems for all households in Norway and numerous countries in the European Union, as well as an increasing amount of distributed solar power built in e.g. Germany and California. [6, 7, 8, 9] The first tendency introduces a potential for substantial increase in communication and control at the consumer side of the electric power grid. The second introduces a possible problem of over-production at times of day with high solar irradiation, giving stability issues for the utilities [10]. Combined, these two imply both a possibility and a need for distributed energy storage in the grid, connecting battery storage units at the consumer end to even out the big hourly differences in power production.

One part of this distributed energy storage could be the main batteries of electric vehicles (EVs) and plug-in hybrid electric vehicles (PHEVs) when these are connected to the electricity supply at home or at work. The number of EVs and PHEVs on the roads is increasing, and with that comes a big battery capacity that could be utilized for purposes other than vehicle propulsion. One example of such utilization is using EV batteries as electricity grid stabilizers through vehicle-togrid (V2G) charging. At any time when a big load or generating unit is connected to or disconnected from the grid, there is an immediate power imbalance which causes a change in grid frequency. [11, Chapter 9] To ensure that the frequency stays within the limits of stability, charging or discharging a fleet of cars connected to the grid could cover some of this immediate power imbalance before the slower generators reacts after some seconds or minutes to completely cover the whole imbalance. A potential issue for EVs and PHEVs when enabling bidirectional charging is that the number of cycles increases. Since the battery degrades with every cycle, this would help degrade the battery faster.[12, 13] With this sort of V2G solution, however, utilizing the EV batteries as grid stabilizers, the charging and discharging would be high-power for a short period of time, meaning the battery would not fully charge or discharge. Such solutions are being tested these days, where EV owners are paid for having their batteries available for the utility to draw or inject power whenever needed.[14, 15, 16] Furthermore, if one is to fully exploit the grid-conditioning potential of the bidirectional OBC, it could also be modified to be able to deliver and consume reactive power, serving as a reactive power compensator. [17]

Another possibility is that the battery owners control the power flow themselves, e.g. to store energy when the electricity price is low, say, when the car is connected to a power supply at work. Later in the evening the power could be sold back to the grid at a higher price, earning money from the price difference. Otherwise it could be supplied to the household when the electricity price is high, saving money. Moreover, a discussed concept is vehicle-to-home (V2H) charging, which allows the car battery to serve as an emergency power source, supplying critical loads during power outages.[18] Yet another possibility for exploiting the EV battery energy, is using the battery to provide standard grid-voltage AC power within the car, supplying applications like PC chargers, refrigerators or TVs. Furthermore, when campers today are in need of AC power for various devices, such as lighting, microwaves, small cooktops or again refrigerators, they use a DC-AC inverter connected to a bank of regular 12V car batteries.[19] If an AC power supply is made available also in the exterior of the EV, then this could replace the need for such solutions and even increase the available energy compared to the 12V battery bank.

Figure 1.1: A sketch of the current Valeo Siemens OBC topology [1]

#### 1.2 The Bidirectional On-Board Charger

A key to utilizing PHEV/EV batteries for non-propulsion purposes could be implementing a bidirectional on-board charger (OBC). Being located within the car, the OBC is an important part of any EV; it is the interface between the DC-voltage EV battery and standard AC power outlets, such as the wall socket at home or in the workplace. Since at the moment, vehicles are standing still during large parts of the day, mostly at home or at work, bidirectional charging should be enabled while connected at these locations. To avoid making the owners of house and workplace invest in DC charging stations, the on-board charger could be made with bidirectional power flow capability to enable V2G charging during this time. Moreover, providing solutions like in-car or exterior grid-voltage AC power supplies would require the DC-AC conversion to happen within the car. Enabling bidirectional conduction capability in OBCs could thus indeed be useful, both for V2G charging and the in-car or exterior solution.

One challenge of a standardized OBC solution is that it has to be able to operate efficiently in a universal AC-voltage range (85-265Vrms), since the grid voltage differs between countries and the charger should be able to operate anywhere.[20] Consequently, the input power will also vary, with maximum power ranging roughly between 1.4 kW and 3.5kW, depending on the AC voltage.[21] Another challenge is that since the OBC is located within the car, it has to be small in size and light in weight, to minimize the physical footprint of the charger and extend the range of the vehicle.

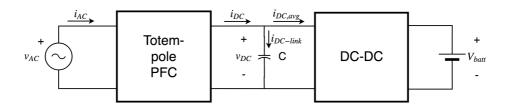

The OBC most often comprises two stages.[22] This is exemplified by the sketch

of the OBC topology used by Valeo Siemens eAutomotive (hereby referred to as Valeo Siemens) reproduced in figure 1.1. Firstly, there is an AC-DC grid interface rectifier with power factor correction (PFC), sinusoidally shaping the drawn AC current in phase with the AC supply mains voltage, to maximize the power factor and remove low-order harmonics, while controlling the voltage ripple at the DC-link capacitor. The switching frequency of the PFC has to be kept high, in order to minimize the size of the inductor and the AC-side filter. At the same time, a higher switching frequency causes higher switching losses, reducing the efficiency. Also, IEC 61000-4-6 defines limits to the emitted EMI in the frequency range of 150kHz to 30MHz, so setting the switching frequency to exceed this lower limit would mean that all of the harmonics needs to be filtered, increasing the size of the filter. Cascaded through the DC-link with this PFC is a DC-DC converter with a high-frequency transformer for galvanic isolation. The DC-DC is controlling the battery-side voltage to be constant, for optimal performance. High switching frequency in the isolated DC-DC converter is decisive to minimize the weight and size of inductors and the transformer, again decreasing the size and weight of the whole OBC. However, in this case higher switching frequency does of course also cause higher switching losses. The efficiency has to be kept high, defined by Valeo Siemens to be above 94%, to maximize the charging speed.[1] The combined maximization of efficiency and power density (kW/dm<sup>3</sup>) is always going to be a trade-off, as explained in [23] with the Pareto front and exemplified with a boost PFC, where at a certain optimal limit, the increasing one is going to require a complementary decrease in the other. This is the compromise of an OBC, where the wish is both high efficiency and high power density. Price is also an important factor, as an OBC would be mass produced and should not lead to a big increase in vehicle cost.

Up until this point, the majority of commercial OBC solutions have been made unidirectional, allowing only grid-to-vehicle (G2V) charging. To make the OBC capable of bidirectional power flow and V2G, there can be no passive diode bridge rectifiers or standalone freewheeling diodes. Some diodes can be removed, implementing more compact solutions, while some have to be replaced by transistors, making the whole charger more complex in terms of control. Every transistor needs its own drive circuit, meaning more transistors can also potentially require a bigger charger volume. For that reason minimizing the number of transistors is something that has to be considered when developing a bidirectional OBC.

With the smart grid still in its birth, the nature of bidirectional charging is still not clear, and different potential modes of operation present different demands for the charger. If operated with the interior power outlet, using it for small TVs, refrigerators or laptop chargers, the charger would most likely be working at a low load for a long period of time. On the other hand, if the vehicle is connected to the grid, working in V2G operation, it could, as mentioned, either be used to sell the battery power to the utility for a good price at times of high demand, or the DSO could use the charger capacity for grid stabilizing purposes. The first case could give an even, high power transfer for hours at a time, while the latter would provoke power transfers at maximum rated power for seconds or minutes. The stress on components and operating efficiency would obviously be quite different in these different cases, and it would be difficult to optimize the charger design for all modes of operation. For that reason, it will be assumed in this evaluation that the charger will during V2G most often be under the control of the distribution system operator (DSO) to regulate stability. Therefore, the relevant PFC topologies will be evaluated considering operation at maximum load for short periods of time. The basis of this decision is that this type of operation has already been tested and considered. The lower efficiency when supplying interior power supply is considered to be of less importance because the drawn power will be lower, and thus the stress and power dissipation will be small.

#### **1.3 The bidirectional PFC**

Having understood the basic composition of an OBC, it is clear that in order to make a bidirectional OBC it is necessary with a bidirectional PFC. However, to design a bidirectional PFC, it is also necessary to understand the basic operation of a unidirectional PFC. A literature review on unidirectional and bidirectional PFCs was performed in the specialization project, and is attached in appendix B. This PFC introduction is based on that analysis. As stated there and above, the PFC is the grid interface of an OBC or another universal power supply, shaping the drawn AC current sinusoidally and in phase with the AC voltage, and controlling the internal DC-link voltage. The conventional boost PFC is structured as in the OBC topology in figure 1.1, consisting of a passive rectifier cascaded with a regular boost converter.[24, ch. 7-4] Here, the switching of the boost transistor is modulated to shape the fundamental inductor current according to the rectified AC voltage seen from the rectifier.

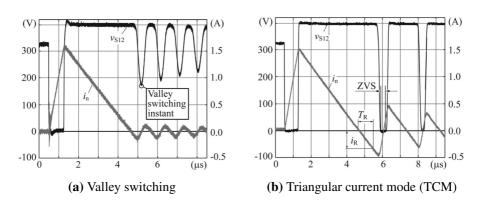

The PFC operates either in continuous conduction mode (CCM), critical conduction mode (CrCM) or discontinuous conduction mode (DCM), all of which are explained in more detail and visualized in appendix B. CCM and CrCM are the most commonly used, where CCM has the advantage of lower current ripple, applying less stress on the semiconductors and inductor and requiring a smaller directmode (DM) ac-side current filter, but at the same time yielding hard switching in both turn-on and turn-off with corresponding higher switching losses. CrCM, on the other hand, enables zero-current switching (ZCS) and possible zero-voltage switching (ZVS) due to the current reaching zero every switching cycle, reducing switching losses but at the same time generating a large current ripple of twice the average current, increasing the stress on the components. For higher power applications it is common to operate in CCM, because the stress on the components would otherwise get too high.[2]

An obvious disadvantage of the boost PFC with regard to bidirectional conduction ability is the the presence of passive diodes both in the rectifier bridge and the freewheeling diode, and so these need to be removed. A first step in that direction is including the operation of the transistor and freewheeling diode into the rectifier bridge, making it a so-called bridgeless PFC, of which there are many variations.[25, 26] This integration has advantages with regards to losses, as the

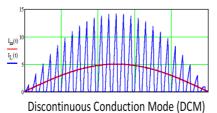

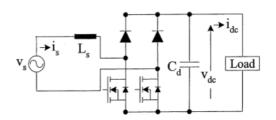

Figure 1.2: The basic bidirectional PFC topology

number of semiconductors in the conduction path is reduced from 3 to 2, reducing especially the conduction losses. Two simple and compact bridgeless topologies with regards to number of semiconductors are the basic bridgeless PFC and the totem-pole PFC, presented in figure B.3 in the appendix. In these topologies, the transistors are "taking turns" operating as boost transistor every other half cycle and remaining turned off (basic bridgeless) or operating as the freewheeling diode (totem-pole) in the other. Out of the two, the basic bridgeless PFC has previously been the preferred topology, with the totem-pole PFC disregarded because of large reverse recovery losses in the MOSFET body diode during CCM operation.[25] On the other hand, a drawback of the basic bridgeless PFC is increased common mode (CM) noise due to the DC-link zero-potential floating with respect to the AC ground. This is explained in more detail in appendix B.

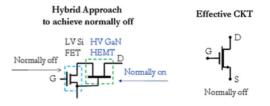

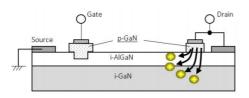

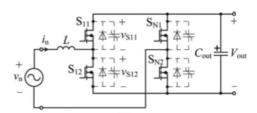

In recent advances, however, the totem-pole PFC has been found increasingly interesting when substituting the rectifier diodes for slow-switching MOSFETs, enabling negative current. That creates a bidirectional PFC topology, the bidirectional totem-pole PFC shown in figure 1.2. For lower-power applications, it has been found that techniques such as triangular current mode (TCM) and CrCM valley switching, enabling low- or zero-voltage switching by discharging the transistor parasiic capacitances through short-term negative currents, can increase efficiency of the totem-pole PFC. This is explained in more detail in appendix B.[3, 27, 28] Interleaving the fast-switching leg, hereby called the totem-leg, i.e. paralleling more than one totem-leg, also improves the efficiency and reduces the stress on the semiconductor components.[27, 29] This is however for lower power levels; at the high power levels of an OBC (3.5kWmax) it is still desirable with CCM operation, to have component stress at a satisfying level. Moreover, given the size restriction of an OBC and that the DM filter does in fact make up one third of the OBC volume, it is beneficial that the lower current ripple in CCM implies a smaller DM filter size.[1]

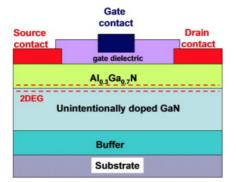

Beneficially, the most recent advances in wide-bandgap power semiconductor devices show that the Gallium Nitride (GaN) High-Electron-Mobility Transistor (HEMT) has been shown to give improvements on the performance of totem-pole PFCs, when used in the fast-switching totem-leg. A literature study has been performed on GaN HEMTs and their application in bidirectional PFCs, and the results are presented in the paper attached in appendix C. The most notable advantage for application in the totem-pole PFC is that, unlike the MOSFET, the GaN HEMT does not contain a reverse body diode, thus solving the problem of reverse recovery losses during CCM operation. Moreover, the GaN HEMTs show superior conduction and switching characteristics all over, due to the combination of high breakdown field and the low-resistivity 2DEG layer. This is explained in more detail in appendix C. In [30] is presented a 1.5kW, 65kHz CCM-operated totem-pole PFC, showcasing an efficiency of 99%. Moreover, it is found through the literature study that currently most 1-phase bidirectional two-stage OBCs proposed in the scientific literature are using the bidirectional totem-pole PFC shown in figure 2.1 [31, 32, 33]. In fact, most proposed 1-phase bidirectional PFCs overall are using the bidirectional totem-pole topology [34, 35]. This indicates that it is possible to design an efficient 3.5kW CCM-operated bidirectional totem-pole PFC. For that reason, the bidirectional totem-pole PFC will be the topology of choice going forward in this master's thesis.

#### 1.4 Scope of work

Although a few cases of the bidirectional totem-pole PFC has appeared in the scientific literature, as presented in the previous section, the author has not come across any verification of the nature its fundamental bidirectional operation. For that reason, the main objective of this master's thesis is to fill that hole, by deriving and developing a fundamental simulation model describing the bidirectional totem-pole PFC and its bidirectional operation. This simulation model will be implemented in Simulink. To verify the use of the bidirectional totem-pole PFC in a bidirectional OBC, the simulation model will be implemented with off-the-shelf components and a control system meeting some demands of a bidirectional OBC and PFC, shown in tables 1.1 and 1.2. The thesis is written in cooperation with Valeo Siemens eAutomotive and is intended to be a building block for further work on a bidirectional OBC, verifying or dismissing the bidirectional totem-pole PFC as a technology to take further. In that sense, describing the currents, voltages and losses in the basic operation of the topology will be important.

The topology will be investigated using MOSFETs and GaN HEMTs as the transistors, disregarding possible solutions with IGBTs. Furthermore, the PFC efficiency will be optimized for a standard AC voltage of 230Vrms, not designing from the efficiency at 120Vrms. The design will be aiming to approach the current Valeo Siemens PFC designs with regards to switching frequency and efficiency, to use similar components and compare performance. As for the control system and gate logic design, an emphasis will be put on making a solution which can be adapted to existing unidirectional boost PFC control systems and gate drives, to create a flexible solution. For the PFC control average current mode control, whith cascaded current and voltage loops containing PI controllers with Symmetrical optimum tuning.

In **chapter 2**, the basic operation of the bidirectional totem-pole PFC is described, deriving expressions for the currents and losses in the boost inductor, DC-link capacitor and transistors.

**Chapter 3** will cover the design and dimensioning of the components, in particular the boost inductor, transistors and DC-link capacitor.

In chapter 4 the bidirectional totem-pole control will be developed, deriving the

| Parameter               | Value             |  |  |

|-------------------------|-------------------|--|--|

| G2V                     |                   |  |  |

| Output DC voltage range | 200Vdc - 1000Vdc  |  |  |

| Max. output DC current  | 12 Adc            |  |  |

| Input AC voltage range  | 85Vrms - 275Vrms  |  |  |

| Max. input AC current   | 16Arms            |  |  |

| Max. input frequency    | 45Hz - 65Hz       |  |  |

| Max. power              | 3.5kW             |  |  |

| Efficiency              | > 94%             |  |  |

| Max. apparent power     | 3680VA            |  |  |

| Lifetime                | 10 000 hours      |  |  |

| V2G                     |                   |  |  |

| Input DC voltage range  | 200Vdc - 1000Vdc  |  |  |

| Max. input DC current   | 12 Adc            |  |  |

| Output AC voltage range | 100Vrms - 250Vrms |  |  |

| Max. output AC current  | 16Arms            |  |  |

| Max. output frequency   | 45Hz - 65Hz       |  |  |

| Max. power              | 3.5kW             |  |  |

| Efficiency              | > 91%             |  |  |

| Max. apparent power     | 3680VA            |  |  |

| THD                     | < 3%              |  |  |

| Lifetime (uncertain)    | 10 000 hours      |  |  |

Table 1.1: Demands and specifications for the bidirectional universal OBC, from [1]

gate drive and control system logic and tuning controllers and verifying through simulations.

Chapter 5 shows the results of some system level simulations.

**Chapter 6** will discuss the design feasibility by evaluating simulation model shortcomings and comparing performance with existing solutions.

Table 1.2: PFC-specific demands and specifications

| Parameter                    | Value |

|------------------------------|-------|

| Efficiency G2V               | >98%  |

| Efficiency V2G               | >97%  |

| Min. DC-link voltage         | 340V  |

| Max. DC-link voltage ripple  | 20V   |

| Max. inductor current ripple | 20%   |

# Basic operation of the bidirectional totem-pole PFC

Based on the reasoning in the introduction, the bidirectional totem-pole PFC was chosen as the most promising bidirectional PFC topology, and so now the operation of this topology must be explained in more detail. It is acknowledged that in order to comply with the current ripple restrictions of 20% (table 1.2), it is necessary to run the bidirectional totem-pole PFC in CCM. This section will consider its basic CCM operation, covering V2G discharging and G2V charging. Moreover, current and voltage waveforms will be derived and portrayed for the main components of the converter, including the boost inductor, the transistors and the DC-

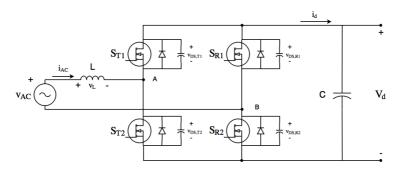

Figure 2.1: The basic bidirectional totem-pole topology

link capacitor. Expressions will be developed for RMS currents and conduction and switching losses for these components. The relevant bidirectional totem-pole topology is shown in figure 2.1, and in the following all variables and parameters will be referred to the notation in this figure.

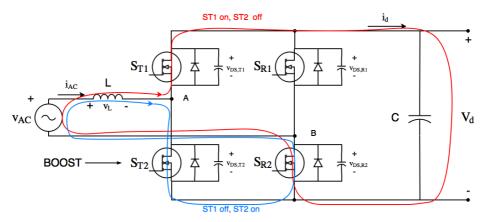

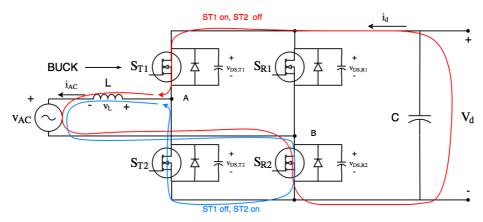

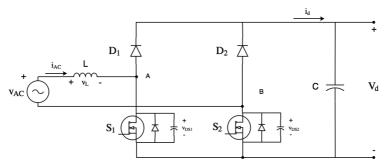

#### 2.1 G2V operation

In G2V operation, with power flow from AC source to DC link, the totem pole is operated as a boost converter with PWM switching, to shape the fundamental waveform of the AC current  $i_{AC}$  like a sine in phase with the AC voltage  $v_{AC}$ . [24] The operation is sketched in figure 2.2. During the positive mains half cycle, the lower totem-leg switch,  $S_{T2}$  is operated with boost PWM switching (figure 2.2a), while the upper totem-leg switch  $S_{T1}$  is operated complementarily; when  $S_{T1}$  is on  $S_{T2}$  is off, and vice versa.  $S_{R2}$  is always on during the positive half cycle. During the negative mains voltage half cycle,  $S_{T1}$  is operated as a boost,  $S_{T2}$  is complementary and  $S_{R1}$  is conducting. The AC current is governed by (2.1), and from that controlled by the average  $v_{AB}$ , which is again controlled by the timevarying duty cycle, to be shaped like in figure B.2.

$$v_L = v_{AC} - v_{AB} = L \frac{di_{AC}}{dt}$$

(2.1)

(a) Mains voltage positive half cycle

(b) Mains voltage negative half cycle

Figure 2.2: The G2V operation of the bidirectional totem-pole PFC.

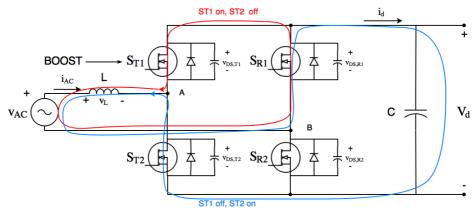

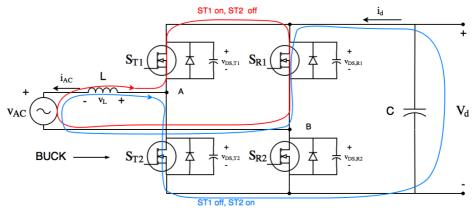

#### 2.2 V2G operation

Conversely, with power flow from DC link to AC side in V2G operation, the totempole is operated as a buck converter, stepping down the voltage from the DC-link to AC-side [24]. The operation is sketched in figure 2.3. In this case, during the positive mains voltage half cycle,  $S_{T1}$  is operated with buck PWM switching,  $S_{T2}$  is complementary and  $S_{R2}$  is conducting, as indicated in figure 2.3a. During negative half cycle,  $S_{T2}$  is buck PWM controlled,  $S_{T1}$  is complementary and  $S_{R1}$ is conducting, as indicated in figure 2.3b. With AC current defined positive from DC-side to AC-side the inductor voltage changes polarity, so that the current is governed by (2.2).

$$v_L = v_{AB} - v_{AC} = L \frac{di_{AC}}{dt}$$

(2.2)

Still, this means the current is controlled by the time-varying duty cycle of the buck-operated switch, controlling  $v_{AB}$ , as it is in the boost operation.

(a) Mains voltage positive half cycle

(b) Mains voltage negative half cycle

Figure 2.3: The V2G operation of the bidirectional totem-pole PFC.

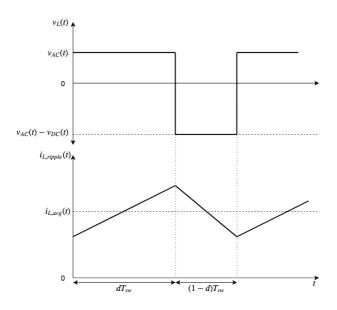

Figure 2.4: CCM  $i_L$  and  $v_L$  ripple over one switching period

#### 2.3 Boost inductor

For this section, when evaluating inductor currents,  $i_L$  and  $I_L$  will be referring to the instantaneous and RMS currents through the inductors, whereas  $I_{AC}$  will be referring to the RMS AC current drawn from the grid.

#### 2.3.1 Current waveforms and ripple

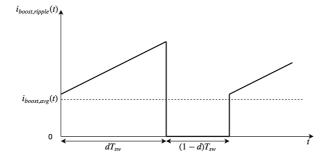

As explained in section 2.1, the bidirectional totem-pole operates as a boost converter during G2V charging. Thus, the inductor current and voltage waveforms over one totem-leg switching period during the positive mains half cycle will be as shown in figure 2.4.[24, ch. 7-4]. During negative half cycle the ripple will be exactly mirrored over the time axis.

As can be found combining figure 2.4 and (2.1), the inductor current ripple at any given point in the AC mains cycle can be given as

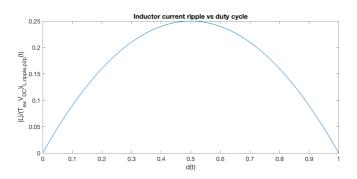

Figure 2.5: Boost CCM  $\Delta i_L$  vs duty cycle

$$\Delta i_L(t) = \frac{1}{L} \int_{t=0}^{d \cdot T_{sw}} v_{AC}(t) dt , \qquad (2.3)$$

where *d* is the duty cycle at this point. Since  $f_{sw} \gg f_{AC}$ ,  $v_{AC}(t)$  and can be considered constant over one switching period, giving from (2.3):

$$\Delta i_L(t) = \frac{T_{sw}}{L} d(t) v_{AC}(t) \tag{2.4}$$

Finally using the boost converter voltage ratio from [24, ch. 7-4],

$$\frac{v_{DC}(t)}{v_{AC}(t)} = \frac{1}{1 - d(t)} , \qquad (2.5)$$

(2.4) can be rewritten as follows:

$$\Delta i_L(t) = \frac{T_{sw} v_{DC}(t)}{L} d(t) (1 - d(t)) .$$

(2.6)

This equation (2.6) is solved graphically in figure 2.5, assuming  $v_{DC}(t)$  is approximately constant and equal to  $v_{DC}(t) \approx V_{DC}$ . Figure 2.5 shows that  $\Delta i_L(d)$  has a parabolic shape, peaking at d = 0.5.

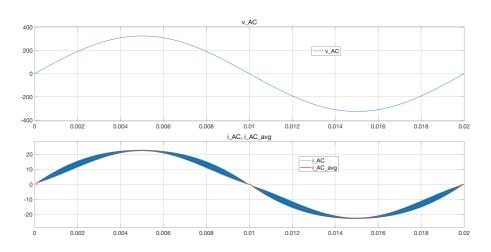

For illustration, the current through the inductor,  $i_{AC}$ , during G2V over a whole mains cycle is shown in figure 2.6. The average inductor current and the AC mains voltage are shown as well for comparison, and they show that the fundamental AC current is more or less in phase with the AC voltage.

Figure 2.6: The inductor current compared to the AC mains voltage throughout one mains cycle.

#### 2.3.2 Conduction losses

The inductor conduction losses mainly comprises two parts: copper losses, which are resistive losses from the resistance in the inductor windings, and core losses, who are mostly due to eddy current losses end hystheresis losses in the magnetic core.[24, ch. 30-1] The hysteresis losses are highly dependent on the core material, but is always given on the following form:

$$P_{L,hyst} = k \cdot f^a \cdot B_{AC}^q , \qquad (2.7)$$

where k, a and q are material dependent constants, f is the magnetic flux oscillation frequency and  $B_{AC}$  is the AC magnetic flux density.[24, ch. 30-1-2] Eddy current losses are also core dependent, given on the form:

$$P_{L,eddy} = \frac{q^2 \omega^2 (B_{AC} + B_{avg})^2}{24\rho_{core}} , \qquad (2.8)$$

where  $\omega$  is the angular frequency of the flux oscillations,  $B_{avg}$  is the flux density constant flux offset and  $\rho_{core}$  is the charge density of the core material.[24, ch. 30-1-4] As mentioned, the copper losses are resistive losses due to the winding resistance, and so they are given by:

$$P_{L,copper} = R_{L,copper} I_L^2 , \qquad (2.9)$$

where  $I_L$  is the RMS inductor current and  $R_{L,copper}$  is the inductor winding resistance. Acknowledging that the core flux density  $B \propto I$  by Ampere's law, as well as that q often takes a value close to 2,[24, ch. 30-1-2] it can be seen from (2.7), (2.8) and (2.9) that all of these losses have a nearly proportional relation to to  $I_L^2$ . Thus, a simplification will be made going forward, merging all of these losses into one equivalent resistance at the given frequency, called  $R_L$ , giving the following loss equation:

$$P_L \approx R_L I_L^2 \,. \tag{2.10}$$

As mentioned, the inductor current ripple must be less than 20%, and for that reason it is assumed that

$$I_L \approx I_{AC} , \qquad (2.11)$$

meaning (2.9) can be rewritten:

$$P_L \approx R_L I_{AC}^2 . \tag{2.12}$$

Figure 2.7: The rectifier-leg transistor drain-source currents throughout one mains cycle during G2V.

# 2.4 Transistors

## 2.4.1 Current waveforms and ripple

#### **Rectifier-leg switches**

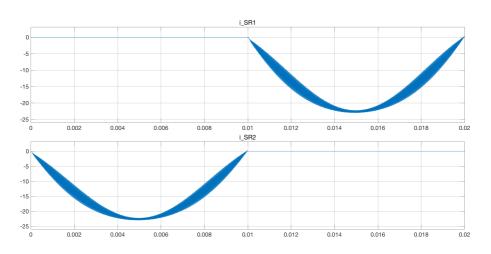

The currents through the transistors will be quite different for the two legs of the totem pole. Simplest are the rectifier legs, who conduct for a whole mains half-period each, as shown in sections 2.1 and 2.2.  $S_{R1}$  conducts during negative mains half cycle,  $S_{R2}$  conducts during the positive. Therefore, the current ripple during the conducting half-cycle of these rectifier-leg transistors will be shaped like the inductor current ripple in figure 2.4.

Figure 2.7 illustrates the drain-source currents of the rectifier-leg transistors throughout the mains cycle during G2V charging. The drain-source currents are evidently always negative during G2V, confirming the operation description from section 2.1. During V2G the currents will, oppositely, always be positive.

(a) The current through the boost switch at an arbitrary point in the AC mains cycle.

(**b**) The totem-pole output current to the DC link at an arbitrary point in the AC mains cycle.

**Figure 2.8:** The current ripple of the totem-leg switches during positive mains half cycle in G2V operation.

#### **Totem-leg switches**

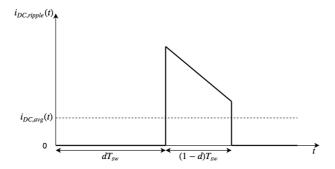

The current of the two totem-pole transistors depend highly on the duty cycle *d* of each of the switches, since the transistors obviously only conducts while they are on. The modulation is different for the different transistors in each mains half-cycle, as mentioned in sections 2.1 and 2.2, and so the switching-period current waveform of each of the transistors will be different as well. To simplify the analysis, switching-period current waveforms will here be shown for the *boost switch* and the *boost complementary switch* during *G2V*. During *V2G*, the boost complementary switch which will be equivalent to the *buck switch*, with the same current waveform, and the boost switch will be equivalent to the *buck complementary switch*.

Deriving the switching-period current waveforms from figure 2.4, the boost switch conducts during  $dT_{sw}$ , whereas the boost complementary switch conducts during  $(1 - d)T_{sw}$ . Hence, the switching-period current waveforms through the boost switch and the boost complementary switch for an arbitrary duty cycle *d* can be given as in figures 2.8a and 2.8b, respectively. The current through the boost complementary switch is the current that is passed from the totem-pole to the DC-link, and is therefore denoted  $i_{DC}(t)$ .

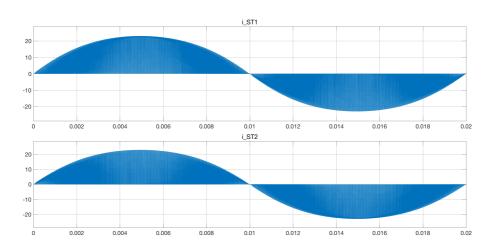

Throughout one mains cycle in G2V operation, the currents of the two switches will be shaped as in figure 2.9. As explained in section 2.1,  $S_{T2}$  is the boost switch during positive half-cycle, having the switching-period current waveform drawn in figure 2.8a, whereas during negative half-cycle it is the complementary switch, having the switching-period current waveform drawn in figure 2.8b, with negative polarity.  $S_{T1}$  is exactly opposite. During V2G, the currents have the same shape, but with opposite polarity.

Figure 2.9: The totem-leg transistor drain-source currents throughout one mains cycle during G2V.

#### 2.4.2 Conduction losses

In the following it will be assumed that *MOSFETs* or *GaN HEMTs* are chosen for both the rectifier leg and the totem leg. In the case of other relevant transistor technologies, such as IGBTs, the conduction losses would not be resistive, but caused by forward voltage and average current through the transistors.

#### **Rectifier-leg switches**

To evaluate the conduction losses in the transistors, expressions have to be developed describing the RMS currents through the transistors. For the rectifier switches  $S_{R1}$  and  $S_{R2}$ , this is trivial, since they will be conducting for half an AC mains period each:

$$I_{SR}^{2} = \frac{1}{2\pi} \int_{\omega t=0}^{\pi} i_{L}^{2}(\omega t) \, d\omega t = \frac{1}{2} I_{L}^{2} \,.$$

(2.13)

Implementing (2.11) in (2.13), we get for each of the rectifier switches:

$$I_{SR} = \frac{1}{\sqrt{2}} I_{AC}.$$

(2.14)

#### **Totem-leg switches**

In the case of the fast-switching totem-leg switches,  $S_{T1}$  and  $S_{T2}$ , the RMS current through each of the transistors depends on the time-varying duty cycle  $d_{ST}$  of the relevant transistor. The discrete-form equation for the RMS current through one of the totem-leg switches can be given as follows:

$$I_{ST}^{2} = \frac{1}{2\pi} \sum_{k=0}^{f_{SW}/f_{AC}} d_{ST}[k] i_{L}^{2}[k] , \qquad (2.15)$$

where k represents one single switching period at one point in the AC mains cycle,  $f_{sw}$  is the switching frequency,  $f_{AC}$  is the AC mains frequency and d in this case is the duty cycle of any of the two totem-leg switches. Taking into account that  $f_{sw}$  will be chosen so that  $f_{sw} \gg f_{AC}$ , (2.15) can be approximated as a continuous integral over the whole AC mains cycle:

$$I_{ST}^{2} = \frac{1}{2\pi} \int_{\omega t=0}^{2\pi} d(\omega t) i_{L}^{2}(\omega t) \, d\omega t \; . \tag{2.16}$$

Moreover, since  $S_{T1}$  and  $S_{T2}$  are switched complementarily, (2.16) can be simplified. Dead time required between turn-off of one transistor and turn-on of the other to avoid cross-conduction is neglected, since it is assumed very small.[24] The complementary switching means one of the switches are always conducting, and as explained in sections 2.1 and 2.2, the roles of the two switches interchange every half cycle. Thus, based on the current waveforms for the boost and complementary switch in figures 2.8a and 2.8b, (2.16) can be rewritten as follows:

$$I_{ST}^{2} = \frac{1}{2\pi} \left( \int_{\omega t=0}^{\pi} d(\omega t) i_{L}^{2}(\omega t) \, d\omega t + \int_{\omega t=0}^{\pi} \left( 1 - d(\omega t) \right) i_{L}^{2}(\omega t) \, d\omega t \right)$$

(2.17)

$$=\frac{1}{2\pi}\int_{\omega t=0}^{\pi} \left(d(\omega t)+1-d(\omega t)\right)i_{L}^{2}(\omega t)\,d\omega t \tag{2.18}$$

$$=\frac{1}{2\pi}\int_{\omega t=0}^{\pi}i_{L}^{2}(\omega t)\,d\omega t \tag{2.19}$$

$$=\frac{1}{2}I_L^2\tag{2.20}$$

This derivation from (2.17) to (2.20) shows that due to the symmetry of the topology, both of the totem-leg switches are conducting in total in half of the AC-mains voltage cycle. This gives the same RMS current in both of the totem-leg switches as in the rectifier-leg switches:

$$I_{ST} = \frac{1}{\sqrt{2}} I_{AC}$$

(2.21)

Based on the derived RMS current expressions in (2.14) and (2.21), the conduction losses in each of the transistors can be determined as follows:

$$P_{cond} = \frac{1}{2} I_{AC}^2 R_{DS,on}.$$

(2.22)

#### 2.4.3 Switching losses

Now that the transistor conduction loss expressions have been established, the next thing needed to estimate the transistor losses is an estimation of the switching losses. As with the derivation of the conduction losses, the following will assume MOSFETs or GaN HEMTs as the chosen transistor technology.

Based on the MOSFET switching characteristics described in [24, ch. 22-5-2], the switching waveforms can be approximated as in figure 2.10. As appears in [36], the switching characteristics of a GaN HEMT can be estimated in a similar way, so figure 2.10 and the following derivations are hence considered valid for both transistor types. The switching energy  $E_{sw}$  is given as  $\int v_{DS}(t) \cdot i_D(t) dt$  over the switching transient duration, giving the following equation based on figure 2.10:

$$E_{sw}[k] = E_{on}[k] + E_{off}[k] = \frac{1}{2}(T_{r,i} + T_{f,v} + T_{r,v} + T_{f,i})v_{DC}[k]i_{L}[k], \qquad (2.23)$$

where  $v_{DC}$  and  $i_L$  are, respectively, the average DC voltage and inductor current over the switching period.

In order to find a simple expression for the switching power  $P_{sw}$ , (2.23) is averaged over half an AC mains cycle. Current and voltage rise and fall times are obviously dependent on  $v_{DC}(t)$  and  $i_L(t)$ , making it somewhat more complex. However,

(b) Turn-off

Figure 2.10: Approximation of the switching characteristics of a MOSFET.

$v_{DC}(t)$  will have a ripple of less than 20%,(table 1.2) meaning it can be assumed to be approximately constant and equal to  $V_{DC}$ , again giving approximately constant  $T_{r,v}$  and  $T_{f_v}$ . Since we are mostly interested in a rough estimate of the losses for transistor dimensioning purposes, it is assumed for simplicity going forward that also the current rise and fall times do not vary much with time. To clean up the expression, we set total switching commutation time  $T_{sw,comm} = T_{r,i} + T_{f,v} + T_{r,v} + T_{f,i}$ . An expression for the average switching energy is obtained:

$$E_{sw,avg} = \frac{1}{\pi} \int_{\omega t=0}^{\pi} E_{sw}(\omega t) d\omega t = \frac{1}{2} T_{sw,comm} V_{DC} I_{AC,avg} , \qquad (2.24)$$

where the average AC current over one half period,  $I_{AC,avg}$ , is given as

$$I_{AC,avg} = \frac{1}{\pi} \int_{\omega t=0}^{\pi} i_{AC,avg}(\omega t) d\omega t = \frac{2\sqrt{2}}{\pi} I_{AC} .$$

(2.25)

This gives approximate transistor switching power loss:

$$P_{sw} = f_{sw} * E_{sw,avg} = \frac{f_{sw}}{2} T_{sw,comm} V_{DC} I_{AC,avg} . \qquad (2.26)$$

Figure 2.11: Illustration of he DC-link capacitor, voltage and currents

## 2.5 DC-link