# Modeling Communication on Multi-GPU Systems

Daniele Spampinato

Master of Science in Computer Science Submission date: July 2009 Supervisor: Anne Cathrine Elster, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

# **Problem Description**

This project evaluates how multiple Graphical Processing Units (GPUs) may best be utilized to offload computations in HPC environments. In particular, we look at models for heterogeneous systems and develop a PDE SOR solver that is used to analyze communication patterns when doing boarder exchanges on multiple GPUs. Our implementation take advantage of the CUDA environment. Testing will be done on the HPC-LAB's new NVIDIA Tesla S1070 and/or other appropriate systems.

Assignment given: 25. January 2009 Supervisor: Anne Cathrine Elster, IDI

Master Thesis

# Modeling Communication on Multi-GPU Systems

Daniele Giuseppe Spampinato daniele.spampinato@gmail.com

Department of Computer and Information Science Norwegian University of Science and Technology, Trondheim (Norway)

July 2009

**Supervisor** Dr. Anne C. Elster

# Preface

Many people, directly or indirectly, influenced the production of this master thesis, and I would like to extend to them my grateful appreciation for their help and support.

I would like to thank my supervisor, Dr. Anne C. Elster, for introducing me into the world of High Performance Computing, and for proposing, together with Thorvald Natvig, the target of this work. I also feel enormously thankful to her for all the great experiences that I had the opportunity to take part in, such as Supercomputing '08 (Austin, TX), IPDPS '09 (Rome), and the IBM EMEA BSRE '09 (Cracow). A special thanks to Jan C. Meyer for his precious suggestions and patience. Our endless, ontological discussions were for me source of great inspiration. And irreplaceable was the entire HPC-Lab at IDI: Rune Hovland, Rune E. Jensen, smund Herikstad, Daniel Haugen, Olav Fagerlund, Eirik Ola Aknes, Owe Johansen, Henrik Hesland, Safrudin Mahic, smund Eldhuset, and Robin Eidissen. I always found in them a valuable help and lots of good ideas. I wish to thank NVIDIA for providing several GPUs to Dr. Anne C. Elster and her HPC-lab through her membership in the NVIDIAs professor partnership program.

This master thesis signs for me the end of the T.I.M.E. project in Norway. It has been the longest and most exciting adventure of my entire life. Impossible to recall all the significant moments and make a complete list of acknowledgments within the space of one page.

My gratitude goes first and foremost to my parents, Armando Spampinato and Giuseppina Rota. They made all this things happen, always supporting and trusting me, no matter what. To them, who dedicate their life to their family, I would like to dedicate this work.

Even though far from home, I have never felt far from all my dears at home, starting from my sister Beatrice, and all my closest friends, that I cannot wait to hug again.

Living in Trondheim was an experience that I will never forget. The Moholt Family has a special place in my heart: Maru, Seu Lki Cecilia, Alejandra, Maria, Ole, Jon, Stefano, Seth, Eva & Luka, Daniele, Francesco "Friz", and Thomas. Together with them, there is a long list of people that I had the fortune to meet during these two amazing years, starting from the fantastic flatmates in MA 28-1: Emily, Kelsy, Gwyneth, Ravan, Elizaveta, Lars, Trine Lise, Helena, to all the other people I had a great time with: Heather, Matt, Anna, Andrea, Vegar, Fabian, Raphael, Sendy, Charlotte, Piotr, Thomas, p. Dominique, p. Etienne, p. Al, Huy, Maria, Karoline, Benedikt, Pia, Sara, Peter, Piotr, Matthias, Charlie, Sabine, Nikolaas, Francesco, Leiv, and many many others: Thanks!

In Italy we have a nice proverb that states:

"Chi trova un amico trova un tesoro."

One who finds a friend, finds a treasure. It must be true. Never felt richer so far.

Dealing with two different countries one must expect a "certain degree" of bureaucracy. I also wish to thank here the two Offices of International Relations for helping me in struggling with that, especially Francesca Fogal, that from Milan has been able to survive my countless requests.

Trondheim, July 16, 2009

Daniele Giuseppe Spampinato

# Abstract

Coupling commodity CPUs and modern GPUs give you heterogeneous systems that are cheap, high-performance with incredible FLOPS counts. Recent evolution of GPGPU models and technologies make these systems even more appealing as compute devices for a range of HPC applications including image processing, seismic processing and other physical modeling, as well as linear programming applications. In fact, graphics vendor such as NVIDIA and AMD are now targeting HPC with some of their products. Due to the power and frequency walls, the trend is now to use multiple GPUs on a given system, much like you will find multiple cores on CPU-based systems. However, increasing the hierarchy of resource wides the spectrum of factors that may impact on the performance of the system.

The lack of good models for GPU-based, heterogeneous systems also makes it harder to understand which factors impact performance the most. The goal of this thesis is to analyze such factors by investigating and benchmarking NVIDIA's multi-GPU solution, their recent NVIDIA Tesla S1070 Computing System. This system combines four T10 GPUs making available up to 4 TFLOPS of computational power. Based on a comparative study of fundamental parallel computing models and on the specific heterogeneous features exposed by the system, we define a test space for performance analysis. As a case study, we develop a red-black, SOR PDE solver for Laplace equations with Dirichlet boundaries, well known for requiring constant communication in order to exchange neighboring data. To aid both design and analysis, we propose a model for multi-GPU systems targeting communication between the several GPUs.

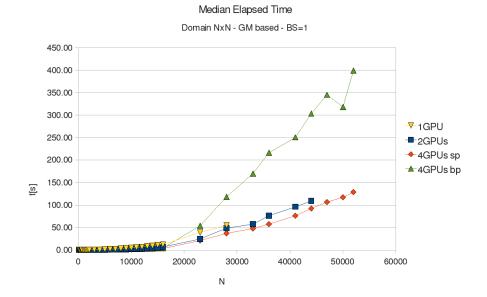

The main variables exposed by the benchmark application are: domain size and shape, kind of data partitioning, number of GPUs, width of the borders to exchange, kernels to use, and kind of synchronization between the GPU contexts. Among other results, the framework is able to point out the most critical bounds of the S1070 system when dealing with applications like the one in our case study. We show that the multi-GPU system greatly benefits from using all its four GPUs on very large data volumes. Our results show the four GPUs almost four times faster than a single GPU, and twice as fast as two. Our analysis outcomes also allow us to refine our static communication model, enriching it with regression-based predictions.

# Contents

| Pı            | reface                          | e                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | i                                                                                                |

|---------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| A             | bstra                           | $\mathbf{ct}$                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | iii                                                                                              |

| Ta            | Table of Contents               |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                  |

| $\mathbf{Li}$ | st of                           | Figure                                                                                                            | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ix                                                                                               |

| $\mathbf{Li}$ | st of                           | Table                                                                                                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | xi                                                                                               |

| 1             | <b>Intr</b><br>1.1<br>1.2       |                                                                                                                   | <b>ion</b><br>9 Goal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                  |

| 2             | Mul<br>2.1<br>2.2<br>2.3<br>2.4 | The N<br>2.1.1<br>2.1.2<br>2.1.3<br>The C<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>The N | U Computing         IVIDIA Tesla Computing Architecture         Streaming Multiprocessors         GPU Memories         The SIMT Paradigm         The SIMT Paradigm         CUDA Programming Model         A Heterogeneous Programming Model         The NVIDIA CUDA Software Stack         Threads Organization         Memory Organization         Mapping to the Tesla Architecture         Compute Capability         Floating-Point Support         VIDIA Tesla S1070 Computing System         amming Multiple GPUs | $egin{array}{cccc} 6 & 6 & 7 & 7 & 9 & 9 & 10 & 11 & 12 & 13 & 13 & 13 & 14 & 14 & 14 & 14 & 14$ |

| 3             |                                 | allel C<br>Paralle<br>3.1.1<br>3.1.2<br>3.1.3                                                                     | Computational Models         el Models         Shared Memory Multiprocessor         Message-Passing Multicomputers         SMP Cluster Computing         rities between SMP Clusters and multi-GPU Systems         Single GPUs as Shared Memory Nodes                                                                                                                                                                                                                                                                   | 17<br>17<br>17<br>20<br>22<br>23                                                                 |

|               |                                 | 3.2.2                                                                                                             | Inter-GPU Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30                                                                                               |

| 4        | Case Study: PDEs |                                                                                                                                          |    |

|----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------|----|

|          | 4.1              | PDE Problems                                                                                                                             | 33 |

|          |                  | 4.1.1 Elliptic PDEs: the Laplace Equation                                                                                                | 34 |

|          | 4.2              | Iterative Methods                                                                                                                        | 37 |

|          |                  | 4.2.1 Jacobi Method                                                                                                                      | 37 |

|          |                  | 4.2.2 Gauss-Seidel Method                                                                                                                | 37 |

|          |                  | 4.2.3 Successive Overrelaxation Method                                                                                                   | 38 |

|          |                  | 4.2.4 Red-Black Successive Overrelaxation                                                                                                | 38 |

| <b>5</b> | Ben              | chmark Application                                                                                                                       | 41 |

|          | 5.1              | Benchmarking Overall Perspective                                                                                                         | 41 |

|          | 5.2              | Exchanging Larger Borders                                                                                                                | 43 |

|          | 5.3              | Data Partitioning                                                                                                                        | 44 |

|          |                  | 5.3.1 Data Storage                                                                                                                       | 46 |

|          | 5.4              | Core Computation                                                                                                                         | 46 |

|          |                  | 5.4.1 Host Computation                                                                                                                   | 47 |

|          |                  | 5.4.2 Device Computation                                                                                                                 | 47 |

|          | 5.5              | Communication and Synchronization                                                                                                        |    |

|          | 0.0              | 5.5.1 Impact of Data Partitioning on Communication                                                                                       |    |

| 6        | Bon              | chmarks vs. Model Estimates                                                                                                              | 61 |

| U        | 6.1              | Experimental Environment                                                                                                                 | 61 |

|          | 6.2              | -                                                                                                                                        |    |

|          | 0.2              | Methodology                                                                                                                              | 63 |

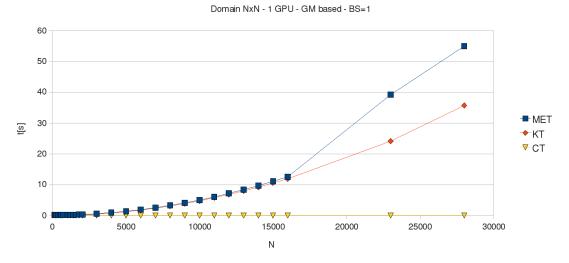

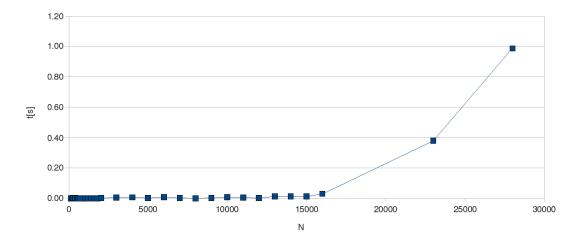

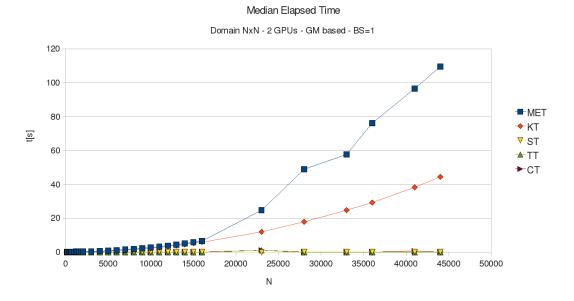

|          |                  | 6.2.1 Collected Output Values                                                                                                            |    |

|          |                  | $6.2.2  \text{Timing} \dots \dots$ | 64 |

|          | 0.0              | 6.2.3 Helper Tools                                                                                                                       | 64 |

|          | 6.3              | Results Discussion                                                                                                                       | 65 |

|          |                  | 6.3.1 Domain Size and Data Partitioning                                                                                                  |    |

|          |                  | 6.3.2 Domain Shape                                                                                                                       |    |

|          |                  | 6.3.3 Global Memory Vs. Texture Based Kernels                                                                                            |    |

|          |                  | 6.3.4 Number of GPUs                                                                                                                     | 71 |

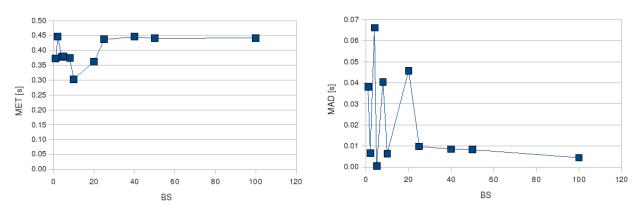

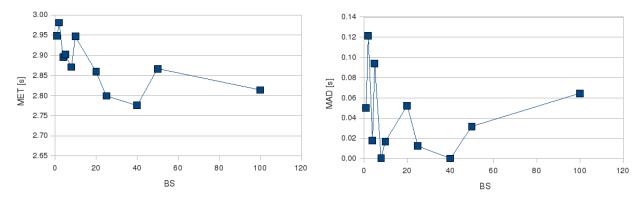

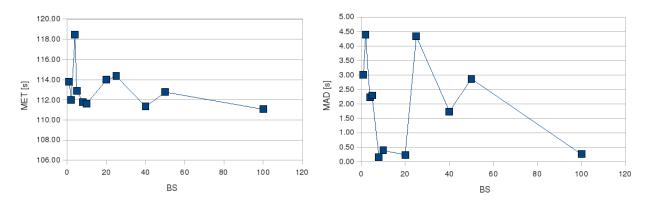

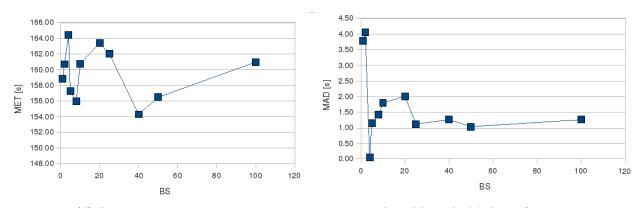

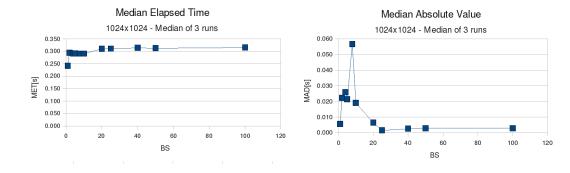

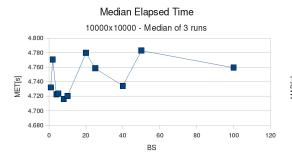

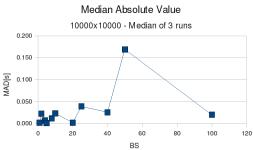

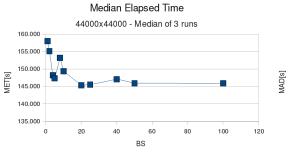

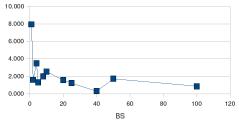

|          |                  | 6.3.5 Border Size                                                                                                                        | 73 |

|          |                  | 6.3.6 Threads Synchronization                                                                                                            | 74 |

| 7        | Cor              | clusions and Future Work                                                                                                                 | 77 |

|          | 7.1              | Future Work                                                                                                                              | 79 |

|          |                  | 7.1.1 An Improved Standard Framework for Benchmarking                                                                                    | 79 |

|          |                  | 7.1.2 A Fast Communication Framework for GPUs                                                                                            | 80 |

|          |                  | 7.1.3 Large Scale Perspective                                                                                                            | 80 |

|          |                  | 7.1.4 Green Computing                                                                                                                    | 80 |

| Bi       | bliog            | graphy                                                                                                                                   | 81 |

| GI       | lossa            | rv                                                                                                                                       | 83 |

|          |                  |                                                                                                                                          |    |

| Α        | Spe              | cifications for Compute Capability 1.3                                                                                                   | 85 |

\_\_\_\_\_

| В            | Coc  | le Samples                                               | 87    |

|--------------|------|----------------------------------------------------------|-------|

|              | B.1  | Benchmark Entry Point                                    | . 87  |

|              | B.2  | Tetra PDE Solver                                         | . 88  |

|              |      | B.2.1 Tetra Class                                        |       |

|              |      | B.2.2 PThread-Base Synchronization Header                | . 88  |

|              |      | B.2.3 Strip Partitioning - Computation and Communication |       |

|              |      | B.2.4 Block Partitioning - Computation and Communication |       |

|              |      | B.2.5 Borders Exchange                                   |       |

|              |      | B.2.6 Strip Partitioning - Texture-based Red Kernel      | . 105 |

| С            | Ben  | chmark Software                                          |       |

|              | Inst | allation                                                 | 109   |

| D            | Hel  | per Tools                                                | 111   |

|              |      | Domain Generator                                         | . 111 |

|              |      | D.1.1 Usage                                              |       |

|              |      | D.1.2 Code: $grid\_gen.c$                                | . 111 |

|              | D.2  | Timer                                                    | . 114 |

|              |      | D.2.1 Usage                                              | . 114 |

|              |      | D.2.2 Code: $timer\_reg.cu$                              | . 114 |

|              | D.3  | Domains Populator                                        | . 115 |

|              |      | D.3.1 Usage                                              | . 115 |

|              |      | D.3.2 Code: $populate.py$                                | . 115 |

|              | D.4  | Benchmark Launcher                                       | . 116 |

|              |      | D.4.1 Usage                                              | . 116 |

|              |      | D.4.2 Code: $launcher.py$                                | . 117 |

| $\mathbf{E}$ | Gra  | phs Collection                                           | 121   |

|              | E.1  | Execution Round 1                                        | . 121 |

|              |      | E.1.1 Global Memory-Based Kernels                        | . 121 |

|              |      | E.1.2 Texture-Based Kernels                              | . 126 |

|              |      | E.1.3 Speedups                                           | . 131 |

|              |      | E.1.4 Regression-Based Predictions                       |       |

|              | E.2  | Execution Round 2                                        |       |

|              |      | E.2.1 Execution Times and Speedups                       |       |

|              | E.3  | Execution Round 3                                        |       |

|              |      | E.3.1 Execution Times                                    | . 137 |

| $\mathbf{F}$ | NO   | TUR Poster                                               | 139   |

# List of Figures

| 2.1  | The graphics pipeline.                                         | 8  |

|------|----------------------------------------------------------------|----|

| 2.2  | Heterogeneous paradigm of execution.                           | 9  |

| 2.3  | Basic CUDA control flow.                                       | 10 |

| 2.4  | The CUDA software stack                                        | 10 |

| 2.5  | Heterogeneous programming with CUDA.                           | 12 |

| 2.6  | The CUDA memory hierarchy                                      | 13 |

| 2.7  | NVIDIA Tesla S1070 Computing System Architecture.              | 14 |

| 2.8  | S1070 full computing configuration.                            | 15 |

| 2.9  | Multi-GPU programming approaches                               | 16 |

| 3.1  | A shared memory multiprocessor model                           | 18 |

| 3.2  | Accessing critical sections.                                   | 19 |

| 3.3  | A multicomputer model                                          | 21 |

| 3.4  | Latency hiding.                                                | 22 |

| 3.5  | An SMP cluster model                                           | 23 |

| 3.6  | Multi-GPU system as a network of GPUs                          | 24 |

| 3.7  | Kernel programming pattern.                                    | 24 |

| 3.8  | Minimal warp occupancy configuration                           | 27 |

| 3.9  | Overlapping computation with memory copy using streams         | 28 |

| 3.10 | 1                                                              | 29 |

| 3.11 | A possible read-write cycle based on linear memory access      | 30 |

| 3.12 | Shared memory structure                                        | 31 |

|      | Shared memory access with and without conflicts                | 32 |

| 3.14 | Inter-GPU communication times.                                 | 32 |

| 4.1  | Mesh grid example.                                             | 35 |

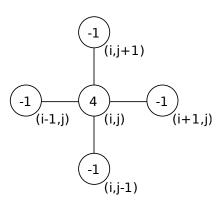

| 4.2  | 5-points stencil for the Laplace equation.                     | 36 |

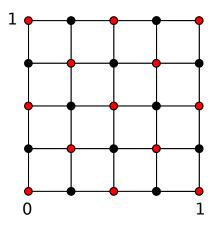

| 4.3  | Red-black ordering.                                            | 39 |

| 5.1  | Domains with equivalent area but different shape               | 41 |

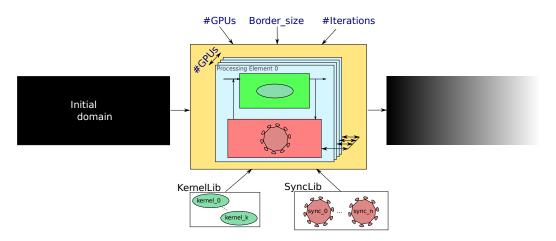

| 5.2  | High-level perspective of the benchmark application.           | 42 |

| 5.3  | Border exchange for a 5-point stencil                          | 44 |

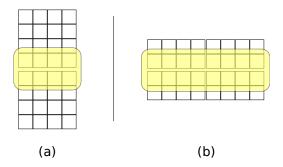

| 5.4  | Strip and block partitioning.                                  | 45 |

| 5.5  | Overall benchmark algorithm.                                   | 47 |

| 5.6  | GPU occupancy parameters using a single thread per threadblock | 49 |

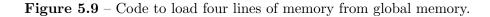

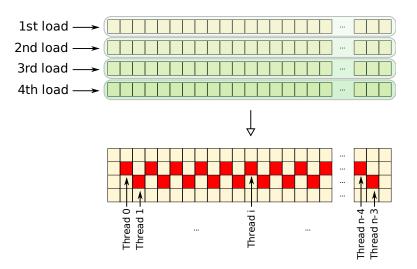

| 5.9  | Code to load four lines of memory from global memory           | 51 |

| 5.10 | Indexing macros.                                               | 51 |

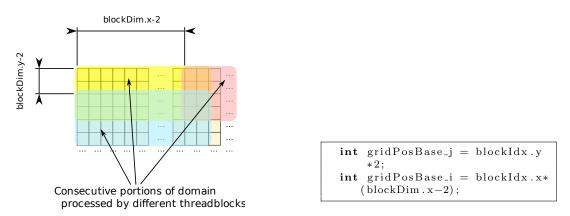

| 5.11 | Code to determine the position of a threadblock in its grid    | 51 |

| 5.12 | Threadblock mapping to shared memory                                 | 52 |

|------|----------------------------------------------------------------------|----|

| 5.13 | Code to determine the red coordinates in shared memory with anal-    |    |

|      | ogous branch-based version                                           | 52 |

| 5.14 | Red SOR step application                                             | 53 |

| 5.15 | Threadblock access pattern to shared memory                          | 53 |

| 5.16 | Code to write data back to global memory                             | 53 |

| 5.17 | Code to determine the black coordinates with analogous branch-based  |    |

|      | version                                                              | 54 |

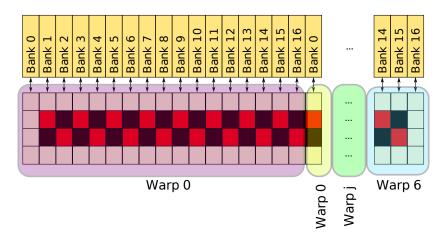

| 5.18 | Data loaded through texture fetching                                 | 54 |

| 5.19 | Texture select & fetch function.                                     | 55 |

| 5.20 | Code to determine the red coordinates in shared memory when using    |    |

|      | block partitioning.                                                  | 55 |

| 5.21 | Border exchange algorithm.                                           | 56 |

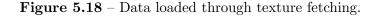

| 5.22 | Petri net describing the interaction between two neighbor threads    | 57 |

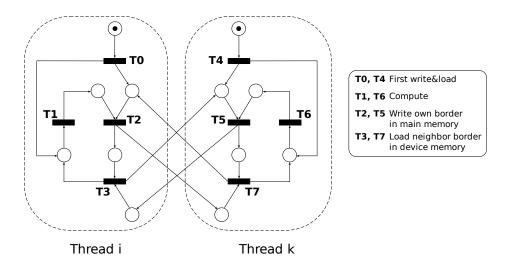

| 5.23 | Chessboard-ordered threads communication                             | 58 |

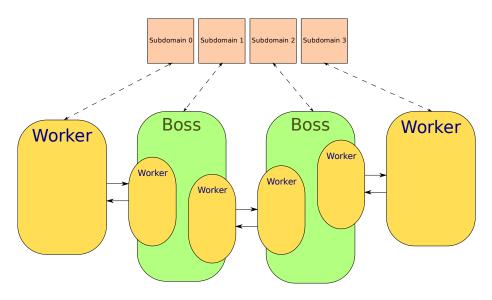

| 5.24 | Boss-worker threads communication.                                   | 58 |

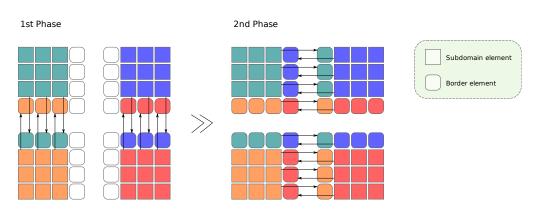

| 5.25 | Communication among threads managing a strip partitioned domain.     | 59 |

|      | Communication flows among blocks.                                    | 60 |

| 5.27 | Communication among threads managing a block partitioned domain.     | 60 |

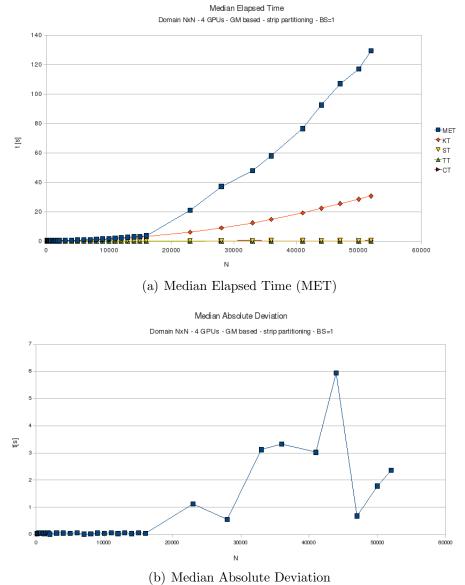

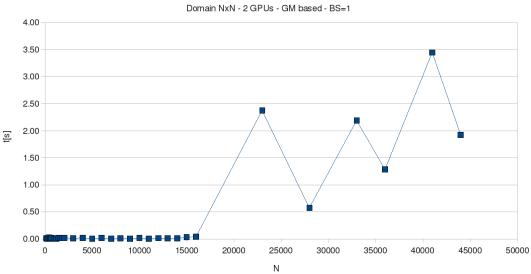

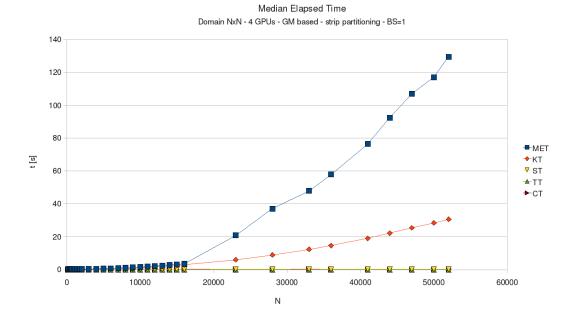

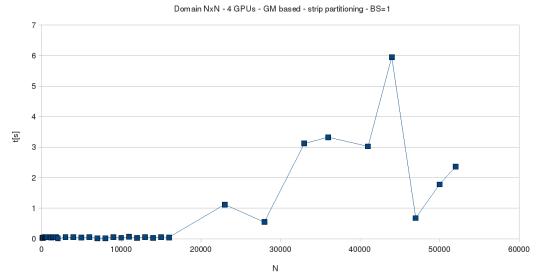

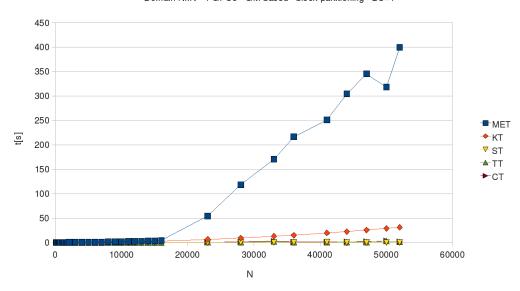

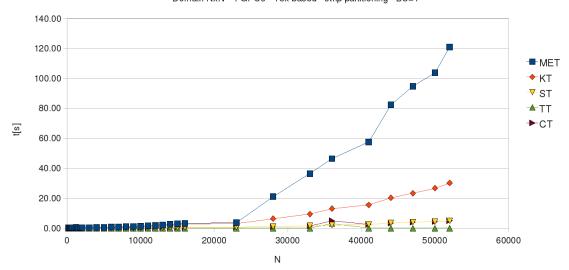

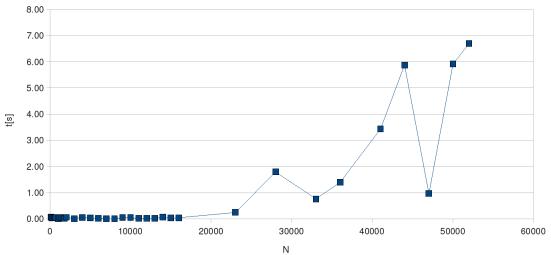

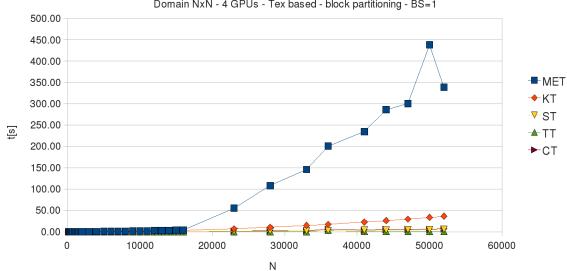

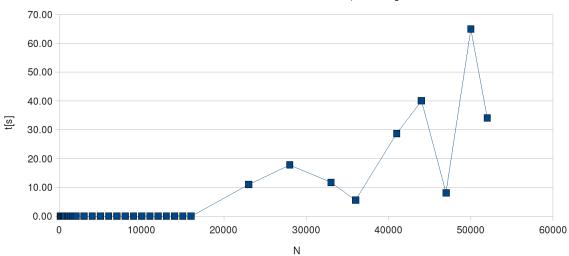

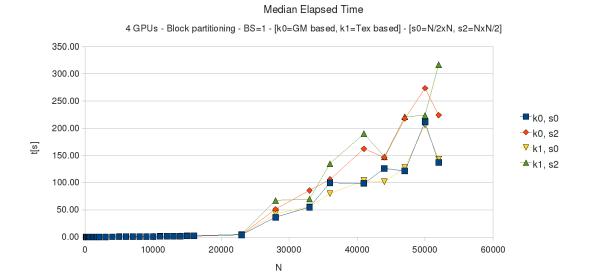

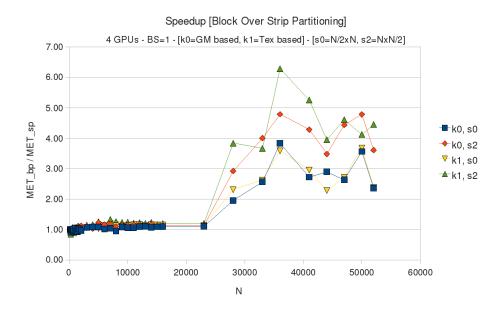

| 6.1  | Strip-partitioned domains: results varying data size                 | 66 |

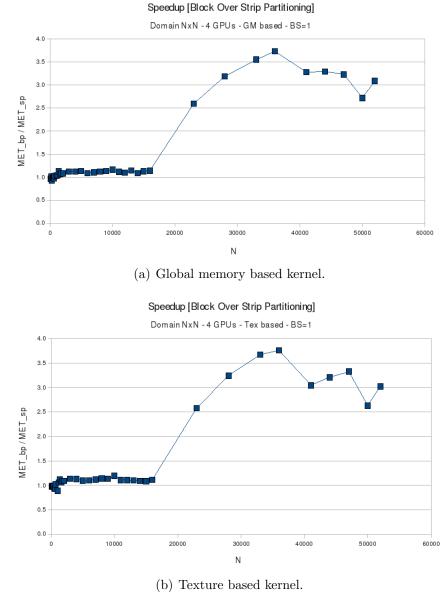

| 6.2  | Block over strip partitioning speedup                                | 67 |

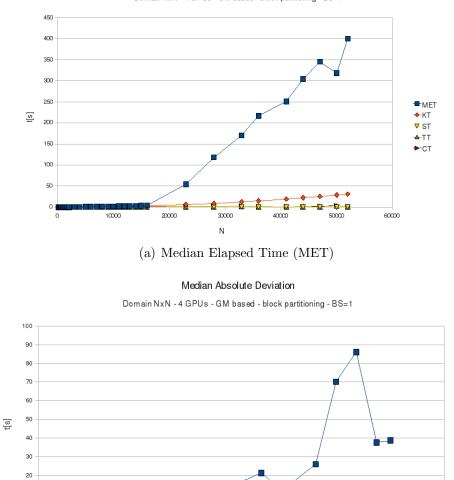

| 6.3  | Block-partitioned domains: results varying data size                 | 68 |

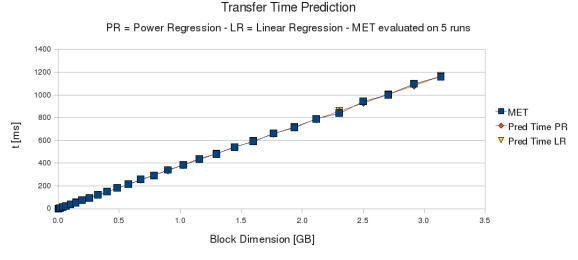

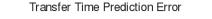

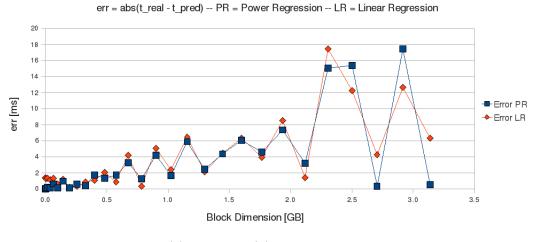

| 6.4  | $T_{GPU-host}(n)$ prediction                                         | 69 |

| 6.5  | $T_{GPU-host}(n)$ prediction fitness test                            | 70 |

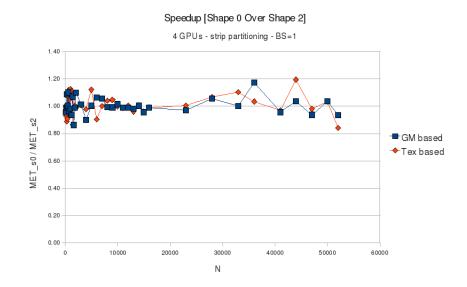

| 6.6  | Strip-partitioned domains: speedups varying domain shape             | 72 |

| 6.7  | Block-partitioned domains: speedups varying domain shape             | 72 |

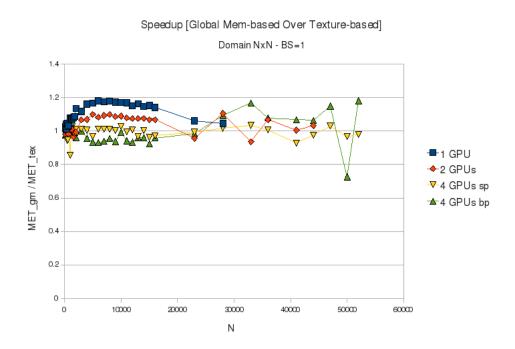

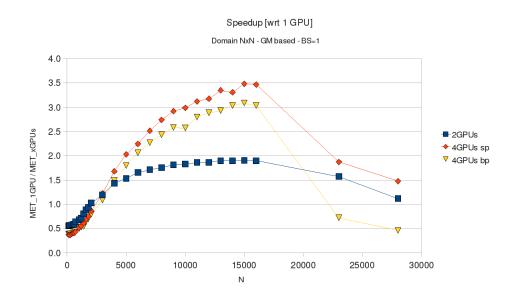

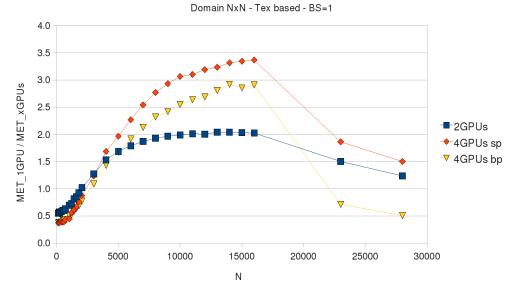

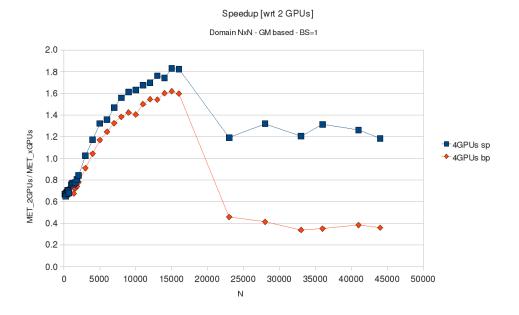

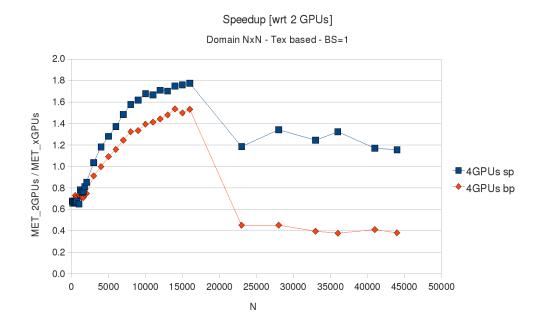

| 6.8  | Speedups varying kernel type                                         | 73 |

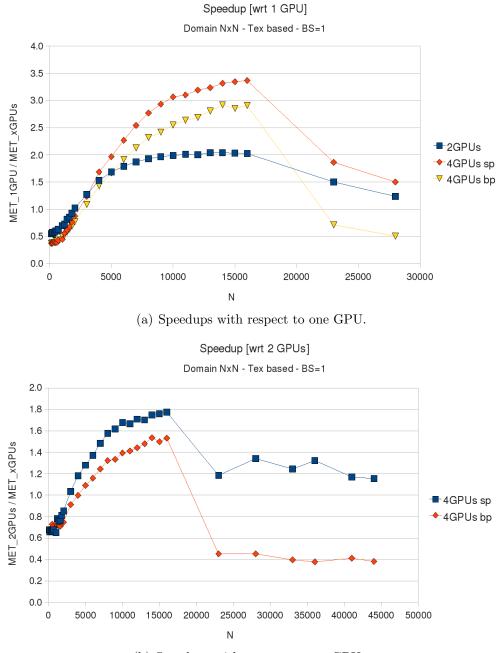

| 6.9  | Speedups varying number of GPUs                                      | 74 |

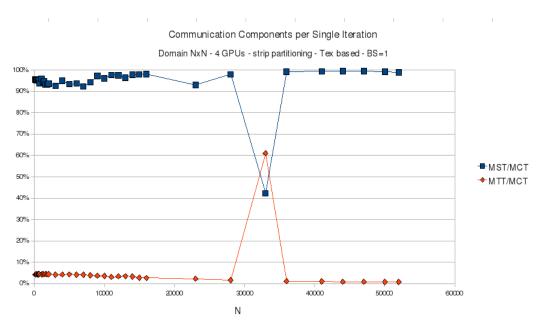

| 6.10 | Precentage of communication used for synchronization and data trans- |    |

|      | fer                                                                  | 75 |

| 6.11 | Border size influence on performance using four GPUs                 | 76 |

# List of Tables

| 4.1 | General prototype PDEs                                            | 34  |

|-----|-------------------------------------------------------------------|-----|

| 5.1 | Benchmarking requirements                                         | 43  |

| 6.1 | CPU Features                                                      | 61  |

| 6.2 | NVIDIA Tesla S1070 Features                                       | 62  |

| 6.3 | Number of attempts per execution depending on the domain size and |     |

|     | the benchmark round.                                              | 63  |

| 6.4 | Comparison between real and attended measurements                 | 66  |

| C.1 | Makefile options.                                                 | 109 |

# Chapter 1 Introduction

The strong interest of the scientific community in developing computational science applications that utilize graphics hardware, has favored a new trend in GPU architecture development. During the current decade, many of the most important manufacturers have thus introduced new product lines targeting scientific computation. In the course of few years, we reached the point where off-the-shelf workstations can combine multicore CPUs and graphics hardware providing performance results comparable to those of some supercomputers in the recent past.

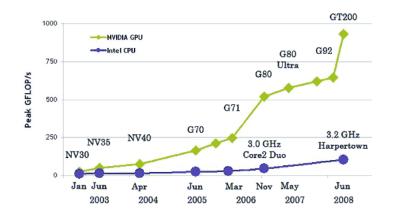

It has been shown that the performance obtained by recent GPUs can get very close to the performance shown by the slowest Top-500 supercomputer only four years ago and the fastest one around 10 years ago. To be convinced, we may just take a look at the two graphs in Figure 1.1 and 1.2. The first one shows the per-

Figure 1.1 – GPU performance trend. (With permission from NVIDIA)

formance trend of GPUs during the present decade. The second one performance trends of the first and last supercomputer in the Top500 list within a larger period. We notice how the performance obtained by recent GPUs can get very close to the performance shown by the slowest supercomputer four years ago and the fastest one around 10 years ago.

Recent evolution of GPGPU models and technologies make these system even more appealing as compute devices for a range of HPC applications including image processing, seismic processing and other physical modeling as well as linear programming applications [27].

If providing a computing node with a GPU accelerator can improve performance, even better results should be achievable using more the one GPU per CPU. Multi-GPU systems increase resources and computing capabilities per node, offering the opportunity to leverage even more speed. An example of a recent multi-GPU system is the NVIDIA Tesla S1070 Computing System, which combine several GPUs to make available up to 4 TFLOPS.

However, increasing the hierarchy of resources issues new challenges to the developers, widening the spectrum of factors that may impact on the performance of a multi-GPU system.

**Figure 1.2** – Performance trends in the top500 list. (With permission from top500.org)

## 1.1 Thesis Goal

The absence of specific models for GPU-based, heterogeneous systems makes it harder to understand what factors are the most in influential in improving or worsening performance. The aim of this work is to investigate such factors in the specific context of the NVIDIA multi-GPU solution, the Tesla S1070 platform. Aside from the intrinsic issues caused by graphics technologies, we will also consider some important models of parallel systems in order to identify some common properties that can help us in our study. Communication is always a relevant aspect when dealing with distributed resources. By designing a benchmark framework around the SOR PDE solver, an applications that constantly requires inter-GPU communication, we are able to develop better a multi GPU model.

## 1.2 Outline

- Chapter 2 presents the technological background, introducing the recent GPU technologies that will support our study. We will focus on NVIDIA's recent technologies, describing in particular the Tesla architecture processing model, the CUDA programming model, and multi-GPU programming.

- Chapter 3 discusses parallel models. It analyzes the shared-memory and the messagepassing models considering possible analogies with multi-GPU systems. These systems are then analyzed in order to point out the main challenges issued by the GPU programming model.

- **Chapter 4** contains the mathematical background necessary to understand the differential equation solver selected as the benchmark application.

- Chapter 5 describes the benchmark test space, which dimensions are related to factors that may impact on performance. The chapter then presents the benchmark application. It highlights the most important decisions at design and implementation level.

- Chapter 6 shows and discusses the results obtained running the benchmark. Results are collected using different test configurations to analyze how these different configurations impact the performance of the multi-GPU system used in our experiments.

- Chapter 7 summarizes the project conclusions and suggests some future work directions.

\_\_\_\_\_

# Chapter 2 Multi-GPU Computing

Graphics hardware is now about forty years old. It was initially developed to support compute-intensive applications such as computer-aided design (CAD) and flight simulation [4]. The last generation of graphics processing units (GPUs) consists of highly parallel, multithreaded, manycore processors. Their large number of streaming processors are well suited for fine-grained, data-parallel workloads, consisting of thousands of independent threads operating concurrently.

Since late 70s, an always larger number of numerical applications are supported by graphics hardware, showing promising results in different scientific fields, such as linear algebra, data compression, database management, and financial services [4, 25, 6, 15]. Normally, when referring to such non-graphics employments of the GPU, it is typical to use the expression general purpose computation on GPUs, or shortly GPGPU<sup>1</sup>. However, the concept of general purpose programming applied to a GPU cannot be confused with the one associated to a normal CPU. Owens *et al.* [25] gives a concise description of the characteristics that an application must feature to successfully map onto a GPU. In particular, it has to be an application with large computational requirements and highly parallelizable, where the throughput is more important than latency.

In the following sections we will give an insight into the processing and programming models exposed by these recent technologies.

# 2.1 The NVIDIA Tesla Computing Architecture

NVIDIA Corporation<sup>2</sup> is currently one of the world's leading manufacturers of graphics technologies. NVIDIA releases GPUs targeting the most computation demanding fields, such as gaming, professional graphics processing, and high performance computing.

Since November 2006, NVIDIA's GPUs are based on the Tesla unified graphics and compute architecture, and since February 2007 they are provided with the

<sup>&</sup>lt;sup>1</sup>http://www.gpgpu.org

<sup>&</sup>lt;sup>2</sup>http://www.nvidia.com

CUDA programming environment to simplify many-core programming. In the official programming guide [23] the NVIDIA Tesla architecture is briefly but completely described in the following way: a set of SIMT multiprocessors with on-chip shared memory. To understand the Tesla's processing model, let us deepen the concepts contained into the previous definition.

## 2.1.1 Streaming Multiprocessors

The Tesla architecture is built around a scalable array of multithreaded streaming multiprocessors (SMs). A multiprocessor consists of eight scalar processors (SPs), two special function units for transcendentals, a multithreaded instruction unit (MIU), and on-chip memory. A SM creates, manages, and executes concurrent threads in hardware with zero scheduling overhead. This is an important factor to allow very fine-grained decomposition of problems by assigning, for instance, one thread to each data element.

## 2.1.2 GPU Memories

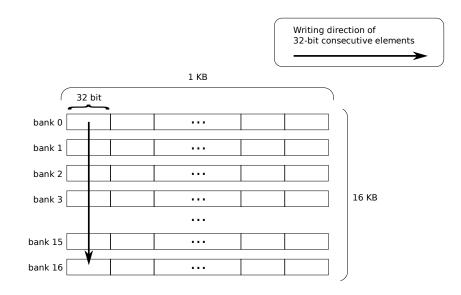

On a GPU we can localize two distinct kinds of memories: on-chip and device memory. With on-chip memory, we refer to:

- A set of 32-bit registers per SP;

- A parallel scratchpad memory, better known as shared memory, per SM. Access times to shared memory are comparable to a L1-cache on a traditional CPU;

- A read-only constant cache shared by all the SPs used to speed up reads from the constant area in device memory;

- A read-only texture cache shared by all the SPs used to speed up reads from the texture region in device memory.

Device memory is a high-speed DRAM memory with higher latency and larger dimension than on-chip memory (typically hundreds of times slower and million times larger). Device memory is subdivided in four regions:

- a read-write, non-cached global area;

- a read-write, non-cached local area;

- a read-only, cached constant area;

- a read-only, cached texture area.

A couple of comments concerning the memory terminology. Device and global memory are, at this point, clearly not synonyms. Global implies the access pattern to that specific area and it is part of the device memory of the GPU. Similarly, local and shared memory are not the same concept. Local memory is part of the device memory (slow) while shared memory is on-chip (fast). Local memory is used by the compiler to keep anything the developer considers local to a thread but, that for some reason, does not fit into the registers of the SP where the thread is executed (e.g. large structures that would consume too many registers).

#### 2.1.3 The SIMT Paradigm

The single instruction, multiple threads (SIMT) paradigm is a new paradigm introduced to manage properly the big amount of threads executable on a Tesla-based GPU. A key difference between the SIMT and the SIMD paradigm is in that a SIMT architecture has no vector width, and a single instruction is issued for and executed by multiple processing elements, supporting full utilization of the cores every time. In contrast, SIMD architectures operate at a reduced capacity when the input size is smaller than the vector dimension.

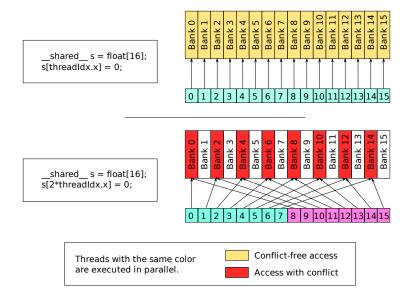

Threads are grouped in warps and mapped to the SPs. One thread is mapped to one SP. Warps are created, managed, and scheduled by the MIU. The number of threads per warp is normally a multiple of the number of SPs. Threads that belong to the same warp start together at the same program address, maintaining a total freedom to branch and execute independently.

Every instruction issue time, the MIU selects a warp that is ready to execute and issues the next instruction to the active threads of the warp. A warp executes one common instruction at a time, so full efficiency is realized when all threads of a warp agree on their execution path. However, threads are free to execute differently, but when this happens, performance risks to be seriously injured. The reason is that disagreements on the control flow force the threads' scheduler to serialize their execution. Once taken all the independent paths, the threads converge back to the next common step in the execution path. Of course, since warps are executed independently, serialization is a problem that might occur just for threads of the same warp. Branch divergences are not the only reason that may lead to threads serialization. If an instruction executed by a warp, regardless of its atomicity, writes to the same location in shared memory for more than one thread in the warp, writes are also serialized. This side effect is called bank conflict. More details about it are given in Section 3.2.1.

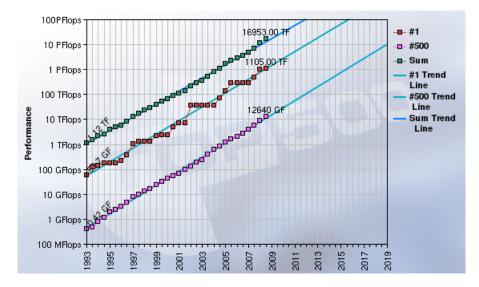

## 2.2 The CUDA Programming Model

Recent programming models for GPUs are the last stage of the evolution of the graphics pipeline. GPGPU developers were used to adopt such a model when implementing their solutions. Basically, we can describe the graphics pipeline as a directed flow of data between its input and its output. The input is provided as a set of triangles which vertices are processed in the first stage of the pipeline, the vertex processor, applying transformations such as rotations and translations. Then, the raster converts the results from the vertex processing to a collection of pixel fragments by sampling the triangles over a specified grid. Such fragments are then computed by the fragment processor, which major task is to compute the color of the several fragments related to each pixel. Texturing, when required, is applied at this point. Finally the framebuffer determines the final color of each pixel in the final image, usually by keeping the closest fragment to the camera for each pixel location. At the beginning the pipeline was conceived as a rigid structure, where the different stages were implemented as fixed functions.

Very soon, GPU designers realized that allowing flexibility would open the possibility to develop more complex effects. In this scenario the pipeline assumed a new connotation, and since the present decade it allows programmability at different level of the processing flow. Older GPU programs were often called shaders, and they were written with shader languages, generally an extension of traditional programming languages in order to support vertices, fragments and interfaces to the pipeline stages (e.g. Cg [16]). Figure 2.1 depicts a typical graphics pipeline with shader programs for vertex and fragment processing. The next step towards a

Figure 2.1 – The graphics pipeline.

modern GPGPU approach was the advent of the unified shader architecture. With the programmable pipeline described above, developers could take better advantage of the repartition of the GPU resources, but still with some unpleasant disadvantage, such as load unbalancing. In that context, the slowest stages burden the whole performance. In a unified shader architecture we find several shader cores able to operate at every level of the pipeline model. Each unified shader core can execute any type of shader and forward the result to another shader core (itself included), until the entire chain of shaders has been executed. The use of unified shader cores allows to allocate resources in a smarter way depending on the specific application, better managing load balancing.

The compute unified device architecture (CUDA) environment<sup>3</sup> presents a cuttingedge programming model well-suited for modern GPUs architectures [23]. NVIDIA developed this programming environment to fit to the processing model of the Tesla architecture, so to expose the parallel capabilities of GPUs to the developers.

<sup>&</sup>lt;sup>3</sup>http://www.nvidia.com/object/cuda\_home.html

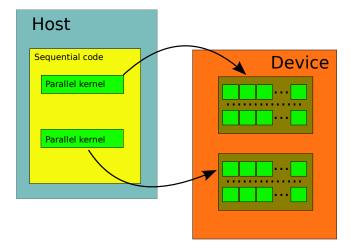

#### 2.2.1 A Heterogeneous Programming Model

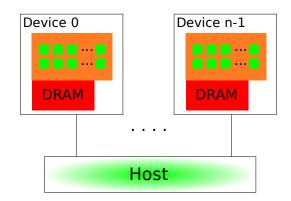

CUDA maintains a separated view of the two main actors involved in the computation, namely the host and the device. The host is the one that executes the main program, while the device is the coprocessor. A typical scenario considers the CPU as the host and a the GPU as the coprocessor, but in general CUDA abstractions may be useful for programming other kinds of parallel systems [20].

Normally CUDA programs contain some pieces of code where intensive computation is required as shown in Figure 2.2. Such code is encapsulated in kernels and executed by the device. The same kernel is executed in parallel by several threads. The number of threads that execute a specific kernel is decided by the programmer and specified when invoking the kernel in the host program (See Section 2.2.3). From a memory point of view, CUDA assumes that host and device maintain their

Figure 2.2 – Heterogeneous paradigm of execution.

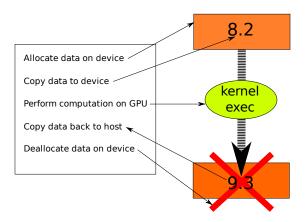

own DRAM, respectively called host and device memory. The most basic example of CUDA processing flow is given in Figure 2.3, and it can be summarized in few elementary steps:

- 1. Allocate memory on the device;

- 2. Copy data from the host memory to the device memory;

- 3. Execute the kernel;

- 4. Copy data from the device memory back to the host memory;

- 5. Deallocate memory on the device.

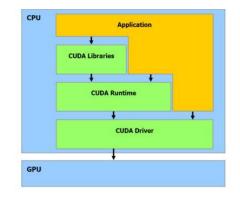

#### 2.2.2 The NVIDIA CUDA Software Stack

Figure 2.4 illustrates the NVIDIA CUDA software stack showing its main layers. A CUDA application can be built upon three main entities: the NVIDIA CUDA Driver API, the NVIDIA CUDA Runtime API, and the NVIDIA CUDA libraries.

Figure 2.3 – Basic CUDA control flow.

Figure 2.4 – The CUDA software stack. (With permission from NVIDIA [23])

The first two layers consist of a low-level Driver API and a higher level Runtime API implemented on top of the first one. Both the APIs are essential to proper manage threads, memory, and kernels invocation on the device. The Runtime API provides a more compact and intuitive interface to the device. On the other hand, even though the Driver API is harder to program, it offers deeper control and language-independence. Since these APIs do the same job at a different level, their use is mutually exclusive.

In the rest of the report every reference to kernel, thread, and memory management is intended through the Runtime API. The CUDA libraries contain mathematical routines of common usage written on top of the NVIDIA CUDA Runtime API, such as FFT and BLAS routines [21, 22].

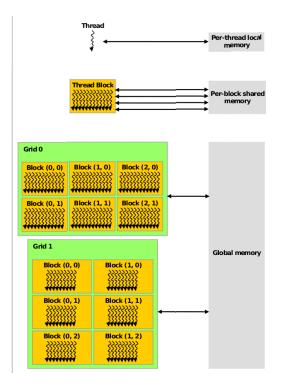

#### 2.2.3 Threads Organization

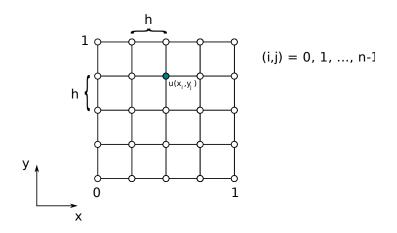

Scientific applications often have to cope with real problems, such as weather and climate forecasting, galaxies evolution, fluid simulation, protein folding, and so on. Applications such as those just mentioned are typically based on numerical methods that require to sample their problem domains in order to have a number of discrete data to elaborate. To better match such mathematical models, the NVIDIA CUDA programming model expresses task and data parallelism through the threads hierarchy. A kernel is a portion of code executed in parallel by different threads. Threads are organized in one-, two-, or three-dimensional, equally-shaped threadblocks. This organization provides a natural way to work with multidimensional structures. Threads within the same threadblock can share data and synchronize themselves through intrinsic synchronization functions.

Multiple threadblocks are organized in one- or two-dimensional grids. Since threadblocks can be executed in any order, in parallel or not, they are required to execute independently. This independence requirement is the key to write scalable code, as it allows thread blocks to be scheduled in any order across any number of cores. While the number of threads per threadblock is limited by physical resources (Section 2.2.5), the number of threadblocks per grid is normally related to the size of the data to be processed.

The programmer has to know a priori the number of threads he wants to dedicate to a specific kernel, and he has to declare it in terms of grid and threadblock dimensions when calling the kernel:

```

kernel <<< dimGrid, dimBlock >>> (...list of parameters...)

```

The expression marked by the two triples of less-than and greater-than signs is called execution environment. Every kernel call is asynchronous, that means that the control returns to the CPU immediately, and it is normally executed by the GPU once all previous CUDA calls have completed. It is also possible to organize kernel executions on different streams, so making kernel calls independent from each other (see Section 3.2.1).

NVIDIA CUDA provides built-in variables that help identifying a number of useful information, like the index of a thread (threadblock) in a threadblock (grid) and the dimension of threadblocks and grids. In this way for instance, a single thread can compute the value of a specific element within a 3D matrix. The thread hierarchy together with such a fine control over the threads allows to define different levels of parallelism [20]. Independent threadblocks of a grid express coarse-grained data parallelism, while grids express coarse-grained task parallelism. Figure 2.5 enriches the execution model of a CUDA program with the threads organization just described.

### 2.2.4 Memory Organization

Every thread has its own local memory. Aside that, threads can use also shared, global, texture and constant memory. Data allocated in shared memory is visible to and accessible by all the threads within the same threadblock. Such data has the same lifetime as the threadblock itself. The global, texture, and constant memory are persistent across kernel invocations by the same application. Figure 2.6 exemplifies the concepts.

**Figure 2.5** – Heterogeneous programming with CUDA. (With permission from NVIDIA [23])

### 2.2.5 Mapping to the Tesla Architecture

When a kernel is invoked, the several threadblocks that compose the grid are enumerated and distributed to SMs with available execution capacity. Every SM can execute several threadblocks. Threads are grouped in warps to be executed. The way a threadblock is split into warps is predefined and always the same: each warp contains threads of consecutive IDs with the first warp containing thread 0. If all the threads of a warp agree on the same execution path than we can estimate the number of clock cycles the GPU needs to execute the whole warp as  $S_w/N_{SP}$ , where  $S_w$  is the warp size and  $N_{SP}$  is the number of SP per SM.

The number of threadblocks a SM can process at once is related to the configuration of the specific launched kernel, and in particular to the amount of registers per thread and shared memory per threadblock requested. This because registers and shared memory are split among the threadblocks associated to the SM. A critical point is that to execute a kernel, a GPU requires enough registers and shared memory per SM to process at least one threadblock, otherwise the kernel invocation would fail.

From a memory point of view, CUDA shared, global, texture, and constant memory naturally fit to the respective Tesla memory areas. From the host, through

Figure 2.6 – The CUDA memory hierarchy. (With permission from NVIDIA [23])

the runtime library, it is possible to allocate memory on the device as linear memory or CUDA arrays. The first allocation method allows a pointer-based management of the memory. CUDA arrays are opaque objects designed and optimized for texture fetching.

## 2.2.6 Compute Capability

Every NVIDIA GPU that can be used in parallel compute mode, is characterized by a compute capability number. Compute capability numbers are defined by a major revision number and a minor revision number. The major revision number indicates the core architecture, while the minor number corresponds to incremental improvements of the core architecture with new features.

In Appendix A, the most relevant features of devices of compute capability 1.3 are summarized. The SP's clock frequency and the total amount of device memory can vary depending on the specific device and can be queried at runtime. The complete specification for the all set of available compute capabilities can be found in [23].

### 2.2.7 Floating-Point Support

All the GPUs of compute capability 1.3 can operate with both single- and doubleprecision floating-point values. However, GPUs belonging to the GeForce GTX 200 family are designed for gaming, where the speed is often more valuable than precision. Those GPUs present some deviations from the IEEE 754 standard for single-precision floating-point values, such as absence of denormalized numbers and smaller set of rounding modes. On the other hand, GPUs designed for HPC completely adhere to the IEEE standard, trying to fulfill the precision requirements typical of scientific applications.

# 2.3 The NVIDIA Tesla S1070 Computing System

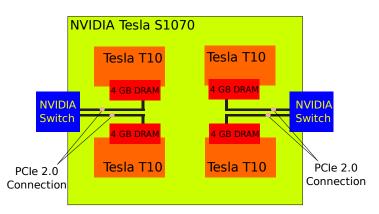

The NVIDIA Tesla S1070 Computing System is a 1U rack-mount system equipped with four Tesla T10 GPUs. Figure 2.7 shows a schematic representation of the system. The Tesla T10 has 240 processing cores working either at 1.296 GHz (-400 configuration) or at 1.44 GHz (-500 configuration). The cores are grouped in 30 SMs. Each core is able to issue up to 3 FLOP per cycle in single precision, i.e. a *multiply* concurrently to a *multiply-add*. A theoretical estimation of the processing

Figure 2.7 – NVIDIA Tesla S1070 Computing System Architecture.

power of the system is

4 GPUs \* (FLOP/cycle \* Frequency \* #Cores)<sub>-400 conf.</sub> =

4 \* (3 \* 1.296 \* 240) GFLOPS = 3.732 TFLOPS in single precision.

4 GPUs \* (FLOP/cycle \* Frequency \* #Cores)<sub>-500 conf.</sub> =

4 \* (3 \* 1.44 \* 240) GFLOPS = 4.147 TFLOPS in single precision.

In double precision, only one core per SM can issue two concurrent operations per cycle, that leads to a theoretical peak of

4 GPUs \* (FLOP/cycle \* Frequency \* #SMs)<sub>-400 conf.</sub> = 4 \* (2 \* 1.296 \* 30) GFLOPS  $\approx$  311 GFLOPS in double precision. 4 GPUs \* (FLOP/cycle \* Frequency \* #SMs)<sub>-500 conf.</sub> = 4 \* (2 \* 1.44 \* 30) GFLOPS  $\approx$  345 GFLOPS in double precision.

From a memory point of view, every GPU is connected to 4 GB high speed DRAM, with a bandwidth of 102 GB/s. This gives to the system a capacity of 16 GB. The connection to the host passes through NVIDIA Switches and PCIe Host Interconnection Cards (HIC). A single PCIe 2.0 16x (or 8x) slot on the host is connected to two GPUs using an NVIDIA Switch and a PCIe HIC. Such a connection is able to

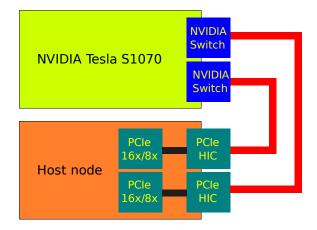

provide a transfer rate up to 12.8 GB/s between the host node and the computing system. A configuration that fully exploits the computing system is given in Figure 2.8. Since power consumption is taking more and more attention today, we can

Figure 2.8 – S1070 full computing configuration.

also mention that the system consumes at most 800 W.

## 2.4 Programming Multiple GPUs

In a multi-GPU context, devices are enumerated progressively. The CUDA Runtime API gives the programmer the possibility to select the device where to execute the kernels. By default device 0 is used. The official CUDA guide [23] reports that a multi-GPU system is guaranteed to work only if the system is composed by the same type of GPUs, and if the Scalable Link Interface (SLI) mode is turned off. SLI is an NVIDIA solution for computer graphics. Basically, it allows two or more GPUs to work together to produce a single graphical output from different input images processed in parallel.

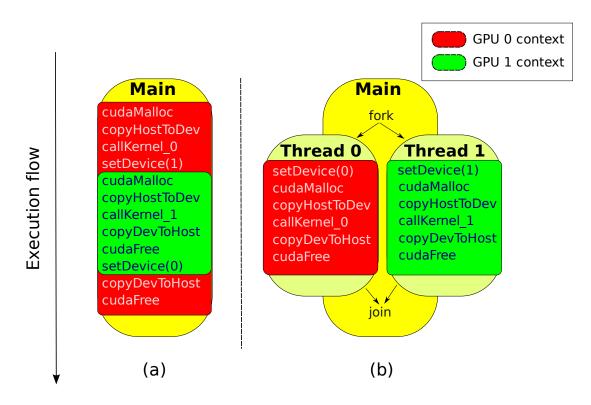

We could take into account at least two main ways to manage the different control flows associated to the GPUs, as depicted in Figure 2.9 for a two-GPUs system. A first way could be to send kernels in a sequential fashion. If the amount of work required to the first GPU is substantial it can be considered a valid solution. Otherwise, a second possibility is to exploit the parallelism offered by modern CPUs.

To use multiple CUDA context we can associate them to different threads, one for each GPU. For optimal performance, the number of CPU cores should not be less than then the number of GPUs in the system. Managing the threads could be done using different approaches. The lowest level one could be to implement an ad-hoc communication layer through system libraries, such as NPTL. Otherwise, existing libraries could be used, such as message-passing libraries adapted to perform shared memory communication [17].

**Figure 2.9** – Two possible approaches to program multiple GPUs: (a) sequential and (b) multithreaded.

# Chapter 3 Parallel Computational Models

In this chapter, we analyze some important parallel computing systems looking for analogies with multi-GPU systems. The aim is to identify the factors that most impact on the performance of a multi-GPU system.

As argued in [19], parallel models often lack of connection to the real world, becoming powerless tools in terms of prediction capabilities. Nontheless, they do not loose their relevance when analyzing new architectures, because they help in focusing on the main characteristics exposed by the systems at issue.

In Section 3.1 we describe two fundamental types of parallel computers, i.e. the shared memory multiprocessor and the message-passing multicomputer. Following, we mention symmetrical multiprocessor (SMP) clusters, which are cost-effective computing platforms that mix shared memory and message-passing features. In Section 3.2, we analyze multi-GPU systems, highlighting their performance factors. Eventual similarities with more classical parallel models can be used to apply common solution patterns to the new architecture.

## 3.1 Parallel Models

There are multiple ways to build a parallel computing system. The two most popular models of parallel computation are shared memory multiprocessors and messagepassing multicomputers. Based on these two basic models it is possible to build different kinds of computing systems, combining in different ways their architectural properties. SMP clusters are one such example where the computing platform combines elements from both the computing models.

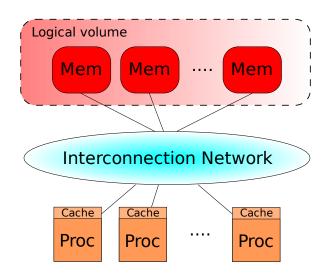

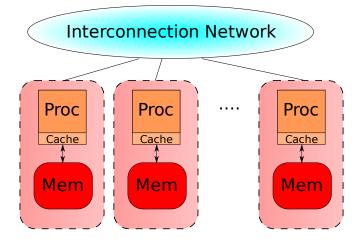

### 3.1.1 Shared Memory Multiprocessor

A shared memory multiprocessor is composed by a set of processing units and a set of memory modules as represented in Figure 3.1. Processing units can be organized at different levels, such as chip-level (a.k.a. multicore CPU) or package-level. In a shared memory system, every single memory location is accessible by any of the processors. This is done implementing a single address space, which assigns to every memory location a unique address. In other words, the set of memory modules are considered as a unique memory volume by the processors. Processors and memory are connected together through some form of interconnection network.

Which kind of interconnection is more opportune for a specific architecture, always depends on its features, such as dimension and cost. Typical interconnection networks are single buses shared by both processors and memory (for small systems), crossbar switches, or any other combination of the two. The kind of interconnection classifies the system depending on the memory access time. When each memory location is accessible to every processor with the same access time, the system has uniform memory access (UMA). On the other hand, when some of the processors require less time to access some memory location, the system has non-uniform access time (NUMA). To reduce communication in the network, it is possible to augment

Figure 3.1 – A shared memory multiprocessor model.

the system with different level of caches to hold the contents of recently referenced memory. There are several ways to program a shared memory system. For the purpose of our work, we just focus on multithreaded programming, where every processor can execute one or more threads. For a broader treatment of shared memory programming methods one could refer to Wilkinson and Allen [29].

When programming a shared memory system, there a number of performance issues to take into consideration. We will now describe three important ones: threads synchronization, caching, and consistency.

#### Synchronization

Shared memory systems give the possibility to organize communication among the processors through memory. Since each memory location is accessible by all the processors, it is possible to use the memory to exchange data among them. If different threads are executed on physically different cores, real parallelism is achieved. Indeterministic scheduling of the threads requires the adoption of proper programming measures.

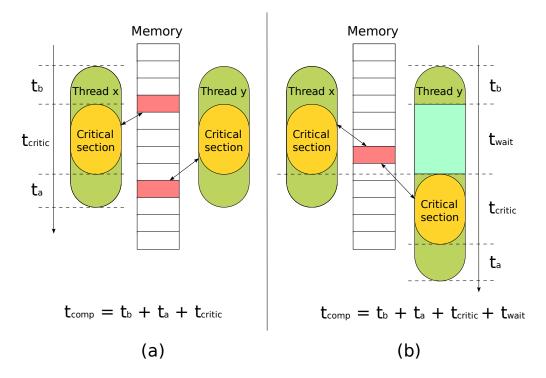

When accessing concurrently the same memory area without an accurate logic, it is possible to produce unexpected results. To prevent such problems threads must be coordinated through synchronization. Most relevant synchronization techniques include thread joins, locks, condition variables, semaphores, and monitors [28]. Consider a group of threads running in parallel some code (see Figure 3.2). If they access different memory locations, then they can be executed concurrently without risks. When some of them reference to the same memory space instead, a way to preserve data coherence is to introduce mutual exclusion on the critical section of the code. This can be done through one of the synchronization techniques mentioned above. However, the fact the just one thread can access the data at a time, requires the execution to be serialized, thus introducing latency in the computation.

**Figure 3.2** – Parallel execution: (a) critical sections accessing different memory locations, (b) critical sections working on the same data set.

#### Caching

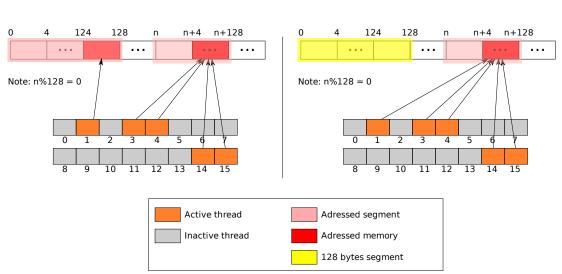

Caches are intermediate memory storages used to deliver higher performance when accessing data or instructions. When accessing a variable or executing an instruction, instead of moving the single requested element, the memory subsystem transfers a block of data that contains it. This block is stored inside the cache, and if the next time the CPU issues that same element or one in the nearby, it can be served very quickly, obtaining the element from the cache.

Different levels of caches can be placed in between the main memory and the processing unit. This levels are characterized essentially by their position and dimension. Normally, on-chip storages have capacity in the order of kilobytes (L1 cache) and megabytes (L2/L3 cache). Other levels can be localized off-chip with a

larger capacity but also a higher latency.

Caches are designed to be invisible to the developer, in the sense that one is not asked to consider them while developing his software. For this reason, they are not programmable elements. However, a cache-aware approach is very important in HPC, since a right use of the cache is able to provide order of magnitude differences in performance [12]. CPU vendors typically release information about the most important features (e.g. cache size, line size, number of ways, etc..) of the caches installed on their processors. Based on these specifications, developers can tune their memory access patterns speeding up their applications. Several methods exists that help optimizing the cache usage [8]. In a parallel environment, there are several issues that could significantly impact on performance.

A first expedient requires to take advantage of temporal and space locality. This can be done grouping instructions that are using same elements, and grouping instructions that access elements that are likely to be stored in a same memory block. When grouping instructions then, it is important to consider the access pattern involved. Often, the logical displacement of objects at the programming level does not reflect the physical displacement at a lower level in memory. For instance, this happens with arrays. Even though accessing a neighbor of an element in a matrix only requires to increment or decrement one the indexes, physically, the neighbor may be found dozens of locations away from the starting element.

When using caches in a shared memory system, another important objective is to reduce false sharing. The false sharing issue is related to the distributed nature of the system. Caching data in a parallel systems, introduces coherency requirements among the nodes' caches. Writing to memory locations stored in the cache of one of the nodes, causes all the blocks in the caches of other nodes to be invalidated or updated if they contain the same values.

#### Consistency

A distributed systems may be adherent to different models called consistency models, that express some properties of parallel executions' final results. One such models is called sequential consistency [14]. Sequential consistency is a consistency model often implemented by shared memory systems. According to the model, when running multiple concurrent programs in their respective orders, the final results has to be the same independently of the instructions interleaving. Some systems, to improve performance, slightly modify the concept of sequential. They allow some degree of out-of-order execution within a program, but always maintaining the sequential consistency of the final result.

## 3.1.2 Message-Passing Multicomputers

When the number of processing units in a parallel computing system increases dramatically, designing a proper shared memory architecture can be rather difficult for several reasons, such as processors-memory connection and cache/memory coherency. Alternatively, a parallel computing model could be composed by several computing elements where each of them is connected to its own memory module. Then, always through some kind of interconnection network, all the processormemory pairs are connected to each other. Such computing architectures are called message-passing multiprocessors or multicomputers, since very often the processormemory pairs are autonomous computing nodes.

A model of multicomputer is given in Figure 3.3. This kind of architecture

Figure 3.3 – A multicomputer model.

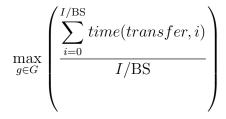

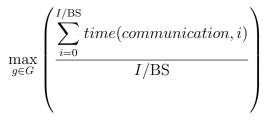

allows higher scalability and ease of construction, but changes completely the communication pattern. Instead of sharing data through a common memory volume, in a multicomputer context data must be transferred from a node to another, thus introducing new performance issues. A simple model for a parallel program is estimated in [29] considering its computation and communication time, which in general depend on the size of the problem and the number of processors:

$$T_{par} = T_{comp}(n, p) + T_{comm}(n, p)$$

. (3.1)

On a shared memory multiprocessor, the communication process is mainly composed by the synchronization overhead. In a message-passing multicomputer instead, we should model the cost of interprocess communication required to produce the final result. What the term  $t_{comm}$  contains depends on the specific communication flow required by the application. If we consider the whole communication time as composed by several communication flows among the processors related to different parts of the program, i.e.

$$T_{comm}(n,p) = \sum_{i} T^{i}_{comm}(n,p) , \qquad (3.2)$$

we may describe the time required by the  $i^{th}$  communication flow as

$$T_{comm}^{i}(n,p) = k^{i}(n,p)(t_{startup} + w^{i}(n,p)t_{word}).$$

(3.3)

The time  $t_{startup}$  is the message latency,  $t_{word}$  is the time required to transfer one data word, and  $w^i(n, p)$  is the number of data words to be transferred, which in general could depend on the problem and the system size.  $k^i(n, p)$  is a general factor

to represent a certain number of communication iterations required by the communication flow.

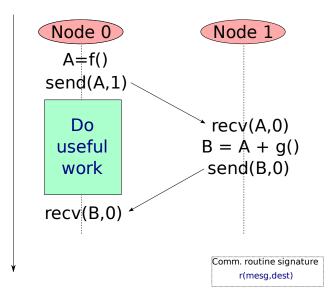

In a multicomputer, a very important objective is to improve performance trying to contain the communication complexity. Depending on the problem, different approaches must be developed to control the communication. However, there is a general principle which is worth remarking. Data transfer are always orders of magnitude greater than elementary operations, such as mathematical ones. In order to not waste time just waiting for data transfers to complete, many communication routines have their nonblocking counterparts. In this way, it is possible to do useful work, while at the same time, the message is moving towards its target (See Figure 3.4). This technique is known as latency hiding.

As for shared memory programming, also message-passing programming can be

Figure 3.4 – Latency hiding.

done in different ways [29]. One common form, is to use a normal high-level programming language, such as C, together with message-passing libraries. The Message-Passing Interface (MPI) standard [1, 26] is very likely the most adopted standard interface for message-passing programming.

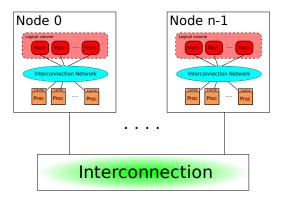

## 3.1.3 SMP Cluster Computing

A cluster of computers is a cost-effective example of multicomputer system. It represents a satisfying trade off between a single commodity computer and an expensive supercomputer in terms of costs and performance. Clusters themselves represent a large family of systems classified by different purposes and implementations.

One of them, called symmetrical multiprocessor (SMP) cluster, is especially interesting for our analysis, insofar as it has a computing model comparable, in our opinion, to the one of a multi-GPU system. A symmetrical multiprocessor is a shared memory multiprocessor with a numerical symmetry between the number of processors and the number of memory modules. When a number of SMPs are linked together, it gives birth to a new architecture called SMP cluster and depicted in Figure 3.5. For the sake of our discussion, The concept of symmetry is not a relevant feature. What is interesting to us, is the programming model that can be adopted on such a architecture. The outer set of SMP nodes could be programmed through message-passing, while multithreading can be used to manage the computation on every shared memory SMP.

Figure 3.5 – An SMP cluster model.

# 3.2 Similarities between SMP Clusters and multi-GPU Systems

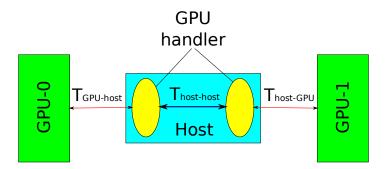

A multi-GPU computing architecture, as described in Chapter 2, has several characteristics that make it similar to the computing model of an SMP cluster. A first analogy comes from the system implementation. As shown in Figure 3.6, every GPU, which in turn is a highly multithreaded system, is linked to every other through the host system. This kind of interconnection, requires communication to setup cooperation in solving a common problem. In the previous chapter, we remarked how GPU systems are today able to compute with theoretical performance in the order of TFLOPS, transferring data between host and device with a rate in the order of GB/s. If we compare that with performance and transfer rate of typical cluster node, we observe that the theoretical instruction densities differ by a constant factor:

$$\frac{Per_{GPU}}{BW_{multi-GPU}} = \frac{TFLOPS}{GB/s} \approx k \cdot \frac{Per_{CPU}}{BW_{cluster}} = k \cdot \frac{GFLOPS}{MB/s} .$$

(3.4)

In this section, we show how some performance issues analyzed in the previous section, can still hold for a multi-GPU system. Of course, because of the difference between a usual processor and a graphics processor, some of the concepts need a proper contextualization, posing sometimes new problematics to surmount.

# 3.2.1 Single GPUs as Shared Memory Nodes

A single NVIDIA Tesla computing architecture, contains hundreds of computing cores, organized in several SMs, connected to different levels of memory. The structure behind processors and memory, involves some new issues that must be carefully

Figure 3.6 – Multi-GPU system as a network of GPUs.

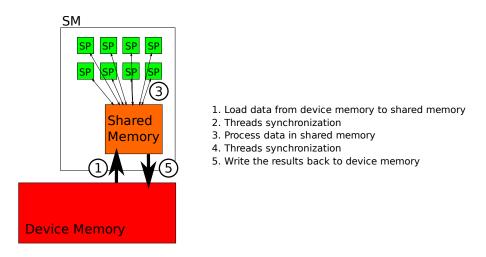

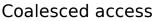

considered. In Section 2.2.1, we introduced a basic CUDA control flow that represents a common host programming pattern. The next step is to understand how kernels can be organized, defining a basic programming pattern also for them. Figure 3.7 shows such a pattern. Every thread loads its own data in shared memory, so to have faster access to them. After that, it performs the required calculation on the data set and writes everything back to global memory. As communication through shared memory might be required by the threads of a same threadblock, synchronization is used to keep results coherent. At the level of a single GPU, an

Figure 3.7 – Kernel programming pattern.

important step for increasing performance is to tune the algorithm in a way that it exposes as much data parallelism as possible. After that, the computing resources have to be allocated, mapping them to the problem using a proper configuration of the execution environment. Memory usage must be optimized at every level of the hierarchy, so to maximize the bandwidth. This is a very crucial step that requires to:

- Minimize the host-device communication. We will focus on this issue in Section 3.2.2 as part of the GPU-GPU communication;

- Use the device memory exploiting the different memory areas' capabilities;

• Use the right access pattern for each type of memory.

Finally, instructions must also be optimized, selecting the fastest ones. We hereby set about discussing these issues in more detail.

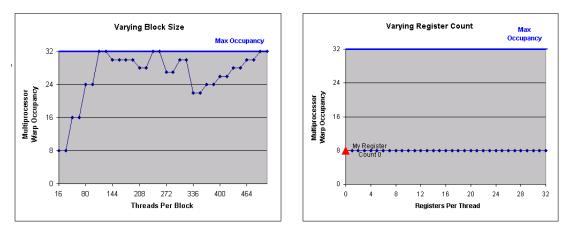

#### **Execution Configuration**

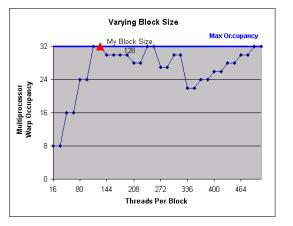

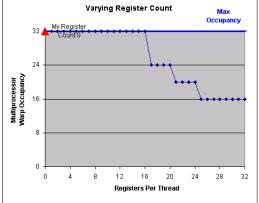

A good execution configuration should ensure an efficient mapping between the thread hierarchy and the parallelism exposed by the problem to solve. We already introduced execution configuration in Section 2.2.3. Here, we intend to discuss how grid structuring can influence performance. To reduce scheduling overhead, resources are split and allocated to each thread. Since resources are in a finite number, it is responsibility of the developer to choose wise dimensions for both grids and threadblocks, so to allocate resources minimizing wastes. If, for instance, at a certain point there are less active threadblocks than available SMs, the computing power of those SMs is wasted. In the same way if there are threads per threadblock that are not multiple of the warp size, a number of SPs would turn out unused. On the other hand, also oversize threadblocks are dangerous. If the number of registers required by a threadblock cannot fit to those available in a SM, the kernel invocation would not succeed.

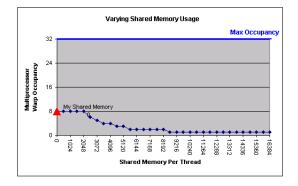

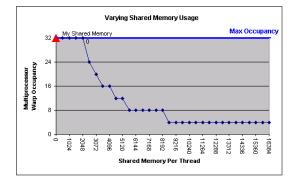

A typical parameter that can lead to optimize the usage of the GPU is the so called multiprocessor occupancy. It is defined as the ratio of the number of active warps per multiprocessor to the maximum number of active warps,

$$SM_{occ} = \frac{W_{active}}{DEF(W_{max\_active})} .$$

(3.5)

The maximum number of active threads per SM, like many other parameters that depends on the specific hardware device, is normally specified by the compute capability of the GPU. Example of such parameters are given in Appendix A for devices of compute capability 1.3. In our notation, we identify the value of a parameter related to a specific compute capability number with the call to DEF(param).

We can formalize such a ratio starting from those variables which definition is normally up to the developer: the number of threads per threadblock  $T_B$ , the number of registers per thread  $R_T$  and the requested amount of shared memory per threadblock  $Sh_{B\_req}$ . A first set of parameters we can calculate are the number of warps, registers, and shared memory per threadblock. Warps and shared memory per threadblock are directly calculated as

$$W_B = \left\lceil \frac{T_B}{\text{DEF}(T_W)} \right\rceil , \quad Sh_B = \left\lceil Sh_{B\_req}, \text{DEF}(Sh_{alloc\_unit}) \right\rceil . \tag{3.6}$$

We indicate with  $\lceil n, s \rceil$  the number n rounded up to a multiple of s. When s = 1 we simply use  $\lceil n \rceil$ . Analogous notation is used for the floor function. Values indicated with a notation similar to  $X_{alloc\_unit}$  indicate the allocation unit sizes for those resources they refer to. So in our case, the number of warps per threadblock  $W_B$  is the calculated as the ratio of the number of threads per threadblock to the

number of threads per warp allowed by the specific GPU. The number of registers per threadblock can be obtained as

$$R'_{B} = \frac{Warp}{Block} \cdot \frac{Thread}{Warp} \cdot \frac{Reg}{Thread} = \left[W_{B}, \text{DEF}(W_{alloc\_unit})\right] \cdot 32 \cdot R_{T} .$$

(3.7)

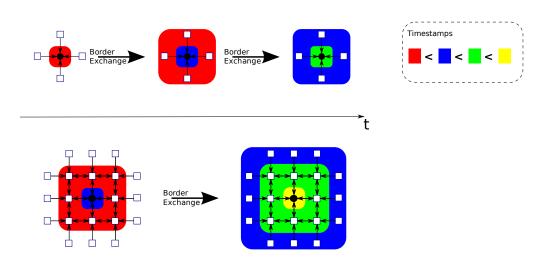

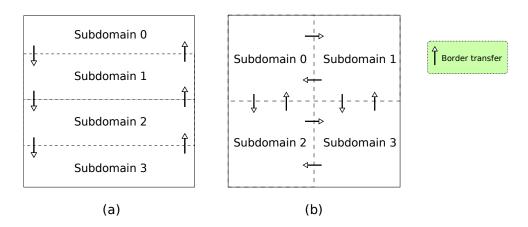

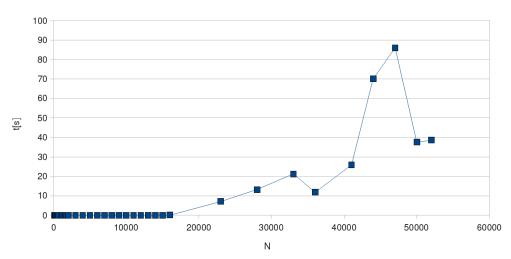

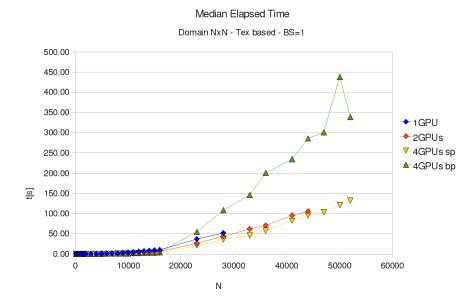

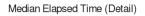

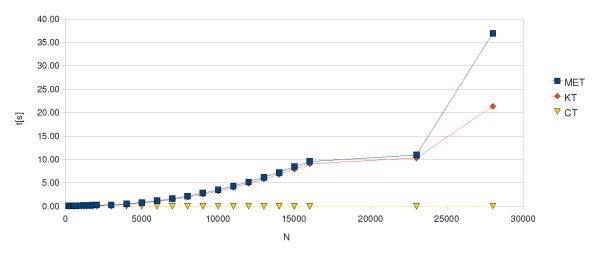

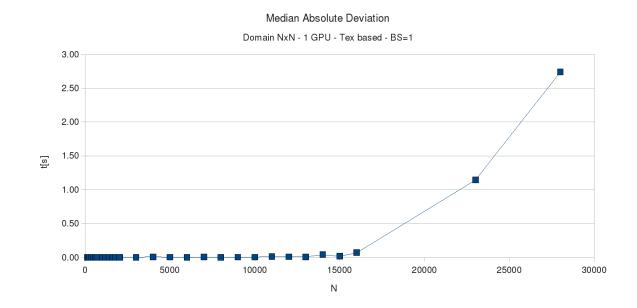

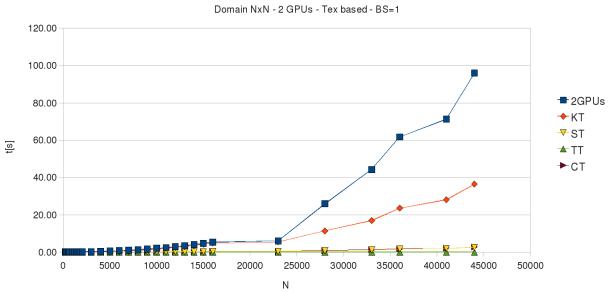

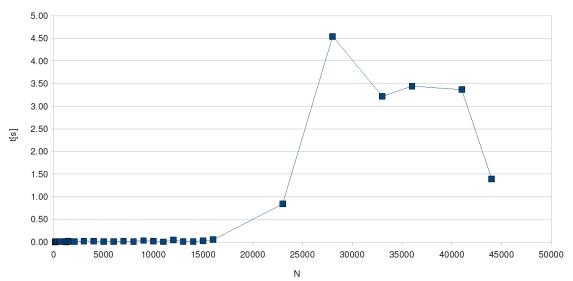

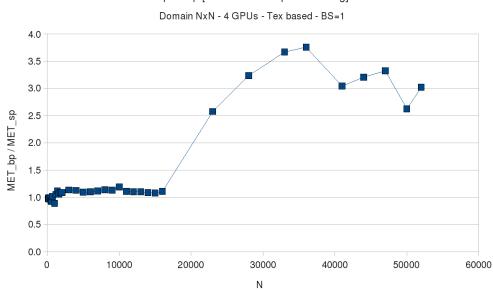

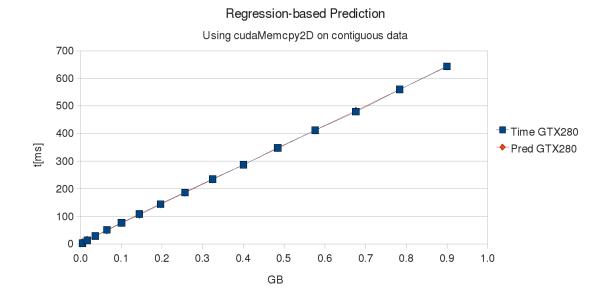

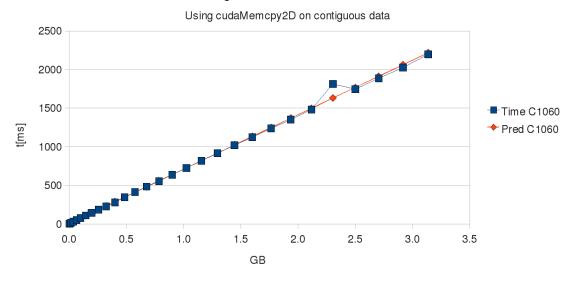

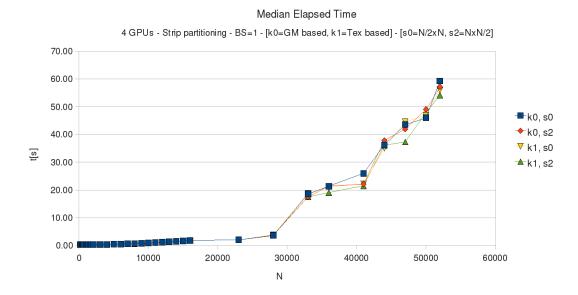

The value  $R'_B$  has to be rounded up to the register allocation unit size: