ISBN 978-82-326-3076-9 (printed ver.) ISBN 978-82-326-3077-6 (electronic ver.) ISSN 1503-8181

o ntnu

# Energy Efficient Computing on

Vectorization and Compression Techniques

Abdullah Al Hasib

# Energy Efficient Computing on Multi-core Processors

Vectorization and Compression Techniques

Thesis for the Degree of Philosophiae Doctor

Trondheim, May 2018

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Computer Science

#### NTNU

Norwegian University of Science and Technology

Thesis for the Degree of Philosophiae Doctor

Faculty of Information Technology and Electrical Engineering Department of Computer Science

© Abdullah Al Hasib

ISBN 978-82-326-3076-9 (printed ver.) ISBN 978-82-326-3077-6 (electronic ver.) ISSN 1503-8181

Doctoral theses at NTNU, 2018:143

Printed by NTNU Grafisk senter

This thesis is dedicated to my parents for their love, endless support and encouragement

# Abstract

Over the past few years, energy consumption has become the main limiting factor for computing in general. This has led CPU vendors to aggressively promote parallel computing using multiple cores without significantly increasing the thermal design power of the processor. However, achieving maximum performance and energy efficiency from the available resources on the multi-core and many-core platforms mandates efficient exploitation of the existing and emerging architectural features at the application level.

This thesis presents the study of some of the existing and emerging technologies in order to identify the potential of exploiting these technologies in achieving high performance and energy efficiency for a set of Smart Grid applications on Intel multi-core and many-core platforms.

The first part of this thesis explores the energy efficiency impact of different multi-core programming techniques for a selected set of benchmarks and smart grid applications on Intel SandyBridge and Haswell multi-core processors. These techniques include different parallelism techniques such as thread-level parallelism using OpenMP, task-based parallelism using OmpSs, data parallelism using SIMD (Single Instruction Multiple Data) instruction sets, code optimizations and use of different existing optimized math libraries. In our initial case studies, SIMD vectorization is proven very effective in providing both high performance and energy efficiency.

Though the SIMD vectorization is proven very effective, it can also exert pressure on the available memory bandwidth for some applications like Powel Time-Series Kernel, causing under-utilization of the computing resources and thus energy inefficient executions. In the second part of this research, we investigate the opportunities of improving the performance of SIMD vectorization for memory-bound applications using SIMD data compression, SIMD software prefetching, SIMD shuffling, code-blocking and other code transformation techniques. The key idea is to reduce the data movement across memory hierarchy by using the idle CPU time. We show that integration of data compression is feasible on the Intel multicore platforms, as long as we can do it in a reasonable time. We present a comprehensive discussion on the SIMD compression techniques and the code transformations required for achieving efficient SIMD computations for memory/cache bound applications using Powel time series kernel as a demonstrator application.

Finally, we perform feasibility study of SIMD optimization and compression techniques across other application domains using k-means clustering algorithm and full-search motion estimation algorithm. We also extended our experiments on Intel many-core architecture using Intel Xeon Phi coprocessor.

# Preface

This thesis is submitted to the Norwegian University of Science and Technology (NTNU) in partial fulfilment of the requirements for the degree of philosophiae doctor (PhD). This doctoral work has been conducted at the Department of Computer Science (IDI), NTNU, Trondheim, Norway. The work has been performed under the supervision of Professor Lasse Natvig.

This PhD in Information Technology has been financed by the Faculty of Information Technology and Electrical Engineering, NTNU, Trondheim.

# Acknowledgements

First and foremost, I would like to express profound gratitude to my supervisor Prof. Lasse Natvig for his helpful and invaluable support, encouragement and supervision throughout my Ph.D. studies. I have learned a lot from him and his continuous guidance helped me to complete my PhD studies successfully. I am thankful to my co-supervisors Jørn Amundsen and Magnus Lie Hetland for the assistance in the early phases of the work and for the valuable feedback and encouragement during the mid-term evaluation meetings.

I extend my heartfelt gratitude to my former colleagues and co-authors Prof. P. G. Kjeldsberg, Juan M. Cebrián and Nikita Nikitin for their great guidance, insightful comments and wisdom during the time we had the chance to work together. In addition, my sincere appreciation goes to all my colleagues in the CARD group and in the entire Department of Computer and Information Science, for having created such a stimulating and pleasant working environment.

All of this would not have been possible without the love of my parents. I am as ever, especially indebted to my parents for their unceasing love, trust and support throughout my life. They supported me to follow my dreams with an endless source of morale and encouragement for me.

Finally, I would like to extend my deepest love and gratitude to my wife Sanjeeda her support, encouragement, and patience, which always kept me going, despite hardships. Without her enduring trust, love, and support throughout these years, I would never have completed this work.

# Contents

| Ab  | ostrac  | t iii                        |

|-----|---------|------------------------------|

| Pr  | eface   | v                            |

| Ac  | know    | vledgements vii              |

| Co  | onten   | ts xiii                      |

| Lis | st of I | Tables xv                    |

| Lis | st of I | Figures xvii                 |

| Lis | st of A | Acronyms xix                 |

| Pa  | rt I:   | Overview 1                   |

| 1   | Intro   | oduction 3                   |

|     | 1.1     | Chip Multiprocessors         |

|     | 1.2     | Energy Efficient Computation |

|     | 1.3     | Research Context             |

|   | 1.4 | Appro  | ach and Main Issues 6                                |  |

|---|-----|--------|------------------------------------------------------|--|

|   | 1.5 | Resear | ch Questions                                         |  |

|   | 1.6 | Thesis | Outline                                              |  |

| 2 | Bac | kgroun | d 9                                                  |  |

|   | 2.1 | Multi- | core and Many-core Processors                        |  |

|   |     | 2.1.1  | Trends in Parallel Computing Architectures 9         |  |

|   |     | 2.1.2  | Dark Silicon and Heterogeneous Computing System . 11 |  |

|   | 2.2 | Multi- | core Computing 12                                    |  |

|   |     | 2.2.1  | OpenMP                                               |  |

|   |     | 2.2.2  | OmpSs                                                |  |

|   |     | 2.2.3  | TBB                                                  |  |

|   |     | 2.2.4  | MPI 13                                               |  |

|   |     | 2.2.5  | Cilk Plus                                            |  |

|   |     | 2.2.6  | CUDA 13                                              |  |

|   |     | 2.2.7  | OpenCL                                               |  |

|   |     | 2.2.8  | Parallel Haskell                                     |  |

|   | 2.3 | Single | Instruction Multiple Data Processing 15              |  |

|   |     | 2.3.1  | SIMD Instruction Sets                                |  |

|   |     | 2.3.2  | SIMD Programming Methods                             |  |

|   |     | 2.3.3  | SIMD Optimization Techniques                         |  |

|   | 2.4 | Data C | Compression                                          |  |

| 3 | Met | hodolo | gy 23                                                |  |

|   | 3.1 | Test A | pplications and Benchmarks                           |  |

|   |     | 3.1.1  | Benchmarks                                           |  |

|   |     | 3.1.2  | Smart Grid Applications                              |  |

|   |      | 3.1.3   | Applications from Different Domain | 28 |

|---|------|---------|------------------------------------|----|

|   | 3.2  | Design  | Space Exploration                  | 29 |

|   | 3.3  | Evalua  | ation Framework                    | 31 |

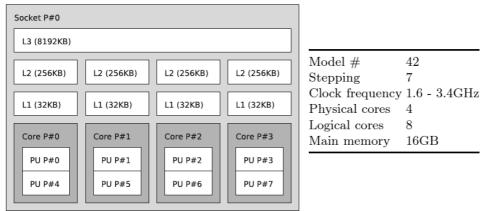

|   |      | 3.3.1   | Test Platforms                     | 31 |

|   |      | 3.3.2   | Profiling and Tracing              | 33 |

|   |      | 3.3.3   | Core Energy Estimation             | 34 |

|   |      | 3.3.4   | System Energy Estimation           | 34 |

|   |      | 3.3.5   | Evaluation of Energy Efficiency    | 35 |

|   |      |         |                                    |    |

| 4 | Rese |         | ,                                  | 37 |

|   | 4.1  | Resear  | rch Process                        | 37 |

|   |      | 4.1.1   | Formalities                        | 37 |

|   |      | 4.1.2   | Publications and Research Themes   | 37 |

|   | 4.2  | Resear  | rch Results                        | 41 |

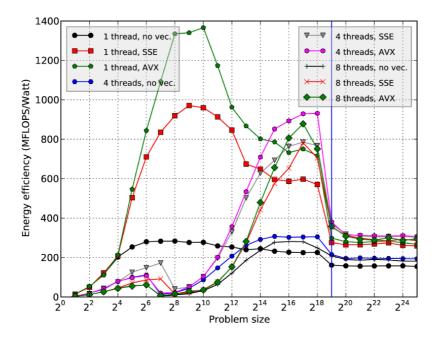

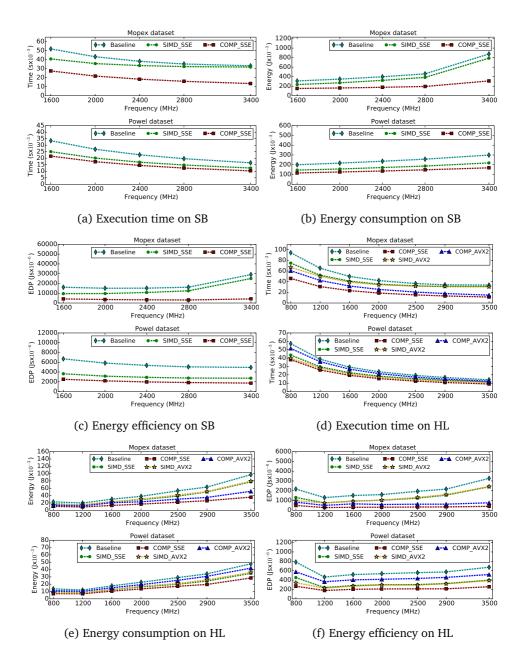

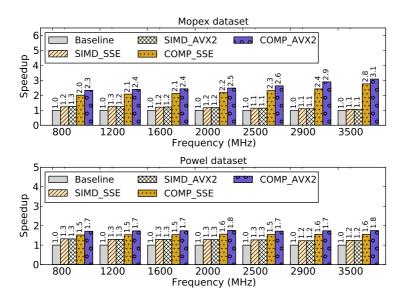

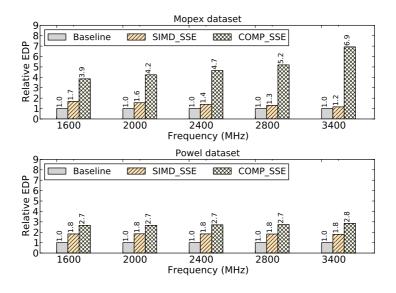

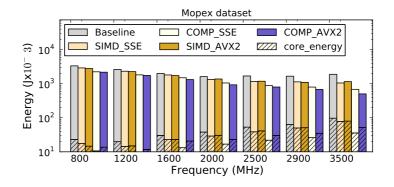

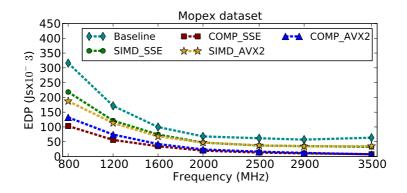

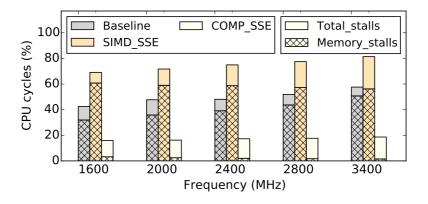

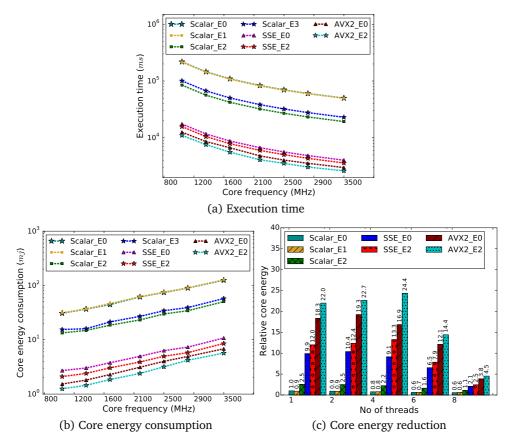

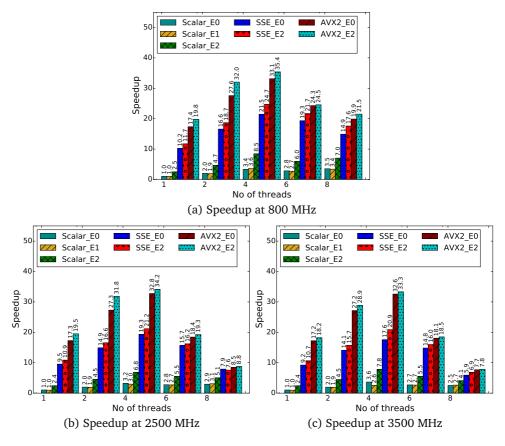

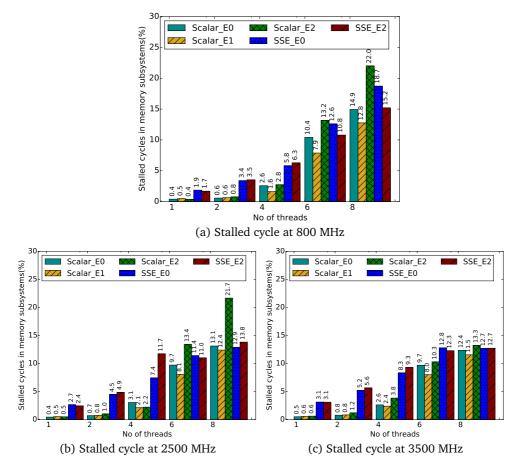

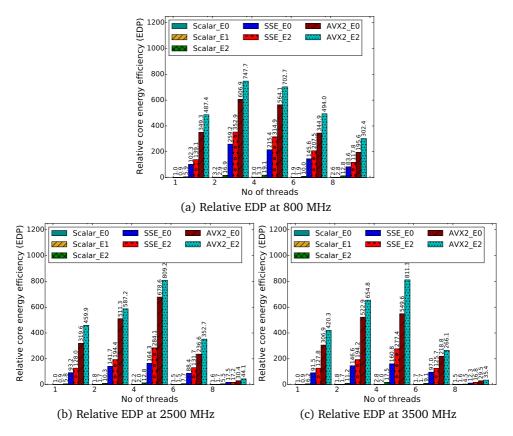

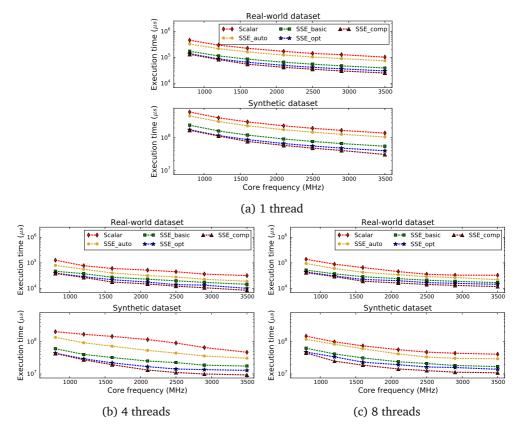

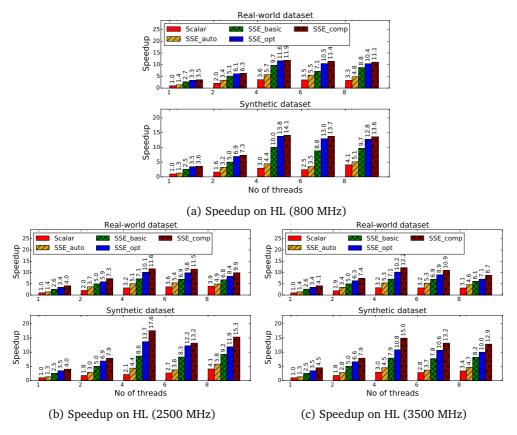

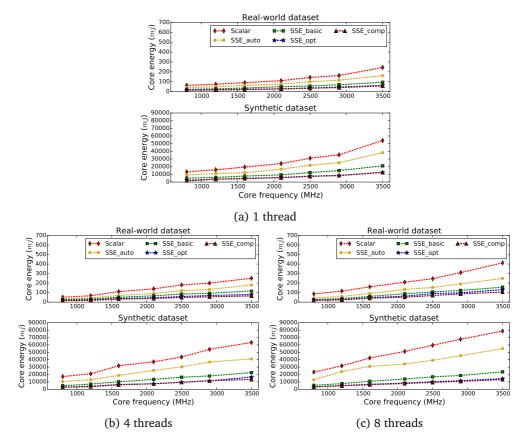

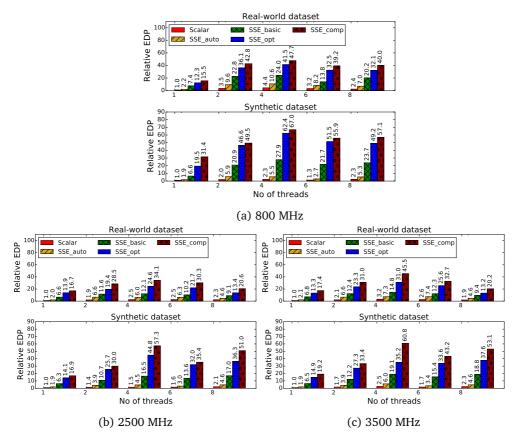

|   |      | 4.2.1   | A.1                                | 41 |

|   |      | 4.2.2   | A.2                                | 42 |

|   |      | 4.2.3   | A.3                                | 43 |

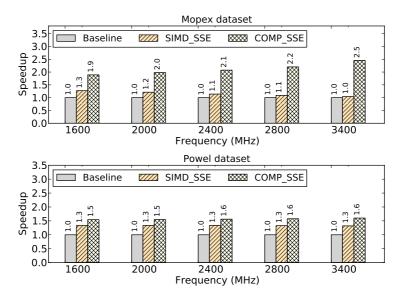

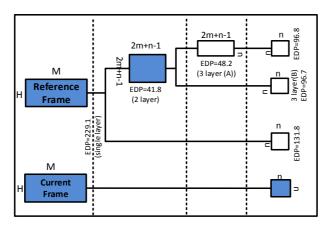

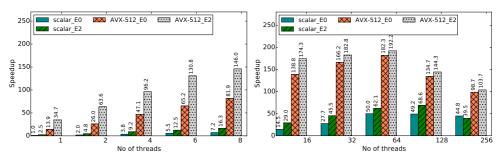

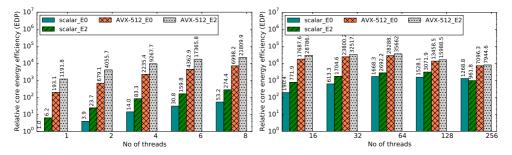

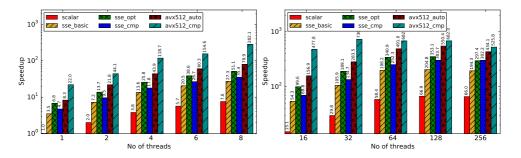

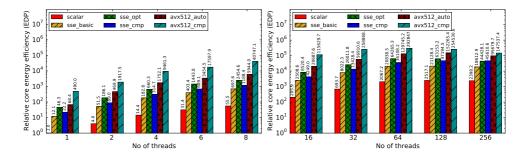

|   |      | 4.2.4   | B.1                                | 45 |

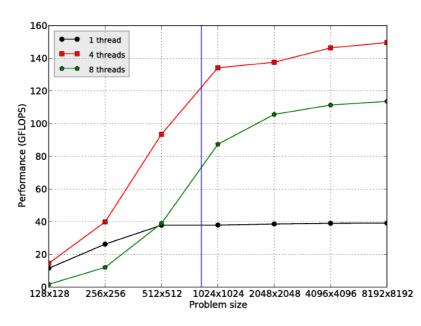

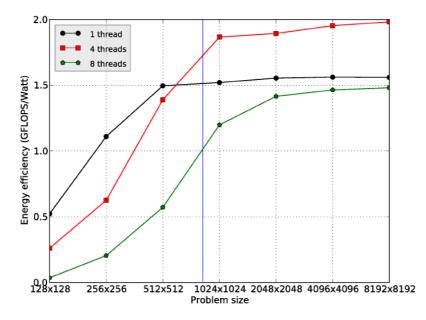

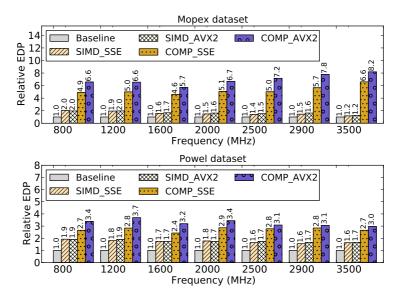

|   |      | 4.2.5   | C.1                                | 46 |

|   |      | 4.2.6   | C.2                                | 47 |

|   | 4.3  | Other   | Publications                       | 49 |

|   |      |         |                                    |    |

| 5 | Con  | cluding | g Remarks                          | 51 |

|   | 5.1  | Conclu  | 1sion                              | 51 |

|   | 5.2  | Future  | e Work                             | 55 |

#### Part II: Papers

| A.1 Ca | se Studies of Multi-core Energy Efficiency in Task Based Pro-                                                |

|--------|--------------------------------------------------------------------------------------------------------------|

| gra    | ms 71                                                                                                        |

| 1      | Introduction                                                                                                 |

| 2      | Background                                                                                                   |

| 3      | Experiments and Results                                                                                      |

| 4      | Related Works                                                                                                |

| 5      | Conclusion and Future work                                                                                   |

|        | formance and Energy Efficiency Analysis of Data Reuse Trans-<br>nation Methodology on Multicore Processor 87 |

| 1      | Introduction                                                                                                 |

| 2      | Related Work                                                                                                 |

| 3      | Energy Efficient Methodology for Multicore Processor 92                                                      |

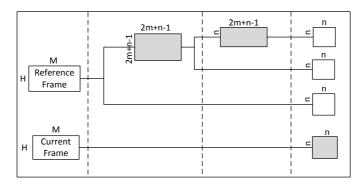

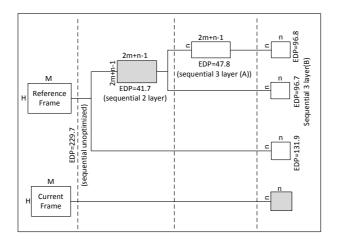

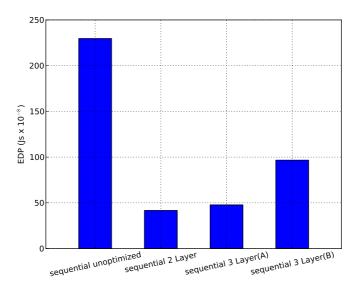

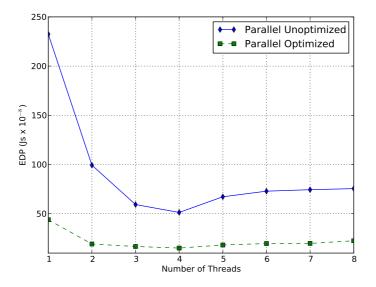

| 4      | Demonstrator Application: Motion Estimation Kernel 94                                                        |

| 5      | Results and Discussion                                                                                       |

| 6      | Conclusion                                                                                                   |

|        | formance Optimization and Evaluation of a Data Cleansing<br>orithm on Multicore Processors 105               |

| 1      | Introduction                                                                                                 |

| 2      | Related Work                                                                                                 |

| 3      | Data Cleansing Algorithm                                                                                     |

| 4      | Performance Optimization Strategies                                                                          |

| 5      | Performance and Energy Efficiency Analysis                                                                   |

| 6      | Conclusion                                                                                                   |

| D 1 WD | EOPDalta, Data Comprossion for Enormy Efficient Compute                                                      |

| в.1 | v-PFORDenta:    | Data  | Compression | for Energy | Efficient | Computa- |    |

|-----|-----------------|-------|-------------|------------|-----------|----------|----|

| 1   | tion of Time Se | eries |             |            |           | 1        | 15 |

|             | 1 | Introduction                                                                                                       | 9  |

|-------------|---|--------------------------------------------------------------------------------------------------------------------|----|

|             | 2 | Related Work                                                                                                       | 0  |

|             | 3 | Powel Hydrological Compute Kernel                                                                                  | 2  |

|             | 4 | Time Series Datasets                                                                                               | 3  |

|             | 5 | V-PFORDelta Compression Algorithm                                                                                  | 4  |

|             | 6 | Results and Discussion                                                                                             | 9  |

|             | 7 | Conclusion                                                                                                         | 9  |

| <b>C.</b> 1 |   | rgy Efficiency Effects of Vectorization in Data Reuse Trans-<br>nations for Many-core Processors – A Case Study 14 | 5  |

|             | 1 | Introduction                                                                                                       | .9 |

|             | 2 | Related Work                                                                                                       | 0  |

|             | 3 | Energy Efficient Methodology for Multi-core and Many-core<br>Processor                                             | 2  |

|             | 4 | Demonstrator Application: Full-Search Motion Estimation Al-<br>gorithm                                             | 5  |

|             | 5 | Results and Discussion                                                                                             | 2  |

|             | 6 | Conclusion                                                                                                         | 6  |

| C.2         |   | ectorized <i>K-means</i> Algorithm for Compressed Datasets – Design<br>Experimental Analysis 18                    |    |

|             | 1 | Introduction                                                                                                       | 7  |

|             | 2 | Related Work                                                                                                       | 9  |

|             | 3 | K-means Clustering Overview                                                                                        | 0  |

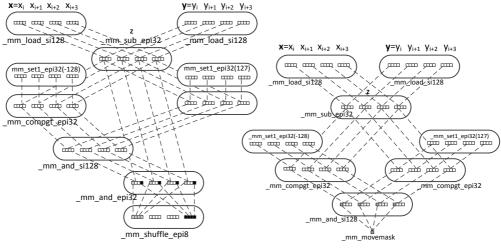

|             | 4 | Multi-threaded Vectorized K-means with Compressed Dataset 19                                                       | 2  |

|             | 5 | Experiments and Results                                                                                            | 8  |

|             | 6 | Conclusions and Future Work                                                                                        | 9  |

# List of Tables

| 2.1 | Intel CPU architectures and trends                      | 10 |

|-----|---------------------------------------------------------|----|

| 2.2 | Summary of a few parallel programming models            | 15 |

| 2.3 | Evolution of SIMD extensions                            | 18 |

| 3.1 | Hardware specifications of the test platforms           | 32 |

| 32  | Used PAPI event-set to monitor cache and memory related |    |

| 0.2 | events                                                  | 33 |

| 3.3 | Model Specific Registers for energy measurements        | 34 |

| 4.1 | Paper categories                                        | 38 |

| 4.2 | Paper category A                                        | 38 |

| 4.3 | Paper category B                                        | 39 |

| 4.4 | Paper category C                                        | 40 |

| 4.5 | Paper category D                                        | 41 |

# List of Figures

| 1.1 | Forty years of microprocessor trend data [6] 4                                      |

|-----|-------------------------------------------------------------------------------------|

| 2.1 | AVX register scheme as extension from the SSE (XMM0-XMM15) 16                       |

| 2.2 | AVX-512 register scheme as extension from the AVX (YMM0-YMM15) and SSE (XMM0-XMM15) |

| 3.1 | Research methodology to conduct this research                                       |

# List of Acronyms

| ASIC   | Application Specific Integrated Circuit       |

|--------|-----------------------------------------------|

| ATLAS  | Automatically Tuned Linear Algebra Software   |

| AVX    | Advanced Vector Extensions                    |

| BLAS   | basic linear algebra subprograms              |

| CMOS   | Complementary Metal-Oxide Semiconductor       |

| CMP    | Chip Multiprocessor                           |

| CUDA   | Compute Unified Device Architecture           |

| EDP    | Energy Delay Product                          |

| FPGA   | Field Programmable Gate Array                 |

| GPU    | Graphic Processing Unit                       |

| HBM    | High-Bandwidth Memory                         |

| HPC    | High Performance Computing                    |

| IEC    | Intel Energy Checker                          |

| MCDRAM | Multi-Channel Dynamic Random Access Memory    |

| MIC    | Many Integrated Core                          |

| MPI    | Message Passing Interface                     |

| MSR    | Model Specific Register                       |

| OpenCL | Open Computing Language                       |

| OpenMP | Open Multi-Processing                         |

| PAPI   | Performance Application Programming Interface |

| SIMD   | single instruction multiple data              |

| SMT    | Simultaneous Multi-threading                  |

| SSE    | Streaming SIMD Extensions                     |

| SVE    | Scalable Vector Extension                     |

| TBB    | Threading Building Blocks                     |

| TDP    | Thermal Design Power                          |

| VPU    | Vector Processing Unit                        |

|        |                                               |

# Part I Overview

# Chapter 1

# Introduction

### 1.1 Chip Multiprocessors

The CPU performance in single core architectures is traditionally improved by the use of smaller, faster and more power efficient transistors in conjunction with the innovative techniques like pipelining, branch prediction, outof-order execution, multilevel cache hierarchy etc. However, as the single core processor hits the power wall [1], the traditional way of improving its performance through frequency scaling and instruction level parallelism becomes too expensive in terms of power and area cost [2]. As a consequence, the enhancement of single core CPU performance is slowing down. To compensate this slowness in performance enhancement and to improve power efficiency, multi-core and many-core architectures are introduced. In these designs, known as Chip Multiprocessors (CMPs), multiple low-power cores are added on a single chip [3]. The underlying concept of CMPs is to improve the throughput of the system by exploiting task-level or threadlevel parallelism using multiple cores without significantly increasing the thermal design power (TDP) of the processor [4, 5]. Today, the mainstream processors are equipped with multiple cores to handle computation intensive applications. More complex system architectures are equipped with coprocessors or accelerators so that the applications can achieve the maximum efficiency.

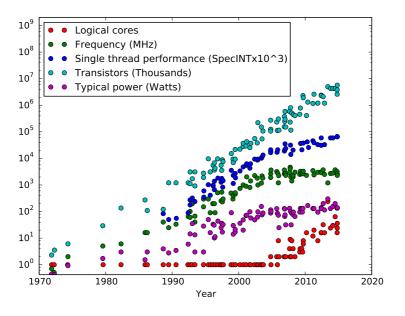

Figure 1.1 presents the trend of microprocessors for the last 40 years. Several interesting observations can be made from the figure: First, the clock speed is leveled off in the recent years due to power densities. Second, the transistor counts continues to increase in accordance to Moore's Law [7]

Figure 1.1: Forty years of microprocessor trend data [6]

as the core counts continues to grow for the last decade. Another important observation is that the single-threaded performance has kept increasing slightly. This is attributed due to the use of energy efficient clever power management and dynamic clock frequency adjustments such as Intel Turbo Boost Technology, AMD Turbo Core Technology etc. These technologies enable the processor to run above its base operating frequency if it operates operating below power, current, and temperature specification limits [8].

## 1.2 Energy Efficient Computation

We have entered an era where CMOS digital computing techniques are reaching physical limits, increasing the importance of energy efficient computations. A large number of research activities have been conducted to develop different energy efficient techniques across different layers in a multi-core system. Low-power circuit design, per-core as well as system wide dynamic voltage and frequency scaling and dynamic power management from operating system level are examples of such techniques [9, 10, 11]. In addition, the unprecedented growth of data, the need for sustainable improvements in computing capacity and energy efficiency in data science, data analytics and scientific computing are becoming greater than ever. However, it is becoming increasingly difficult to extract more system performance by adding more and more processing cores due to the limitations of *Dennard scaling* [12, 13, 14]. The resulting slowdown in the performance improvement is due to the fact that a significant fraction of the cores has to be switched off (or operated at low frequencies) at any point in time for the power and the thermal limits. This phenomenon is known as *Dark Silicon* [15]. To bridge this dark silicon performance gap, it is absolutely necessary to both improve the energy efficiency of hardware components of the system and to exploit application level energy efficient techniques.

However, for many applications (e.g. commercial applications), it is often undesirable to gain energy efficiency by sacrificing the performance. Therefore, it is also important to realize that energy efficiency does not necessarily mean a process to reduce the energy consumption through compromising the performance [2]. Achieving maximum performance from the available resources on the multi-core platforms mandates the exploitation of all architectural features and their intrinsic parallelism across all granularities [16] such as thread/task-level parallelism and data parallelism. To facilitate thread-level and task-level parallelism, new programming languages, language extensions and libraries are continuously being developed. OpenMP [17], OmpSs [18], Cilk++ [19], Intel Threading Building Blocks (TBB) [20], CUDA [21], OpenCL [18] are some of the popular programming constructs on multi-core and many-core platforms.

Most modern processors also support single instruction multiple data (SIMD) instructions to provide additional throughput and power efficiency through data parallelism [22]. Intel has started supporting 512-bit SIMD computations though Advanced Vector Extensions (AVX-512) [23] and ARM is going to release Scalable Vector Extension (SVE) [24] instruction sets to support up to 2048-bit vectors. Therefore, recent trends clearly show the importance of vectorization in future High Performance Computing (HPC) systems. However, SIMD computations can also turn a CPU bound application into memory bound if the processor runs out of reservation stations or load/store queue entries. Unfortunately, existing software tools and techniques are not often fully able to exploit modern multi-core and many-core architectures [25, 26]. As a consequence, a major research challenge of today is to devise tools and techniques so as to translate the multi- and many-core parallel resources into real application performance.

# 1.3 Research Context

Smart grids employ information technology to improve the efficiency, reliability and security of the power generation, transmission and distribution processes under the increasing energy demands. In support to the vast potential for development in the Smart Grid sector, NTNU aims at establishing a national center for smart grid research in co-operation with industries, public bodies and other actors.

This dissertation is supported by a PhD fellowship in Smart Grid Research, and was partly performed in cooperation with Powel AS. Powel AS is one of the leading companies in Norway developing solutions to meet the requirements of smart grid technology. One of the smart grid applications studied here is a hydrological time series compute kernel obtained from Powel AS that receives multiple hydrological time series data from database (or reads from file) and produces a summary series.

# 1.4 Approach and Main Issues

The energy efficiency of computer systems can be improved at various levels and by many approaches. They include low power design and hardware energy saving techniques, system architecture innovation and relevant parallelization techniques, dynamic power management at the OS level, resource scheduling and code optimization using energy aware algorithms and data structures [27] etc. Recent research [22, 28, 16] has revealed the potential of using SIMD execution units to improve the performance and energy-efficiency of compute intensive applications in modern multicore systems [22, 28, 16]. However, despite the potential of SIMD instructions in developing energy efficient applications, modern compilers still do not have adequate auto-vectorization support for complex codes [29, 30]. Moreover, extracting performance from SIMD and thread-level parallelism is not trivial and a careless implementation can easily obliterate the advantages of modern processors. As a consequence, these powerful processing units (i.e. SIMD units) of modern multi- and many-core systems are often largely underutilized.

It is also important to realize that a significant portion of the overall energy consumption in modern processors is due to data communication across the memory hierarchy [31]. Such consumption is expected to grow even bigger with the unprecedented growth of big data and the emergence of exascale computing. Therefore, it is important to improve the cache effectiveness not only in terms of performance, but also for energy efficiency. SIMD pro-

cessing typically improves the CPU computational power and, if used wisely, can be seen as an opportunity to improve on the application data transfers by compressing/decompressing the data, specially for memory-bound applications.

This dissertation strives to improve energy efficiency of a set of compute intensive as well as memory bound applications by fully exploiting the parallelism potential of SIMD architectures. We primarily focused on designing SIMD friendly data structures and strategies to enhance the utilization of SIMD execution unit as well as to increase the effective cache capacity using compression techniques and on-chip data availability so as to improve the cache hit ratio at the Last Level Cache (LLC). Because of the well known processor-memory performance gap (also called the memory wall), this will significantly reduce the cost of data access and thus enhance the performance and power efficiency.

## 1.5 Research Questions

Our objective in this thesis is to explore and analyze different multi-core programming methods to improve performance and energy efficiency of some selected smart grid applications. Primarily we will focus on addressing the following research questions:

- RQ 1: To what extent multi-core programming, particularly multithreading along with SIMD vectorization, can be suitable for the selected smart grid applications?

- RQ 2: To what extent can we improve the energy efficiency of the selected applications by using SIMD compression techniques?

- RQ 3: Can we extend our research results to another application domain?

# 1.6 Thesis Outline

This thesis contains an overview of the research context, research methods and a collection of six papers being produced as a result of this thesis work. The main work and contributions are in the enclosed papers. The overview of the thesis is organized as follows: First, Chapter 2 presents the theoretical background and the relevant research work. Chapter 3 illustrates the methodology used to complete this research work. Chapter 4 contains a brief summary of the included papers. Finally, 5 concludes the thesis with some retrospective remarks and the possibilities of future enhancements.

# Chapter 2

# Background

This chapter provides more insights about the multi-core and many-core architectures, multi-core programming, and data compression algorithms.

### 2.1 Multi-core and Many-core Processors

#### 2.1.1 Trends in Parallel Computing Architectures

The demand for faster computers is ever increasing, but the dramatic growth of single processor performance has come to an end due to several technological limitations (such as power wall, memory wall, ILP wall) [3]. To overcome these technological barriers, the leading processor manufactures, from Intel and AMD to Qualcomm and NVIDIA, have shifted their production pipelines from single-core processors to multi-core processors where multiple cores are put-together on a single chip to meet the performance goals without using the maximum operating frequency. As a consequence, multi-core processors result in dramatic increase in the MIPS-per-watt performance compared to that of single-core processors [5, 3].

Today, multi-core processors have become the dominant architecture for the mainstream processors to meet the demand of compute intensive applications. They usually feature up to 24 cores (Table 2.1), but can have beyond 60 cores. Such multi-core processors are often referred to as many-core to express a high core count and are often used for high performance computing (HPC). Often many-core processors have more complex architecture consisting of co-processors, accelerators such as Graphic Processing Units (GPUs) and Field Programmable Gate Arrays (FPGAs) over a PCIe interconnect or even on the same chip.

| Code            | Processor       | Product name | Frequency | Core(s) | Thread(s) | SIMD  | Process    |

|-----------------|-----------------|--------------|-----------|---------|-----------|-------|------------|

| name            | name            | (Intel Xeon) | (GHz)     |         |           | width | technology |

| Nehalem         | Nehalem         | W5580        | 3.20      | 4       | 8         | 128   | 45 nm      |

| Ivenalem        | Westmere        | W5680        | 3.33      | 6       | 12        | 128   | 32 nm      |

| Sandy Bridge    | Sandy Bridge    | E3-1280      | 3.50      | 4       | 8         | 256   | 32 nm      |

| Salidy blidge   | Ivy Bridge      | E7-4890 v2   | 2.80      | 15      | 30        | 256   | 22 nm      |

| Haswell         | Haswell         | E7-8890 v3   | 2.50      | 18      | 36        | 256   | 22 nm      |

| паѕмен          | Broadwell       | E7-8890 v4   | 2.20      | 24      | 48        | 256   | 14 nm      |

| Skylake         | Skylake         | E3-1885 v5   | 3.50      | 4       | 8         | 512   | 14 nm      |

| Knights Ferry   | Knights Ferry   | _1           | 1.20      | 32      | 128       | 512   | 45 nm      |

| Knights Corner  | Knights Corner  | Phi 7120P    | 1.24      | 61      | 244       | 512   | 22 nm      |

| Knights Landing | Knights Landing | Phi 7290F    | 1.50      | 72      | 288       | 512   | 14 nm      |

Table 2.1: Intel CPU architectures and trends

The recent trend in CPU architectures from Intel is presented in Table 2.1. It is apparent that the evolution of Intel processor architectures has been driven by the increased parallelism for the last decade. As the processor frequency is coming down to reduce power dissipation, the core count is kept increasing to meet the performance requirements using simultaneous multithreading (SMT), also known as hyper-threading which is a commercial trademark for Intel's proprietary implementation of SMT. The emergence of Intel Many Integrated Core architecture (e.g. Knights Corner, Knights Landing) featured with many lightweight cores (tens or even hundreds in near-future) is therefore an attempt to address the problem of improving the energy efficiency without compromising performance.

Also it can be noticed that Intel has given emphasis on achieving higher performance for multimedia and other data-parallel applications through introducing and extending SIMD architectures. Since the introduction of SIMD architectures on general purpose processors, the width of the SIMD registers (SIMD-width) has been increased gradually and now it has become 4-times greater than its initial width. This enhancement can potentially improve the performance of integer and double-precision floating point computations in video encoding, image processing, 3D modeling, scientific simulations, time-series and many other applications by up to 16- and 8-times respectively using Advanced Vector Extensions (AVX-512) instruction set. Moreover, the SIMD units are also augmented with special fused instructions (e.g Fused Multiply-Add, Fused Multiply-Subtract) to improve both performance and energy efficiency.

<sup>&</sup>lt;sup>1</sup>Product-name is not available, since it is not a commercial product.

#### 2.1.2 Dark Silicon and Heterogeneous Computing System

With the introduction of many- and multi-core architectures, the number of cores on die continues to increase to have enough parallelism for the future applications. However, as Dennard Scaling (i.e. scaling feature sizes and voltages by the same factor) can no longer be maintained with the increasing number of cores, power density (i.e. power consumption per unit area of silicon) continues to rise and is becoming a major limiting factor to the performance of future computing systems. Consequently, these trends might result in next generation chips having more on-chip resources (e.g. processing cores, hardware accelerators, cache blocks and so on) than what can be used simultaneously. In other words, due to the power and thermal limits, a significant fraction of these on-chip resources has to be turned off at any given point in time. This phenomenon is known as *dark silicon* [12, 13, 14]. The challenge is therefore how to make the best use of the abundance of transistors in the dark silicon era [32].

Several techniques have been proposed to mitigate the effect of *dark silicon*. Some of these techniques include near-threshold computing (i.e. operating at a very low voltage to power-on more cores) [33], selective boosting (i.e. satisfy performance requirements by executing boosted cores at the required frequencies for the entire boosting periods, while throttling down the other cores) [34], "Cherry Picking" [35] of cores (i.e. exploiting process variations to select a subset of cores, mapping threads to the selected set of cores and assigning operating frequencies to each core to maximize performance under power budget).

The *dark silicon* issue has also been studied in the context of Heterogeneous computing systems (i.e. systems with many different types of processing cores such as CPUs (Central Processing Units), GPUs (Graphics Processing Units), DSPs (Digital Signal Processors), ASICs (Application Specific Integrated Circuits) etc.). With the integration of specialized processing elements for different types of software applications, the system can dynamically select only a subset of the available processing elements depending on the workload characteristics. Such systems can provide substantial performance and power benefits over general purpose systems [36, 37]. General purpose processors coupled with reconfigurable devices are another promising form of heterogeneous systems that can mitigate the effect of the *dark silicon* phenomenon. Often such heterogeneous components can provide more efficient solutions than full software based solutions on general purpose processing elements. In this context, Microsoft is heading up deploying FPGA-accelerated nodes to improve the performance of computationally ex-

pensive operations in Bing's Indexserve engine [38]. However, the scope of this thesis is limited to Intel multi-core and many-core systems only.

# 2.2 Multi-core Computing

Multi-core and many-core computing architectures exhibit multiple levels of parallelism through a wide range of architectural features such as multithreading support using multiple cores and data-parallelism (per-core) using SIMD instructions. The effective exploitation of the underlying hardware is therefore crucial for achieving superior performance on current and future processors. For the last few years, researchers have been continuously developing new programming languages, language extensions and libraries to achieve the maximum efficiency by utilizing the modern processors. Here we briefly highlight the key features of some of the well known programming models.

#### 2.2.1 OpenMP

Open Multi-Processing (OpenMP) is the de-facto standard for shared memory programming [39]. It is featured with a set of compiler directives, environment variables and runtime library for explicitly expressing multithreaded parallelism. OpenMP uses fork-join based execution model. It can be classified as mid-level programming model as the implementation details of work-load partitioning, worker management and communication synchronization are kept hidden from the programmer. On the other hand, the programmer has the option to explicitly define scheduling, control the thread affinity, etc. Originally, OpenMP used to provide data-parallelism using these compiler directives. Since the release of OpenMP-3.0, it has started to support task parallelism as well [40].

#### 2.2.2 OmpSs

OmpSs is a task-based programming model and framework focused on supporting heterogeneous multi-core and many-core architectures [18]. This programming model puts an effort to glue the concepts of OpenMP and StarSs [41] together by extending the OpenMP features through incorporating support for asynchronous task-parallelism and heterogeneous architectures. Furthermore, it uses an extended memory model as well as threadpool execution model instead of fork-join model. Some of the new features of OpenMP 4.0 are inherited from OmpSs. OmpSs is built on top of Mercurium compiler and Nanos++ runtime system [42].

#### 2.2.3 TBB

Threading building blocks (TBB) is another popular C++ runtime library for parallel programming developed by the Intel Corporation [20]. It contains data structures and algorithms used to parallelize an application and to enhance performance on multi-core systems. TBB provides high-level abstraction as it hides the details about the threading mechanisms for performance and scalability. Threading building blocks introduces the concepts of task-stealing, recursive splitting etc. Task-stealing allows TBB to significantly reduce load imbalance as well as improve its performance scalability [43].

#### 2.2.4 MPI

Message Passing Interface (MPI) [44] is the dominant programming model for programming distributed parallel machines. It provides a comprehensive messaging API that can be used to communicate between processes that reside in separate address spaces. Typically, the optimal performance is achieved when each MPI process is mapped on a separate core. For easier coordination among processes, MPI interface provides functionality for communication, synchronization and virtual topology.

### 2.2.5 Cilk Plus

Cilk Plus is an extension to C/C++ to provide both task and data parallelism [45]. Though Cilk Plus evolved from Cilk, it differs from Cilk in different aspects such as support for loop, C++ language and constructs to solve data race problems. It features simple but powerful ways of specifying parallelism. Cilk Plus provides the \_Cilk\_spawn and \_Cilk\_sync keywords to spawn and synchronize tasks; \_Cilk\_for loop is a parallel replacement for sequential loops in C/C++. Tasks in the Cilk Plus environment are executed within a work-stealing framework. Every worker thread has deque<sup>2</sup> of tasks and the thread treats its deque as a stack, by pushing and popping tasks at the back of it. On the contrary, the thieves steal tasks from the front of the deques [46].

### 2.2.6 CUDA

CUDA (Compute Unified Device Architecture) is a set of C++ language extensions plus an accompanying runtime API for programming NVIDIA Graphics Processing Units (GPUs) [21]. This programming model is primarily developed for data parallel applications demanding intensive graphics

<sup>&</sup>lt;sup>2</sup>A double-ended queue

processing. However, it does not provide any viable interface for creating dynamic tasks or handling load balancing issues. Such support has to be entirely coordinated by the programmer. Nevertheless, it includes explicit memory management functions to assist programmers in extracting benefits from the underlying hardware.

CUDA allows programmers to launch large batches of SIMT (Single Instruction Multiple Thread) threads. These threads are hierarchically organized into warps, blocks, and grids, in which the finest thread group (e.g. a warp of 32 threads) runs the same set of instructions in SIMD fashion. Threads in a block are mapped into the same streaming microprocessor (SM) and execute the same kernel in lock-step fashion. Threads in different SMs may run different kernels without any performance penalty though. Finally, the thread-blocks in a grid are executed independently and in an arbitrary order.

## 2.2.7 OpenCL

OpenCL (Open Computing Language) is an open standard for parallel computing on heterogeneous architecture [47]. One of the main objectives of OpenCL is to increase portability across different platforms ranging from simple embedded micro-controllers to general purpose CPUs and massivelyparallel GPGPU hardware pipelines. To this end, OpenCL provides a top level abstraction to the low level hardware as well as consistent memory and execution models. Though OpenCL provides functional code portability, its performance is not always portable across different platforms [48, 49].

## 2.2.8 Parallel Haskell

Haskell is a pure functional programming language [50]. Haskell offers diverse extensions and libraries for developing parallel or concurrent programs. Some of the well-known extensions for developing parallel applications in Haskell are:

- Glasgow Parallel Haskell: an extension to provide thread-based semiexplicit parallelism on multi-cores [51].

- Accelerate: an embedded domain-specific language for programming the GPU [52].

- HaskellMPI, Glasgow Distributed Haskell, Eden, Cloud Haskell: to develop programs on distributed computing environment [53, 54].

| Programming<br>models | Memory<br>model        | Parallelism<br>model |              | Levels of<br>abstraction |

|-----------------------|------------------------|----------------------|--------------|--------------------------|

| models                | model                  | data                 | task         | abstraction              |

| OpenMP                | shared mem             | $\checkmark$         | $\checkmark$ | mid                      |

| OmpSs                 | shared mem             | $\checkmark$         | $\checkmark$ | mid                      |

| MPI                   | msg passing            | $\checkmark$         | $\checkmark$ | low                      |

| Cilk Plus             | shared mem             | $\checkmark$         | $\checkmark$ | mid                      |

| TBB                   | shared mem             | $\checkmark$         | $\checkmark$ | mid                      |

| OpenCL                | hierar. mem            | $\checkmark$         | $\checkmark$ | low                      |

| CUDA                  | hierar. mem            | $\checkmark$         | -            | low                      |

| Parallel Haskell      | shared mem/msg passing | $\checkmark$         | $\checkmark$ | high                     |

| SIMD                  | -                      | $\checkmark$         | -            | low                      |

Table 2.2: Summary of a few parallel programming models.

• Meta-par: aims to unify parallel heterogeneous programming using Eden, Cloud Haskell [55].

Table 2.2 briefly summarizes the features of some of the well-known parallel programming models.

# 2.3 Single Instruction Multiple Data Processing

In the recent years, support for fine grained data parallelism using SIMD instructions is becoming prevalent in virtually every processor in the market. Most of the computers today implement some form of SIMD instruction set. SIMD instructions provide higher performance, better energy efficiency and greater resource utilization [22]. Applications with potential for performance improvement using SIMD instructions are very common. However, despite the potential of SIMD instructions in developing energy efficient applications, modern compilers still do not have adequate auto-vectorization support for complex codes [29, 26]. Therefore, manual vectorization is often required to enhance code efficiency to a large extent.

## 2.3.1 SIMD Instruction Sets

MMX<sup>TM</sup>, Streaming SIMD Extensions (SSE) and Advanced Vector Extensions (AVX) are some of the examples of SIMD instruction sets supported by Intel. MMX<sup>TM</sup>, SSE, AVX and AVX512 support 64-bit, 128-bit, 256-bit and 512-bit vector computations respectively. 3DNow! of AMD, NEON of

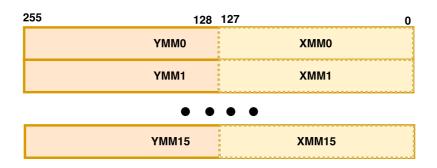

Figure 2.1: AVX register scheme as extension from the SSE (XMM0-XMM15)

ARM, AltiVec of IBM/Motorola are examples of SIMD instruction sets supported by other microprocessor vendors. However, here we briefly present the key features of different SIMD instruction sets for Intel architectures since our experiments have been conducted on Intel processors only.

## $MMX^{\mathsf{T}\mathcal{M}}$

The MMX<sup>TM</sup> instruction set was introduced in 1997 by Intel on Pentium processors. This instruction set uses 8 64-bit MMX registers and the operations are limited to integer values only. MMX is seldom used in modern processors; SSE and AVX are more commonly used SIMD instruction sets.

## **Streaming SIMD Extension**

Streaming SIMD Extension was introduced with the Pentium III processor in 1999 [56]. This instruction set uses 8 (xmm0 - xmm7) and 16 (xmm0 - xmm15) dedicated 128-bit XMM registers on 32-bit and 64-bit architectures, respectively. SSE supports single-precision floating point operations (but not double precision), and using XMM registers, it is possible to process four floating point number simultaneously. SSE2 introduced in 2000 on Pentium 4 extends SSE by adding support of double precision floating point and integer values (i.e. replaces MMX integer vector instructions) and added over 70 new instructions. SSE4.1, available since the introduction of Intel Penryn [57], consists of 47 instructions for media data manipulation such as Single- and double-precision dot product, streaming load, packed blending, packed integer min/max, sum of absolute differences for 4-byte blocks. SSE4.2 is first available in Nehalem-based Core i7 processors [58] and consists of 7 new instructions for text processing and some applicationspecific operations such as CRC32 (calculates cyclic redundancy check of a block of data) or POPCNT (counts the number of bits set in a word).

| 511   | 255   | 127 0 |

|-------|-------|-------|

| ZMMO  | ҮММО  | ХММО  |

| ZMM1  | YMM1  | XMM1  |

| • •   | • •   |       |

| ZMM31 | YMM31 | XMM31 |

Figure 2.2: AVX-512 register scheme as extension from the AVX (YMM0-YMM15) and SSE (XMM0-XMM15)

#### Advanced Vector eXtension

AVX is the next generation of the SIMD instruction sets supported from Intel Sandy Bridge (i.e. since 2011) processors [59]. It offers instruction sets for YMM registers. There are total 16 YMM registers (ymm0 – ymm15) in the CPUs and the size of each YMM register is twice (i.e. 256-bit) as big as the size of XMM register. The lower 128-bits of these registers are aliased to the respective 128-bit XMM registers. It is possible to perform simultaneous processing of eight single precision floating point numbers or four double precision floating point numbers on these registers. AVX register scheme is illustrated in Figure 2.1. AVX2 extends AVX by promoting most of the 128-bit SIMD integer instructions with 256-bit numeric processing capabilities. It also provides enhanced functionality for broadcast/permute operations, vector shift instructions with variable-shift count as well as support for fetching non-contiguous data elements from memory.

#### Advanced Vector eXtensions-512

The AVX-512 instruction set extends AVX to 512-bit. It was introduced in Intel's Xeon Phi x200 (i.e. Knights Landing in 2016) processor. Advanced Vector eXtension-512 uses 32 512-bit ZMM registers (zmm0 – zmm31) to enable processing of twice the number of data elements that AVX/AVX2 can process with a single instruction and four times that of SSE. It is further featured with 8 dedicated mask registers, a new set of blending instructions using mask registers, embedded rounding and broadcast operations, additional gather/scatter support, high speed math instructions (e.g. new fused multiply-add, exponential/reciprocal etc.). Figure 2.2 illustrates AVX-512 register scheme and Table 2.3 presents the evolution of SIMD instruction sets for Intel architecture.

| Year of      | SIMD      | Introduced           | Vector  | Major                                         |

|--------------|-----------|----------------------|---------|-----------------------------------------------|

| Introduction | Extension | in                   | size    | new features                                  |

| 1997         | MMX       | Pentium MMX          | 64-bit  | Integer arithmetic operations                 |

| 1999         | SSE       | Pentium III Katmal   | 128-bit | Single precision FP support                   |

| 2000         | SSE2      | Pentium 4 Willamette | 128-bit | Integer and double precision FP supports      |

| 2004         | SSE3      | Pentium 4 Prescott   | 128-bit | Complex arithmetic and graphics supports      |

| 2007         | SSE4.1    | Penryn               | 128-bit | Dot product and conversion                    |

| 2009         | SSE4.2    | Nehalem              | 128-bit | POP-count, CRC                                |

| 2011         | AVX       | Sandy Bridge         | 256-bit | Basic FP and elementary math operations       |

| 2013         | AVX2      | Haswell              | 256-bit | Extension of SSE(2/4) instructions to 256-bit |

| 2016         | AVX512    | Knights Landing      | 512-bit | 512-bit extensions to the 256-bit AVX(2)      |

Table 2.3: Evolution of SIMD extensions

## 2.3.2 SIMD Programming Methods

SIMD programming can be mainly done using three methods such as inline assembly [60], intrinsic function [61], and vector class [62].

## **Inline Assembly**

Inline assembly allows a programmer to handle almost every part of the program in order to gain maximum performance benefit from the system. However, writing assembly code is complicated and it demands cautious handling of data transfer between CPUs and memories. Listing 2.1 illustrates AT&T syntax based inline assembly codes [63] to perform summation of two arrays, where the name of the vector registers (e.g. *xmm0*) to be used with the opcodes are explicitly mentioned (e.g. *movups*).

```

1 asm volatile (

_2 "movups %1, %% xmm0 \n\t" //Move values from A[i] to

xmm0

"movups %2, %% xmm1 \n\t" //Move values from B[i] to

xmm1

3

4 "addps %% xmm0, %% xmm1 \n\t" //Add packed single-precision

floating-point values from xmm0 to xmm1.

"movups %% xmm1, %0" //Move values from xmm1 to C[i]

5

6

"= m" (C[i]) //=m indicates C[i] is an output and it is in

7

memory

8 :

"m" (A[i]), //m indicates A[i] is an input and it is in memory

9

10 "m" (B[i]) //m indicates B[i] is an input and it is in memory

11);

```

Listing 2.1: Inline assembly code to perform summation of two arrays.

## **SIMD Intrinsic**

SIMD intrinsic uses standard C/C++ language and thus coding is easier as compared to the coding with inline assembly. However, it comes with the

cost of not having any guarantee that the code is optimized to the highest level. Listing 2.2 shows SIMD intrinsic codes to sum-up two arrays. As we can see in the example listing, SIMD variables (e.g.  $xmm_A$ ) are used in the code rather than explicitly using physical register names.

```

1 __m128 xmm_A = _mm_load_ps(A);

2 __m128 xmm_B = _mm_load_ps(B);

3 __m128 xmm_C = _mm_add_ps(xmm_A, xmm_B);

4 __mm_store_ps(C, xmm_C);

```

Listing 2.2: SIMD intrinsic code to perform summation of two arrays.

#### **Vector Class**

Vector class is a library that encapsulate SIMD intrinsics for different hardware platforms behind a common interface. Compared to SIMD intrinsic functions, vector class is easier to program with. It also leads to more portable code. However, the downside of this model is that it provides lower performance than the other models. In Listing 2.3, the summation of two arrays is done using vector class. In the listing, the type F32vec4 in example is a class that encapsulates the intrinsic type  $\_m128$  which represents a 128-bit vector register holding 4 floating point numbers of 32 bits each. Moreover, instead of using SIMD instructions or assembly codes, the overloaded operators + are used to add the vectors. Therefore, the code is much easier to understand than the two other models.

```

1 F32vec4 vec_A;

2 F32vec4 vec_B;

3 F32vec4 vec_C;

4 loadu(vec_A, A);

5 loadu(vec_B, B);

6 vec_C = vec_A + vec_B;

7 storeu(C, vec_C);

```

Listing 2.3: Vector class code to perform summation of two arrays.

### 2.3.3 SIMD Optimization Techniques

The following section briefly covers the different performance optimization techniques using SIMD computations.

#### **Data Packing**

Using SIMD (e.g. SSE, AVX, AVX-512) instruction sets and their corresponding vector registers (e.g. 128-bit XMM, 256-bit YMM, 512-bit ZMM), one can pack multiple data into a single XMM/YMM/ZMM register. These data items can be processed simultaneously. Moreover, SIMD instruction sets also contain special instructions for frequently used- or critical-operations such as matrix transpose, square root, sum of absolute difference etc. to improve the performance even further.

### **Data Reuse**

Vector register space is increasing gradually in the modern processors (e.g. AVX-512 featured microprocessors have 32 ZMM registers representing 2 KB of register space). It is also possible to increase the performance of the SIMD code using data reuse. SIMD intrinsics or inline assembly allows a programmer to have control over this register space. Thus, a programmer can use inline assembly or intrinsics to reuse existing registers effectively so as to reduce unwanted data transfer.

### **Asynchronous Computation**

Data transmission along the memory hierarchy is a slow process. SIMD computation creates additional pressure to the memory hierarchy as it demands simultaneous accesses of more data elements than the scalar computation. Fortunately, this transmission process can be hidden to a certain degree using asynchronous computation, which is a technique to perform computation and data transmission simultaneously [64]. SIMD instructions provide some basic prefetching methods to provide support of asynchronous communication. Prefetching instructions provide hints to CPU for preloading the data into cache before the actual computation begins [65]. It is important to note that these instructions do not force the data to be preloaded into the cache. Thus it is not guaranteed that the data will be preloaded into the cache.

## 2.4 Data Compression

In modern processors, a significant amount of energy is consumed in the memory hierarchy due to data transmission. For instance, in Xeon Phi Knight's Corner (KNC) co-processor, caches are responsible for around 45% and 12% of the core power distribution for non-compute-intensive and compute-intensive applications, respectively [31]. Therefore, the use of application specific compression methods can increase the effective cache capacity, reduce cache misses and improve the performance and system energy. In this section, we present some of the most widely used loss-less integer compression techniques.

Some of the earliest integer compression techniques are Delta coding [66], Variable-byte (VarByte) coding [67], Rice and Golomb coding and Elias

Gamma coding [68]. Delta coding encodes integer numbers by subtracting successive values. The fundamental concept is to code the first value as it is. The remaining values are represented as the differences between successive values. A good compression ratio can be achieved by this approach if the differences between successive values are small. VarByte is a simple byte-oriented compression method. It uses a variable number of bytes to represent integer values (e.g. 34 is represented using 8 bits, 144 is represented using 16 bits). This compression technique is fast but it provides low compression ratio. Golomb and Rice coding are bit oriented coding schemes. In Golomb coding, an integer (i) is coded by quotient (q) and remainder (r) of division by the divisor (d). In case of *Rice coding*, the divisor used is a power of 2. These coding schemes provide good compression ratio for small integer values but the decompression speed is quite slow. In Elias Gamma coding, an integer (i) is encoded by its binary representation preceded by |log<sub>2</sub>i| zeros. This relatively slow technique provides good compression when small integers are more frequent than large integers.

In recent years, several fast compression techniques have been proposed, including the Simple family (S9, S16) [69], Frame Of Reference (FOR) or Patched Frame Of Reference (PFOR) [70]. *Simple9* encoding technique packs as many integers as possible in 32 bits (one word). This encoding technique is fast and provides better compression ratio than *VarByte. FOR* and *PFOR coding* compress a block of numbers at a time (e.g. 128 numbers). A fixed number of bits are used to encode each regular number in case of fixed-length encoding. The numbers that cannot be encoded using fixed length bits are considered exceptions and stored using 4 bytes. In *varint-G8IU* [71], a variable number of integers are encoded in 8 bytes. Once encoded, they are grouped together along with a 1-byte descriptor containing the unary representations of the lengths of each encoded integer. 8 data bytes can be used to encode from 2 to 8 integers depending on the size of the encoded integers. The number of integers is encoded by the number of zeros in the descriptor.

More recently, SIMD-based compression techniques have gained popularity. Stepanov et al. presented a taxonomy for variable-length integer encoding formats and presented a byte preserving integer encoding algorithm using SIMD instructions [72]. Schlegel et al. applied SIMD-based decompression algorithms to derive parallel versions of two well-known integer compression techniques: Null Suppression and Elias Gamma encoding [71]. In [73], Ao et al. proposed a linear regression-based parallelized compression technique for lists intersection. In [74], Zhang et al. proposed a parallel com-

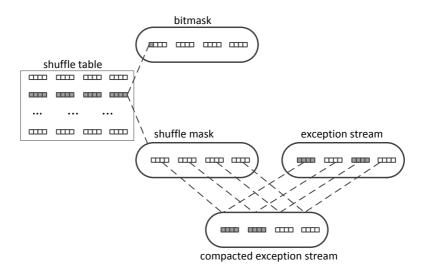

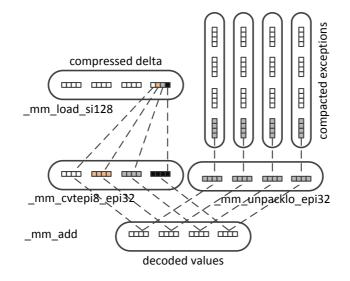

pression algorithm that aims to improve the instruction level parallelism by exploiting a 4-way vertical data layout format. Lemire et al. proposed a delta coding-based compression technique, *FastPFOR*, that uses vectorized binary packing over blocks of 128 integers [75]. This scheme stores the exceptions on a per page basis, but selects the base value *b* on a per block basis. They had shown that their approach is nearly twice as fast as the previously fastest schemes on desktop processors (*varint-G8IU* and *PFOR*). The authors have further extended their work by computing prefix sum using SIMD operations in their proposed algorithm [76].

# Chapter 3

# Methodology

This chapter discusses the methodology used to conduct this research work. This methodology involves choosing a set of applications to study, exploring different techniques for energy efficient computations and identifying suitable methods for estimating or measuring consumed energy on the target platforms. The rationale behind these selections are explained in this section. Section 3.1 lists the applications and benchmarks that are chosen and explains the reasons behind those selections. Then we discuss the programming languages and techniques that are taken into considerations during design space exploration in Section 3.2. Finally, the evaluation framework used for obtaining and analyzing the results is presented in Section 3.3.

# 3.1 Test Applications and Benchmarks

A selected set of applications and benchmarks are used in the different experiments presented in this research work. Here, we refer to an "application" as a program designed to perform a group of coordinated functions, tasks, or activities for the benefit of the user such as word processing program. On the other hand, a "benchmark" refers to a program or a set of programs that are commonly used in performance comparison of various subsystems across different chip/system architectures. LINPACK [77] is an example of a benchmark suite used to measure the floating point computing power of a system.

Selection of applications and benchmarks used in this thesis is primarily guided by the following two criteria.

• Research collaboration with industry and academia.

• Relevancy with the experiments as well as ease of integration with the framework.

Application set selection process is predominantly based on the research collaboration with the industry (e.g. Powel AS for Hydrological Timeseries) and internal research group (e.g. Boye Annfelt Høverstad et al. for Data cleansing). On the other hand, the selected benchmarks (FFTW, BlackScholes etc) are widely used, well known representatives of important real-world applications and can be integrated to our evaluation framework.

## 3.1.1 Benchmarks

1 dimensional FFTW (Fastest Fourier Transform in the West) kernel [78], BlackScholes from the PARSEC (Princeton Application Repository for Shared-Memory Computers) benchmark suite [79] and a tiled matrix-matrix multiplication routine [80] are chosen for evaluation.

## **1D FFTW**

The Fastest Fourier Transform in the West (FFTW) is a software benchmark that efficiently implements Discrete Fourier Transform [78]. The implementation takes advantage of the available vector units (e.g. SSE/SSE2/AVX, Altivec) on the underlying platform. Performance of FFT heavily depends on the design of the memory subsystem and how well it is exploited. In general, FFTW delivers reasonably good performance on all hardware due to its self tuning design. In the first step, it creates a plan of execution for the given problem, and then it executes the plan. The plan is chosen by heuristically tailoring execution to the current system (e.g. querying cache sizes), and several different plans are tested to find the fastest candidate.

## BlackScholes

BlackScholes is part of the PARSEC benchmark suite [79]. The PARSEC benchmark suite consists of a number of multithreaded applications representing both current and emerging workloads for multi-processing systems. Workloads in the benchmark cover different application domains (e.g. recognition, mining, synthesis and systems application), different parallelism granularity and exhibit different runtime behaviour. BlackScholes is considered as the simplest of all PARSEC workloads [81]. It uses Black-Scholes partial Differential Equation (PDE) to calculate the prices for a portfolio of European-style options. BlackScholes is a compute-bound workload, and its performance is limited by the amount of floating-point calculations a processor can perform.

### **Matrix Multiplication**

Matrix multiplication is widely used in many scientific and engineering applications. Double-precision GEneral Matrix-matrix Multiplication (DGEMM) is an important routine of the LINPACK benchmark [77], which is used to rank the top 500 supercomputers [82]. In this thesis, a tiled matrix multiplication algorithm is used. Matrices are decomposed into tiles of  $(M \times N)$  elements, and then the DGEMM routine is applied at the tile level. While there exist several basic linear algebra subprograms (BLAS) libraries (such as Intel Math Kernel Library, ATLAS and OpenBLAS) [83], we have used ATLAS (Automatically Tuned Linear Algebra Software) library for the optimized DGEMM routine [84]. Being a portable library, ATLAS automatically tunes itself to the underlying architecture to maximize performance. Furthermore, tiled matrix multiplication also suits very well to the worksharing constructs of parallel programming models like OpenMP, OmpSs etc.

## 3.1.2 Smart Grid Applications

## **Powel Hydrological Time Series Kernel**

Powel AS is one of the leading companies in Norway developing solutions to meet the requirements of Smart Grid applications [85]. These solutions contain computer programs and systems for maintaining maps over power lines and pipes, metering of electricity, inflow modeling and forecasting as well as power generation planning. Some of their developed products include [86]:

- Inflow forecasting and power inflow: A program to forecast, simulate and optimize hydropower generation process depending on weather forecasts, snow cover, ground and landscape conditions.

- Hydrometric simulations and Powel Sim/Shop:

- Powel sim: Short term hydropower planning software to calculate the consequence of a given plan by using inflow forecasts.

- Powel Shop: A program for short-term optimization of hydropower generation to find how to generate the contracted energy at the lowest possible cost.

- Powel MDMS: Powel meter data management system consists of programs for metering, maintaining and performing computations on different time series data.

In this thesis, we have studied Powel hydrological time series kernel, a part of Powel MDMS which is responsible for generating a summary series from a number of time series data given as input to the system. Each series  $(s_i)$  in the input dataset (ds) can be formally defined as,

$$\mathbf{ds} = \{s_i\}_{i=0}^{n-1}, s_i = (t_i, v_i, q_i)$$

where  $v_i$  represents the hydrological in-flow measured in  $m^3/sec$  at time  $t_i$ , and  $q_i$  represents the status information (e.g. valid or invalid data) for the measurement at time  $t_i$ .

The kernel takes two time series as inputs at a time and performs computations as it passes over the data points at each time instance, generating a new time series as output. Initially, it computes time axis **t** vector of the resultant series from the given inputs. Next, for each  $t_i$  in the resultant series, the kernel takes the corresponding  $v_i$  from the input series and computes  $v_i$  of the resultant series. Any missing value in the input series is estimated using linear interpolation. The corresponding  $q_i$  parameter is also updated to indicate that the value is interpolated. Finally, all the aforementioned steps are repeated until the entire dataset (**ds**) is processed.

Powel hydrological time series kernel is implemented in C++. It performs computationally inexpensive O(n) operations and the data access pattern is sequential. However, the kernel needs to process a huge volume of time series data, and consequently it becomes limited by the memory subsystem. Parallelism is handled at a higher level, serving multiple requests simultaneously, further increasing the pressure on the memory hierarchy.

## **Data Cleansing Application**

Data cleansing is a process of detecting and correcting or removing corrupted data in a dataset. Among the 4 different cleansing approaches (statistical methods, clustering, pattern based methods and association rules) [87], we studied a statistical method presented by Chen et al. in [88]. This algorithm is used in a research study to understand the impact of it as a pre-processing step for predicting loads in smart grids.

Data Cleansing model is based on the algorithm proposed by Chen et al. in [88]. The essence of the proposed solution to the detection of corrupted data is to model the intrinsic patterns or structure of load data. The model found can be used to judge the presence of abnormal deviations from the patterns, and thus to identify corruption of data. Assume that *n* data points  $(t_i, y_i)_{i=1}^n$  of a load curve have been collected. The underlying data generation process is modeled as a continuous function.

$$y_i = \mathfrak{m}(\mathfrak{t}_i) + \mathfrak{e}_i \tag{3.1}$$

where  $y_i$  is the data value at time  $t_i, m(t)$  is the underlying function and  $\varepsilon_i$  is the error term. It is assumed that the error term  $\varepsilon_i$  is normally and independently distributed with the mean of zero and constant variance  $\sigma^2$ . The main task is to find an appropriate estimate of the function m(t), namely  $(\hat{m})(t)$ , using the collected load data as a sample of observations. Then the point-wise confidence interval can be built based on the estimate of m(t). A data point is judged as corrupted if it locates outside the confidence interval. Corrupted data at t time will be replaced by the estimated value  $(\hat{m})(t)$ .

A smoothing parameter is used to control the curve smoothness. A smoother curve m(t) tends to model global patterns since it is less sensitive to local deviations, whereas a rougher curve m(t) is more capable of modeling local patterns. Different settings of the smoothing parameter can be chosen to model global or local patterns.

The basic idea of nonparametric smoothing is the local averaging procedure. Specifically, the curve can be estimated by

$$\hat{m}(t_{i}) = \frac{1}{n} \sum_{i=1}^{n} W_{i}(t) y_{i}$$

(3.2)

where  $\{W_i(t)\}_{n=1}^n$  denotes a sequence of weights which depend on the whole vector  $\{T_i\}_{n=1}^n$ . The idea is to approximate the function m(t) by taking a weighted sum or linear combination of a sufficiently large number K of basis functions  $\varphi_k(t)$

$$m(t_i) = \sum_{k=1}^{K} C_k \varphi_k(t)$$

(3.3)

where  $C = (c_1, c_2, ..., c_K)$  is the coefficient vector. To estimate coefficients **C** from the observations  $(t_i, y_i)_{i=1}^n$ , we define an *n* by *K* matrix

$$\Phi = \begin{vmatrix} \phi_{1}(t_{1}) & \phi_{2}(t_{1}) & \dots & \phi_{K}(t_{1}) \\ \phi_{1}(t_{2}) & \phi_{2}(t_{2}) & \dots & \phi_{K}(t_{2}) \\ \vdots & \vdots & \vdots & \vdots \\ \phi_{1}(t_{n}) & \phi_{2}(t_{n}) & \dots & \phi_{K}(t_{n}) \end{vmatrix}$$

(3.4)

A simple smoother could be obtained if the coefficients **C** are determined by minimizing the Sum of Squared Error (SSE) as

$$SSE = \sum_{j=1}^{n} \left| y_j - \sum_{k=1}^{K} C_k \varphi_k(t) \right|^2$$

(3.5)

$$m(t_{i}) = \sum_{k=1}^{K} C_{k} \varphi_{k}(t) = (\vec{y} - \Phi^{\mathsf{T}} \vec{c})^{\mathsf{T}} (\vec{y} - \Phi^{\mathsf{T}} \vec{c})$$

(3.6)

Now, the coefficients can be estimated by minimizing the penalized sum of squared errors (PENSSE). PENSSE is given by

$$\mathsf{PENSSE}_{\lambda} = (\vec{y} - \Phi^{\mathsf{T}}\vec{c})^{\mathsf{T}}(\vec{y} - \Phi^{\mathsf{T}}\vec{c}) + \lambda \vec{c}^{\mathsf{T}}\mathsf{R}\vec{c} \tag{3.7}$$

Then the coefficients  $\vec{c}$  can be estimated by setting the derivative of PENSSE with respect to  $\vec{c}$  to be zero

$$\hat{\vec{c}} = (\Phi^{\mathsf{T}} \Phi + \lambda R)^{-1} \Phi^{\mathsf{T}} \vec{y}$$

(3.8)

where  $\lambda$  is the smoothing parameter and  $R = \int D^2 \vec{\Phi}(t) D^2 \vec{\Phi}(t)^T dt$ .

Finally, the fitted value vector  $\hat{\vec{y}}$  is computed by

$$\hat{\vec{y}} = \Phi \hat{\vec{c}} = \Phi (\Phi^{\mathsf{T}} \Phi + \lambda R)^{-1} \Phi^{\mathsf{T}} \vec{y}$$

(3.9)

## 3.1.3 Applications from Different Domain

Apart from the aforementioned applications, we have also considered data mining (k-means) and multimedia (motion estimation) applications in our evaluation process.

## K-means Algorithm

K-means is one of the most widely used clustering methods. Among the different variants to this algorithm, we set our baseline as Lloyd's algorithm [89]. The advantage of this algorithm is its simplicity: starting with a set of randomly chosen initial centers, the kernel repeatedly assigns each input point to its nearest center, and then recomputes the centers given the point assignment. However, the algorithm is sensitive to its initialization process in obtaining a good solution. In [90], a randomized seeding technique is proposed to improve the accuracy and speed of k-means algorithm.

More recent works involve optimizing k-means computations using distance bounds and triangular inequality [91]. In [92], a fine-grained SIMD based approach is proposed which computes n distances from the n data points to the same centroid in one loop. In [93], Hadian and Shahrivari have used a KD-tree (k-dimensional tree) based structure where each node for the KDtree is represented by a bounding box specifying the minimal axis-parallel hyper-rectangle containing all associated points. Consequently, the search for nearest centroid is accelerated. In [94, 95], the authors proposed an algorithm that performs the distance calculations in parallel on the GPU while sequentially updating the cluster centroids on the CPU based on the results from the GPU calculations. In these optimization methods, parallelism is done at the task level, where the data is divided into smaller chunks and each chunk is processed in sub-tasks. All of these tasks execute the same logic as in the Lloyd's algorithm.

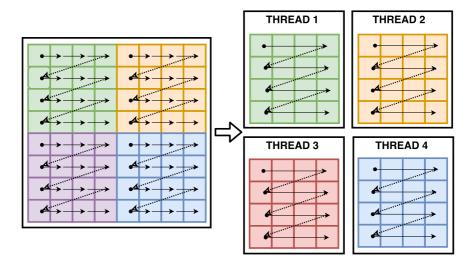

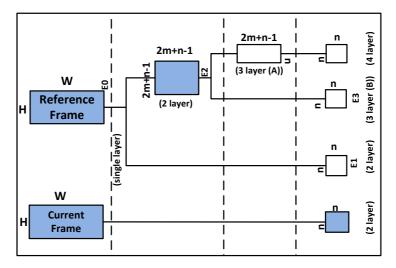

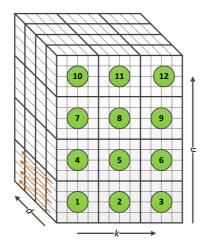

## **Full Search Motion Estimation**

Motion Estimation (ME) is a core part of different video compression algorithms. Block-based ME algorithms involve finding the candidate block within a specified search area in a reference frame that is most similar to the current block in the current frame. A "full-search motion estimation" algorithm performs an exhaustive search over the entire search region to find the optimal solution. This process is computationally intensive and costs about 80% of the video frame encoding time [96]. Therefore, it has been chosen as one of our test applications in the thesis.

# 3.2 Design Space Exploration

An important goal of this thesis is to improve performance and energy efficiency of a selected group of applications on multi-core and many-core platforms. To this end, we explored a number of state-of-the-art multi-core programming techniques (e.g. OpenMP, SIMD programming, optimized lib-

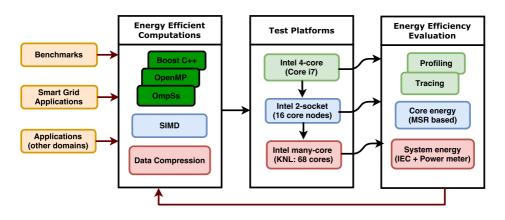

Figure 3.1: Research methodology to conduct this research

raries such as ATLAS, MKL) and followed some of the promising optimization strategies (e.g. loop transformation, code reorganization, blocking, lookup table usage) to port the selected set of applications and benchmarks onto modern multi-core desktop processing systems. While doing so, we focused on providing interesting insights on the effects of using these programming tools and techniques on applications' performance and energy efficiency. Essentially, we focused on addressing the research question 1 (RQ-1) at this point.