Olaf René Birkeland

# Searching large data volumes with MISD processing

Thesis for the degree doctor philosophiae

Trondheim, September 2008

Norwegian University of Science and Technology Faculty of Information Technology, Mathematics and Electrical Engineering Department of Computer and Information Science

#### NTNU

Norwegian University of Science and Technology

Thesis for the degree doctor philosophiae

Faculty of Information Technology, Mathematics and Electrical Engineering Department of Computer and Information Science

© Olaf René Birkeland

ISBN 978-82-471-1099-7 (printed version) ISBN 978-82-471-1100-0 (electronic version) ISSN 1503-8181

Doctoral theses at NTNU, 2008:207

Printed by NTNU-trykk

#### Abstract

Historically, supercomputing has focused on number crunching. Nonnumeric applications, such as information retrieval and analysis, have to a lesser extent been able to exploit the inherent resources of supercomputers. This thesis presents the results from the development of a novel multiple instruction, single data (MISD) architecture, targeting evaluation of complex queries in large data volumes. For such applications, this architecture provides a better price versus performance ratio, better use of the available memory bandwidth, lower power consumption, as well as linear scalability.

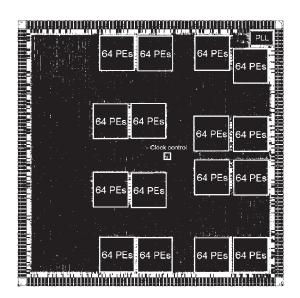

The core element of this technology is the Pattern Matching Chip (PMC). Each chip provides 1024 processing elements, with an accumulated performance of  $10^{11}$  operations per second. Multiple chips can be run in parallel with linear scalability, either within one computer, or in larger clusters. Up to half a million processing elements have been used in parallel in this project, providing  $5 \cdot 10^{13}$  operations per second at 48 GB per second data throughput, in a unit smaller than one cubic meter. Even larger systems can be constructed, still with linear scalability.

Through the novelty of this hardware architecture, the performance gained has enabled information processing in a way that would have been cost prohibitive with traditional computers. Such processing has demonstrated the capability of finding nuggets of valuable data in large and complex data volumes. The main effort — thus also the most important practical results — has been in bioinformatics. However, the technology has applicability in numerous other data mining applications.

## Preface

**T** HIS DISSERTATION is submitted to the Norwegian University of Science and Technology (NTNU) in partial fulfillment of the requirements for the degree of *Doctor philosophiae*. The dissertation contains seven papers, which will be referenced as Paper I through Paper VII, and one patent (see List of Papers on page xiii and List of Patents on page xv).

## Acknowledgement

Fortunately, my solitude position as a hardware developer within the Interagon team has been complemented by extremely skillful software developers. Without them, the result would only be a large numbers of transistors etched into silicon. Within Interagon, I would especially like to thank Magnar Nedland for his excellent analytical capabilities, his depth of hardware competence, and his ability to produce flawless software; Pål Sætrom as the mastermind in using genetic programming to tap the resources of the PMC; and Ola Snøve for moving to Oslo. Without the inspiration and guidance from Ola, I would not have started writing this thesis.

The Interagon team started as a project group within Fast Search & Transfer (FAST) in 1998, backed by professor Arne Halaas at NTNU. Arne has a long experience in data filtering that substantially accelerated our development. He has provided valuable suggestions and guidance throughout the entire project. FAST and Interagon should both be honored for having stamina in funding this research over such a long period of time. Interagon has been backed by NTNU's bioinformatics platform in the national functional genomics programme (FUGE). Furthermore, professor Lasse Natvig at NTNU deserves a large credit for reading through my manuscript and providing numerous valuable comments on the content.

I would also thank my co-authors for their contributions, including Ståle H. Fjeldstad, Thomas Grünfeld, Arne Halaas, Håkon Humberset, Magnar Nedland, Ola Snøve Jr., Børge Svingen, and Pål Sætrom. Finally, I would like give my greatest gratitude to my entire family, especially my wife Anne Ma and our children René and Ingrid, for their love and support. You demonstrate that working as a team is a lot more productive — not just when developing computer technology.

Olaf René Birkeland Oslo, April 25th 2008

iv

# Contents

| Prefac  | e iii                                                     |

|---------|-----------------------------------------------------------|

| Conte   | nts v                                                     |

| List of | Figures ix                                                |

| List of | Tables xi                                                 |

| List of | Papers xiii                                               |

| List of | Patents xv                                                |

| 1 Int   | roduction 1                                               |

| 1.1     | Aim of Study                                              |

| 1.2     | Thesis structure    2                                     |

| 1.3     | Research questions                                        |

| 1.4     | Research methods                                          |

| 1.5     | Contributions                                             |

| 1.6     | Paper Abstracts                                           |

| 1.7     | On joint authorship                                       |

| 1.8     | Supplementary material                                    |

|         | rdware aware optimizations in data search applications 13 |

| 2.1     | Background 14                                             |

|         | 2.1.1 The evolution of the x86 processor                  |

|         | 2.1.2 The evolution of memory technology                  |

| 2.2     | Sorting large arrays                                      |

|         | 2.2.1 Characteristics of search application at hand 20    |

|         | 2.2.2 Rearranging memory references                       |

|         | 2.2.3 In-place radix sort                                 |

|         | 2.2.4 Algorithm complexity                                |

|         | 2.2.5 Measuring the sorting throughput                    |

#### CONTENTS

|   | 2.3 | <ul> <li>2.2.6 Remarks on practical aspects</li></ul> | · · · · · · · · · | <ol> <li>28</li> <li>29</li> <li>29</li> <li>30</li> <li>32</li> <li>35</li> </ol> |

|---|-----|-------------------------------------------------------|-------------------|------------------------------------------------------------------------------------|

| 3 | Sea | iential data processing — in parallel                 |                   | 37                                                                                 |

| 0 | 3.1 | When indices fall short                               |                   | 37                                                                                 |

|   | 3.2 | Pattern matching without indices                      |                   | 39                                                                                 |

|   | 5.2 | 3.2.1 Dynamic programming                             |                   | 39                                                                                 |

|   |     | 3.2.2 Finite state machines                           |                   | 40                                                                                 |

|   |     | 3.2.3 Limitations with dynamic programming and        |                   |                                                                                    |

|   | 3.3 | Sequential data processing                            |                   | 42                                                                                 |

|   | 3.4 | Improving speed by parallel execution                 |                   | 42                                                                                 |

|   | 3.5 | Sequential access is aligned with technology trends   |                   | 43                                                                                 |

|   | 0.0 | sequential access is anglied with technology tiends   |                   | 40                                                                                 |

| 4 |     | Pattern Matching Chip                                 |                   | 45                                                                                 |

|   | 4.1 | Introduction                                          |                   | 45                                                                                 |

|   | 4.2 | Existing technologies                                 |                   | 46                                                                                 |

|   | 4.3 | Design goals                                          |                   | 48                                                                                 |

|   |     | 4.3.1 Linearly scalable architecture                  |                   | 48                                                                                 |

|   |     | 4.3.2 No preprocessing before analyzing data          |                   | 48                                                                                 |

|   | 4.4 | Previous architectures                                |                   | 49                                                                                 |

|   |     | 4.4.1 The F and H-matrices                            |                   | 49                                                                                 |

|   |     | 4.4.2 The MS160                                       |                   | 50                                                                                 |

|   | 4.5 | Implementation choices for the PMC                    |                   | 52                                                                                 |

|   |     | 4.5.1 Increasing parallelism                          |                   | 53                                                                                 |

|   |     | 4.5.2 Maintaining high data throughput                |                   | 54                                                                                 |

|   |     | 4.5.3 Balancing memory volume with processing         | 1                 | 56                                                                                 |

|   |     | 4.5.4 Memory interface                                |                   | 56                                                                                 |

|   |     | 4.5.5 Data distribution                               |                   | 56                                                                                 |

|   |     | 4.5.6 Processing elements                             |                   | 59                                                                                 |

|   |     | 4.5.7 Result processing                               |                   | 60                                                                                 |

|   |     | 4.5.8 System interface                                |                   | 60                                                                                 |

|   |     | 4.5.9 Query configuration                             |                   | 61                                                                                 |

|   | 4   | 4.5.10 Scalability                                    |                   | 61                                                                                 |

|   | 4.6 | Designing the PMC                                     |                   | 62                                                                                 |

|   |     | 4.6.1 Extensive acceptance testing                    |                   | 62                                                                                 |

|   |     | 4.6.2 Hardware and software co-development .          |                   | 63                                                                                 |

vi

#### CONTENTS

|   |     | 4.6.3     | ASIC and hardware system co-development          | 65 |

|---|-----|-----------|--------------------------------------------------|----|

|   |     | 4.6.4     | Final ASIC and full scale system tests           | 66 |

|   | 4.7 | Progra    | amming model                                     | 67 |

|   |     | 4.7.1     | Interagon Query Language (IQL)                   | 68 |

|   |     | 4.7.2     | Code compilation and mapping                     | 69 |

|   |     | 4.7.3     | Multi-threaded execution                         | 69 |

|   | 4.8 | Distan    | nce metrics                                      | 71 |

|   |     | 4.8.1     | One dimensional data                             | 71 |

|   |     | 4.8.2     | Multidimensional data                            | 71 |

|   |     | 4.8.3     | PMC distance metrics avoid expensive arithmetics | 74 |

|   | 4.9 | Result    | S                                                | 76 |

| 5 | Apr | olication | ns for the Pattern Matching Chip                 | 79 |

|   | 5.1 | Introd    | uction                                           | 79 |

|   | 5.2 |           | cteristics of suitable applications              | 80 |

|   | 5.3 |           | data mining                                      | 82 |

|   |     | 5.3.1     | Bioinformatics                                   | 83 |

|   |     | 5.3.2     | Digital network communication                    | 85 |

|   |     | 5.3.3     | Written text                                     | 85 |

|   | 5.4 | Vector    | data processing                                  | 86 |

|   | 5.5 |           | ic programming                                   | 87 |

|   |     | 5.5.1     | Methodology and issues with genetic programming. | 87 |

|   |     | 5.5.2     | Molecular biology                                | 88 |

|   |     | 5.5.3     | Financial fraud                                  | 88 |

|   |     | 5.5.4     | Seismic processing                               | 89 |

|   | 5.6 | Comm      | nonalities across application areas              | 90 |

| 6 | Eva | luation   | of results                                       | 93 |

|   | 6.1 | Summ      | nary of findings                                 | 93 |

|   |     | 6.1.1     | Better usage of available memory bandwidth       | 93 |

|   |     | 6.1.2     | Scalable parallel architecture                   | 94 |

|   |     | 6.1.3     | Low cost — high performance                      | 94 |

|   | 6.2 | Propos    | sitions to the research questions                | 95 |

|   | 6.3 |           | ation of the contributions                       | 97 |

|   |     | 6.3.1     | Summary of contributions                         | 97 |

|   |     | 6.3.2     | Comparison with state-of-the-art                 | 97 |

|   |     | 6.3.3     | Discussion                                       | 97 |

|   | 6.4 | Furthe    | er work                                          | 98 |

|   |     | 6.4.1     | Context save and restore                         | 98 |

|   |     | 6.4.2     | Spatial awareness beyond 1D                      | 99 |

| viii         | Contents |     |

|--------------|----------|-----|

| Glossary     |          | 101 |

| Bibliography |          | 107 |

| Papers       |          | 121 |

# **List of Figures**

| 1.1  | Relations between papers in this thesis                  | 6  |

|------|----------------------------------------------------------|----|

| 2.1  | Block diagram of the Intel 8086 processor                | 15 |

| 2.2  | Block diagram of the Intel Pentium4 (Prescott) processor | 16 |

| 2.3  | Historic development of the x86-family of CPUs           | 17 |

| 2.4  | Radix sort algorithm                                     | 21 |

| 2.5  | In-place radix sort example                              | 23 |

| 2.6  | In-place radix sort algorithm                            | 25 |

| 2.7  | In-place radix sort scalability                          | 27 |

| 2.8  | Half-adder                                               | 30 |

| 2.9  | Adding four bits with half-adders                        | 31 |

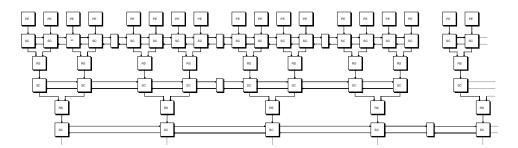

| 2.10 | Implementation of parallel bit-serial bit counting       | 33 |

| 0.1  |                                                          | 40 |

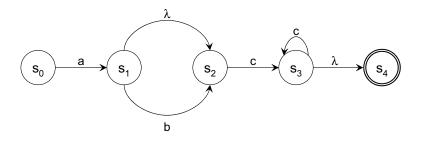

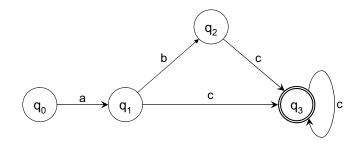

| 3.1  | NFA state machine accepting the pattern $ab?c+$          | 40 |

| 3.2  | DFA state machine accepting the pattern $ab?c+$          | 40 |

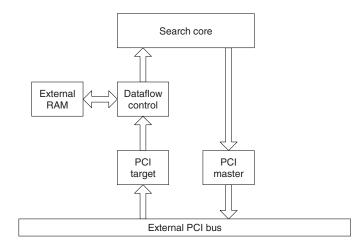

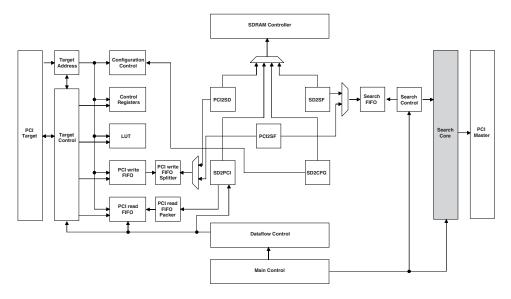

| 4.1  | MS160 block diagram                                      | 50 |

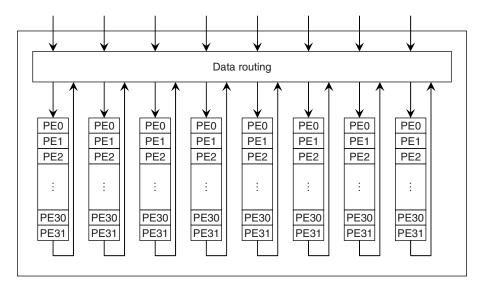

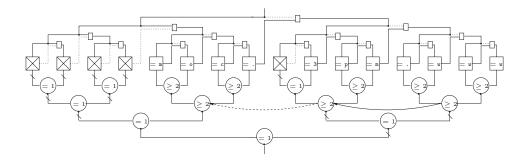

| 4.2  | High level PMC block diagram                             | 53 |

| 4.3  | Data distribution for a small query                      | 57 |

| 4.4  | Detail level PMC block diagram                           | 58 |

| 4.5  | PMC search core data distribution                        | 58 |

| 4.6  | PMC search core result processing                        | 59 |

| 4.7  | PMC FPGA test jig                                        | 64 |

| 4.8  | PMC ASIC test jig                                        | 67 |

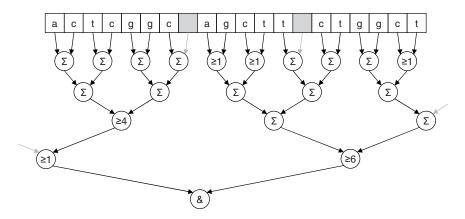

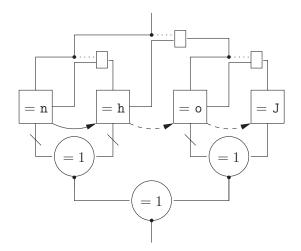

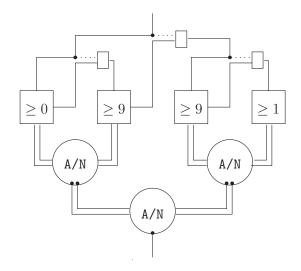

| 4.9  | Mapping of a siRNA query                                 | 70 |

| 4.10 | Multithreading of query evaluation                       | 70 |

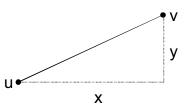

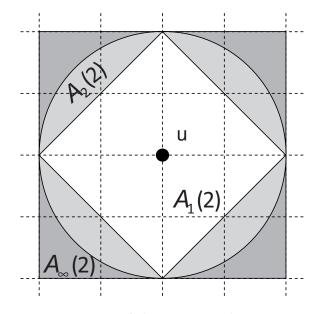

| 4.11 | 2D distance decomposition                                | 72 |

| 4.12 | Comparison of Minkowski metrics in 2D                    | 73 |

| 5.1  | PMC search card                                          | 80 |

| 5.2  | Cluster of PMC-accelerated machines                      | 81 |

| 5.3  | Deriving data from music for PMC-enabled searching       | 86 |

| 2.0  |                                                          | 00 |

| List of Figures |

|-----------------|

| List of Figures |

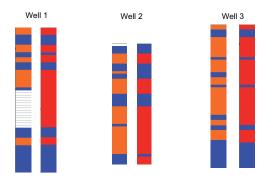

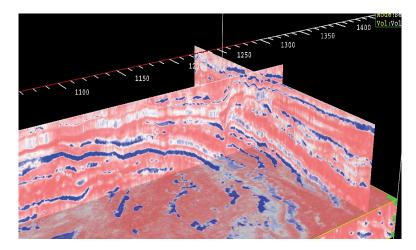

| 5.4 | Test wells for lithology training    | 90 |

|-----|--------------------------------------|----|

| 5.5 | Predicted properties of seismic cube | 91 |

х

# List of Tables

| 1.1 | Relations between papers and contributions       | 5  |

|-----|--------------------------------------------------|----|

|     | Performance development for DRAM devices         |    |

| 4.1 | Technical data for different string search ASICs | 76 |

| 5.1 | Comparison of siRNA screening capabilities       | 83 |

## **List of Papers**

- Paper I Arne Halaas, Børge Svingen, Magnar Nedland, Pål Sætrom, Ola Snøve Jr., and Olaf René Birkeland. A recursive MISD architecture for pattern matching. Published in *IEEE Trans. on* VLSI Syst., 12(7):727–734, 2004.

- Paper II Olaf René Birkeland, Ola Snøve Jr., Arne Halaas, Magnar Nedland, and Pål Sætrom. The petacomp machine — A MIMD cluster for parallel pattern-mining. 2006 IEEE International Conference on Cluster Computing. In proceedings.

- **Paper III** Ola Snøve Jr., Håkon Humberset, Olaf René Birkeland, and Pål Sætrom. Sequence Explorer: interactive exploration of genomic sequence data, 2005. Manuscript.

- **Paper IV** Ola Snøve Jr., Magnar Nedland, Ståle H. Fjeldstad, Håkon Humberset, Olaf René Birkeland, Thomas Grünfeld, and Pål Sætrom. Designing effective siRNAs with off-target control. Published in *Biochem. Biophys. Res. Commun.*, 325(3):769–773, 2004.

- **Paper V** Olaf René Birkeland, Magnar Nedland, Ola Snøve Jr. Massively parallel MIMD system achieves high performance in a spam filter. Presented at *Parallel Computing* 2005. In proceedings.

- Paper VI Pål Sætrom, Olaf René Birkeland, Ola Snøve Jr. Boosting improves stability and accuracy of genetic programming in biological sequence classification Presented at *Genetic Programming Theory and Practice* 2006. Published as book chapter in *Genetic Programming Theory and Practice IV* by T. Soule and R. Riolo and W.P. Worzel (editors), Springer, 2007.

- Paper VII Olaf René Birkeland, Ola Snøve Jr. The Pattern Matching Chip Technical whitepaper for Interagon AS, 2002

# **List of Patents**

**Patent I** Børge Svingen, Arne Halaas and Olaf René Birkeland. A processing circuit and a search processor circuit. International patent PCT/NO99/00344, 1999

This patent is not enclosed in the printed version of this thesis. It can be obtained at http://v3.espacenet.com/origdoc?RPN=WO0029981

# Chapter 1

# Introduction

**T** HIS doctoral thesis discusses searching through large data volumes with multiple instruction, single data (MISD) processing. In order to test the applicability of this approach, a custom processor was designed and implemented, called the Pattern Matching Chip (PMC). Throughout this thesis I will describe the reasoning behind the PMC's construction, and how this architecture was able to efficiently solve demanding non-numeric applications.

## 1.1 Aim of Study

The overall aim of this research was to investigate and design methods for searching though large volumes of data. The initial work focused on an index based search system, with construction of new algorithms for efficient processing of the related data structures. As index based systems have limitations in the type of queries that can be handled, the focus was switched to processing unstructured data natively. Although no common definition of *unstructured* data exists, the term is used in this thesis to cover any kind of data where no efficient indexing scheme is known.

The main part of this research has been to identify, design and test a novel MISD architecture for processing unstructured data. The hypothesis of this being an efficient way for processing came from the observed unsuitability of SIMD architectures to parallelize such processing. It is important to note that this work does not claim to replace index based systems in general. This thesis will discuss a subset of search applications where indexing has several disadvantages, and where the proposed architecture is shown to be more appropriate.

In a MISD architecture, multiple parallel searches are executed on a

#### Introduction

smaller number of data streams. In the extreme case, there is one shared data stream, originating from a high bandwidth source. The speed of sequential data transfer bandwidth has historically scaled better than other storage technology performance parameters (Patterson 2004). Architectures based on sequential rather than random memory access can thus more readily exploit memory technology improvements.

Further, MISD processing presents a different way of algorithm construction. Evaluating this approach is only possible by formulating new algorithms specifically for the PMC. These algorithms can be benchmarked versus exiting methods solving the same tasks. Our research has demonstrated the applicability of the PMC across multiple application areas.

Throughout all the papers and underlying work, my main contributions on the hardware side have been within designing the processor and system architecture, and identifying feasible implementations. The latter includes everything from ASIC development, to handling the production of the final systems. A lot of effort has been put into making the system as general as possible, enabling multiple application usage cases. On the software side, I have worked on overall algorithm design, and finding effective mappings from the problem domains onto the PMC feature set.

## **1.2** Thesis structure

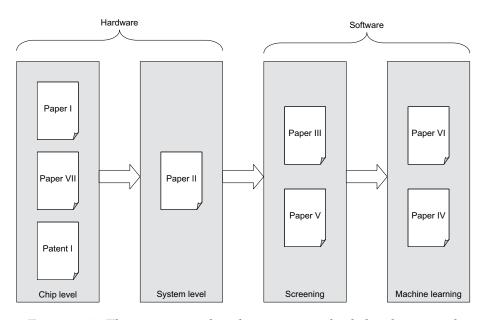

This thesis includes seven papers and one patent as the main contributions. The papers will be referenced as Paper I through Paper VII, as defined in the List of Papers on page xiii. Reprints of the original papers are attached at the end of this thesis. The relations between the papers are shown in figure 1.1.

The introduction to this thesis provides the overall structure of the document. Chapter 2 describes work done in bridging the architectural gap between software algorithms, the CPU and system memory in index systems. From this work it became evident that the random access pattern exhibited by many algorithms was not optimal for the most common semiconductor memory technology, dynamic RAM (DRAM). Chapter 3 discusses a somewhat unconventional approach for searching large volumes of data through parallel searches across multiple sequential fragments. This approach brought up a number of data processing applications, for which a traditional CPU would not be a good solution. This led to the creation of the PMC, as described in chapter 4. Chapter 5 describes how this technology was used in different applications. The last chapter summarizes the findings of the research, providing some ideas for further work.

## **1.3 Research questions**

The following is a list of the most important research questions behind this thesis. The propositions to these questions will be summarized in section 6.2.

**RQ1** What are the system requirements for doing unstructured data processing efficiently?

The main focus for computer performance is on calculation throughput, FLOPS, exemplified by the constant competition for inclusion in the Top500 ranking (http://www.top500.org). Computers are to an increasing extent being used for handling "information", rather than crunching numbers. This might need more attention to other aspects than calculation performance, for example data bandwidth.

**RQ2** What are the constraints for processing unstructured data with standard CPU technologies?

Off-the-shelf computer hardware has very good availability and affordability. The generic computer is although a tradeoff in functionality to enable a fit with as many application categories as possible. Is the *central* processing regime also suitable for unstructured data processing? Could such processing be served better with a more distributed system?

**RQ3** *Can other processing architectures than* SIMD *provide better performance for unstructured data processing?*

SIMD (single instruction, multiple data) is currently the most common CPU architecture in personal computers and servers. This is a good fit for many computational intensive applications, where the same operation is applied to more than one data element. For example, all the components of a vector might be scaled with the same factor, regardless of their value. Otherwise, if the flow of operations is dependent on the data values — an important feature for unstructured data processing — , it would be hard to take advantage of the parallelism in a SIMD architecture.

**RQ4** *What are the obstacles for massively parallel systems in unstructured data processing?*

Massively parallel systems have scalability limited by Amdahl's law. Furthermore, large numbers of processors are likely to have high power consumption and space requirements, not only for the system Introduction

itself, but also the associated cooling systems. What aspects of unstructured data processing can be exploited to overcome — or lessen the impact of — these aspects?

**RQ5** What applications could benefit from unstructured data processing?

Although researching new technology has a value by itself, improvements in solving real problems are needed for long term sustainability. What existing application classes could benefit from such processing? Does a novel technology approach enable new opportunities?

### **1.4 Research methods**

The research process leading to this thesis has gone through several phases, requiring different methodologies. The initial work for processing unstructured data on regular CPUs consisted mainly of research, development and testing of small prototypes for critical code sections. These served as tools for better understanding of the bottlenecks in such systems.

This first phase suggested that the SIMD architecture was not a good fit for the applications under investigation. Thus the next phase included a study of existing literature on alternative technologies. A MISD architecture was in theory a good fit, but lagged behind the other alternatives in terms of existing research and deployment. Furthermore, we wanted a degree of parallelism not previously tested in existing studies. Thus most of the proposed ideas for a MISD architecture could only be simulated on existing hardware.

To identify if this architecture and parallelism imposed limitations overseen by theoretical estimations, the third phase was to identify, design and construct such an MISD processing device, the PMC, and the surrounding hardware and software systems. This phase is further described in chapter 4.

Armed with this technology, the fourth and final phase consisted of extensive benchmarking of the novel architecture in several applications; both synthetic scenarios — and in my opinion more importantly — real world applications.

## 1.5 Contributions

The main contributions of this thesis are:

4

|           |    | С  | ontril | butio | ns |    |

|-----------|----|----|--------|-------|----|----|

| Paper     | C1 | C2 | C3     | C4    | C5 | C6 |

| Paper I   | ٠  | ٠  | ٠      | ٠     |    |    |

| Paper 11  |    | ٠  | ٠      | ٠     |    | ٠  |

| Paper III |    | ٠  |        |       |    | ٠  |

| Paper IV  |    | •  |        |       |    | •  |

| Paper v   |    | •  | ٠      | ٠     |    | •  |

| Paper VI  |    |    |        |       |    | •  |

| Paper VII | ٠  |    |        |       |    |    |

| Patent I  | •  |    |        |       | •  |    |

Table 1.1: Relations between papers (see section 1.6) and contributions (see section 1.5).

- **C1** Development of the Pattern matching Chip (PMC), an MISD architecture parallel processor implemented as an ASIC

- **C2** A scalable system architecture, with proven operation of 500,000 parallel processing elements at near 100 % utilization.

- C3 A parallel processing architecture with low infrastructure requirements.

- **C4** A power efficient design, with power consumption at par with or better than alternative technologies.

- C5 Patenting of the PMC architecture

- **C6** Research, development and benchmarking of selected applications for the PMC architecture.

The merits of the research are presented in the enclosed papers, while chapter 2 through 6 rather provides the context of the overall work. Given the diversity of topics covered in the papers, all details will not be reiterated in these chapters. Table 1.1 summarizes the relations between the papers and the respective contributions.

## **1.6** Paper Abstracts

Paper I and Paper IV have appeared in peer-reviewed scientific journals. Paper V and Paper VI have been presented at scientific conferences. Pa-

Figure 1.1: The papers in this thesis present both hardware and software aspects of our work. Paper I, Paper VII and Patent I describe research and design of the chip level technology. The cluster level system is covered by Paper II. Paper III and Paper V present the usage of this cluster when screening for occurrences of predefined patterns. Finally, Paper IV and Paper VI explain how the same cluster can be used for accelerating genetic programming.

per VI will also be published as a book chapter with Rick Riolo as editor. Paper II has been accepted for conference presentation in September 2006. Paper III has been submitted for publication, but not yet accepted. Paper VII is a technical note. More detailed information on each paper can be found in the List of Papers on page xiii.

The patent has been filed in the European EP system and 13 additional countries. The patent has so far been granted by 6 of these 14 patent bodies, with 8 countries still pending. Due to the volume of the patent (107 pages), it is not reprinted in this thesis. A version can be found for downloading at the address given in the List of Patents at page xv. The patent is a formalization of the material in Paper I and Paper VII, thus reading the entire patent is not required for an understanding of the work behind this thesis.

The following list of abstracts is taken from the papers and patent related to the research in this thesis.

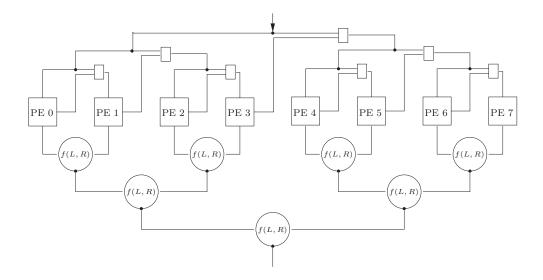

- **Paper I** *A recursive* MISD *architecture for pattern matching.* Many applications require searching for multiple patterns in large data streams for which there is no preprocessed index to rely on for efficient lookups. A multiple instruction stream-single data stream (MISD) VLSI architecture that is based on a recursive divide and conquer approach to pattern matching is proposed. This architecture allows searching for multiple patterns simultaneously. The patterns can be constructed much like regular expressions, and add features such as requiring sub-patterns to match in a specific order with some fuzzy distance between them, and the ability to allow errors according to prescribed thresholds, or ranges of such. The current implementation permits up to 127 simultaneous patterns at a clock frequency of 100 MHz, and does  $1.024 \times 10^{11}$  character comparisons per second.

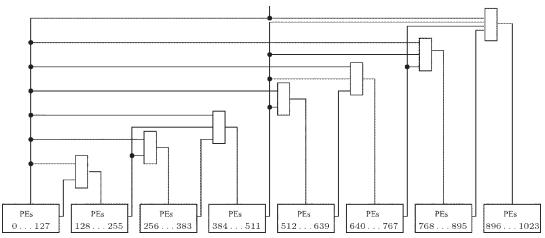

- **Paper II** *The petacomp machine A* MIMD *cluster for parallel pattern-mining.* Multiple instruction stream-single data stream (MISD) architectures have not found many practical applications in supercomputing. We present a multiple instruction stream-multiple data stream (MIMD) cluster implementation that uses MISD search processors with extreme pattern mining performance as a building block.

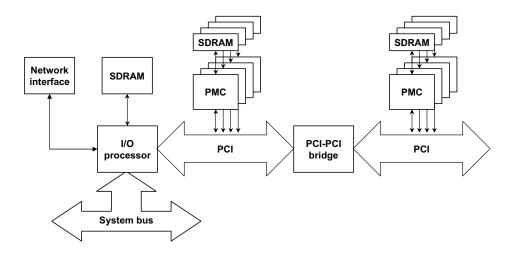

We use PCI cards that hold sixteen search processors with local memory to build a relatively small cluster of five PC nodes with six PCI cards each. This cluster can handle anything between 64 independent queries at 48 GB per second, to 30,720 independent queries at 100 MB per second.

#### Introduction

The cluster's performance characteristics are such that we can easily scale the system to  $10^{15}$  operations per second with containable overhead using just 100 nodes. Further, the solution has lower power consumption and memory bandwidth requirements than comparable technologies.

- **Paper III** Sequence Explorer: interactive exploration of genomic sequence data. Current solutions for complex motif searching in DNA and protein sequences are not interactive as users usually wait tens of seconds before the results can be viewed. We propose a hardware-accelerated client-server solution that is fast enough to retain the interactive feeling even when screening whole genomes. We structured our framework for interactive sequence analysis around query, dataset, filter, and result presentation modules. The query and dataset specification enable simultaneous, interactive screening of multiple complex queries against several datasets. The filters impose restrictions such as only allowing hits to be reported if they occur in coding regions, and the different result presentations include histograms and hit lists. Our results show that interactive searching is possible even though response times vary significantly depending on filter, network bandwidth and hit frequencies. With a relatively small server, we obtain response times of about one and a half second on gigabytes of data when queries are sufficiently complex to avoid network bottlenecks due to high hit frequencies.

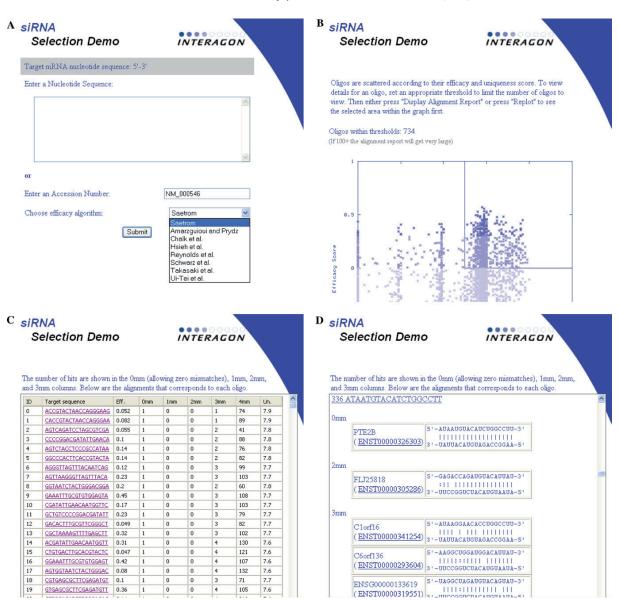

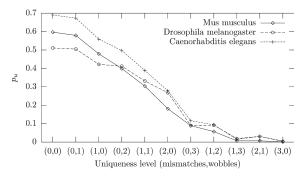

- **Paper IV** *Designing effective siRNAs with off-target control.* Successful gene silencing by RNA interference requires a potent and specific depletion of the target mRNA. Target candidates must be chosen so that their corresponding short interfering RNAs are likely to be effective against that target and unlikely to accidentally silence other transcripts due to sequence similarity. We show that both effective and unique targets exist in mouse, fruit fly, and worm, and present a new design tool that enables users to make the trade-off between efficacy and uniqueness. The tool lists all targets with partial sequence similarity to the primary target to highlight candidates for negative controls.

- **Paper v** *Massively parallel MIMD system achieves high performance in a spam filter.* Supercomputer manufacturing is usually a race for floating point operations, and must therefore opt for a design that allows for the highest possible clock frequency. Many modern applications are, however, limited not only by the number of operations that can be performed on the data, but by the available memory bandwidth. We

review the main features of a MISD architecture that we have introduced earlier, and show how a system based on these chips is able to scale with respect to query and data volume in an email spam filtering application. We compare the results of a minimal solution using our technology with the performance of two popular implementations of deterministic and nondeterministic automatons, and show how both fail to scale well with neither query nor data volumes.

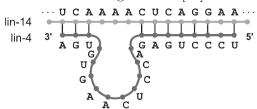

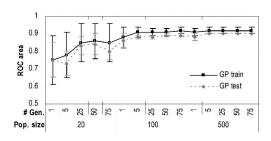

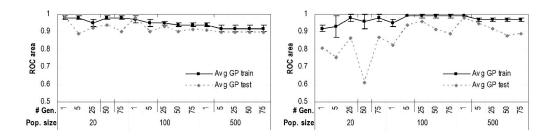

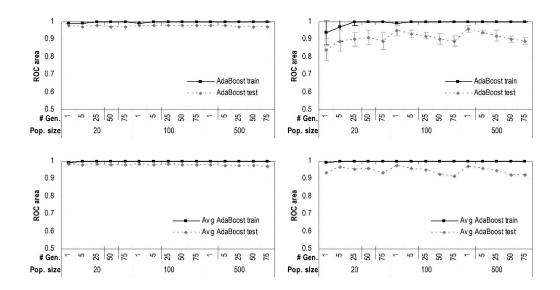

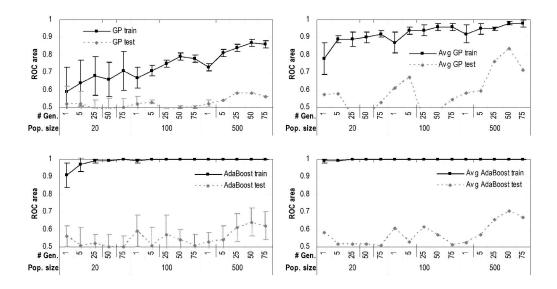

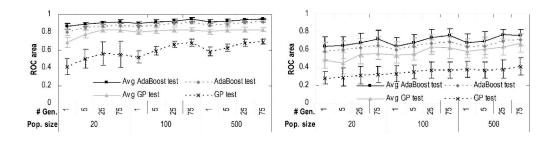

- **Paper VI** *Boosting improves stability and accuracy of genetic programming in biological sequence classification.* Biological sequence analysis presents interesting challenges for machine learning. Using one of the most important current problems the recognition of functional target sites for microRNA molecules as an example, we show how joining multiple genetic programming classifiers improves accuracy and stability tremendously. When moving from single classifiers to bagging and boosting with cross-validation and parameter optimization, you require more computing power. We use a special-purpose search processor for fitness evaluation, which renders boosted genetic programming practical for our purposes.

- **Paper VII** *The Pattern Matching Chip.* The Pattern Matching Chip (PMC) is an Application Specific Integrated Circuit (ASIC), capable of searching for advanced patterns in arbitrary data at a constant high speed. The PMC is based on breakthroughs made by researchers at the Norwegian University of Science and Technology (NTNU), who have devoted more than 15 years into developing ASICs for approximate searching. With a clock frequency of 100 MHz, the PMC is able to search with up to 64 distinct queries on 100 MB of data per second.

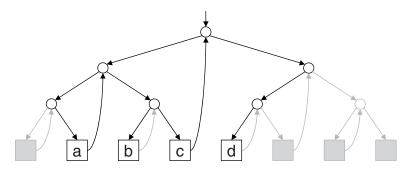

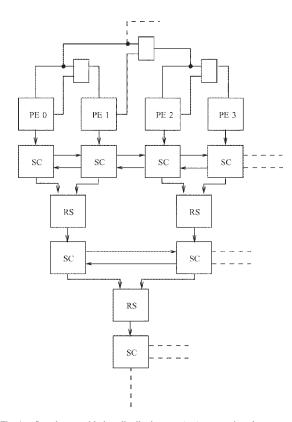

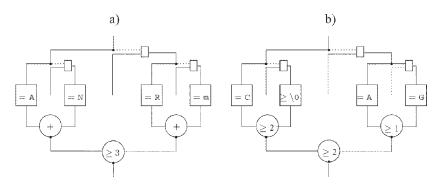

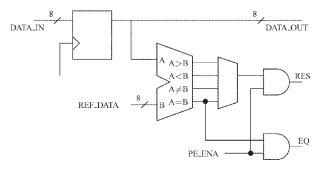

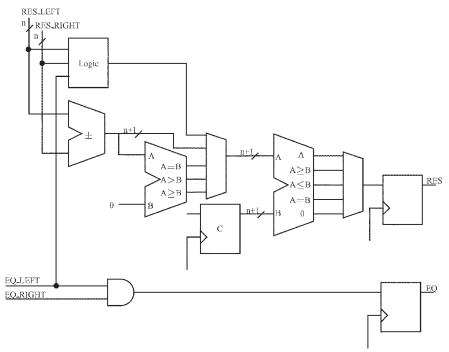

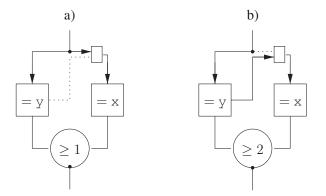

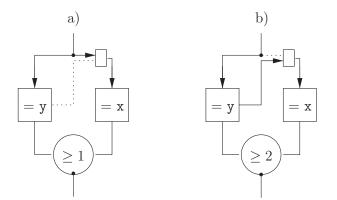

- **Patent I** *A processing circuit and a search processor circuit.* A processing circuit  $P_1$  for recognition and comparison of complex patterns in high speed data streams can form a node in a network of circuits of this kind and comprises an interface for inputting of parameters for the circuit, at least one kernel processor  $P_0$  in the form of a comparator unit (COM) for comparing two data words, a logic unit (E) connected with the comparator unit and comprising a multiplexer (MUX1), a first D flip flop (2), a latency unit (LAT) for delaying a positive binary value with a given number of time units, a second D flip flop (4), a sequence control unit (SC) which monitors and controls a comparison operation in the comparator unit (COM), and a result selector (RS) which combines two result values from other processing circuits or other result selectors.

Introduction

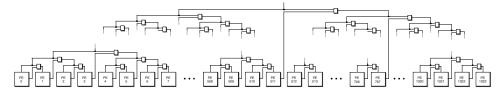

A search processor circuit (PMC) for performing search and comparison operations on complex patterns comprises a multiprocessor unit  $P_n$  with processing circuits  $P_1$  in a tree structure and forms a binary or superbinary tree with n + 1 levels S and degree k = 2m, m being a positive integer  $\geq 1$ . An underlying level  $S_{n-q}$  generally comprises  $2^{mq}$  circuits  $P_{n-q}$  provided nested in the  $2^{m(q-1)}$  circuits  $P_{n-q+1}$  on the level  $S_{n-q+1}$ . A 0th level  $S_0$  defined for q = n in the unit  $P_n$  comprises  $2^{m(n-1)}$  to  $2^{mn}$  kernel processors  $P_0$  which form comparator units (COM) in the circuits  $P_1$ . All circuits  $P_1, P_2 \dots P_n$  have identical interfaces (I) and a logic unit (E) with a result selector (RS) for collecting the results of a search operation or a comparison operation. Use in search engines for search and retrieval of data stored in data bases.

## 1.7 On joint authorship

All papers and patents building the base for this dissertation origin from collaborations with several other people, bringing together a multidisciplinary team, with each member contributing with unique competence in our respective fields.

The papers and patents are listed on page xiii and xv respectively. My specific contributions beyond co-writing all of the manuscripts are as follows:

- **Paper I** Contributed to the architecture research for the PMC, identified suitable solutions for implementation, headed the research project.

- **Paper II** Researched the cluster architecture, evaluated the resulting performance, identified potential system enhancements.

- **Paper III** Defined requirement specifications, researched implementation optimizations, and wrote the user tutorial.

- **Paper IV** Contributed to the research on methodology, especially on ensuring efficient usage of the PMC.

- **Paper v** Identified workload distribution scheme, performed performance comparisons.

- Paper VI Contributed to methods.

- **Paper VII** Selected topics to be presented. Researched selection of processing element functions to provide both any Boolean function as well as higher order functionality.

Patent I Contributed to the architecture research for the PMC

# 1.8 Supplementary material

I have written a tutorial on usage of the screening application described in Paper III. This tutorial is available upon request.

# Chapter 2

# Hardware aware optimizations in data search applications

Grove giveth and Gates taketh away

Robert Metcalfe (1946 - )

THERE is a large gap between the increments in raw compute speed and the resulting application level benefits. While the semiconductor industry has been able to keep on track with Gordon Moore's predictions, often referred to as "Moore's law", providing a doubling in the number of transistors on an integrated circuit every 18 months, all of this added compute power has not been harnessed.

This chapter will describe some of the most important issues that prevent applications from getting full advantage of hardware improvements. The discussion will focus on two main aspects. First, the widening gap in performance between processing and memory (Wilkes 2001); secondly — and perhaps even more important — the resulting effects when this memory gap and other feats of a modern processor are not top priorities within the general programmer community. For most applications, advanced compilers can help bridging the technology gap (Tian et al. 2005). For data intensive algorithms, the programmer can use hardware awareness to gain large improvements (Eichenberger et al. 2005). These aspects will be illustrated by examples taken from the implementation of an index based web search engine, described in more detail in Risvik (2004).

The examples presented in this chapter are taken from work done in the construction of commercial program code in 2000, and are not previously published. The proposed solutions are more an illustration of achievable improvements through CPU-aware programming, than claiming to be the

state-of-the-art algorithms in their respective fields. The main purpose of this chapter is to describe the difficulties in getting decent performance from a SIMD architecture applied to algorithms with a data dependent instruction flow. These findings provided motivation and inspiration for developing an application targeted processor architecture, which will be described in the following chapters.

## 2.1 Background

Modern approaches to programming agree that code optimization should wait until a profiler reports a performance bottleneck in the application. The 20-80 rule applies to all stages of software development, meaning that large portions of a programmer's time and a program's runtime are spent on relatively small parts of the total volume of code (see for instance Beck 2001, for a discussion of these topics). Programmers should therefore write comprehensible code that implements simple designs rather than opting for complex solutions that often turn out to have only a marginal effect on the application's performance.

Add to the aforementioned arguments that today's compilers often outsmart the average programmer when it comes to local optimizations, and it may seem like it is all a matter of selecting the best algorithm with respect to theoretical complexity and memory requirements. This is not the case. Critical parts of the code, as identified by performance profiling, may benefit significantly from architecture-dependent code optimizations.

#### 2.1.1 The evolution of the x86 processor

One of the most widespread processor architectures is based on the Intel 8086 processor from 1978, also referred to as the x86 architecture. This architecture will be used as an example throughout this chapter. Although several other architectures exist, modern x86 implementations incorporate much of the same concepts found in other processors.

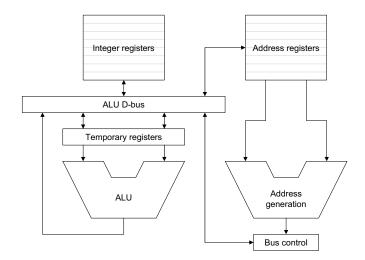

During its years of existence, the x86 CPU architecture has changed considerably. The original 8086, as shown in figure 2.1, was executing one instruction at a time<sup>1</sup>. All but the very simplest instructions required multiple clock cycles, being executed as a small program within the CPU itself

<sup>&</sup>lt;sup>1</sup>The 8086 did also have a separate bus interface unit that speculatively fetched the next instructions. The main purpose of this unit was to remove the memory latency, that is the function of a cache, rather than parallel execution

#### 2.1 Background

Figure 2.1: Block diagram of the Intel 8086 processor. All operations are executed by a single ALU.

as microcode. A typical computer had a very limited amount of memory, typically in the tens of kilobytes.

This posed an understandable model for the programmer when designing algorithms. The determining factor for performance was the number of operations required, and how this depended on the dominating size n of the problem at hand. The performance was analyzed using the Onotation for characterizing algorithms, where a linear algorithm would be described as O(n), and a cubic algorithm as  $O(n^3)$ . The focus among programmers where thus to get to the fastest algorithm based on the Onotation. (More information on O-notation can be found in Aho et al. 1982, page 16–27).

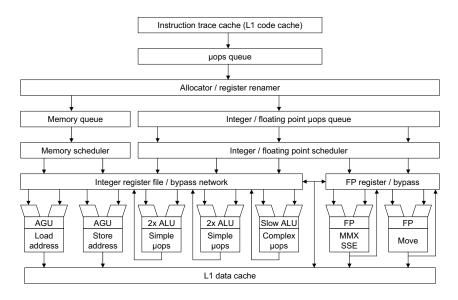

Throughout the generations following the original 8086, deeper pipelining and higher frequencies were used. Released in 2005, the Prescott design was a very different architecture, as shown in figure 2.2 (Boggs et al. 2004). The instructions are decoded into RISC-style micro-operations, which are fed to the execution engine. Instead of a single ALU, there were seven execution units, of which two could issue two operations per clock cycle. Thus up to nine instructions can be started in a single clock cycle<sup>2</sup>. The processor has a deep pipeline with 31 stages. There could potentially be more than a hundred operations in some state of execution at any moment. The parallelism implied high sensitivity to serial dependencies in the in-

<sup>&</sup>lt;sup>2</sup>Only three operations can complete simultaneously

Figure 2.2: Block diagram of the Intel Pentium4 (Prescott) processor. Execution is run in parallel across two floating point and five integer ALUS (Boggs et al. 2004, Adapted from).

struction stream, as warned by Amdahl's law (Amdahl 1967). A previous study suggests that this level of instruction level parallelism is not readily achievable (Wall 1991).

From the initial 8086 and up to the Prescott design, each generation gave dramatic increases in clock frequency, but the instruction processing latency saw small reductions. New architectures even increased this latency at their time of introduction. This latency can to a large extent be handled by compilers in combination with an out-of-order execution engine. There are although limits to what can be achieved with these methodologies (Gerber et al. 2006). If the algorithms are constructed with a 25 year old architecture in mind, reaching high utilization of the available processing power is unlikely. Consequently, handbooks guiding programmers to suitable practices are needed (Intel Corporation 2004).

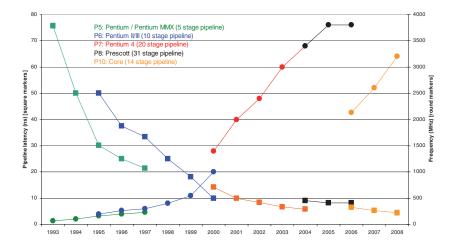

Figure 2.3 shows an abrupt change between the Prescott and the more recent Core design in terms of clock frequency. The Prescott architecture was intended to scale to 10 GHz, but never got faster than 3.8 GHz. The main obstacle preventing increased clock frequency was not the speed of the transistors, but rather the power consumption. When reducing geometries below 90 nm, the transistor leakage became larger than expected (Kr-ishnarnurthy et al. 2002; Mistry et al. 2007).

#### 2.1 Background

Figure 2.3: Development of clock frequency and instruction processing latency of the x86-family of CPUs over time. Clock frequency is plotted with round line markers against the right hand axis. Latency is plotted with square line markers against the left hand axis.

The Core design reduced the clock frequency, and at the same time almost halved the number of pipeline stages. As a result, the execution latency did not increase despite the reduced frequency. Even though the clock frequency of the Core architecture has increased gradually with the maturity of the design, the road maps from Intel; the largest x86 manufacturer; does not suggest major future cycle time reductions.

Further advances in processing throughput are anticipated to stem from using multiple processor cores, either identical copies, or heterogeneous designs (Kumar et al. 2003). Parallel cores can also be implemented by hyper-threading, which replicates the part of a processor holding the state, but not the execution units (Marr et al. 2002). The replicated states and their respective threads run alternatingly, increasing the time between instruction issue within the same thread. Since each thread runs slower, memory access latency is reduced when measured in execution cycles. If the threads can run independently, the overall processing throughput is larger than for a higher frequency, single threaded execution.

Future processor designs, not only in the x86-family, it thus likely to increase the number of parallel execution cores, but not provide significant speed-up for single threaded applications. Any algorithm with a built in serial dependency must be redesigned to increase its performance.

Table 2.1: Performance for DRAM devices over several generations. Random access time is given as the time from issuing a row select command from idle mode, until data appears. Per-pin bandwidth is the available bandwidth per data pin on the component. Data adapted from Hennessy and Patterson (2007, figure 5.14).

| Year | Density  | Random access | Per-pin bandwidth |

|------|----------|---------------|-------------------|

| 1980 | 64 Kbit  | 150 ns        | 13 Mbit/s         |

| 1986 | 1 Mbit   | 100 ns        | 40 Mbit/s         |

| 1992 | 16 Mbit  | 60 ns         | 66 Mbit/s         |

| 2000 | 256 Mbit | 45 ns         | 133 Mbit/s        |

| 2004 | 1 Gbit   | 35 ns         | 533 Mbit/s        |

| 2006 | 2 Gbit   | 40 ns         | 1600 Mbit/s       |

### 2.1.2 The evolution of memory technology

Apart from the changes in processing architecture, there have also been large changes in the memory subsystem. The most commonly used memory technology is still dynamic RAM (DRAM) due to its low price and high storage capacity. As shown in table 2.1, the storage volume of DRAM devices has increased dramatically, with a factor of 30000 over 25 years. The random access time has had less than a four-fold reduction, and has seen no improvement for the latest generation. Notably, the per-pin transfer bandwidth has seen better improvements (Patterson 2004). Combined with wider memory interfaces, this substantial increase in bandwidth, at a level above the reduction of random access time, can be exploited in algorithm development, as will be shown in section 2.2 and 2.3. Burger et al. (1996) have predicted that off-chip access at one point will become so expensive that all memory will reside on the CPU itself. So far, the integration of processing and memory is not widespread, but some implementations exist (Gebis et al. 2004; Kirsch 2003; Patterson et al. 1997).

In addition to hyper-threading mentioned in the previous section, caching is used at one or more hierarchical levels to hide the increasing difference in processing speed and memory random access time (Hennessy and Patterson 2007, chapter 5). This do indeed provide a large performance benefit in the average case, but one can no longer consider all memory accesses to be equal. We can rank different memory accesses in order of increasing execution time.

- **Cache access** Data residing in one of the cache levels is accessible with low latency. For the uppermost cache level, this is usually within one clock cycle (e.g. 0.3 ns).

- **Sequential access** Due to the high bandwidth of memory, sequential access has a low cycle time even from DRAM (less than 1 ns). Cache fills and flushes are done through cache lines; reading address n in memory will in most cases cause the entire cache line to be retrieved. If n is th last element of a cache line, most processors will do speculative prefetching of location n + 1, giving sequential reads a further advantage over sequential writes.

- **Random access** Random access to DRAM is relatively slow. Table 2.1 gives the access time for the DRAM itself as 40 ns even for the most recent devices. The CPU to memory bridge adds an additional delay of the same order of magnitude.

- **Paged memory** Paged memory is residing on a disk drive, and will in the context of a CPU take forever to access (e.g. 10 ms). For the remaining discussions, all memory structures will be assumed to fit within the system memory, and not require paging. The principles explained, will still increase the performance if paging should occur, as paging also performs better with sequential than random accesses.

As a guideline, an algorithm should try to work with a subset of the data that can fit within the cache (memory locality). As bringing data in and out of the cache is costly, the data should preferably be processed to its final results with a single access. With the expectation of large memory subsystems, algorithms frequently use large data structures residing in memory. When accessing such structures, maintaining a predictable, preferably also sequential, address sequence is beneficial. Random accesses will have low cache hit ratios, and a large performance impact.

In the following sections some of these principles will be applied to real examples, demonstrating the performance potential that can be harnessed when keeping the processor architecture in mind during algorithm development.

#### 2.2 Sorting large arrays

Sorting is a common subproblem within many applications (Knuth 1997, chapter 5). For example, it can be used to maintain ordering between elements within a data structure for more efficient retrieval, or for ranking ele-

ments before providing this as output to a user or other applications. Sorting has been investigated for decades, but still no golden solution solves all kinds of sorting problems. Quicksort is considered to work well for most common application and data volumes (Knuth 1997, section 5.5), but is not suited for parallel machines (Knuth 1997, section 5.2.2). Other important sorting algorithms are insertion sort, bin sort and radix sort.

#### 2.2.1 Characteristics of search application at hand

The sorting application that will be discussed, originated from ranking web pages based on a user query. With a myriad of web pages, combined with the lack of specificity in typical web user queries, most queries result in a list of millions of potential web pages. Risvik (2004) describes an architecture where each web page in the listing has a relevance score. In order to present the user with a ranked list of results, not only for the ten most relevant web pages, but also anywhere within the results, the list must be sorted.

A sorting algorithm had already been implemented based on recursive bin sort. This algorithm was taking much of the CPU processing time (30 % in typical scenarios), which was considered to be unacceptably high. The algorithm was theoretically very efficient, with  $O(n \log n)$  complexity. Further analysis with CPU profiling tools<sup>3</sup> confirmed the suspicion that the task was not computationally demanding. But more alarming, the analysis showed that most of the time was spent waiting for memory references. There were obvious margins for improvement if the memory access pattern could be optimized.

#### 2.2.2 Rearranging memory references

The main limitations causing the memory bottleneck were an unpredictable access pattern, and multiple intermediate moves of each data record before reaching its final position. The unpredictability of the memory write operations lies within the problem itself: With unsorted data as input, the final location is data dependent. The clue to a solution would lie in minimizing the number of such moves to a minimum.

This reduction was achieved by investigating the data more elaborately before moving any records. This must be very efficient to not become a bottleneck by itself. Reading sequentially through the data to calculate their

<sup>&</sup>lt;sup>3</sup>Intel VTune

#### procedure radixsort;

```

{ Sorts list A of n records with keys consisting of fields f_1, \ldots, f_k

of types t_1, \ldots, t_k respectively. The procedure uses arrays

B_i of type \operatorname{array}[t_i] of listtype for 1 \le i \le k, where listtype

is a linked list of records. }

begin

for i := k downto 1 do begin

for each value v of type t_i do {clear bins}

make B_i[v] empty;

for each record r on list A do

move r from A onto the end of bin B_i[v],

where v is the value of field f_i of the key of r;

for each value v of type t_i, from lowest to highest do

concatenate B_i[v] onto the end of A

end

end {radixsort}.

```

Figure 2.4: Radix sort algorithm (as defined in Aho et al. 1982, page 281).

value distribution was considered. Such an approach could be integrated with a variant of radix sort.

#### 2.2.3 In-place radix sort

Radix sort (Hildebrandt and Isbitz 1959) is a sorting algorithm that divides the sorting problem into sorting on a single bit of the sorting key at a time, which also can be extended to work on multi-bit symbols (see Knuth 1997, section 5.2.3 for details). A variant of this principle is being used even outside computer algorithms, such as the postal service. Here, each shipment is initially sorted into bins by the most significant digit in the zip code, thereafter each bin is resorted with regards to the next digit(s). A formal description of the radix sort algorithm is given in figure 2.4. Note that this radix sort starts by sorting on the least significant digit first, for later concatenation of the individual digit bins and resorting on the next digit of increasing significance.

Due to the splitting in figure 2.4 of the sorting key into fields  $f_i$ , the resulting complexity for fixed size integer keys (where *k* is constant) is given

by Aho et al. (1982, page 281) as

$$O(n + \sum_{i=1}^{k} s_i) \tag{2.1}$$

where  $s_i$  is the number of different values of type  $t_i$ . However, since  $s_i$  has a constant upper bound for fixed size integers, the complexity is reduced to O(n).

Variable sized keys would also affect the complexity of e.g. Quicksort. The analysis of Quicksort resulting in  $O(n \log n)$ , assumes that each comparison is O(1). In practice, all digital computers require O(m) for a comparison, with *m* being the length of the variables.

While radix sort as described in figure 2.4 is O(n) for integer keys, it has some serious disadvantages for sorting extremely large arrays. Most obvious is the doubled memory usage for storing the sorting bins, and secondly the handling of these when implemented as lists. More subtle, but even more important, is the fact that radix sort starts out with the least significant digit. Thus the records brought together in the same bin are not more likely to end up in each others vicinity in the final sorted order. This implies no gain in locality when processing the data, prohibiting the cache system from hiding the memory latency of the DRAM system memory.

To improve the locality, advice was taken from the postal service sorting method mentioned above: Start sorting on the most significant digit instead. This would result in much better data locality after the initial sorting step.

There was also a need to remove the duplicated memory footprint. It was observed that if one could put a record directly into the correct position range for each sorting iteration, there would be only one swap element at any time requiring extra storage, i.e. in-place sorting.

In-place MSD radix sort implementations have been compared by Al-Darwish (2005), who argues that infrequent usage of such algorithms is due to the misconception of complex implementations and tedious bookkeeping. This was also stated by McIlroy et al. (1993) as *"The troubles with radix sort are in implementation, not in conception"*. Variants of radix sort have been used for sorting strings (Bentley and Sedgewick 1997) or using adaptive digit size (Maus 2002). Adaptive sorting algorithms seek to avoid worst case behavior due to input data values (Estivill-Castro and Wood 1992)

Given the application at hand, several optimizations could be applied. The sorting keys were fixed size integers, simplifying management of the in-place swapping of records. Similarly, by avoiding program flow de-

2.2 Sorting large arrays

| 72 | 24 | 02 | 44 | 79 | 45    | 35 | 17 | 31 | 51            | 12      | 62          | 09    | 52 | 50 |

|----|----|----|----|----|-------|----|----|----|---------------|---------|-------------|-------|----|----|

| 0x |    | 1x |    | 2x | 2x 3x |    | 4x |    | 5x            |         | <b>&gt;</b> | 6x 7x |    | x  |

| -  | -  |    | ŗ  |    |       | ŀ  |    | ŗ  |               |         |             |       |    | -  |

|    |    |    |    |    |       |    |    |    |               |         |             |       |    |    |

| 02 | 09 | 12 | 17 | 24 | 31    | 35 | 44 | 45 | 52            | 51      | 50          | 62    | 72 | 79 |

|    |    |    |    |    |       |    |    |    | x0            | x1      | x2          |       |    |    |

|    |    |    |    |    |       |    |    |    | <b>~ &gt;</b> | <b></b> | <>          |       |    |    |

|    |    |    |    |    |       |    |    |    |               |         |             |       |    |    |

| 02 09 12 17 24 31 35 44 45 50 51 52 62 7 | 79 |

|------------------------------------------|----|

|------------------------------------------|----|

Figure 2.5: Example of in-place radix sort using octal numbers.

pendent on the value of the sorting keys, there was no need to make an adaptive algorithm.

These ideas were implemented into a variant of most significant digit (MSD) in-place radix sort, with figure 2.5 showing the steps in a simple case. For simplicity, the example uses two-digit octal numbers. The top-most line consists of n = 15 such unsorted numbers. Starting with the most significant digit, the number of occurrences of each symbol for that digit is found by reading linearly through all the data. This finds two numbers starting with 0, another two starting with 1, and so on. After finding the value distribution, pointers can be placed to the sections of the array that should be used for each value of this digit.

The next step will swap all records into the right range with respect to this digit. The algorithm starts by finding the lowest labeled range containing any elements, as some ranges might be empty. The first record in this range, in this case 72, becomes the swap element. This number is put into the first position of the correct range, taking the place of 52 which now becomes the new swap element. The pointer for the first available position in the range 7x is updated accordingly. This process continues (through 51 and 12) until we reach 02 which is taking the vacant position previously held by 72. Once such a swap cycle completes, the first element that has not yet been moved is found, starting another swap cycle. This process is terminated after n swaps. Since no element will be swapped more than once due to the design of the algorithm, all elements must now have been swapped, and consequently be placed in the correct range.

The process is repeated recursively within each range on the next digit,

as shown in the middle line of figure 2.5. In this case, only the range 5x needs to be reordered, ending with a sorted array as shown in line 3. A listing of this algorithm implemented in the C programming language is shown in figure 2.6, using radix 256 on 32-bit integers.

Some of the implementation details in figure 2.6 justify an explanation. The function takes the data array as an argument, in addition to the size *n* and the number of right-hand shifts (*shift*) that is needed to bring the current sorting digit into the least significant byte of the key. Invoking the function is thus done with *shift* set to 24.

The switch statement on lines 7–12 counting occurrences could have been replaced by the following statement:

Even though this is more general, expanding the capability of the function beyond 32-bit integers, it infers a non-constant shift as well as a redundant AND-operation for the most significant bit. Constant shifts can be aggressively optimized by the compiler, speeding up the execution. The swapping is also started at the highest labeled value range, as the search for value ranges that need processing is more efficient with a decrement of the loop variable *i*.

Insertion sort is used when the size of each value range becomes relatively small. The threshold for shifting to insertion sort is architecture dependent. Insertion sort proved useful after reaching a level when the code and all data in the current range could be contained in the uppermost cache levels of the CPU. Furthermore, the arrays *last*, *ptr* and *cnt* have some redundancy. Two tables would be sufficient, at the expense of code readability.

#### 2.2.4 Algorithm complexity

In the analysis of the run time of the algorithm proposed in figure 2.6, n is the number of records to sort, each having a key of m binary digits (bits). In each iteration, a radix of  $2^d$  is used for the partial sorts, with d being the number of bits in that radix.  $c_i$  will be used for denoting constant factors. The initial counting of occurrences has a run time of

$$t_1(n) = c_1 \cdot n \tag{2.2}$$

Building the pointer tables has a run time of

$$t_2(n) = c_2 \cdot 2^d \tag{2.3}$$

```

1

void inplace_radixsort(ArrayRep a[], unsigned int n, unsigned int shift) {

2

unsigned int last [256], ptr [256], cnt [256];

3

unsigned int i, j, k, sorted, remain;

4

ArrayRep temp, swap;

5

6

memset(cnt, 0, 256*sizeof(unsigned int)); // Zero counters

7

switch (shift) { // Count occurrences

8

case 0: for(i=0; i<n; i++) cnt[a[i]._rankValue&0xFF]++; break;

9

case 8: for(i=0; i<n; i++) cnt[(a[i]._rankValue>>8)&0xFF]++; break;

10

case 16: for(i=0; i<n; i++) cnt[(a[i]. rankValue>>16)&0xFF]++; break;

case 24: for(i=0; i<n; i++) cnt[a[i]. rankValue>>24]++; break;

11

12

}

13

sorted = (cnt[0]==n); // Accumulate counters into pointers

14

ptr[0] = n - cnt[0];

15

last [0] = n;

16

for(i=1; i<256; i++) {

ptr[i] = (last[i]=ptr[i-1]) - cnt[i];

17

18

sorted \mid = (cnt[i]==n);

19

20

if (!sorted) { // Go through all swaps

21

i = 255;

22

remain = n;

23

while(remain>0) {

24

while(ptr[i]==last[i]) i--; // Find uncompleted value range

25

j = ptr[i]; // Grab first element in cycle

26

swap = a[j];

27

k = (swap._rankValue >> shift) & 0xFF;

28

if (i!=k) { // Swap into correct range until cycle completed

29

do {

30

temp = a[ptr[k]];

31

a[ptr[k]++] = swap;

32

k = ((swap=temp)._rankValue >> shift) & 0xFF;

33

remain--;

34

} while (i!=k)

35

a[j] = swap; // Place last element in cycle

36

}

37

ptr[k]++;

38

remain--;

39

}

40

41

if (shift>0) { // Sort on next digit

42

shift -= 8;

43

for(i=0; i<256; i++)

44

if (cnt[i]>INSERT_SORT_LEVEL) inplace_radixsort(&a[last[i]-cnt[i]], cnt[i], shift);

45

else if (cnt[i]>1) insertion_sort(&a[last[i]-cnt[i]], cnt[i]);

46

}

47

}

```

Figure 2.6: Modified radix sort for in-place sorting of 32-bit integer keys using an initial occurrence count.

#### 26 Hardware aware optimizations in data search applications

The swapping stage will move one of the n elements in each iteration, yielding

$$t_3(n) = c_3 \cdot n \tag{2.4}$$

In the recursive sorting on the next digit, insertion sort is only used for arrays below a constant size, and can thus in the context of this analysis be considered to run in constant time. Thus the recursion step takes

$$t_4(n) = c_4 \sum_{i=0}^{2^d} T(\frac{n}{r_i})$$

(2.5)

where  $r_i$  is the number of elements in range *i* for each of the 2<sup>*d*</sup> symbols in the partial sort key, and T(n) is the runtime of the overall algorithm. Furthermore,  $\sum_{i=0}^{2^d} r_i = n$ . The run time is thus recursively defined as

$$T(n) = (c_1 + c_3) \cdot n + c_2 \cdot 2^d + c_4 \sum_{i=0}^{2^d} T(\frac{n}{r_i})$$

(2.6)

It is obvious that a high number *d* of bits to be used in the radix will degrade the performance. In the implementation shown, d = 8. The run time is then given as

$$T_{d=8}(n) = c_5 + c_6 \cdot n + c_4 \sum_{i=0}^{256} T_{d=8}(\frac{n}{r_i})$$

(2.7)

with

$$\sum_{i=0}^{256} r_i = n \tag{2.8}$$

Thus  $T_{d=8}(n)$  has the complexity O(n).

#### 2.2.5 Measuring the sorting throughput

The new algorithm was benchmarked on different CPUs, spanning from 450 MHz Pentium III to 1.4 GHz Pentium4, resulting in three times faster execution compared to the original recursive binsort. As expected, the memory accesses were still the bottleneck, but were now being used more efficiently. For example, in test runs with 100 million records with random keys, each record was in average only moved 1.7 times (out of the theoretical maximum of 4) before reaching a location where the remaining sorting would be done by insertion sort, occurring in only in the uppermost cache level.

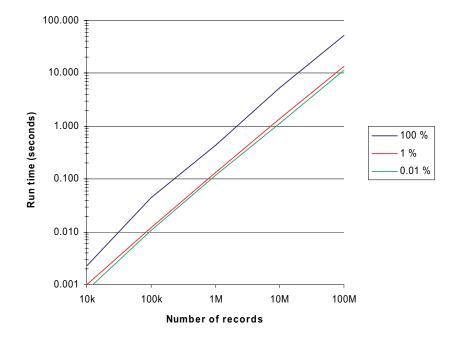

Figure 2.7: Scalability of in-place radix sort for complete (100%) and partial (1% and 0.01%) sorts. The fractional sorts can establish correct sorting for any range of keys, or any region within the fully sorted list. Note that both axes are plotted with logarithmic scale. Each record consists of 8 byte, including the 32-bit key. These tests were run on a 733 MHz Pentium III.

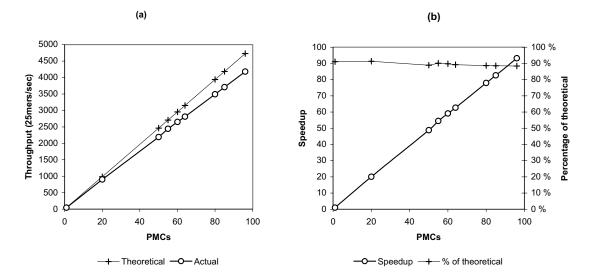

As shown in figure 2.7, the run time is indeed linear with respect to the number of records, in correspondence with the complexity analysis in section 2.2.4. This figure also shows the run time when sorting only a specified fraction of the array as described in section 2.2.6.

#### 2.2.6 Remarks on practical aspects

Although the above algorithm sorts the entire array, this was not needed in all application cases. For example, a user of a web search engine might only request results ranked from position 1000 to 1500. A variant of the algorithm that takes this into account was developed. After sorting on the most significant digit, only the relevant subsets of ranges were sorted on the lesser digits.

For the even more common web search, where the user only wants the top n records, a separate version of insertion sort holding only the n highest ranked records in sorted order was developed. This provided a further seven fold performance increase, since the memory accesses in practice were reduced to a linear read of all records. Using this algorithm, processing speed was able to run at the peak bandwidth of the memory subsystem.

A final note should be made on swapping records in memory as opposed to just pointers to the same records. As pointers usually would be smaller than the entire records, this might be considered advantageous. In reality, the records needed to be more than 20 times the size of a pointer for this to hold true on the test machines mentioned in section 2.2.5. Storing pointers requires additional memory, stealing both storage space and bandwidth. Additionally, accessing a small pointer still requires a full cache line access between the cache and system memory. Sorting through pointers should thus only be used in applications with large records.

#### 2.3 Counting the number of 1-bits

Another problematic area within the web search engine was the seemingly simple task of counting bits, that is finding the number of bits set to 1 in a long vector. There are multiple algorithms for solving this problem, where the optimal solution might not be the most intuitive one.

#### 2.3.1 The naive approach

The simplest way for counting the bits would be to use two nested loops. Since modern CPUs do not access bits individually, but rather longer words, working directly on the bit level becomes impractical. The outer loop would iterate through all the words containing the bit vector, while the inner loop would accumulate the number of bits within each such word.

For each bit, three operations would be needed: Shifting the bit to the least significant position, masking off any higher order bits, and accumulating the final result. This tedious algorithm takes in the range of 200 instructions just for processing one 64-bit word. Furthermore, a direct implementation would have large serial dependencies between the instructions, prohibiting efficient use of all the available parallelism in the CPU, shown in figure 2.2

#### 2.3.2 Using a lookup table

The typical way to get around the problems described in the previous section, is to replace the inner loop with looking up precomputed values in a table. For a word size of  $n \cdot m$  bits, the number of bits would be found through n lookups in a table of  $2^m$  potential values. While m should be large to reduce n, and thus the number of operations, the size of the lookup table grows exponentially with m. Selecting m in an implementation is thus a balancing act, most commonly ending up with m = 8 as a good compromise.

An often overseen implication of this approach is the memory accesses inferred by the table lookups. Even though this table is relatively small, each read of a word from the bit vector, is followed by *n* read operations from the lookup table. Solving performance issues by using more memory accesses is not attractive in a long term perspective, given the widening gap between compute speed and memory bandwidth.

Furthermore, the functional units of the CPU are not really kept busy. Each addition would never add a value larger than m to the accumulator. With a 64-bit processor and m = 8, only the least significant byte of the registers are effectively used, corresponding to 12.5%.

To increase the performance, two separate issues must be considered: The full register width of the CPU should be used for processing. At the same time, this should be achieved without accessing temporary data structures like the lookup table.

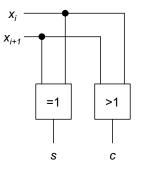

Figure 2.8: Adding bit  $x_i$  and  $x_{i+1}$  resulting in sum *s* and carry *c*.

#### 2.3.3 Using the full register width

In order to find a better implementation for this problem, the basic operations in binary additions had to be investigated. This disclosed a processing flow where every bit in the involved registers has the possibility of doing some actual work on every operation.

#### **Basics of binary addition**

The addition of two single digits is shown in figure 2.8, using a half-adder. The sum *s* is the XOR of the inputs, while the carry *c* is the AND of the inputs. The concatenation of *c* and *s* are also a two-bit binary number containing the sum, that is  $\sum_{j=i}^{i+1} x_j$ .

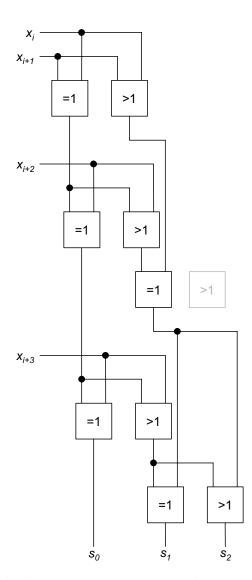

By chaining half-adders, the sum of more than two bits can be produced. Without a potential carry bit at every stage, the circuitry can be simpler than if chaining complete full-adders, as shown in figure 2.9, for calculation of  $\sum_{j=i}^{i+3} x_j$

#### Parallelizing bit serial addition

At first glance, this approach might look like a step in the wrong direction. In order to exploit CPU parallelism, bit serial adding has been introduced. An important observation is although that all operations on the data are now two input, single output binary operations. Such AND/XOR functions can be run effectively in registers, where the result of each bit position will not affect the other bits in the same register. Thus parallel operations can be run in one register. For a *n*-bit register, *n* summations are carried out in parallel. The register bank is so to speak used orthogonally, with *n* se-

30

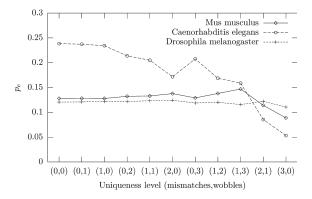

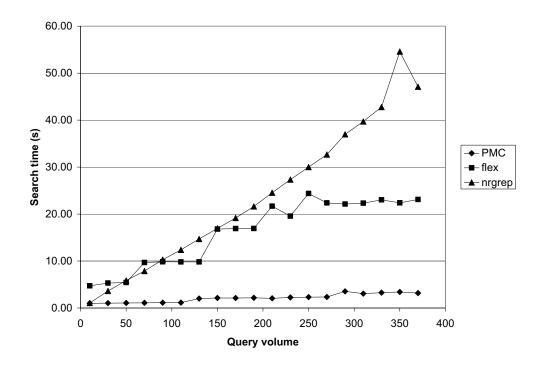

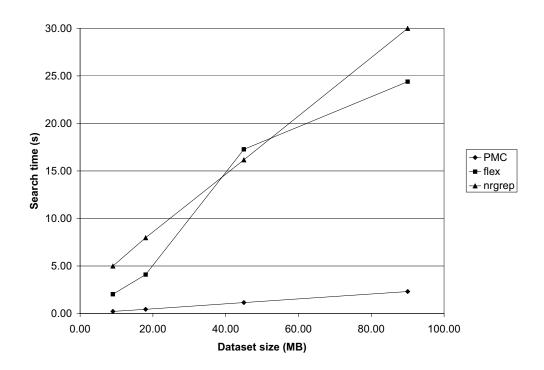

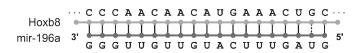

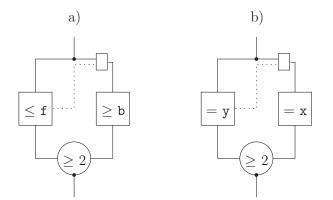

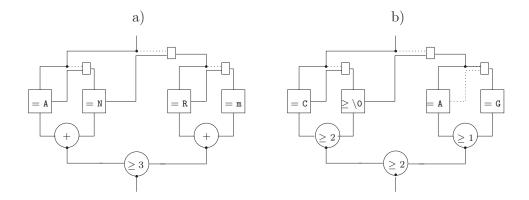

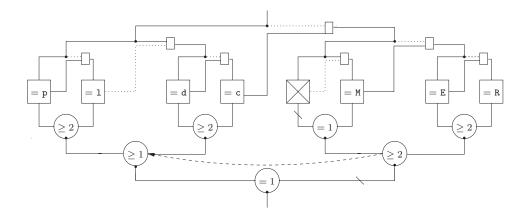

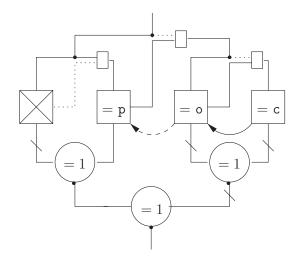

Figure 2.9: Calculating  $x_i + \ldots + x_{i+3}$  into the sum  $s_2s_1s_0$ . Unused part of half-adder is shown in gray.