Cyril Banino-Rokkones

# Algorithmic and Scheduling Techniques for Heterogeneous and Distributed Computing

Thesis for the degree philosophiae doctor

Trondheim, March 2007

Norwegian University of Science and Technology Faculty of Information Technology, Mathematics and Electrical Engineering Department of Computer and Information Science

#### NTNU

Norwegian University of Science and Technology

Thesis for the degree philosophiae doctor

Faculty of Information Technology, Mathematics and Electrical Engineering Department of Computer and Information Science

© Cyril Banino-Rokkones

ISBN 978-82-471-1075-1 (printed version) ISBN 978-82-471-1089-8 (electronic version) ISSN 1503-8181

Doctoral theses at NTNU, 2007:49

Printed by NTNU-trykk

# Abstract

The computing and communication resources of high performance computing systems are becoming heterogeneous, are exhibiting performance fluctuations and are failing in an unforeseeable manner. The Master-Slave (MS) paradigm, that decomposes the computational load into independent tasks, is well-suited for operating in these environments due to its loose synchronization requirements. The application tasks can be computed in any order, by any slave, and can be resubmitted in case of slave failures. Although, the MS paradigm naturally adapts to dynamic and unreliable environments, it nevertheless suffers from a lack of scalability.

This thesis provides models, techniques and scheduling strategies that improve the scalability and performance of MS applications. In particular, we claim that deploying multiple masters may be necessary to achieve scalable performance. We address the problem of finding the most profitable locations on a heterogeneous Grid for hosting a given number of master processes, such that the total task throughput of the system is maximized. Further, we provide distributed scheduling strategies that better adapt to system load fluctuations than traditional MS techniques. Our strategies are especially efficient when communication is expensive compared to computation (which constitutes the difficult case).

Furthermore, this thesis investigates also the suitability of MS scheduling techniques for the parallelization of stencil code applications. These applications are usually parallelized with domain decomposition methods, that are highly scalable, but rather impractical for dealing with heterogeneous, dynamic and unreliable environments. Our experimental results with two scientific applications show that traditional MS tasking techniques can successfully be applied to stencil code applications when the master is used to control the parallel execution. If the master is used as a data access point, then deploying multiple masters becomes necessary to achieve scalable performance. ii

# Preface

This doctoral thesis is submitted to the Norwegian University of Science and Technology (NTNU) in partial fulfillment of the requirements for the degree *Doktor Ingeniør*.

The work herein was performed at and funded by the Department of Computer and Information Science (IDI) at NTNU, under the supervision of Professor Lasse Natvig.

The thesis consists of two parts. The first part contains an introduction to the topics of the study, a summary of our contributions, and opens up for future work directions. The second part gathers the main contributions, presented as a collection of seven research papers. The layouts of the papers have been modified from their original form for the sake of presentation. Their contents have not been modified.

### Acknowledgments

I am grateful to my supervisors Professor Lasse Natvig, Doctor Jørn Amundsen, and Professor Einar Rønquist for the support and advises they have given me. I thank Doctor Anne Catherine Elster for her invitation to Norway and for helping me to get started with my PhD thesis. I would also like to thank Einar M. R. Rosenvinge and Eivind Smørgrav whom I had the pleasure to work with on parts of this thesis. I want also to thank my friends and colleagues at IDI, who contributed to create a pleasant atmosphere during these four years.

I cannot thank enough Doctor Olivier Beaumont for having introduced me to the field of heterogeneous scheduling, for his guidance and support throughout the last four years, and for having invited me to a stay at the University of Bordeaux (LaBRI) that resulted in a fruitful collaboration. Thanks also to Doctor Arnaud Legrand for invaluable technical advice regarding the simulator used in this thesis.

I could never have surmounted all the obstacles that arose during these four tumultuous years, without the support of my family. I am indebted to my mother for her love and devotion during all my life. I thank my brother Jérémy for his love and friendship. I am deeply grateful to *svigers* Klara and Steinar for having included me in their family from the very beginning. And of course, I would like to thank the most important person in my life, my wife Nina, for her unconditional love and support.

Finally, I want to extend my deepest love to the two persons that I miss profoundly: To my father who guided me into life with love and kindness, and to Håvard that opened my eyes with his happiness and self-irony. Without them, I would not be who I am today. To these two persons I, with love, dedicate this thesis.

> Cyril Banino-Rokkones Trondheim, November 2006.

# Contents

| Ι | Co   | ntext   |                                              | 3  |

|---|------|---------|----------------------------------------------|----|

| 1 | Intr | oductio | n                                            | 5  |

|   | 1.1  | Evolut  | tion of parallel computers                   | 5  |

|   | 1.2  |         | ds network-based computing                   | 6  |

|   | 1.3  |         | nallenges of high performance computing      | 7  |

|   |      | 1.3.1   | Data movements                               | 7  |

|   |      | 1.3.2   | Heterogeneity, variability and unreliability | 8  |

|   | 1.4  | Resear  | rch focus                                    | 9  |

|   |      | 1.4.1   | The master-slave paradigm                    | 9  |

|   |      | 1.4.2   | Research questions                           | 10 |

|   |      | 1.4.3   | Research methods                             | 11 |

|   | 1.5  | Thesis  | outline                                      | 13 |

| 2 | Inde | ependen | ut-task scheduling                           | 15 |

|   | 2.1  | -       | uction to scheduling theory                  | 15 |

|   |      | 2.1.1   | DAG, makespan and Gantt-chart                | 16 |

|   |      | 2.1.2   | Heuristics for DAG scheduling                | 16 |

|   | 2.2  | Makes   | pan minimization                             | 18 |

|   |      | 2.2.1   | Independent task applications                | 18 |

|   |      | 2.2.2   | Divisible load theory                        | 21 |

|   | 2.3  | Throug  | ghput maximization                           | 27 |

|   |      | 2.3.1   | Performance metric                           | 27 |

|   |      | 2.3.2   | Theoretical model                            | 28 |

|   |      | 2.3.3   | Scheduling policies                          | 29 |

|   |      | 2.3.4   | Formulation of the steady-state regime       | 30 |

|   |      | 2.3.5   | Schedule reconstruction                      | 31 |

|   |      | 2.3.6   | Example                                      | 33 |

|   |      | 2.3.7   | The bandwidth-centric principle              | 34 |

|   |      | 2.3.8   | Network equivalence                          | 34 |

|   |      | 2.3.9   | Extensions                                   | 35 |

|   | 2.4  | Contri  | butions                                      | 35 |

|    |      | 2.4.1 Location-aware master-slave tasking                 | 35 |

|----|------|-----------------------------------------------------------|----|

|    |      | 2.4.2 Distributed schedule construction                   | 37 |

|    |      | 2.4.3 Collection-aware master-slave tasking               | 38 |

| 3  | Sten | cil code applications                                     | 39 |

|    | 3.1  | Introduction to stencil computations                      | 39 |

|    | 3.2  | Sequential optimizations                                  | 40 |

|    | 3.3  | Parallel implementation issues                            | 41 |

|    |      | 3.3.1 Domain decomposition                                | 41 |

|    |      |                                                           | 42 |

|    |      | 3.3.3 Fault tolerance                                     | 43 |

|    | 3.4  | Contributions                                             | 43 |

|    |      | 3.4.1 Image filtering application                         | 44 |

|    |      | 3.4.2 Lattice gauge theories                              | 44 |

|    |      |                                                           | 47 |

| 4  | Con  | clusion                                                   | 49 |

|    | 4.1  | Contributions                                             | 49 |

|    |      | 4.1.1 Master-slave tasking                                | 49 |

|    |      | 4.1.2 Stencil code applications                           | 50 |

|    |      | 4.1.3 Summary                                             | 51 |

|    | 4.2  | Future work                                               | 51 |

|    | Bibl | iography                                                  | 53 |

| II | C    | ontributions                                              | 73 |

| 1  | Loc  | ation-aware master-slave tasking on the grid              | 75 |

| -  | 1.1  |                                                           | 77 |

|    | 1.2  | Grid computing, facility location and supply chain design | 79 |

|    | 1.3  |                                                           | 80 |

|    | 1.4  | Optimizing master placement                               | 82 |

|    |      | 1.4.1 Mathematical formulation of the B-COVER problem     | 82 |

|    |      | 1.4.2 Complexity of <i>B-COVER</i>                        | 83 |

|    | 1.5  | Greedy heuristics                                         | 84 |

|    | 1.6  | Simulations                                               | 85 |

|    |      | 1.6.1 Methodology                                         | 85 |

|    |      | 1.6.2     Scheduling issues                               | 86 |

|    |      | 1.6.3 Results                                             | 86 |

|    | 1.7  | Conclusion and future work                                | 88 |

### Contents

| 2 | A dis             | stributed procedure for bandwidth-centric scheduling of independent- |  |  |  |  |  |  |  |  |  |  |  |

|---|-------------------|----------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|   | task applications |                                                                      |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.1               | Introduction                                                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.2               | Related work                                                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.3               | Our steady-state model                                               |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.4               | The bandwidth-centric principle                                      |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.5               | Reversing the tree traversal                                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.6               | Reconstructing the schedule                                          |  |  |  |  |  |  |  |  |  |  |  |

|   |                   | 2.6.1 Asynchronous schedule                                          |  |  |  |  |  |  |  |  |  |  |  |

|   |                   | 2.6.2 Event-driven schedule                                          |  |  |  |  |  |  |  |  |  |  |  |

|   |                   | 2.6.3 Local scheduling                                               |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.7               | Efficient start-up phase                                             |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.8               | Example                                                              |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.9               | Future work                                                          |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.10              | Conclusion                                                           |  |  |  |  |  |  |  |  |  |  |  |

| 3 | Mast              | ter-slave tasking on asymmetric networks 115                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.1               | Introduction                                                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.2               | Related work                                                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.3               | Platform model                                                       |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.4               | Maximizing the throughput                                            |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.5               | Bandwidth optimization                                               |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.6               | Task-flow control                                                    |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.7               | Scheduling heuristics                                                |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.8               | Simulations results                                                  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.9               | Conclusion and future work                                           |  |  |  |  |  |  |  |  |  |  |  |

| 4 | Onli              | ne task scheduling on heterogeneous clusters: an experimental        |  |  |  |  |  |  |  |  |  |  |  |

|   | study             |                                                                      |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.1               | Introduction                                                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.2               | Framework                                                            |  |  |  |  |  |  |  |  |  |  |  |

|   |                   | 4.2.1 Test-case application: matched filtering                       |  |  |  |  |  |  |  |  |  |  |  |

|   |                   | 4.2.2 Test-bed platform: athlon-based cluster                        |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.3               | Scheduling master/worker applications                                |  |  |  |  |  |  |  |  |  |  |  |

|   |                   | 4.3.1 Previous scheduling strategies                                 |  |  |  |  |  |  |  |  |  |  |  |

|   |                   | 4.3.2 The monitor strategy                                           |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.4               | Implementation                                                       |  |  |  |  |  |  |  |  |  |  |  |

|   |                   | 4.4.1 Data staging                                                   |  |  |  |  |  |  |  |  |  |  |  |

|   |                   | 4.4.2 Multithreaded processes                                        |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.5               | Empirical results and analysis                                       |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.6               | Conclusions and future work                                          |  |  |  |  |  |  |  |  |  |  |  |

| 5 | Para  | allelizing lattice gauge theory models on commodity clusters      | 143 |

|---|-------|-------------------------------------------------------------------|-----|

|   | 5.1   | Introduction                                                      | 145 |

|   | 5.2   | Test-case application                                             | 147 |

|   | 5.3   | Domain decomposition and detailed balance condition               | 147 |

|   | 5.4   | Theoretical models                                                | 149 |

|   | 5.5   | Theoretical results                                               | 150 |

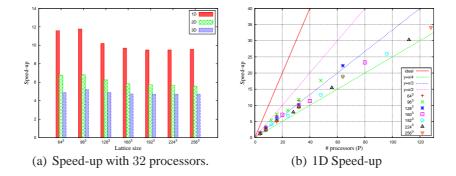

|   |       | 5.5.1 1D decomposition                                            | 151 |

|   |       | 5.5.2 2D decomposition                                            | 151 |

|   |       | 5.5.3 3D decomposition                                            | 151 |

|   |       | 5.5.4 Speed-up and efficiency tradeoff                            | 152 |

|   | 5.6   | Experimental results                                              | 153 |

|   | 5.7   | Related work                                                      | 155 |

|   | 5.8   | Conclusion                                                        | 156 |

| 6 | Don   | nain decomposition vs. master-slave in apparently homogeneous     | 5   |

|   | syste |                                                                   | 159 |

|   | 6.1   | Introduction                                                      | 161 |

|   | 6.2   | Related work                                                      | 164 |

|   | 6.3   | Our lattice gauge theory model                                    | 165 |

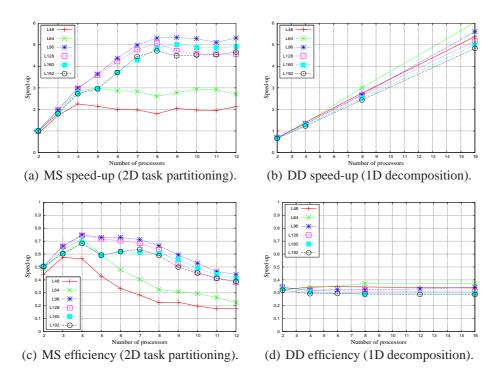

|   | 6.4   | Domain decomposition implementation                               | 167 |

|   | 6.5   | Master-slave implementation                                       | 169 |

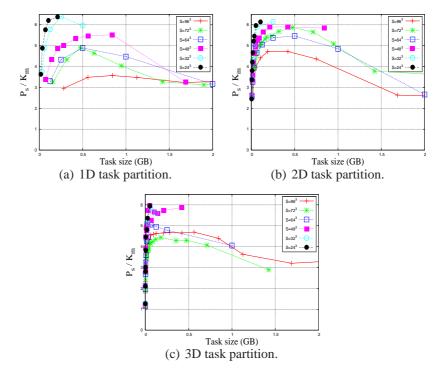

|   |       | 6.5.1 Task partitioning                                           | 169 |

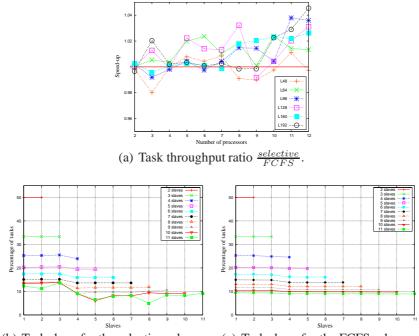

|   |       | 6.5.2 Selective scheduling                                        | 170 |

|   |       | 6.5.3 FCFS vs. selective scheduling                               | 171 |

|   | 6.6   | Domain decomposition vs. master-slave                             | 172 |

|   | 6.7   | Future work                                                       | 174 |

|   | 6.8   | Conclusion                                                        | 174 |

| 7 | Data  | a layout and access transformations for efficient stencil computa | -   |

|   | tions | •                                                                 | 179 |

|   | 7.1   | Introduction                                                      | 181 |

|   | 7.2   | Stencil computations                                              |     |

|   | 7.3   | Previous work                                                     | 184 |

|   | 7.4   | Data layout transformations                                       | 187 |

|   |       | 7.4.1 2D skewed data layout                                       |     |

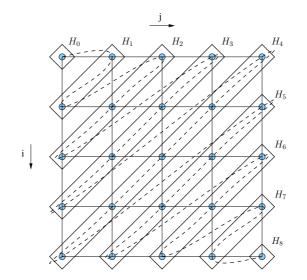

|   |       | 7.4.2 3D skewed data layout                                       |     |

|   | 7.5   | Data access transformations                                       | 191 |

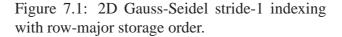

|   |       | 7.5.1 Skewed stride-1 indexing                                    | 191 |

|   |       | 7.5.2 Stencil decomposition                                       |     |

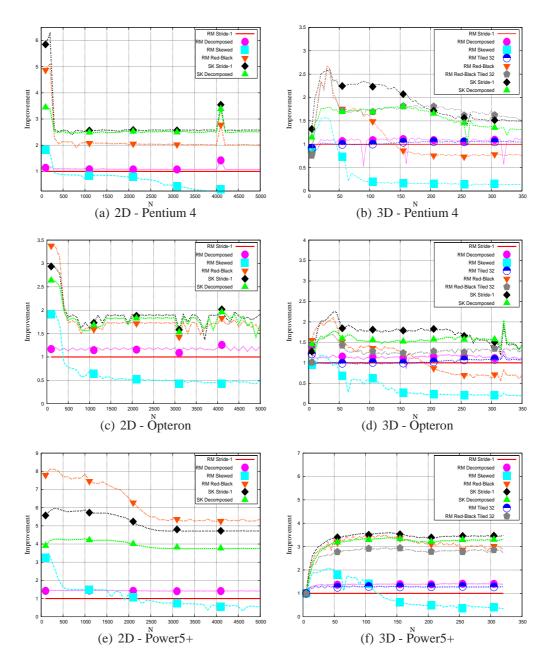

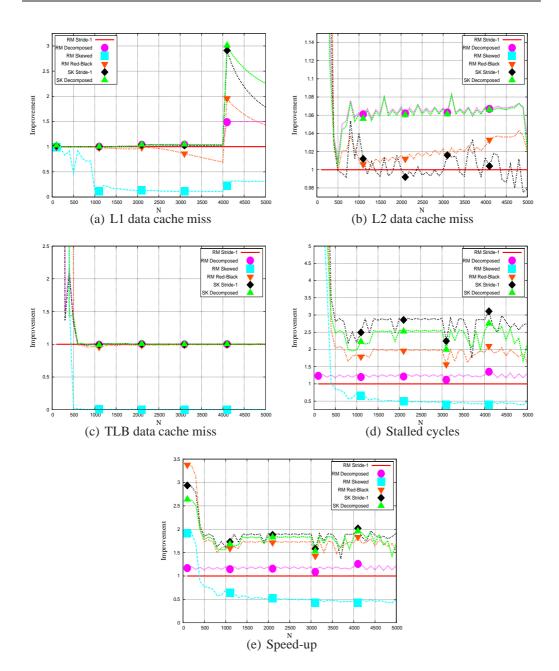

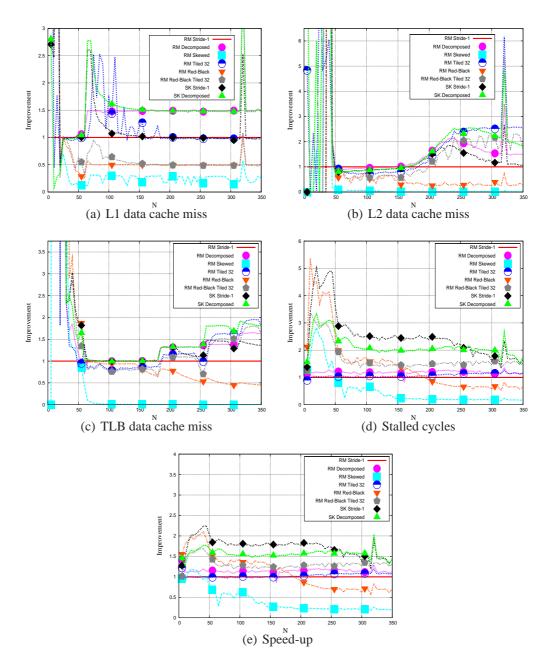

|   | 7.6   | Experimental results                                              |     |

|   |       | 7.6.1 Methodology                                                 |     |

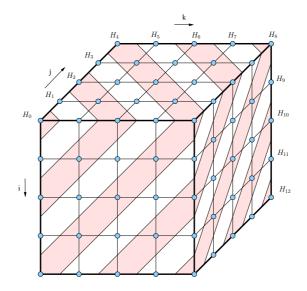

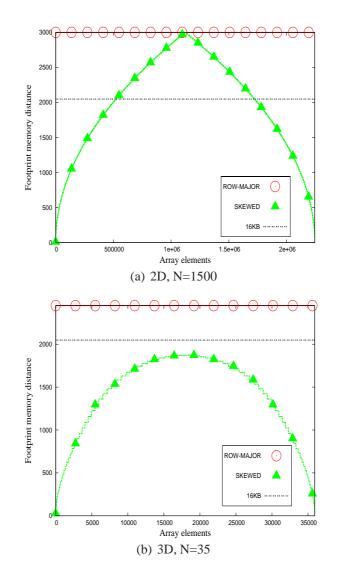

|     | 7.6.2  | Resu  | ilts a | and | int | erp | ore | tat | ior | ı |  |  |  |  |  |   |   |   |  | 196 |

|-----|--------|-------|--------|-----|-----|-----|-----|-----|-----|---|--|--|--|--|--|---|---|---|--|-----|

| 7.7 | Conclu | ision |        |     |     |     |     |     |     |   |  |  |  |  |  | • | • | • |  | 202 |

# Part I Context

# Chapter 1

# Introduction

# **1.1** Evolution of parallel computers

In the last decades, the field of high performance computing has seen a rapid evolution in terms of architectures, technologies and system utilization. The need for always more computing power in a multitude of domains (e.g. scientific and engineering simulations, data mining, signal and image processing, etc) has impulsed the emergence of parallel computing systems. The idea of parallel computing can be illustrated by the well-known motto: *Unity is strength*, i.e. grouping small individual forces together results in a powerful single force. Based on this principle, the precursor parallel computing machines - called *vector computers* - were born in the 1960's, and raised enthusiasm within the scientific community. These vector supercomputers were very expensive due to their special design for performance, but became quickly obsoletes because of rapid technological improvements [175].

In the mid 1990's, *massively parallel processing* systems (MPP) appeared on the high performance computing market, and became really strong competitors for traditional vector supercomputers. Most MPPs are distributed memory systems composed of hundreds or thousands relatively inexpensive processors connected together with custom designed fast interconnects. Each processor is self-contained, with its own cache and memory chips and additional supporting hardware. In the same genre, a *cluster* is a collection of workstations/PCs interconnected by a local network. The broad adoption of cluster systems results from their cost to performance ratio unmatched by any other computing system.

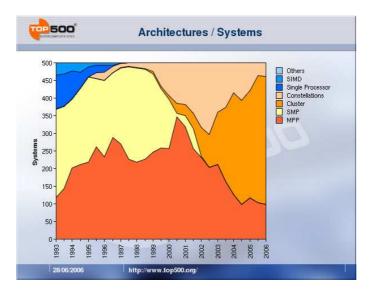

Figure 1.1 depicts the recent architectural trends within the top500 supercomputers [1]. Note that single processor systems cannot match the performance achieved by parallel systems, and logically disappeared from the top500 list. MPP systems on the other hand constitute the most powerful architecture, albeit the share of cluster systems is rapidly increasing. One can also observe a diminution

Figure 1.1: Architectures share over time (obtained from [1]).

of *constellation*<sup>1</sup> systems in the list.

It should be noted that this evolution has been possible only at the cost of constant and massive efforts in the development of standard software and notably of high performance libraries such as BLAS [129], MPI [94], LINPACK, LAPACK or ScaLAPACK [74]. While greater performance requires technological improvements, *portability*, that is the ability of a program to be executed on different systems, requires the use of interfaces in form of libraries.

# **1.2** Towards network-based computing

Although parallel computers have proven to deliver good and stable performance, financial or technical constraints limit the scale of these systems, and consequently the amount of computing power they can supply. Reproducing the successful motto at a bigger scale, the seek for always more computing power conducted to the interconnection of geographically dispersed parallel computers, and the *Grid* was born [88]. Grid computing provides the ability to perform computations at unprecedent scale by taking advantage of several networked supercomputers.

<sup>&</sup>lt;sup>1</sup>The difference between a cluster and a constellation comes from the relationship between the number of nodes and the number of processors in each node of the system. If there are fewer processors per node than there are nodes in the system then you have a cluster. But if there are more processors per nodes than there are nodes in the system, then you have a constellation. This differentiation is motivated by the different approaches for programming cluster and constellation systems.

The aggregation of personal computing resources can also supply large amounts of computing power. For instance, every large institution owns hundreds of PCs interconnected by a LAN, and has hence a huge amount of potential computing power at its disposal. Livny showed that most of the workstations are often idle, and proposed Condor [178], a system for exploiting this "wasted" computing power. The Condor system has been very successful, and similar commercial solutions are now available to enterprises [60].

With the growing popularity of the Internet and the advance in technology, this idea has been expanded world wide. *Internet computing* seeks to exploit otherwise idle workstations and PCs spread over the Internet. One of the most successful Internet computing applications is the *SETI@home* project [6] whose goal is to analyze radio telescopic data, searching for signs of extraterrestrial intelligence. The success of SETI has inspired many other @home applications and impulsed an ever-growing research trend for supporting this kind of applications [92, 167, 174]. Similarly, *Peer-to-Peer* networks have also been used to run large scale applications on geographically dispersed computing resources [55, 61, 147].

The early adoption of network-based computing platforms is focused on applications that expose a large degree of parallelism with little or no coupling, and whose high computational demands cannot be met by single parallel computers [60]. They are typically implemented under the Master-Slave (MS) paradigm (depicted in greater details in Section 1.4.1). Many applications have been or can be implemented under the MS paradigm: They include Monte Carlo simulations [22], collaborative computing efforts such as SETI@home [6, 174], biological sequence comparisons [171], or also distributed problems organized by companies like Entropia [60].

It should finally be noted that, although harnessing computing power spread over computer networks is much cheaper than buying a new parallel computer, utilizing efficiently these dispersed and volatile resources turns out to be a much more complex task.

# **1.3** The challenges of high performance computing

#### **1.3.1** Data movements

Delivering huge amounts of computing power is a difficult task. Bringing data quickly to the processing units is probably one of the most important and challenging issues that high performance computing must face. Interestingly, this problem is not a new one:

"In my opinion this problem of making a large memory available at

reasonably short notice is much more important that of doing operations such as multiplication at high speed." — (Alan Turing, 1947)

If we look back in history, the source of the problem is clear: In the last decade, processor performance has been steadily improving at a much more higher rate (55%) than memory performance (7%) [101]. This huge gap between memory performance and processor performance is popularly known as the *memory wall* [190]. Modern CPUs are so fast that memory transfers constitute the practical limitation on the processing speed. Therefore, modern computer architectures rely on a hierarchical arrangement of memory (caches) to help bridging that widening gap. Each level of the hierarchy is of higher speed and lower latency, but is of smaller size than lower levels.

In addition to the memory wall, parallel computers disclose another gap. The computational speed of the processors is typically much faster than the communication speed of the interconnect [66]. Therefore, a wealth of efforts have been made to design parallel algorithm that lessen the impact of communication. The situation is exacerbated for Grid applications communicating over high latency WAN links.

Thus, efficiently managing data movements is of tremendous importance at all the levels of modern computing systems. Undoubtedly, this issue will remain of paramount importance for future computing systems as well.

#### **1.3.2** Heterogeneity, variability and unreliability

High performance computing systems are becoming *heterogeneous*, interconnecting resources with different hardware and software. This heterogeneity makes resource selection paramount in order to increase the sustained performance. Balancing the computational load among several processors is already difficult on homogeneous systems, it becomes even harder on heterogeneous systems [113,114].

System load fluctuations are caused by applications that compete for shared resources within the system (e.g. processors and network links). Consequently, the load and availability of the resources fluctuate over time, due to the unpredictable interactions of the users with the system. Several adaptation techniques have been elaborated with the ultimate goal being self-adaptation where the application adapts to its environment without user intervention. For instance, the AppLeS methodology [39] consists in deploying a scheduling agent that monitors the system load, utilizes performance predictions and application-specific information to dynamically generate a schedule application. Casanova et al. [53] present a task farming strategy for scheduling independent task applications onto Grid environments that adapts dynamically the number of tasks submitted to the system in function of system load fluctuations. At last, Heymann et al. [102],

propose a strategy that adjusts dynamically the number of slave processes that participate to a Master-Slave computation.

When increasing the number of computing and communication resources composing the system, the number of resource failures that are likely to occur increases accordingly. Large-scale systems - composed of hundreds or thousands of processors - are hosting applications that may run for days, and in these conditions, one expects resource failures (both hardware and software) to be the rule rather than the exception. This has a direct impact for applications that must survive to resource failures [73] (more on fault tolerance in Section 3.3.3).

Thus, large-scale computing systems are heterogeneous, dynamic and unreliable environments that require adapted, flexible and robust techniques and algorithms.

### **1.4 Research focus**

This section begins with a description of the MS paradigm, with an emphasis on why - we believe - this paradigm is well-suited for distributed, heterogeneous, dynamic and unreliable computing systems. Thereafter, we identify and expose the shortcomings that come with the MS paradigm, state the research questions studied in this thesis, and present our main research methods. At last, we conclude with the organization of the thesis.

#### **1.4.1** The master-slave paradigm

The Master-Slave paradigm, also called Master-Worker or task farming paradigm, consists of two entities: A master process and several slave processes. The master is responsible for decomposing the computational domain into a number of smaller independent work units, usually called *tasks*, which are delegated to the slaves for parallel remote computation. The main asset of the MS paradigm is its robustness to resource failures. Its loosely coupled structure presents only one single point of failure - whose failure will cause an interruption of the computation - in the form of the master process. If some slave processes die, the computation can carry on with the remaining slaves. Hence, the number of slaves can be adapted dynamically to the number of available resources. If new resources appear during the computation, they can be incorporated as new slaves, and if a resource disappears (e.g. fails or is reclaimed by its owner) the tasks that were allocated to this machine are simply reallocated to other slaves [20]. Moreover, fast slaves with nothing left to do towards the end of the computation can receive unfinished tasks already delegated to other slaves. Redundant results or *replicas* are simply discarded [64]. This mechanism increases the chance to assign tasks

to fast slaves, but comes at the expense of wasted computing power. Nevertheless, it has been shown that replicating the tasks only twice, leads to significant improvements [64].

In its simplest form, the MS paradigm works as follows. The master initially distributes one task to every slave, then the slaves compute their tasks and send the results back to the master, which triggers the latter to send additional tasks. As slaves execute tasks at their own paces, they will automatically request tasks proportionally to their computing speeds. This is popularly known as *self-scheduling* (also called *demand-driven* or *work-queue*). By construction, self-scheduling adapts well to the performance fluctuations of the computational resources. If a slave suddenly gets some external load, it will process tasks less rapidly, and hence request tasks less frequently. When the conditions get back to normal, the slave will ask for tasks at its maximal pace.

However, self-scheduling is not efficient for platforms composed of heterogeneous networks. When heterogeneity applies also to the communication links, resource selection strategies become necessary in order to efficiently utilize the available computing resources. Consider for instance the case where a fast slave is connected to the master via a slow communication link. The slave will process tasks faster than it receives them, and will occupy most of the master communication bandwidth. In these conditions, it may be more advantageous to serve slower slaves but that are interconnected with rapid communication links.

This brings about the communication to computation (C-C) ratio issue, common to all parallel programs. Applications being implemented under the MS paradigm must exhibit a large C-C ratio, meaning that the time required to send a task to a slave is much smaller than the time required for the slave to process it. Otherwise there is no possible benefits from a parallel implementation under the MS paradigm.

Finally, the centralization of the data in one single place clearly limits the scalability of the system. Adding more slaves than the master can handle introduces slave starvation, and worse, might cause contention at the master site, degrading the overall performance. Several studies have proposed strategies to automatically and dynamically adjust the number of slaves involved in the computation to optimize the master utilization [86, 102, 149].

#### **1.4.2 Research questions**

In appreciation of the problems pointed out above, we believe that the main issue that needs to be addressed, is the lack of scalability of the MS paradigm. Hence, the main research question identified and explored in this thesis is:

#### Q-1 How should the MS paradigm be enhanced to improve its scalability?

On the one hand, sending - and receiving - all the data in a single place constitutes the bottleneck of the MS paradigm. On the other hand, centralizing the scheduling decision making process might be inefficient when dealing with largescale dynamic systems. The amount of information that needs to be gathered at a central location may require a prohibitive amount of time. System conditions may have changed by the time the information has been gathered to the scheduler. These two observations imply that (i) the master location(s) should be carefully selected, and (ii) scheduling decisions should be made in a decentralized fashion.

This thesis investigates also the suitability of MS techniques to applications that are not usually implemented as such, but that could nonetheless benefit from it. In particular, we think of adaptation to system load fluctuations and resilience to resource failures. Hence, the second research question explored in this thesis has been formulated as follows:

#### Q-2 Can MS scheduling techniques be applied to stencil code applications?

Answering this question implies to:

- Identify stencil code application candidates.

- Implement and evaluate a MS implementation of the selected applications.

We have chosen stencil code applications as candidates for such investigation because several applications of this kind are used at NTNU. Usually, stencil applications are parallelized with *domain decomposition* (DD) methods, that decompose the computational domain into sub-domains assigned to the processors. However, the DD methods make it difficult to account for system heterogeneity, to adapt to system fluctuations, and to handle system failures (more on this in Chapter 3).

#### **1.4.3 Research methods**

#### Static models for conceiving dynamic strategies

Some people believe that static models are inappropriate for designing dynamic scheduling strategies. We mean, on the contrary, that every dynamic environment can be considered as a succession of static contexts. Our research philosophy consists in studying heterogeneous static environments, in order to identify which property or aspect of the problem is the determinant factor that directly impacts on system performance. Then, knowledge that has been acquired on static networks can be embedded within dynamic scheduling strategies.

A subtle point similar to the *bounded irregularity* pointed out by Bast [23] corroborates our research methodology. If the system load fluctuates in an unforeseeable manner throughout the entire execution time, then it becomes impossible to guarantee anything, and the straightforward *self-scheduling* strategy comes out as an optimal strategy. It is therefore important to design algorithms that are efficient when the system stabilizes, and in this context, it makes sense to work with static models in the first place.

#### **Real experiments vs. simulations**

The evaluation and comparison of different scheduling strategies can be done either via real experiments or via simulations. Real experiments are important because they allow to test the behavior of an algorithm on a computer which is more complex than the model used to design the algorithm. However, large-scale experiments are difficult to reproduce because of the intrinsic instability of the platform. It is indeed impossible to guarantee that a large-scale platform will remain exactly in the same state between two tests, thereby forbidding any rigorous comparison between two scheduling strategies.

In contrast, simulations allow to fully control the experimental process. One can guarantee that two scheduling strategies were run in the exact same system conditions. Besides, Grid simulators are becoming more and more realistic. Sim-Grid [51] for instance, the simulator used in this study, allows to model real network topologies and their associated resource characteristics, such as CPU speed, network bandwidth and latency. In addition, it accounts for the congestion generated by multiple connections taking place simultaneously on the same link or on the same machine. The dynamic behavior of the system is described within trace files (CPU load and availability, network bandwidth and latency) that can be artificially generated, or that can be captured on real systems by Grid monitoring tools such as the Network Weather Service [187, 188].

The final advantage that simulations offer over real experiments is diversity. Setting up real experiments is a time-consuming process, which in the end gives results only for the test-bed system. In contrast, simulations allow to study a wide variety of computing systems with little additional efforts. For all these reasons, we used the SimGrid simulator toolkit for testing and comparing our scheduling strategies intended for computational Grids.

On the contrary to Grid environments, the reproducibility of experiments is possible on parallel computers. Most supercomputers provide dedicated access to their computational nodes, such that applications running simultaneously on the system get exclusive access to the nodes. There might still be interferences on the network or with the file system due to applications competing for shared resources, but these interferences can be attenuated if the experiments are repeated a sufficiently large number of times.

#### **Problem analogies**

Another research method used in this thesis is the search for analogies between problems. Indeed, different problems may actually share the same objectives, or face the same intrinsic difficulty. Hence, models and techniques used for one kind of problems can successfully be applied to another kind of problems. For instance, we highlight in Paper 1 the analogy between Facility Location problems and resource location problem. In particular, we use a Facility Location model to formulate our resource location problem, and to ultimately derive an efficient heuristic.

Identifying or building transformations from one problem to another is very useful for attacking new problems [89]. In Paper 1, we prove the NP-hardness of our resource location problem by a reduction from the Maximum Knapsack problem. And in Paper 3, we use a 2-dimensional Cartesian representation to derive an optimal principle for independent-task scheduling onto heterogeneous tree-shaped platforms.

### **1.5** Thesis outline

The rest of this thesis is organized as follows. Chapter 2 provides an introduction to scheduling theory, an overview of the state-of-art of scheduling independent task applications, and concludes by exposing how the contributions of this thesis fit within previous work. Chapter 3 presents stencil code applications, highlights the main issues for efficiently implementing these applications, and concludes by exposing our contributions when working with stencil code applications. Chapter 4 concludes the first part of the thesis, by summarizing our main contributions, discussing some limitations and proposing future work directions.

Our contributions are gathered in the second part of this thesis. Paper 1 addresses the problem of efficiently deploying multi-master MS applications onto heterogeneous platforms. Paper 2 presents a lightweight distributed method for building asynchronous schedules. Paper 3 presents distributed scheduling techniques intended for asymmetric networks. Paper 4 introduces a new MS scheduling strategy tested with an image filtering application on a low-cost PC cluster. Papers 5 and 6 present respectively a DD and a MS implementations of a Lattice Gauge Theory model. Finally, Paper 7 presents cache-efficient optimization techniques for improving the performance of stencil code applications.

# **Chapter 2**

# **Independent-task scheduling**

This chapter starts with an introduction to scheduling theory by presenting the general concepts common to most scheduling problems. Then, we present the state-of-the-art regarding independent task scheduling, the application class of interest for the framework of this thesis. We present theoretical results for the most common optimization objective, namely minimizing the total execution time (or makespan), and show how modifying the scheduling objective (by considering throughput maximization) helps deriving asymptotically optimal algorithms. Finally, we present the contributions of this thesis for the independent task scheduling problem, and how do they fit within previous work.

### **2.1** Introduction to scheduling theory

One of the challenges in exploiting the power of parallel computers is to map, or *schedule*, the parallelism contained in a program onto a set of processors, in order to achieve performance goals such as minimizing execution time, minimizing communication delays, or maximizing system throughput [54]. Scheduling problems are difficult. There are many factors that affect the decision process, such as the number and nature of the tasks to execute, task priority, current system load, affinity between tasks and machines, or resource usage policies. It is not too surprising then, that most scheduling problems turn out to be NP-complete [89], as they consider optimal execution schedules under a number of constraints. Consequently, one must often resorts to heuristics in order to generate efficient schedules in a reasonable amount of time [82].

#### 2.1.1 DAG, makespan and Gantt-chart

Application programs are composed of different tasks that must be executed in a certain order to produce the desired results. The tasks that are independent of each other are the ones whose execution order can be changed without modifying the result of the program. Hence independent tasks can be executed simultaneously by different processors.

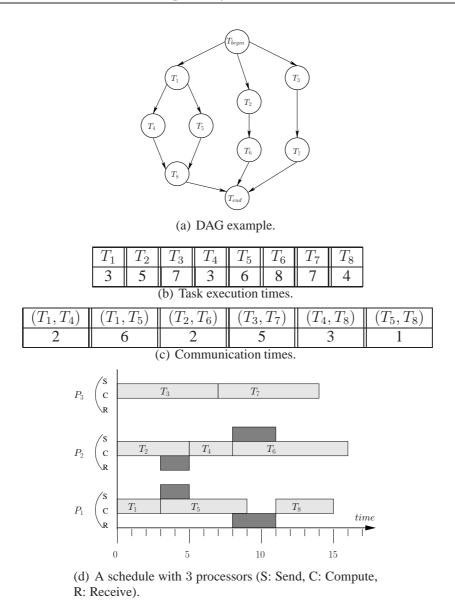

A directed acyclic graph (DAG) is used to represent the task dependencies of a program, where transitivity edges are omitted (see Figure 2.1 (a)). Usually,  $T_{begin}$  and  $T_{end}$  are fictive tasks used to facilitate the identification of the start and the end of the program. The usual scheduling objective is to minimize the total execution time of the schedule  $(T_{end} - T_{begin})$ , also called *makespan*.

The macro-dataflow model [62, 82, 170] has been widely used in the literature for modeling communication costs associated to task dependencies. If two dependent tasks u and v have been assigned to different processors, a communication delay occurs. More precisely, if task u is completed at time-step t, then the execution of task v cannot start before time-step  $t + c(v_1, v_2)$ . But if two dependent tasks reside on the same processors, the data transfer between the predecessor to the successor occurs via memory accesses. Since memory accesses are typically much faster than inter-processor communications, it is reasonable to neglect them. Figure 2.1 depicts a DAG example with the associated task execution times and inter-task communication times, and a Gantt-chart for visualizing a possible schedule with three processors.

The major drawback of the macro-dataflow model is the lack of realism when modeling communication operations. A processor can send and receive any number of messages concurrently, and the number of messages that can simultaneously circulate on the network is not bounded in any way. These assumptions are not realistic for modeling modern computing systems, and more advanced communication models are required.

#### 2.1.2 Heuristics for DAG scheduling

Scheduling arbitrary DAGs with the makespan minimization as objective is known to be NP-hard [166]. Consequently, a profusion of heuristics have been proposed, including list scheduling heuristics [83] and task clustering schemes [151]. Two versions of this problem have been investigated, depending on whether or not task duplication is allowed. The obvious benefit of task duplication, is to spare communication overhead by allowing several copies of a task to be executed by different processors. In general, scheduling with task duplication produces shorter makespans than without [151].

List scheduling heuristics are greedy algorithms that try to allocate as many

Figure 2.1: DAG example (a), task execution times (b), inter-task communication times (c) and Gantt-chart of a schedule (d).

tasks as possible at any given time-step. In a first phase, a priority is attributed to every task based on the number of their predecessors, and the tasks are inserted in a list by decreasing priorities. In a second phase, the algorithm iterates over the list built in the first phase and schedules the tasks on the processor that allows the earliest starting time of the task. The attribution of task priorities in the first phase has a tremendous impact on the performance of list scheduling heuristics. Not surprisingly, most list scheduling heuristics assign higher priorities to tasks located on the critical path of the DAG (i.e. located on the longest path of the DAG).

On the other hand, task clustering heuristics [90, 151] try to shorten the critical path of the DAG. Paths are shortened by clustering several tasks into coarser grain tasks. This admittedly reduces the communication overhead, but comes at the expense of increased processing times of the coarser tasks. This new tradeoff implies to determine adequate task granularity to achieve load balancing [151].

### 2.2 Makespan minimization

In order to minimize the makespan of a schedule, one must distribute the tasks to the processors in a way to achieve optimal load balance, that is, all the processor finishing times must differ as little as possible. Depending on the framework of the study, different model assumptions are made. Common to all studies is (i) the assumption that all the tasks initially reside in one place of the system and (ii) scheduling tasks onto a processor incurs an overhead.

### 2.2.1 Independent task applications

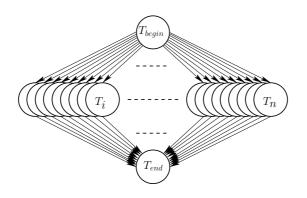

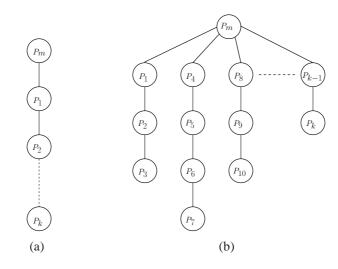

Independent task applications exhibit a very simple DAG structure (see Figure 2.2). In the early research on independent task scheduling, much attention has been devoted to homogeneous multiprocessor systems composed of identical processors interconnected with homogeneous networks [98, 109, 127]. The scheduling complexity of these problems lies in the *task irregularity* assumption, stating that the task processing times vary in an unpredictable manner. Hagerup [98] claims that in practice, task irregularity can arise from *algorithmic variance* - where the nature of the data being processed leads to different execution times - and from *system induced variance* - provoked by external events such as cache misses, operating system interference, clock interrupts, etc.

On the other hand, heterogeneous platforms are becoming widespread, and their efficient utilization requires a good understanding of the added complexity that heterogeneity introduces. For instance, it has been shown that greedy protocols that delegate as much work as possible to the fastest processors are not adapted to the heterogeneity of the platform [36, 161]. Therefore, more advanced techniques are required. In this context, the difficulty of the scheduling problem has been moved from task irregularity to platform heterogeneity. Hence, the research focus has been devoted to scheduling regular independent task applications onto heterogeneous platforms [36, 80, 161].

Figure 2.2: DAG of an independent task application.

#### Scheduling irregular tasks on homogeneous systems

Scheduling irregular tasks gives often rise to bin-packing problems known to be NP-complete. Most of the well-known scheduling heuristics work under the assumption that a fixed overhead incurs each time a bunch of tasks is delegated to a processor, no matter how large the bunch is.

Under this assumption, it appears that *static chunking*, which consists in delegating all the tasks intended to a processor at once minimizes the scheduling overhead. What limits the efficiency of static chunking in practice is the difficulty to accurately estimate the task execution times, which often leads to load unbalance among the processors.

Because one may not have accurate information - or no information at all - on the different task processing times, it might be a good idea to not put all its eggs in the same basket, that is, not send all the tasks intended to a processor at once. This approach is popularly known as *online scheduling*. The simplest strategy of this kind is the *self-scheduling* strategy [64, 98], where tasks are handed out on a one-by-one basis. By construction, the self-scheduling strategy produces a schedule in which the finishing times of the processors differ by at most the processing time of a single task. This is, in a sense, very satisfactory considering that this quantity is assumed to be very small compared to the overall execution time. However, this strategy comes at the expense of a large scheduling overhead in the form of excessive communications. Actually, *self-scheduling* is just the opposite of *static chunking* which minimizes scheduling overhead at the risk of a large load imbalance.

To achieve better tradeoffs, hybrid schemes have been proposed that schedule not all, but several tasks at a time. The idea being that early chunks should be large in order to keep the scheduling overhead small, while smaller chunks are required towards the end of the computation to achieve a good load balance among the processors. Following this principle, a multitude of heuristics using chunks of decreasing sizes have been proposed. Hagerup [98] gives a comprehensive overview of the most popular heuristics.

Bast stresses a subtle point about the task irregularity assumption [23]. When nothing is known about the task processing times, no advantage lies in scheduling several tasks at a time, since in principle a single task might take an equally long time. In these conditions, *self-scheduling* comes out as an optimal scheduling strategy. Therefore, hybrid schemes are meaningful only when there is a kind of *bounded irregularity* of the task processing times, by which it is assumed that a larger number of tasks incurs a larger total processing time than a smaller number of tasks. This bounded irregularity is accounted by so-called *stochastic scheduling* techniques, where the task execution times are modeled as independent, identically distributed random variables with a common probability distribution D having a mean  $\mu > 0$  and a variance  $\sigma > 0$  [98, 109, 127]. Within these settings, Kruskal and Weiss [127] studied the *fixed size chunking heuristic*, that consists in using chunks of a fixed number of tasks. However, the stochastic model complicates greatly the design and performance analysis of heuristics, and very few studies have reported theoretical results under this model.

#### Scheduling regular tasks on heterogeneous systems

When dealing with heterogeneous computing systems, more efforts have been putted into the computing and communication models, at the expense of a simpler task execution times model.

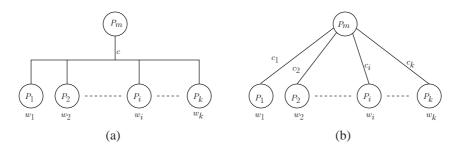

Initially, all the tasks reside on one processor called the master processor  $P_m$ . The tasks will be sent over a network for remote computation by a set of k slave processors  $P_1, \ldots, P_k$ . Further, it is assumed that the master can communicate with the slaves only one at time (single-port model), requiring  $c_i$  time units to communicate with slave  $P_i$ . The number of tasks that can be communicated within  $c_i$  time units depends on the framework of the study. At last, it takes  $w_i$  time units to slave  $P_i$  to process one task.

Two optimization problems have been formulated in the literature [36, 161]. The first one is the traditional makespan minimization problem, while the second one aims at maximizing the throughput of the system, i.e. the number of tasks executed within a given time frame T. Interestingly, if a polynomial time algorithm  $\mathcal{A}$  can be formulated for the throughput maximization problem, then it is possible to solve the makespan minimization problem in polynomial time using algorithm  $\mathcal{A}$  combined with a dichotomic search on T [36]. And vice versa for solving the throughput maximization problem using an algorithm that solve the makespan minimization problem using an algorithm that solve the makespan minimization problem using an algorithm that solve the makespan minimization problem using an algorithm that solve the makespan minimization problem combined with a dichotomic search on the total number of tasks to be processed.

The throughput maximization problem with heterogeneous processors inter-

connected by a bus (see Figure 2.3 (a)) is polynomial in the case when there is only one initial communication per slave [36] (similar to static chunking). In this scenario, the master pays a fixed communication delay c for sending an unbounded number of tasks intended to a slave. The goal is to find the best permutation  $\sigma$  that determines the order in which the slaves should be served. The problem becomes NP-complete when a final communication between the slaves and the master is necessary to send back the computational results. The problem complexity increases significantly because two permutations  $\sigma_1$  and  $\sigma_2$ , one for sending the tasks and one for receiving the results, must now be determined.

Figure 2.3: Bus (a) and "star" (b) networks.

The throughput maximization problem under the assumptions that (i) each task sent to slave  $P_i$  incurs a communication cost of  $c_i$  time units, and (ii) the processors are interconnected by a heterogeneous "star" (see Figure 2.3 (b)), is also polynomial [36]. This result has been extended for heterogeneous linear daisy chains and "spider" graphs (see Figure 2.4), with a polynomial time algorithm for solving the makespan minimization problem [80]. Finally, the problem becomes NP-complete for heterogeneous tree-shaped platforms [81].

### 2.2.2 Divisible load theory

#### **Application model**

The *divisible load* model [43,45,176] embodies applications whose computational workload is composed of a large number of homogeneous low-granularity computations called *work units*. There are no communication dependencies between the work units which can therefore be processed in parallel. The total application workload can hence be split into *chunks* of arbitrary size (each chunk corresponding to a given number of work units), and this in a linear fashion, i.e. the computation and communication time requirements of a chunk are proportional to its size.

The divisible load model has been widely studied, and the *divisible load the*ory (DLT) has emerged as a new scheduling paradigm for distributed computing

Figure 2.4: Linear daisy chain (a) and "spider" graph (b) networks.

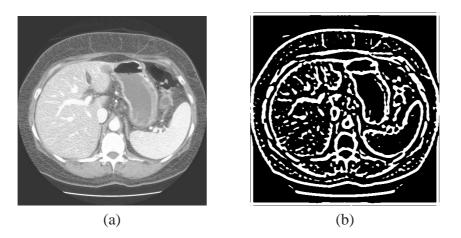

platforms [43]. Many applications have been implemented under this paradigm including image processing (e.g. edge detection [176]), processing of massive experimental data set, signal processing applications [45], pattern searching, file compression, joining operation in relational databases operations, graph coloring or genetic search [76]. This section presents fundamental DLT concepts which are closely related to some of the work presented in this thesis.

#### Framework

The basic DLT assumptions are the following. A system composed of p + 1 processors  $P_0, P_1, \ldots, P_p$  is considered. The processor  $P_0$  called *originator* or *master* plays a particular role. At the beginning of the computation, the whole workload is stored in the memory of the originator processor  $P_0$ . The originator then scatters the workload over the network to the p remote processors, that will process their shares of the workload in parallel. It is widely accepted in the DLT that the return of the computational results to the master can be neglected. This assumption is made for the sake of simplicity, and may not be realistic for some applications. Still, gathering the results to the originator has been incorporated in the DLT model for special cases as shown in [38, 49]. The data scattering and gathering parts are highly dependent of the underlying platform topology and scheduling policy adopted.

#### **Theoretical model**

Typical divisible load models target heterogeneous platforms. We describe below the standard notations used in the DLT literature [45]:

- $\alpha_i$  is the fraction of workload allocated to processor  $P_i$ ,

- $\alpha = (\alpha_0, \alpha_1, \dots, \alpha_p)$  is the load distribution vector,

- $T(\alpha)$  is the makespan associated to load distribution  $\alpha$ ,

- $T_{cp}$  is the time taken to process a work unit by the standard processor,

- $w_i$  is the ratio of the time taken by processor  $P_i$  to compute a given load, to the time taken by a standard processor to compute the same load,

- $T_{cm}$  is the time taken to communicate a work unit on a standard link,

- $z_i$  is the ratio of the time taken by link  $L_i$  to communicate a given load, to the time taken by a standard link to communicate the same load.

The *standard* processor and link might be any processor or link of the platform used as a reference. With these notations, it takes  $\alpha_i w_i T_{cp}$  time units for processor  $P_i$  to process its share  $\alpha_i$  of the load. Similarly, it takes  $\alpha_i z_i T_{cm}$  time units to send the load fraction  $\alpha_i$  over the network link  $L_i$ .

#### **Scheduling policies**

Divisible load models can usually be solved algebraically for optimal allocation to processors and links under a certain *scheduling policy*. The scheduling policy adopted depends of the characteristics of the computing platform targeted in the study. Traditionally, scheduling policies have three components:

- *Load distribution model*: Processors may or may not distribute the load concurrently to several other processors. Under sequential load distribution a processor can communicate load fractions to other processors only one at a time. Conversely, under parallel load distribution, data transmission may happen simultaneously on all communication links.

- *Processor operating mode*: Processors might be equipped *with front-end* or not. A processor equipped with front-end is capable to overlap computation with communication, while a processor without front-end cannot. The *with front-end* model is widely used in the literature, because it seems more representative to actual computing platforms characteristics, albeit the *without front-end* model has been studied as well [35].

- *Communication model*: In most DLT studies, processors are able to communicate only with their neighbors in a *store and forward* fashion. Other communication models such as *store and bypass* [119], circuit or cut-through switching [99] have also been studied.

#### **Optimality principle**

The *optimality principle* is a fundamental result, that grounds the DLT, stating that to obtain optimal processing time - i.e. a minimal makespan - all the participating processors must stop computing at the same time [43, 45]. Intuitively, if the processors stop computing at different times, it is possible to redistribute some of the load from the late processors to the early processors.

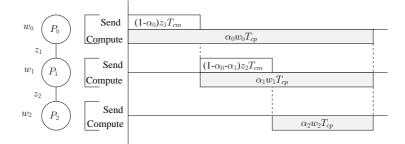

The first architecture to be applied the optimality principle is the daisy chain because of its simplicity. Consider a daisy chain, where processors are equipped with front-ends, communicating under the store and forward model, and with the originator located on a exterior node of the chain. The originator  $P_0$  must send all the load intended to the rest of the chain to its neighbor  $P_1$ , which will subtract its share and forward the rest to its neighbor  $P_2$ , and so on until the last processor has received its share of the load. Hence, we get the following equation set, illustrated by the Gantt-chart given in Figure 2.5:

$$\sum_{i=0}^{p} \alpha_i = 1 \tag{2.1}$$

$$\forall 0 \le i < p, \ \alpha_i w_i T_{cp} = (1 - \sum_{j=0}^i \alpha_j) z_{i+1} T_{cm} + \alpha_{i+1} w_{i+1} T_{cp}$$

(2.2)

Figure 2.5: Load distribution on a 3-processor daisy chain.

Different scenarios have been considered for the daisy chain network, such as the load originating at an interior or exterior node of the chain, and with or without gathering the computational results back to the originator [45].

#### Load distribution sequence

Tree and bus networks allow for better performance than daisy chains, because generating much less communication. Indeed, in a daisy chain, the load intended to processor  $P_k$  must travel through k - 1 links before reaching its destination. The amount of communication generated by the chain topology is hence equal to:

$$\begin{aligned} \mathcal{C}_{chain} &= [(1 - \alpha_0)z_1 + (1 - \alpha_0 - \alpha_1)z_2 + \dots + (1 - \alpha_0 - \dots - \alpha_{k-1})z_k]T_{cm} \\ &= [\sum_{i=1}^k \alpha_i z_1 + \sum_{i=2}^k \alpha_i z_2 + \dots + \alpha_k z_k]T_{cm} \\ &= T_{cm} \sum_{j=1}^k \sum_{i=j}^k \alpha_i z_j \end{aligned}$$

In contrast, the amount of communication generated by a single level tree (or star) network is equal to  $C_{star} = T_{cm} \sum_{i=1}^{k} \alpha_i z_i$ .

As opposed to daisy chains, tree-shaped networks open up the possibility for varying the order or *sequence* of the load distribution among the child processors. This brings about the problem of resource selection, as it has been shown that the optimality principle leads to optimal schedules only for a carefully chosen and ordered subset of child nodes [37, 45].

A recent theorem [37] states that an optimal load distribution for the star network topology is obtained by utilizing all the processors of the network, with a load distribution sequence ordered by increasing link capacities  $z_i$  (fast links first).

But if the load distribution sequence is fixed a priori, then it has been shown that the optimal processing time can be achieved by distributing the load only to "fast" processor-link pairs. An exact expression that distinguishes the fast processor-link pairs from the slow ones has been derived [43], and a *reduced* network can be obtained by removing the slow processor-link pairs. The load is then distributed among the remaining processors using the optimality principle.

#### Installments and sequencing

Under the *with front-end* model, sending all the load intended to the processors in a single message leads to poor utilization of the processors. Indeed, the sequential load distribution imposes that the last processors to be served are waiting idle, while their predecessors in the load distribution sequence are receiving their share of the load. To address this problem, *multi-round* or *multi-installment* algorithms have been proposed [42, 43, 192]. These algorithms dispatch the load in multiple rounds and thus improve overlap of communication with computation.

The two main questions that must be answered when designing multi-round algorithms are: What should the chunk sizes be at each round? And how many rounds should be used? Most of multi-round algorithms assume a fixed number of rounds. A review of multi-round algorithms can be found in [37], but the main observations therein are: (i) dividing the workload into large chunks

reduces communication overhead, (ii) sending small chunks at the beginning of the execution makes it possible to overlap communication with computation and (iii) sending small chunks at the end of the execution leads to better load balance among processors. Not surprisingly, observations (i) and (iii) - that proved useful for scheduling irregular tasks onto homogeneous processors - hold also within DLT settings. Based on these three observations, Casanova and Yang [191] have proposed an algorithm that starts by sending larger and larger chunks, and ends by sending smaller and smaller chunks.

Finally, the linear DLT model may lead to flawed solutions as there is no prohibitive cost for sending large numbers of very small messages [52, 192]. Indeed, the linear model implies that an infinite number of rounds where an infinitesimal amount of work is sent out at each round gives an optimal task allocation. Although an affine model - that accounts for network latencies - addresses this issue and renders the model more realistic, it nevertheless increases significantly the complexity of the problem [37, 192].

#### Network equivalence

A useful concept in DLT is the notion of *network equivalence*, that makes possible to assimilate some network topologies to a unique processor of equivalent power via closed-form expressions or numerical procedures [24]. For instance, these network equivalences can be utilized to show that speedup is bounded from above by a quantity independent of network size, but dependent of network topology [68]. This feature provides a mean to compare the performance of finite configurations of processors against infinite ones [25, 160]. The network equivalence concept proves also to be useful for theorem proving [21, 37].

The network equivalence concept has been successfully applied to several network topologies, including daisy chains [25, 160], arbitrary trees [25, 142] or 2dimensional meshes [46]. Daisy chains - although not very common in practice prove useful in this context, as they serve as a good basis for studying more complex architectures such as 3-dimensional [75] and k-dimensional meshes [134] via network equivalence transformations.

Also, the network equivalence principle allowed to formally identify the impact of sequential load distribution on the performance saturation within DLT networks [25]. Although the speedup increases as the number of processors and installments increase, it nevertheless tends to saturation because of the repetitive overhead in propagating the load into the network. The situation is somewhat similar to Amdahl's law [95] as the communication overhead associated to the load transfer takes place in a sequential fashion [45]. On the contrary, speedup is scalable under the parallel load distribution model, that is when nodes can transmit load simultaneously to all their neighbors [176].

#### **Model extensions**

The divisible load model has been applied successfully to a wide variety of interconnection topologies including daisy chains [160], star graphs [37], hypercubes [135], two, three and k-dimensional meshes [48, 75, 134], and arbitrary trees [142].

The original DLT model has been extended in many ways, including finite memory processor [78], memory hierarchy design of recent computers [79], network latencies [34, 47], processor latencies for initiating a computation [191], processor release times [41], unknown network resources [120], and adaptation to Grid computing [194, 196].

# 2.3 Throughput maximization

### 2.3.1 Performance metric

For applications with very long execution times - typically days or weeks -, two schedules whose durations differ only by a few minutes can be considered as equivalent [32]. In this case, *makespan* minimization might not be the appropriate performance metric. Besides, we saw that makespan minimization greatly complicates the scheduling problem, which can hinder algorithmic design.

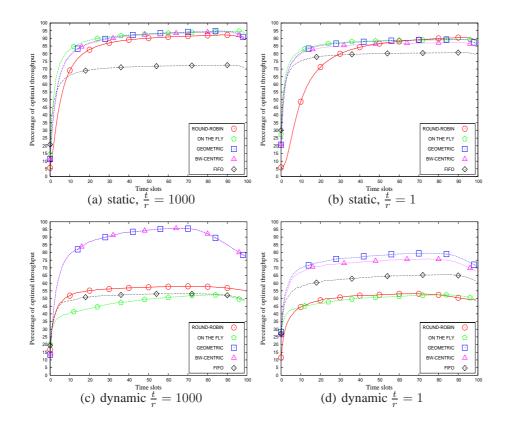

A more meaningful and more practical objective function is *throughput maximization*, that is maximizing the number of tasks executed per time unit [14, 32, 107, 169]. Indeed, deriving asymptotically optimal schedules is very satisfactory for such lengthy applications.

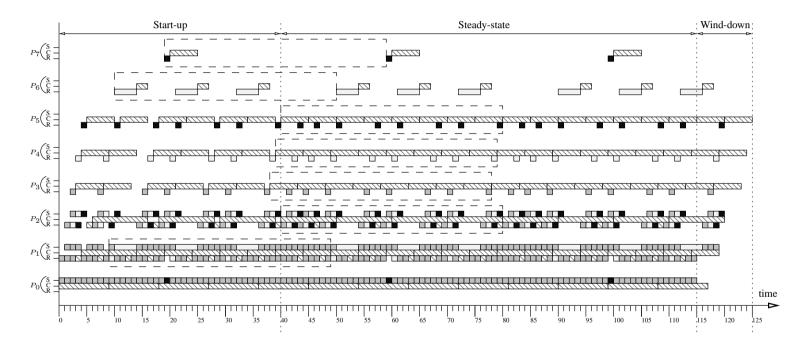

Lengthy executions of independent task applications can be decomposed into three phases: A *start-up* phase, a *steady-state phase* and a *wind-down* phase [126]. During start-up, the computation begins with the master starting to delegate tasks to the slaves. Then, the steady-state regime sees the master sending tasks and receiving results from the slaves in a somewhat regular fashion. And finally, the computation terminates with the *wind-down* phase during which the master collects the last results from the slaves. Since the target applications are expected to run for a very long time, the steady-state phase will dominate the total execution time, such that the *start-up* and *wind-down* phases can reasonably be neglected. This is the main argument for focusing on optimizing the *steady-state* regime.

During steady-state, the initial integer formulation can be relaxed, and replaced by a continuous time model. The goal is to describe the activities of the resources during each time unit: What fraction of time is spent communicating (and with who) and what fraction of time is spent computing. To some extent, this continuous time model is similar to the divisible load model, since both domains can be divided into infinitesimally small quantities. The main difference being that one needs to construct a valid periodic schedule (where an integer number of tasks is treated per time period) based on the resource activity descriptions.

### 2.3.2 Theoretical model

The theoretical models employed in the literature are very similar to DLT models. Usually, the execution time of a task on a processor  $P_i$  is modeled by a single value  $w_i$ , such that processor  $P_i$  requires  $\alpha_i w_i$  time units to compute  $\alpha_i$  tasks. Similarly, it takes  $c_{ij}$  time units to send a task from processor  $P_i$  to processor  $P_j$ . It is possible to have  $c_{ij} \neq c_{ji}$ , that is bandwidth asymmetry on the network links. This linear model is the most common model found in the literature due to its simplicity [30, 106, 161, 169].

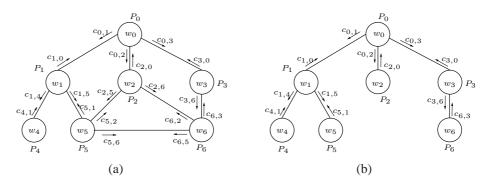

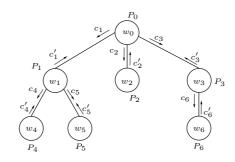

Figure 2.6: Graph network (a) and spanning tree (b).

The two most popular topologies used for modeling complex and large-scale platforms are undirected graphs and spanning trees (see Figure 2.6) [14, 104–106, 126, 169]. Both topologies model the network as sequences of network links or *paths*, that may be shared by several routes, which is necessary to obtain somewhat realistic platform models [52]. The vertices or nodes of the platform represent computing resources capable of computing and/or communicating with their *neighbors* at (possibly) different rates.

Although graph networks provide more general platform models, they nevertheless introduce routing decision making, which greatly complicates the scheduling problem. In contrast, the hierarchical topology of tree networks has the advantage to remove routing decision problems [30, 81, 108, 126, 168]. However, it has been shown that the problem of extracting the best spanning tree from a given network is NP-complete, and that even though such a tree could be found, there exist networks for which the performance of the optimal tree is arbitrarily worse than the whole network performance [14]. Nevertheless, these unusual networks have been constructed to prove the superiority of graphs over trees, and might not be representative of realistic networks.

### 2.3.3 Scheduling policies

Just like DLT models, steady-state models are governed under a certain scheduling policy. Steady-state scheduling policies have also three components:

- *Network interface*: Very similar to the DLT *load distribution model*, a processor may or may not communicate concurrently to several neighbors. The *single-port* model for both incoming and outgoing communication, restricts a processor to open one communication in emission and one in reception simultaneously [14, 30, 108, 126]. At the other end of the spectrum, processors can communicate simultaneously with all their neighbors in emission or reception, which amounts to the *multi-port* model, or *network-flow* model [169]. In between is a model allowing an unbounded number of incoming and outgoing communications to happen simultaneously, but at a restricted rate amounting to the hardware limitation of the network interface [104–107].

- *Processor operating mode*: Processors can perform three basic operations, sending messages, receiving messages and performing computation. The degree of simultaneity and concurrency between these actions depends on the capacity of the target machine. If all activities can be performed simultaneously, then we speak of a *full-overlap* model [14, 106, 169]. At the other end of the spectrum is the *sequential* model where a machine can perform only one activity at a time. Beaumont et al. [29] define a variety of models that cover all the possible combinations of concurrency between the processor activities.

- Communication model: In most literature studies, processors are able to communicate only with their neighbors under the store and forward model. Thus, a task can be processed only after receiving all the data associated with that task. More precisely, if  $P_i$  sends a task to  $P_j$  at time-step t, then  $P_j$  cannot start executing the associated task, or forwarding it before time-step  $t + c_{i,j}$ .

Interestingly, Beaumont et al. [29] showed that any operating model, resulting from a combination of the different overlap and network interface characteristics of a machine can be reduced to the *single-port, full-overlap* model. This is presumably the most powerful argument for the utilization of this model, albeit the communication serialization that comes with it greatly complicates the scheduling problem [32]. Another reason for using this model is that standard communication libraries like MPI [94] and PVM [96], usually use sequential or binomial tree based schemes to support collective communications [181], relying hence only on point-to-point communications.

### **2.3.4** Formulation of the steady-state regime

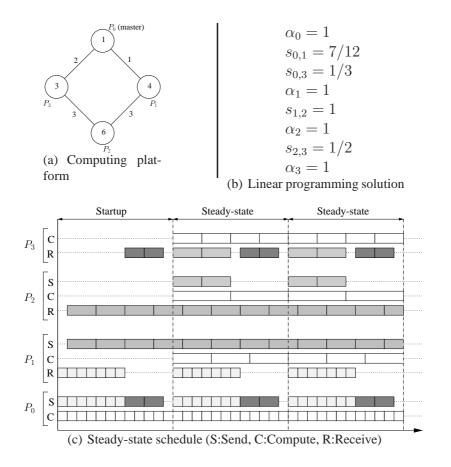

One of the strengths of steady-state scheduling, is the possibility to derive an optimal solution using linear programming techniques. Not only this solution can be used to construct an asymptotically optimal schedule, but it can also be used to evaluate the performance of decentralized heuristics against the optimal solution.

Let us formally express the steady-state scheduling problem on a graph platform G = (V, E, w, c), where each processor  $P_i \in V$  operates under the *singleport, full-overlap* model. Let  $P_m$  denote the master processor, where all the tasks reside initially. To ease the presentation, assume that the size of the task output data is much smaller than the size of the task input data, such that the results collection at the master site can be neglected. We aim at determining the constraints induced by our problem during steady-state.

**Processor operations.** Let n(i) denote the index set of the neighbors of processor  $P_i$ . During one time unit let:

- $\alpha_i$  be the fraction of time spent by  $P_i$  computing,

- s<sub>i,j</sub> be the fraction of time spent by P<sub>i</sub> sending input files to each neighbor processor P<sub>j</sub>, j ∈ n(i),

As these variables correspond to the activity during one time unit, we have the following constraint sets:

$$\forall i, \quad 0 \le \alpha_i \le 1 \tag{2.3}$$

$$\forall i, \forall j \in n(i), \quad 0 \le s_{i,j} \le 1 \tag{2.4}$$

One port model for outgoing communications. Because send operations to the neighbors of  $P_i$  are assumed to be sequential, we have the equation:

$$\forall i, \quad \sum_{j \in n(i)} s_{i,j} \le 1 \tag{2.5}$$

One port model for incoming communications. Because receive operations from the neighbors of  $P_i$  are assumed to be sequential, we have the equation:

$$\forall i, \quad \sum_{j \in n(i)} s_{j,i} \le 1 \tag{2.6}$$

The master  $P_m$  should not receive unprocessed tasks from its neighboring processors, which gives the following equation:

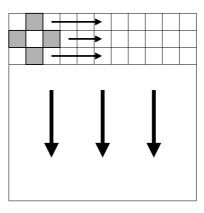

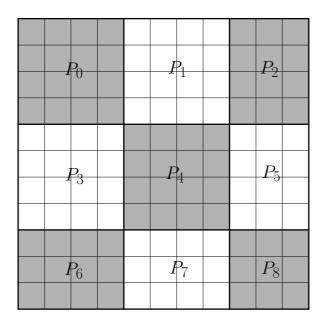

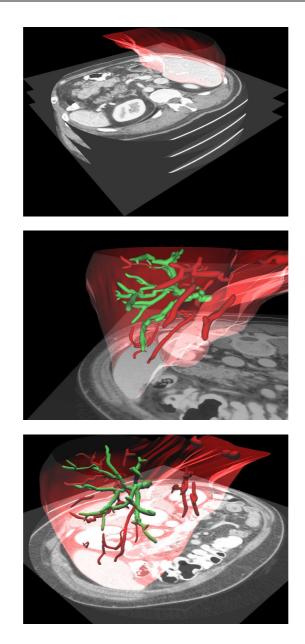

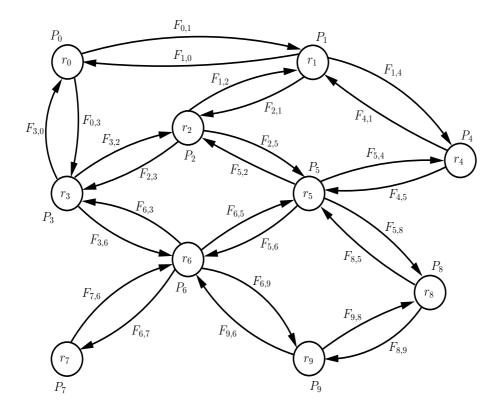

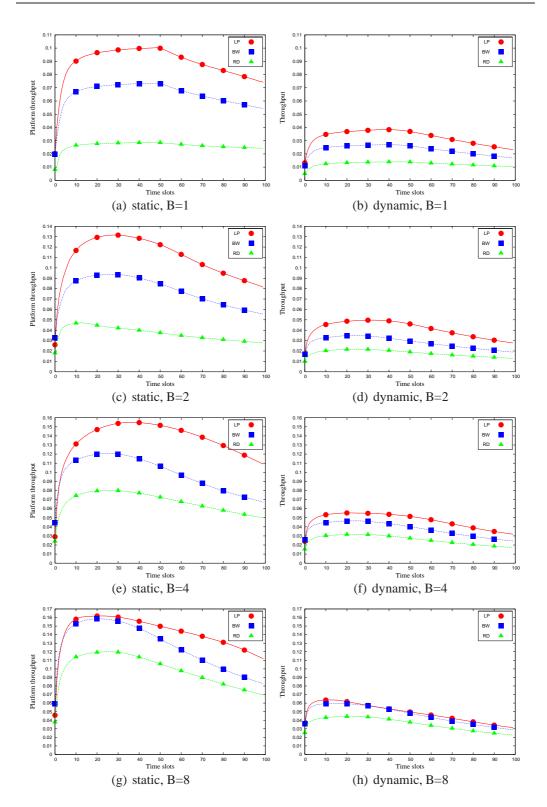

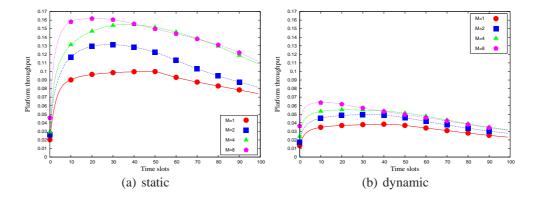

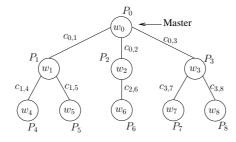

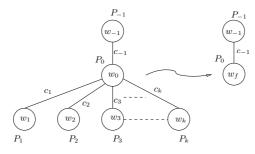

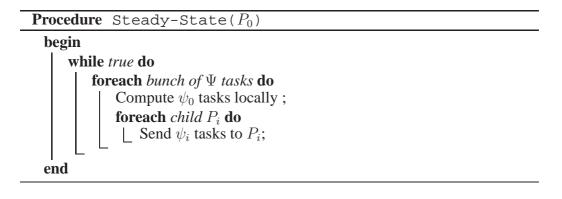

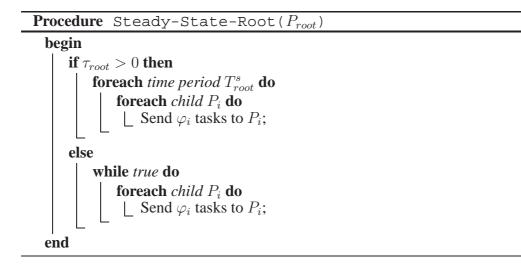

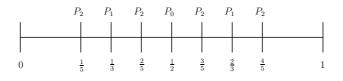

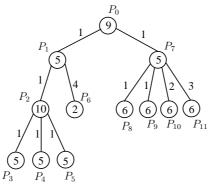

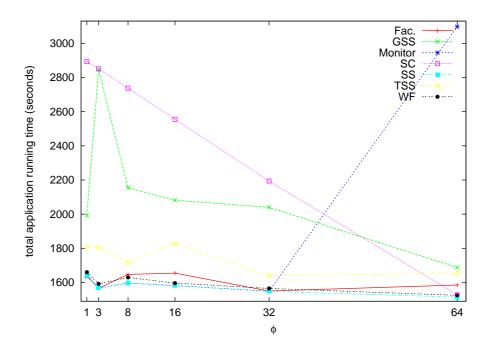

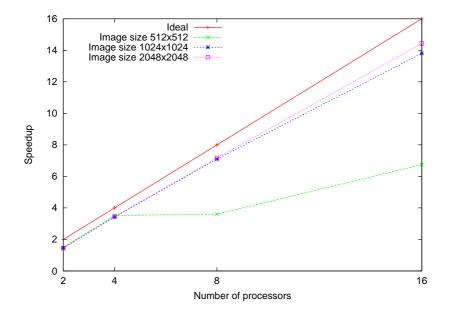

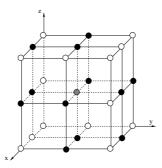

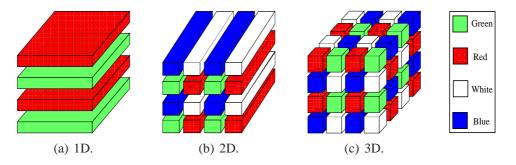

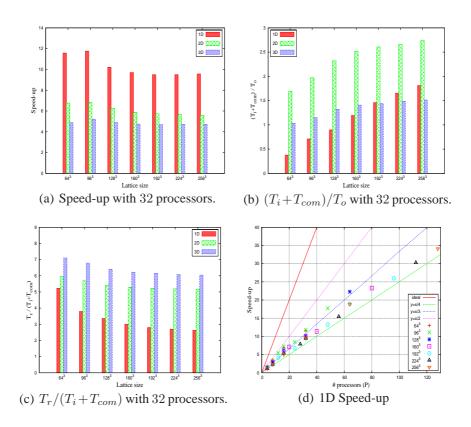

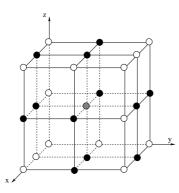

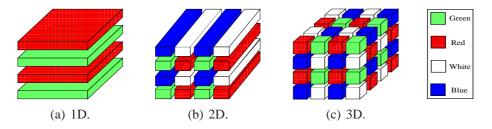

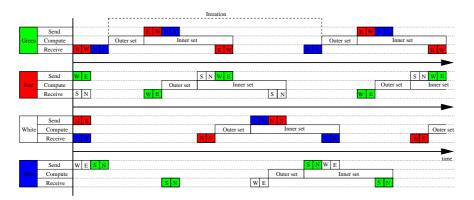

$$\forall j \in n(m), s_{j,m} = 0 \tag{2.7}$$