# Multilevel Power Electronic Converters for Electrical Motor Drives

**Richard Lund**

## Norwegian University of Science and Technology

## Faculty of Information Technology, Mathematics and Electrical Engineering

Department of Electrical Power Engineering

2005

## ISBN 82-471-6995-9

## ISSN 1503-8181

### 2005:62

# **I** PREFACE

All my life I've been fond of technical gadgetry. Why they work, and often after dissembling, why they DON'T.

My first amazement to power electronics, actually without knowing it, was when I bought my first electronic speed controller for my radio-controlled electrical model car (one of many). Right out of the box the car was equipped with a simple speed controller made out of resistors. They got very hot, and the battery went flat all too early. After buying a new electronic speed controller, the car was controlled smoothly, the controller was cold, and my batteries lasted longer. What an invention! Years later, after attending the university, I discovered that the new electronic speed controller was a simple Buck-converter.

After taking power electronics classes at the university, I was hooked on the topic. Controlling large amount of power by electronics, without almost any losses. It was clear, I wanted to work with power electronics.

For my Master's thesis, I was fortunate to do my work at University of Madison, Wisconsin under the supervision of Professor T. A. Lipo at Wisconsin Electric Machines and Power Electronics Consortium (WEMPEC). At WEMPEC I met M. D. Manjrekar, who at that time was a Ph.D. student at the university. He introduced me to multilevel power conversion, and for 6 months I worked with him on the topic. The interest grew, and as I was offered a Ph.D. student position at NTNU, I was very sure that I wanted to work with multilevel converters. The unique mixture of power electronics and environment at WEMPEC brought me back for a few months during spring 2002.

There are many I would like to thank through all these years. First, I would like to thank my advisor Prof. Roy Nilsen for his support over the years, and for his belief in me. Second, I would like to thank all the colleagues at Department of Electrical Power Engineering, NTNU, for their help and support. Two students gave valuable help in the project, and should be noted, a big thanks to Jonas Beverfjord and Christian Dick. A special note of thanks to my colleague Sigurd Øvrebø. For 10 years now, he has been a very good friend and discussion partner. During the last stressful months, Sigurd has been a stable shoulder to cry and laugh on. Thanks again, Sigurd. I owe my family big thanks for their constant support and encouragement, particularly my uncle, Per, for reading through this manuscript. Last but not least I pay gratitude to Lill-Mari for reminding that there are more things in life than power electronics.

Again, thank you all!

The road to the doctoral degree has not always been an easy one. But I've gained a lot of knowledge, both technical and human.

"Minds are like parachutes, they only function when open"

-Thomas Dewar

Richard Lund

Trondheim 10. jan. 2005 Richard Lund

# **II** ABSTRACT

Power electronic converters are widely used in industrial power conversion systems both for utility and drives applications. As the power level increases, the voltage level is increased accordingly to obtain satisfactory efficiency. During the last years, the voltage rating of fast switching high voltage semiconductors such as the Insulated Gate Bipolar Transistor (IGBT) has increased. Still, there is a need for series connection of switching devices. In this area of applications, the Multilevel Converter has shown growing popularity.

The fundamental advantages of the Multilevel Converter topologies are low distorted output waveforms and limited voltage stress on the switching devices. The main disadvantages are higher complexity and more difficult control.

In this thesis, Multilevel Converters are analysed for large motor drive applications. The main focus has been on converter losses, output waveform quality and control.

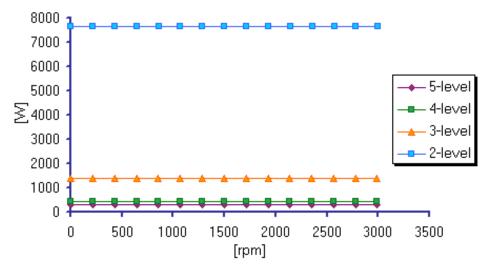

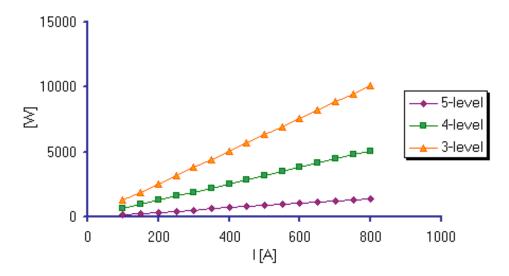

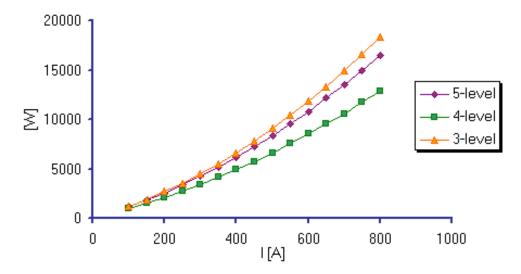

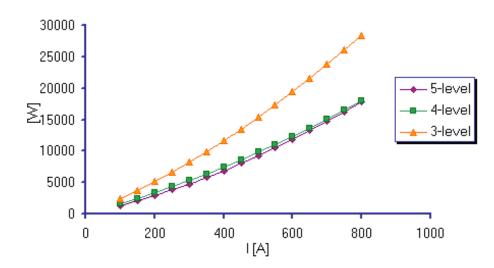

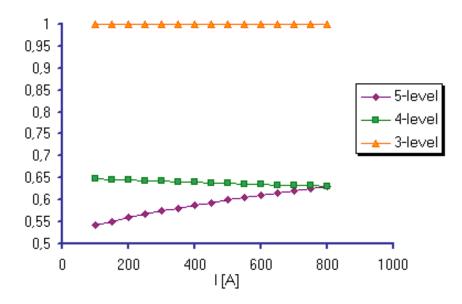

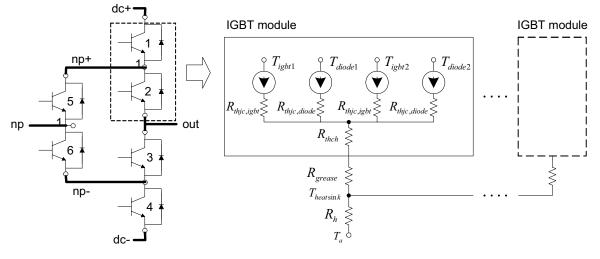

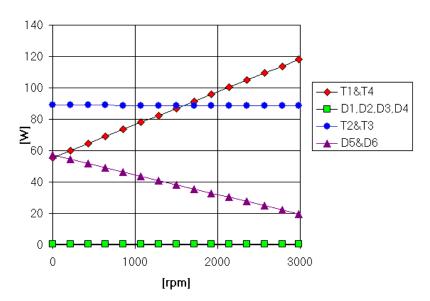

Analytical expressions for both switching and conduction losses for 4- and 5-level Diode Clamped Converters have been developed. The investigation shows that the losses can be reduced by utilizing a multilevel topology for a 1 MW drive. This work is presented in [46]. The same reduction in losses is proven for a 2300V/ 3 MW drive.

Analytical expressions for the harmonic losses in 3-level converters have been developed for 2 different Carrier Based PWM schemes, presented in [56], [57] and [58]. Also Space Vector PWM are investigated and compared by simulations, in addition to 4- and 5-level Carrier Based PWM.

DC-bus balancing in both 3- and 5-level converters is discussed. Balancing in 3-level converters can be achieved by proper control. Balancing in 5-level converters can be achieved by proper arrangement of isolated DC-supplies.

One 40kW 3-level converter and one 5kW 5-level converter has been designed and built. Experimental verification of the analytical and simulated results is shown.

### TABLE OF CONTENTS

| Ι   | PREFAC             | E                                                                                                                                             | I     |

|-----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Π   | ABSTRA             | .ст                                                                                                                                           | . III |

| ΙΝΤ | RODUCT             |                                                                                                                                               | 1     |

|     |                    | TION TO MULTILEVEL CONVERTERS                                                                                                                 |       |

|     |                    | F THE THESIS                                                                                                                                  |       |

| No  | MENCLA             | TURE                                                                                                                                          | 5     |

| 1   |                    | IEW OF MULTILEVEL TOPOLOGIES                                                                                                                  |       |

| -   |                    | DUCTION                                                                                                                                       |       |

|     |                    | GURATIONS WITH DIODE CLAMPS                                                                                                                   |       |

|     |                    | CITOR CLAMPED CONVERTERS                                                                                                                      |       |

|     |                    | LEVEL MULTIPLE THREE-PHASE CONVERTERS                                                                                                         |       |

|     |                    | ADED MULTICELL CONVERTERS                                                                                                                     |       |

|     |                    | RALIZED MULTILEVEL CONVERTER                                                                                                                  |       |

| 1.  | 7 COMPA            | ARISON OF TOPOLOGIES                                                                                                                          | .16   |

| 2   | Μοριι              | ATION STRATEGIES FOR MULTILEVEL CONVERTERS                                                                                                    | 10    |

| -   |                    | VIEW OF MODULATION STRATEGIES                                                                                                                 |       |

|     |                    | IRONOUS MODULATION                                                                                                                            |       |

|     |                    | ndamental Frequency Modulation                                                                                                                |       |

|     | 2.2.2 Pro          | ogrammed PWM                                                                                                                                  | .24   |

|     |                    | CHRONOUS MODULATION                                                                                                                           |       |

|     |                    | rrier Based PWM                                                                                                                               |       |

|     |                    | ace Vector PWM                                                                                                                                |       |

|     | -                  | ER BASED PWM VS. SPACE VECTOR PWM FOR MLC                                                                                                     |       |

| 3   | ANALY              | FICAL LOSS CALCULATIONS                                                                                                                       | .45   |

| 3.  |                    | YTICALLY METHOD FOR CALCULATING DISCONTINUOUS CURRENTS                                                                                        |       |

|     |                    | odelling the conducting losses                                                                                                                |       |

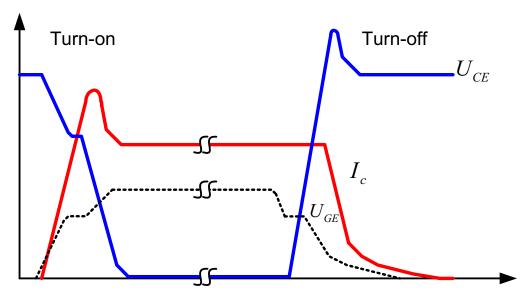

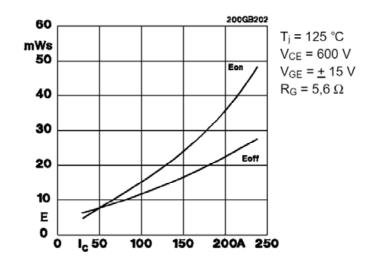

|     |                    | odelling the switching losses                                                                                                                 |       |

| 3.2 |                    | HING SIGNALS AND LOAD CURRENTS                                                                                                                |       |

| 3.  | 3 3-LEVE           | EL CONVERTER                                                                                                                                  | .49   |

| 3.4 | 4 4-LEVE           | EL CONVERTERS                                                                                                                                 | .52   |

|     | 3.4.1 To           | pology and performance                                                                                                                        | . 52  |

|     | 3.4.2 Co           | nducting losses                                                                                                                               | .55   |

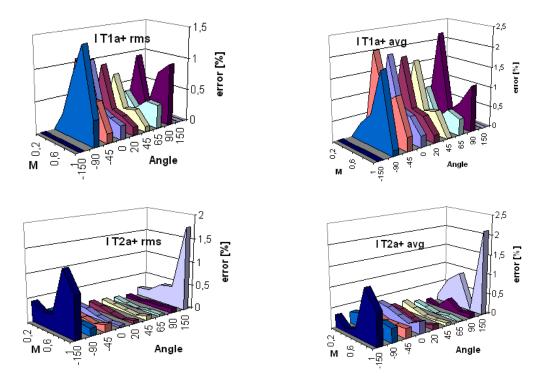

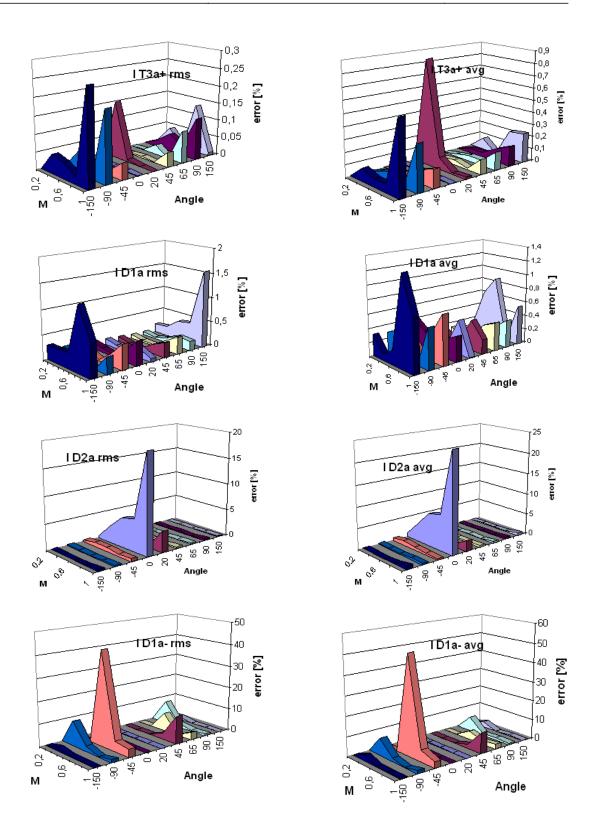

|     | 3.4.2.1            | For $T_{1a^+}$ and $T_{3a^-}$                                                                                                                 |       |

|     | 3.4.2.2            | For $T_{2a^+}$ and $T_{2a^-}$                                                                                                                 |       |

|     | 3.4.2.3            | For $T_{3a+}$ and $T_{1a-}$                                                                                                                   |       |

|     | 3.4.2.4<br>3.4.2.5 | For the freewheeling diodes $D_{1a}$ , $D_{2a}$ , $D_{3a}$ , $D_{1a+}$ , $D_{2a+}$ and $D_{3a+}$<br>For clamping diodes $D_{1a}$ and $D_{4a}$ |       |

|     | 3.4.2.6            | For clamping diodes $D_{1a}$ and $D_{4a}$                                                                                                     |       |

| 3.4.3 Switching losses                                                                                  | 65        |

|---------------------------------------------------------------------------------------------------------|-----------|

| 3.4.3.1 For $T_{1a^+}$ and $T_{3a^-}$                                                                   |           |

| 3.4.3.2 $T_{2a+}$ and $T_{2a-}$                                                                         | 67        |

| 3.4.3.3 For $T_{3a^+}$ and $T_{1a^-}$                                                                   |           |

| 3.4.3.4 For freewheeling diodes $D_{1a-}$ , $D_{2a-}$ , $D_{3a-}$ , $D_{1a+}$ , $D_{2a+}$ and $D_{3a+}$ | 69        |

| 3.4.3.5 For clamping diodes $D_{Ia}$ and $D_{4a}$                                                       |           |

| 3.4.3.6 For clamping diodes $D_{2a}$ and $D_{3a}$                                                       |           |

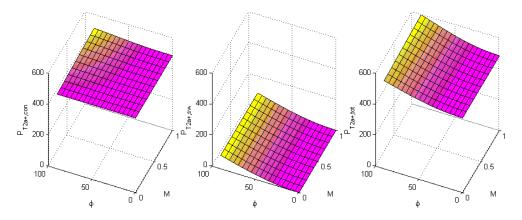

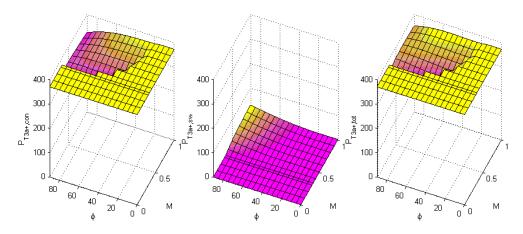

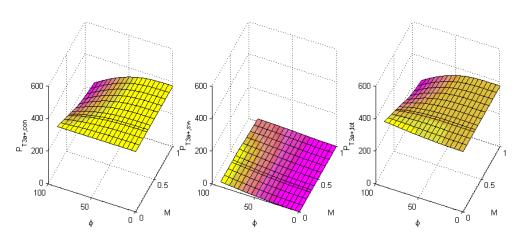

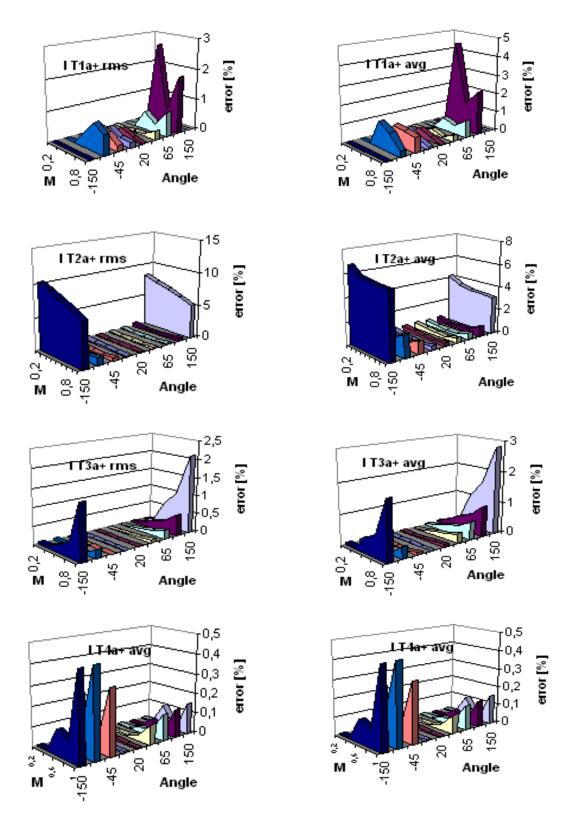

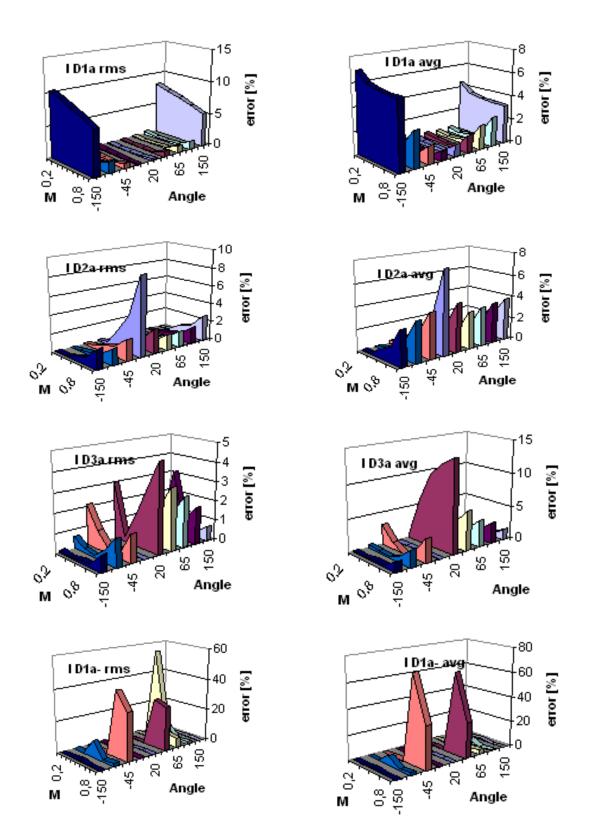

| 3.4.4 Evaluation of the expressions                                                                     | 73        |

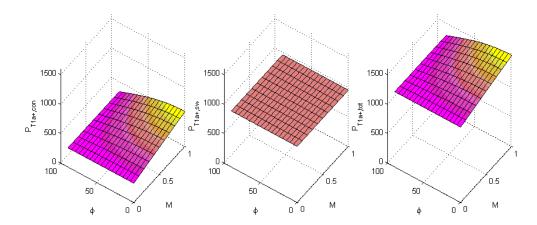

| 3.5 5-LEVEL CONVERTER                                                                                   | 74        |

| 3.5.1 Topology and performance                                                                          | 74        |

| 3.6 CONCLUSION                                                                                          | 76        |

| 4 Loss Calculations- Case Studies                                                                       | 79        |

| 4.1 DRIVE PARAMETERS                                                                                    |           |

| 4.2 LOSSES WITH CONSTANT DC-BUS VOLTAGE                                                                 |           |

| 4.3 LOSSES AT EQUAL DEVICE VOLTAGE UTILIZATION                                                          |           |

| 4.4 Losses in Medium Voltage Drives                                                                     |           |

|                                                                                                         |           |

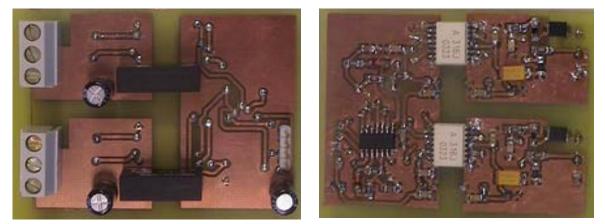

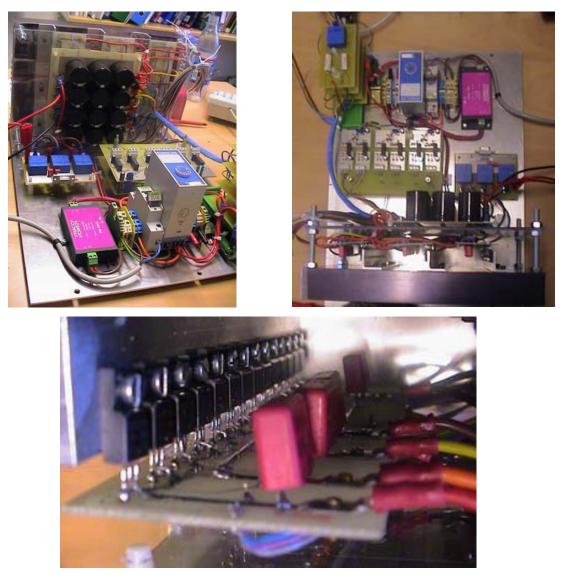

| 5 CONSTRUCTION OF PROTOTYPES                                                                            | 91        |

| 5.1 3-LEVEL 40KW IGBT CONVERTER                                                                         | 91        |

| 5.1.1 Dimensioning of the switching components                                                          | 91        |

| 5.1.2 Sizing of the DC-bus capacitors                                                                   |           |

| 5.1.3 Schematic overview of the components                                                              |           |

| 5.1.4 DC-bus layout                                                                                     |           |

| 5.1.5 Dual-pulse switching                                                                              |           |

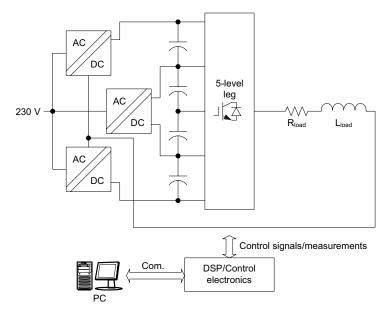

| 5.2 5-LEVEL 3KW IGBT CONVERTER                                                                          |           |

| 5.2.1 Main power circuit                                                                                |           |

| 5.2.2 Gate driver                                                                                       |           |

|                                                                                                         |           |

| 6 HARMONICS                                                                                             |           |

| 6.1 HARMONIC CURRENT                                                                                    |           |

| 6.2 ANALYTICAL CALCULATIONS OF HARMONIC CURRENT FOR 3-                                                  | LEVEL PWM |

|                                                                                                         |           |

| 6.2.1 Symmetry and space vectors                                                                        |           |

| 6.2.2 Method of derivation                                                                              |           |

| 6.2.3 Analytical equations for pure sinusoidal CBPWM                                                    |           |

| 6.2.4 Analytical equations for sinusoidal CBPWM with 3 <sup>rd</sup> harn                               |           |

|                                                                                                         | •         |

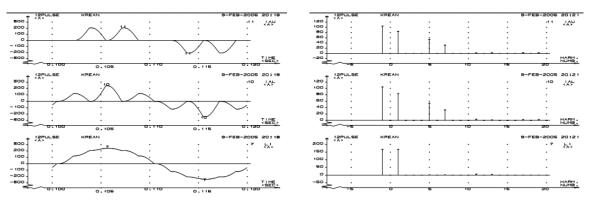

| 6.2.5 Verification by experiments                                                                       |           |

| 6.3 SIMULATED HARMONICS FOR 3-LEVEL PWM                                                                 |           |

| 6.4 HARMONICS FOR 4-LEVEL AND 5-LEVEL PWM                                                               |           |

| 6.5 CONCLUSION                                                                                          |           |

|                                                                                                         | 118       |

| 7 DC-BUS BALANCING                                                                                      | 119       |

| 7.1 SWITCHING FUNCTIONS                                                                                 | 119       |

| 7.2 EVALUATION OF THE METHOD                                                                            |           |

| 7.3 DC-BUS BALANCING IN 3-LEVEL CONVERTERS           |     |

|------------------------------------------------------|-----|

| 7.3.1 Switching vectors and current flow             |     |

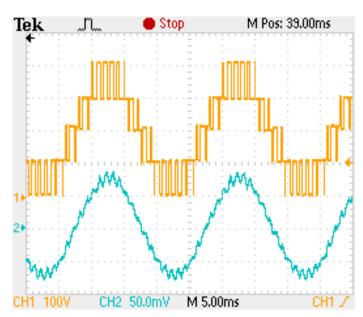

| 7.3.2 Experimental verification                      |     |

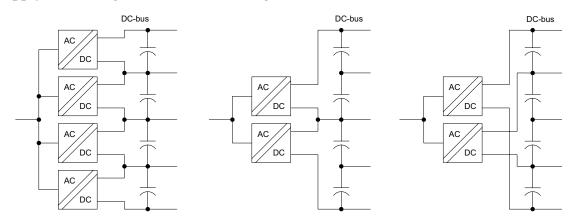

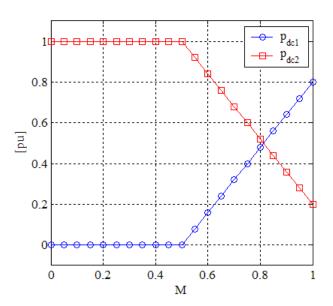

| 7.4 DC-BUS BALANCING IN 5-LEVEL CONVERTERS           |     |

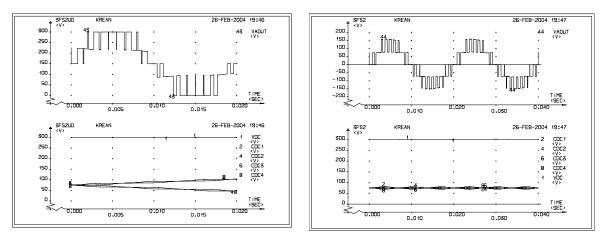

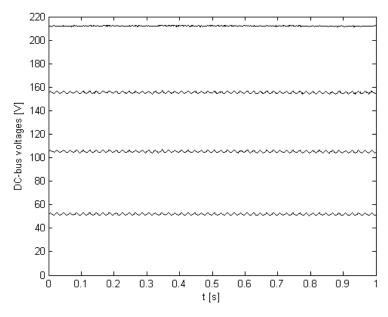

| 7.4.1 Simulation of DC-bus balancing                 |     |

| 7.4.2 Verification by experiment                     |     |

| 7.4.3 Rectifier solutions in 5-level converters      | 135 |

| 7.5 CONCLUSIONS                                      |     |

| 8 CONCLUSIONS AND SCOPE OF FURTHER WORK              | 139 |

| 8.1 DISCUSSION AND CONCLUSION                        |     |

| 8.2 SCOPE OF FURTHER WORK                            |     |

| 9 REFERENCES                                         |     |

| APPENDIX                                             | 149 |

| A RESULTS FROM SIMULATIONS OF A 4-LEVEL CONVERTER    |     |

| <b>B</b> Loss Calculations for 5-level Converters    | 151 |

| B.1 SWITCHING LOSSES                                 | 151 |

| B.1.1 M > $1/2$                                      | 151 |

| B.1.2 M < $1/2$                                      | 156 |

| B.2 CONDUCTING LOSSES                                |     |

| B.2.1 M>1/2                                          | 157 |

|                                                      |     |

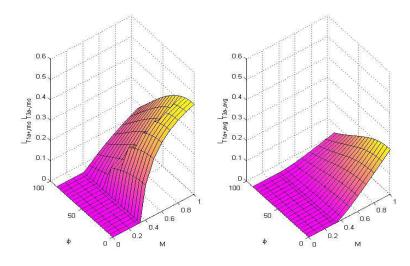

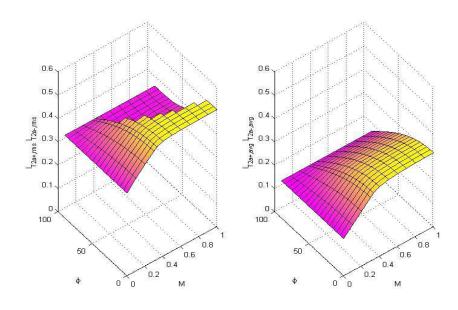

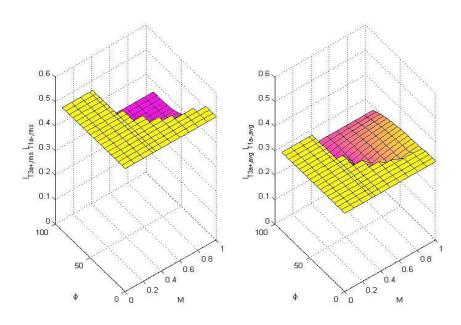

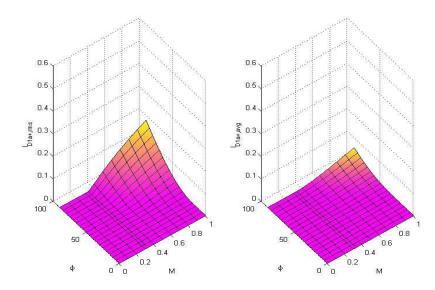

| B.2.2 M < 1/2<br>B.2.3 Evaluation of the expressions |     |

## INTRODUCTION

### **Introduction to Multilevel Converters**

Multilevel Converters (MLCs) have been attracting attention in recent years, and have been proposed as the best choice in several medium and high voltage applications. Such applications can be Static VAr Compensators [1] and Large Electrical Drives, as in [2] and [3].

In the extrapolation of converters to higher power levels, the fundamental question of increasing the converter current rating (devices in parallel) or the converter voltage rating (devices in series) always has to be answered. The conduction losses in converters favour the increased voltage approach. All these factors contribute to the necessity for multilevel converter topologies or series connection of devices in traditional converter topologies.

As mentioned, for high voltage applications, the main advantage of a multilevel structure is the active clamping of the voltage levels. Series connections in traditional solution for high power converters is complex with fast switching devices because of simultaneous switching and correct static and dynamic voltage sharing of series devices.

Other advantages for the MLC topologies are lower distortion at the output, reduced EMC/EMI problems and in some cases, lower overall losses. The disadvantages are more complex control and increased mechanical complexity.

MLCs have also been shown to be a promising technology for low voltage and low power applications by using MOSFETs instead of IGBTs. Low voltage power-MOSFETs have achieved a significant cost advantage at about 5:1 compared to IGBTs, because of the widespread use in automotive and power supplies industry [5]. In [5], a 3-level converter for low power drives (1kW/110V) is developed using modest priced 150V MOSFETs. In [30], a multilevel converter for automotive dual (14V/42V) battery system is presented. A switch-mode power

amplifier is constructed in [6]. This MOSFET based cascaded H-bridge converter has a rating of  $\pm 100V/100A$ .

Numerous topologies and modulation strategies have been introduced and widely studied in literature, as presented in Chapter 1 and 2. Thanks to the high technological level of new power devices, especially the IGBT, these converters have gained more attention than current source converters in the high power applications the last years. For high power electrical motor drives the 3-level diode clamped converter, originally named Neutral Point Clamped (NPC) converter was one of the first topologies [11] that attracted attention.

Several large vendors have adopted this 3-level topology for their medium voltage drives. ABB is using the 3-level topology in both their ACS 1000 and ACS 6000 series, with output voltages from 2.3 kV to 4.16 kV, and power range from 315 kVA-27 MVA [7]. Siemens SIMOVERT MV [8] is also utilising this topology with voltage and power range 2.3 kV-6.6 kV and 660 kVA-9 MVA, respectively. Not only European vendors, but also Asian vendors such as Mitsubishi employ the popular 3-level converter [10].

Other vendors have adopted other topologies for their converters. Robicon [25] is using a Cascaded Multicell topology for their medium voltage drives. One of the disadvantages of this topology is the need for isolated DC-bus supplies. Robicon is using a multi-winding transformer on the input side to accomplish this. Hence, input currents with very low distortion are generated. Alstom has introduced a new series of converters in the medium voltage range called SYMPHONY [9]. The topology used is a capacitor clamped converter with a 4-level output voltage.

Even though there exist several topologies on the market, the diode clamped converter seems to be the most popular multilevel converter topology.

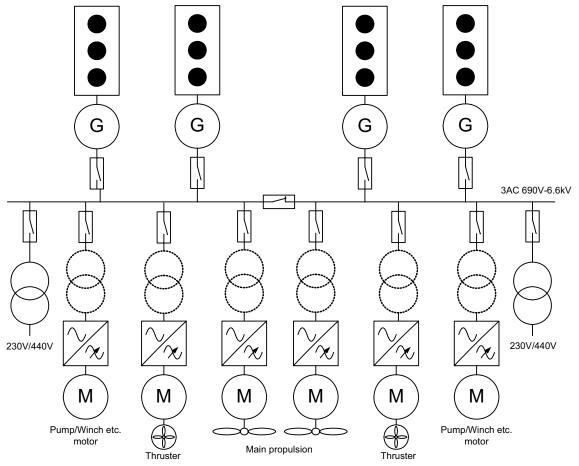

An ongoing research project at NTNU, called *All Electric Ship* is dealing with issues in electrification of ships. Applications could be main propulsion, positioning thrusters, winches and actuation etc. A typical system of such a system is shown in Figure 0.1.

For main propulsion in the megawatt range, multilevel conversion is a promising alternative. The maximum power rating of low voltage Pulse Width Modulated (PWM) converter drives is limited by practical current ratings such as motor and cables (~2500A). Hence at the widely used 690V voltage, the limit today is ~3 MVA [7]. Even though improved components and knowledge move this limit up to 5 MVA, motor and converter manufacturers prefer the medium voltage range (2.3 kV-6.6 kV) at this power level. Also, as more electrical equipment is introduced in the ship, the power consumption is increased, and it is likely to believe that medium voltages become more common in the main supply. Direct connection to this voltage is preferable to avoid transformers, thus the need for high voltage converters is increasing.

The wish for a solution without a transformer omits the cascaded multi cell topology, leaving only the diode clamped and the capacitor clamped topologies as alternatives. Since the diode clamped converter is the most common, the work in this thesis is mainly concentrated on this topology.

Figure 0.1: Typical all electric ship system.

### **Outline of the Thesis**

The thesis is organized into eight different chapters, each chapter covering important aspects of Multilevel Converters (MLCs). Many MLC topologies have evolved the last decade, and Chapter 1 gives an overview of the state of the art of different Multilevel Converter topologies.

In addition to all the different topologies presented the last years, a corresponding amount of modulation schemes have been developed. Both synchronous and asynchronous Pulse Width Modulation (PWM) is presented. Carrier based PWM and Space Vector PWM (SVPWM) are investigated in detail. Simulation models for the different modulation methods have also been developed.

One of the main parts of this thesis is the investigation of the switching and conduction losses for MLCs. Chapter 3 presents analytical expressions for

calculation of the conduction- and switching losses for 4- and 5-level Diode Clamped Converters. By this, a direct comparison to utilization of different switches in the same topologies, and comparison between different topologies can be performed without time consuming simulations.

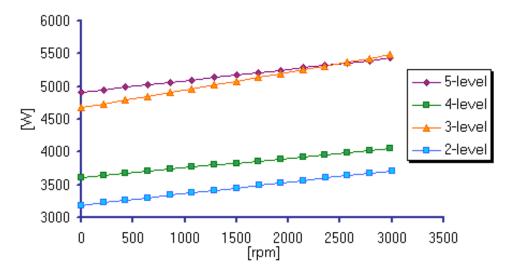

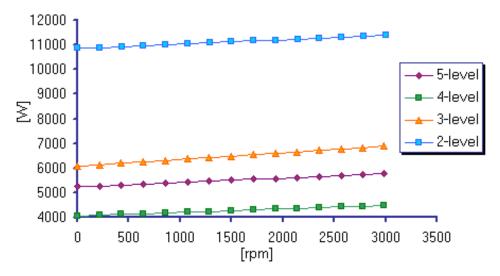

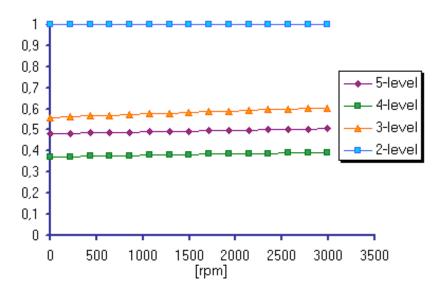

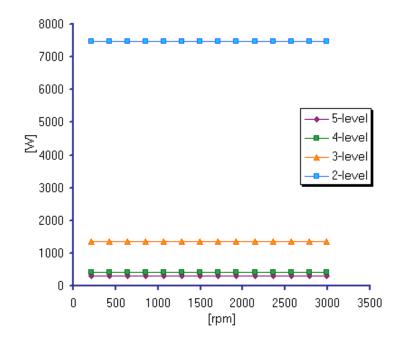

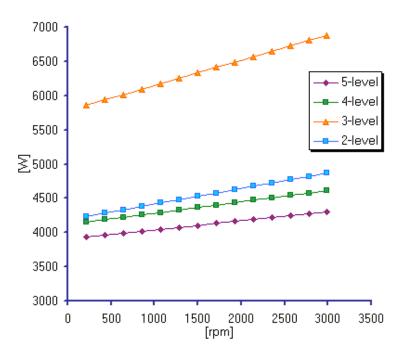

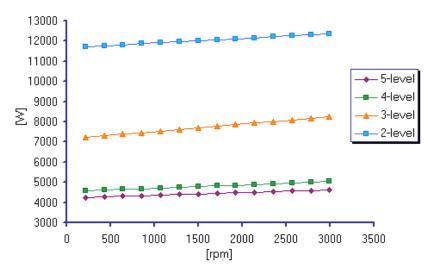

This comparison is performed in Chapter 4. A 1 MW/1500 V converter based on 2-, 3-, 4- and 5-level topologies, and a 3 MW/ 2300 V converter (3-, 4-, 5-level) are analysed and compared.

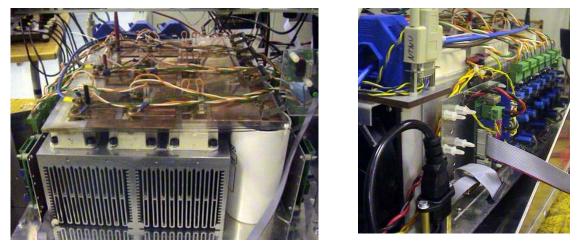

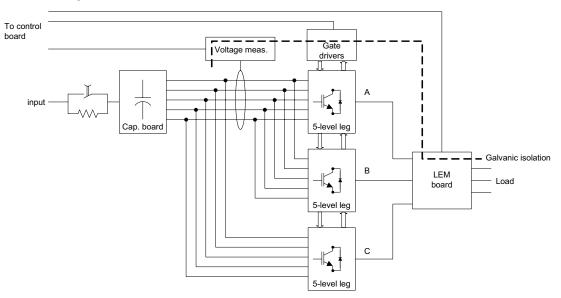

To verify the theory and simulations of harmonics and DC-bus balancing, laboratory models have been designed and built. A short presentation of a 40 kW 3-level, and a 5 kW 5-level converter is shown in Chapter 5.

In Chapter 6, the harmonic losses at the output of MLCs are analysed. For the 3level converter, analytical equations are simplified and developed for two different modulation techniques. Extensive simulations are performed for other kinds of modulation strategies for the 3-level topology, and also for 4- and 5-level topologies. The analytical expressions and simulations are supported by measurements in the laboratory.

One important area of research in MLC is the DC-bus balancing of the capacitor voltages in the DC-link. Problem description and simulation models are developed in Chapter 7 for 3-level and 5-level converters. Measurements on the experimental prototypes are performed for verification of the theory.

Finally, conclusions, discussion and scope of further work are presented in Chapter 8.

In this thesis, different computer programs have been utilized to simplify the analysis: MATLAB [68] has been used for general analysis, numerical modelling and general plotting, KREAN [67] and Saber Designer [70] have been used for electrical circuit analysis, and MAPLE [69] has been a valuable tool for analytical mathematics. In addition, Microsoft Office has been used for typing the manuscript and for making spreadsheets.

# NOMENCLATURE

| $lpha_i$                                     | : Switching angle                                                       |

|----------------------------------------------|-------------------------------------------------------------------------|

| $\underline{\alpha}^{s}$                     | : $\alpha$ -axis vector, stator coordinates                             |

| $\underline{\beta}^{s}$                      | : $\beta$ -axis vector, stator coordinates                              |

| $\zeta_s^s$                                  | : Angle of reference voltage vector w.r.t. $\underline{\alpha}^{s}$     |

| $\zeta_s^{s'}$                               | : Angle of reference voltage vector w.r.t. nearest $\underline{u}_{L1}$ |

| ω                                            | : Angular speed                                                         |

| arphi                                        | : Phase angle                                                           |

| $\varphi_1, \varphi_2, \varphi_3, \varphi_4$ | : Crossing angles between switching areas                               |

| <u>a</u>                                     | : Scaling space vector                                                  |

| $a_{\alpha}, a_{\beta}$                      | : Coordinates of left corner of transformed vector space                |

| $b_{lpha},b_{eta}$                           | : Coordinates of right corner of transformed vector space               |

| CSI                                          | : Current Source Inverter                                               |

| С                                            | : Capacitor                                                             |

| $c_{\alpha}, c_{\beta}$                      | : Coordinates of upper/lower corner of transformed vector space         |

| DSP                                          | : Digital Signal Processor                                              |

| d                                            | : Duty cycle                                                            |

| $D_{ij}$                                     | : Diode, number i in phase j                                            |

| E(I)                                         | : Dynamic switching energy                                              |

| $E_{REC}$              | : Diode turn-off energy                    |

|------------------------|--------------------------------------------|

| $E_{ON}, E_{OFF}$      | : Transistor switching energy, turn on/off |

| $ESR_n$                | : Equivalent Series Resistance             |

| F                      | : Generalized function                     |

| $f_s$                  | : Fundamental output frequency             |

| $f_{sw}$               | : Switching frequency                      |

| f                      | : frequency                                |

| GTO                    | : Gate Turn-off Thyristor                  |

| H(i)                   | : Peak harmonic component                  |

| $h_{_{ji}}$            | : switching function element               |

| Н                      | : switching function element               |

| i                      | : Current                                  |

| i                      | : General integer                          |

| <u>I</u> <sub>in</sub> | : DC-bus current vector                    |

| $\underline{I}_{out}$  | : Converter output current vector          |

| $i_{np}$               | : Neutral point current                    |

| $I_{C}$                | : Collector current                        |

| $I_{C,N}$              | : Rated collector-emitter current          |

| $I_{cap,rms,n}$        | : Harmonic capacitor RMS current           |

| $\Delta i_{_N}$        | : Ripple current                           |

| $\Delta i_n$           | : Nominal ripple current                   |

| $\Delta I_{N,rms}$     | : RMS ripple current                       |

| Î                      | : Peak current                             |

| I <sub>avg</sub>       | : Average current                          |

| I <sub>rms</sub>       | : RMS current                              |

| $I_{cap,rms,n}$        | : Harmonic capacitor RMS current           |

| IGBT                    | : Insulated Gate Bipolar Transistor              |

|-------------------------|--------------------------------------------------|

| j                       | : General integer                                |

| j                       | : Phase index, j=a, b, c                         |

| j                       | $\therefore \sqrt{-1}$                           |

| k                       | : General integer, k=1,                          |

| $k_{1,T}, k_{2,T}$      | : Switching loss constants                       |

| MOSFET                  | : Metal Oxide Field Effect Transistor            |

| MLC                     | : Multilevel Converter                           |

| М                       | : Modulation index                               |

| $m_{ji}$                | : Average switching function                     |

| $M_{s}$                 | : Modulation index for SVPWM                     |

| $M_{3}$                 | : Modulation index for 3. harm signal            |

| п                       | : Number of output levels in converter structure |

| n <sub>cell</sub>       | : Number of converter cell                       |

| NPC                     | : Neutral Point Clamped                          |

| <i>n<sub>uout</sub></i> | : Number of available switch combinations        |

| PWM                     | : Pulse Width Modulation                         |

| $P_{sw}$                | : Switching losses                               |

| $P_c$                   | : Conduction losses                              |

| $P_{c,out}$             | : Converter output voltage                       |

| $P_{cap,tot}$           | : Total capacitor power losses                   |

| RMS                     | : Root-Mean-Square value                         |

| $r_{f}$                 | : Forward conducting resistance                  |

| $S_{j}$                 | : Multi pole switch                              |

| SVPWM                   | : Space Vector Pulse Width Modulation            |

| $T_{ij}$                | : Transistor, number i in phase j                |

| $T_{sw}$                | : Switching period                               |

|                         |                                                  |

| $T_p$                                                            | : Fundamental period              |

|------------------------------------------------------------------|-----------------------------------|

| t                                                                | : Time                            |

| τ                                                                | : Sample time                     |

| Т                                                                | : Time period                     |

| Т                                                                | : Temperature                     |

| $t_{\mu}$                                                        | : Microscopic time                |

| $U_{_{dc}}$                                                      | : DC-bus voltage                  |

| $u_{trii}(t)$                                                    | : Carrier signal, number i        |

| $u_{stj}(t)$                                                     | : Control signal, j=a, b, c       |

| $u_{stj}^{'}(t), u_{stj}^{"}(t), u_{stj}^{"}(t), u_{stj}^{"}(t)$ | : Modified control signals        |

| $\underline{U}_0$                                                | : Zero voltage vector             |

| $\underline{U}_{S1}$ , $\underline{U}_{S2}$                      | : Small voltage vectors           |

| $\underline{U}_{M}$                                              | : Medium voltage vectors          |

| $\underline{U}_{L1}$ , $\underline{U}_{L2}$                      | : Large voltage vectors           |

| $\underline{\mathcal{U}}_U$                                      | : Induced voltage vector          |

| $\underline{U}_{out}$                                            | : Converter output voltage vector |

| $\underline{U}_{in}$                                             | : DC-bus voltage vector           |

| $\underline{\mathcal{U}}_{st,ref}$                               | : Reference voltage vector        |

| $u_{com1}(t), u_{com2}(t)$                                       | : Common mode injection signals   |

| $U_{f}$                                                          | : Dynamic forward voltage         |

| $U_{f0}$                                                         | : Static forward voltage          |

| $U_{\scriptscriptstyle CE}$                                      | : Collector–emitter voltage       |

| $U_{\scriptscriptstyle GE}$                                      | : Gate-emitter voltage            |

| VSI                                                              | : Voltage Source Inverter         |

# 1 OVERVIEW OF MULTILEVEL TOPOLOGIES

#### 1.1 Introduction

During the last 20 years, several multilevel converter topologies have evolved. A brief presentation of the different topologies is presented in the following.

The multilevel converter main components are an array of power semiconductor switches and a stack of capacitor voltage sources.

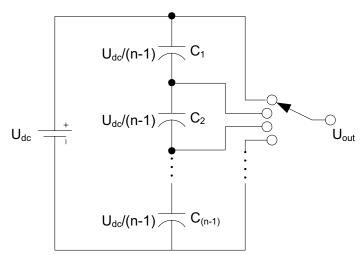

Figure 1.1: One phase leg of a generalized n-level converter.

By connecting the output of the converter to the stack of capacitors a multilevel output voltage is achieved. Figure 1.1 shows one phase leg of a generalised *n*-level converter. It consists of a DC-source, *n*-1 capacitors, and a *n*-pole switch. By connecting the switch to different poles, *n*-levels can be synthesised at the output terminal with respect to the negative DC-rail.

#### 1.2 Configurations with Diode Clamps

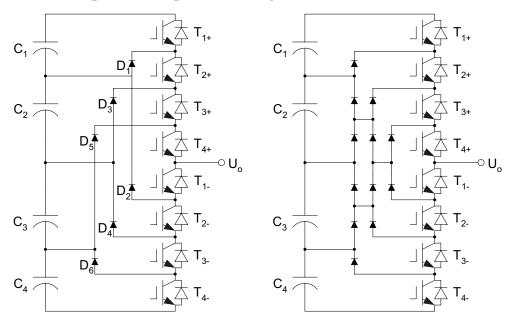

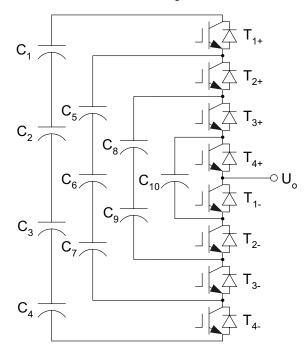

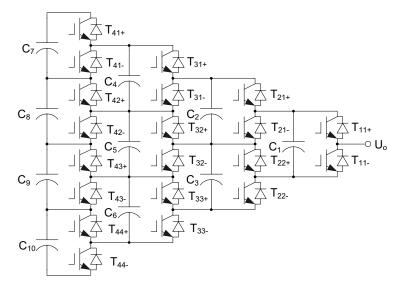

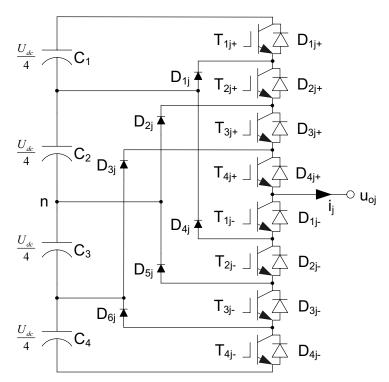

The oldest reference to multilevel power conversion is often stated to start with the paper presented by Nabae et al. [11]. The resultant PWM waveform from this Neutral Point Clamped (NPC) topology (3-level) showed considerably better spectral performance compared to a conventional PWM VSI (2-level). This NPC converter has been extended to higher number of levels in [14]. Figure 1.2 (left) shows one phase-leg of a 5-level Diode Clamped Converter. One phase leg consists of  $2 \cdot (n-1)$  active switches and (n-1)(n-2) clamping diodes. The total DC-bus voltage  $U_{dc}=4V$  is evenly distributed across the DC-capacitors,  $C_1$ - $C_4$  ( $U_{C1}=U_{C2}=U_{C3}=U_{C4}=V$ ). Hence, an output voltage of 0, V, 2V, 3V and 4V is possible at the output with respect to the negative DC-rail.

Figure 1.2: 5-level Diode Clamped Converter: Conventional (left). Pyramid connected clamping diodes (right).

These five levels are obtained by closing a set of four switches (Table 1-1). This creates a bi-directional current path connecting two of the clamping diodes back-to-back from the taps on the DC-bus to the output.

It should be noted that Diode Clamped Converters with odd number of levels (n = 3, 5, 7, ...) offer a neutral point access. It is also possible to synthesize topologies with even number of levels (n = 4, 6, 8, ...). Converters with even number of levels have a handicap in single phase applications where a neutral point is needed. These topologies have on the other hand proven to be well suited for drive applications ([15] and [16]). Although each active switching device is only required to block a voltage level of  $U_{dc}/n-1$ , the clamping diodes must have different voltage ratings. When closing the four lower switches ( $T_{1-}T_{4-}$ ) in a 5-level topology (Figure 1.2, left),  $D_2$  must block 3V ( $3U_{dc}/4$ ) and  $D_2$  needs to block 2V ( $U_{dc}/2$ ). Similar, by closing the four upper switches ( $T_{1+}-T_{4+}$ ),  $D_5$  must withstand  $3U_{dc}/4$  and  $D_5$ ,  $U_{dc}/2$ .

| Output | T <sub>1+</sub> | T <sub>2+</sub> | T <sub>3+</sub> | T <sub>4+</sub> | T <sub>1-</sub> | T <sub>2-</sub> | T <sub>3-</sub> | T <sub>4-</sub> |

|--------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 4V     | ON              | ON              | ON              | ON              | OFF             | OFF             | OFF             | OFF             |

| 3V     | OFF             | ON              | ON              | ON              | ON              | OFF             | OFF             | OFF             |

| 2V     | OFF             | OFF             | ON              | ON              | ON              | ON              | OFF             | OFF             |

| 1V     | OFF             | OFF             | OFF             | ON              | ON              | ON              | ON              | OFF             |

| 0      | OFF             | OFF             | OFF             | OFF             | ON              | ON              | ON              | ON              |

Table 1-1: Switch combinations for a 5-level Diode Clamped Converter.

Assuming that the voltage rating of the clamping diodes are the same as the active switching devices, the number of diodes is  $(n-1) \cdot (n-2)$  pr. phase. An interesting approach is to configure the diodes in a pyramid as presented in [17] and shown in Figure 1.2 (right). By this configuration, each clamping diode will have to block the same voltage, but the total number of diodes is the same as for the conventional topology.

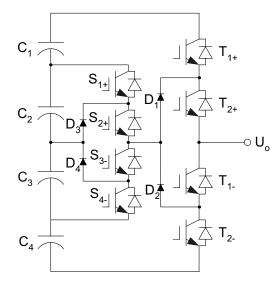

A Cascaded Diode Clamped Converter has been presented in [18], and this topology is shown in Figure 1.3. This converter consists of a main NPC converter with an auxiliary NPC converter at the neutral point. The auxiliary converter is common for all bridge-legs. For a 5-level converter this topology only needs 16 active switching devices. The drawback is the voltage rating of the main converter devices. A blocking voltage of  $U_{dc}/2$  is needed.

Figure 1.3: Cascaded Diode Clamped Converter.

The switching configurations for the Cascaded Diode Clamped Converter are given in Table 1-2. By using the auxiliary converter, the innermost dc-bus taps are accessed.

| Output | T <sub>1+</sub> | T <sub>2+</sub> | T <sub>1-</sub> | T <sub>2-</sub> | <b>S</b> <sub>1+</sub> | $S_{2^+}$ | S <sub>1-</sub> | S <sub>2-</sub> |

|--------|-----------------|-----------------|-----------------|-----------------|------------------------|-----------|-----------------|-----------------|

| 4V     | ON              | ON              | OFF             | OFF             | OFF                    | OFF       | OFF             | OFF             |

| 3V     | OFF             | ON              | ON              | OFF             | ON                     | ON        | OFF             | OFF             |

| 2V     | OFF             | ON              | ON              | OFF             | OFF                    | ON        | ON              | OFF             |

| 1V     | OFF             | ON              | ON              | OFF             | OFF                    | OFF       | ON              | ON              |

| 0      | OFF             | OFF             | ON              | ON              | OFF                    | OFF       | OFF             | OFF             |

Table 1-2: Switch combinations for a 5-level Cascaded Diode Clamped Converter.

#### 1.3 Capacitor Clamped Converters

Another approach to multilevel power conversion is to use clamping capacitors instead of clamping diodes. This topology was presented in [12], and is also referred as a Flying Capacitor Converter. It consist of  $2 \cdot (n-1)$  active switches,  $(n-1) \cdot (n-2)/2$  clamping capacitors and (n-1) main DC-bus capacitors. A 5-level converter is shown in Figure 1.4. If each capacitor has a voltage of V, the converter can synthesize 0, V, 2V, 3V and 4V at the output.

Figure 1.4: 5-level Capacitor Clamped Converter.

The Flying Capacitor Converter is more flexible in switch combinations for different voltage levels than the diode clamped converter as listed in Table 1-3. However, a problem with this topology is the complicated control of the floating

capacitor voltages [13]. Balancing of the different capacitor voltages is beyond the scope of this thesis, and will not be discussed any further.

| Output | Switching combinations (conducting switches)                               |                                       |                                       |                                       |                                                                                 |                                       |

|--------|----------------------------------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------------------------------------------------|---------------------------------------|

| 4V     | T <sub>1+</sub> - T <sub>4+</sub>                                          |                                       |                                       |                                       |                                                                                 |                                       |

| 3V     | $T_{1+} - T_{3+}$<br>and $T_{1-}$                                          | $T_{2+} - T_{4+}$<br>and $T_{4-}$     | $T_{1+}, T_{3-}, T_{3+}$ and $T_{4+}$ |                                       |                                                                                 |                                       |

| 2V     | T <sub>1+</sub> , T <sub>2+</sub> , T <sub>1-</sub><br>and T <sub>2-</sub> | $T_{3+}, T_{4+}, T_{1-}$ and $T_{2-}$ | $T_{1+}, T_{3+}, T_{1-}$ and $T_{3-}$ | $T_{1+}, T_{1-}, T_{2-}$ and $T_{3-}$ | $\begin{array}{c} T_{2^+}, T_{3^+}, \\ T_{2} \text{ and } \\ T_{4} \end{array}$ | $T_{2+}, T_{3+}, T_{1-}$ and $T_{2-}$ |

| 1V     | $T_{1+}, T_{1-}, T_{2-}$<br>and $T_{3-}$                                   | $T_{4+}, T_{2-}, T_{3-}$ and $T_{4-}$ | $T_{3+}, T_{1-}, T_{3-}$ and $T_{4-}$ |                                       |                                                                                 |                                       |

| 0      | T <sub>1-</sub> - T <sub>4-</sub>                                          |                                       |                                       |                                       |                                                                                 |                                       |

Table 1-3: Switch combinations for a 5-level Capacitor Clamped Converter.

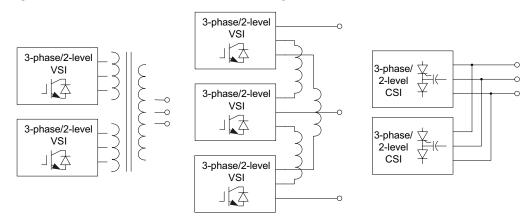

### 1.4 Multilevel Multiple Three-Phase Converters

Multilevel output can also be achieved by adding and phase-shifting several 3-phase 2-level VSIs by using a multi-winding transformer as shown in Figure 1.5 (left). Another approach presented in [19] is to arrange the converters in a delta configuration as shown in the middle of Figure 1.5.

Figure 1.5: Mulitlevel Converters by serial connection of several 3-phase 2-level VSI/CSIs.

Both of these topologies need extra interconnecting reactances or transformers, thus the converters become bulky and lossy. An alternative approach is presented in [20] using Current Source Inverters (CSIs), shown in Figure 1.5 (right).

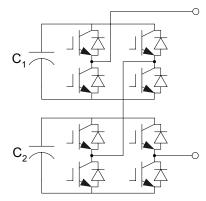

#### 1.5 Cascaded Multicell Converters

This class of Multilevel Converters is based on series connection of single-phase converters, and the earliest reference is probably [21] back in 1973, and used for plasma stabilisation in [22]. It was also introduced for Static VAr applications in [24] and for drive applications in [25]. One topology consists of single-phase Hbridge which is connected in series, forming a phase-leg. As can be seen in Figure 1.6, the output can be  $0, \pm V$  and  $\pm 2V$ , if the capacitor voltages are  $U_{C1} = U_{C2} = V$ , and hence a 5-level output is obtained. If  $n_{cell}$  is the number of single-phase Hbridges per phase-leg,  $n = 2 \cdot n_{cell} + 1$  levels is obtained at the output. This arrangement is called an Order-1 configuration [27]. In [23] and [26] an extension of this topology is presented. By letting  $U_{C1} = V$  and  $U_{C2} = 2V$ , the output can be  $0, \pm V, \pm 2V$  and  $\pm 3V$ . Thus a 7-level output is obtained. In general,  $n = 2^{n_{cell}+1} - 1$  levels are obtained at the output. This arrangement is called at the output. This arrangement is called an Order-2 configuration. It is also possible to let  $U_{C1} = V$  and  $U_{C2} = 3V$ , the output is then  $0, \pm V, \pm 2V, \pm 3V$  and  $\pm 4V$ . Thus a 9-level output is obtained. In general,  $n = 3^{n_{cell}}$  levels are obtained at the output is obtained. In general,  $n = 3^{n_{cell}}$  levels are obtained at the output is obtained.

Figure 1.6: 5-level Cascaded Multicell Converter using series connection of singlephase H-bridge converters.

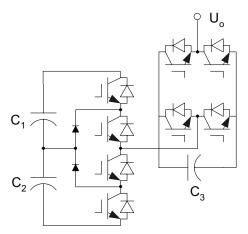

Another approach is to connect single phase converters in series with the output of each phase of a multiple phase converter. In [28] and [29] a topology based on a 3-phase NPC converter and 3 single phase H-bridges is presented (Figure 1.7). By letting  $U_{CI} + U_{C2} = 3V$  and  $U_{C3} = V$ , the output can be  $0, \pm V, \pm 2V, \pm 3V$  and  $\pm 4V$ . Thus a 9-level output is obtained. It is possible to operate the converter without any supply of the low voltage converter. To obtain this, no active power can be transferred over the small voltage converter.

Figure 1.7: 9-level Hybrid Asymetric Converter.

#### 1.6 Generalized Multilevel Converter

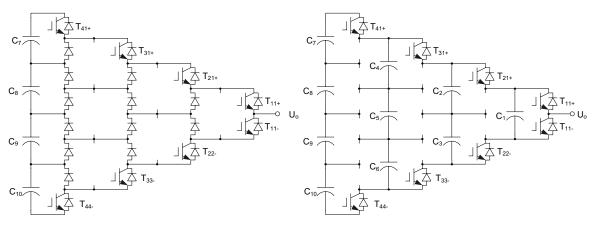

In [30] a generalized structure of a Multilevel Converter is presented, one phase leg of such a 5-level converter is shown in Figure 1.8.

Figure 1.8: Generalized 5-level converter leg.

The uttermost switches  $(T_{11+}-T_{x1+} \text{ and } T_{11-}-T_{xx-}, x=1..4)$  are used to synthesize the desired voltage waveforms, The rest of the devices are used for clamping and balancing of the capacitors voltages. The switching rules are as follows: each switch pole is an independent switching unit, i.e  $T_{xx+}$  and  $T_{xx-}$  are complementary. Any adjacent two switches are complementary. This means that if any switch state is set, the others are known. An Example: if  $T_{41+}$  is on,  $T_{41-}$  is off.  $T_{42+}$ ,  $T_{43+}$  and  $T_{44+}$  are on.  $T_{42-}$ ,  $T_{43-}$  and  $T_{44-}$  are off. The switch combinations are similar to those found for the Capacitor Clamped Converter in Table 1-3, i.e. one combinations for 2V ( $C_{1-}C_{10}=V$ ). From the converter in Figure 1.8 it is also possible to deduce other

topologies. By removing the inner switches (except the freewheeling diodes) and the inner capacitors, the Diode Clamped Converter with pyramid stacked diodes in Figure 1.2 (right) can be extracted. By removing the inner switches with freewheeling diodes, the Capacitor Clamped Converter in Figure 1.4 can be deduced. These topologies are shown in Figure 1.9.

Figure 1.9: Deduced converter topologies: Diode Clamped Converter (left), Capacitor Clamped Converter (right).

#### 1.7 Comparison of Topologies

In Table 1-4, a comparison of the main different topologies is given. The table shows the number of primary switching devices, DC capacitors and output levels for all 3 phases.

| Topology                                | Primary switching<br>devices | DC Capacitors | Output<br>levels |

|-----------------------------------------|------------------------------|---------------|------------------|

| Diode Clamped                           | 6k                           | k             | k+1              |

| Capacitor Clamped                       | 6k                           | 3k-2          | k+1              |

| Cascaded Multicell Converter<br>1-Order | 12k                          | 3k            | 2k+1             |

| Cascaded Multicell Converter<br>2-Order | 12k                          | 3k            | $2^{k+1}$ -1     |

| Cascaded Multicell Converter<br>3-Order | 12k                          | 3k            | 3 <sup>k</sup>   |

Table 1-4: Comparision of converter topologies (3 phases), k=1....

The Cascaded Multicell topology can generate the most number of levels from a given number of switching devices and DC-busses. E.g., for a 5-level Diode Clamped or Capacitor Clamped Converter (k=4), 24 primary switching devices are needed. By using 24 primary switching devices in a Cascaded Multicell Converter

(k=2), 9 levels are generated at the output. The main problem with this topology is that a separate, isolated DC-supply is needed for every DC-bus level and phase. Further, the Capacitor Clamped topology is presented in the literature as difficult to control, and needs balancing capacitors. The Diode Clamped topology has its disadvantages such as the unequal voltage rating of the clamping diodes. Balancing issues for high number of levels as discussed in Chapter 7 are also a concern, but the technology is proven for 3-level converters as discussed in the introduction chapter. The main focus in this thesis will hence be on Diode Clamped Converters.

# 2 MODULATION STRATEGIES FOR MULTILEVEL CONVERTERS

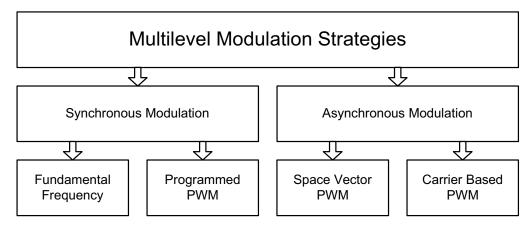

Since the introduction of multilevel power converters, a number of different topologies have been discussed. A lot of research has been performed to control the output waveform of these converters. Numerous modulation strategies have been presented in the literature, the most interesting are summarized in [31], [32] and [33].

### 2.1 Overview of Modulation Strategies

Multilevel modulation can be divided into two main categories, Synchronous Modulation and Asynchronous Modulation. Figure 2.1 shows a block diagram of the most popular methods used.

Figure 2.1: Schematic overview of multilevel modulation strategies.

#### 2.2 Synchronous Modulation

Synchronous Modulation methods are a class of modulation schemes where the switching of the devices is synchronized with the reference voltages. In these methods the switching frequency is low and usually equal to the fundamental frequency (e.g. 50-200 Hz).

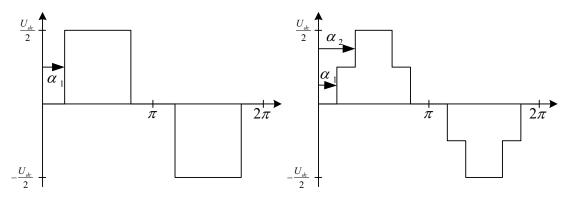

#### 2.2.1 Fundamental Frequency Modulation

Fundamental Frequency Modulation is used for slow switching semiconductors such as Gate Turn-off Thyristors (GTOs). This scheme of modulation is a synchronous modulation method, since the there is only one commutation of the switches per fundamental cycle of the output voltage. By utilizing such a modulation strategy, the output level waveform has a stepped shape. Figure 2.2 shows an output waveform for 3-level and 5-level converter respectively.

Figure 2.2: Stepped output waveform, 3-level (left), 5-level (right).

This strategy needs only low switching frequency capability from the devices. However, it is possible to optimize the switching angles  $\alpha_i$ , (i=1..m) for a given modulation index M, so as to minimize a set of dominant harmonics in the output. By Fourier analysis, the  $k^{th}$  harmonic of a *n*-level waveform can be derived as follows:

$$H(k) = \frac{4}{\pi k} \frac{U_{dc}}{2} \frac{2}{n-1} \sum_{i=1}^{m} \cos(k\alpha_i)$$

(2.1)

Because of half-wave symmetry of the waveform, only odd harmonic component will exists, thus k=1, 3, 5, 7, ... The switching angles  $\underline{\alpha} = [\alpha_1, \alpha_2, ..., \alpha_m]^T$  are shown in Figure 2.2. From the figure, the following yields:

$$\alpha_1 < \alpha_2 < \dots < \alpha_m < \frac{\pi}{2} \tag{2.2}$$

It may be verified that if all the switching angles are set to zero, the output falls back to a conventional 2-level waveform and the fundamental voltage in this case is given by:

$$H(1)_{\rm max} = \frac{4}{\pi} \frac{U_{dc}}{2}$$

(2.3)

In general, there exist *m* degrees of freedom due to *m*  $\alpha_i$ 's. For the 3-level modulation only one parameter can be controlled, the fundamental component, H(1) when one switching per. device and fundamental period is used. For a 4-level and 5-level converter, two independent parameters exist. This can be use to eliminate one dominant harmonic. It may be noted that the 5<sup>th</sup> is the most dominant harmonic since the even harmonics are cancelled because of the half wave symmetry and triple harmonics are eliminated in a three-phase three-wire system. Hence, the following set of equations has to be solved:

$$H(1) = \frac{U_{dc}}{2}M \quad , \quad H(5) = 0 \tag{2.4}$$

where  $0 \le M \le 4/\pi$ . Eq. (2.1) yields:

$$H(1) = \frac{U_{dc}}{\pi} \left[ \cos \alpha_1 + \cos \alpha_2 \right] , \quad H(5) = \frac{U_{dc}}{5\pi} \left[ \cos(5\alpha_1) + \cos(5\alpha_2) \right]$$

(2.5)

To solve these equations, a technique described in [26] can be used. Suppose a vector of angles  $\underline{\alpha} = [\alpha_1, \alpha_2, ..., \alpha_m]^T$  satisfies a set of equations  $f_i(\underline{\alpha}) = 0$  to be solved. Then, one can formulate an equivalent minimization problem as follows; Let:

$$F(\underline{\alpha}) = \sum_{i=1}^{m} f_i(\underline{\alpha})^2$$

(2.6)

$F(\underline{\alpha})$  is always non-negative, and therefore, if values of  $\alpha$  exist for which  $F(\alpha) = 0$ , these have to be the minimum points for  $F(\underline{\alpha})$ . When  $F(\underline{\alpha})$  is zero, each  $f_i(\underline{\alpha})$  must be zero, thus the solution of the set of the equations is to search for the minima of Eq.(2.6). For a 5-level converter, the optimization functions can be found from Eq. (2.4)-(2.6):

$$f_1(a_1, \alpha_2) = \frac{U_{dc}}{\pi} \left[ \cos \alpha_1 + \cos \alpha_2 - \frac{\pi}{2} M \right]$$

$$f_2(a_1, \alpha_2) = \frac{U_{dc}}{5\pi} \left[ \cos(5\alpha_1) + \cos(5\alpha_2) \right]$$

(2.7)

This leads to the final optimization function:

$$F(\alpha_{1},\alpha_{2}) = \left(\frac{U_{dc}}{\pi}\right)^{2} \left[ \left(\cos\alpha_{1} + \cos\alpha_{2} - \frac{\pi}{2}M\right)^{2} + \frac{1}{5^{2}}\left(\cos(5\alpha_{1}) + \cos(5\alpha_{2})\right)^{2} \right]$$

(2.8)

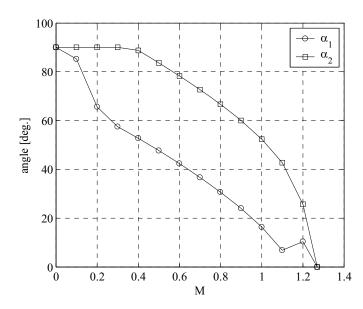

Figure 2.3: Switching angles for a 5-level converter.

Eq. (2.8) can be solved in MATLAB optimization toolbox and the results from the simulations are given in Figure 2.3.

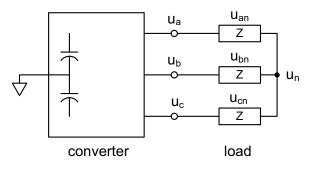

To simulate the output waveforms in this chapter, MATLAB has been used. Figure 2.4 shows a simplified simulation schematic where  $u_a$ ,  $u_b$  and  $u_c$  are the converter output voltages and  $u_{an}$ ,  $u_{bn}$  and  $u_{cn}$  are the load voltages for a, b and c phase respectively.  $u_n$  is the neutral point voltage of the load, also referred to as common-mode or zero-sequence voltage. If a symmetrical load is used, it can be shown that the zero-sequence voltage is:

$$u_{n}(t) = \frac{1}{3} \left( u_{a}(t) + u_{b}(t) + u_{c}(t) \right)$$

(2.9)

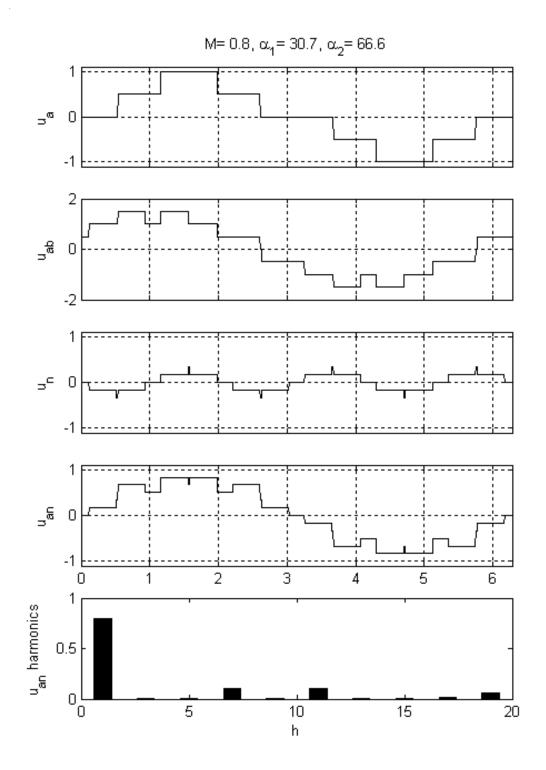

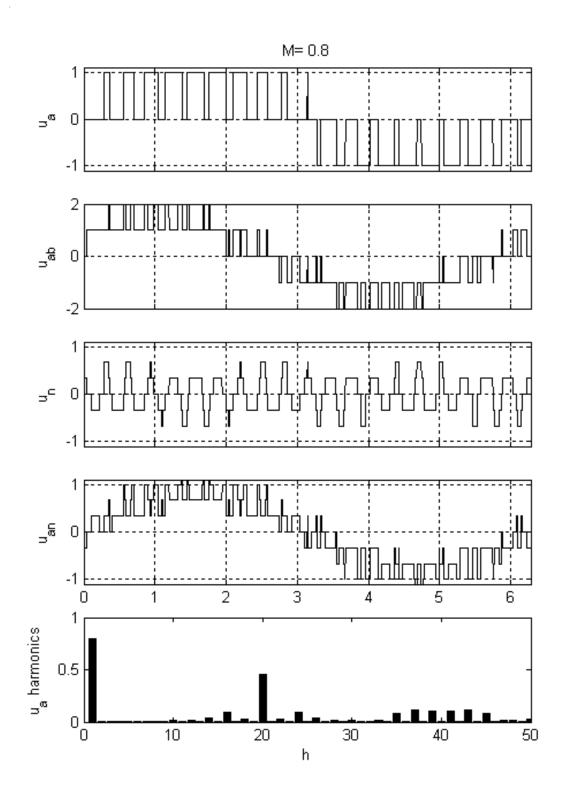

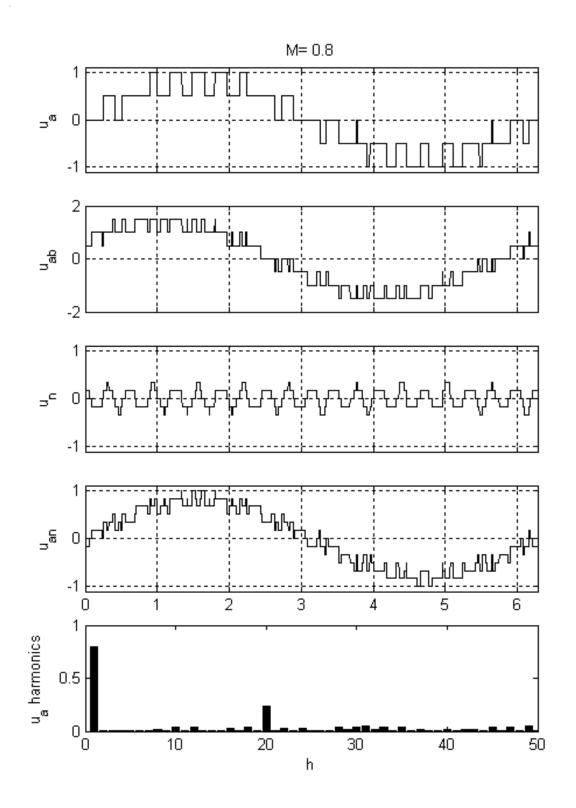

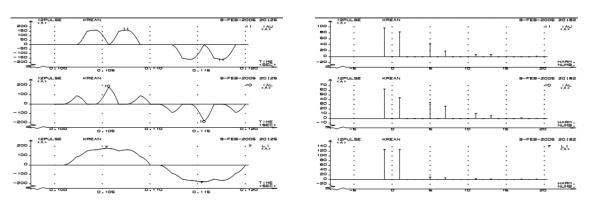

Figure 2.5 shows the simulated output voltages for the fundamental frequency modulation at modulation depth M=0.8, resulting in switching angles at  $\alpha_1=30.7^{\circ}$  and  $\alpha_2=66.6^{\circ}$ . From top, the converter phase voltage, the line voltage, the zero sequence voltage, and the load phase voltage are shown. At bottom, the harmonics from the load phase voltage is shown.

Figure 2.4: Simplified converter simulation model.

The triple harmonics in the load phase voltage are non-exciting, due to the symmetrical three phase system. Also the  $5^{th}$  harmonic is zero, caused by the harmonic elimination.

Figure 2.5: Stepped wave output waveforms from 5-level converter.

#### 2.2.2 Programmed PWM

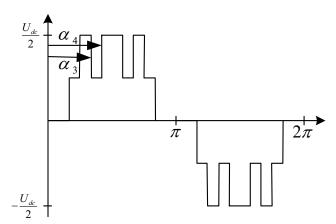

It is also possible to extend the Fundamental Frequency Modulation by introducing more switching angles in the output waveform as illustrated in Figure 2.6. This will introduce notches in the output waveform, and the number of commutations will increase per. fundamental cycle. This method is called Programmed PWM. By doing this, several harmonic components can be eliminated in the output waveform. In Figure 2.6, four angles can be controlled, thus three harmonics can be eliminated in addition to control of the fundamental voltage. To find the switching angles, the same method presented in Eq.(2.1)-(2.2) and (2.6) can be used. As more switching angles are introduced, the waveform converges to a classical PWM pattern.

Finding the optimized switching angles is quite computation intensive, and in a real application they are calculated off-line, and stored in look-up tables in the control system.

Figure 2.6: Programmed PWM for a 5-level converter.

### 2.3 Asynchronous Modulation

In this class of modulation methods, the switching is asynchronous with the reference voltages. This will introduce sub-harmonics of the fundamental component in the output voltage, but at high switching frequency (e.g. >1 kHz) the amplitude of the sub harmonics are small, and the asynchronous modulation method can be used [54].

#### 2.3.1 Carrier Based PWM

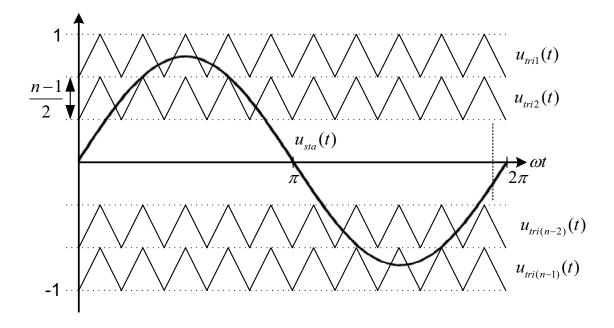

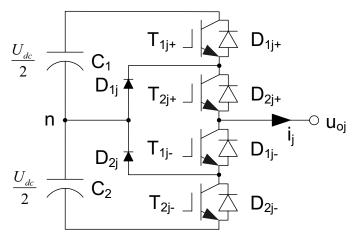

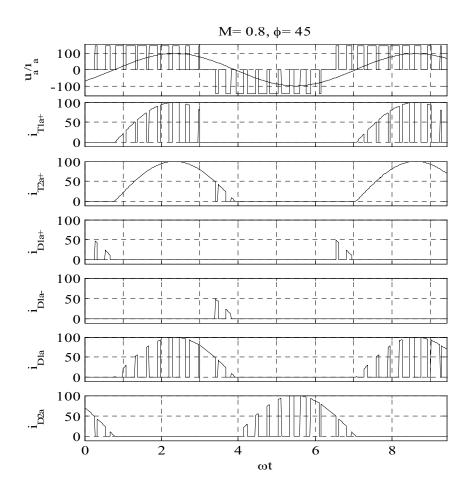

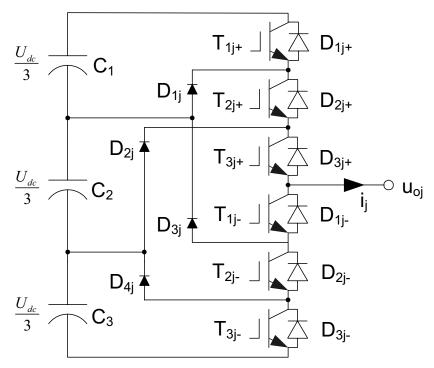

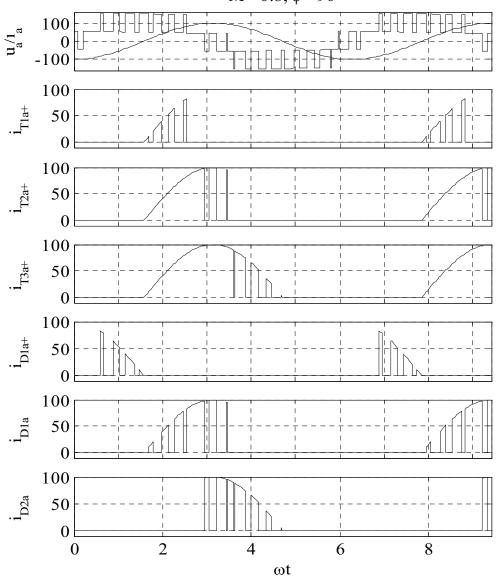

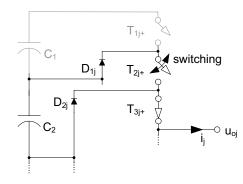

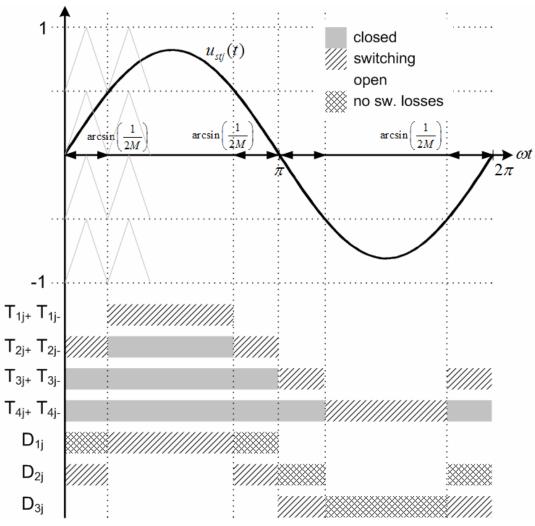

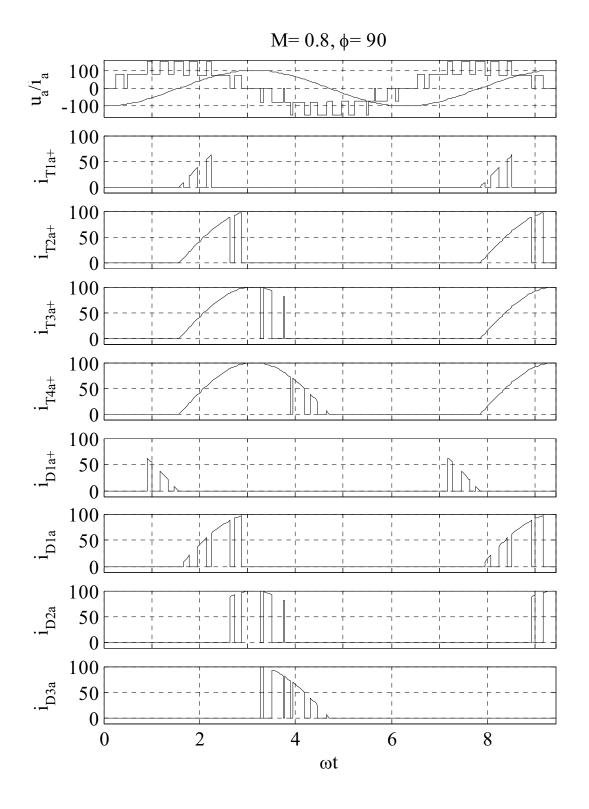

Sinusoidal Carrier Based Pulse Width Modulation (CBPWM) is a classical approach, and is widely used in the literature. Figure 2.7 shows one phase of a Generalized Diode Clamped converter, which consists of 2(n-1) active devices.  $T_{ij+}$  and  $T_{ij-}$  are complementary (except for delay at turn on), where i=1..(n-1) and j=a,

*b*, *c*. A generalized sinusoidal CBPWM strategy is shown in Figure 2.8. (*n*-1) carriers,  $u_{trii}(t)$ , are distributed in bands from -1 to +1.

Figure 2.7: Generalized n-level Diode Clamped Converter (DCC).

Figure 2.8: Generalized sinusoidal CBPWM.

The control signals for sinusoidal CBPWM are:

$$u_{sta}(t) = M \sin(\omega t)$$

$$u_{stb}(t) = M \sin(\omega t - 2\pi/3)$$

$$u_{stc}(t) = M \sin(\omega t + 2\pi/3)$$

(2.10)

where *M* is the modulation index, and  $\omega$  the angular frequency. Of course, *cos* functions can also be used in Eq.(2.10), *sin* functions are only used for convenience. Both *sin/cos* are named sinusoidal function, and give the same characteristics/performance.

Switching of transistor  $T_{ij+}$  (i.e transistor number *i* in phase *j*) is done by the following algorithm:

if

$$u_{stj}(t) > u_{trii}(t)$$

then  $T_{ij+}$  on

else  $T_{ij+}$  off

The duty cycles, i.e average on-times for the switching devices within a switching period, can be expressed as:

$$d_{ij}(t) = \frac{n-1}{2}u_{sij}(t) + \frac{2i-n+1}{2}$$

(2.11)

When  $u_{sti}(t)$  is inside band *i*. In addition,

if  $u_{stj}(t)$  > band i then  $d_{ij+}(t) = 1$ else if  $u_{stj}(t)$  < band i then  $d_{ij+}(t) = 0$

E.g, if the control signal  $u_{sta}(t)$  in Figure 2.8 is larger than the carrier signal  $u_{tril}(t)$ , transistor  $T_{1a^+}$  in Figure 2.7 is turned on. Else, transistor  $T_{1a^+}$  is off.

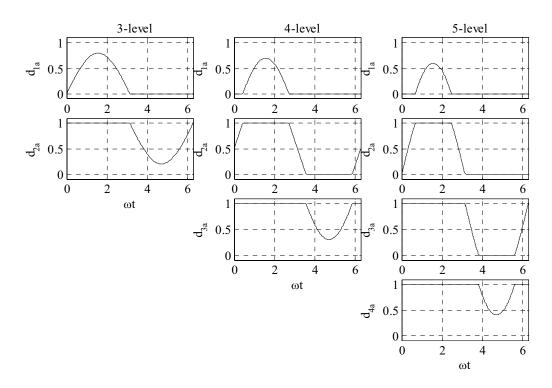

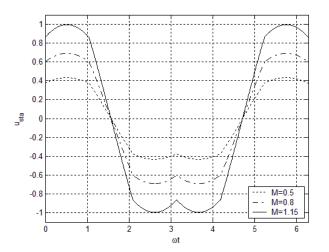

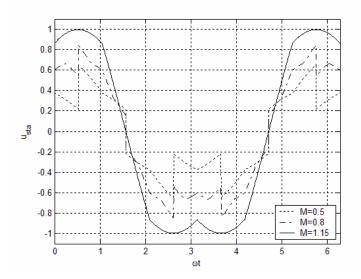

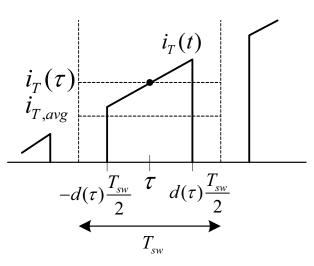

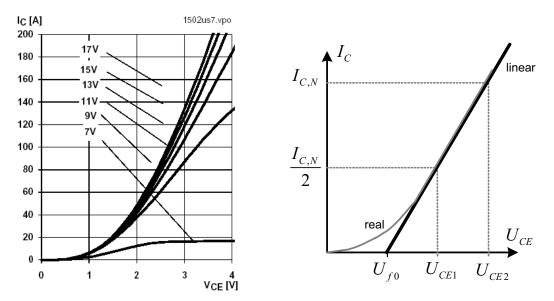

Figure 2.9 shows an example of the duty cycles at M=0.8 for 3-, 4- and 5-level converters respectively.

Looking at a 3-level converter, the boarders of the two carrier bands become trivial:

$$M\sin(\omega t) = 0 \Leftrightarrow \omega t = \arcsin(0) \tag{2.12}$$

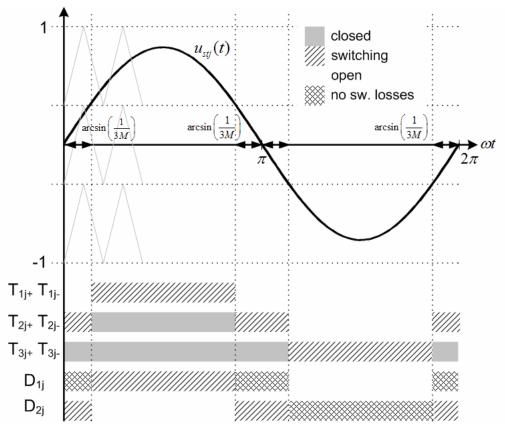

For the 4- and 5-level topology, the crossings will be as in (2.13) and (2.14) respectively.

$$M\sin(\omega t) = \frac{1}{3} \Leftrightarrow \omega t = \arcsin(\frac{1}{3M})$$

(2.13)

$$M\sin(\omega t) = \frac{1}{2} \Leftrightarrow \omega t = \arcsin(\frac{1}{2M})$$

(2.14)

Figure 2.9: Duty cycles for 3-, 4-, and 5-level converters for M=0.8.

From this, the expressions for the duty cycles for phase *a* can be expressed as:

For the 3-level topology, the upper positive transistor  $T_{1a+}$  is switched on/off when the control signal is positive, while the lower positive transistor  $T_{2a+}$  is turned on. When the control signal is negative, the upper transistor is turned off, and  $T_{2a+}$  is switching.  $T_{1a-}$  and  $T_{2a-}$  are complementary to  $T_{1a+}$  and  $T_{2a+}$  respectively.

$$d_{1a} = \begin{cases} M\sin(\omega t) & , \quad 0 < \omega t < \pi \\ 0 & , \quad \pi < \omega t < 2\pi \end{cases}$$

(2.15)

$$d_{2a} = \begin{cases} 1 & , \quad 0 < \omega t < \pi \\ M\sin(\omega t) + 1 & , \quad \pi < \omega t < 2\pi \end{cases}$$

(2.16)

The 4-level topology has three carrier bands controlling the three positive transistors. The upper positive transistor  $T_{Ia+}$  is switched on/off when the control signal is in the upper carrier band, and is switched off in the two lower bands. The middle positive transistor is switched on/off in the middle band, switched on in the upper band, and switched off in the lower band. The lower positive transistor is switched off in the two upper bands. From this, the duty cycles are:

$$d_{1a} = \begin{cases} 0 , \quad 0 < \omega t < \arcsin(\frac{1}{3M}) \\ \frac{3}{2}M\sin(\omega t) - \frac{1}{2} , \arcsin(\frac{1}{3M}) < \omega t < \pi - \arcsin(\frac{1}{3M}) \\ 0 , \quad \pi - \arcsin(\frac{1}{3M}) < \omega t < 2\pi \end{cases}$$

$$(2.17)$$

$$d_{2a} = \begin{cases} \frac{3}{2}M\sin(\omega t) + \frac{1}{2} &, \quad 0 < \omega t < \arcsin(\frac{1}{3M}) \\ 1 &, \quad \arcsin(\frac{1}{3M}) < \omega t < \pi - \arcsin(\frac{1}{3M}) \\ \frac{3}{2}M\sin(\omega t) + \frac{1}{2} &, \quad \pi - \arcsin(\frac{1}{3M}) < \omega t < \pi + \arcsin(\frac{1}{3M}) \\ 0 &, \quad \pi + \arcsin(\frac{1}{3M}) < \omega t < 2\pi - \arcsin(\frac{1}{3M}) \\ \frac{3}{2}M\sin(\omega t) + \frac{1}{2} &, \quad 2\pi - \arcsin(\frac{1}{3M}) < \omega t < 2\pi \end{cases}$$

$$d_{3a} = \begin{cases} 1 &, \quad 0 < \omega t < \pi + \arcsin(\frac{1}{3M}) < \omega t < 2\pi \\ \frac{3}{2}M\sin(\omega t) + \frac{3}{2} &, \quad \pi + \arcsin(\frac{1}{3M}) < \omega t < 2\pi - \arcsin(\frac{1}{3M}) \\ 1 &, \quad 2\pi - \arcsin(\frac{1}{3M}) < \omega t < 2\pi \end{cases}$$

$$(2.19)$$

Similarly, the same rules apply for *the 5-level converter*. Here, the four positive transistors are controlled using four bands. The upper positive transistor  $T_{Ia+}$  is switched on/off when the control signal is in the upper band etc. This gives the duty cycles for the 5-level topology:

$$d_{1a} = \begin{cases} 0 , \quad 0 < \omega t < \arcsin(\frac{1}{2M}) \\ 2M\sin(\omega t) - 1 , \arcsin(\frac{1}{2M}) < \omega t < \pi - \arcsin(\frac{1}{2M}) \\ 0 , \quad \pi - \arcsin(\frac{1}{3M}) < \omega t < 2\pi \end{cases}$$

$$(2.20)$$

$$d_{2a} = \begin{cases} 2M\sin(\omega t) , & 0 < \omega t < \arcsin(\frac{1}{2M}) \\ 1 , & \arcsin(\frac{1}{2M}) < \omega t < \pi - \arcsin(\frac{1}{2M}) \\ 2M\sin(\omega t) , \pi - \arcsin(\frac{1}{2M}) < \omega t < \pi + \arcsin(\frac{1}{2M}) \\ 0 , & \pi + \arcsin(\frac{1}{2M}) < \omega t < 2\pi \end{cases}$$

$$(2.21)$$

$$d_{3a} = \begin{cases} 1 & , & 0 < \omega t < \pi \\ 2M\sin(\omega t) + 1 & , & \pi < \omega t < \pi + \arcsin(\frac{1}{2M}) \\ 0 & , \pi + \arcsin(\frac{1}{2M}) < \omega t < 2\pi - \arcsin(\frac{1}{2M}) \\ 2M\sin(\omega t) + 1 & , & 2\pi - \arcsin(\frac{1}{2M}) < \omega t < 2\pi \end{cases}$$

$$d_{4a} = \begin{cases} 0 & , & 0 < \omega t < \pi + \arcsin(\frac{1}{2M}) < \omega t < 2\pi \\ 2M\sin(\omega t) + 2 & , \pi + \arcsin(\frac{1}{2M}) < \omega t < 2\pi - \arcsin(\frac{1}{2M}) \\ 0 & , & 2\pi - \arcsin(\frac{1}{2M}) < \omega t < 2\pi \end{cases}$$

$$(2.22)$$

For the *b* and *c* phase, the duty cycles are the same as in Eq. (2.15)-(2.23) only shifted  $-2\pi/3$  and  $-4\pi/3$  respectively.

By using the expressions for the duty cycles, a simplified implementation of the modulation method in a digital control system is obtained. The duty cycle values can be used directly in the PWM units of a DSP.

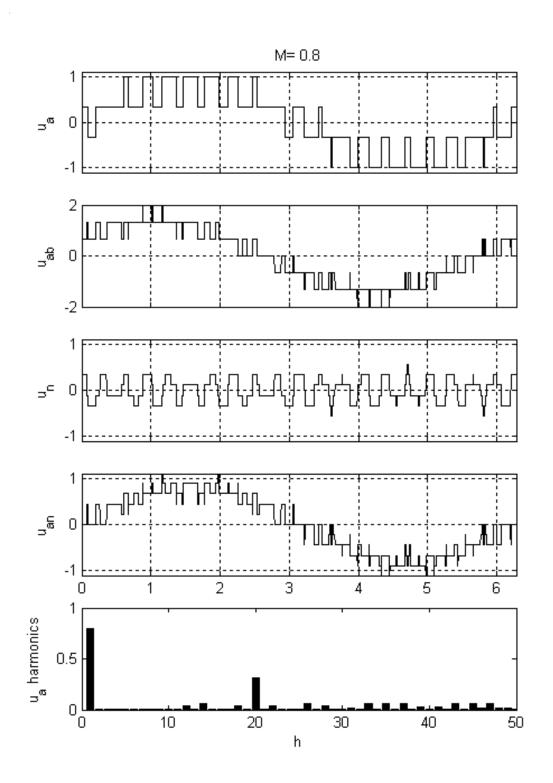

It should be noted that duty cycle calculations as presented here, can be easily performed for control voltages with third harmonic injection to increase the modulation depth, or any kind of added common mode voltage. Output waveforms for the CBPWM strategies are shown in Figure 2.10-Figure 2.12 for M=0.8. The different voltages simulated, are as indicated in Figure 2.4, which shows the simplified converter model.

Figure 2.10: CBPWM output waveforms for a 3-level converter.

Figure 2.11: CBPWM output waveforms for a 4-level converter.

Figure 2.12: CBPWM output waveforms for a 5-level converter.

## 2.3.2 Space Vector PWM

As for all the others modulation strategies presented in this thesis, the Space Vector PWM (SVPWM) for multilevel converters evolves from modulation schemes for 2-level converters. [35] gives a nice overview of modulation strategies for this converter topology. In the last 20 years, numerous SVPWM strategies have been proposed for the 2-level converter. In the last 10 years, several SVPWM for multilevel converters has been proposed. The popularity of the SVPWM strategy is because of the direct digital implementation in today's DSP-based control systems [35]. Other advantages are lower harmonic distortion, and extended modulation depth compared to classical sinusoidal PWM modulation.

In a three-phase *n*-level converter, the number of available switch combinations is given by:

$$n_{uout} = n^3 \tag{2.24}$$

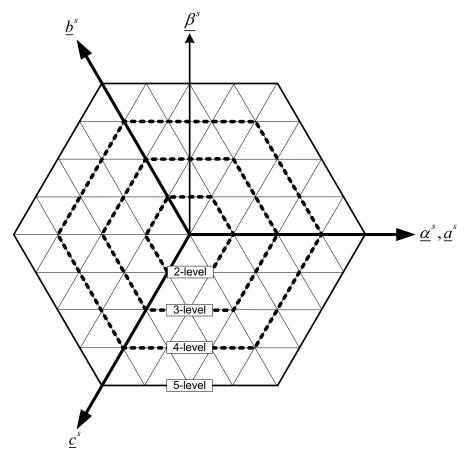

For a 2-level converter this yields 8 combinations, for the 3-level 27 combinations and so on. Figure 2.13 shows a comparison of the output vector-space for different levels.

Figure 2.13: Comparision of the respective output vector-spaces for multilevel converters.

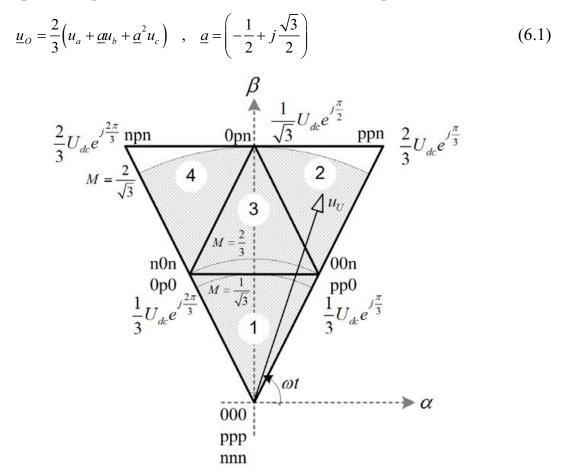

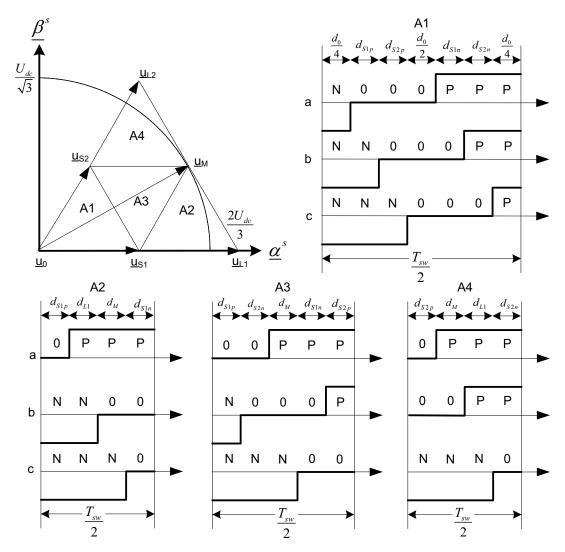

#### **3-level Space Vector PWM**

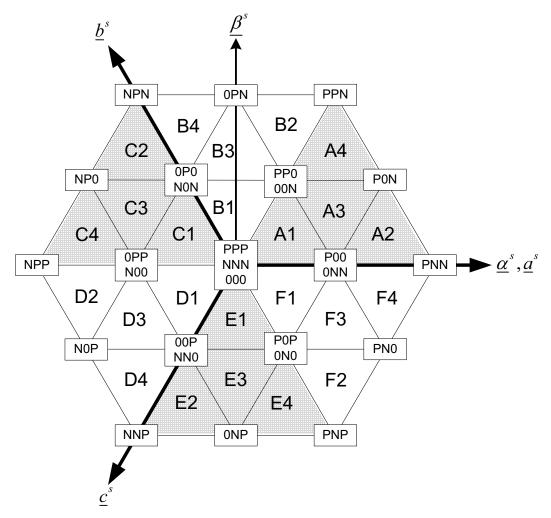

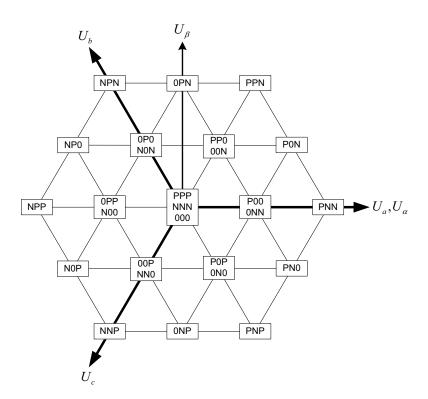

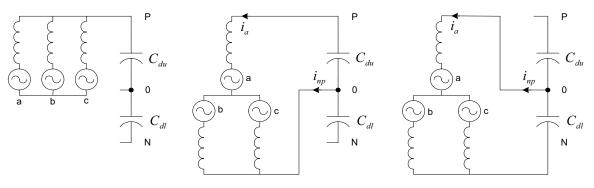

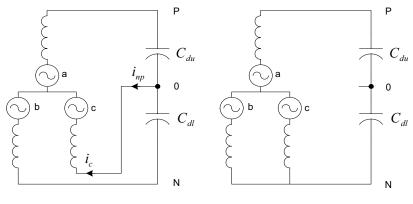

It should be noted that some of the switching combinations are redundant, two or more switch combinations gives the same output voltage vector. It's well known that only 7 different voltage vectors are available in a 2-level topology. For the 3-level converter the number of different voltage vectors is 18. Figure 2.14 shows the vector-space for a 3-level converter with redundant states. P and N denote the upper and lower DC-bus respectively. Neutral point connection is denoted with  $\theta$ .

Figure 2.14: Space vector diagram of a 3-level converter.

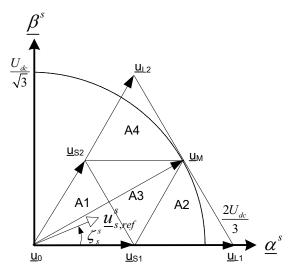

Available vectors can be divided into four groups (Figure 2.15): Zero vectors as  $\underline{U}_0$ , Small vectors as  $\underline{U}_{SI}$  and  $\underline{U}_{S2}$ , Medium vectors as  $\underline{U}_M$ , and Large vectors as  $\underline{U}_{L1}$  and  $\underline{U}_{L2}$ :

$$\underline{U}_{0} = 0 \qquad \underline{U}_{S1} = \frac{U_{dc}}{3} \qquad \underline{U}_{S2} = \frac{U_{dc}}{3}e^{j\frac{\pi}{3}}$$

$$\underline{U}_{M} = \frac{U_{dc}}{\sqrt{3}}e^{j\frac{\pi}{6}} \qquad \underline{U}_{L1} = \frac{2U_{dc}}{3} \qquad \underline{U}_{L2} = \frac{2U_{dc}}{3}e^{j\frac{\pi}{3}}$$

(2.25)

The reference vector is defined as:

$$\underline{U}_{s,ref}^{s} = \frac{U_{dc}}{\sqrt{3}} M_{s} e^{j\zeta_{s}^{s}}$$

(2.26)

where  $M_s$  is the SVPWM modulation index. It can be shown that the relationship between the CBPWM modulation factor M, and  $M_s$  is:

$$M = \frac{2}{\sqrt{3}} M_s \approx 1.15 M_s \tag{2.27}$$

Hence, the DC-bus utilization is 15% better for SVPWM compared to sinusoidal CBPWM.

## Calculation of duty cycles

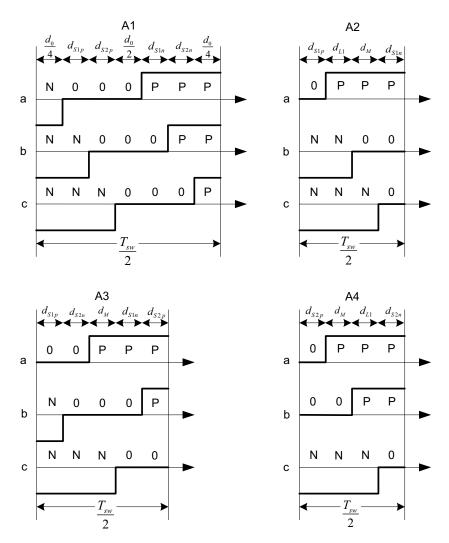

Figure 2.15 shows sector A of a 3-level vector space. From Figure 2.15, the duty cycles can be found for the respective vectors from voltage/time balance during one switching period  $T_{sw}$ .

Figure 2.15: Switching vectors in sector A.

In triangle *A1*, two small vectors and one zero vector are used. From voltage/time balance we have:

$$T_{sw}\underline{U}_{s,ref}^{s} = T_{sw}(d_{0}\underline{U}_{0} + d_{S1}\underline{U}_{S1} + d_{S2}\underline{U}_{S2})$$

$$(2.28)$$

$$T_{sw} \frac{U_{dc}}{\sqrt{3}} M_s e^{j\zeta_s^s} = T_{sw} U_{dc} \left( d_0 0 + d_{S1} \frac{1}{3} + d_{S2} \frac{1}{3} e^{j\frac{\pi}{3}} \right)$$

(2.29)

Decomposed into real- and imaginary quantities gives:

$$\frac{1}{\sqrt{3}}\cos(\zeta_s^s) = (d_{s_1}\frac{1}{3} + d_{s_2}\frac{1}{6})$$

(2.30)

$$\frac{1}{\sqrt{3}}\sin(\zeta_s^s) = (d_{s_1}\frac{1}{3} + d_{s_2}\frac{1}{2\sqrt{3}})$$

(2.31)

For the real and imaginary part respectively. The sum of the vector durations must sum up to the total switching period:

$$T_{sw}(d_0 + d_{s1} + d_{s2}) = T_{sw}$$

$$d_0 + d_{s1} + d_{s2} = 1$$

(2.32)

This gives the duty cycles in triangle *A1*:

$$d_{S1} = M_s(\sqrt{3}\cos(\zeta_s^s) - \sin(\zeta_s^s)), \quad d_{S2} = 2M_s\sin(\zeta_s^s), \quad d_0 = 1 - d_{S1} - d_{S2}$$

(2.33)

In triangle A2, one small-, one medium- and one large vector are used:

$$T_{sw}\underline{U}_{s,ref}^{s} = T_{sw}(d_{S1}\underline{U}_{S1} + d_{L1}\underline{U}_{L1} + d_{M}\underline{U}_{M})$$

(2.34)

$$T_{sw} \frac{U_{dc}}{\sqrt{3}} M_s e^{j\zeta_s^s} = T_{sw} U_{dc} \left( d_{S1} \frac{1}{3} + d_{L1} \frac{2}{3} + d_M \frac{1}{\sqrt{3}} e^{j\frac{\pi}{6}} \right)$$

(2.35)

Using the same methods as for triangle A1, the duty cycles are:

$$d_M = 2M_s \sin(\zeta_s^s), \quad d_{L1} = -1 + M_s(\sqrt{3}\cos(\zeta_s^s) + \sin(\zeta_s^s)), \quad d_{S1} = 1 - d_M - d_{L1}$$

(2.36)

In triangle A3, two small vectors and one medium vector is utilized:

$$T_{sw}\underline{U}_{s,ref}^{s} = T_{sw}(d_{s1}\underline{U}_{s1} + d_{s2}\underline{U}_{s2} + d_{M}\underline{U}_{M})$$

(2.37)

$$T_{sw} \frac{U_{dc}}{\sqrt{3}} M_s e^{j\zeta_s^s} = T_{sw} U_{dc} \left( d_{S1} \frac{1}{3} + d_{S2} \frac{1}{3} e^{j\frac{\pi}{3}} + d_M \frac{1}{\sqrt{3}} e^{j\frac{\pi}{6}} \right)$$

(2.38)

Again, using the same methods as for triangle A1, the duty cycles are:

$$d_{s1} = 1 - 2M_s \sin(\zeta_s^s), \quad d_{s2} = 1 + M_s (\sin(\zeta_s^s) - \sqrt{3}\cos(\zeta_s^s)), \quad d_m = 1 - d_{s1} - d_{s2} (2.39)$$

Triangle A4 is similar to triangle A2, utilizing one small, one medium and one large vector:

$$T_{sw}\underline{U}_{s,ref}^{s} = T_{sw}(d_{S2}\underline{U}_{S2} + d_{M}\underline{U}_{M} + d_{L1}\underline{U}_{L2})$$

$$(2.40)$$

$$T_{sw}\frac{U_{dc}}{\sqrt{3}}M_{s}e^{j\zeta_{s}^{s}} = T_{sw}U_{dc}\left(d_{S2}\frac{1}{3}e^{j\frac{\pi}{3}} + d_{M}\frac{1}{\sqrt{3}}e^{j\frac{\pi}{6}} + d_{L2}\frac{2}{3}e^{j\frac{\pi}{3}}\right)$$

(2.41)

Again, using the same methods as for triangle A1, the duty cycles are:

$$d_{s2} = 2 + M_s(\sqrt{3}\cos(\zeta_s^s) - \sin(\zeta_s^s)), \quad d_M = M_s(\sqrt{3}\cos(\zeta_s^s) - \sin(\zeta_s^s))$$

$$d_{L2} = 1 - d_M - d_{s2}$$

(2.42)

The duty cycles for the other sectors (*B*, *D*, *E*, *F*, *G*) are exactly the same, except for  $\zeta_s^s = \zeta_s^{s'}$ . Where  $\zeta_s^{s'}$  is the angle with respect to the closest  $U_{LI}$ -axis.

#### Finding the triangle number k

For a 2-level converter, finding one of the six sectors is trivial, since the sector borders are only dependent on the reference angle  $\zeta_s^s$ . For a 3-level converter the problem is more complicated. In [37], the problem is solved by simplification of the vector space into a 2-level vector space which is moved around in the 3-level space by applying offsets to the origin. In [36] the solution is done by a coordinate transform of the reference axis.

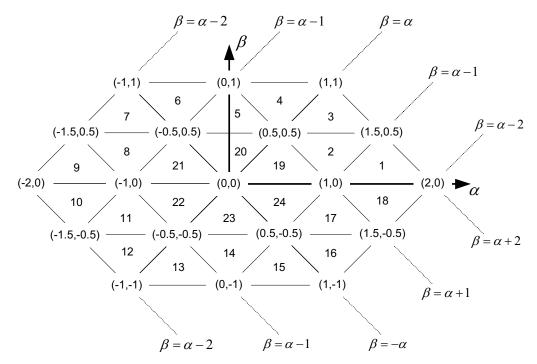

Figure 2.16: Transformed vectorspace with triangle numbers.

Another solution is presented here, and instead of changing the reference axis, the vector-space is transformed by transforming the coordinates of the vector space by a factor of  $(1,\sqrt{3})/3U_{dc}$  as shown in Figure 2.16. By this, a simpler set of coordinates for the corners of the triangles are found. Also, the reference voltage is transformed.

Defining that the left corner of each triangle is always A  $(a_{\alpha}, a_{\beta})$ , the right corner B  $(b_{\alpha}, b_{\beta})$  and either the upper or lower corner C  $(c_{\alpha}, c_{\beta})$ . As can be seen from the transformed vector space only the coordinates for A  $(a_{\alpha}, a_{\beta})$  have to be found, since corner B and the  $\alpha$ -component to corner C is fixed in position with respect to A. The  $\beta$ -component to corner C can be found from the sign of the  $\beta$ -component of the reference voltage. To find the corresponding coordinates, the following calculation has to be done:

i=1; while

$$(i-1>-u_{\alpha}+u_{\beta})$$

i=i-1;

j=-2; while  $(j+1< u_{\alpha}+u_{\beta})$  j=j+1;

Where *i* and *j* are integers [-2..2], and  $u_{\alpha}$  and  $u_{\beta}$  are the real and imaginary components of the transformed reference voltage, respectively. The coordinates of the A corner is then found from the intersection of the straight lines  $\beta = \alpha + 1$  and  $\beta = -\alpha + j$ :

$$a_{\alpha} = \frac{1}{2}(j-i), \quad a_{\beta} = \frac{1}{2}(i+j), \quad b_{\alpha} = a_{\alpha} + 1, \quad b_{\beta} = a_{\beta}, \quad c_{\alpha} = a_{\alpha} + \frac{1}{2}$$

(2.43)

Depending on the sign of  $u_{\beta}$ , the final  $c_{\beta}$  is:

$$c_{\beta} = a_{\beta} + \frac{sign(u_{\beta})}{2} \tag{2.44}$$

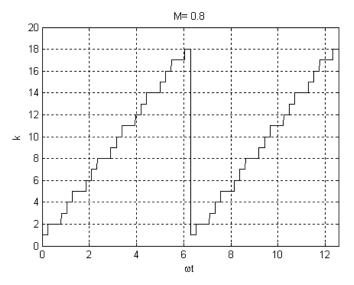

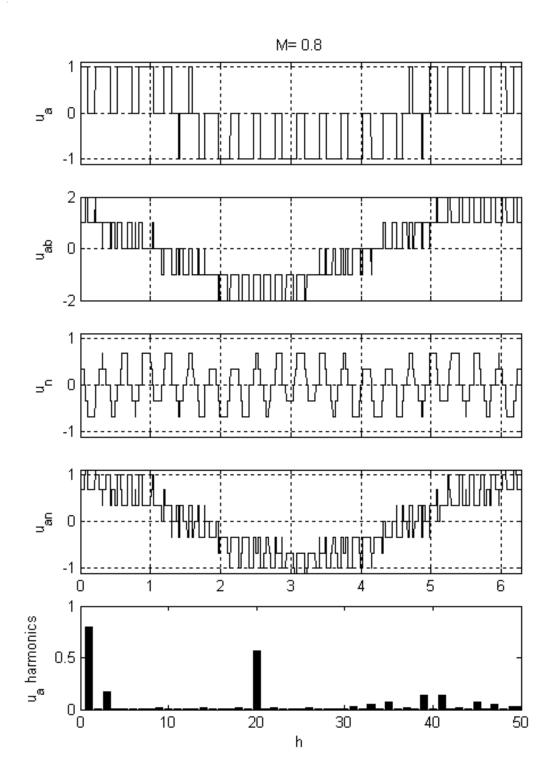

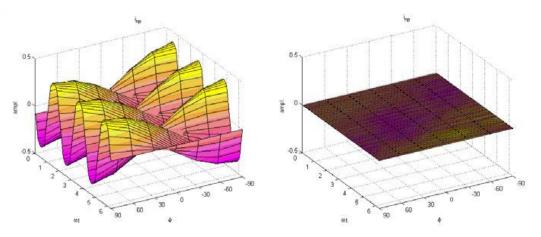

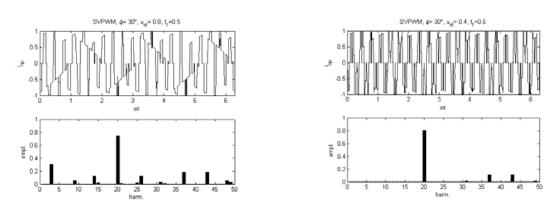

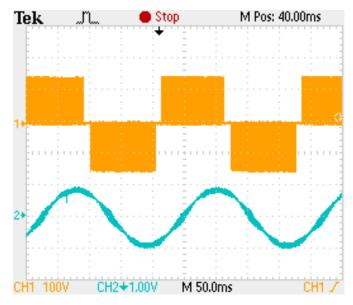

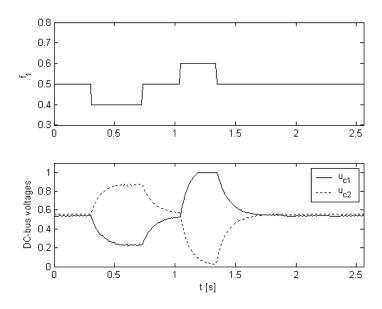

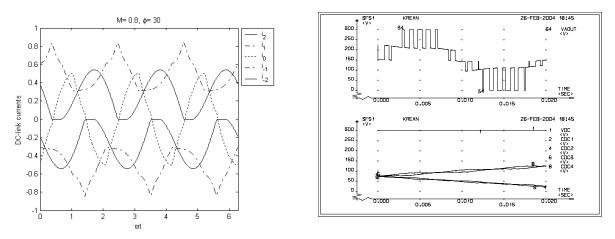

Hence, the triangle for the reference voltage vector is located. Figure 2.17 shows a result from a simulation displaying the triangle number for the reference vector at modulation depth  $M=0.8/M_s=0.693$ . When the location of the reference vector is found, there exist several ways of arranging the different output switching vectors of the converter. As for 2-level SVPWM [35] there exist a variety of different SVPWM methods for the 3-level topology. Because of the large number of available switching states, the configurations are numerous. Figure 2.18 shows one way of placing the different output vectors in sector A of the vector space. This method is presented in [34]. As will be shown in Chapter 7, this method is very useful for balancing of the DC-bus voltages. Figure 2.19 shows a simulation where the output waveforms are displayed for the SVPWM method described. The 3.harmonic component in the phase-leg voltage is caused by the modulation strategy, and will be cancelled in the load phase voltages and line-line voltages.

Figure 2.17: Triangle (k) selection at M=0.8.

Figure 2.18: Vector placement for SVPWM in Sector A.

Figure 2.19: Output waveform for 3-level SVPWM.

## 2.4 Carrier Based PWM vs. Space Vector PWM for MLC

Space Vector PWM (SVPWM) gives a direct calculation of the duty cycles for the switches. In Carrier Based PWM (CBPWM), the duty cycles can be derived from the control signals as shown in Chapter 2.3.1 and visualized in Figure 2.9. From this, it is clear that the corresponding control signals for Space Vector PWM can be found from the duty cycles. When comparing SVPWM and CBPWM it is convenient to write the control signals for sinusoidal modulation as:

$$u_{sta}(t) = M \cos(\omega t)$$

$$u_{stb}(t) = M \cos(\omega t - 2\pi/3)$$

$$u_{stb}(t) = M \cos(\omega t + 2\pi/3)$$

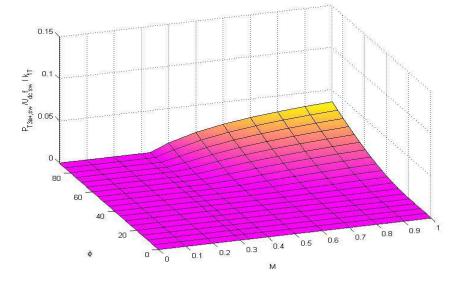

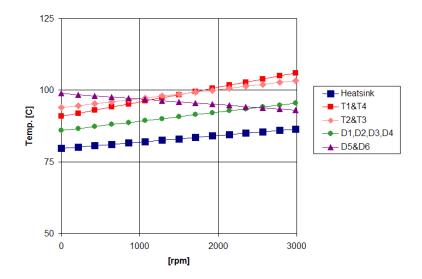

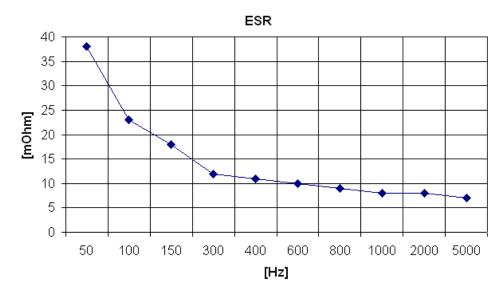

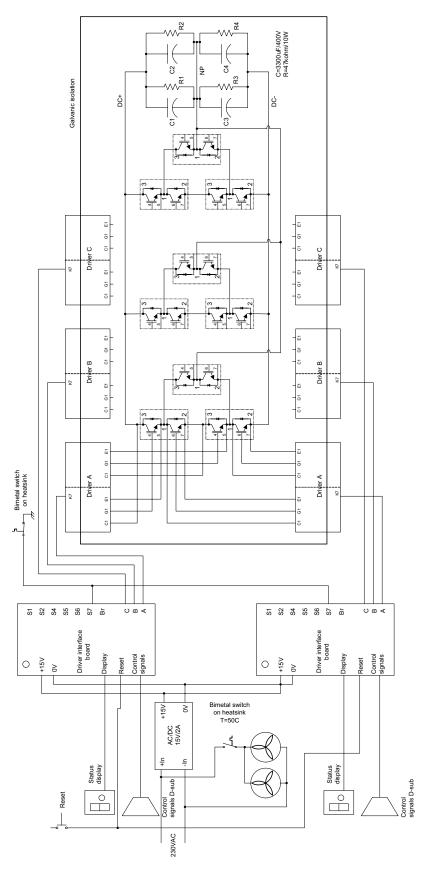

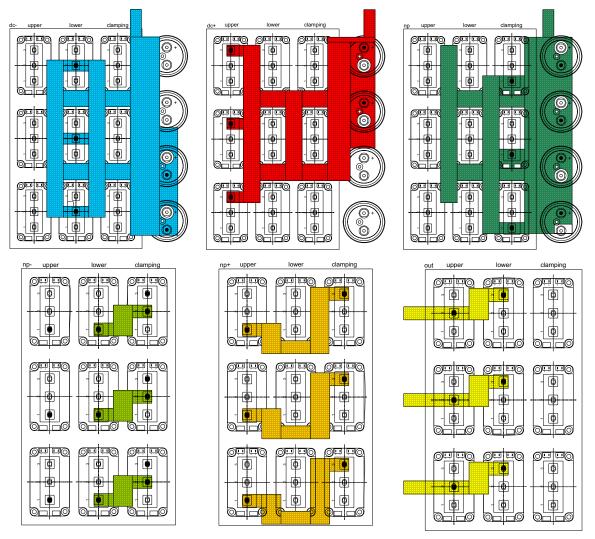

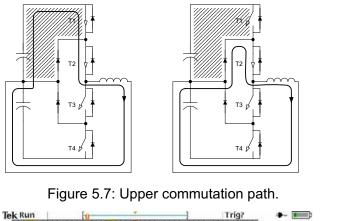

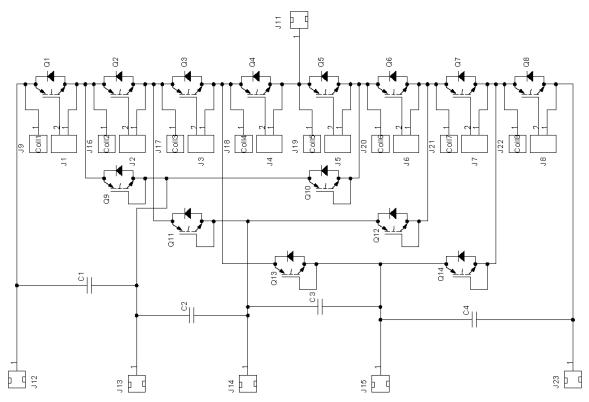

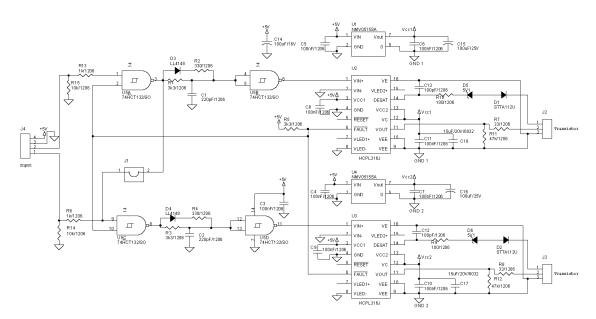

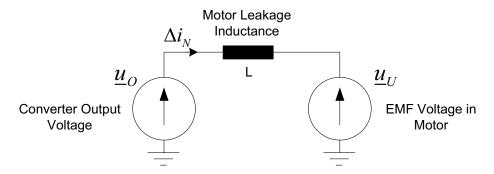

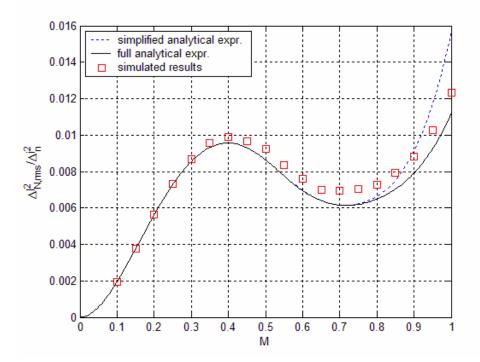

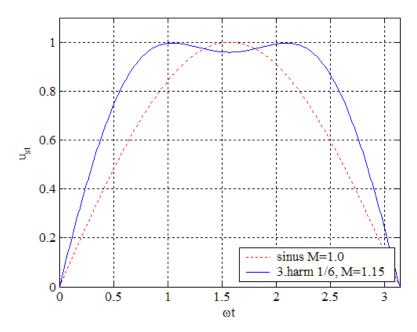

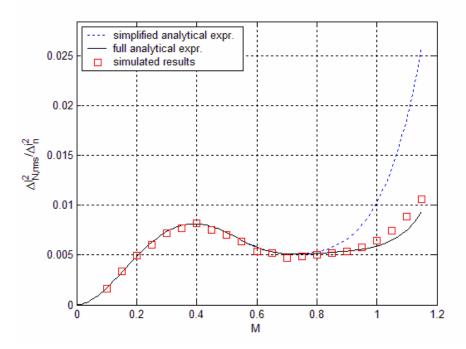

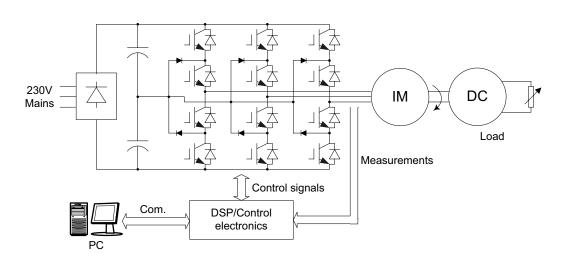

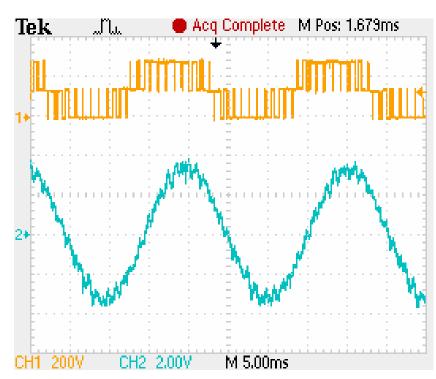

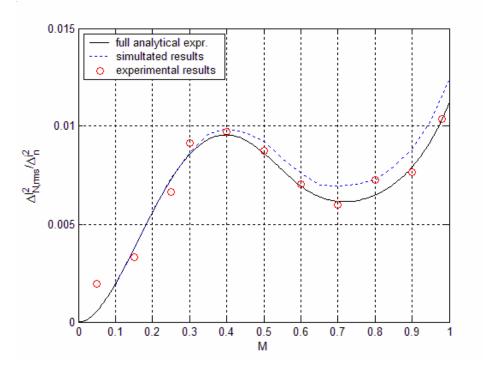

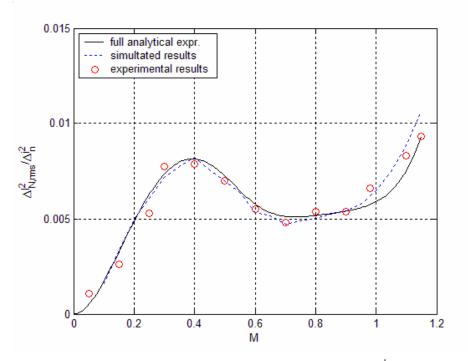

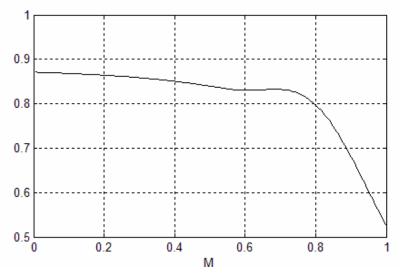

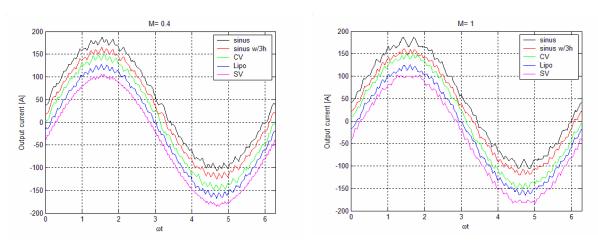

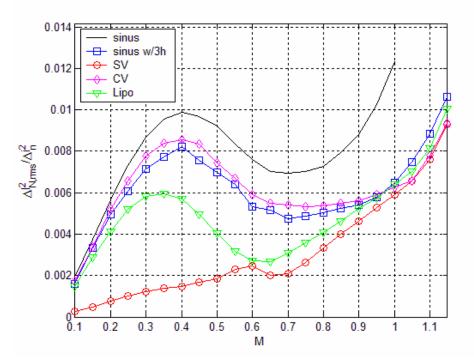

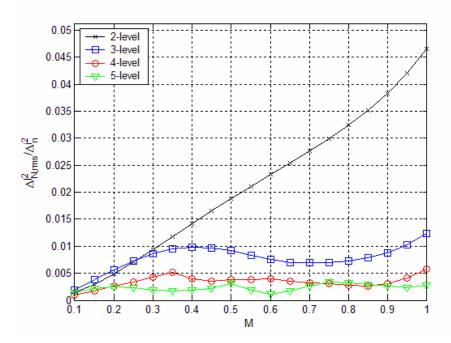

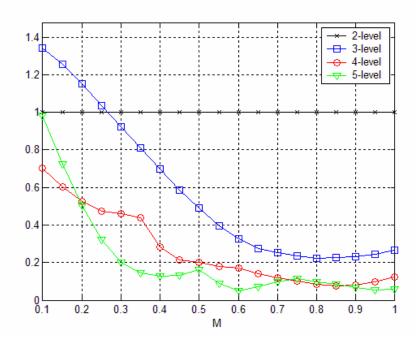

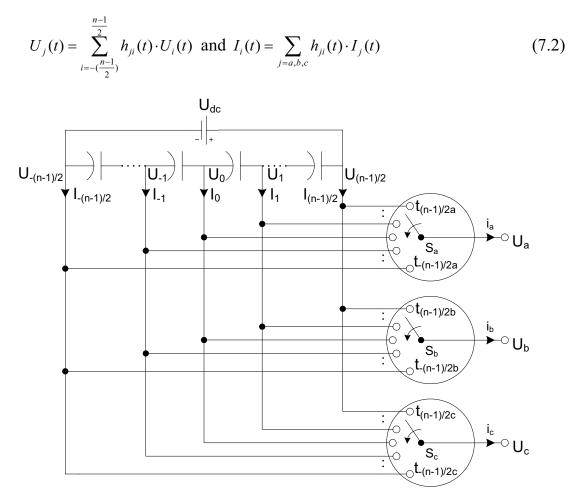

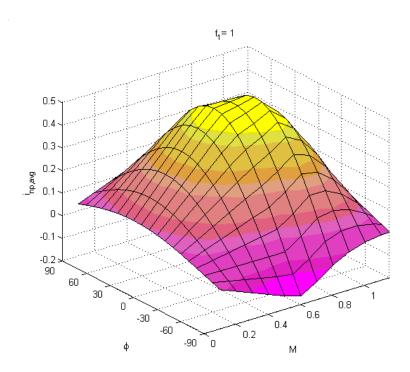

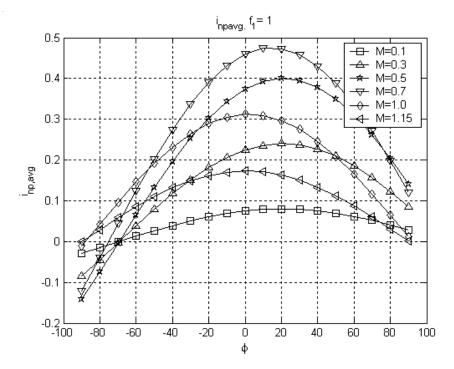

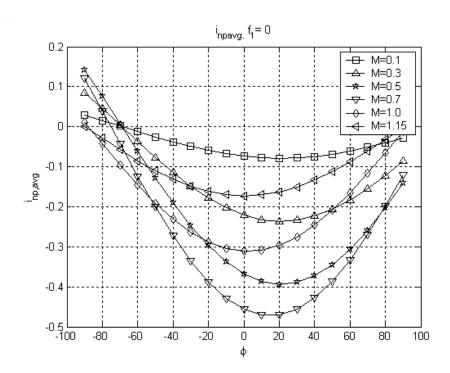

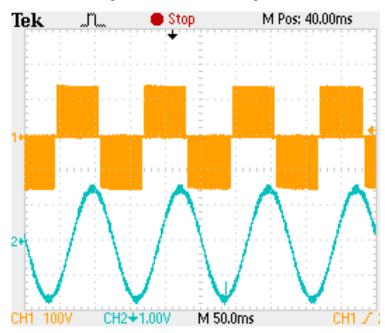

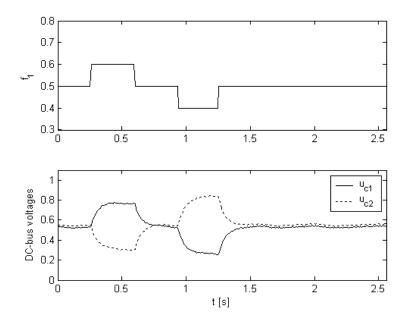

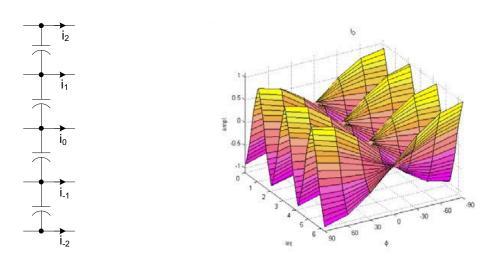

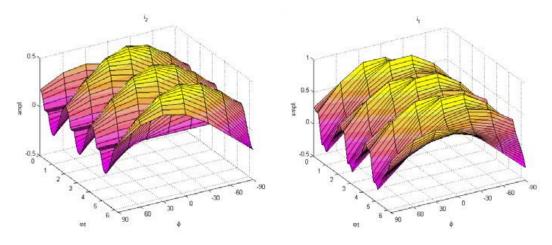

(2.45)