# Design of Low-Power Reduction-Trees in Parallel Multipliers

by

## Saeeid Tahmasbi Oskuii

Dissertation submitted to the Norwegian University of Science and Technology in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Department of Electronics and Telecommunications Norwegian University of Science and Technology Trondheim, Norway

## Abstract

Multiplications occur frequently in digital signal processing systems, communication systems, and other application specific integrated circuits. Multipliers, being relatively complex units, are deciding factors to the overall speed, area, and power consumption of digital computers. The diversity of application areas for multipliers and the ubiquity of multiplication in digital systems exhibit a variety of requirements for speed, area, power consumption, and other specifications. Traditionally, speed, area, and hardware resources have been the major design factors and concerns in digital design. However, the design paradigm shift over the past decade has entered dynamic power and static power into play as well.

In many situations, the overall performance of a system is decided by the speed of its multiplier. In this thesis, parallel multipliers are addressed because of their speed superiority. Parallel multipliers are combinational circuits and can be subject to any standard combinational logic optimization. However, the complex structure of the multipliers imposes a number of difficulties for the electronic design automation (EDA) tools, as they simply cannot consider the multipliers as a whole; i.e., EDA tools have to limit the optimizations to a small portion of the circuit and perform logic optimizations. On the other hand, multipliers are arithmetic circuits and can result in better optimization results. The different structures obtained using the different arithmetically equivalent solutions, have the same functionality but exhibit different temporal and physical behavior. The arithmetic equivalencies are used earlier mainly to optimize for area, speed and hardware resources.

In this thesis a design methodology is proposed for reducing dynamic and static power dissipation in parallel multiplier partial product reduction tree. Basically, using the information about the input pattern that is going to be applied to the multiplier (such as static probabilities and spatiotemporal correlations), the reduction tree is optimized. The optimization is obtained by selecting the power efficient configurations by searching among the permutations of partial products for each reduction stage. Probabilistic power estimation methods are introduced for leakage and dynamic power estimations. These estimations are used to lead the optimizers to minimum power consumption. Optimization methods, utilizing the arithmetic equivalencies in the partial product reduction trees, are proposed in order to reduce the dynamic power, static power, or total power which is a combination of dynamic and static power. The energy saving is achieved without any noticeable area or speed overhead compared to random reduction trees. The optimization algorithms are extended to include spatiotemporal correlations between primary inputs. As another extension to the optimization algorithms, the cost function is considered as a weighted sum of dynamic power and static power. This can be extended further to contain speed merits and interconnection power. Through a number of experiments the effectiveness of the optimization methods are shown. The average number of transitions obtained from simulation is reduced significantly (up to 35% in some cases) using the proposed optimizations.

The proposed methods are in general applicable on arbitrary multi-operand adder trees. As an example, the optimization is applied to the summation tree of a class of elementary function generators which is implemented using summation of weighted bit-products. Accurate transistor-level power estimations show up to 25% reduction in dynamic power compared to the original designs.

Power estimation is an important step of the optimization algorithm. A probabilistic gate-level power estimator is developed which uses a novel set of simple waveforms as its kernel. The transition density of each circuit node is estimated. This power estimator allows to utilize a global glitch filtering technique that can model the removal of glitches in more detail. It produces error free estimates for tree structured circuits. For circuits with reconvergent fanout, experimental results using the ISCAS85 benchmarks show that this method generally provides significantly better estimates of the transition density compared to previous techniques.

## Preface

This thesis is submitted in partial fulfillment of the requirements for the degree of Philosophiae Doctor (Ph.D.) at the Department of Electronics and Telecommunications, Norwegian University of Science and Technology (NTNU). My main supervisor has been Associate Professor Per Gunnar Kjeldsberg, while my cosupervisors have been Associate Professor Lars Lundheim and Professor Geir Øien, all of whom are with the Department of Electronics and Telecommunications at NTNU. I spent about four months at Electronics Systems group at Linköping University for research cooperation under the supervision of Assistant Professor Oscar Gustafsson. The last six months I have worked at the University of Oslo.

The studies have been carried out in the period from January 2004 to March 2008. The work includes the equivalent of half a year of full-time course studies and approximately one year of teaching duties. The latter included being a teaching assistant in several graduate courses, as well as being an advisor for one student working on his master thesis.

The work included in this thesis has been funded by the Department of Electronics and Telecommunications, NTNU.

### Acknowledgments

I have a theory that when I am happy, time passes more quickly. It has been over four years now from the day I started as a Ph.D. student at Norwegian University of Science and Technology and these four years have passed extremely quick. Indeed, these years have been nothing but happiness and excitement and I owe this to many people who have helped me in this part of my life and in the course of my research throughout these years.

First of all, I would like to thank my supervisor, Associate Professor Per Gunnar Kjeldsberg. I could not have imagined having a better advisor for my Ph.D., and without his constant encouragement, perceptiveness and advice over these years I could ever come this far. I am very grateful for his encouragement, common-sense and being available to help me whenever I needed it. I am also very grateful to my co-supervisors Associate Professor Lars Lundheim and Professor Geir Øien for the valuable discussions and insightful advise.

I am thankful to Assistant Professor Oscar Gustafsson who was hosting me during my stays at Linköping University. I am very grateful for his fruitful discussions, valuable comments, and feedback. My special thanks also go to Kenny Johansson for his contributions to this thesis. I am amazed by his punctuality and his ability to find small errors. I am also grateful to Professor Jim Tørresen at ROBIN group, Department of Informatics, University of Oslo, for letting me have an office at his group.

I would also like to thank my colleagues and friends at the Department of Electronics and Telecommunications, NTNU and especially those of the Circuits and Systems and Signal Processing groups. There are many people I should thank for making these years so memorable, and by naming a few of them I will certainly run the risk of forgetting others. Therefore, I simply want to thank all the people who have made these years so enjoyable.

I would like to express my gratitude to my treasured family for their support and unconditional love throughout all these years. And last but most importantly, I am greatly indebted to my sweet Jeiran, my wife, for all support and encouragement. She has been the greatest source of love and inspiration.

# Contents

| Ab | ostrac  | t          |                                         | i   |

|----|---------|------------|-----------------------------------------|-----|

| Pr | eface   |            |                                         | iii |

| Ac | know    | ledgme     | nts                                     | iv  |

| Li | st of A | Abbrevia   | ations                                  | XV  |

| 1  | Intro   | duction    | 1                                       | 1   |

|    | 1.1     | Sources    | s of Power Consumption                  | 2   |

|    |         | 1.1.1      | Static Power Dissipation                | 2   |

|    |         | 1.1.2      | Dynamic Power Dissipation               | 3   |

|    |         |            | 1.1.2.1 Short-Circuit Power Dissipation | 3   |

|    |         |            | 1.1.2.2 Switching Power Dissipation     | 4   |

|    |         | 1.1.3      | Power Consumption in Multipliers        | 5   |

|    | 1.2     | Probab     | ilistic Treatment of Multipliers        | 6   |

|    | 1.3     | Outline    | e of the Thesis                         | 9   |

|    | 1.4     | Main C     | Contributions                           | 11  |

| 2  | Mul     | tiplicatio | on Schemes                              | 13  |

|    | 2.1     | Classifi   | ication of Multipliers                  | 16  |

|    |         | 2.1.1      | Sequential Multipliers                  | 16  |

|    |         | 2.1.2      | Parallel Multipliers                    | 16  |

|    |         | 2.1.3      | Array Multipliers                       | 17  |

|    | 2.2     | Parallel   | l Multipliers                           | 17  |

|    |         | 2.2.1      | Partial Product Generation              | 17  |

|    |         |            | 2.2.1.1 Higher Radix Multipliers        | 20  |

|    |         |            | 2.2.1.2 Recoding Techniques             | 21  |

|   |      | 2.2.2    | Partial Pr   | roduct Accumulation                             | 23 |

|---|------|----------|--------------|-------------------------------------------------|----|

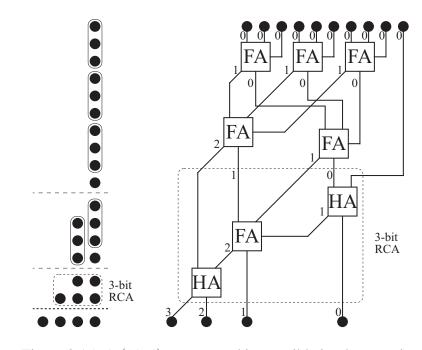

|   |      |          | 2.2.2.1      | Carry-Save Adders                               | 25 |

|   |      |          | 2.2.2.2      | Wallace Reduction Tree                          | 27 |

|   |      |          | 2.2.2.3      | Dadda Reduction Tree                            | 31 |

|   |      |          | 2.2.2.4      | Modified Dadda-Wallace Reduction Tree           | 32 |

|   |      |          | 2.2.2.5      | Generalized Parallel Counters                   | 34 |

|   |      |          | 2.2.2.6      | Parallel Multipliers with Redundant Full-Adders | 34 |

|   |      | 2.2.3    | The Fina     | l Carry Propagate Adder                         | 37 |

|   | 2.3  | Flexib   | ility in the | Reduction Tree                                  | 39 |

|   |      | 2.3.1    | Optimizi     | ng for Area, Delay and Hardware Resources       | 39 |

|   |      | 2.3.2    | Optimizi     | ng for Power                                    | 40 |

|   | 2.4  | Choice   | e of the Mu  | Iltiplier Structure                             | 41 |

| 3 | Pow  | er Estii | nation in (  | Combinational Circuits                          | 43 |

|   | 3.1  | Dynan    | nic Power    | Estimation                                      | 43 |

|   |      | 3.1.1    | Power Es     | stimation using Simple Waveform Set             | 44 |

|   |      |          | 3.1.1.1      | Simple Waveform Set                             | 46 |

|   |      |          | 3.1.1.2      | Computation of Simple Waveform Sets             | 48 |

|   |      |          | 3.1.1.3      | Dealing with interdependencies                  | 50 |

|   |      |          | 3.1.1.4      | Glitch filtering                                | 52 |

|   |      |          | 3.1.1.5      | Experiments                                     | 55 |

|   |      | 3.1.2    | High-Lev     | vel Power Estimation                            | 59 |

|   | 3.2  | Static   | Power Esti   | mation                                          | 60 |

| 4 | Trai | nsition- | Activity A   | ware Design of Reduction-Trees                  | 63 |

|   | 4.1  | Constr   | ruction of t | he Reduction Tree                               | 63 |

|   | 4.2  | Metho    | d 1: Optim   | nization of Complete Reduction Tree             | 66 |

|   |      | 4.2.1    | Power Es     | stimation                                       | 71 |

|   |      | 4.2.2    | Notation     | of the multipliers                              | 72 |

|   |      | 4.2.3    | Experime     | ents                                            | 73 |

|   | 4.3  | Metho    | d 2: Progre  | essive Design of Reduction Tree                 | 78 |

|   |      | 4.3.1    | Progressi    | ive PPRT Design and the SWS Power Estimator .   | 81 |

|   |      | 4.3.2    | Experime     | ents                                            | 83 |

|   |      | 4.3.3    | Runtime      | and Complexity                                  | 90 |

| 5 | PPR  | T Opti   | mization i   | n Presence of Highly Correlated Inputs          | 95 |

|   | 5.1  | _        |              | Correlation of Inputs                           | 96 |

|   |      | 5.1.1    |              | g Spatial Correlations                          | 97 |

|   |      |          |              |                                                 |    |

|   |     | 5.1.2 Modeling Temporal Correlations                             |

|---|-----|------------------------------------------------------------------|

|   | 5.2 | Design Methodology                                               |

|   | 5.3 | Experiments                                                      |

|   |     | 5.3.1 Temporal correlations of input words                       |

|   |     | 5.3.2 Spatial correlations of input words                        |

|   |     | 5.3.3 MAC-based FIR filter                                       |

| 6 | Red | ucing the Static Power for the PPRT 113                          |

|   | 6.1 | Progressive Reduction-Tree Design                                |

|   |     | 6.1.1 Experiments                                                |

|   | 6.2 | Reducing Total Power for the PPRT                                |

|   |     | 6.2.1 Experiments                                                |

| 7 | Opt | imization of Multipliers Operating with Variable Word-Length 123 |

|   | 7.1 | Variable Word-Length                                             |

|   | 7.2 | Experiments                                                      |

|   |     | 7.2.1 General-Purpose Multiplier                                 |

|   |     | 7.2.2 FFT Processor with Variable Word-Length                    |

| 8 | Fun | ction Generation using a Weighted Sum of Bit-Products 137        |

|   | 8.1 | Elementary Function Generation                                   |

|   |     | 8.1.1 Approximation using a Weighted Sum of Bit-Products 140     |

|   |     | 8.1.2 Architecture                                               |

|   | 8.2 | Optimized Summation-Tree Generation                              |

|   | 8.3 | Experiments                                                      |

| 9 | Con | clusions 151                                                     |

|   | 9.1 | Low-Transition Reduction-Tree Generation                         |

|   | 9.2 | Low-Leakage Reduction-Tree Generation                            |

|   | 9.3 | Generalized Multi-Operand Adders                                 |

|   | 9.4 | Probabilistic Gate-Level Power Estimator                         |

|   | 9.5 | Directions for Future Work                                       |

|   |     | 9.5.1 Power Estimation with Realistic Delay Models 153           |

|   |     | 9.5.2 Including Speed and Interconnect Power                     |

|   |     | 9.5.3 Different PP Generation and Reduction Schemes 154          |

|   |     | 9.5.4 Other Search Algorithms                                    |

|   |     | 9.5.5 Pipelining                                                 |

|   |     | 9.5.6 Optimization of Synthesized Designs                        |

|   |     |                                                                  |

| Ap | Appendix 1      |                                                                                  |  |  |

|----|-----------------|----------------------------------------------------------------------------------|--|--|

| A  |                 | Putation of static probabilitiesPairwise Correlation CoefficientsA.1.1An Example |  |  |

| B  | <b>B</b> .1     | mples of Computing SWSsTree-Structured exampleA 2-to-1 MUX Example               |  |  |

| Bi | Bibliography 19 |                                                                                  |  |  |

# **List of Figures**

| 1.1  | Dynamic and static power in Watt for microprocessor chips                          | 3  |

|------|------------------------------------------------------------------------------------|----|

| 1.2  | Computation of static probabilities                                                | 8  |

| 2.1  | Shift-and-Add multiplication scheme                                                | 14 |

| 2.2  | Block diagram for a shift-and-add multiplier                                       | 15 |

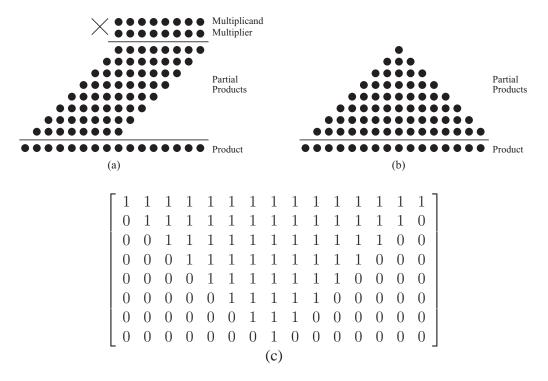

| 2.3  | The dot-diagram representation of an $8 \times 8$ -bit multiplier                  | 15 |

| 2.4  | Signed multiplication                                                              | 19 |

| 2.5  | $8\times8\text{-bit}$ Radix-4 multiplication in dot-diagram and its structure $$ . | 20 |

| 2.6  | Overlapping multiple bit scanning in radix-4 MBR                                   | 22 |

| 2.7  | Accumulating PPs using two-operand adders                                          | 23 |

| 2.8  | Carry propagation and carry-free operation                                         | 24 |

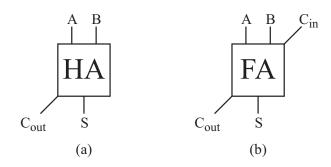

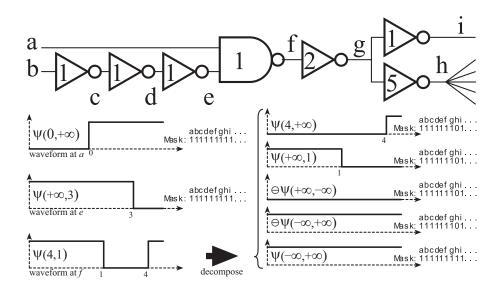

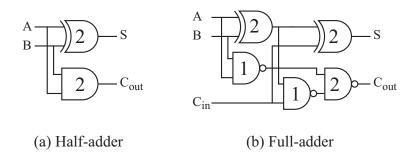

| 2.9  | A half-adder(a) and a full-adder(b)                                                | 26 |

| 2.10 | A typical gate-level implementation of full-adder and half-adder .                 | 27 |

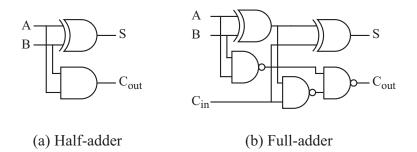

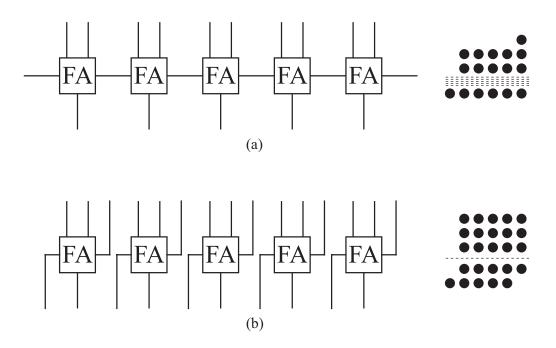

| 2.11 | The relationship between RCA and CSA                                               | 28 |

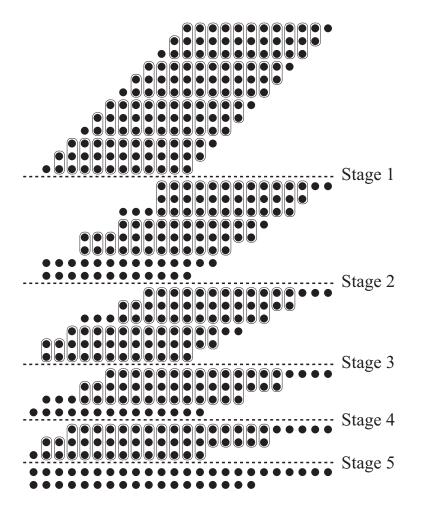

| 2.12 | Wallace's scheme for a $12 \times 12$ -bit unsigned multiplier                     | 30 |

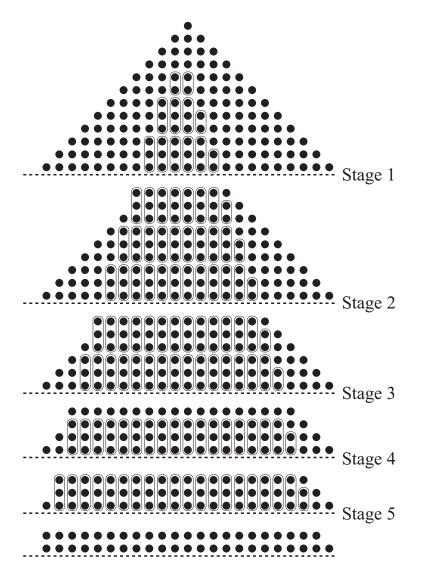

| 2.13 | Using Dadda's strategy for a $12 \times 12$ -bit multiplier                        | 33 |

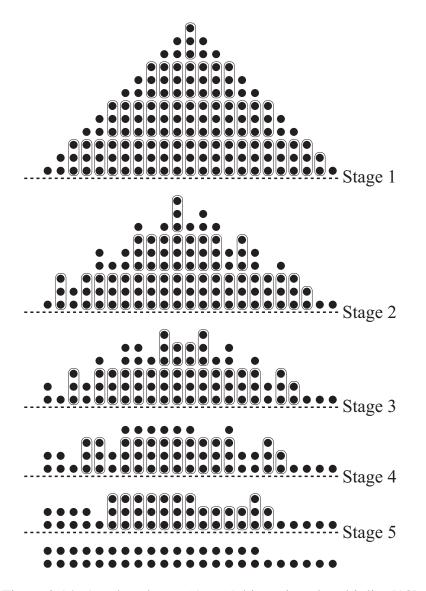

| 2.14 | A reduced-area $12 \times 12$ -bit unsigned multiplier [13]                        | 35 |

| 2.15 | A $(10; 4)$ counter and its possible implementation                                | 36 |

| 2.16 | Examples of generalized parallel counters                                          | 36 |

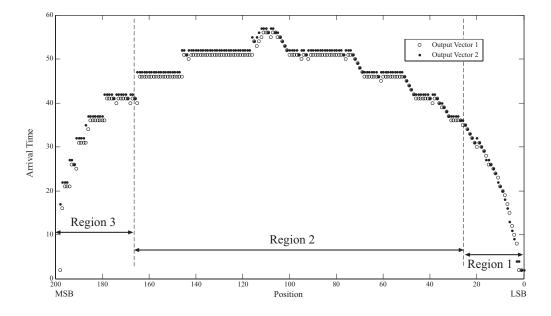

| 2.17 | The arrival time profile for output bit-vectors of the dadda PPRT .                | 38 |

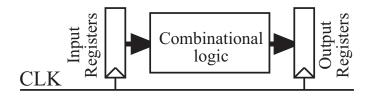

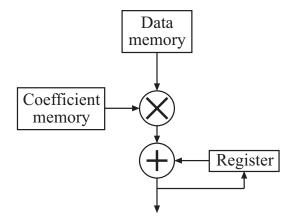

| 3.1  | The target circuit architecture for power estimator                                | 45 |

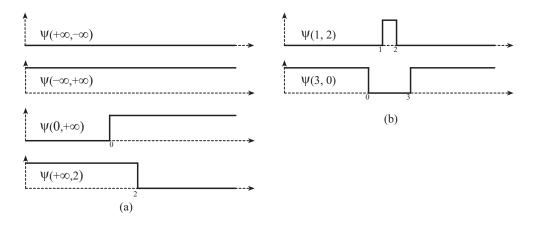

| 3.2  | Examples of simple and non-simple waveforms                                        | 47 |

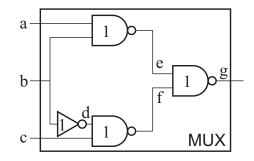

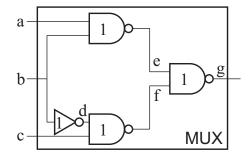

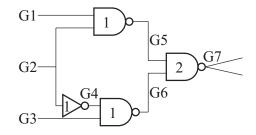

| 3.3  | A 2-to-1 MUX example                                                               | 48 |

| 3.4  | Generation and decomposition of non-simple waveforms                               | 49 |

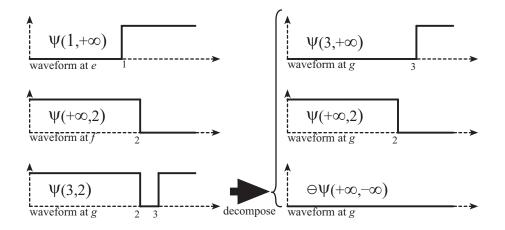

| 3.5  | Algorithm I for computing SWSs                                                     | 50 |

| 3.6  | Algorithm II for computing SWSs with glitch filtering                              | 53 |

| 3.7  | An example of glitch filtering                                                     | 54 |

| 3.8  | Propagation delays in Full-adders and Half-adders                                                  | 55  |

|------|----------------------------------------------------------------------------------------------------|-----|

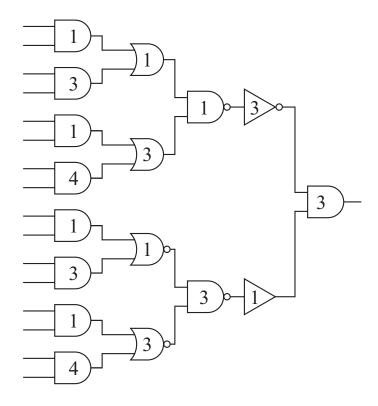

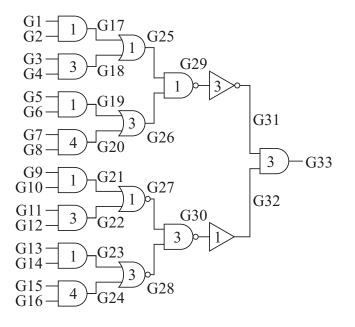

| 3.9  | An example tree-structured circuit                                                                 | 56  |

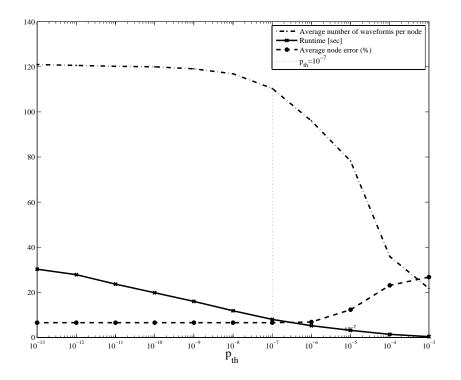

| 3.10 | Average node error, average number of waveforms per node and runtime versus $p_{th}$ for C1355     | 58  |

| 3.11 | A NAND gate with possible input values                                                             | 62  |

|      |                                                                                                    | -   |

| 4.1  | The multiplier generation algorithm                                                                | 64  |

| 4.2  | The PPM, FA and HA matrices for a $12\times12\text{-bit}$ unsigned multiplier                      | 65  |

| 4.3  | The multiplier optimization algorithm - Method 1                                                   | 67  |

| 4.4  | Sorting PPs based on their estimated transition densities                                          | 70  |

| 4.5  | Worst-case multiplier algorithm - Method 1                                                         | 71  |

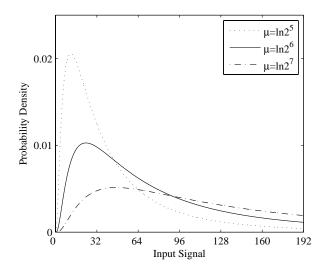

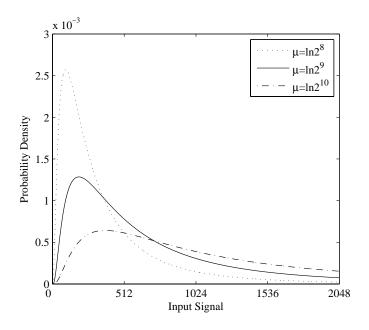

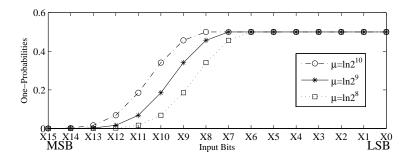

| 4.6  | Log-normal signal distribution                                                                     | 77  |

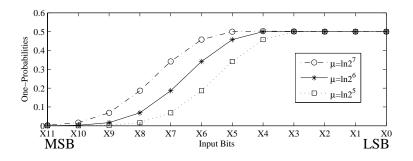

| 4.7  | One-probabilities of input bits with log-normal distribution                                       | 77  |

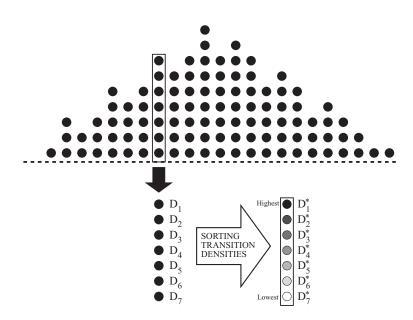

| 4.8  | The multiplier optimization algorithm - Method 2                                                   | 79  |

| 4.9  | Progressive reduction-tree design using SWS power estimator                                        | 82  |

| 4.10 | The worst-case multiplier generation algorithm                                                     | 84  |

|      | Log-normal signal distribution                                                                     | 89  |

|      | One-probabilities of input bits with log-normal distribution                                       | 89  |

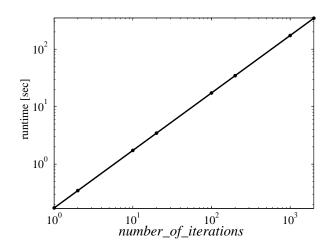

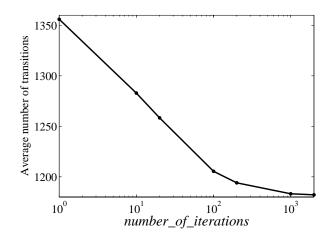

| 4.13 | Runtime versus number of iteration in SA                                                           | 92  |

|      | Average number of transitions versus number of iterations in SA .                                  | 92  |

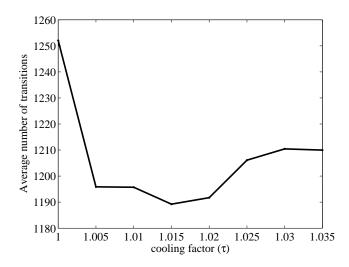

| 4.15 | Cooling factor                                                                                     | 93  |

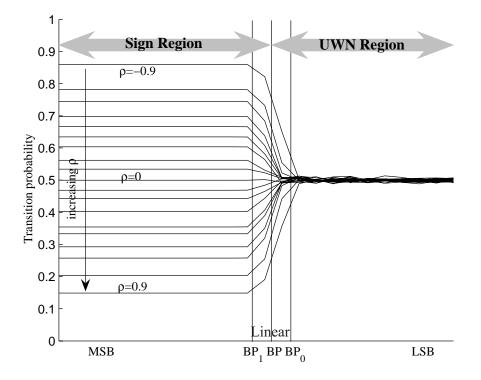

| 5.1  | Transition activity vs. bit positions with varying $\rho$                                          | 99  |

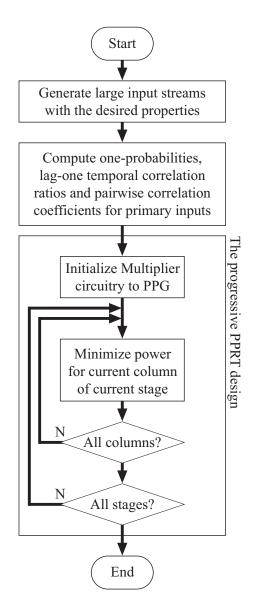

| 5.2  | The generalized design methodology                                                                 | 02  |

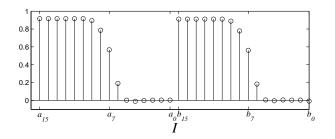

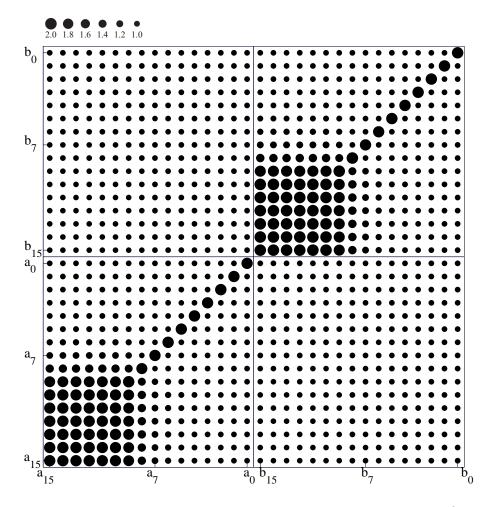

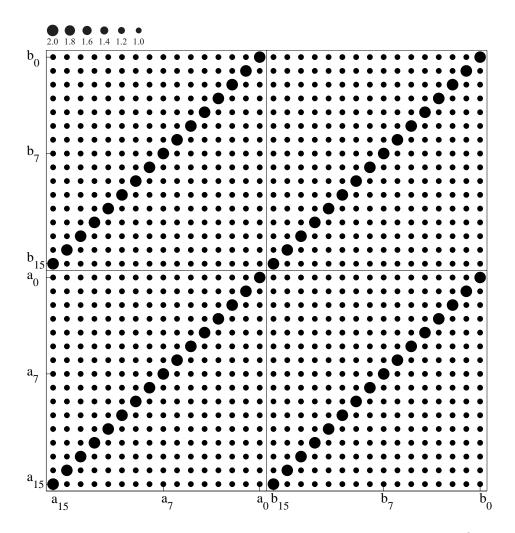

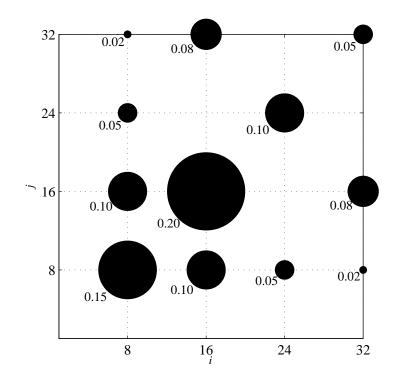

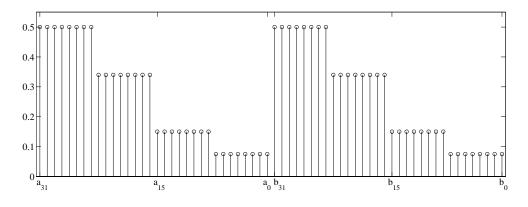

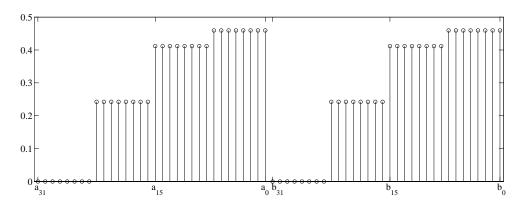

| 5.3  | Illustration of lag-one temporal correlation ratio vector ( $\mathcal{R}$ ) for $\Phi_{0.99}^{16}$ |     |

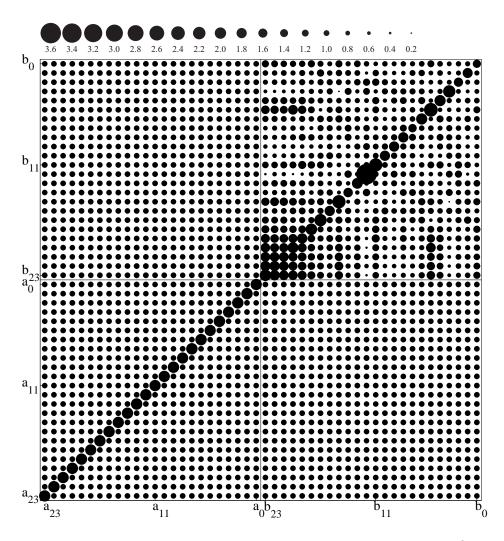

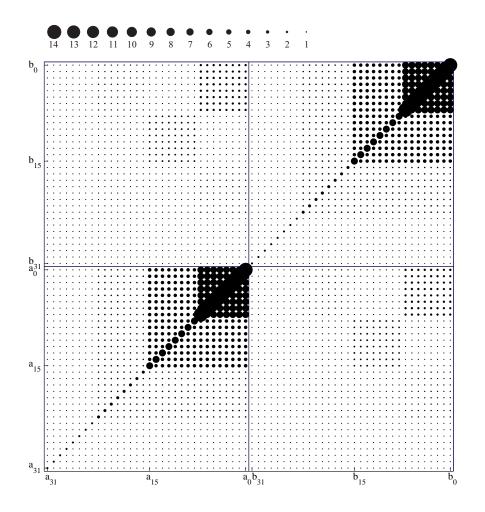

| 5.4  | Illustration of pairwise correlation coefficient matrix ( $C$ ) 1                                  |     |

| 5.5  | Illustration of pairwise correlation coefficient matrix $(C)$ 1                                    |     |

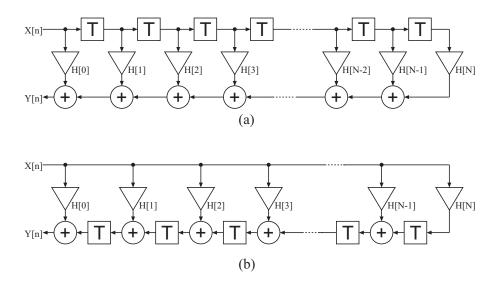

| 5.6  | FIR filter implementation                                                                          |     |

| 5.7  | Multiply accumulate architecture                                                                   | 10  |

| 5.8  | Illustration of pairwise correlation coefficient matrix ( $C$ ) 1                                  | 12  |

| 6.1  | Progressive reduction-tree design using static power estimator 1                                   | 15  |

| 6.2  | Progressive PPRT design for total power reduction                                                  |     |

|      |                                                                                                    |     |

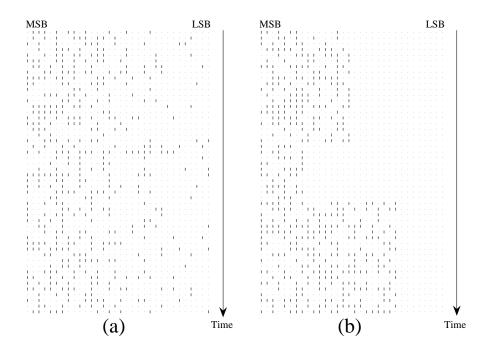

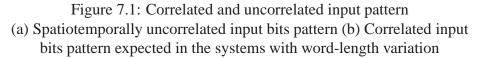

| 7.1  | Correlated and uncorrelated input pattern                                                          |     |

| 7.2  |                                                                                                    | 29  |

| 7.3  |                                                                                                    | .32 |

| 7.4  |                                                                                                    | 33  |

| 7.5  | Lag-one temporal correlation ratios for primary input bits 1                                       | 34  |

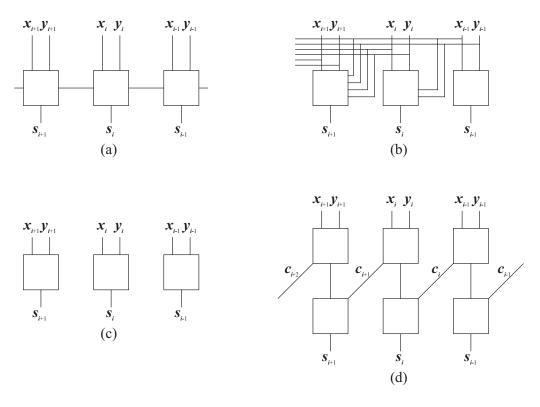

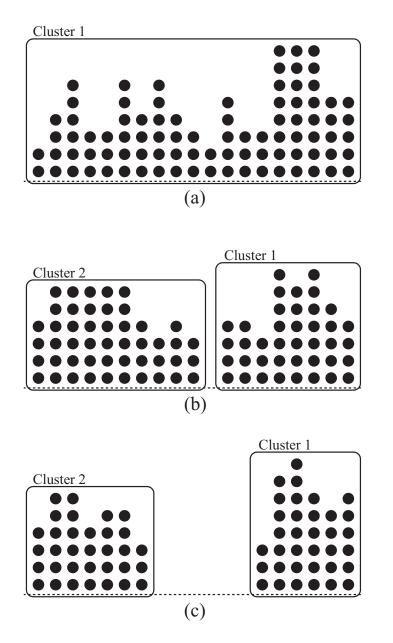

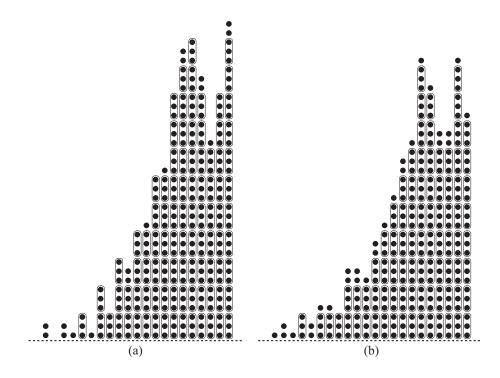

| 8.1 | Different patterns for partial products in multi-operand adders 138     |

|-----|-------------------------------------------------------------------------|

| 8.2 | Architecture used for approximating elementary functions 142            |

| 8.3 | Progressive reduction-tree design algorithm for function generators 144 |

| 8.4 | The primary PP pattern for the (a) COSINE and (b) SINE functions 146    |

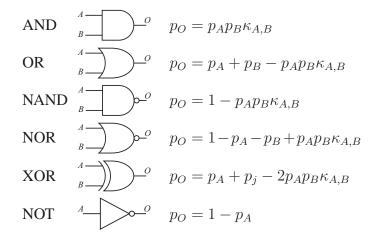

| A.1 | Calculating output one-probability of the basic logic gates 160         |

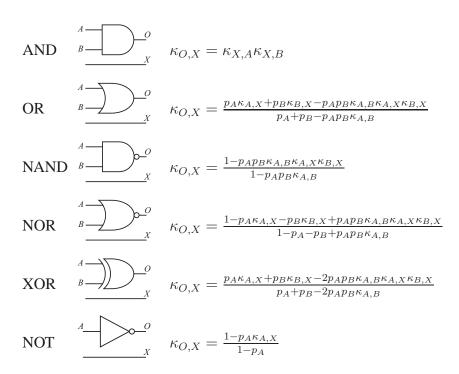

| A.2 | Calculating correlation coefficients for basic logic gates 162          |

| A.3 | An example of static probability computation                            |

|     | An example tree-structured circuit                                      |

| В.2 | A 2-to-1 MUX example                                                    |

# **List of Tables**

| 2.1  | Booth's recoding algorithm                                                                      | 21 |

|------|-------------------------------------------------------------------------------------------------|----|

| 2.2  | Radix-4 modified Booth's recoding algorithm                                                     | 22 |

| 2.3  | Truth-table and behavioral representation of half-adder                                         | 26 |

| 2.4  | Truth-table and behavioral representation of full-adder                                         | 26 |

| 2.5  | The Dadda sequence for minimal number of reduction stages                                       | 31 |

| 3.1  | Power estimation error for ISCAS'85 benchmark circuits with                                     |    |

|      | fanout delay assignment. All errors are in percentage                                           | 57 |

| 3.2  | Runtime and computation complexity for ISCAS'85 benchmark                                       |    |

|      | circuits with fanout delay assignment. All errors are in percentage.                            | 59 |

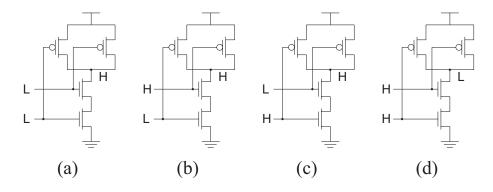

| 3.3  | The normalized leakage current for the logic gates                                              | 61 |

| 4.1  | Number of search alternatives in one column                                                     | 69 |

| 4.2  | The search alternatives of a 7-bit column                                                       | 70 |

| 4.3  | Estimated energy per operation for different multipliers [pJ]                                   | 74 |

| 4.4  | Estimated energy per operation for optimized multipliers [pJ]                                   | 74 |

| 4.5  | Estimated energy per operation for multipliers with log-normal                                  |    |

|      | inputs                                                                                          | 78 |

| 4.6  | Average number of transitions for different multipliers                                         | 85 |

| 4.7  | Average number of transitions with realistic delay model                                        | 86 |

| 4.8  | Estimations of energy per operation from Synopsys Power Com-                                    |    |

|      | piler for $0.35 \mu m$ CMOS library                                                             | 86 |

| 4.9  | Estimations of energy per operation from Synopsys Power Com-<br>piler for a $65nm$ CMOS library | 86 |

| 4.10 |                                                                                                 | 88 |

|      | Average number of transitions for different multipliers                                         | 90 |

| 4.11 | Average number of transitions for different multipliers                                         | 90 |

| 5.1         | Average number of transitions for different multipliers with tem-<br>porally correlated inputs                                                                           |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2         | Average number of transitions for different multipliers with spa-                                                                                                        |

|             | tially correlated inputs                                                                                                                                                 |

| 5.3         | Average number of transitions for MAC-based FIR filter 111                                                                                                               |

| 6.1         | Unsigned multipliers with independent input bits                                                                                                                         |

| 6.2         | Signed $16 \times 16$ multipliers with correlated input bits $\ldots \ldots \ldots 118$                                                                                  |

| 6.3         | $16 \times 16$ multipliers optimized for total power $\dots \dots \dots$ |

| 7.1         | Non-zero elements in the word-length probability density matrix                                                                                                          |

|             | $(\mathcal{W})$ in example 1                                                                                                                                             |

| 7.2         | Average number of transitions for different multipliers 130                                                                                                              |

| 7.3         | Word-length probabilities for an FFT processor with fading channel135                                                                                                    |

| 7.4         | Average number of transitions for different multipliers 135                                                                                                              |

| 8.1         | Coefficient values in terms of function values                                                                                                                           |

| 8.2         | Function definitions                                                                                                                                                     |

| 8.3         | Average transition activity per clock cycle                                                                                                                              |

| 8.4         | Estimated energy per operation from NanoSim [pJ]                                                                                                                         |

| <b>B</b> .1 | Average transition activity for nodes in Figure B.1                                                                                                                      |

| B.2         | The simple waveform sets for the example tree-structured circuit . 172                                                                                                   |

| B.3         | Average transition activity for nodes in Figure B.2                                                                                                                      |

| <b>B</b> .4 | The simple waveform sets for the 2-to-1 MUX example 174                                                                                                                  |

# **List of Abbreviations**

| Abbreviation | Definition                              | Page |

|--------------|-----------------------------------------|------|

| ASIC         | Application Specific Integrated Circuit | 1    |

| CMOS         | Complementary Metal-Oxide-Semiconductor | 2    |

| CORDIC       | COordinate Rotation DIgital Computer    | 139  |

| CPA          | Carry-Propagate Adder                   | 23   |

| CSA          | Carry-Save Adder                        | 25   |

| CSD          | Canonical Signed Digit                  | 22   |

| CSNR         | Channel Signal to Noise Ratio           | 132  |

| CUT          | Circuit Under Test                      | 44   |

| DBT          | Dual Bit Type                           | 98   |

| DCT          | Discrete Cosine Transform               | 139  |

| DDFS         | Direct Digital Frequency Synthesizer    | 139  |

| DFT          | Discrete Fourier Transform              | 139  |

| DSP          | Digital Signal Processor                | 1    |

| EDA          | Electronic Design Automation            | 1    |

| FA           | Full-Adder                              | 25   |

| FFT          | Fast Fourier Transform                  | 139  |

| FIR          | Finite-length Impulse Response          | 103  |

| HA           | Half-Adder                              | 25   |

| GA           | Genetic Algorithm                       | 154  |

| LN           | Log-Normal distribution                 | 116  |

| LSB          | Least Significant Bit                   | 37   |

| MAC          | Multiply-Accumulate                     | 95   |

| MBR          | Modified Booth's Recoding               | 22   |

| MSB          | Most Significant Bit                    | 37   |

| MSD          | Minimum Signed Digit                    | 142  |

| Abbreviation | Definition                                 | Page |

|--------------|--------------------------------------------|------|

| OBDD         | Ordered Binary Decision Diagram            | 61   |

| OFDM         | Orthogonal Frequency Division Multiplexing | 132  |

| OPT          | Optimized                                  | 72   |

| PDF          | Probability Density Function               | 6    |

| PP           | Partial Product                            | 13   |

| PPG          | Partial Product Generation                 | 17   |

| PPM          | Partial Product Matrix                     | 14   |

| PPRT         | Partial Product Reduction Tree             | 27   |

| RCA          | Ripple-Carry Adder                         | 23   |

| RFO          | Reconvergent FanOut                        | 50   |

| RND          | Randomly generated multiplier              | 72   |

| ROBDD        | Reduced Ordered Binary Decision Diagram    | 157  |

| ROM          | Read Only Memory                           | 140  |

| RT           | Reduction Tree                             | 27   |

| SA           | Simulated Annealing                        | 80   |

| SNR          | Signal to Noise Ratio                      | 132  |

| SWS          | Simple Waveform Set                        | 46   |

| TDM          | Three Dimensional Minimization             | 40   |

| TPS          | Tagged Probabilistic Simulation            | 43   |

| UD           | Uniform Distribution                       | 116  |

| UWN          | Uniform White Noise                        | 98   |

| VHDL         | VHSIC Hardware Description Language        | 73   |

| VHSIC        | Very High Speed Integrated Circuits        | xvi  |

| VLSI         | Very Large Scale Integration               | 1    |

| VMA          | Vector Merge Adder                         | 37   |

| WC           | Worst-Case                                 | 72   |

| WSS          | Wide Sense Stationary                      | 6    |

## Chapter 1

## Introduction

Multipliers have been important since the introduction of the digital computers. Multiplication occurs frequently in Digital Signal Processing (DSP) systems, communication systems and other Application Specific Integrated Circuits (ASICs). Because of the significance of multiplication in scientific and engineering computations, this area has received much attention in the past decades which has led to a number of implementation techniques for multiplication. These are surveyed in many textbooks such as [50, 93, 105, 141, 195, 199]. The vast variety of application areas for multipliers exhibits different requirements for speed, area, power consumption and other specifications. Based on these requirements, which are imposed from the system that the multiplier will be operating in, different characteristics of the multiplier will be given different priorities. It is the designers task to choose a suitable multiplication algorithm and implementation method according to these priorities. Traditionally, the design priorities have been given to speed and area. However, the fast evolution of digital systems has caused a major paradigm shift in the past years. Now, other parameters like low-power, flexibility, testability and reliability have entered into the play. Power dissipation has become an important constraint in the design of digital systems. This is even more important for battery-powered applications where the energy budget is extremely limited. Low-power design has become a new area in VLSI technology and power-aware design is inevitable in the new Electronic Design Automation (EDA) tools.

Multipliers are generally computationally heavy circuit parts. Basically a large number of transistors with high transition activities has to be devoted to perform the multiplication. More transistors with high transition activities mean more internal capacitance, more overall switching and consequently more power dissipation. Also the total leakage current is expected to be large in a multiplier because of its large active area. Multipliers are among the main contributors of area and power consumption in a DSP system and, more importantly, they are usually placed in the critical paths of such systems.

Throughout this thesis, a design methodology is proposed for reducing the dynamic and static power dissipation in parallel multipliers. It is assumed that the multiplier will be operating in real-time systems where high-speed is essential. Therefore, among the variety of implementation methods, high-speed parallel implementation methods are addressed. The proposed optimization method in this thesis, which will be elaborated in the following chapters, is an interconnection reordering algorithm based on the input data characteristics. It is applicable directly on all full-adder based parallel multipliers. With some changes the optimization method is applicable for majority of the reduction schemes. The optimization only modifies the interconnects between logic gates and the logic gates and the architecture remains unchanged.

### 1.1 Sources of Power Consumption

The total power dissipation in CMOS circuits results from a combination of dynamic and static sources:

$$P_{Total} = P_{Static} + P_{Dynamic} \tag{1.1}$$

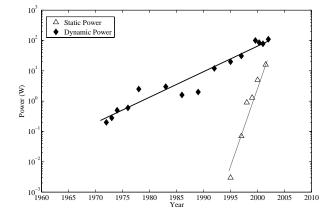

Figure 1.1 shows a scaling scenario throughout past years for both the dynamic and the static power consumption [125]. It can be seen that the problem of static power due to the leakage has emerged in the 1990s. Both fractions of the total power consumption grow exponentially but the leakage power with a much big-ger rate. From the trajectory of the evolutions in dynamic and static power consumption, it can be expected that in future the static power will not be negligible anymore.

#### **1.1.1 Static Power Dissipation**

Ideally, the static power consumption of CMOS gates should equal to zero as the PMOS and NMOS devices are never on simultaneously in steady-state operation. However, the static power consumption in CMOS circuits results from imperfect cut-off of the transistors and causes power dissipation even without any switching activity. The leakage currents are always present, flowing through the reverse

Figure 1.1: Dynamic and static power in Watt for microprocessor chips

biased diode junctions of the transistors located between the source or drain and the substrate. Another important source of leakage current is subthreshold current of the transistors. A CMOS transistor can experience a drain-source current, even when the gate-source voltage is below the threshold voltage. The subthreshold leakage current increases as the threshold voltage becomes smaller.

With an increasing number of transistors both the total capacitance as well as the total channel width which is relevant for leakage currents grows [135]. Thus an exponential growth of the amount of devices, according to Moore's law, directly results in exponentially increased leakage power dissipation. It is worth mentioning that the junction leakage currents are by thermally generated carriers. Therefore, their value increases exponentially with increasing junction temperature.

#### **1.1.2 Dynamic Power Dissipation**

The dynamic power,  $P_{Dynamic}$ , in Eq. 1.1 can be divided into two parts:

$$P_{Dynamic} = P_{Switching} + P_{Short-Circuit}$$

(1.2)

#### **1.1.2.1** Short-Circuit Power Dissipation

$P_{Short-Circuit}$  is due to direct-path short-circuit current which arises when both NMOS and PMOS transistors are simultaneously active, conducting current directly from voltage supply to ground. The short-circuit power dissipation can be

written as:

$$P_{Short-Circuit} = V_{DD}I_{SC} \tag{1.3}$$

where  $V_{DD}$  is the supply voltage and  $I_{SC}$  is the short-circuit current that flows between  $V_{DD}$  and ground during the switching of the gates. The power dissipation due to short circuit currents shows a strong dependency on the supply and threshold voltage [138, 190, 191]. Short circuit power consumption can be kept within bounds by careful design and tuning the switching characteristics (slope engineering) of complementary logic.

#### 1.1.2.2 Switching Power Dissipation

$P_{Switching}$  is due to charging and discharging of the load capacitances in the circuit. Each time the load capacitor at node *i* is charged through a transistor, part of the energy is dissipated in the transistor while the remainder of the energy drawn from power supply is stored on the load capacitance. The amount of dissipated energy per transition is equal to [151]:

Energy per transition

$$= \frac{1}{2}V_{DD}^2C_i$$

(1.4)

where  $V_{DD}$  is the supply voltage and  $C_i$  is the load capacitance at node *i*. Therefore, the average power dissipation at node *i* due to switching will be equal to:

$$P_i^{sw} = \frac{1}{2} V_{DD}^2 D_i C_i \tag{1.5}$$

where  $D_i$  is the transition density at node *i*. The notion of transition density which is the average number of transitions per second is proposed in [130] (DENSIM).  $D_i$  is defined as:

$$D_i = \lim_{T \to \infty} \frac{n_i(T)}{T} \tag{1.6}$$

where  $n_i(T)$  is the number of transitions at node *i* in a time interval of length *T*. Average number of transitions in one clock cycle can be defined as:

$$\overline{n_i} = \frac{D_i}{f_{clk}} \tag{1.7}$$

where  $f_{clk}$  is the clock frequency. The average switching power consumed in a combinational circuit is then given by:

$$P_{total}^{sw} = \sum_{i=1}^{N} P_i^{sw} = \frac{1}{2} V_{DD}^2 \sum_{i=1}^{N} C_i D_i = \frac{1}{2} f_{clk} V_{DD}^2 \sum_{i=1}^{N} C_i \overline{n_i}$$

(1.8)

where N is the total number of nodes,  $C_i$  is the total load capacitance at node i,  $D_i$  is the transition density for node i and  $\overline{n_i}$  is the average number of transitions at node i per clock cycle.

#### **1.1.3** Power Consumption in Multipliers

As will be discussed in Chapter 2, multipliers can in general be implemented as sequential and combinational circuits. In this thesis the focus is on the parallel multipliers which are purely combinational circuits. Therefore, the three sources for power consumption in general circuits (i.e., switching power, short-circuit power and leakage power) are present in parallel multipliers as well.

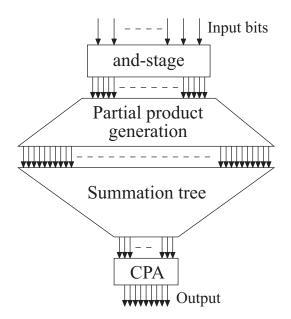

Parallel multipliers are fairly large circuit portions with high transistor density. Large active area directly leads to large leakage power dissipation in parallel multipliers. As will be elaborated in Chapter 2, parallel multipliers have three computation steps: partial product generation, partial product accumulation and vector merge addition. The accumulation of partial products is a computationally heavy task and in general this part of the multiplier dictates the overall computation delay, area and power consumption in the parallel multipliers. A number of techniques, that will be discussed in Chapter 2, has been proposed to move parts of the computation burden from the partial product accumulation step to the partial product generation step. However, even after applying such techniques, the partial product accumulation step is the dominating portion for delay, area, and power. Comprehensive discussions about the power consumption in different multiplier structures are given in [24, 25, 118]

Imbalanced signal paths within the structure of the parallel multipliers lead to high density of spurious transitions. The steady-state transitions, also referred to as functional activities, are the transitions that are necessary to perform the computation task. On the other hand, spurious (hazardous) transitions or glitches dissipate power without producing any useful computations. The ratio of the hazardous component to the total power depends strongly on the logic depth and the signal arrival time balance. In a 32-bit multiplier, the power dissipation due to glitches is about three times higher than that due to functional activities [143].

The glitch pattern is particularly dependent on the gate delays. Indeed, two identical circuits at gate-level with different gate delays may have a totally different glitch pattern and power consumption. Current power estimation techniques often handle both zero delay (no glitch) and real delay models. In the first model, it is assumed that all changes at the circuit inputs propagate through the internal gates of the circuits instantaneously. The latter model assigns each gate in the circuit a finite delay and can thus account for the hazards in the circuit. A realdelay model significantly increases the computational requirements of the power estimation techniques while improving the accuracy of the estimates. In the context of parallel multipliers, taking the glitches into account is extremely important, because glitches consume a considerable amount of power. Consequently, considering gate delays is essential in optimization of parallel multipliers.

### **1.2** Probabilistic Treatment of Multipliers

When the behavior of a digital system becomes so complicated that it cannot be described deterministically, probabilistic treatment of the system is useful to quantify the behavior. In many applications, the input signals to a multiplier can be modeled as discrete time random processes. The discussion here is restricted to a short description of random processes. A more specific definition of random processes is available in probability textbooks such as [7, 122].

A discrete random process X at any specific time n is a random variable, X[n]. The first order distribution function of X[n] is:

$$F_{X[n]}(\mathcal{X};n) = p\{X[n] \le \mathcal{X}\}$$

(1.9)

where  $\mathcal{X}$  is a real number ( $\mathcal{X} \in \mathbb{R}$ ). The corresponding probability density function (PDF) is:

$$f_{X[n]}(\mathcal{X};n) = \frac{\partial F_{X[n]}(\mathcal{X};n)}{\partial \mathcal{X}}$$

(1.10)

The second order distribution function is:

$$F_{X[n_1]X[n_2]}(\mathcal{X}_1, \mathcal{X}_2; n_1, n_2) = p\{X[n_1] \le \mathcal{X}_1, X[n_2] \le \mathcal{X}_2\}$$

(1.11)

Similarly, the second order PDF is:

$$f_{X[n_1]X[n_2]}(\mathcal{X}_1, \mathcal{X}_2; n_1, n_2) = \frac{\partial^2 F_{X[n_1]X[n_2]}(\mathcal{X}_1, \mathcal{X}_2; n_1, n_2)}{\partial \mathcal{X}_1 \partial \mathcal{X}_2}$$

(1.12)

Note that two random variables  $X[n_1]$  and  $X[n_2]$  can be correlated to each other.

Throughout this thesis, the input data words applied to the multiplier are denoted by random processes A and B. Furthermore, it is assumed that A and B are ergodic. Ergodicity is defined for wide sense stationary (WSS) random processes. A random process is WSS if the ensemble average and the autocorrelation

function are invariant to a time shift. The ensemble average of X is:

$$E[X[n]] = \int_{-\infty}^{+\infty} \mathcal{X} f_X(\mathcal{X}; n) d\mathcal{X}$$

(1.13)

The auto correlation is defined as:

$$R_{XX}(n_1, n_2) = E\left[X[n_1]X[n_2]\right] = \iint_{-\infty}^{+\infty} \mathcal{X}_1 \mathcal{X}_2 f_{X_1, X_2}(\mathcal{X}_1, \mathcal{X}_2; n_1, n_2) d\mathcal{X}_1 d\mathcal{X}_2$$

(1.14)

Therefore a process is WSS if E[X[n]] and  $R_{XX}(n, n + \eta)$  are independent of n. E[X[n]] is constant for all values of n, and  $R_{XX}(n, n + \eta)$  can be denoted as  $R_{XX}(\eta)$ .

A WSS random process is ergodic if the time average of any realization of the random process is equal to the ensemble average of the variable. The time average of X is defined as:

$$\overline{X} = \lim_{N \to \infty} \frac{1}{N} \sum_{n=1}^{N} X[n]$$

(1.15)

A WSS random process X is ergodic in mean if  $\overline{X} = E[X]$ . It is ergodic in autocorrelation if

$$R_{XX}(\eta) = \lim_{N \to \infty} \frac{1}{N} \sum_{n=1}^{N} X[n] X[n+\eta]$$

(1.16)

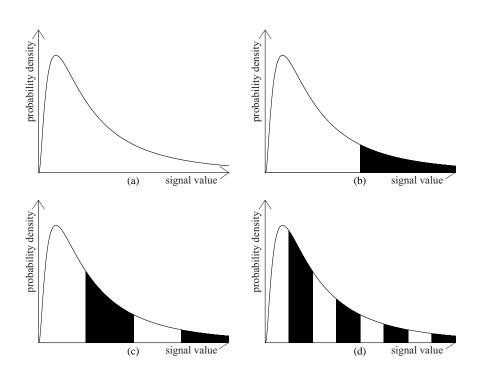

The inputs of  $M \times N$ -bit multiplier, A[n] and B[n], are quantized and represented with M and N bits respectively. The *i*:th and *j*:th input bit in the first and second operands are denoted as  $a_i[n]$  and  $b_j[n]$ , respectively  $(a_{N-1}[n]$  and  $b_{M-1}[n]$  are the most significant bits). The values of A and B must be limited to the maximum and minimum numbers that can be represented using M and N bits, respectively. The one-probabilities (and zero-probabilities) of individual bits in the data words can be computed by integrating the PDFs for the intervals where the bits are 1 (or 0). The one-probability for a bit is referred to as the static probabilities of that bit as well. For example let us assume a real random variable X with values in the interval  $[0, 2^N)$ . X will be uniformly digitized (truncated) using an unsigned N-bit word. Figure 1.2(a) depicts an example distribution function for the real valued random variable X. Figure 1.2(b-d) illustrate the parts of the distribution function where the N:th, (N - 1):th and (N - 2):th bits are one,

respectively. By integrating over these intervals the one-probabilities can be computed. The one-probability for the MSB can be written as:

$$p_{x_{N-1}} = \int_{2^{N-1}}^{2^N} f_{X[n]}(\mathcal{X}; n) d\mathcal{X}$$

(1.17)

The one-probability for *i*:th bit is:

$$p_{x_{i-1}} = \sum_{r=1}^{2^{N-i}} \left( \int_{(2r-1)2^{i-1}}^{r2^i} f_{X[n]}(\mathcal{X}; n) d\mathcal{X} \right)$$

(1.18)

For many applications the distribution of input words are unknown. However, high-level simulations of the system can provide realistic input streams for the multiplier inputs. Let us assume that a realistic input stream with  $N_S$  samples is available for both input operands. Using this input stream the static probabilities of the input bits can be approximated as:

$$p_{x_i} = \lim_{N_S \to +\infty} \frac{1}{N_S} \sum_{n=0}^{N_S - 1} x_i[n]$$

(1.19)

### **1.3** Outline of the Thesis

Chapter 1 has presented a brief introduction to the concepts and importance of low-power design. It has also discussed the sources of power consumption in the multipliers. The probabilistic treatment of multipliers introduced in this chapter will be a key consideration for the subsequent chapters.

Chapter 2 presents the relevant background information about multipliers in the following order:

- Classification of multipliers into sequential, parallel and array multipliers

- The purpose of basic steps in parallel multipliers: partial product generation, partial product accumulation and the final carry propagate adders

- Prevalent methods for designing the partial product generation step, the partial product accumulation step, and the final carry propagate adder in parallel multipliers

- The arithmetic flexibilities in the partial product reduction-tree structure

• The multiplier structure that will be used in the experiments in the subsequent chapters

Chapter 3 presents the power estimation methods used in this thesis. A probabilistic gate-level power estimation technique presented in Section 3.1.1 and a high-level power macro model based estimator presented in Section 3.1.2 will be utilized as dynamic power estimators in the optimization algorithms in Chapters 4 through 8. A leakage power estimator presented in Section 3.2 will be utilized as the static power estimator in Chapter 6.

Chapter 4 presents two optimization algorithms for designing low-power partial product reduction-trees. The first method optimizes the complete reductiontree using the power macro model based estimator presented in Section 3.1.2. The second method designs the reduction-tree progressively using the power estimator presented in Section 3.1.1. Each method is evaluated using a number of experiments.

Chapter 5 extends the progressive partial product reduction tree design algorithm in Chapter 4 to include the potential correlations between the primary inputs. The correlations are classified into two sources: temporal correlation and spatial correlations. Methods for including the temporal and spatial correlations in the power estimator are presented. This is followed by experiments for multipliers with highly correlated inputs.

Chapter 6 introduces a change in the progressive partial product reduction tree design algorithm in Chapter 4 to minimize the static power instead of the dynamic power. The dynamic power estimator is replaced by the static power estimator presented in Chapter 6. Additionally, Chapter 6 presents a method to optimize the reduction-tree for static power and dynamic power simultaneously. In this method a weighted sum of static power and dynamic power will be used in the optimization algorithm as the cost function.

Chapter 7 extends the optimization algorithms, presented in Chapters 4 and 5, on multipliers with variable word-length. Experiments on two scenarios, where the multiplier may operate with variable word-length, are presented in this Chapter.

Chapter 8 presents a different application area for the introduced optimization algorithms in Chapters 4 and 5. While Chapters 4 through 7 focus on the parallel multipliers, Chapter 8 extends the power reduction technique to a special class of elementary function generators. This class of elementary function generators is built using a summation-tree which can be optimized in a similar way as the reduction-trees in the parallel multipliers. Chapter 9 presents the conclusions of this thesis, and recommendations for future work. This is followed by appendices and the bibliography.

### **1.4 Main Contributions**

This thesis has led to several contributions, with the principal ones listed here below:

- Power-optimized partial product reduction tree design algorithm using power estimation based on power macro model and suggestions for limiting the search space

- Power-aware reduction tree design methodology using the progressive reduction tree design algorithm

- Extending the progressive reduction tree design algorithm to include spatiotemporal correlations between primary inputs

- Extending the progressive reduction tree design algorithm to optimize for static power or total power which is a combination of static and dynamic power

- Generalizing the application area to arbitrary multi-operand adder trees and applying the progressive reduction tree design algorithm to elementary function generators build using weighted sum of bit-products

- Probabilistic dynamic power estimation technique for combinational logic circuits using the simple waveform set

The proposed algorithms and the automated VHDL generation describing the optimized reduction trees are implemented in C++ and MATLAB as part of the work behind this thesis.

## Chapter 2

## **Multiplication Schemes**

This chapter briefly reviews a number of widely-used high-speed multiplication techniques, focusing mainly on the parts that will be addressed in the following chapters. More elaborate discussions about the multiplication techniques are given in [45, 50, 93, 105, 141]. Moreover, the discussions of this chapter are only limited to fixed-point multipliers. In fact, the floating-point multipliers consist of a fixed-point multiplier for the significands, plus peripheral and support circuitry to deal with the exponents and special values  $(0,\pm\infty, \text{ etc.})$  [4, 16, 36, 62, 124]. Therefore the optimization methods discussed in the following chapters are also applicable for floating-point operators.

A fixed-point multiplication involves two basic steps: generating partial products (PPs) and accumulating the generated PPs. The diverse multiplication schemes differ in the generation and/or accumulation methods. Consequently, speed-up in the multiplication process is achieved in two ways: generating less number of PPs in the first step or accelerating their accumulation in the second step. The simplest scheme for multiplication, known as shift-and-add scheme, consists of cycles of shifting and adding with hardware or software control loops. Let us use the following notation to illustrate this scheme for an unsigned  $M \times N$ -bit multiplier:

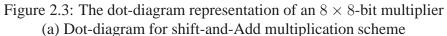

Figure 2.1: Shift-and-Add multiplication scheme

Binary representationMultiplicand $A = \sum_{\substack{i=0\\N-1}}^{M-1} a_i 2^i$  $(a_{M-1}a_{M-2} \dots a_1 a_0)_2$ Multiplier $B = \sum_{\substack{j=0\\N+M-1}}^{N-1} b_j 2^j$  $(b_{N-1}b_{N-2} \dots b_1 b_0)_2$ Product  $(P = A \times B)$  $P = \sum_{\substack{k=0\\k=0}}^{N-1} p_k 2^k$  $(p_{N+M-1}p_{N+M-2} \dots p_1 p_0)_2$

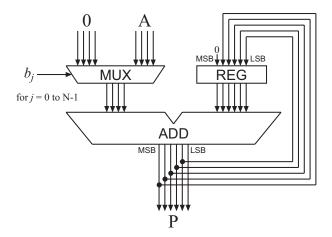

Figure 2.1 illustrates the generation, shifting and summing of partial products for an unsigned  $M \times N$ -bit multiplier and Figure 2.2 shows the block diagram of a shift-and-add multiplier in which the PPs are implemented using a multiplexer. The PPs can also be implemented using logical AND gates. The multiplication is performed in N cycles of shifting and adding. The product is given in Eq. 2.1.

$$P = \sum_{k=0}^{N+M-1} p_k 2^k = \left(\sum_{i=0}^{M-1} a_i 2^i\right) \left(\sum_{j=0}^{N-1} b_j 2^j\right) = \sum_{i=0}^{M-1} \sum_{j=0}^{N-1} a_i b_j 2^{i+j}$$

(2.1)

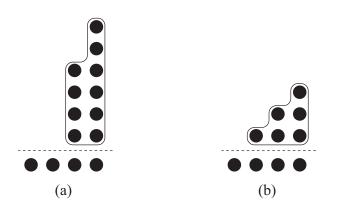

The PPs are more conveniently illustrated using a dot-diagram. A dot-diagram is useful when only the positioning and alignment of bits, rather than their values, are important. Figure 2.3(a) illustrates the PPs for an unsigned  $8 \times 8$ -bit multiplier. Figure 2.3(b) is an alternative dot-diagram representation for the same multiplier. Each dot in the diagram is representing a single bit which can be a zero or one. In the dot-diagram representation, only the horizontal position of the PPs has significance. By relaxing the vertical positions of PPs, the dot-diagram can be altered as shown in Figure 2.3(b).

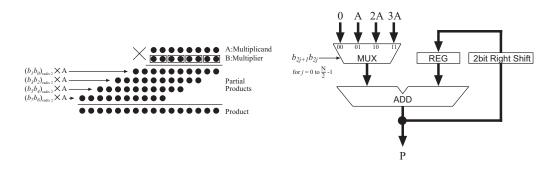

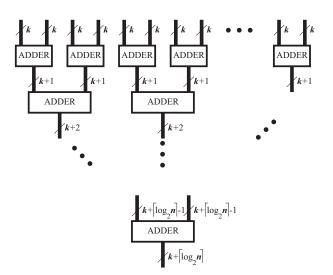

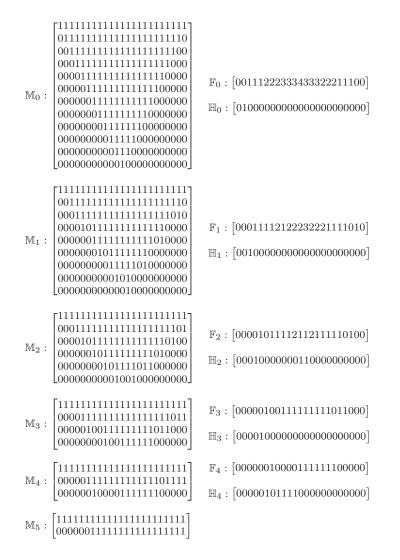

The partial product matrix (PPM) is another representation tool for PPs. The PPM is a boolean matrix that represents a PP with the weight j by placing a 1 or TRUE in column j. The elements in the PPM that do not correspond to a PP are

Figure 2.2: Block diagram for a shift-and-add multiplier

- (b) An alternative dot-diagram representation

- (c) The corresponding partial product matrix

represented with a 0 or FALSE. Therefore, the PPM is equivalent to dot-diagram representation of the PPs. Note that the size of the PPM can be arbitrary large as long as it contains all PPs. However, conventionally, the minimum size PPM that contains all PPs is chosen; i.e. both the first column and the last column in the PPM must include a PP (a TRUE value). The PPs are normally accumulated through several stages, resulting in a number of intermediate PPMs. Throughout this thesis the initial PPM is denoted as  $M_0$  and contains all initial PPs in the column corresponding to their weight.  $M_i$  denotes the partial product matrix after *i*th stage of reduction. The operator  $||M_i||$  is also defined so that it returns the maximum height of the partial product matrix; i.e., the largest number of PPs with equal weight for  $M_i$ .

### 2.1 Classification of Multipliers

Multiplication schemes are commonly classified in three general types: sequential, parallel and array multipliers [93, 106, 195]. This is not a universal classification and some hybrid multiplication schemes do not fall into exactly one of these categories. For example, as a compromise between sequential and parallel multipliers, partially combinational multipliers are introduced to achieve higher performance but still keep the hardware small. Examples of such multipliers are described in [4, 63, 107, 162]

#### 2.1.1 Sequential Multipliers

The sequential multipliers generate the PPs sequentially and add each newly generated PP to the previously accumulated sum. The sequential multipliers were popular when the hardware was expensive and bulky. They are still in use in applications where the speed is not critical or the high parallelism achieved by multiple operating sequential multipliers compensates for the low speed. Shift-and-Add multiplication is an example of sequential multipliers.

#### 2.1.2 Parallel Multipliers

The parallel multipliers generate all PPs in parallel and then use fast multi-operand adders for their accumulation. Parallel multipliers are the main focus of this thesis; Therefore the structure of parallel multipliers will be discussed more elaborately in Section 2.2.

#### 2.1.3 Array Multipliers

Array multipliers iteratively utilize (almost) identical cells that generate new PPs and accumulate them simultaneously and therefore there is no separate circuit for PP generation and for their accumulation. In this way, the overhead that is due to the separate controls of these two steps is avoided. Examples of array multipliers are presented in [33,49,109,110,137].

### 2.2 Parallel Multipliers

Today parallel multipliers are popular because of the need for high speed operators. In addition to the high-speed requirement, more area is available nowadays, compared to the past. As mentioned earlier, the speed enhancement in multipliers are achieved in two ways: reducing the number of generated PPs and using faster techniques to accumulate the PPs. In order to investigate the speed enhancement methods in multipliers, the partial product generation (PPG) and partial product accumulation methods must be investigated.

#### 2.2.1 Partial Product Generation

The PPs are generated using multiplexers or AND gates in an unsigned radix-2 shift-and-add multiplication. For multiplication of signed-magnitude numbers, the unsigned multiplication core can be used for the magnitude part of the inputs, with an extension that the sign bit is computed separately by checking the two input operands' sign bits. Multiplication of signed values with complement representation is a bit more complex. One way is to complement the negative operands, multiply the unsigned values and then complement the result if necessary; i.e. when only one of the input operands are negative. Such a pre-complement and post-complement method is suitable for 1's complement numbers but is too complicated for 2's complement numbers. For a 2's complement multiplier to yield correct product of its inputs, sign extension is needed on PPs. The PPs must be sign-extended to the width of the final product. Robertson in [158] suggests a more efficient procedure for 2's complement numbers compared to pre- and postcomplement approach. Roberston classifies the multiplication in 2 cases. Case 1 is when the multiplier is positive. In this case the original shift-and-add approach (with right-shifts) can be utilized with only one consideration that the right-shifts are arithmetic shifts rather than logic shifts; i.e. when the multiplicand is negative, 1 will be entered in MSB instead of 0. Case 2 is when the multiplier is negative. In this case a correction step is required in the last step of shift-and-add multiplication. That is, the multiplicand will be subtracted instead of being added.

For 2's complement multiplication a number of direct methods are developed [6, 15, 70, 145]. Let us consider the following 2's complement representation for the multiplicand, the multiplier and the product:

$$\begin{split} \text{Multiplicand} \qquad & A = -2^{^{M-1}}a_{^{M-1}} + \sum_{i=0}^{M-2} 2^{^{i}}a_{^{i}} \\ \text{Multiplier} \qquad & B = -2^{^{N-1}}b_{^{N-1}} + \sum_{j=0}^{N-2} 2^{^{j}}b_{^{j}} \\ \text{Product} (A \times B) \quad & P = -2^{^{N+M-1}}p_{^{N+M-1}} + \sum_{k=0}^{N+M-2} 2^{^{k}}p_{^{k}} \end{split}$$

Therefore, the product will be computed as:

$$P = \left(-2^{M-1}a_{M-1} + \sum_{i=0}^{M-2} 2^{i}a_{i}\right) \times \left(-2^{N-1}b_{N-1} + \sum_{j=0}^{N-2} 2^{j}b_{j}\right)$$

$$= \sum_{i=0}^{M-2} \sum_{j=0}^{N-2} a_{i}b_{j}2^{i+j} + a_{M-1}b_{N-1}2^{N+M-1}$$

$$-\left(\sum_{j=0}^{N-2} a_{M-1}b_{j}2^{j+M-1} + \sum_{i=0}^{M-2} a_{i}b_{N-1}2^{i+N-1}\right)$$

(2.2)

Figure 2.4(a) depicts the product computation for 2's complement numbers. In order to avoid the complication that subtraction or sign extension will introduce in most applications, Baugh and Wooley in [6] proposed an efficient method for 2's complement multiplication that handles subtractions by taking the 2's complement of the terms to be subtracted. In 2's complement representation negation of an integer word X can be obtained by the formula -X = comp(X) + 1; where comp(X) is bitwise inversion of the bits in word X. Figure 2.4(b) illustrates the PPM formation using Baugh-Wooley's method. Baugh-Wooley's strategy increases the maximum column height by 2 and this can potentially increase the accumulation delay. Hatamian and Cash in [70] modified Baugh-Wooley multiplier and reduced the maximum number of PPs to its previous value as in the unsigned multiplier. Figure 2.4(c) illustrates the modified 2's complement multiplier.

|                 |                   |                       |                                             |                     | $a_4$                   | $a_3$                | $a_2$                | $a_1$                | $a_0$                |

|-----------------|-------------------|-----------------------|---------------------------------------------|---------------------|-------------------------|----------------------|----------------------|----------------------|----------------------|

|                 |                   |                       | ×                                           |                     | $b_4$<br>$-a_4b_0$      | b <sub>3</sub>       | $\frac{b_2}{a_2b_0}$ | $\frac{b_1}{a_1b_0}$ | $\frac{b_0}{a_0b_0}$ |

|                 |                   |                       |                                             | $-a_4b_1$           | $-a_4 b_0$<br>$a_3 b_1$ | $a_3b_0$<br>$a_2b_1$ |                      |                      | $u_0 v_0$            |

|                 |                   |                       | $-a_4b_2$                                   |                     | $a_{2}b_{2}$            |                      |                      |                      |                      |

|                 |                   | $-a_{4}b_{3}$         | $a_3b_3$                                    | $a_2b_3$            | $a_1b_3$                | $a_0b_3$             |                      |                      |                      |

|                 | $a_4b_4$          | $\frac{-a_3b_4}{p_7}$ | $-a_{2}b_{4}$                               | $-a_{1}b_{4}$       | $-a_0b_4$               |                      |                      |                      |                      |

| $p_9$           | $p_8$             | $p_7$                 | $p_6$                                       | $p_5$               | $p_4$                   | $p_3$                | $p_2$                | $p_1$                | $p_0$                |

|                 |                   |                       |                                             | (a                  | .)                      |                      |                      |                      |                      |

|                 |                   |                       |                                             |                     | $a_4$                   | $a_3$                | $a_2$                | $a_1$                | $a_0$                |

|                 |                   |                       | ×                                           |                     | $b_4$                   | $b_3$                | $b_2$                | $b_1$                | $b_0$                |

|                 |                   |                       |                                             |                     | $a_4\overline{b_0}$     | $a_3b_0$             | $a_2b_0$             | $a_1b_0$             | $a_0b_0$             |

|                 |                   |                       |                                             | $a_4\overline{b_1}$ | $a_3b_1$                | $a_2b_1$             | $a_1b_1$             | $a_0b_1$             |                      |

|                 |                   |                       | $a_4\overline{b_2}$                         | $a_3b_2$            | $a_2b_2$                | $a_1b_2$             | $a_0b_2$             |                      |                      |

|                 |                   | $a_4\overline{b_3}$   | $a_3b_3$                                    | $a_2b_3$            | $a_1b_3$                | $a_0b_3$             |                      |                      |                      |

|                 | $a_4b_4$          | $a_3\overline{b_4}$   | $a_2\overline{b_4}$                         | $a_1\overline{b_4}$ | $a_0b_4$                |                      |                      |                      |                      |

|                 | $\overline{a_4}$  |                       |                                             |                     | $a_4$                   |                      |                      |                      |                      |

| 1               | $\overline{b_4}$  |                       |                                             |                     | $b_4$                   |                      |                      |                      |                      |

| $p_9$           | $p_8$             | $p_7$                 | $p_6$                                       | $p_5$               | $p_4$                   | $p_3$                | $p_2$                | $p_1$                | $p_0$                |

|                 |                   |                       |                                             | (b                  | )                       |                      |                      |                      |                      |

|                 |                   |                       |                                             |                     | $a_4$                   | $a_3$                | $a_2$                | $a_1$                | $a_0$                |

|                 |                   |                       | ×                                           |                     | $b_4$                   | $b_3$                | $b_2$                | $b_1$                | $b_0$                |

|                 |                   |                       |                                             | 1                   | $a_4b_0$                | $a_3b_0$             | $a_2b_0$             | $a_1b_0$             | $a_0b_0$             |

|                 |                   |                       |                                             | $a_4b_1$            | $a_3b_1$                | $a_2b_1$             | $a_1b_1$             | $a_0b_1$             |                      |

|                 |                   |                       | $a_4b_2$                                    |                     | $a_2b_2$                |                      |                      |                      |                      |

|                 |                   | $\overline{a_4b_3}$   | $a_3b_3$                                    | $a_2b_3$            | $a_1b_3$                | $a_0b_3$             |                      |                      |                      |

|                 |                   |                       |                                             | $\overline{a_1b_4}$ |                         |                      |                      |                      |                      |

| 1               | $a_4b_4$          | $u_{3}v_{4}$          | <i>a</i> <sub>2</sub> <i>o</i> <sub>4</sub> |                     |                         |                      |                      |                      |                      |

| $\frac{1}{p_9}$ | $a_4b_4$<br>$p_8$ | $p_7$                 | $p_6$                                       |                     |                         | $p_3$                | $p_2$                | $p_1$                | $p_0$                |

Figure 2.4: Signed multiplication (a) 2's complement multiplication with positive and negative partial products. (b) Baugh-Wooley multiplier 2's complement multiplier

(c) Modified Baugh-Wooley 2's complement multiplier

Figure 2.5:  $8 \times 8$ -bit Radix-4 multiplication in dot-diagram and its structure

In addition to the Baugh-Wooley and modified Baugh-Wooley multiplication methods, an alternative method to handle 2's complement multiplication is proposed by Pezaris in [145]. Pezaris's method employs different types of full-adders depending on whether they have positive or negative weight.

### 2.2.1.1 Higher Radix Multipliers

Reduction in the number of generated partial products is favorable because it reduces the complexity of the following accumulation steps; thus it decreases the execution and amount of hardware involved. One way to reduce the number of PPs is to examine two or more bits of the multiplier at a time. Although higher representation radix leads to fewer digits, it requires generation of multiples of the multiplicand. For example in radix-4 multiplication each digit can assume the values 0, 1, 2 or 3; therefore 0, A, 2A and 3A are needed, where A is the multiplicand. In fact a part of the complexity is moved from the PP accumulation step to the PP generation step. This method is efficient specially when these multiples of the multiplicand can be precomputed [141, Chapter 10].

As illustrated in Figure 2.5, the number of partial products are reduced by a factor 2 for radix-4 multiplication. The multiples A and 2A are easy to obtain (2A is simply the shifted version of A), but 3A is a hard multiple and requires an addition operation (3A = 2A + A). This addition can be combined with the addition required with each shift-and-add step. Doing so there will be a need for a 3-operand adder. As will be discussed later in Section 2.2.2.1, carry-save adders can be used to reduce the number of operands from three to two. The time required to perform this computation is approximately equal to the delay of one full-adder cell (i.e. 2 XOR gates) regardless of the number of bits in the operands.

| Current input bit | Previous input bit | Recoded bit | Explanation               |

|-------------------|--------------------|-------------|---------------------------|

| $b_j$             | $b_{j-1}$          | $b'_j$      |                           |

| 0                 | 0                  | 0           | Consecutive zeros         |

| 0                 | 1                  | 1           | End of a string of ones   |

| 1                 | 0                  | 1           | Start of a string of ones |

| 1                 | 1                  | 0           | Consecutive ones          |

Table 2.1: Booth's recoding algorithm

## 2.2.1.2 Recoding Techniques

Various algorithms for reducing the number of generated partial products have been proposed. Many of these algorithms benefit from the fact that a group of consecutive zeros or ones may generate fewer PPs. A group of i consecutive ones (or zeros) can be represented by the difference between two bit sequences each having a single nonzero bit. The string property is the base for such algorithms:

$$2^{j+i-1} + 2^{j+i-2} + \ldots + 2^{j+1} + 2^j = 2^{j+i} - 2^j$$

(2.3)

The longer the sequence of ones or zeros, the larger is the achieved saving. In order to benefit from this transformation, the binary number representation needs to be changed from the conventional representation in digit set  $\{0,1\}$  to the signed-digit representation in digit set  $\{-1,0,1\}$  [5]. The process of converting the representation digit set to another digit set is referred as recoding in the literature.