# Distributed Generation – Power Electronic Converters, Communication and Control

Erik Stjernholm Hoff

Norwegian University of Science and Technology Faculty of Information Technology, Mathematics and Electrical Engineering

Department of Electric Power Engineering

April - 2007

# Printed version: ISBN 978-82-471-1951-8 Electronic version: ISBN 978-82-471-1965-5 2007:89

# Abstract

This thesis tries to explain the changes in the control of power electronic converters that are possible by the use of communication. Many of the renewable energy sources such as photovoltaic panels are geographically dispersed. The power rating per generator is therefore typically low. If this kind of energy source should dominate an electrical grid, the number of generators must be high. There should also be means of controlling this large number of generators simultaneously and safely. The cost of safe communication may be too high compared to the power contribution of a single generator. The Internet offers a low-cost solution, but it cannot guarantee real-time properties. Similarly to the Internet itself, it is shown how communication errors can be detected and handled in a safe manner by the end-system, in this case the generator. The generator can detect a communication timeout, and change control algorithms in order to guard itself and the connected electricity grid. When necessary, it can also disconnect and work as a local standalone power supply. In order to be able to supply all kinds of loads, the generator (in this case an inverter) is primarily voltage controlled. This results in challenges concerning current distortion. The use of feed-forward for cancellation of common grid voltage harmonics is discussed, simulated and measured. An anti-islanding algorithm for voltage controlled inverters is also developed, simulated and measured in this thesis. A DC/DC-converter for optimized connection of a photovoltaic panel is built, exploiting the photovoltaic panel properties to reduce the size and the losses significantly. Although most contributions are connected to details and parts of the system, the interactions between communication and control are emphasized.

# Acknowledgements

I think my parents can agree that already from childhood I was busy testing out what I have learned in practice. Both chemistry and electronics were interesting fields. By giving me an electronics set instead of a chemistry set, I guess they hoped to avoid explosions of any kind. Usually I was making less harmful projects, like finding out how to power toy cars by using photovoltaic panels.

It was in the lectures of Professor Roy Nilsen at NTNU that I was first introduced to power electronics and drives. This opened up a new world to me, and I understood that I just had to learn about the programming of microcontrollers and digital signal processors. The four years I have spent on this PhD have been very interesting and educational. I would like to thank Professor Tore Undeland, NTNU for informing me about this PhD scholarship and for being my supervisor the first months. Thanks to Professor Lars Norum, NTNU for being my main supervisor and for helpful support after I was accepted as a PhD student. Help from other PhD students is not only motivating but also important. I will therefore like to thank William Gullviks company ActiveDSP for sharing the DSPcomm program with fellow PhD students free of charge, and for giving a starting point DSP code. Special thanks go to Tore Skjellnes, Pål Andreassen and Guiseppe Guidi for long and helpful discussions. I am very grateful for the comments and corrections given by post.doc. Marta Molinas and Professor Tore Undeland.

Thanks to the Research Council of Norway (NFR) and Power-One for funding this KMB (competence project with user cooperation) project under grant number 146524/210. Last but not least thanks to my wife Carina for listening, helpful discussions, proofreading and helping me to be able to finish this work on time. My daughter, Ellen, has also been an inspiration and made it both necessary and easier to see my work in a larger perspective.

# Table of contents

| 1                             | Introduct                 | Introduction                                     |     |  |

|-------------------------------|---------------------------|--------------------------------------------------|-----|--|

|                               | 1.1 Con                   | tributions                                       | 4   |  |

|                               | 1.2 Outline of the thesis |                                                  |     |  |

| 2 Detailed system description |                           |                                                  | . 7 |  |

|                               |                           | rgy optimization                                 |     |  |

|                               | 2.2 Grid                  | l connection and associated control algorithms   | . 8 |  |

|                               | 2.2.1                     | UPS control algorithm                            | 11  |  |

|                               | 2.2.2                     | Anti-islanding control algorithm                 | 13  |  |

|                               | 2.2.3                     | Voltage support control algorithm                | 14  |  |

|                               | 2.3 Ener                  | rgy management system                            | 14  |  |

|                               | 2.3.1                     | Internet protocol                                | 15  |  |

|                               | 2.3.2                     | Communication scalability                        | 17  |  |

|                               | 2.3.3                     | Monitoring                                       |     |  |

|                               | 2.4 Ove                   | rall control for safe operation                  | 19  |  |

| 3                             | 0,                        | ource modeling and control                       |     |  |

|                               | 3.1 Phot                  | tovoltaic cells                                  |     |  |

|                               | 3.1.1                     | The photovoltaic panel                           | 25  |  |

|                               | 3.2 PV                    | panel voltage control                            | 28  |  |

|                               | 3.2.1                     | Converter efficiency                             |     |  |

|                               | 3.2.2                     | MPPT                                             | 28  |  |

|                               | 3.2.3                     | PV panel power reduction                         | 30  |  |

|                               | 3.2.4                     | Series-connected boost converter                 |     |  |

|                               | 3.2.5                     | Series-connected bidirectional flyback converter |     |  |

|                               |                           | DC-converter discussion                          |     |  |

| 4                             | Inverter r                | nodeling and simulation                          | 41  |  |

|                               | 4.1 Inve                  | erter                                            | 41  |  |

|                               | 4.1.1                     | LCL-filter                                       |     |  |

|                               | 4.1.2                     | Transient faults < 30 ms                         |     |  |

|                               | 4.1.3                     | Integrating isolation circuit                    | 44  |  |

|                               | 4.1.4                     | 3-phase transformations                          | 47  |  |

|                               | 4.2 LCI                   | <i>J</i> -filter and grid voltage model          |     |  |

|                               | 4.2.1                     | Single phase LCL-filter and grid model           |     |  |

|                               | 4.2.2                     | Three phase LCL filter model                     |     |  |

|                               | 4.2.3                     | Three phase grid including 5th and 7th harmonic  |     |  |

|                               | 4.2.4                     | Observability                                    |     |  |

|                               | 4.2.5                     | Discretization of the observer                   |     |  |

|                               | 4.2.6                     | Observer pole assignment                         | 67  |  |

|                               | 4.2.7                     | Frequency adaptive observer                      |     |  |

|                               |                           | ulations                                         |     |  |

|                               | 4.3.1                     | Grid 1st harmonic estimation                     |     |  |

|                               | 4.3.2                     | Grid 5th and 7th harmonics estimation            |     |  |

|                               | 4.4 Mea                   | isurements                                       | 74  |  |

| 5   | Inverter control                                   | 77  |  |  |  |

|-----|----------------------------------------------------|-----|--|--|--|

| 5   | .1 State feedback for LCL-filter resonance damping |     |  |  |  |

| 5   | .2 Feed-forward for voltage harmonics cancellation |     |  |  |  |

|     | 5.2.1 Compensation by inverse transfer function    | 86  |  |  |  |

|     | 5.2.2 Simulations without state feedback           |     |  |  |  |

|     | 5.2.3 Compensation by choice of eigenvectors       | 91  |  |  |  |

|     | 5.2.4 Simulations with state feedback              |     |  |  |  |

| 5   | .3 Inverter power control                          | 93  |  |  |  |

|     | 5.3.1 Voltage support algorithm                    | 97  |  |  |  |

|     | 5.3.2 Anti-islanding algorithms                    | 99  |  |  |  |

| 5   | .4 DC/DC-converter controller 1                    | 101 |  |  |  |

| 6   | Software 1                                         |     |  |  |  |

| 6   | .1 Software framework for controllers 1            | 106 |  |  |  |

| 6   | .2 DC/DC-converter controller 1                    | 108 |  |  |  |

|     | 6.2.1 DC/DC-converter safe control algorithms 1    | 109 |  |  |  |

| 6   | .3 Inverter controller 1                           |     |  |  |  |

|     | 6.3.1 Inverter safe control algorithms             | 113 |  |  |  |

| 6   | .4 Local communication bus 1                       | 117 |  |  |  |

| 6   | .5 DG gateway software 1                           | 118 |  |  |  |

|     | 6.5.1 DG gateway 1                                 |     |  |  |  |

|     | 6.5.2 Grid management software 1                   |     |  |  |  |

| 6   | .6 Communication discussion 1                      |     |  |  |  |

|     | 6.6.1 CANbus communication 1                       |     |  |  |  |

|     | 6.6.2 UDP communication                            | 125 |  |  |  |

|     | 6.6.3 Error tolerance                              |     |  |  |  |

| 7   | System simulations and measurements 1              |     |  |  |  |

| 7   | .1 Grid connection testbench 1                     |     |  |  |  |

|     | .2 Voltage support algorithm tests 1               |     |  |  |  |

|     | .3 Anti-islanding control algorithm tests 1        |     |  |  |  |

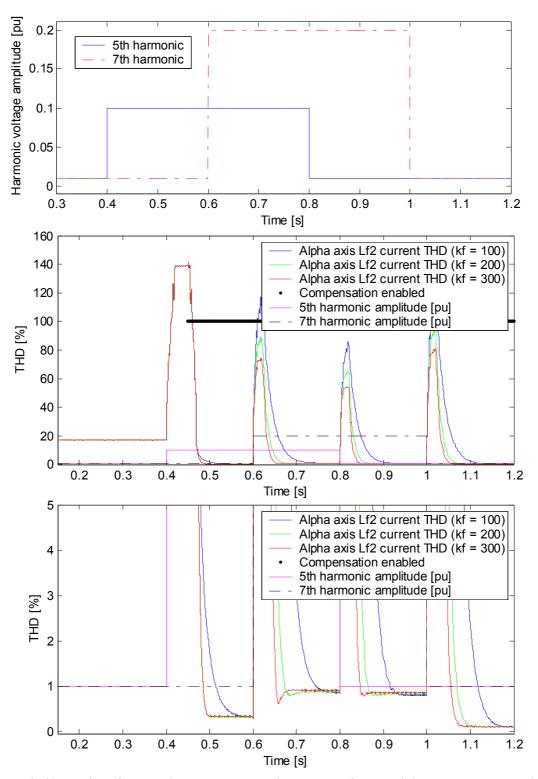

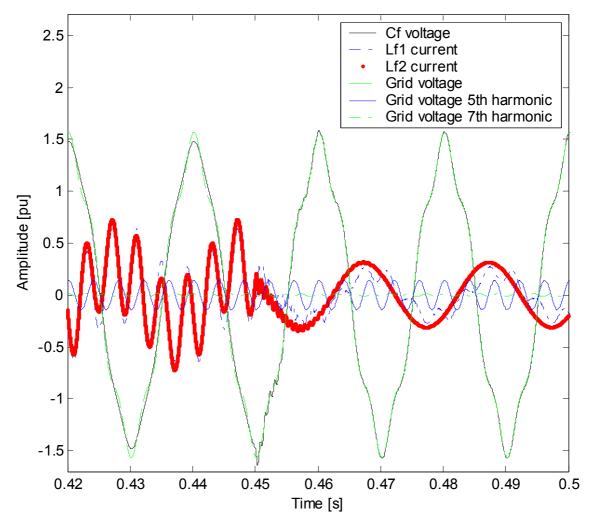

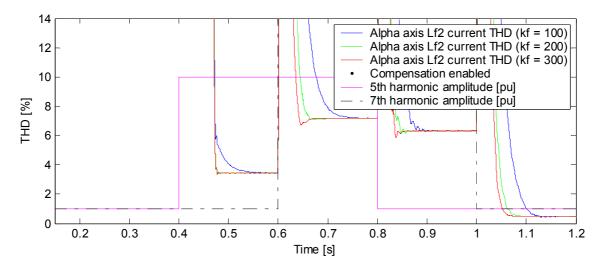

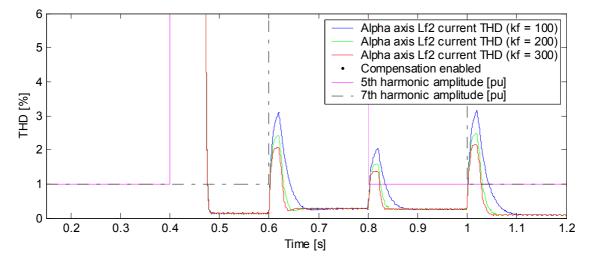

|     | .4 Feed-forward for current THD reduction 1        |     |  |  |  |

|     | .5 Transients during control algorithm changes 1   |     |  |  |  |

| 8   | Discussion of simulations and experiments 1        |     |  |  |  |

| 8   | .1 Inverter voltage control discussion             |     |  |  |  |

|     | 8.1.1 Measurement noise                            |     |  |  |  |

|     | 8.1.2 State-space observer and state feedback      |     |  |  |  |

| 8   | .2 Inverter power control discussion               |     |  |  |  |

|     | 8.2.1 Anti-islanding algorithm                     |     |  |  |  |

|     | 8.2.2 Testbench                                    |     |  |  |  |

|     | 8.2.3 Voltage support algorithm                    |     |  |  |  |

| 9   | Conclusion 1                                       |     |  |  |  |

| 10  | Further work                                       |     |  |  |  |

|     | erences 1                                          |     |  |  |  |

| App | Appendices 169                                     |     |  |  |  |

vi

# **1** Introduction

Fossil-fueled thermal electric power plants emit large amounts of CO<sub>2</sub> that affect the climate. One possible solution to reduce CO<sub>2</sub>-emissions is substituting fossil fueled plants with renewable energy such as biomass, solar, wind and/or hydropower. Such renewable energy sources are geographically dispersed, and therefore do not have an economy of scale compared to thermal plants. For example, photovoltaic panels can be used as a building cladding, where they do not occupy valuable land area. The surface of one building is however limited, and thus the power of one such generator is small. In addition, often such a generator is close to the consumer. It is thus possible to reduce the capacity of the transmission lines because there is less electricity to transport. The owner of such a generator is often also a power consumer. The owner then avoids any kWh-taxation of the electricity that is internally produced and consumed. Private ownership may therefore encourage demand-side management. For some consumers improving the security of supply is more important than the kWh-cost. Locally owned generators may give a positive contribution in this respect, assuming suitable control is applied. Locally owned generators also encourage generators with little local environmental impact.

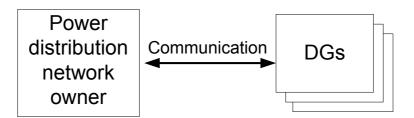

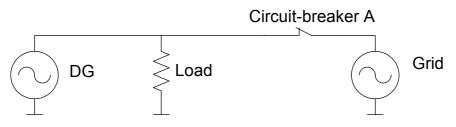

Distributed Generation (DG) can be defined as an electric power source connected directly to the distribution network or even on the customer side of the meter [1, 2]. These are often small-scale renewable energy sources, such as photovoltaic panels, biomass or wind turbines. The localization of the DGs can be used beneficially for both the consumer and the producer. Communication and power electronics are the enabling technologies that are necessary to realize many of the possible benefits of DG [3]. A possible communication setup is shown in Figure 1.

Figure 1: Communication for controlling a large number of Distributed Generation units (DGs).

The network owner and the customer must have a mutual agreement concerning the grid connection [4]. Both parties can be energy producers and energy consumers, depending on the local energy available. Internet communication offers the network owner a low-cost solution to control the local energy production in a way that is beneficial to both parties.

Optimization of the energy production is one of the purposes of information exchange in power systems. It gives the DG owner the possibility to produce energy in the most optimal way. One example is the electricity cost, which varies with time. When using biomass-fired DG only during periods with high energy cost, a DG owner can increase profit margins with regard to fuel cost. The network owner can also use the DGs for peak shaving. Grid reinforcements may be avoided if local energy sources are installed, and if there are communication systems for power management and control.

The internal system of a DG must be designed to meet new requirements introduced by the use of communication. The internal functions range from energy source optimization, to energy storage control, as well as the grid connection. Local energy sources can be divided in dispatchable sources (such as biomass and pump-storage hydropower) and non-dispatchable sources (such as photovoltaic panels and wind power). The latter should be run at full power whenever possible because the fuel cost is zero.

The existing grid requirements prevent the DGs from providing power locally during grid failures. If the grid requirements were modified, the main grid could be separated into smaller islands of active local grids to protect against failures [5]. These could then supply the local grid, and give customers a more reliable power supply compared to the alternative of no local energy sources. The small islands of possibly isolated grids must, however, be able to balance production and consumption of power. This is best done by having some dispatchable energy sources or energy storage. These can then guarantee an adequate amount of power when needed.

An important feature of a power supply system is fault tolerance. Possible fault situations in addition to grid failures are communication failures, which should also be handled in a controlled way. This requires the connected converters functioning safely without communication. Optimization may be lost, but neither people nor machines should be harmed. The DG should also tolerate grid failures and thus avoid interrupting the power supply of the nearest critical load.

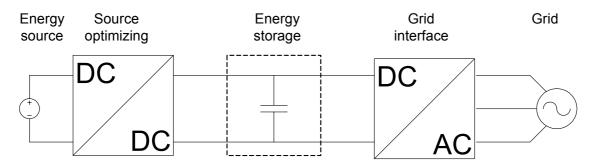

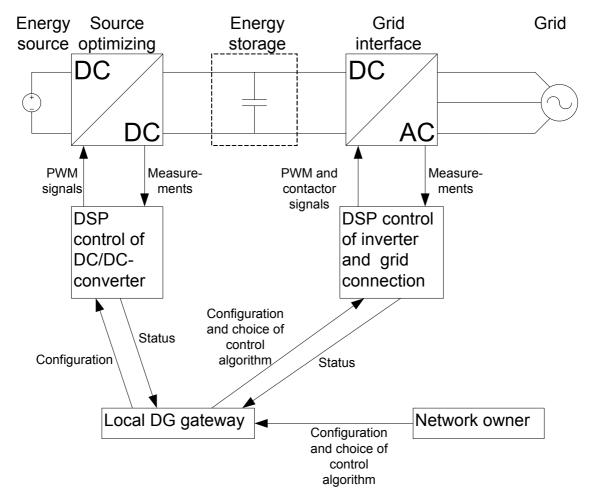

The primary energy source can be optimized using digital control. Photovoltaic panels are controlled using Maximum Power Point Tracking (MPPT). Similar methods can be applied for optimizing the speed of wind turbines and even small hydropower turbines. When combined with high efficiency converters, the energy output can be improved. Co-design of the control and the DC/DC-converter hardware may improve the overall efficiency and reduce its size. A schematic representation of the converters in a typical DG with power electronic converters is shown in Figure 2.

2

Figure 2: A DG including two power electronic converters with energy storage in between.

A system for grid connection of small-scale renewable energy sources must meet certain requirements from the customer and the network owner. The customer wants an efficient and reliable system at low cost. The network owner has requirements regarding harmonic pollution of the grid, as well as safety measures for equipment and personnel. Requirements vary according to the location of the DGs, even within Norway [4]. The network owner may put too strict grid connection requirements on the local DG owner. A network owner may then effectively block DGs.

The possibility to remotely control various DGs is an improvement. Control of any number of DGs can be achieved using communication. There are various communication possibilities, but using an existing infrastructure supporting point-to-point communication is beneficial. The specific cost of communication per kWh electricity produced must be kept low. This excludes any custom-made infrastructure which may be used in larger generating facilities. The Internet offers possibilities for relatively simple integration of different services into an energy management system. The point-to-point communication offers possibilities of distributed systems. This can share out the processing and communication load within the system, and therefore not overload the network owner. Second, the integration with other information systems, such as the electricity cost, enables more economic electricity production. Failure and status information can be given through a number of channels, ranging from email to real-time protocols.

Reliability is a major concern for an increasing number of customers. Uninterruptible Power Supplies (UPS) are commonly used to avoid undesirable power outages in businesses ranging from hospitals to small offices. Smaller companies relying on computers typically have an UPS to avoid down-time due to grid power outages. A DG can meet the power deficiency of local loads in case of grid failure. This requires, however, voltage control and a means of isolating the critical loads from the grid.

# 1.1 Contributions

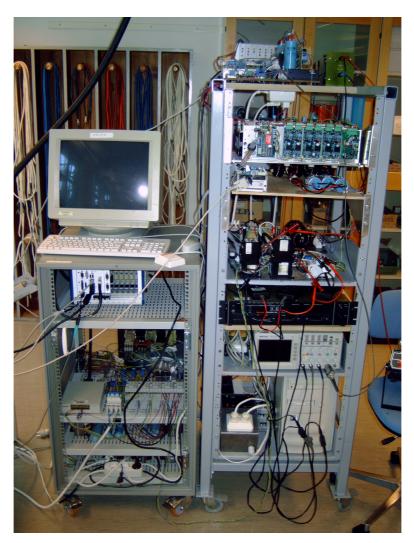

A DG system using control based on Internet communication, digital controllers and a new DC/DC-converter for photovoltaic panels is presented. All these three system components interact, thus it is undesirable to design the parts independently. A laboratory setup has been built, in order to investigate design issues and to test the performance of the system.

An Internet communication system for DG is presented, which has not yet been applied for island detection for DG. The communication may fail, and safe control algorithms make the system soft real-time. If real-time communication errors do not lead to dangerous situations, a system can be called soft real-time.

The soft real-time control can give grid-connected DGs new possibilities to support the local voltage. This can be considered the opposite of the anti-islanding algorithms applied to most of today's DGs. Three different control algorithms, all based on a voltage-controlled AC/DC-converter (inverter), are demonstrated. Basing all these control algorithms on voltage control, the transition between connection states can be done smoothly without interrupting the power to a local critical load. Feed-forward for decoupling of common grid voltage harmonics is tested. An anti-islanding algorithm for a voltage controlled inverter is presented. Such anti-islanding control has not been published by others.

Photovoltaic (PV) panel connected DC/DC-converters is discussed. A known concept is applied to a flyback converter. The concept is to limit the DC/DC-converter voltage control range [6-8]. The DC/DC-converter is then only capable of converting the expected voltage variations during normal operation. It is typically <sup>1</sup>/<sub>4</sub> of the nominal voltage. Given suitable topology, the transistors can switch only a fraction of the voltage or the current from the PV panel. This can give a significant reduction of the size and the losses of the DC/DC-converter, compared to a standard DC/DC-converter. The flyback converter differs from previously published work by being bi-directional, meaning it can step the PV panel voltage both up and down.

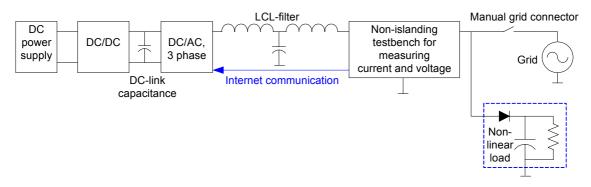

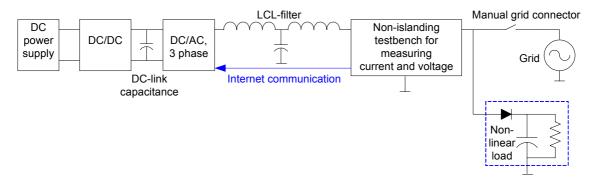

A DG system has been implemented in the laboratory. It consists of a controllable DC source representing a PV panel. This feeds energy to a DC/DC-converter. The energy is fed to the DC-link capacitance of a 3-phase inverter, acting as the energy storage. The inverter is connected to the load and/or the electricity grid through an LCL-filter and an electromechanical contactor. A testbench has been developed for testing of islanding detection time and harmonics.

# **1.2** Outline of the thesis

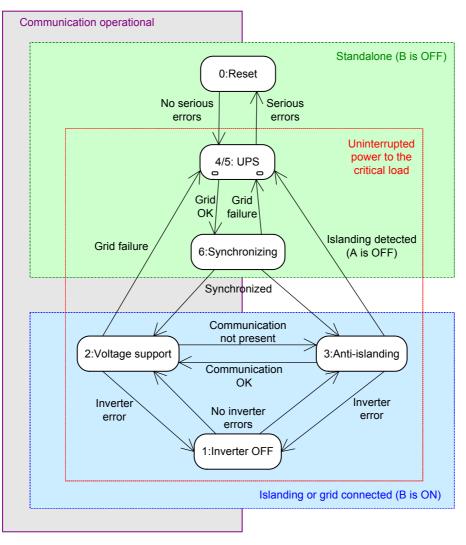

Chapter 2 describes the requirements of a grid-connected DG with communication. A laboratory setup is presented, which shows how such a system may look in the future. Use of communication may lead to changes the control, especially of the inverter. Some of these possible changes are presented.

Chapter 3 presents the energy source which is a photovoltaic panel. Normally a DC/DCconverter optimizes the photovoltaic panel power output. When there is excess power the control of the DC/DC-converter is important. This chapter presents the concept of limited range voltage control, applied to a flyback-based converter.

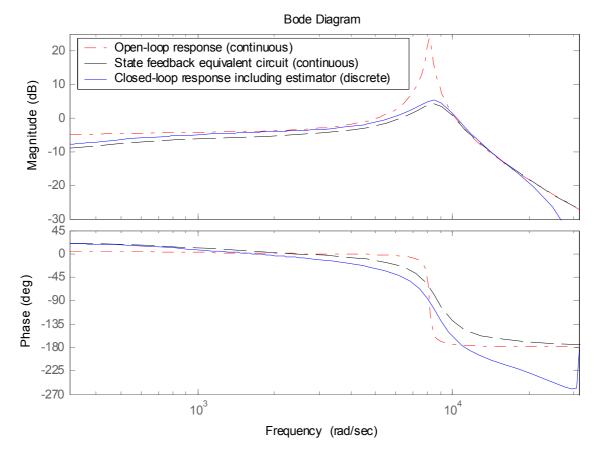

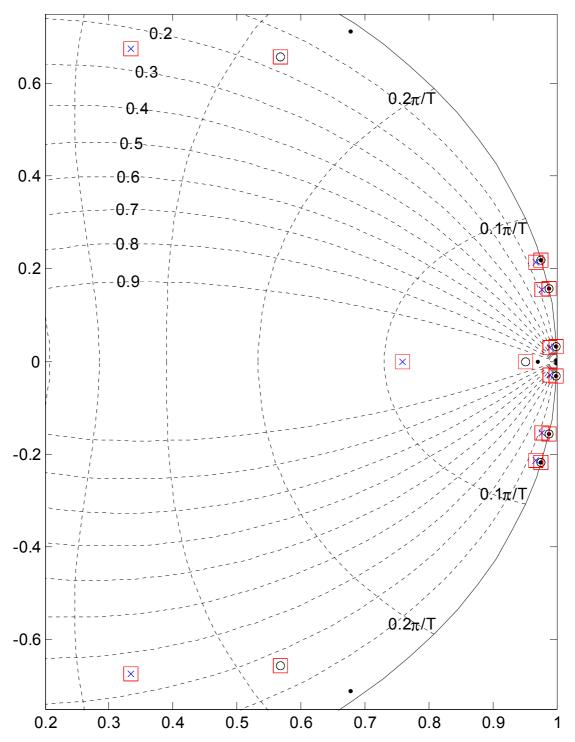

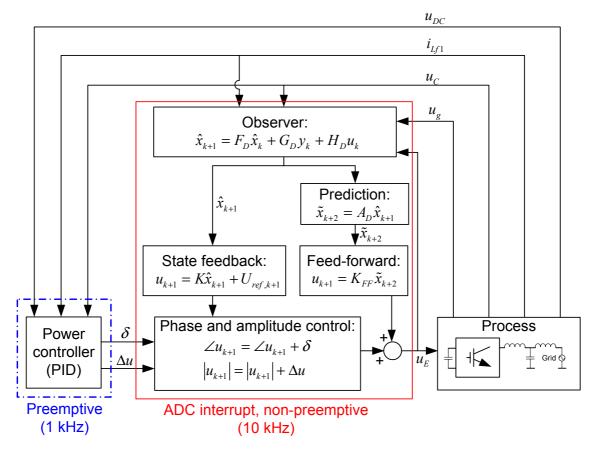

Chapter 4 deals with the modeling and simulation of the inverter. A model of the LCLfilter and the grid with some harmonics is presented. The model is the basis of a full state-space observer, which is discretized and designed. The response is simulated in Matlab Simulink, and some measurements are included.

Chapter 5 describes the controllers for the inverter and the DC/DC-converter. All control algorithms are based on a voltage controlled inverter. State feedback is used for damping the LCL-filter resonance. It is designed by pole matching of the feedback loop and a discretized equivalent circuit with virtual resistors. This is seen in relation with feed-forward for grid current THD improvement. A voltage support algorithm is presented, and it is compared to an anti-islanding algorithm developed.

Chapter 6 presents the software framework. Software is a significant part of the laboratory setup. Most of the work presented in this thesis is intended for use in control software.

Chapter 7 presents the system test results and compares this to simulations. The control algorithms are tested and simulated. Communication and grid events causing control algorithm transitions are verified.

Chapters 8, 9 and 10 summarize the discussion. Conclusions are drawn, and further work is suggested.

Chapter 1: Introduction

# 2 Detailed system description

A DG unit has been designed for the case of feeding power from a photovoltaic panel to a 3-phase electricity grid. The presented solution shows many of the design possibilities, problems and benefits of a DG using communication. The focus is thus on the interface between communication, digital control and power electronic converter design. The system can be divided into two main parts: The energy source using a DC/DC-converter for energy optimization, and the inverter for grid connection. The inverter has a filter as well as electromechanical contactor connected to the grid and a local load.

#### 2.1 Energy optimization

The main purpose of the DC/DC-converter is optimizing the energy output from a photovoltaic (PV) panel, using Maximum Power Point Tracking (MPPT). The converter ensures that the PV panel is operating at optimal voltage under all insolation and temperature conditions. Good conversion efficiency is in this respect essential in order to obtain a net energy gain, minimizing losses. For non-dispatchable energy sources like photovoltaics, the power output can vary from zero power during night to full power during bright and sunny days. The converter must therefore have high efficiency in the whole power range. The European weighted efficiency also given in [9], gives a representative measure of which power levels a PV-connected converter operates:

$$\eta_{ewo} = 0.03 \cdot \eta_5 + 0.06 \cdot \eta_{10} + 0.13 \cdot \eta_{20} + 0.1 \cdot \eta_{30} + 0.48 \cdot \eta_{50} + 0.2 \cdot \eta_{100}$$

(2.1)

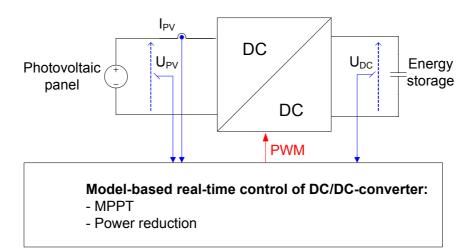

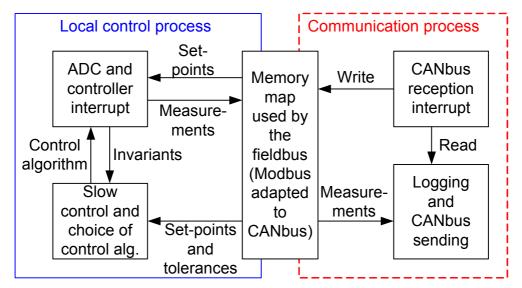

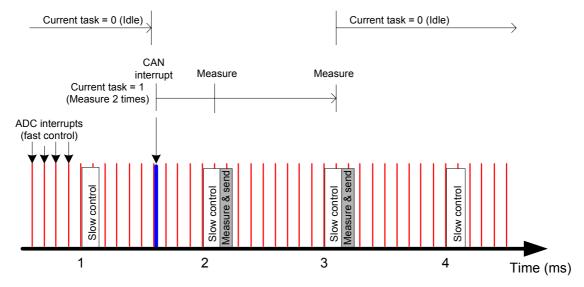

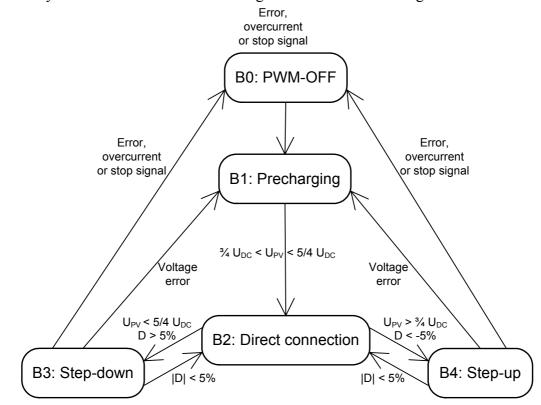

where  $\eta_x$  is the converter efficiency at x percent of the rated power. The DC/DC-converter control system is shown in Figure 3.

Figure 3: The DC/DC-converter control system.

The DC/DC-converter should be able to handle full energy storage. In this case it reduces the energy source power output. The voltage or current control necessary to reduce the power becomes the dimensioning criteria of the DC/DC-converter. It is thus necessary to control the DC/DC-converter in such a way that it can have a minimal size, and still supply as much energy as accepted by the energy storage. The photovoltaic panel is presented in detail in Chapter 3.

# 2.2 Grid connection and associated control algorithms

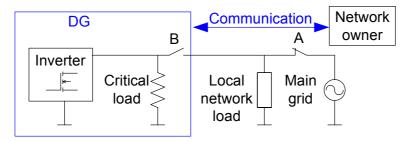

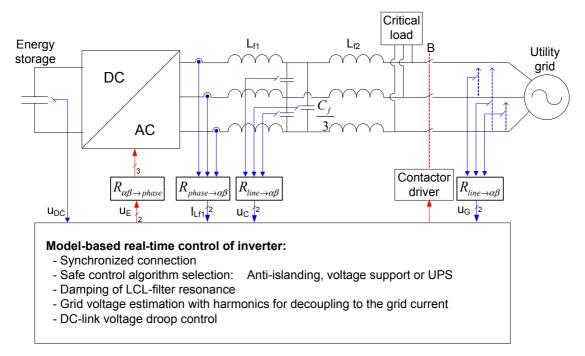

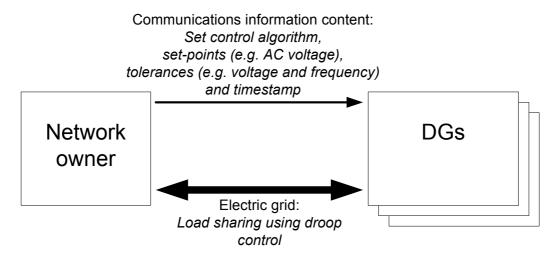

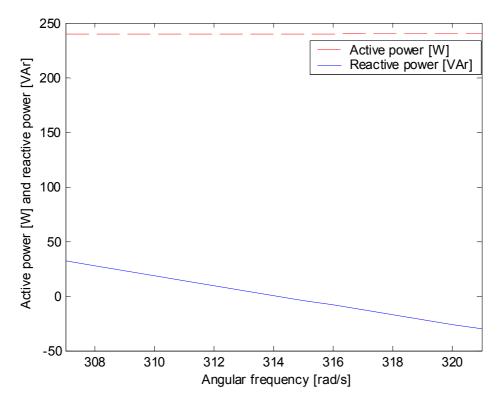

The grid connection circuit diagram is shown in Figure 4.

Figure 4: The grid connection circuit diagram.

The circuit breaker A is controlled by the network owner. The DG does not know the state of circuit breaker A explicitly. Circuit breaker B is controlled by the DG, but it may be overridden by the network owner when the communication is operational. There are three relevant connection states as defined in Table 1.

| <b>Connection state</b> | Circuit breaker state |     |  |  |

|-------------------------|-----------------------|-----|--|--|

|                         | Α                     | B   |  |  |

| Grid connected          | ON                    | ON  |  |  |

| Islanding               | OFF                   | ON  |  |  |

| Standalone              | Not relevant          | OFF |  |  |

Table 1: The connection states described by circuit breaker states.

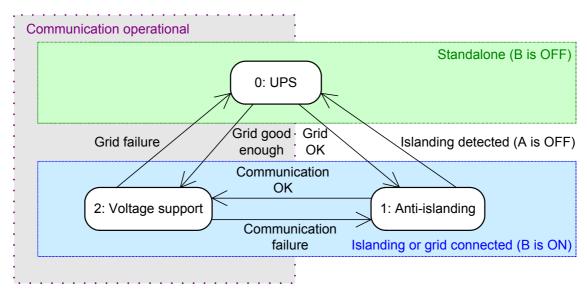

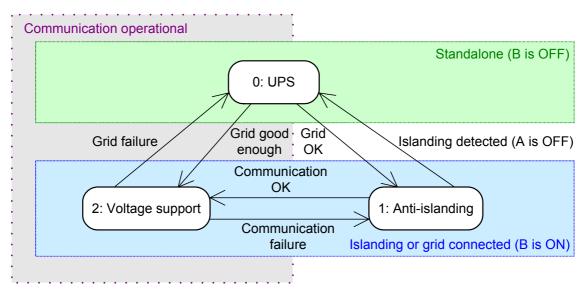

In the grid connected state, all available active power should be fed to the grid. In islanding connection state, the local network may be supplied by the DG when possible and if allowed by the network owner. When standalone the DG has isolated itself from the network, but it can still supply the critical load. These three connection states are related to three different inverter control algorithms. There is not a one-to-one relationship between the connection states and the inverter control algorithms due to the unknown state of circuit breaker A. The inverter can be controlled in one of the three different control algorithms specified in Table 2.

| Control        | Circuit breaker s | Communication |                 |  |

|----------------|-------------------|---------------|-----------------|--|

| algorithm      | Α                 | В             |                 |  |

| Anti-islanding | Observable ON N   |               | Not operational |  |

| Voltage        | Not observable    | ON            | Operational     |  |

| support        |                   |               |                 |  |

| UPS            | Not relevant      | OFF           | Not relevant    |  |

Table 2: The inverter control algorithms in relation with circuit breaker and communication states.

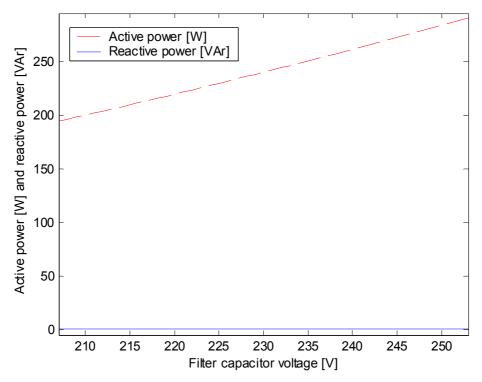

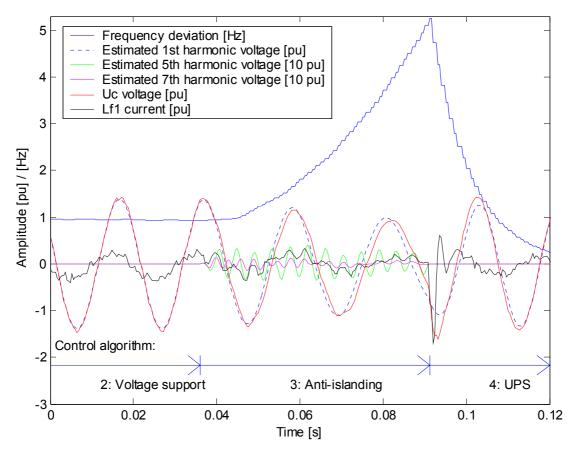

Finding the state of circuit breaker A can be done by so-called anti-islanding control of the inverter. An anti-islanding algorithm tries to observe the circuit breaker A state, which is not possible in the voltage support control algorithm. The voltage support control algorithm may on the other hand enable islanding of a grid segment, or support a weak grid by reactive power compensation. The UPS control algorithm supplies a critical load when B is OFF. The three main control algorithms of the inverter are shown in Figure 5.

Figure 5: Inverter main control algorithms (rounded boxes) and connection states (squares).

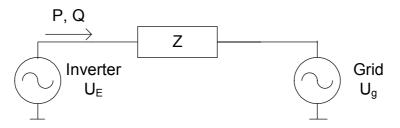

The inverter controls the grid connection. The inverter must meet a number of, and occasionally even contradictory, requirements. One example is that the grid current should be sinusoidal as specified in [10, 11]. When the grid is disconnected the same inverter serves as a power supply for the critical load. This operation requires the voltage to be sinusoidal independently of the current drawn. Voltage control also simplifies transitions between connection states. All three algorithms are therefore based on a voltage controlled inverter, also shown in [12, 13]. The inverter connections are shown in Figure 6.

Figure 6: The inverter connections. The neutral connector is not connected (3-wire system).

The grid connection includes a filter which reduces the switching frequency component entering the grid. There are three frequently used alternatives: The purely inductive filter (L-filter), the LC-filter and the LCL-filter. The L-filter requires larger magnetic components compared to the LC or LCL-filter, but it is easier to control (concerning stability). A purely inductive filter however, will not damp any switching frequency if open-circuited. This is often the case in a UPS system. The LCL-filter on the other hand is smaller concerning stored energy, and the different inductors can be optimized for different frequencies. This makes the filter smaller. The main disadvantage of the LCLfilter is its inherent resonance frequency. It is defined by  $L_{fl}$  and  $C_f$  when the grid is considered open-circuited.

$$f_{0,LCL,OC} = \frac{1}{2 \cdot \pi \sqrt{L_{f1} \cdot C_f}}$$

(2.2)

When short-circuited or connected to a stiff voltage source such as the grid, the resonance frequency is given by  $L_{fl}$  in parallel with  $L_{f2}$  and  $C_{f}$ .

$$f_{0,LCL,SC} = \frac{1}{2 \cdot \pi \sqrt{\frac{L_{f1} \cdot L_{f2}}{L_{f1} + L_{f2}}} C_f}}$$

(2.3)

Damping of this resonance can be accomplished using feedback control of the  $C_f$  voltage and inductor currents. The  $C_f$  current, which is the difference of the inductor currents, is often used. The voltages and currents are not necessarily measured, but can be estimated using a state-space observer such as the Luenberger observer [14] used in this work. The load-connected inductor in an LCL-filter limits the disturbance frequency, so that it is within the controller bandwidth. In an LC-filter, there are no limits how high the resonance may be. It is thus not guaranteed that the resonance frequency can be damped by a controller for an LC-filter. An LCL-filter also provides a load or grid current less sensitive to filter capacitor voltage errors. The LCL-filter is therefore used in the laboratory setup.

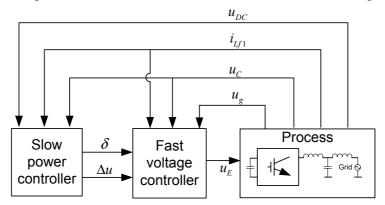

Synchronizing is the responsibility of the inverter controller, which measures the grid voltage, and uses this to adjust its voltage amplitude, frequency and phase. Synchronization can be done using an observer. The use of this observer also offers the possibilities of applying standard design and analysis methods like pole assignment. Both the LCL-filter and the grid voltage can be expressed in state-space form for model-based estimation and prediction used for controlling the inverter. The fast voltage controller is identical for the three different control algorithms. Only the slower power control and some harmonic concerns differ in the two grid-connected control algorithms (anti-islanding and voltage support).

#### 2.2.1 UPS control algorithm

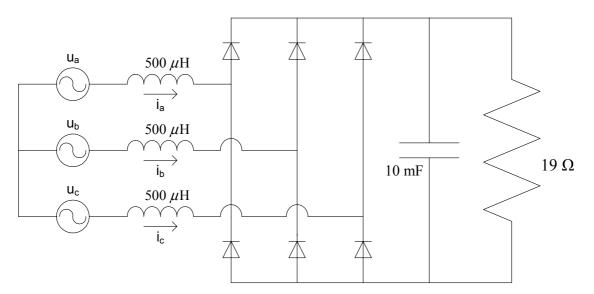

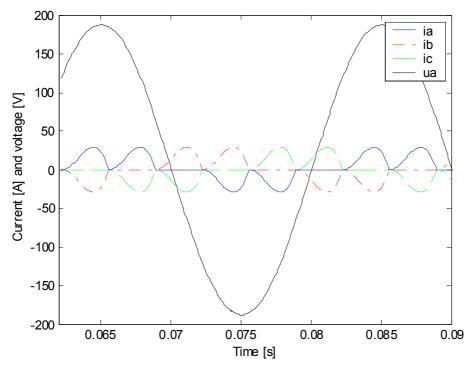

The UPS control algorithm is characterized by sinusoidal reference voltage control. This algorithm is operative when the grid fails. A typical load in this case is a nonlinear load. A 3-phase diode rectifier load shown in Figure 7 gives a representative circuit for a nonlinear load.

Figure 7: A diode rectifier load representative of electronical loads.

The disadvantage of nonlinear loads is the fact that the current drawn is not sinusoidal as shown in Figure 8.

Figure 8: Typical current waveforms of the circuit in Figure 7 (simulation results).

In order to supply a sinusoidal voltage, the inverter cannot be current controlled for this type of load and thus must instead be voltage controlled. The current will have a number of harmonic components. The typical critical load is computers, which are single-phase

loads. This unbalanced diode rectifier load gives a 3rd harmonic in addition to the 5th, 7th and higher frequency components also caused by a balanced diode rectifier load.

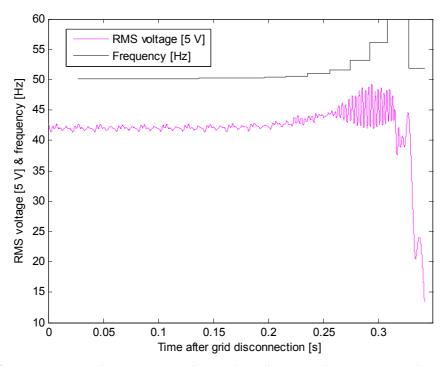

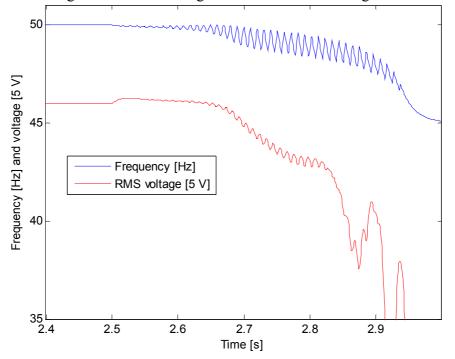

## 2.2.2 Anti-islanding control algorithm

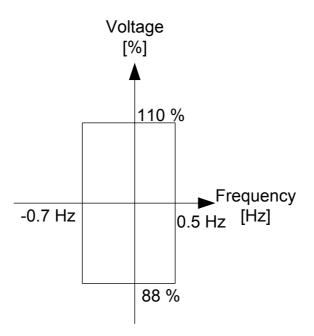

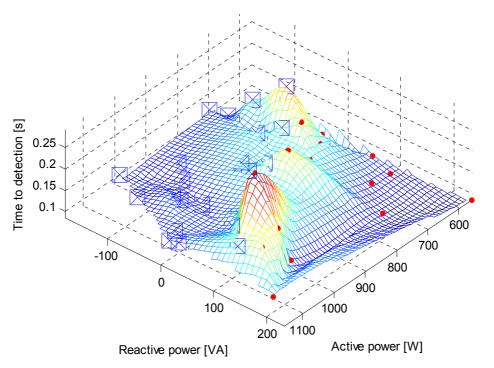

The anti-islanding control algorithm is used when there is a question of unintended islanding anywhere in the connected grid. Such a situation may appear when the locally produced power balances the load, followed by a disconnection event somewhere in the grid. The anti-islanding control algorithm drives the frequency or the amplitude of an eventual grid island out of the main grid tolerances, which indicates a grid island. The DG should then disconnect the grid.

It is important to be able to detect such a situation for personnel safety. The reason for a grid disconnection event is usually a fault. Without this algorithm, an islanding connection state can be hidden. The network owner may believe the disconnected part is not energized. Repair personnel could then be exposed to an electric shock. If a grid island has a phase 180° shifted from the main grid when reconnecting, an effective short-circuit could occur. This may result in damage of equipment or blown fuses. Grid connected distributed power supplies is required to detect an islanding connection state within 2 seconds, as a protection against these two situations [11]. The principle of islanding is shown in Figure 9.

Figure 9: The principle of islanding: If DG production equals the load when the grid is disconnected, they can keep on running forming an island.

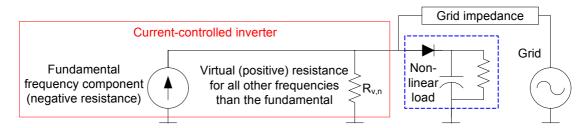

This control algorithm is normally grid-connected. The first control aim is to control the grid current to be sinusoidal. The fundamental frequency component can be controlled by applying amplitude and phase shifted voltage compared to the grid voltage. The grid-side inductor current will then be close to sinusoidal. This method is, however, more sensitive to measurement and model errors compared to current control. Compensation of the most common harmonic currents such as 3rd, 5th and 7th can be done using feed-forward of the individual grid voltage harmonics. This improves the current waveform to acceptable levels when using voltage control.

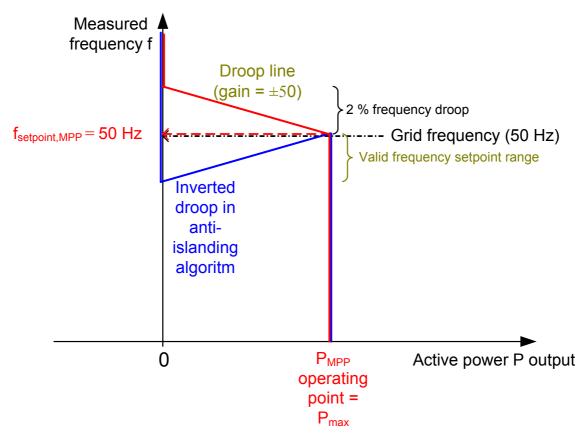

The second control aim is to detect an eventual islanding connection state in the grid. This avoids the risk of a stable island, measured by frequency and voltage. There are many methods for detecting this. Some algorithms such as Sandia Frequency Shift (SFS), Sandia Voltage Shift (SVS), and Slip Mode frequency Shift (SMS) can detect such a situation reliably [15]. All three algorithms use positive feedback in order to destabilize either the frequency or the voltage amplitude. This drives the frequency or voltage of an eventual island out of predefined tolerances. A stiff grid connection is on the other hand not affected. All known published work is based on current-controlled inverters. One publication relevant to the voltage controlled inverter presented here is anti-islanding algorithms for rotating machinery [16]. A positive feedback anti-islanding algorithm for voltage-controlled inverters will be presented in Chapter 5.

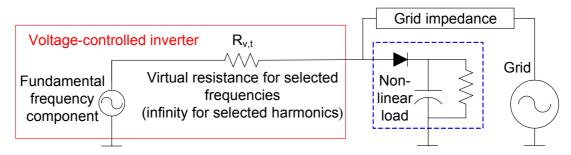

## 2.2.3 Voltage support control algorithm

In a voltage support control algorithm, the inverter should stabilize both the voltage and the frequency of the grid, regardless whether it is in islanding or grid-connected connection state. The control of the inverter must then be opposite of the anti-islanding control, but similar to the control of larger power production facilities. Such a stabilizing function makes it impossible to distinguish an islanding connection state from a stiff grid connection.

Grid islands are not necessarily a disadvantage, because they can limit failures and thus improve grid voltage reliability. This relies on the ability of the network owner to control the islands. When there is no electrical connection, which is the case for an island, an alternative control method must be based on information from the network owner. The information can ensure the safety of repair personnel and equipment.

The voltage support control algorithm should include the voltage controllability of the UPS control algorithm. For the same reasons as the UPS algorithm, the inverter should be able to supply a non-sinusoidal load current. The voltage support algorithm also acts as a reactive power compensator and active power stabilizer. This balances the production and consumption of both reactive power and active power in islanding connection state (limited by production capacity). When the grid is connected the algorithm helps to stabilize the local voltage by reactive power regulation of the grid. There should be means of controlling differently the various DGs. The network owner should also be able to change the DGs set-points (e.g. AC voltage) and tolerances (e.g. frequency and AC voltage) in real-time. This can be accomplished by using an energy management system.

# 2.3 Energy management system

In this thesis, the voltage support algorithm is based on voltage control. Internet communication ensures that the network owner always will be able to exit this voltage support algorithm to stop a grid island. In the work of Borle et al. [17], a voltage support algorithm has been applied, but with current control and without the use of communication. A communication system for protection against unintentional islanding

is described by Ropp et al. [18]. However, this is based on power-line communication and it is therefore unavailable during islanding connection state. It does not represent an extra control path, but simply replaces an anti-islanding algorithm in the inverter controller. Pettigrew proposes a system which changes the DG control if communication is lost, in order to detect islanding under all circumstances [19].

On the other hand, Internet cannot guarantee timeliness. It can only support soft realtime systems. In case of communication loss (detected through a timeout), the system fails to a safe control algorithm based on previously received information. For example if both control paths in Figure 10 are broken, the system degrades to UPS control (standalone connection state).

Figure 10: Communication as a method for controlling grid segments independently of the grid.

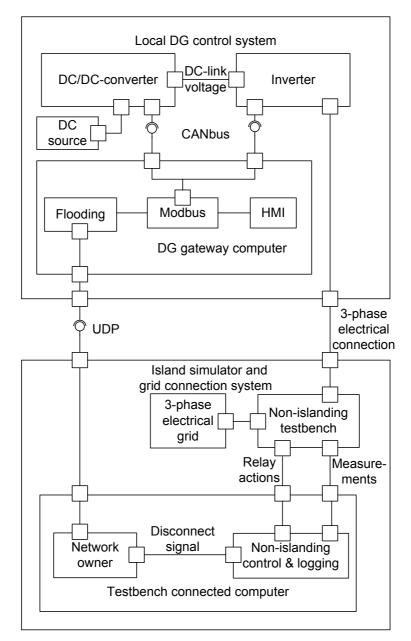

The energy management system uses communication to control a number of DGs. The design of the communication system is divided in two parts, a local communication bus, and a long-distance Internet communication algorithm. The local communication bus is a CANbus (Controller Area Network bus), connected to the different controllers of a DG. This is connected to the Internet by a DG gateway. It makes it possible to control the DGs externally, for example by the network owner.

### 2.3.1 Internet protocol

The cost of communication must be kept low. A promising approach is using existing infrastructure, such as the Internet. However, it is neither reliable nor real-time. Fault detection must therefore be placed in the DG. This is similar to the philosophy of the Internet, which has little error correction at the network layer, but compensates this by more advanced error handling in the end-user computers.

The Internet protocol (IP) has disadvantages making it less suitable for power control. It is not real-time because no priority is built in. The reliability during power outages is questionable. A combination of an unreliable communication channel and a fail-safe local control system may be a good choice. The degree of autonomous control in a more general context is discussed by Moslehi et al. [20]. A combination of autonomous DGs with additional functions served by communication is used in this thesis. However, it is important to detect a communication failure. The communication failure detection is done using a heartbeat message with a timestamp. Failure is signaled when the communication system crashes or fails, or in situations when the network owner stops sending these messages. Failure is then detected by the DG through a timeout. The Internet protocol is a network layer protocol in the in the OSI reference model [21] shown in Figure 11.

| Application layer  |

|--------------------|

| Presentation layer |

| Session layer      |

| Transport layer    |

| Network layer      |

| Data link layer    |

| Physical layer     |

Figure 11: The seven layers of the OSI reference model.

Transport layer communication protocols can be classified into connection-oriented and connection-less protocols. Transmission Control Protocol (TCP) is a connection-oriented protocol, on contrary to the User Datagram Protocol (UDP) which is a connection-less protocol. Both are based on the Internet protocol. A power gateway based on HTTP (TCP/IP), is shown by Mawire [22].

A basic requirement for the communication system for DG is scalability. Communication that includes acknowledges directly faces problems when a large number of DGs are to be controlled. The User Datagram Protocol (UDP) is connection-less, and it does not include acknowledge in any of the phases of the communication. It represents a protocol with less overhead compared to TCP. The destination is addressed simply by the IP address and the port number. It is a best-effort protocol and hence guarantees neither ordering nor delivery. Unlike TCP, the UDP does not have congestion control. This makes it controversial to run high-bandwidth applications like multimedia over UDP [23]. UDP-based protocols are in general sufficient for soft real-time applications. The UDP segment, or transport-layer packet structure is shown in Table 3.

Table 3: The UDP segment structure.

| ◀                                          | 32 bits  |  |  |  |

|--------------------------------------------|----------|--|--|--|

| Source port number Destination port number |          |  |  |  |

| Length                                     | Checksum |  |  |  |

| Application data (message)                 |          |  |  |  |

UDP gives the programmer complete control of the information that is transmitted due to its simplicity.

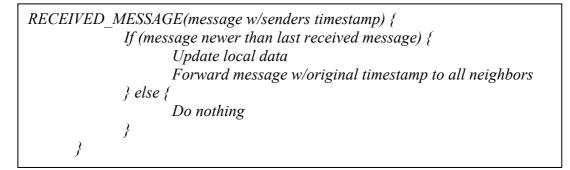

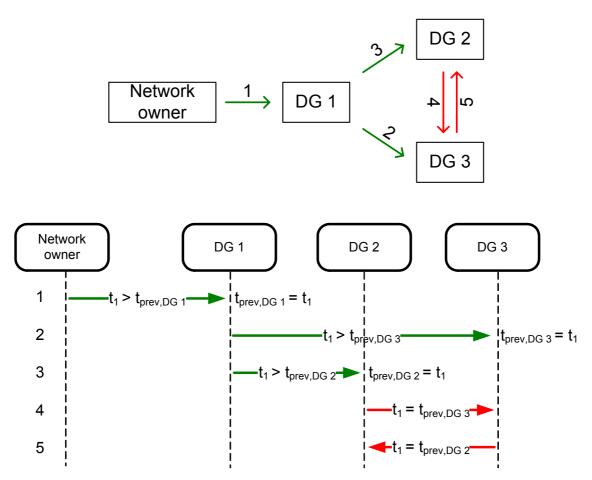

## 2.3.2 Communication scalability

Scalability is of vital importance for large-scale communication. In order to implement real-time communication, the loading of the master (in this case the network owner) must be taken into consideration. The number of DGs should be possible to increase to several thousands without reaching limits caused by communication bandwidth to the master (network owner). Epidemic algorithms offer this property as described by Demers et al. [24]. They mimic how an epidemic spreads in a population. Flooding is the simplest form of an epidemic algorithm. It can be imagined as flooding water, trying every possible path to the sea. The fastest route determines the convergence time. The end-condition can be given as a fixed number of recursions, or it can be defined by the moment when one message is received twice as shown in Figure 12.

Figure 12: Flooding algorithm used in a limited network.

A more advanced epidemic algorithm is gossiping. It mimics how gossip randomly spreads in a population. Vanthournout uses gossiping for scaleable DG communication [25]. This algorithm is not real-time. Flooding has a shorter time delay. It is here demonstrated through practical implementation of a flooding algorithm consisting of one master (network owner) and two slaves (DGs). The flooding algorithm with three slaves (DGs) can be visualized as shown in Figure 13.

Figure 13: Flooding relies on forwarding of received messages to neighbors until a message has been received twice. This ends the forwarding process. Accepted messages are indicated by green arrows, while red arrows indicate previously received messages.

#### 2.3.3 Monitoring

KWh-metering is perhaps the best driver to communication not only to DG but also to kWh-counters in private homes and in industry in Norway. There are many commercial solutions to this, and standardization is a part of this. Use of communication for monitoring of DG is commercially available. What is needed is mainly a standardization of the data exchange format. An example of such is the ODEL 2.1 XML version presented by Feilberg [26]. The data exchange format used in this thesis is inspired by the ODEL 2.1 XML format.

The monitoring data should be accessible mainly for the owner of the DG. However, it would be beneficial for the network owner also to know both the instantaneous production within one area and type of production (in order to predict the load). A distributed system presented by Vanthournout [25] can be used to get the aggregated production within one area.

# 2.4 Overall control for safe operation

Power electronic converters require a fast and reliable response time. They must therefore operate safely without the communication operative. Communication status can be used for choosing a safe control algorithm, but the control algorithms themselves can not rely on communication due to timeliness and reliability concerns.

The converter tolerances concerning voltage, current, temperature and other variables depend on the type of power electronic converter. A fail-to-safe-mode control must therefore be implemented, for each converter. For most power electronic components, a safe operating area (SOA) is defined [27]. The different components in a DG system have different safety-critical variables. Table 4 shows some relevant examples.

| Standalone inverter | Grid-connected inverter  | DC/DC-converter     |  |

|---------------------|--------------------------|---------------------|--|

|                     |                          |                     |  |

| Temperature         | Temperature              | Temperature         |  |

| DC voltage          | DC voltage               | Output voltage      |  |

| AC current          | AC current               | Input voltage       |  |

| Driver-level faults | Driver-level faults      | Current             |  |

|                     | AC frequency             | Driver-level faults |  |

|                     | AC voltage               |                     |  |

|                     | Communication (optional) |                     |  |

These safety-critical variables are specified with a minimum and/or a maximum value defining the tolerances. In cases where the variables can be controlled, a tolerance violation should lead to an appropriate change of the control algorithm to avoid further consequences. The tolerance values are defined so that the system is gracefully degradable.

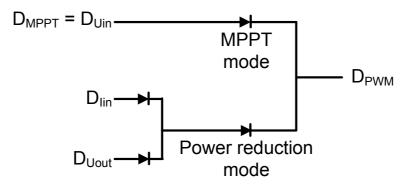

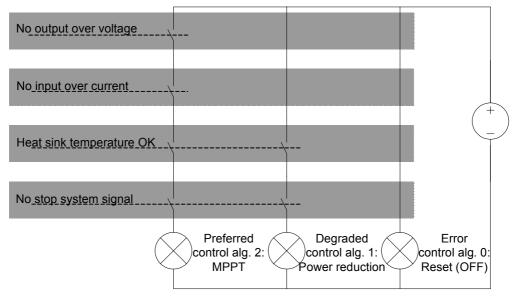

The DC/DC-converter applied in this work can be used in order to illustrate the concept of a gracefully degradable system. If during MPPT the DC/DC-converter looses its load, the energy source must reduce the output power. Otherwise the output voltage may increase out of boundaries. A gracefully degradable system prevents the converter from immediately shutting down, but instead controls the output voltage by switching to a power reduction control algorithm. The list of preferred control algorithms is shown in Table 5.

| Preference number | Control algorithm      |  |  |

|-------------------|------------------------|--|--|

| First priority:   | A2: MPPT               |  |  |

| Second priority:  | A1: Power reduction    |  |  |

| Last priority:    | A0: Reset (system OFF) |  |  |

Table 5: List of preferred control algorithms for the DC/DC-converter.

The requirements for the control algorithms in Table 5 can often be ordered in a decision table, as shown in Table 6.

| Current control<br>algorithm | No output<br>over-<br>voltage | No input<br>over-<br>current | Heat sink<br>temperature<br>OK | No stop<br>system<br>signal | Hexadecimal representation |

|------------------------------|-------------------------------|------------------------------|--------------------------------|-----------------------------|----------------------------|

| A0: Reset (OFF)              | 0                             | 0                            | 0                              | 0                           | 00                         |

| A1: Power reduction          | 0                             | 0                            | 1                              | 1                           | С                          |

| A2: MPPT                     | 1                             | 1                            | 1                              | 1                           | F                          |

| Bit number                   | 0                             | 1                            | 2                              | 3                           |                            |

Table 6: Decision table for the DC/DC-converter system control algorithms

Voltage and current are connected to the transition between Algorithms A2 and A1. Heat sink temperature is one example of a parameter that can be connected to transitions between Algorithms A1 and A0. This method has been implemented for ensuring safe operation of both converters in the system. Temperature measurements were not implemented in the laboratory setup. For more detailed information, see Chapter 6.

# 3 Energy source modeling and control

There are a variety of competing technologies as energy sources for DG, such as wind, hydropower, and different fuels such as biogas. In this work, however, photovoltaic (PV) is chosen as the energy source due to its scalability, simplicity and availability. A PV system is easily scaled by the number of PV cells. It has no moving parts, and it is thus reliable. The sun is shining in most places, although the average yearly energy yield varies with latitude and local climate. The technology is promising, but there is a need for cost reduction.

The power output of a photovoltaic panel for a given irradiation and temperature depends on the operating voltage. This voltage can be held fixed, as is most common in battery systems, or it can be varying, which it is for most grid-connected systems. In order to decouple the PV panel voltage and the DC-link voltage of the inverter, a DC/DC-converter is commonly used. The maximum power point (MPP) can then be tracked, using a maximum power point tracking (MPPT) algorithm for optimizing the PV panel operating voltage.

The model of the photovoltaic panel is valuable for the control and choice of DC/DCconverter. Especially during periods with more available PV power than consumed by the load, the control and the choice of DC/DC-converter topology is important. This chapter presents a model of the PV panel. A DC/DC-converter topology is then discussed. The control of this DC/DC-converter is described at the end of Chapter 5.

Silicon is the most common material for photovoltaics. Other materials such as galliumarsenide (GaAs) give higher efficiency, but the production cost is considerately higher compared to silicon. These materials are often used in space applications and in concentrating PV systems.

## 3.1 Photovoltaic cells

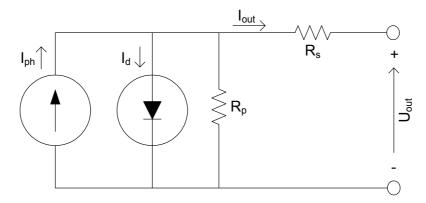

The photovoltaic cell can be considered as a semiconductor pn-junction. Instead of conducting in the forward-conducting region (forward-conducting diode), one makes use of the reverse space charge region generation current caused by photons,  $I_{ph}$ . This gives rise to a current  $I_{out}$  flowing in the reverse (blocking) direction of the pn-junction, as shown in Figure 14.

Figure 14: The photovoltaic cell equivalent circuit scheme.

One silicon photovoltaic cell can be modeled according to Equation (3.1) [28]. The last term (the current trough  $R_p$ ) is added to the original equation to model pn-junction imperfections due to e.g. shunts in the silicon crystal structure.

$$I_{out} = I_{ph} - I_{or} \left[ \frac{T}{T_r} \right]^3 \cdot e^{\frac{q_e \cdot E_G}{K \cdot B} \left( \frac{1}{T_r} - \frac{1}{T} \right)} \cdot \left[ e^{\frac{q_e \cdot (U_{out} + I_{out} \cdot R_s)}{K \cdot B \cdot T}} - 1 \right] - \frac{U_{out} + I_{out} \cdot R_s}{R_p}$$

(3.1)

where:

I<sub>out</sub> = Photovoltaic cell output current [A]

- $I_{ph}$  = Photovoltaic current ( $\propto$  irradiance) [A]

- I<sub>or</sub> = Saturation current [A]

- T = Solar cell actual temperature  $[^{\circ}K]$

- $T_r$  = Reference temperature (298 [°K])

- $q_e$  = Electron charge =  $1.602 \cdot 10^{-19} [coulomb]$

- $E_G$  = Silicon band gap (1.1 [eV])

K = Bolzmann's constant =

$$1.38 \cdot 10^{-23} \left[ \frac{Joule}{^{\circ}K} \right]$$

- B = Ideality factor of the diode

- $R_s$  = Equivalent series resistance

- $R_p$  = Equivalent parallel resistance

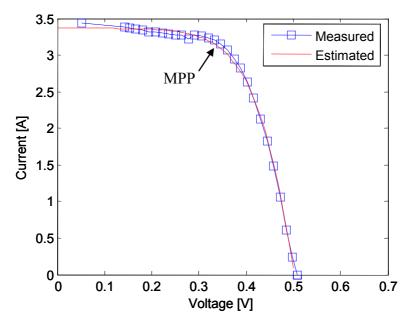

The maximum output voltage is given by the diode forward conduction voltage drop (approximately 0.7 V), which for silicon is highly temperature dependent. The IV-characteristic based on Equation (3.1) and estimated parameters specified in Table 7 are shown in Figure 15.

| Parameter       | Value                     |

|-----------------|---------------------------|

| I <sub>ph</sub> | 3.36 [A]                  |

| I <sub>or</sub> | 1.91·10 <sup>-7</sup> [A] |

| Т               | 382 [°K]                  |

| В               | 1.55                      |

| R <sub>p</sub>  | 1.84·10 <sup>⁵</sup> [Ω]  |

| R <sub>s</sub>  | 9.26 [mΩ]                 |

Table 7: Estimated parameters of the PV model

Figure 15: Typical IV-characteristic of a silicon photovoltaic cell. The measurements are scaled from measurements from two series-connected 80 Wp type Photowatt PW 750 PV panels (72 cells). The measurements were taken manually using an IGBT in the active region as an adjustable load.

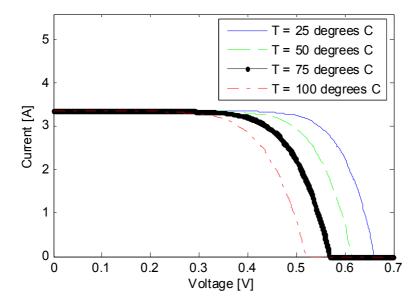

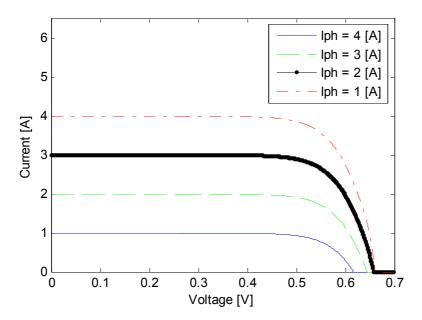

More advanced methods for modeling PV cells, such as a two-diode model exist. For this work the presented single-diode model is assumed sufficient. Typical temperatureand irradiance dependence is shown in Figure 16 and Figure 17, calculated using Equation (3.1) with the parameters specified in Table 7.

Figure 16: The variation of output current and voltage as a function of the temperature.

Figure 17: The variation of output current and voltage as a function of  $I_{ph}$ . The current  $I_{ph}$  is approximately proportional with the irradiance.

One can observe that the voltage is approximately inversely proportional to the temperature. The irradiance has some influence on the voltage. However, increased irradiance leads to higher cell temperature. In sum, the irradiance has less influence on the steady-state voltage under normal operating conditions, than Figure 17 indicates.

## 3.1.1 The photovoltaic panel

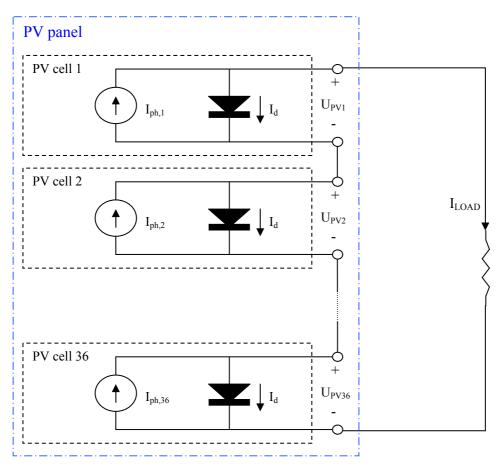

A typical photovoltaic panel consists of a number of series-connected photovoltaic cells. A common standard panel for 12 V lead-acid battery charging is 36 cells in series, as shown in Figure 18.

Figure 18: A 36-cell PV panel circuit-scheme representation.

Assuming equal irradiation, temperature and cell parameters a PV panel can be modeled simply by scaling the voltage of a single PV cell. Using the same approach for paralleling, the current can then be multiplied by the number of paralleled strings. These simplifications do not hold for cell inequalities and partial shading of the PV panel.

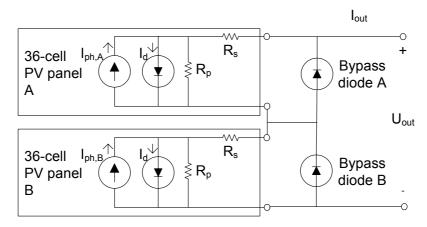

Bypass diodes are often connected in anti-parallel with the PV cell pn-junction equivalent scheme diode. Bypass diodes are usually not connected over every cell in a PV panel, but instead one diode serves 10-20 PV cells in series. This is sufficient to avoid heat damage of a shadowed cell caused by its absorption of the power produced by the other non-shadowed cells of the series connection. A test setup consisting of two PV panels and a bypass diode per panel (36 cells) is shown in Figure 19.

Figure 19: A test setup for testing of bypass diodes in connection with shading of one single cell.

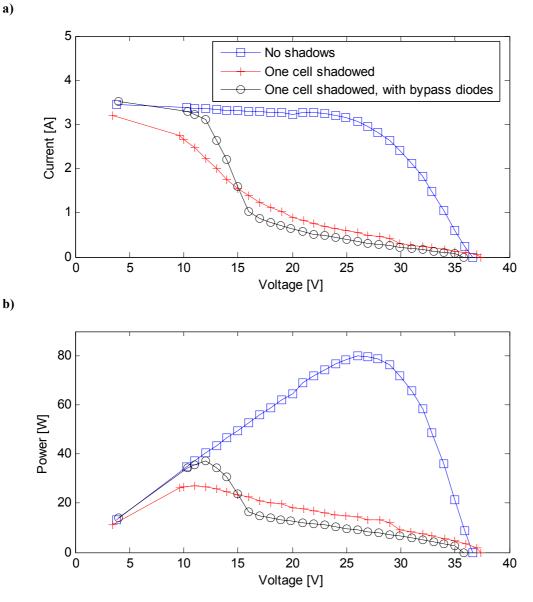

Figure 20 shows how the shading of one cell in one of the PV panels affects the IV-curve of the two series-connected PV panels.

Figure 20: a) Measurements of the shading effect on a photovoltaic panel (2 series-connected 80 Wp type Photowatt PW 750). b) resulting output power.

The combination of blocking or partially conducting cells and conducting bypass diodes makes the IV-curve deviate from the scaled single-cell equivalent. One effect that can be seen due to partial shading is an unexpected large difference in MPP voltage,  $U_{MPP}$ , compared to open-circuit voltage,  $U_{OC}$ .

Assuming that bypass diodes are applied, the photovoltaic panels can be short- or opencircuited without damaging the panels. Apart from the MPPT algorithm and a method to reduce the panel output power, control of the PV-panel is not needed.

## 3.2 PV panel voltage control

Control of the PV panel voltage is associated with MPPT and power reduction controllers (output voltage or current limitation). These two purposes are contradictory and only one of these two control algorithms can control the DC/DC-converter at a time. The sizing of the DC/DC-converter is associated with the control of the PV panel voltage.

#### 3.2.1 Converter efficiency

The control of the PV panel voltage is an advantage, but the cost of and losses in the converter needed can, however, offset much of the gain. This is also the case for other systems such as variable-speed turbines compared to fixed-speed turbines (wind or hydropower). Analyzing the physical properties of the photovoltaic panel, converter efficiency and size, one can estimate the gain. The efficiency of a DC/DC-converter is usually significantly lower at partial loading compared to full load, and a converter with less than full power rating is therefore beneficial. This is valid concerning maximum current [29] as well as voltage regulating range [6-8].

#### 3.2.2 MPPT

MPPT can improve the energy output of a PV panel [30]. The gain is however very temperature dependent [31] and depends on DC/DC-converter efficiency [32]. There are two major classes of MPPT algorithms. Having knowledge about the relationship between current and voltage of a given PV panel, one only needs to measure one of the two in order to get sufficient information to perform MPPT. The other class of algorithms, which is used in this work, utilizes the measurements of both current and voltage of the PV panel. The MPPT algorithm then finds the MPP by calculating the output power at different voltages.

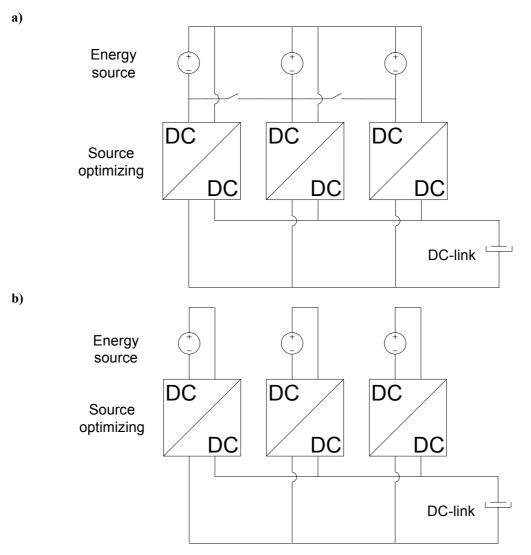

Parallel connection of DC/DC-converters with MPPT on the PV panel side, requires communication for MPPT. The connection has been called the team concept by Myrcik and Calais [9]. The other alternative, paralleling on the DC-link side is done for the string converter. The main difference between the two circuit schemes is the string converter does not require communication, while the team concept needs real-time communication for controlling the PV panels in MPPT algorithm. The string converter is compared to the team concept in Figure 21.

Chapter 3: Energy source modeling and control

Figure 21: a) The team concept. b) String converters.

The team concept is able to adjust the power level by shutting OFF some of the converters. All active converters except one (controlling the PV voltage) are able to operate at their optimal load point concerning efficiency or other measures. This solution also offers redundancy as one failed converter only reduces the maximum output power of the system, but a failure has no influence on medium power levels. Communication is necessary for selecting the converter to control the PV panel voltage, and for measuring the aggregated power from all the paralleled converters. The rest of the converters are either OFF or current-controlled.

The string converter has gained popularity during the last few years. It is less sensitive to partial shading as the optimum PV panel voltage is tracked independently in the individual strings.

### 3.2.3 PV panel power reduction

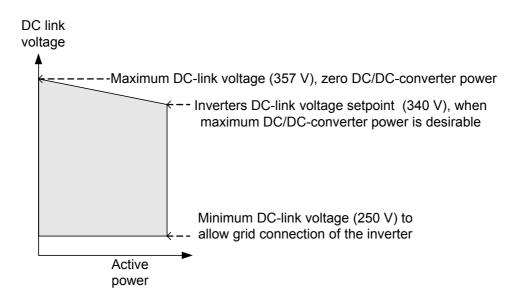

When the PV panel is connected to a DC/DC-converter, control of the panel is vital. The input power from the PV panels must be controlled in order to make the DC/DC-converter work as desired. Most converter topologies (such as boost converter) may output too high voltage or current if not properly controlled. When output power is controlled, the DC/DC-converter is made safe without use of communication. The inverter and the DC/DC-converter both decide the power level through a DC-link droop of 5 %, as shown in Figure 22.

Figure 22: DC voltage droop control of the DC/DC-converter in power reduction control algorithm.

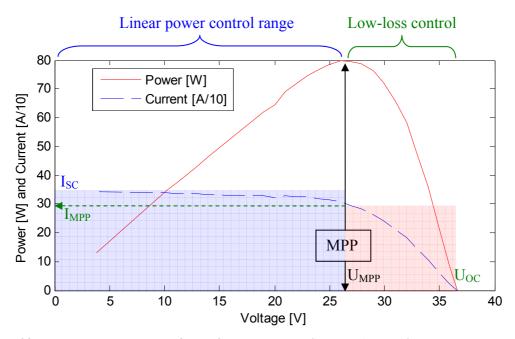

A thorough discussion about DC droop is shown by Karlsson [33]. Gaining control of the output power from the PV panel one needs to look at the connection between voltage and power output from the panel. This is shown in Figure 23.

Figure 23: Measured power curve for a 72-cell photovoltaic panel (two series-connected Photowatt PW 750). The colored squares indicate the current- and voltage-rating of the DC/DC-converter. The left, blue square shows the required voltage and current rating when controlling the PV panel voltage from MPP to short-circuit. The right, red square shows the required voltage difference and current rating when controlling the PV panel from MPP to open-circuit.

In order to reduce the power output, two regions of this plot give possible solutions. From a control perspective the most linear part of the curve, from the MPP down to short-circuit current,  $I_{SC}$ , may be beneficial. This requires a converter current rating equal to  $I_{SC}$  which is higher than the  $I_{MPP}$ . This controller does not give limited current (and thus power) rating.

Dimensioning for  $I_{MPP}$  is possible if the region from MPP,  $U_{MPP}$ , to open-circuit,  $U_{OC}$ , is used for power reduction. This makes it possible to reduce the converter rating both concerning maximum current, as well as the maximum input- and output voltage difference. Limited power rating is thus possible.

## 3.2.4 Series-connected boost converter

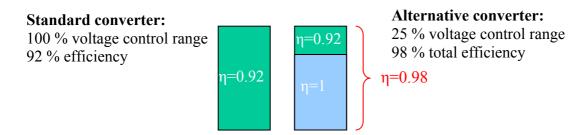

The optimal voltage of a photovoltaic panel,  $U_{MPP}$ , varies only by a fraction of nominal voltage when the PV panel produces noticeable amounts of power. A voltage variation of only 23 % keeps the voltage at optimum for a temperature span of 75 °C and constant irradiation, assuming the parameters given in Table 7. This makes it possible to decrease the converter losses according to the voltage variation. These losses are then reduced to approximately <sup>1</sup>/<sub>4</sub> of the normal value, which again leads to an increase of the DC/DC-converter efficiency from for example 92 % to 98 %. The low voltage variation also gives the possibility of minimizing the dimensions of the converter to about <sup>1</sup>/<sub>4</sub> of the normal size. This concept for optimal converter design is shown in Figure 24.

#### Figure 24: Method of reducing the DC/DC-converter losses.

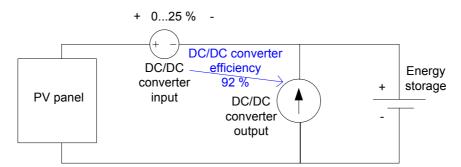

The method is patented by Beach and Brush [6] for a specific boost topology (Series-Connected Boost Converter, SCBC) and it is also described by Button [7] and Kimnach [8]. A step-down solution for lower voltages than these publications is shown in Figure 25.

Figure 25: The conceptual circuit scheme of a converter with limited range voltage control

A DC/DC-converter based on a flyback converter with both step-up and step-down capabilities is used in this work. Descriptions of converter topologies can be found in [34].

#### 3.2.5 Series-connected bidirectional flyback converter

The ideal DC/DC-converter circuit for PV panels would be able to transform the voltage both up and down with regard to the output DC-link voltage. A close match between the PV panel output voltage and the DC-link voltage could then be easier to accomplish. Some MPPT methods, which use the open-circuit voltage, need 24 % change between open-circuit voltage and MPP, plus the change due to weather variations. A solution which is close to satisfying these requirements is shown in Figure 26.

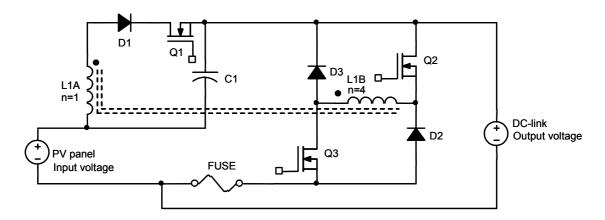

Figure 26: A series-connected bidirectional flyback converter. Inductors L1A and L1B are magnetically connected, with a turns ratio of <sup>1</sup>/<sub>4</sub>. Snubbers are not included in the drawing.

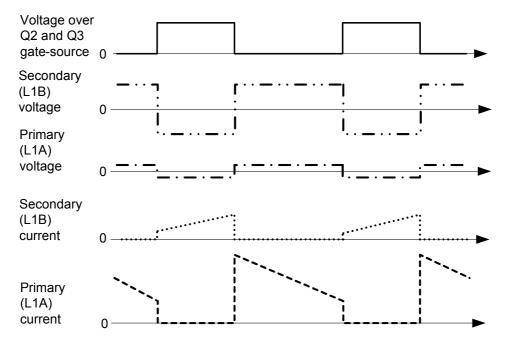

To avoid conduction in D2 and D3 when Q1 is ON, the duty cycle is limited to  $\pm 45$  %. The benefits compared to a standard boost converter, is the fact that the switches Q2 and Q3 carry <sup>1</sup>/<sub>4</sub> of the current. Idealized switching waveforms are shown in Figure 27.

Figure 27: Idealized switching waveforms of the bidirectional flyback converter in boost mode.

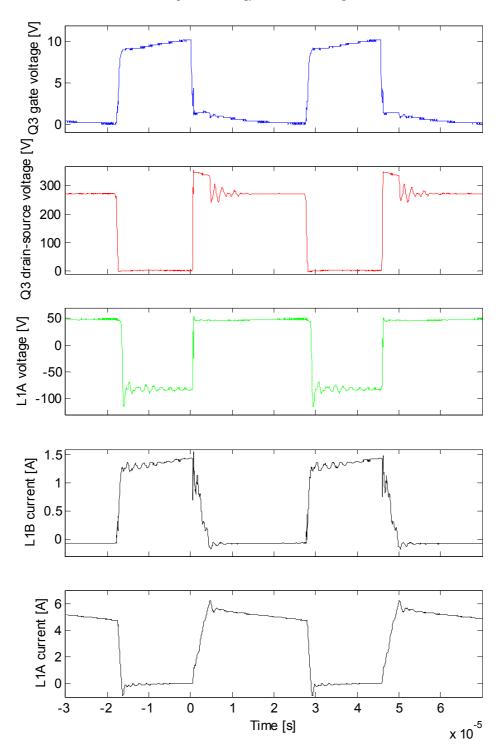

The leakage inductance is neglected here, together with the snubbers. The effect of the leakage inductance can be observed on the measured waveforms in Figure 28.

Figure 28: Waveforms recorded at 300 V input and 340 V output. The four upper traces were recorded with 3.4 A input current. The lowest trace was recorded separately with 3.3 A input current. All waveforms were recorded using 16-point averaging.

When coolMOS Q2 and Q3 turn OFF, the leakage inductance energy is freewheeled through diodes D2 and D3. Even though RC-snubbers were used for reduction of ringing, it can still be observed in the waveforms. It can be observed that the switching coolMOS Q2 and Q3 current is less than half the input current. This can reduce the switching loss to less than a standard boost converter, even though there are two switches. The benefit of using limited range voltage control is, however, higher if the input and output voltages are closer.

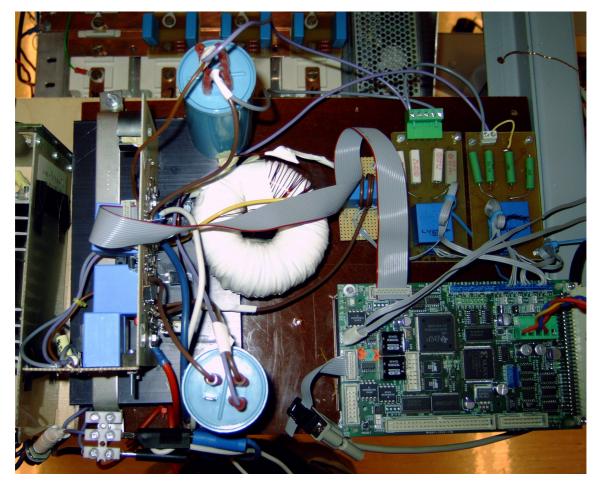

The extra switch, Q1, makes the DC/DC-converter bidirectional, thus giving the opportunity of having an input voltage higher than the output voltage. Although this switch carries the entire current, the switching voltage is only approximately  $\frac{1}{2}$  of the total voltage. The switching losses can therefore be reduced compared to a standard buck converter. The voltage regulating range can therefore be connected to efficiency in a way that can be exploited in PV systems. The DC/DC-converter developed is shown in Figure 29.

Figure 29: The DC/DC-converter developed for use in the laboratory setup.

## 3.3 DC/DC-converter discussion

There is an optimal ratio between the DC/DC-converter power rating and the PV panel power rating. The ratio between converter current rating and the PV panel maximum current is connected to the geographical latitude of the PV panel. The optimization is mainly based on a tradeoff between:

- 1. no-load losses (increases with size),

- 2. peak power loss due to undersized converter (decreases with size)

- 3. cost (increases with size).

On the other hand, the voltage control range is connected to:

- 1. Converter topology

- 2. The ratio between the PV-panel voltage and the DC-link voltage

The patented series-connected boost converter [6-8] implements the limited range voltage control based on a forward converter. It can only step up the voltage from a PV panel. Other topologies can implement the same principle of limited range voltage control, like the flyback-based topology presented here. It can both step the voltage up and down. The switching action can also be bypassed when not needed, for example when the PV panel optimum voltage equals the DC-link voltage.

Voltage control tradeoff number 2 puts narrow limits on the number of PV cells in series connection. Freedom of scaling is important for building-integrated PV. For small systems with a low number of paralleled strings, the fixed string size may be difficult to scale. On the other hand, for large systems consisting of a high number of paralleled strings, the system can be scaled by the number of parallels. A fixed number of cells in each string then does not represent a major limitation. The limited range voltage control principle is thus best suited for the paralleling of several PV panel strings.

This parallel connection can be done in at least two different ways, as shown in Figure 21. Parallel connection on the PV panel side is one option, called the team concept. Real-time communication is then necessary for MPPT. Parameter inequalities and shading of the PV panel cells give different optimum operating voltages for the paralleled strings. The strings then do not work on their individual maximum power point, reducing the PV panel output unnecessary. The limitation concerning partial shading is believed to be the most important reason why this team concept has not been used more in buildings.

The paralleling of strings with independent DC/DC-converters for each string does not require communication for MPPT. In this case MPPT is possible using only locally measured current and voltage. It is robust concerning inequalities for the different strings due to cell parameter differences and partial shading, because the string voltages are controlled independently. The partial shading losses may be significant for building-integrated PV, but this depends on the specific building.

A system with limited range voltage control may in some designs require maximum system voltage rated semiconductors in order to be safe during startup or unexpected shutdown of parts of the converter system. For example, a short-circuit of the PV panel in the laboratory setup would cause the DC-link voltage to be applied over the normally low-voltage switching transistor, if not properly secured by a diode. Startup of the system when the DC-link voltage is zero, results in the input voltage over this switch. All the switches in the DC/DC-converter are 800 V coolMOS switches, although the maximum expected DC-link voltage is 360 V. The limited range voltage control is thus not connected to the switch voltage rating, but only to the inductors and the thermal management. Using full voltage rated switches reduces the efficiency compared to using low voltage switches. The efficiency still is expected to be significantly higher compared to a standard DC/DC-converter with full range voltage control.

Limiting the voltage control range of a PV-panel connected DC/DC-converter, makes it harder or impossible to detect shaded or damaged PV cells. A standard full voltage regulating range converter can detect unexpected partial shading or damaged PV panel cells, if implemented in software. Such a detection mechanism may be implemented by measuring the complete IV-curve, and look for local maxima. These local maxima are most probably caused by some bypass diodes being activated, shorting some cells above a certain current. In the single-shadowed cell measurement presented here, there is only one global maximum. It is, however, placed unexpectedly far away from the opencircuit voltage. This unexpected location of the MPP can also be used for the detection of PV panel failures. These methods of discovering single cell shadowing or failure are impossible to use reliably for a converter that cannot control the input voltage in the area of the actual MPP. A converter having limited range input voltage control thus cannot detect such situations. The probability of a PV panel failure is small due to the 20 years guarantee of PV panels given by most manufacturers. Unexpected partial shading is difficult to differentiate from expected partial shading due to for example flag poles. The loss of such a measurement method is probably of little significance.

The laboratory setup DC/DC-converter is designed to control the PV panel voltage  $\pm 20$  % of DC-link voltage. Being able to control in both directions is different from other publications about limited range voltage control. The power supply simulating the PV-panel has a maximum power output of 3 kW. However, the flyback topology does have power limitations. The converter is thus designed for a power output of 1.7 kW, but it was never tested at more than 1.2 kW. For a string of series-connected PV cells, this is a sufficient power output. It was also sufficient for the anti-islanding testing of the DG system.

In order to justify the use of a DC/DC-converter for MPPT, the efficiency must be high. MPPT is most useful where the PV panel voltage varies a lot, which is mainly a result of temperature variance. DC/DC-converters with limited range voltage control can give higher efficiencies and smaller sizes, but they put limitations on the number of seriesconnected PV cells in each string. In order to avoid large partial shading losses, independent control of every parallel string is best. The limited range voltage control DC/DC-converter is suitable for this application.

Chapter 3: Energy source modeling and control

# 4 Inverter modeling and simulation

The inverter is controlled using an observer. It is a model of the physical process (inverter, LCL-filter and grid). Developing a good model of the inverter including the LCL-filter and the grid is therefore important. This chapter describes the applied mathematical models. The models are developed in the continuous time domain, and then implemented in the discrete time domain.

Due to the dual function of the inverter (both grid-connected and standalone), the filter cannot be an L-filter, so an LCL-filter is chosen. This can handle diode-rectifier load, which cycles between nearly short-circuit and open-circuit during one fundamental frequency period. In order to block the 3rd harmonic current of a symmetric diode rectifier load, the neutral wire is left disconnected. The current DC component is neglected. Also the voltage DC component is neglected because line voltages, not phase voltages, are measured.

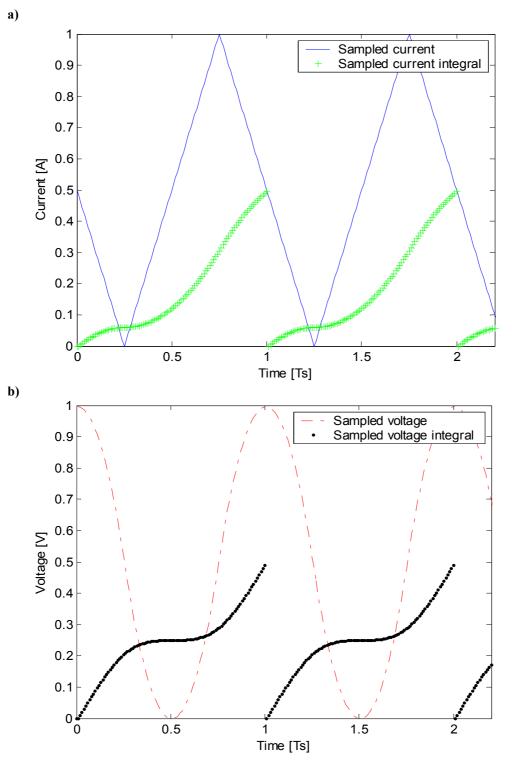

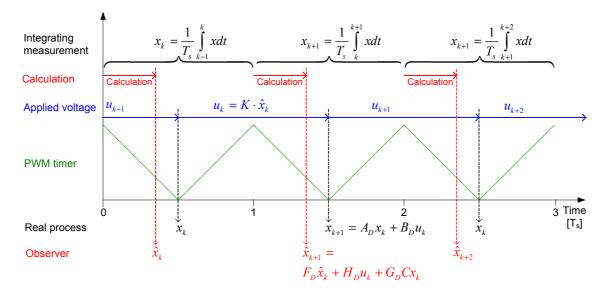

A method for cancelling undesirable effects of switching ripple in the measured variables is presented. Based on analog integration it introduces a time delay. This is more clearly defined compared to hall-effect sensors which have a phase shift. This measurement method is used for the fastest dynamics only, which are the LCL-filter measurements. Hall-effect sensors are used for the grid voltage measurements which contain less switching ripple.

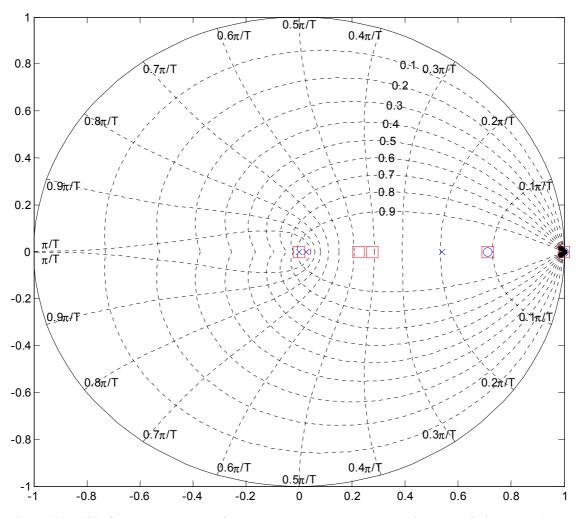

All models presented are based on the stationary frame. The models are presented starting from the LCL-filter, and eventually including a 3-phase grid model. Observability is verified, and the discretization method of the model and the observer is presented. Matlab/simulink models are used for verifying the discrete observer.

## 4.1 Inverter

A grid connected inverter is necessary in all DG including a DC energy source (photovoltaic panels, fuel cells or rectified AC in for example wind turbines). The most common topology is a 2-level voltage source inverter (VSI), as shown in Figure 30.

Figure 30: Voltage-source inverter topology with an LCL-filter.

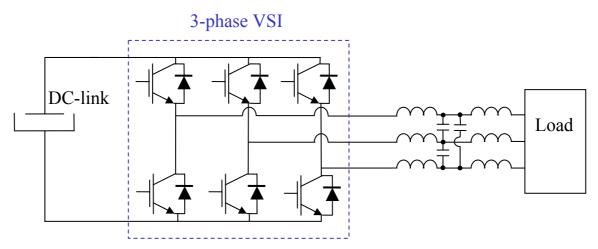

The VSI has many possibilities concerning functionality due to its fast response. Its main objective in this thesis is to run both standalone and grid connected. The VSI is connected to the 3-phase grid without the use of a transformer, but only using an LCL-filter.

#### 4.1.1 LCL-filter

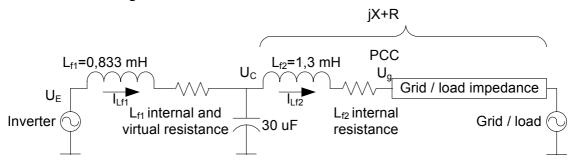

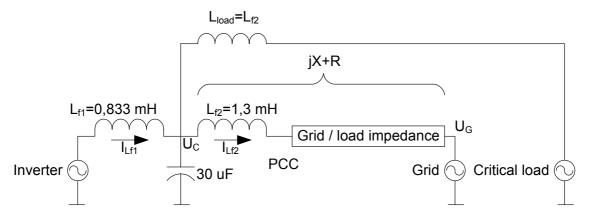

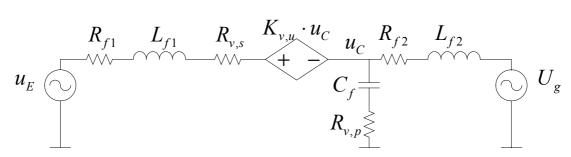

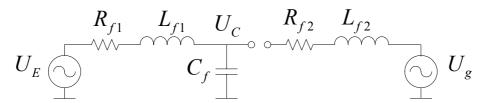

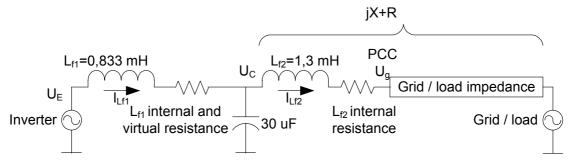

The purpose of the LCL-filter is to block the switching frequency, but pass the 50 Hz component. The inductor closest to the VSI should pass some low-order harmonics (3rd, 5th and 7th) in order to mirror the grid voltage at the filter capacitor. The LCL-filter was designed to supply a diode-rectifier load, which consumes harmonic currents. The filter should not have too large inductors. On the other hand it should be sufficiently large for the 10 kHz digital controller to reject the LCL-filter resonance satisfactorily. The LCL-filter is shown in Figure 31.

Figure 31: The inverter and the LCL-filter used for grid connection.  $L_{f1}$  is 2.47 % in pu, and  $L_{f2}$  is 3.85 % in pu.  $C_f$  produces 0.1 pu of reactive power under nominal conditions.

The LCL-filter should have low losses, equivalent with a high quality factor Q. The resonance peak must then be damped by the digital controller. In order to do so, the

resonance frequency must be within the bandwidth of the controller. The resonance frequency must be lower than half the sampling frequency, which in this case equals the switching frequency. For open-circuited operation, the LCL-filter resonance frequency is given by

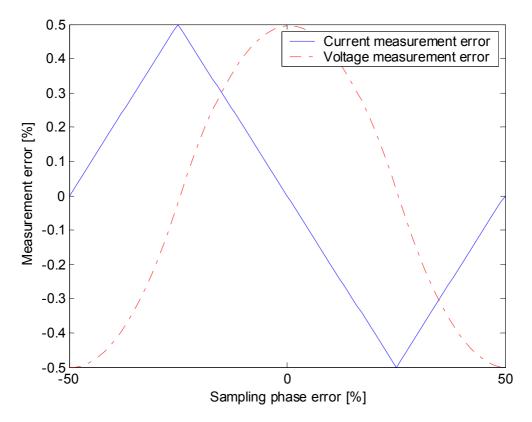

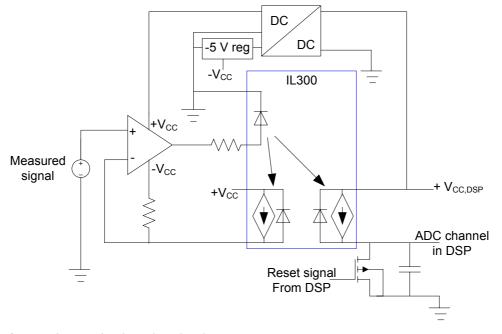

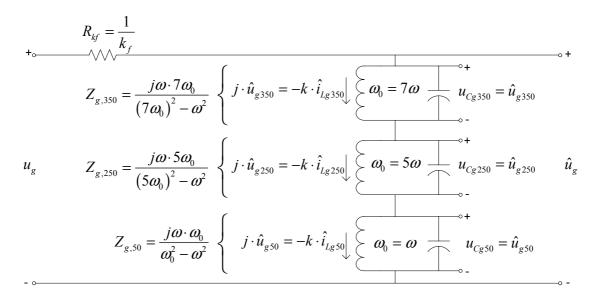

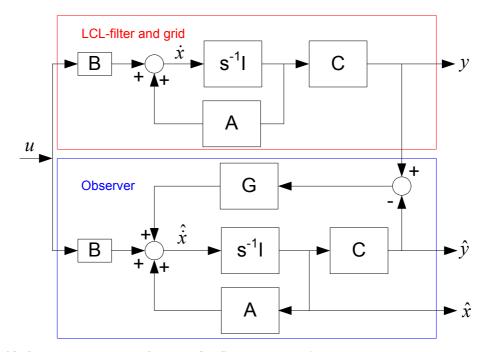

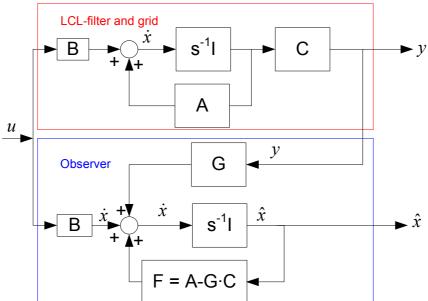

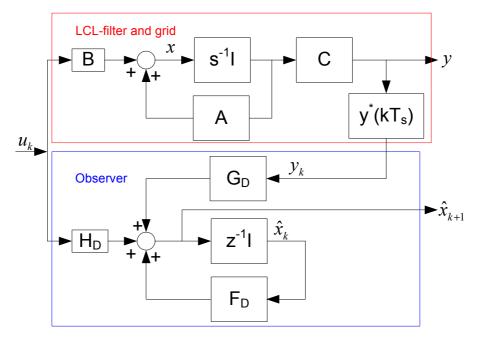

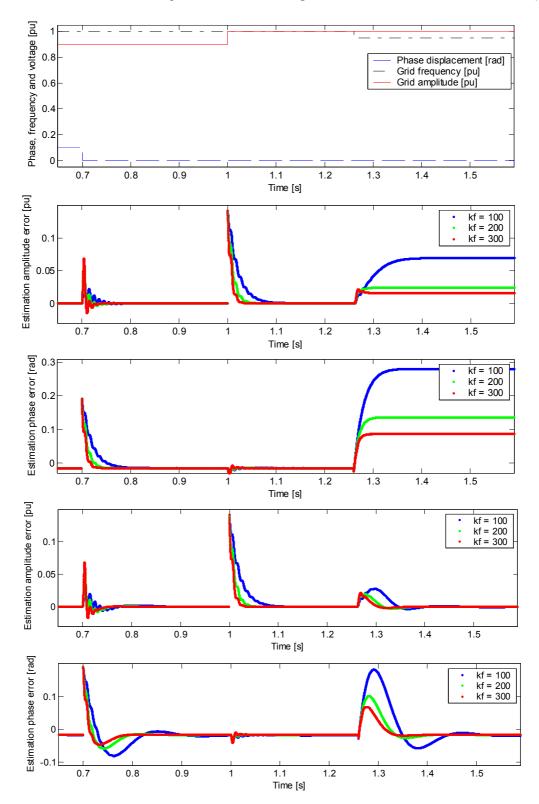

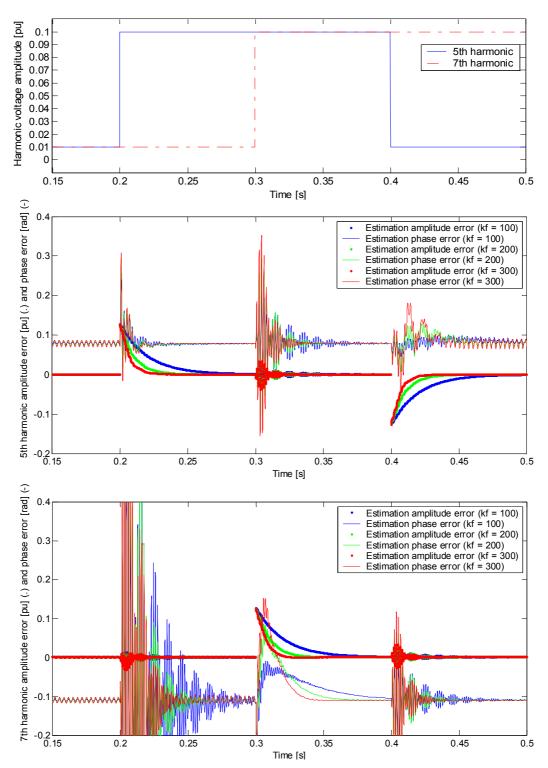

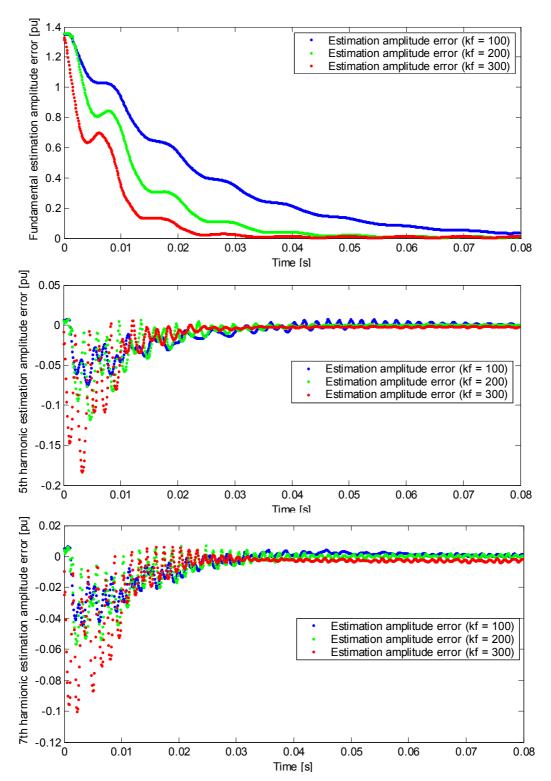

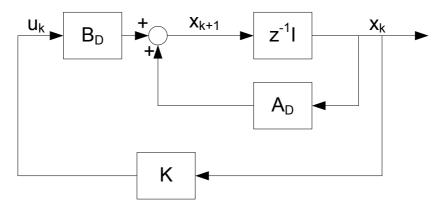

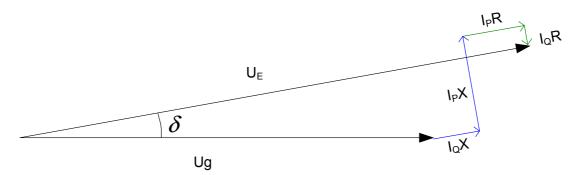

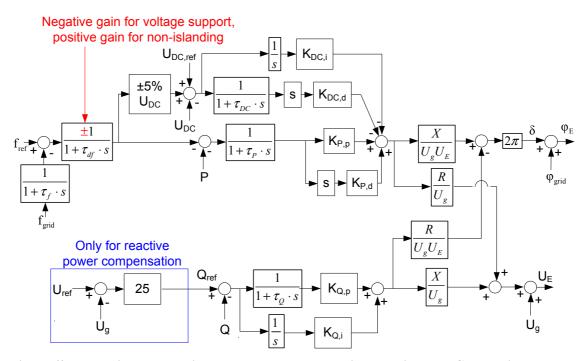

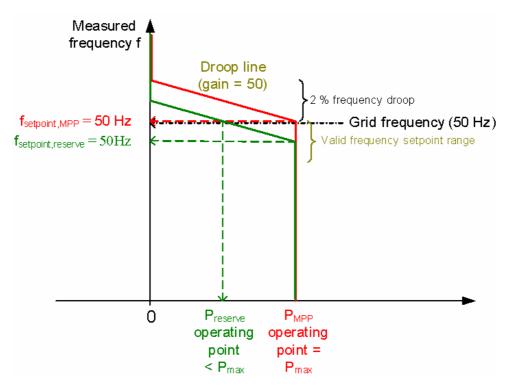

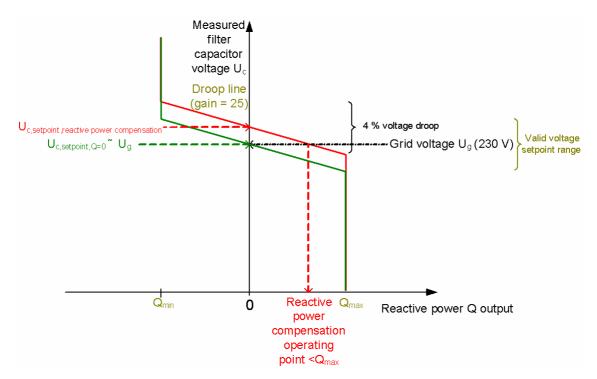

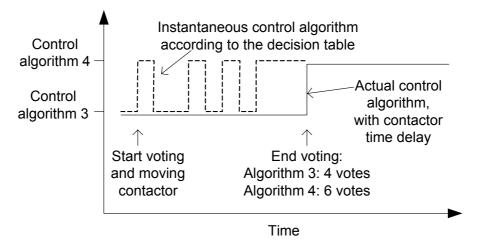

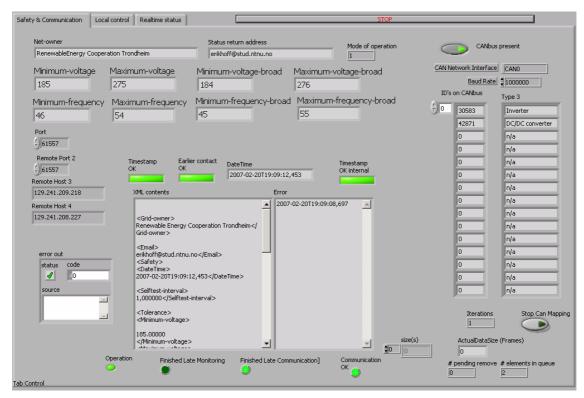

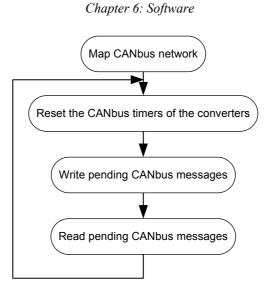

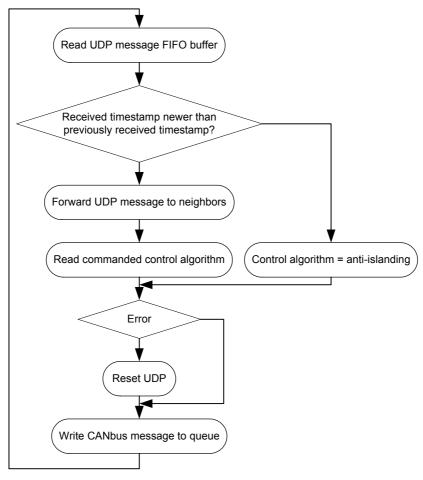

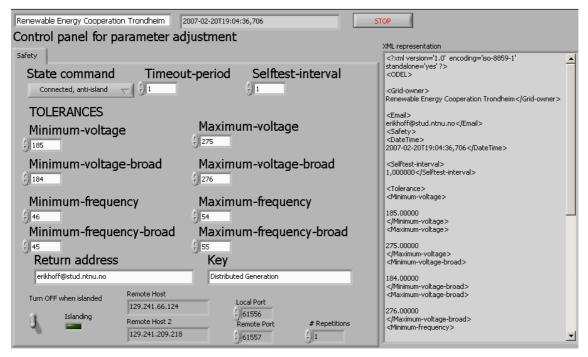

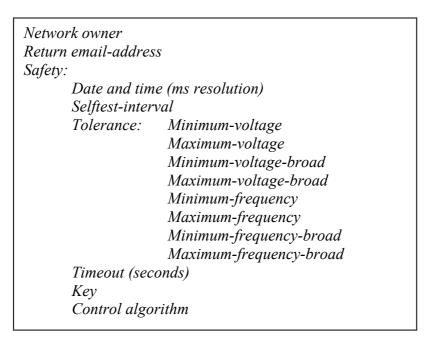

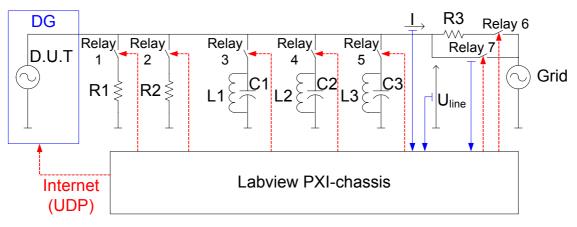

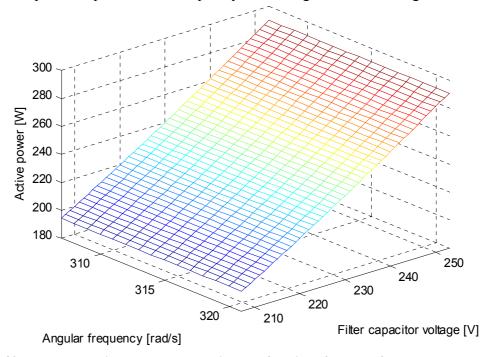

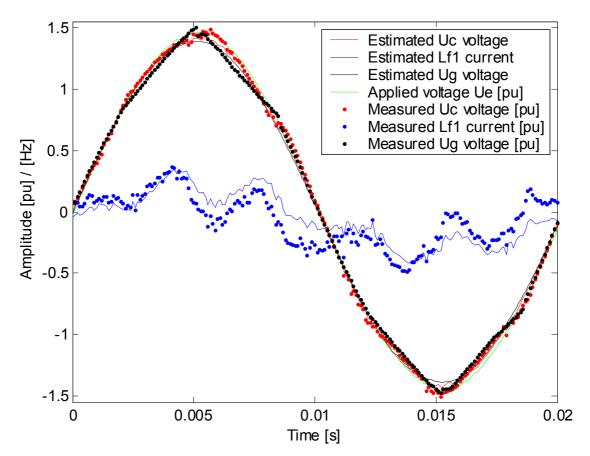

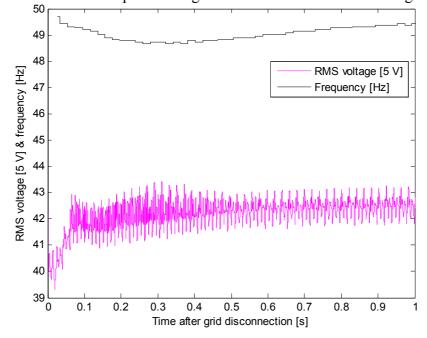

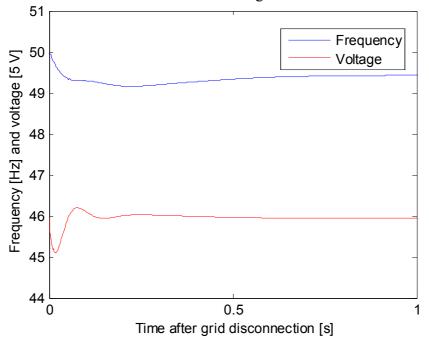

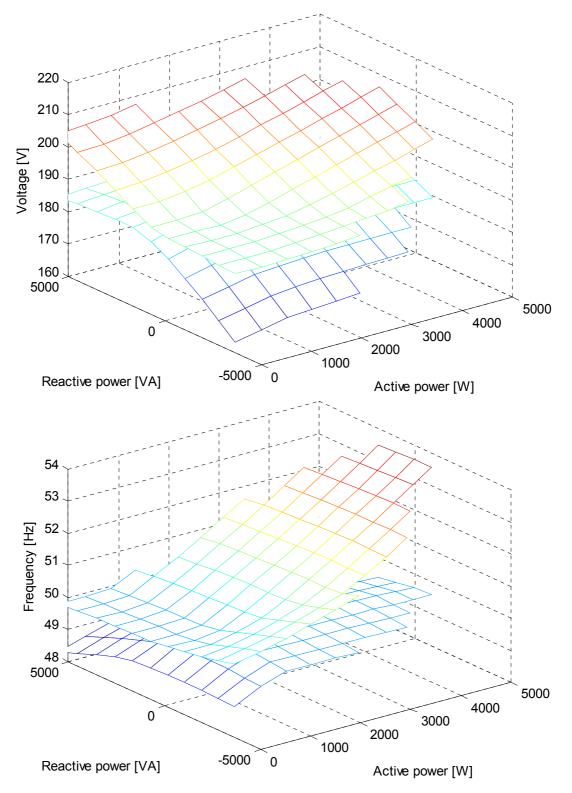

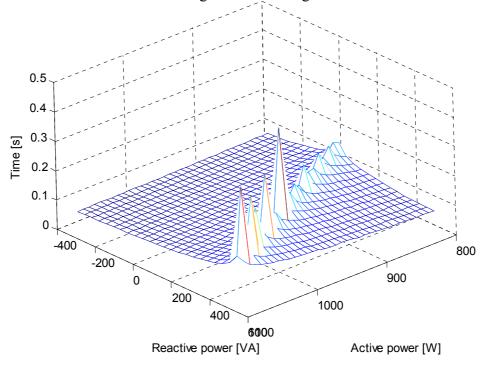

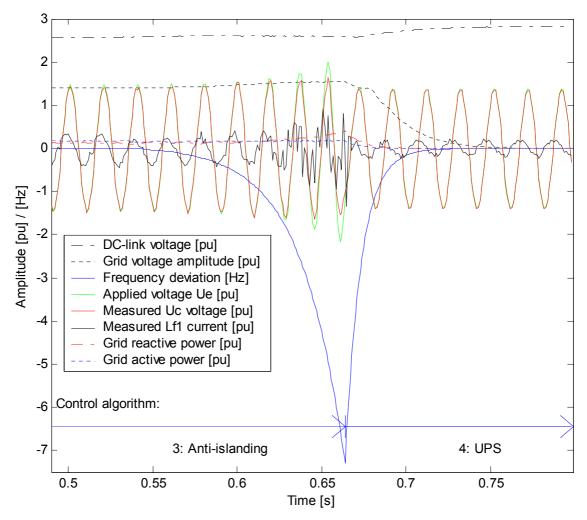

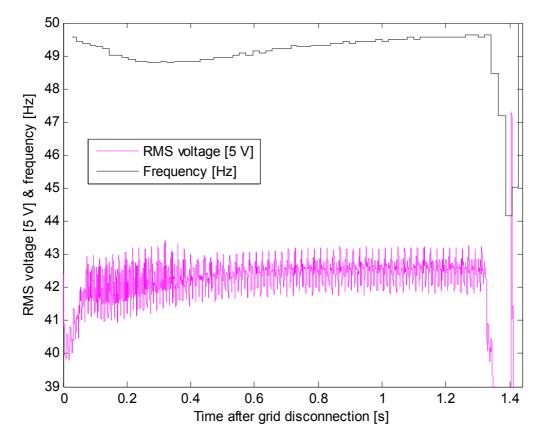

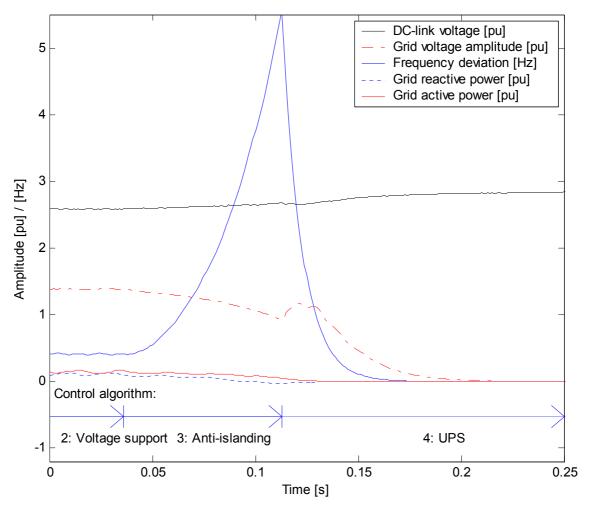

$$f_{0,LCL,OC} = \frac{1}{2 \cdot \pi \sqrt{L_{f1} \cdot C_f}} \tag{4.1}$$