Noise Tolerant Voltage-Controlled LC Oscillator Circuits for Deep Submicron VLSI System-on-a-Chip Radio Circuits

by

Jukka Typpö

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOKTOR INGENIØR

July 31, 2003

# Abstract

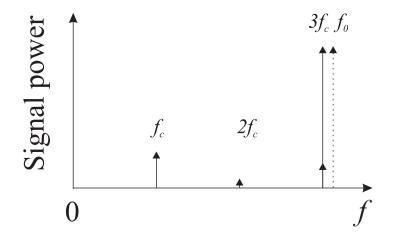

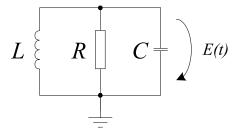

This thesis studies the problems with maintaining the spectral purity of fully integrated VCO circuits for radio frequency synthesizers in single-chip system designs. *LC* tank circuit oscillator circuits are shown to convert amplitude variation in the tank circuit voltage into frequency modulation, if voltage dependent capacitances are present in the tank circuit. Since the parasitic capacitances of the gain transistors and the capacitance of the varactor device in a VCO circuit are voltage dependent, any interfering signal, that is able to modulate the amplitude of the VCO tank circuit voltage waveform, is converted to FM sidebands in the output signal spectrum. It is also shown that the AM-FM conversion may be prohibited under some conditons.

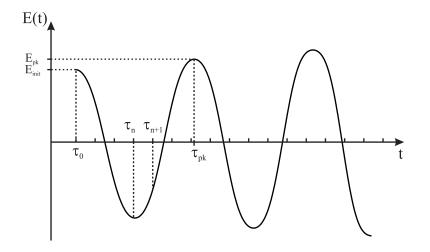

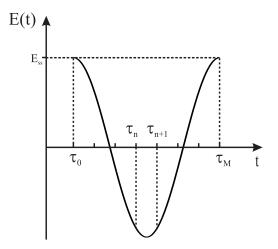

A new method for simulating the steady-state voltage waveform of an LC tank circuit oscillator is presented. In this method, one complete oscillation cycle is simulated piecewise, employing the known solution of the damped harmonic motion equation. The voltage-dependent parameters of the equation are updated in the beginning of each segment. The steady state is found by matching the initial conditions and the final conditions of one complete oscillation cycle, using a numerical optimization algorithm. The method avoids finding the solution of the differential equation with variable coefficients.

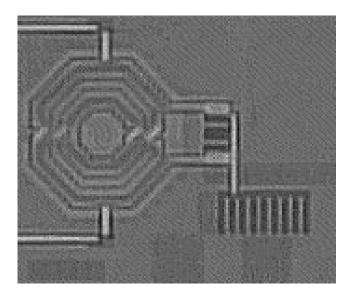

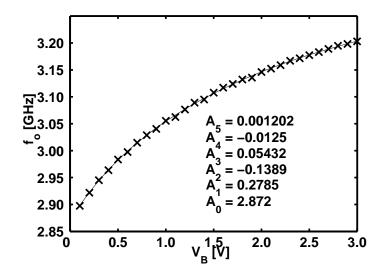

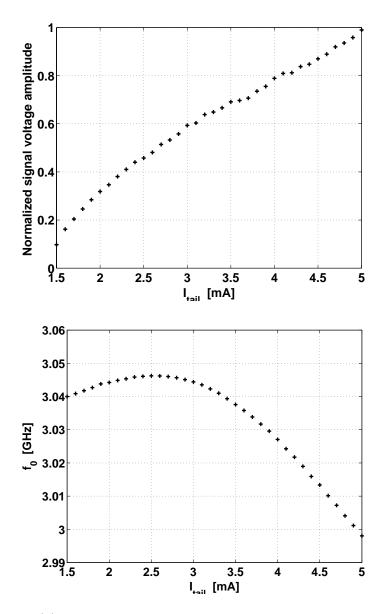

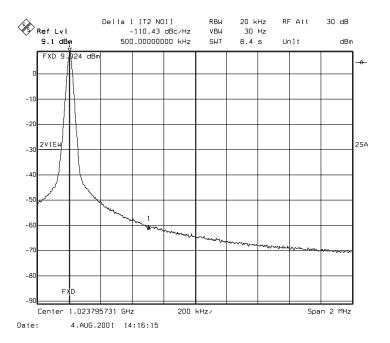

For minimizing the sensitivity of integrated VCO circuits to the intra-chip noise sources, this work proposes minimizing the AM-FM conversion by designing the VCO in the way that the voltage dependent capacitances of the oscillator core circuit are made to cancel each other's effects on the oscillation frequency at some amplitude level. Experimental results demonstrate 15 dB suppression of the sidebands due to the modulated tail current noise in a negative- $G_m$  spiral inductor PFET VCO circuit. The varactorless prototype circuit is implemented in a 0.35  $\mu m$  CMOS technology. The measured tuning range of the 3 GHz back gate tuned VCO circuit is 10 %, and the current consumption of the core circuit is 2.5 mA. The phase noise level is -110 dBc at 500 kHz offset frequency. The last part of this thesis discusses the problems with modeling and characterizing small MOS transistors, and presents characterization of 28  $\mu m$  wide MOSFSET devices. A new method for extracting the drain and source electrode resistances from the measured  $Z_{22}$  response is presented. The response is measured at a constant and very low signal frequency, with  $V_{ds} = 0 V$  and with various gate-source bias voltage values. At low signal frequencies, the equivalent diagram of the MOSFET is dramatically simplified, since all parasitic capacitors of the device may be ignored. Consequently, the number of degrees of freedom in the curve fitting is reduced to only two.

ii

# Acknowledgements

First, I would like to thank Professor Trond Sæther for giving me the opportunity to work on this interesting research field, and being an exellent supervisor. I also would like to thank Professor Mohammed Ismail, who invited me to visit The Ohio State University.

I am grateful for the co-operation with my fellow Ph.D. student Mikael Hammer, who also worked intensively on RF CMOS problems at The Department of Telecommunications, and designed two CMOS prototype chips with me. Discussions and correspondence Professors Trond Ytterdal, Timo Rahkonen and Arne Rønnekleiv have stimulated many of the ideas presented in this thesis.

I was also lucky enough to work with many people who may not directly have contributed to the contents of my writing, but helped me in getting where I wanted to go. Thomas Diefenbaugh provided me excellent computer support during my visit in Columbus. Tormod Njølstad and Johnny Pihl have contributed with stimulating discussions and helping with many computer-related problems here in Trondheim. Shevana Bianca Aquariux, Snorre Aunet, Sverre Pettersen, Lucero Alvarez, and all my other fellow Ph.D. students and the employees at the Department of Physical Electronics have provided me nice working atmosphere and positive social contributions that I will not forget. My friends, and members of Akademisk Radioklubb and Dykker-Gruppa NTNUI, have contributed with many relaxing minutes, hours, days, and weeks. Without my friends and free-time activities, I would not have been able to complete this work. Finally, I would like to thank my mother and my father for the patiency and support they have showed during these years.

This work has been financed by the Research Council of Norway.

ACKNOWLEDGEMENTS

# Contents

| Abstract                    |                                                 |         |                                                      | i   |

|-----------------------------|-------------------------------------------------|---------|------------------------------------------------------|-----|

| A                           | ckno                                            | wledge  | ments                                                | iii |

| 1                           | Introduction                                    |         |                                                      | 1   |

|                             | 1.1                                             | Intra-o | chip Noise Coupling in Single Chip Systems           | 3   |

|                             | 1.2                                             | Resear  | ch Problem                                           | 4   |

|                             | 1.3                                             | Main (  | Contributions                                        | 5   |

|                             | 1.4                                             | Thesis  | Outline                                              | 6   |

| <b>2</b>                    | VLS                                             | SI Pro  | cesses for SoC Applications                          | 9   |

|                             | 2.1                                             | Techno  | blogy Choice                                         | 10  |

|                             |                                                 | 2.1.1   | Silicon-on-Insulator                                 | 11  |

|                             |                                                 | 2.1.2   | SiGe HBT BiCMOS                                      | 14  |

|                             |                                                 | 2.1.3   | CMOS                                                 | 17  |

|                             | 2.2                                             | Design  | n Tools                                              | 20  |

|                             | 2.3                                             | Parasi  | tics                                                 | 21  |

|                             | 2.4                                             | Conclu  | isions                                               | 21  |

| 3 Intra-chip Noise Coupling |                                                 |         | Noise Coupling                                       | 25  |

|                             | 3.1                                             | Supply  | Voltage Noise                                        | 25  |

|                             | 3.2                                             | Comm    | on Return Path                                       | 27  |

|                             | 3.3                                             | Induct  | ive and Capacitive Coupling                          | 28  |

|                             | 3.4 Interference Coupling Through the Substrate |         |                                                      | 28  |

|                             |                                                 | 3.4.1   | Signal Coupling from the On-Chip Interference Source |     |

|                             |                                                 |         | to the Substrate                                     | 30  |

|                             |                                                 | 3.4.2   | Interference Coupling from the Substrate to the Vic- |     |

|                             |                                                 |         | tim Circuit                                          | 31  |

|                             |                                                 | 3.4.3   | Methods for Reducing the Substrate Noise Couping     | 32  |

|                             |                                                 | 3.4.4   | Substrate Noise Analysis Methods                     | 32  |

|                             | 3.5                                             | Conclu  | isions                                               | 33  |

# CONTENTS

| 4        | Interference Conversion in the VCO |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |

|----------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

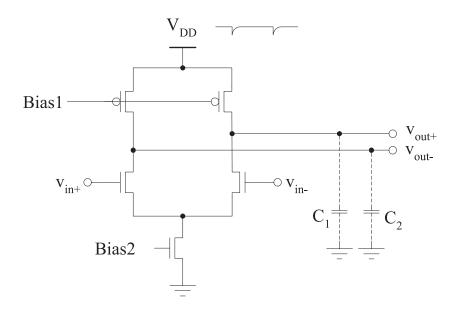

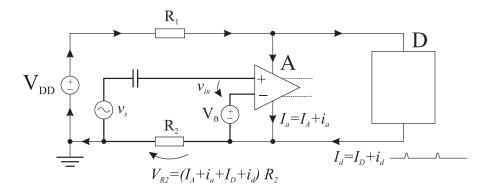

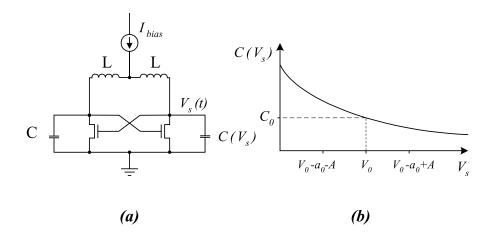

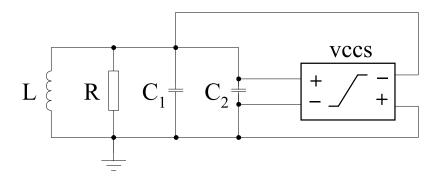

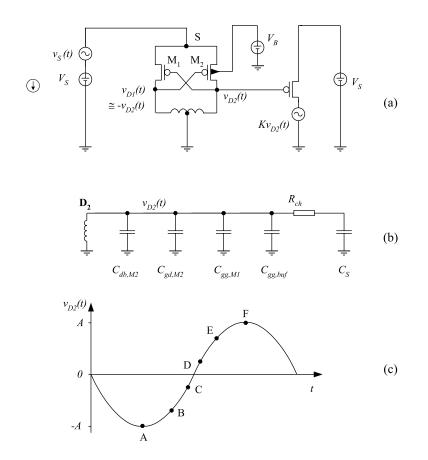

|          | 4.1                                | Negative- $G_m$ VCO Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36 |  |

|          | 4.2                                | Amplitude Modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38 |  |

|          | 4.3                                | Frequency Modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41 |  |

|          | 4.4                                | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43 |  |

|          | 4.5                                | Injection Locking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |  |

|          | 4.6                                | Noise Coupling from the Substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45 |  |

|          | 4.7                                | Noise Coupling Inside the VCO Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45 |  |

|          | 4.8                                | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47 |  |

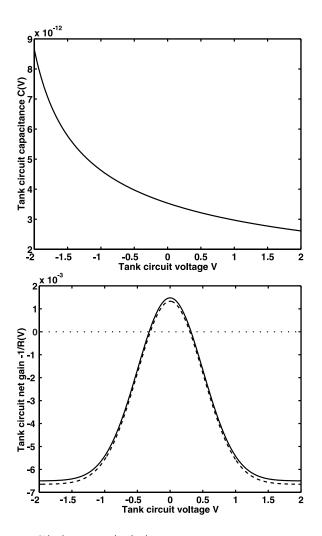

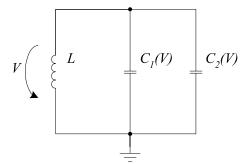

| <b>5</b> | Los                                | ossy Tank Circuit Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |

|          | 5.1                                | LRC Circuit Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50 |  |

|          | 5.2                                | LC Oscillator Steady-state Voltage Waveform $\hfill \hfill \hfil$ | 52 |  |

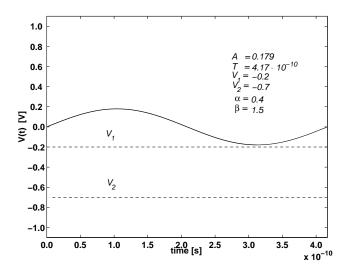

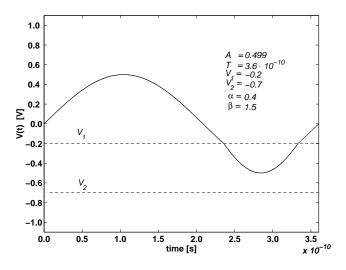

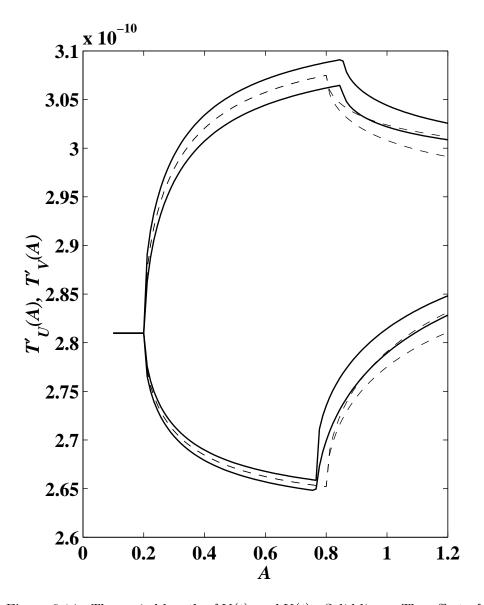

|          | 5.3                                | Simulating The $LC$ Oscillator Steady State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |  |

|          | 5.4                                | Simulation Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56 |  |

|          | 5.5                                | Other Methods for Simulating $LC$ Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 56 |  |

|          | 5.6                                | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59 |  |

| 6        | Vol                                | tage Dependent Capacitances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61 |  |

|          | 6.1                                | Piecewise Sinusoidal Waveform Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62 |  |

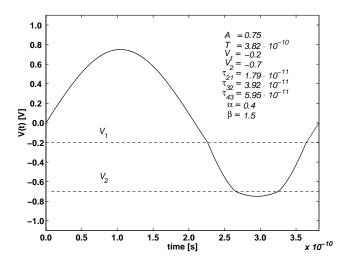

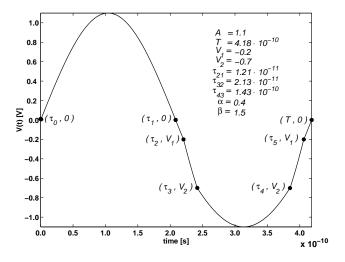

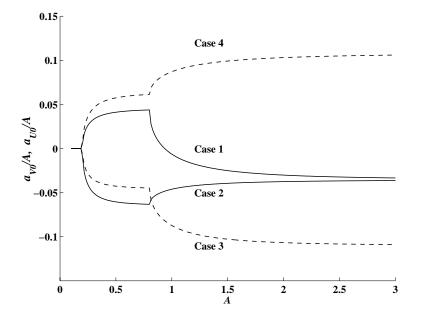

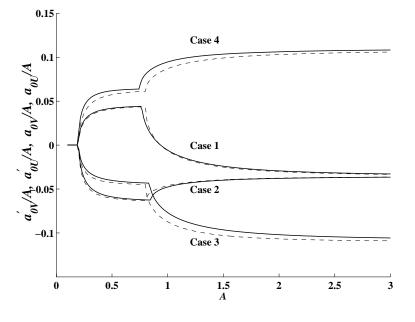

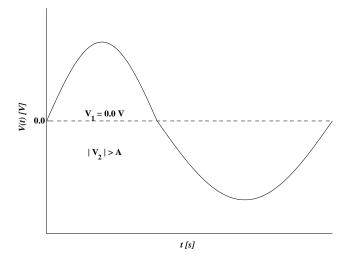

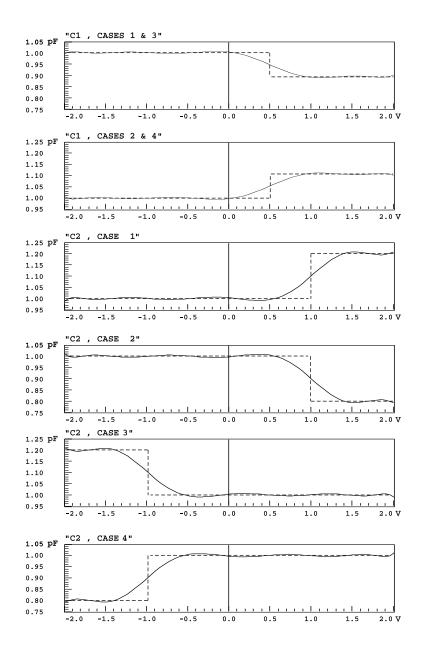

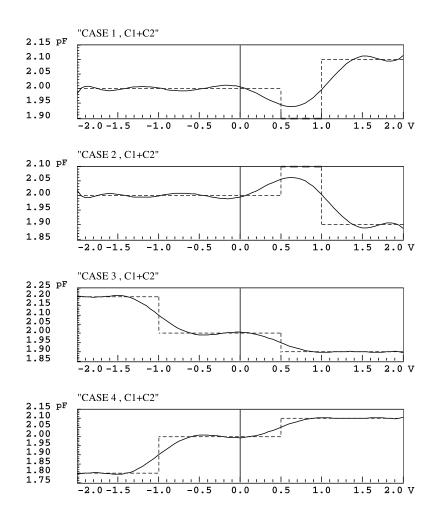

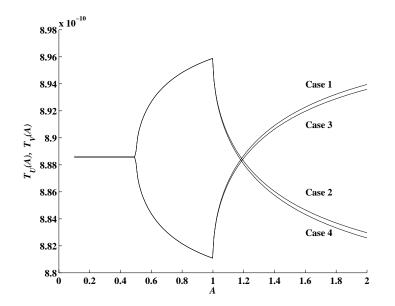

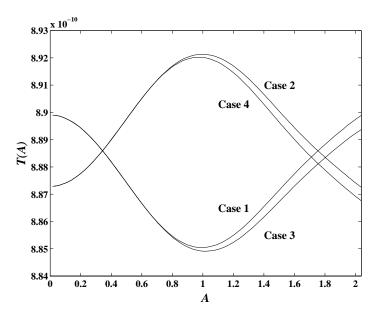

|          |                                    | 6.1.1 Case 1: $V_1 \cdot V_2 > 0$ , $\alpha < 1$ and $\beta > \alpha$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66 |  |

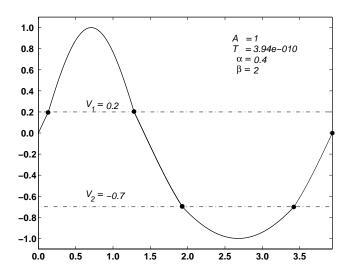

|          |                                    | 6.1.2 Case 2: $V_1 \cdot V_2 > 0$ , $\alpha > 1$ and $\beta < \alpha$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70 |  |

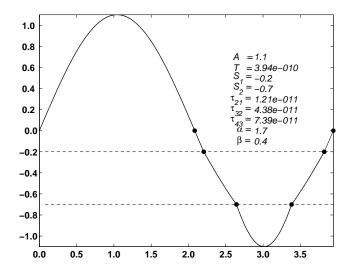

|          |                                    | 6.1.3 Case 3: $V_1 \cdot V_2 < 0$ , $\alpha < 1$ and $\beta > \alpha \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 71 |  |

|          |                                    | 6.1.4 Case 4: $V_1 \cdot V_2 < 0$ , $\alpha > 1$ and $\beta < \alpha$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 72 |  |

|          | 6.2                                | Parameters $\alpha$ and $\beta$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72 |  |

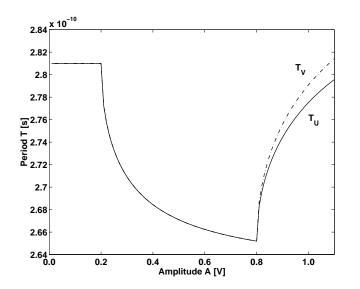

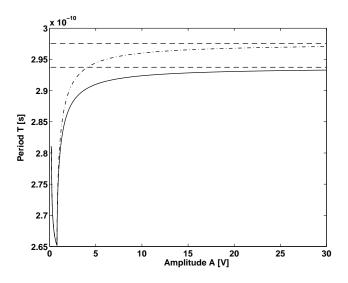

|          | 6.3                                | Period Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 74 |  |

|          | 6.4                                | DC Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |  |

|          | 6.5                                | Limits of the Parameter Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 86 |  |

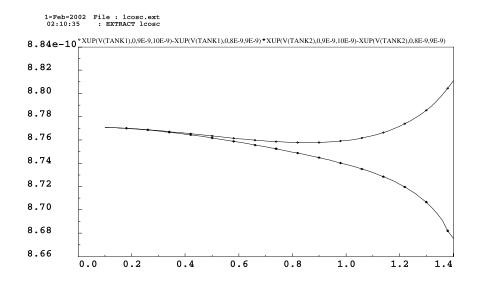

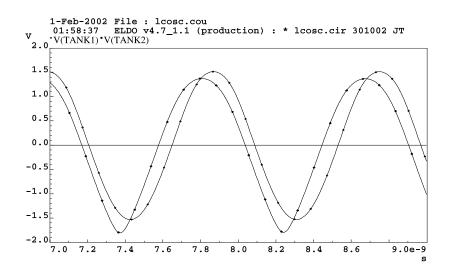

|          | 6.6                                | Comparison with Simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 90 |  |

|          | 6.7                                | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 97 |  |

| 371   |  |

|-------|--|

| - V I |  |

## CONTENTS

| C                        | ONTI                             | ENTS   |                                                                                                  | 1     |

|--------------------------|----------------------------------|--------|--------------------------------------------------------------------------------------------------|-------|

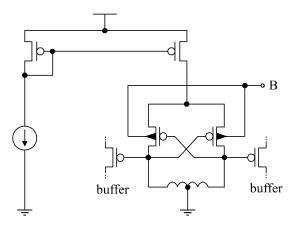

| 7                        | PFI                              | ET VC  | CO in an n-well Technology                                                                       | 99    |

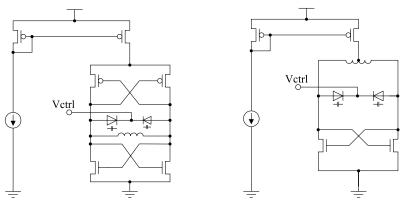

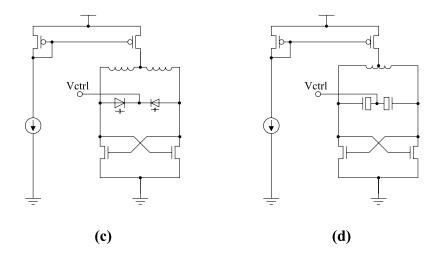

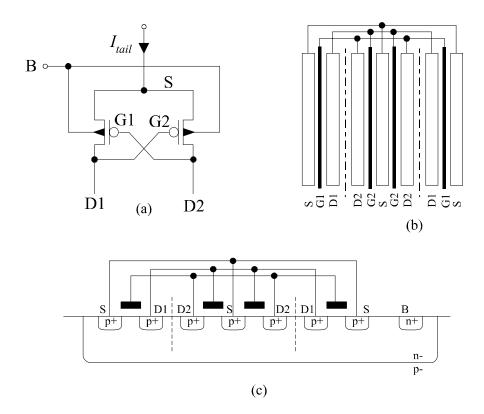

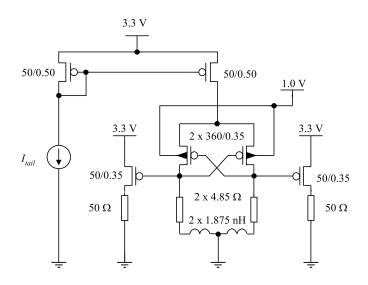

|                          | 7.1                              | Back   | Gate Tuned PFET VCO Circuit                                                                      | 101   |

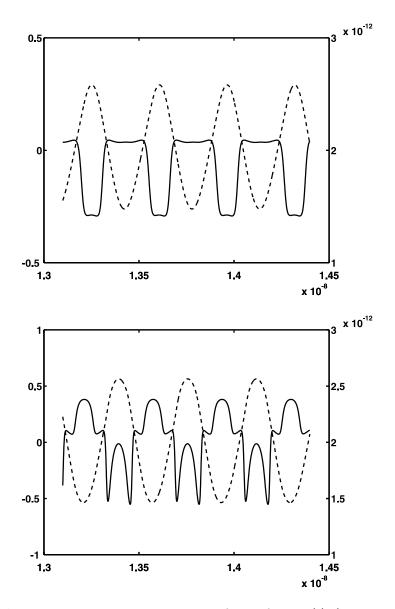

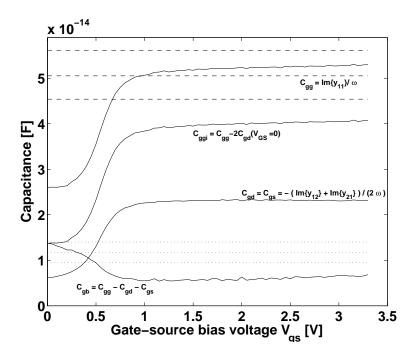

|                          | 7.2                              | Voltag | ge Dependent Parasitic Capacitances                                                              | 102   |

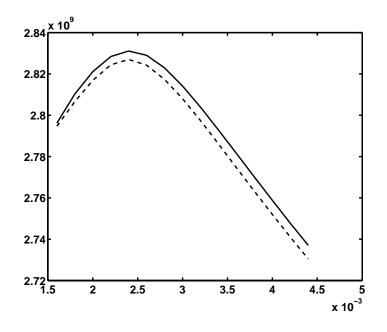

|                          | 7.3                              | Quasi  | -static Transient Simulations                                                                    | 106   |

| 7.4 Experimental results |                                  |        | imental results                                                                                  | 109   |

|                          | 7.5                              | Concl  | usions                                                                                           | 117   |

| 8                        | Characterizing Small MOSFETs 119 |        |                                                                                                  | 119   |

|                          |                                  | 8.0.1  | DUT Stability During the S-parameters Measurement                                                | t 121 |

|                          |                                  | 8.0.2  | Problems with Characterizing Small MOSFET Device                                                 | es122 |

|                          | 8.1                              | Model  | ling the Small-signal MOSFET Operation                                                           | 125   |

|                          |                                  | 8.1.1  | Modeling the Gate and Channel as a Double Distrib-                                               |       |

|                          |                                  |        | uted RC Transmission Line                                                                        | 126   |

|                          |                                  | 8.1.2  | MOSFET Gate Capacitor with Two Resistive Elec-                                                   |       |

|                          |                                  |        | trodes $\ldots$ | 127   |

|                          |                                  | 8.1.3  | Quasi-static MOSFET Small Signal Model with Ex-                                                  |       |

|                          |                                  |        |                                                                                                  | 101   |

| 8            | Cha  | racteri                | zing Small MOSFETs                                                   | 119 |

|--------------|------|------------------------|----------------------------------------------------------------------|-----|

|              |      | 8.0.1                  | DUT Stability During the S-parameters Measurement                    |     |

|              |      | 8.0.2                  | Problems with Characterizing Small MOSFET Device                     |     |

|              | 8.1  |                        | ing the Small-signal MOSFET Operation                                | 125 |

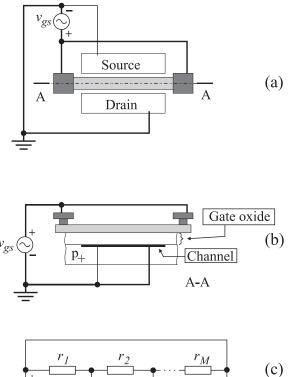

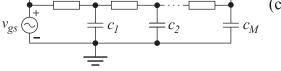

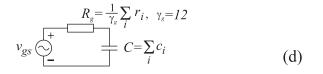

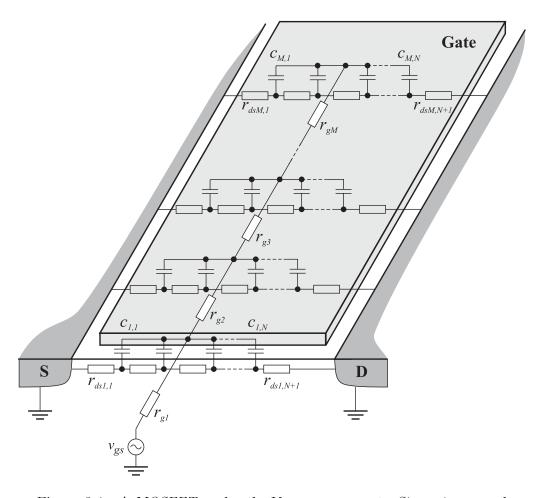

|              | -    | 8.1.1                  | Modeling the Gate and Channel as a Double Distrib-                   | -   |

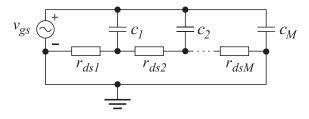

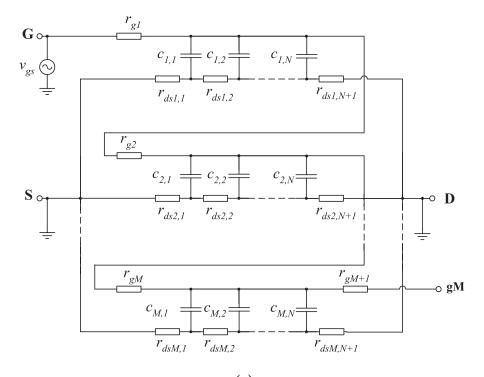

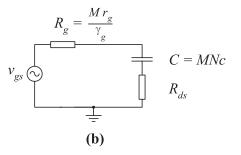

|              |      | 0                      | uted RC Transmission Line                                            | 126 |

|              |      | 8.1.2                  | MOSFET Gate Capacitor with Two Resistive Elec-                       |     |

|              |      |                        | trodes                                                               | 127 |

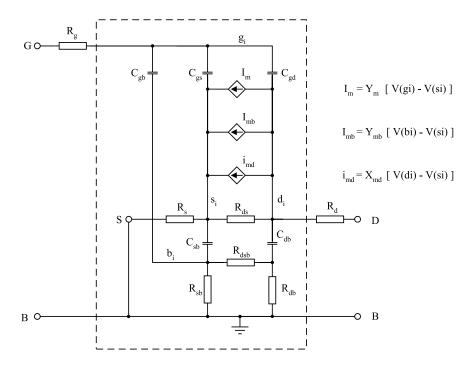

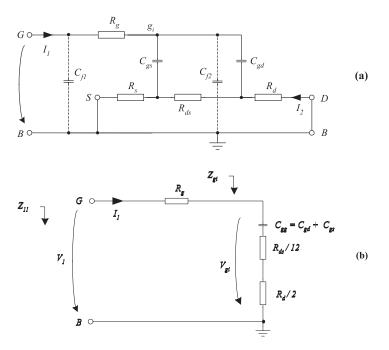

|              |      | 8.1.3                  | Quasi-static MOSFET Small Signal Model with Ex-                      |     |

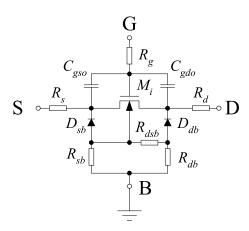

|              |      |                        | ternal Lumped Parasitics                                             | 134 |

|              |      | 8.1.4                  | Input Capacitance of the Common Source Stage                         | 136 |

|              |      | 8.1.5                  | Gate-Drain Capacitance in the Linear Region and                      |     |

|              |      |                        | Strong Inversion                                                     | 139 |

|              |      | 8.1.6                  | Gate-bulk Capacitance                                                | 141 |

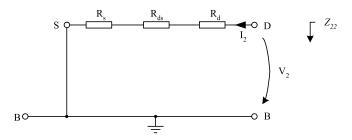

|              |      | 8.1.7                  | Drain and Source Resistances                                         | 141 |

|              |      | 8.1.8                  | Gate Resistance                                                      | 143 |

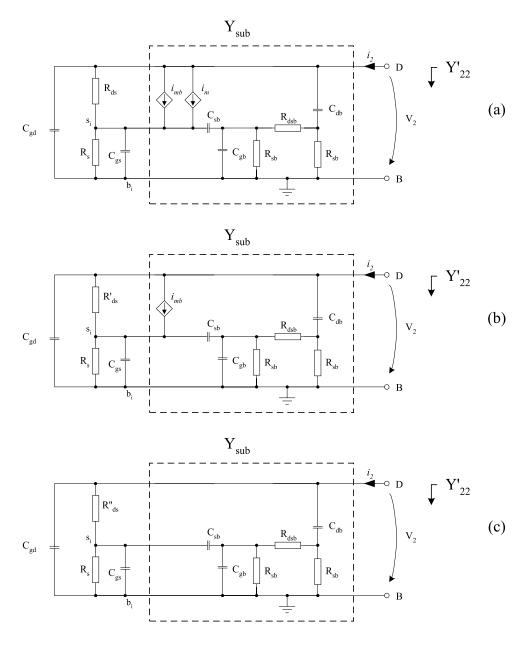

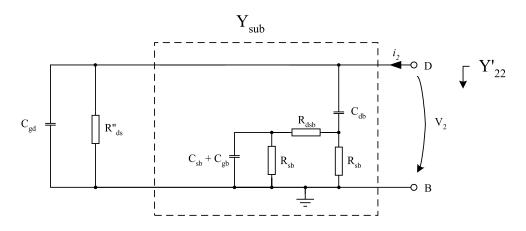

|              |      | 8.1.9                  | Substrate Network                                                    | 144 |

|              |      | 8.1.10                 | Reliable Parameters Extraction                                       | 147 |

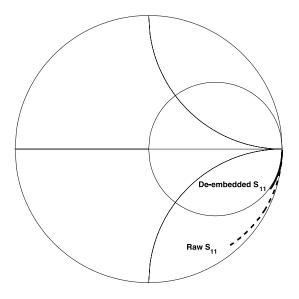

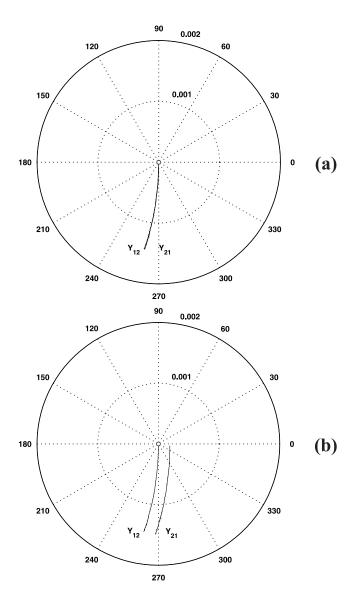

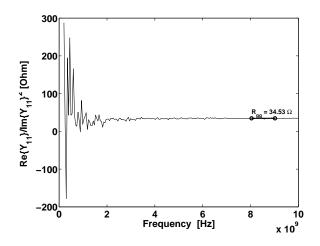

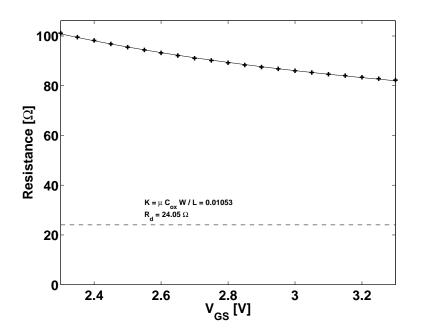

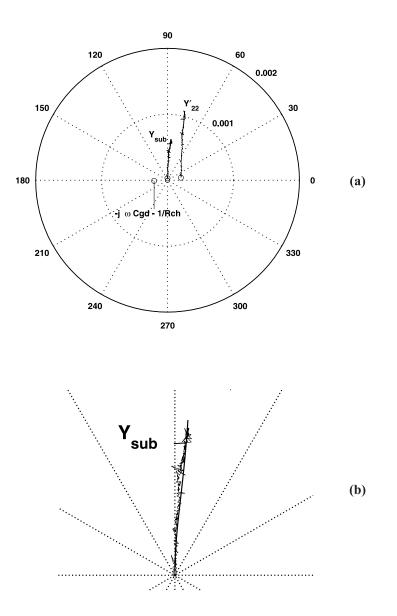

|              | 8.2  | 2 Experimental Results | 148                                                                  |     |

|              |      | 8.2.1                  | MOSFET Measurement Setup                                             | 149 |

|              |      | 8.2.2                  | Parameters Extraction Results                                        | 150 |

|              | 8.3  | Conclu                 | usions                                                               | 158 |

| 9            | Con  | clusior                | lS                                                                   | 161 |

| ٨            | Don  | anad E                 | Iarmonic Motion Equation                                             | 163 |

| A            | Dan  | iipeu 1                | la nome motion Equation                                              | 105 |

| В            | Sim  | ulating                | $ {\rm the} \ LC \ {\rm Oscillator} \ {\rm Steady} \ {\rm State} \\$ | 167 |

| $\mathbf{C}$ | Piec | ewise                  | Sinusoidal Voltage Waveform Model                                    | 179 |

|              |      | C.0.1                  | Cases 1 and 2: Only one side of the waveform is                      |     |

|              |      |                        | distorted when $A >  V_2 $                                           | 179 |

|              |      | C.0.2                  | Cases 3 and 4: Both sides of the waveform are dis-                   |     |

|              |      |                        | torted when $A >  V_2  \dots \dots \dots \dots \dots \dots$          | 183 |

1

CONTENTS

# Chapter 1

# Introduction

During the recent decades, commercially available digital MOSFET integrated circuits (ICs) have developed from relatively simple integrated logic and memory circuits to systems that include tens of millions of transistors on the same chip. Employing digital CMOS technologies, or slightly modified versions of them, complex analog and mixed mode circuits have also been developed. For these reasons, CMOS has been the preferred VLSI (Very Large Scale Integration) semiconductor technology for more than two decades, especially for applications where low power consumption and low production cost, rather than the operation speed, are the main concerns. Due to this wide industrial use, CMOS technologies have also developed in very fast pace, compared to the other mature and widely used IC technologies, like circuits based on NMOS, bipolar, or GaAs transistors.

In addition to increasing the packaging density and the speed of the transistors, and decreasing the power consumption of the chip, the recent trend of semiconductor technology development has been to integrate analog signal processing, radio frequency (RF) circuits, microelectromechanical systems (MEMS), electro-optical, chemical, and biological functions together with digital circuits on the same piece of silicon [1]. For this purpose, the semiconductor technology that is used must also meet the special needs that these other system parts have. Despite of some limitations, CMOS technologies seem to have the potential to play a significant role also with these System-on-a-Chip (SoC) applications, since the production cost in large volumes is lower than with the current date alternatives.

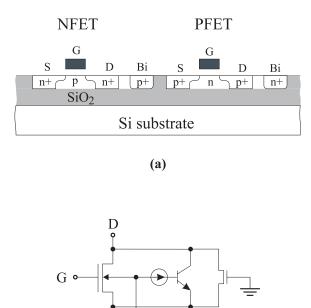

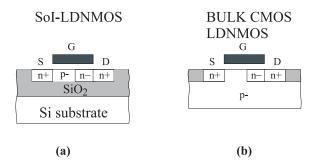

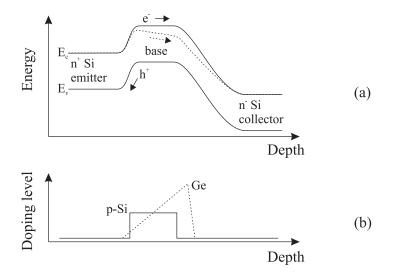

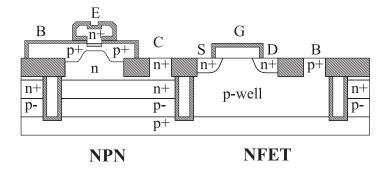

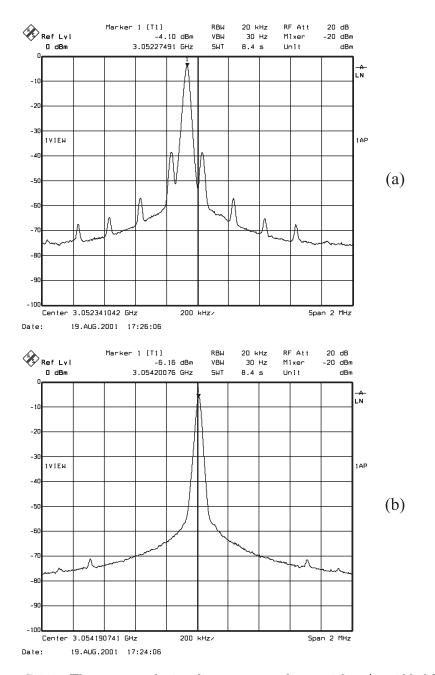

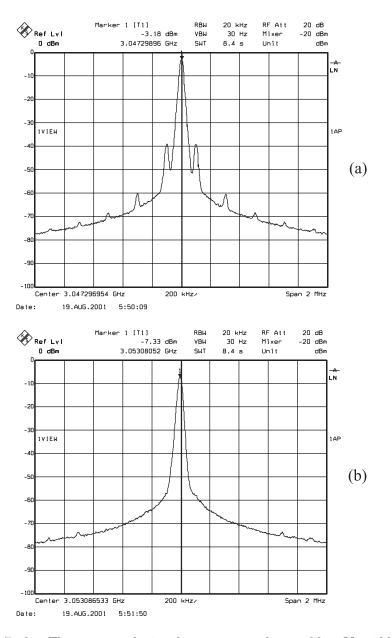

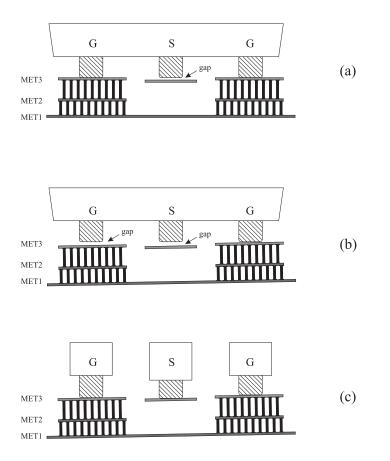

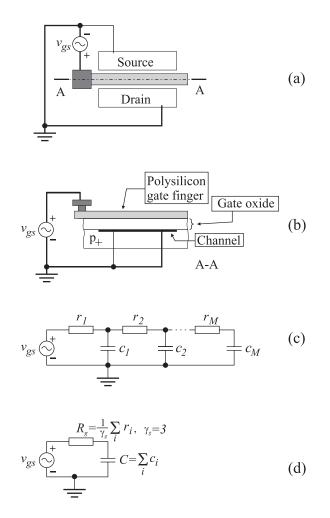

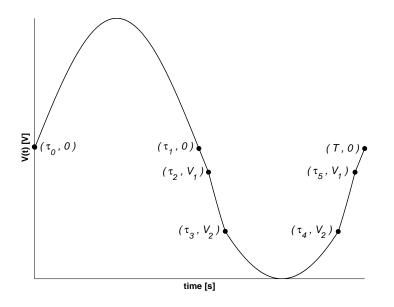

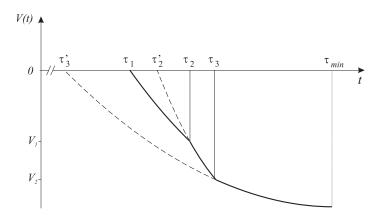

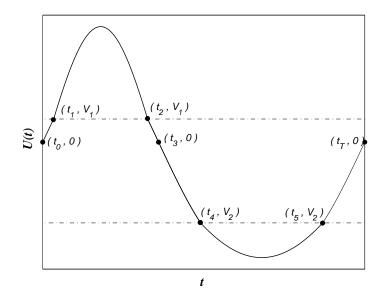

The practical problems and solutions of RF circuits design have traditionally been very different from the digital circuits design issues, since singlechip integration of systems, that employ wireless telecommunications, has not been feasible earlier. Dedicated RF engineers have designed the RF parts of systems like the mobile telephone. They have had the freedom of using their own design tools and design methods, and employing IC processes that are particularly suitable for RF circuit design. Since the trend of development now is single-chip systems, the RF engineers must use the same semiconductor IC process with the digital circuits designers, which forces the RF designers to tolerate some compromises. In most SoC designs, the digital system parts will cover the majority of the functionality and chip area. Therefore, the transistor properties in most available SoC semiconductor processes are optimized for digital, rather than for RF circuits design. On the other hand, the needs of the digital circuit designers have made the parasitic capacitances and the conductor resistances to decrease, which helps the RF circuit designer's work. Since single-chip system RF designers must use the same IC process as all other designers in the same project, they must accept the limitations that this brings, and try to employ design tools and design methods that the other designer communities have developed.