ISBN 978-82-326-2776-9 (printed ver.) ISBN 978-82-326-2777-6 (electronic ver.) ISSN 1503-8181

o ntnu

# Accelerating Sparse Linear Algebra and Deep Neural Networks on Reconfigurable

Yaman Umuroğlu

### Accelerating Sparse Linear Algebra and Deep Neural Networks on Reconfigurable Platforms

Thesis for the Degree of Philosophiae Doctor

Trondheim, April 2018

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Computer Science

#### NTNU

Norwegian University of Science and Technology

Thesis for the Degree of Philosophiae Doctor

Faculty of Information Technology and Electrical Engineering Department of Computer Science

© Yaman Umuroğlu

ISBN 978-82-326-2776-9 (printed ver.) ISBN 978-82-326-2777-6 (electronic ver.) ISSN 1503-8181

Doctoral theses at NTNU, 2018:1

Printed by NTNU Grafisk senter

### Abstract

Regardless of whether the chosen figure of merit is execution time, throughput, battery life for an embedded system or total cost of ownership for a datacenter, today's computers are fundamentally limited by their energy efficiency. Using specialized hardware-software solutions for particular applications or domains is a well-known approach to increase energy efficiency of computing systems. Reconfigurable logic in the form of Field-Programmable Gate Arrays (FPGAs) is a particularly promising substrate for hardware specialization, owing to its runtime reconfigurability, vastly parallel compute fabric and widespread availability. However, mapping computation to reconfigurable logic in a way which provides performance and efficiency benefits is a significant challenge due to the vast design space. In this thesis, we study how two particular domains can benefit from specialized architectures on reconfigurable logic. We focus on sparse linear algebra and deep neural network inference, whose execution is known to be particularly problematic on today's general-purpose computers.

For sparse linear algebra, lack of spatial and temporal locality in memory accesses pose a fundamental problem. We address this problem by taking advantage of the flexibility of reconfigurable logic to construct specialized memory systems. We propose a hardware-software caching scheme which uses lightweight preprocessing to extract key access pattern information from sparse matrices to offer greatly increased random access efficiency with minimal on-chip memory usage. Furthermore, we demonstrate the broader applicability of the specialization for sparse linear algebra to graph analytics with an accelerator for breadth-first search that uses off-chip memory bandwidth more efficiently compared to prior work.

For deep neural network inference, the sheer energy and hardware resource cost of floating point computation is a fundamental limitation on energy efficiency. Exploiting recent advances in training highly quantized neural networks (QNNs), we demonstrate how FPGAs can be leveraged for accurate, energy-efficient and high-performance neural network inference. We propose the FINN framework to generate customized architectures with compute resources tailored to user-specified performance requirements while exploiting multiple levels of parallelism for high energy efficiency. We also describe mathematical simplifications for making QNN inference more resource-efficient, and show how binary matrix operators can be used as bit-serial building blocks for higher-precision computation.

### Preface

This thesis is submitted in partial fulfilment of the requirements for the degree of *philosophiae doctor* (PhD) at the Norwegian University of Science and Technology (NTNU). It is a compilation thesis consisting of an introductory part, seven scientific articles and a concluding part, in accordance with Section 10.1 of the "Regulations for the Doctoral Degree at the Norwegian University of Science and Technology". The articles have been reformatted to keep the appearance of the thesis more consistent, but their scientific content is identical to the published versions.

Associate Professor Magnus Jahre was the main supervisor for the project, with Professor Per Gunnar Kjeldsberg and Doctor Asbjørn Djupdal as the co-supervisors. The research was funded internally by the university, and was carried out mainly at the NTNU Department of Computer Science in Trondheim, Norway and partially at Xilinx Research Labs in Dublin, Ireland.

### Acknowledgements

First and foremost, I would like to thank my advisor Associate Professor Magnus Jahre for his unwavering support, apt supervision and good advice. I left every single supervision meeting feeling better than how I came in, and I truly appreciate that he provided me with enough academic freedom to fly with my own wings. I am also extremely grateful to have had the opportunity to work with Michaela Blott during my internship at Xilinx Research Labs in Dublin. Her energy, enthusiasm and dedication are a major source of inspiration to me.

Next, a big round of thanks to my colleagues at the NTNU Computer Architecture Lab and at Xilinx Research Labs. From lunchtime discussions on emergent complexity to payday beers with idle banter, from Rammstein concerts to paper discussion colloquia, they have been an invaluable source of support for both my social wellbeing and my mental growth as a researcher.

And finally, the unspoken heroes of this thesis, whose names appear on no author list of any of my articles but who have made them possible with their endless patience, love and support. My most sincere and heartfelt thanks to my partner Håkon Marthinsen and my parents Betigül Umuroğlu and Fersal Umuroğlu.

> Yaman Umuroğlu Trondheim, 29th November 2017

### Contents

| Α. | A. Overview                                                         |    |  |  |  |

|----|---------------------------------------------------------------------|----|--|--|--|

| 1. | Introduction                                                        |    |  |  |  |

|    | 1.1. Dark Silicon and the Need for Accelerators                     | 3  |  |  |  |

|    | 1.2. Choice of Specialization Domains and Substrate                 | 5  |  |  |  |

|    | 1.3. Research Questions                                             | 6  |  |  |  |

|    | 1.4. Thesis Outline                                                 | 7  |  |  |  |

| 2. | Background                                                          | 9  |  |  |  |

|    | 2.1. Field-Programmable Gate Arrays                                 | 9  |  |  |  |

|    | 2.2. Hardware/Software Codesign                                     | 11 |  |  |  |

|    | 2.3. Implementing Field-Programmable Gate Array (FPGA) Accelerators | 11 |  |  |  |

|    | 2.4. Memory System Design                                           | 12 |  |  |  |

|    | 2.5. The Roofline Model                                             | 14 |  |  |  |

| 3. | Research Summary                                                    |    |  |  |  |

|    | 3.1. Overview                                                       | 17 |  |  |  |

|    | 3.2. Articles on Sparse Linear Algebra                              | 17 |  |  |  |

|    | 3.3. Articles on Deep Neural Networks                               | 21 |  |  |  |

|    | 3.4. Other Articles                                                 | 23 |  |  |  |

| B. | Sparse Linear Algebra                                               | 29 |  |  |  |

| 1. | Introduction                                                        | 31 |  |  |  |

| •• | 1.1. On Sparsity                                                    | 31 |  |  |  |

|    | 1.2. Sparse Kernels                                                 | 32 |  |  |  |

| 2. | Background                                                          | 33 |  |  |  |

|    | 2.1. Sparse Matrix–Vector Multiplication                            | 33 |  |  |  |

|    | 2.2. Breadth-First Search as Sparse Linear Algebra                  | 33 |  |  |  |

|    | 2.3. Computational Properties                                       | 35 |  |  |  |

|    |                                                                     |    |  |  |  |

#### Contents

| B1. | An Energy Efficient CM Backend for FPGA SpMV Accelerators      | 39  |

|-----|----------------------------------------------------------------|-----|

|     | B1.1. Introduction                                             | 39  |

|     | B1.2. Background                                               | 41  |

|     | B1.3. Decoupling SpMV Memory Behavior and Computation          | 44  |

|     | B1.4. Designing A Bandwidth-Saturating Backend                 | 45  |

|     | B1.5. Experimental Evaluation                                  | 51  |

|     | B1.6. Related Work                                             | 59  |

|     | B1.7. Conclusion and Future Work                               | 61  |

| B2. | . A Vector Caching Scheme for Streaming FPGA SpMV Accelerators | 65  |

|     | B2.1. Introduction                                             | 65  |

|     | B2.2. Background and Related Work                              | 67  |

|     | B2.3. Vector Caching Scheme                                    | 70  |

|     | B2.4. Experimental Evaluation                                  | 76  |

|     | B2.5. Conclusion and Future Work                               | 80  |

| B3. | . Random Access Schemes for Efficient FPGA SpMV Acceleration   | 85  |

|     | B3.1. Introduction                                             | 86  |

|     | B3.2. Background                                               | 88  |

|     | B3.3. Frontend Architectures and Random Access                 | 91  |

|     | B3.4. The Nonblocking Cooperative Vector Caching Scheme        | 95  |

|     | B3.5. Experimental Setup                                       | 105 |

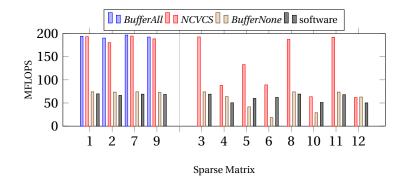

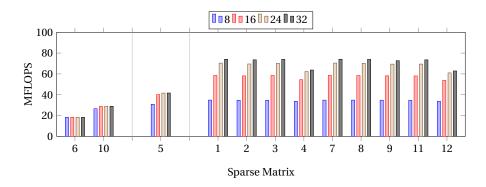

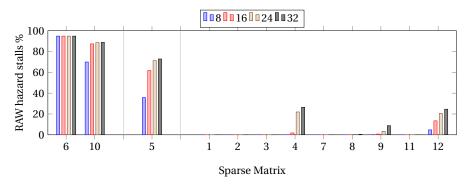

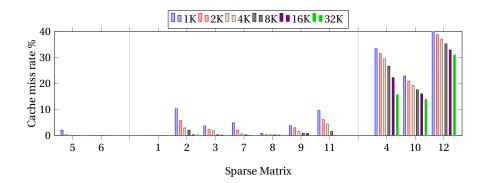

|     | B3.6. Results                                                  | 106 |

|     | B3.7. Conclusion and Future Work                               | 117 |

| B4. | . Hybrid BFS on a Single-Chip FPGA-CPU Heterogeneous Platform  | 121 |

|     | B4.1. Introduction                                             | 122 |

|     | B4.2. Background                                               | 123 |

|     | B4.3. Hybrid BFS on an FPGA-CPU Hybrid                         | 126 |

|     | B4.4. Results                                                  | 135 |

|     | B4.5. Related work                                             | 141 |

|     | B4.6. Conclusion and Future Work                               | 142 |

| ~   |                                                                | 150 |

| C.  | Deep Neural Networks                                           | 153 |

| 1.  | Introduction                                                   | 155 |

|     | 1.1. Inference with Deep Neural Networks                       | 155 |

|     | 1.2. Quantized Neural Networks                                 | 156 |

| 2.  | Background                                                     | 159 |

|     | 2.1. The Anatomy of Inference Computations                     | 159 |

|     | 2.2. Redundancy and Quantization                               | 160 |

#### Contents

|    | 2.3. Computational Properties                                         | .62 |

|----|-----------------------------------------------------------------------|-----|

| CI | FINN: A Framework for Fast, Scalable BNN Inference                    | 67  |

|    | C1.1. Introduction                                                    | .67 |

|    | C1.2. Background                                                      | .69 |

|    | C1.3. BNN Performance and Accuracy                                    | .73 |

|    | •                                                                     | .75 |

|    | с с                                                                   | .86 |

|    |                                                                       | .93 |

| C2 | Scaling BNNs on Reconfigurable Logic                                  | 99  |

|    |                                                                       | 200 |

|    |                                                                       | 201 |

|    | C2.3. BNNs on Reconfigurable Logic                                    | 202 |

|    | C2.4. Padding for BNN Convolutions                                    | 205 |

|    | C2.5. Evaluation                                                      | 207 |

|    | C2.6. Conclusion                                                      | 213 |

| C3 | Streamlined Deployment for Quantized Neural Networks 2                | 217 |

|    | C3.1. Introduction                                                    | 217 |

|    | C3.2. Streamlined QNNs                                                | 219 |

|    | C3.3. Inference with Few-Bit Weights and Activations on Mobile CPUs 2 | 222 |

|    | C3.4. Evaluation                                                      | 224 |

|    | C3.5. Conclusion and Future Work                                      | 229 |

| ~  |                                                                       | 20  |

| D. | Concluding Remarks 23                                                 | 39  |

| 1. | Conclusion 2                                                          | 241 |

|    | 1.1. Research Question 1                                              | 241 |

|    |                                                                       | .41 |

|    |                                                                       | 242 |

| 2. | 1.2. Research Question 2         2                                    |     |

| 2. | 1.2. Research Question 2   2     Future Work   2                      | 242 |

## Part A

Part A.

Overview

### 1. Introduction

Computers have gradually transformed human society, fueled by the extraordinary trend of increasing compute power in smaller form-factors at a cheaper price as predicted by Moore's Law [22]. However, this trend has stagnated and today's computers are now limited by their *energy efficiency*, i.e., computers must perform more computation for the same amount of (or less) electrical energy than what they use today if this trend is to be sustained.

The overarching goal of this thesis is to gain insight into how this problem can be alleviated by means of *specialized hardware for particular types of applications*. The remainder of this chapter will introduce the problem and the proposed approach in more details, then describe the structure of the rest of the thesis.

#### 1.1. Dark Silicon and the Need for Accelerators

For over forty years, improvements in transistor size, supply voltage scaling and architecture fueled the increase in the computational power of general-purpose Central Processing Units (CPUs), but there is evidence that this trend is not sustainable [18]. While the number of transistors per area keeps growing in newer semiconductor technology generations, it is no longer possible to power all the transistors on the chip without significantly increasing the power budget. In many cases, increasing the power budget is not feasible due to limitations in cooling or battery life. Keeping the same power budget results in areas on the chip without power, referred to as *dark silicon* [11].

With Dark Silicon clouding the horizon for computing systems, computer architects have been searching for new solutions. Taylor [27] mentions four generic classes of solutions (referred to as "The Four Horsemen of the Dark Silicon Apocalypse") which could be used to attack the dark silicon problem. These can be summarized as follows:

• The Shrinking Horseman, shrinking chip sizes to prune dark silicon areas.

#### 1. Introduction

Table 1.1.: Heterogeneity trends in smartphones. Compiled from [21, 35–38].

| Product          | Year | Cores                                        |

|------------------|------|----------------------------------------------|

| Nokia 9000       | 1996 | 24 MHz CPU                                   |

| Palm Treo 650    | 2004 | 312 MHz CPU                                  |

| Samsung SGH-D500 | 2005 | 100 MHz CPU + Saturn DSP                     |

| Nokia N810       | 2007 | 330 MHz CPU + 220 MHz DSP + GPU + ima-       |

|                  |      | ging accelerator                             |

| Motorola Moto X  | 2013 | 1.7 GHz dual-core CPU + GPU + imaging ac-    |

|                  |      | celerator + natural language processing core |

|                  |      | + contextual computing core                  |

- *The Dim Horseman,* using underclocked logic or near-threshold voltage designs to increase operating efficiency.

- *The Deus Ex Machina Horseman,* fundamental breakthroughs in transistor technology which will lessen or remove the dark silicon problem.

- The Specialized Horseman, which is further elaborated below.

The last of these ideas, aptly named "The Specialized Horseman", proposes a move towards specialized, highly energy-efficient co-processors or accelerators. In a manner of speaking, dark silicon is a manifestation of a lack of energy efficiency. Specialized logic targeting particular applications or domains can offer energy efficiency that is orders of magnitude greater than general-purpose processors on an equal or greater level of performance [7, 14, 16, 19, 24]. This would contribute significantly to the overall energy efficiency of the system for running applications targeted by specialized logic.

More energy-sensitive platforms such as smartphones and mobile computing devices have already been demonstrating a trend of heterogeneous processors with increasingly specialized components in the form of System on a Chip (SoC) elements, as illustrated in Table 1.1. There is also a significant shift towards accelerators in the computer architecture research community, which is evidenced by the number of sessions dedicated to specialized hardware in top computer architecture conferences. For instance, in the programme of the 2016 International Symposium on Computer Architecture (ISCA), there were three entire sessions dedicated to neural network accelerators, as well as another session for graph analytics and big data accelerators. In light of this information, **The Specialized Horseman** was chosen to be the method for improving the energy efficiency of computing systems in this thesis.

#### 1.2. Choice of Specialization Domains and Substrate

The very word *specialization* implies that the resulting accelerators are not *general-purpose*, i.e., they cannot execute arbitrary compute workloads, but only the particular ones that they were designed for. We note that the *degree* of specialization is particularly important; due to the costs involved in designing such systems, it is desirable to make them *domain-specific* (suitable for a range of applications) instead of *single-application-specific*. Cong et al. [8] refer to this approach as *customizable domain-specific computing*, and motivate it with three observations:

- 1. Each user or enterprise typically has high computing demand only in one or a few application domains (e.g., graphics for game developers, circuit simulation for integrated circuit designers, financial analytics for investment banks), which can be targeted with accelerators for high performance and efficiency. Other computing needs, such as e-mail or word processing can be satisfied with available computing technologies.

- 2. The gap in performance and efficiency between a domain-specific solution and a general-purpose solution can be several orders of magnitude.

- 3. Designing a custom Application-Specific Integrated Circuit (ASIC) for each and every application is prohibitively expensive, hence some customizability to address a range of applications is needed.

Two key methodology questions in domain-specific accelerator research are *what* to accelerate, and *where* to accelerate it in terms of the hardware substrate. These questions are addressed in the following subsections.

#### 1.2.1. The Domains

As specialized acceleration has limited applicability, the choice of which domain(s) will be accelerated is significant. In this thesis, the following criteria were used to guide the topic and level of specialization for acceleration:

• *Necessity.* The target domains should require acceleration. Computations that already meet performance and efficiency requirements on existing general-purpose computers does not necessitate specialization and acceleration to the same extent as computation which runs too slowly or inefficiently on current devices.

#### 1. Introduction

- *Impact.* The acceleration of target domains should have some impact, e.g., they should be considered to be of major importance for the progress of science or possessing large market potential.

- *Granularity.* The chosen level of specialization should be able to address a range of applications, instead of targeting just a particular implementation of a single application.

The "13 Berkeley Dwarfs" proposed by Asanovic et al. [1] were a major source of inspiration in the choice of these focus areas for this thesis. These "dwarfs" are particular algorithmic methods that capture a widely-occurring pattern of computation and communication believed to be of major importance for at least the next decade of computing, which by definition fulfill two of the three criteria listed above. The focus areas for this thesis were chosen to be **Sparse Linear Algebra**, which is explored in Part B, and **Deep Neural Networks**, which is explored in Part C. In terms of the Berkeley Dwarfs, these focus areas fall within the Sparse Linear Algebra and Dense Linear Algebra dwarfs. The introduction sections in each part provide more insight into why these focus areas were chosen.

#### 1.2.2. The Hardware Substrate

A suitable hardware substrate is necessary to study and evaluate how the proposed accelerators will perform. The chosen substrate for specialization in this thesis is reconfigurable logic in the form of **Field-Programmable Gate Arrays (FPGAs)**. As will be described in more detail in Section 2.1, the behavior of any digital circuit can be constructed in the FPGA as long as there are enough logic resources available, and can be changed as many times as desired. FPGAs have received significant attention as a new engine for heterogeneous computing in the last few years, as exemplified by Intel's 2015 acquisition of the world's second-largest FPGA maker Altera, and their subsequent announcements regarding Xeon+FPGA chips.

#### 1.3. Research Questions

The overarching goal for this thesis is *to gain insight into how the energy efficiency of computer systems can be improved via specialization*. Based on the choice of focus domains and substrate discussed in Section 1.2, the goal is formulated as two research questions:

RQ1. How can sparse linear algebra benefit from FPGA acceleration?

1.4. Thesis Outline

#### RQ2. How can deep neural network inference benefit from FPGA acceleration?

These questions permit exploration on both sides of the traditional hardware-software boundary. That is, we do not restrict the effort to exploring FPGA hardware accelerator architectures, but also accept changes that go across the traditional hardware-software boundary. This may include changing the data layout, data preprocessing and mathematical reformulations, and may be seen as a limited form of hardware/software codesign (Section 2.2). This allows for optimizing the computation as a whole without being limited by the traditional rigid abstraction boundary, potentially yielding greater acceleration and efficiency.

#### 1.4. Thesis Outline

This is a *compilation thesis* organized into four parts; an introductory part followed by two parts containing a compilation of research articles, and a final part with concluding remarks.

This introductory part (Part A) contains an overview of the general problem, the research questions pursued, and the general background necessary to understand the research articles in the thesis. Afterwards, it presents a brief summary of the articles included in the thesis, how they are related to general computing concepts and to each other. The second and third parts consist of a collection of research articles on the design of accelerators for sparse linear algebra (Part B) and deep neural networks (Part C), respectively. As these two domains are substantially different in terms of their computational requirements, they both start with an introduction to and some background on their respective fields to help the reader better understand the context of the articles. The final part of the thesis (Part D) concludes with a summary of results from the research articles and presents several directions for future work.

### 2. Background

This chapter provides the general background necessary to understand the content of this thesis, pertaining to FPGAs as an acceleration fabric, design of FPGA accelerators and memory systems. Parts B and C contain their own background chapters with further domain-specific details on sparse linear algebra and deep neural networks.

#### 2.1. Field-Programmable Gate Arrays

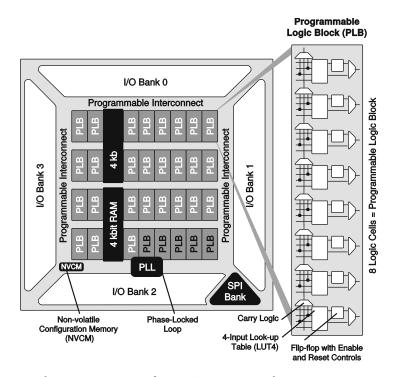

Field-Programmable Gate Arrays (FPGAs) are chips containing arrays of Look-Up Tables (LUTs), fixed-function blocks, signal routing and clock networks, as exemplified in Figure 2.1. By configuring the contents of the LUTs and how they are connected together with each other and fixed-function blocks, the behavior of any digital circuit can be constructed in the FPGA, and this configuration can be changed as many times as desired. These capabilities of realizability and reconfigurability are of prime importance for the choice of FPGAs as an accelerator substrate for this thesis. In general, a circuit implemented in reconfigurable logic will always be slower and less efficient than a comparable, dedicated circuit in silicon. However, this efficiency gap is smaller for applications that can make use of the fixed-function blocks, and off-the-shelf reconfigurable chips do not carry the prohibitive price tags of mask costs or post-production errors for ASICs.

Due to the repetitive and regular structure of their internal components, FPGAs have benefited substantially from the improvements in semiconductor process technology, and today's models possess substantial on-chip memory capacity, bandwidth and compute capabilities. They have received significant attention as a new engine for heterogeneous computing in the last few years, and significant acceleration on keyvalue stores [15], financial option pricing [10], and genome sequencing [26] have been demonstrated on FPGAs. Besides the potential performance advantages, Hoe [13] points out that FPGA acceleration is first and foremost about energy efficiency, owing to their high-degree of slow-clocked parallelism and avoidance of Von Neumann programmability overheads.

2. Background

Figure 2.1.: The organization of a Lattice Semiconductor iCE40 FPGA. Reproduced from [23].

#### 2.2. Hardware/Software Codesign

Implementations of modern computer systems can be quite complex, even when targeting a single domain or application. For instance, a modern SoC such as the Xilinx Zynq family of chips may contain several different (heterogeneous) computing engines as well FPGA fabric. Achieving desired functionality on such a system requires exploring a vast design space that encompasses hardware architecture exploration, mapping the functionality to available resources and assessing performance and efficiency to remain within system constraints. This process is referred to as *hardware/software codesign* [28] and as the name implies, it involves the concurrent design of hardware and software. The key advantage obtained in this method is the ability to approach the problem as a larger whole, potentially increasing the performance and efficiency of the final solution by making adjustments without being limited by the traditional abstraction layers in computer architecture.

Several research articles in this thesis use codesign-like techniques, such as partioning an algorithm for hybrid execution between a CPU and an FPGA accelerator, performing mathematical simplifications on neural networks at compile time, and preprocessing data in software to extract relevant characteristics for reconfigurable hardware.

#### 2.3. Implementing FPGA Accelerators

FPGAs are notorious for being difficult to program [3]. The entry point for most FPGA vendor tools are Register Transfer Level (RTL) designs expressed in Verilog or VHDL, which introduce several challenges for rapid development. As the chosen evaluation technique for this thesis is FPGA implementation, other languages and tools were used to overcome two of the traditional RTL design challenges:

1. Language features. In terms of languages, neither Verilog nor VHDL were originally conceived to express synthesizable RTL constructs – they were intended for *simulating* hardware, which means it is possible to express programs in them that cannot be synthesized into FPGA circuits. Furthermore, both languages first appeared in the 1980s, and lack the powerful abstraction facilities that are common in modern programming languages, which further decreases design productivity. Chisel was proposed by Bachrach et al. [2] to address these problems. It is embedded into the Scala language, which has extensive capabilities for building Domain-Specific Languages (DSLs). A Chisel program is a *parametrizable hardware generator* that expresses which RTL primitives are instantiated and how they are connected together, and barring syntax errors its output is guaranteed to be synthesizable. By using different backends, it is possible to

#### 2. Background

generate Verilog or a cycle-accurate C++ simulation of the design from the same source code, which boosts productivity. Chisel was used in the implementation of the papers contained in Part B of this thesis.

2. *Abstraction level.* Even with the capabilities of languages like Chisel, RTL design is less productive and more challenging than software development. Namely, in RTL design, the designer must carefully specify (and debug) the cycle-by-cycle behavior of a complex circuit by cobbling together simple components, designing state machines and control logic to ensure correct behavior, and adding pipeline registers to increase the clock frequency when desired. High-Level Synthesis (HLS) tools such as Vivado HLS [40] aim to close this gap by allowing the designer to specify the behavior and desired performance of the circuit at a higher level of abstraction, and synthesizing RTL from this specification. This approach works especially well for circuits with static schedules, such as matrix multiplications whose sizes are known at compile time. To pursue these benefits, Vivado HLS was used for the accelerator implementations in Part C of this thesis.

#### 2.4. Memory System Design

How data is laid out, accessed, stored and moved between parts of the system is a key component for any computer architecture, including accelerators. This section provides background on several memory system design concepts that are used in the thesis.

#### 2.4.1. On-Chip Memory

FPGAs contain a limited amount of On-Chip Memory (OCM), sometimes referred to as Block RAM (BRAM). Any address in any BRAM can be accessed with a single clock cycle of latency, which can deliver multiple terabytes per second of memory bandwidth in modern FPGAs. As with any other component on the FPGA, on-chip memory blocks do not enforce a particular architecture upon the designer, and can be flexibly connected to other components to shape the memory system as designed. For instance, they can be configured as read-only memory (ROM) whose contents are set at FPGA configuration time, as a FIFO buffer storage by adding enqueue/dequeue logic, or as caches by adding appropriate management logic.

#### 2.4. Memory System Design

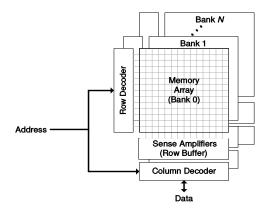

Figure 2.2.: The internal three-dimensional organization of DRAM, showing banks, rows and columns. Reproduced from [20].

#### 2.4.2. Off-Chip Memory

Any memory that is accessed via external I/O pins is off-chip memory, although in this thesis the term is used to refer to off-chip DRAM, commonly found on FPGA boards to provide a reasonably large-capacity memory at low cost. These DRAM chips are interfaced by a memory controller on the FPGA which services memory requests from the accelerator(s) by implementing the signaling standard required by DRAM. Due to the internal organization of DRAM chips shown in Figure 2.2, the way in which memory accesses are scheduled has a large impact on the achievable throughput and access latency [20]. Namely, data can be read or written only as an entire DRAM row in each bank. This makes accessing sequential positions as large bursts very effective, since the entire DRAM row buffer can be utilized. However, performing fine-grained random accesses involves repeatedly fetching new rows without utilizing the entirety of the previously fetched row buffer, which increases the access latency and decreases effective bandwidth substantially. For instance, orders-of-magnitude worse bandwidth is reported on the RandomAccess benchmark included in the HPCC benchmark suite [17] compared to sequential accesses. This is a key problem for sparse linear algebra kernels with random memory access patterns, which Part B of this thesis focuses on.

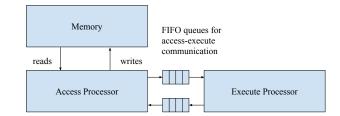

#### 2.4.3. Decoupled Access-Execute and Latency-Insensitive Design

Decoupled access-execute architectures originally proposed by Smith [25] refers to architectures with a dedicated access component, which is responsible for memory

#### 2. Background

Figure 2.3.: Conceptual overview of a decoupled access-execute architecture.

operations such as reads and writes, and a dedicated *execute* component, which is responsible for carrying out computation on accessed memory and producing results. These two components communicate via FIFO queues, as conceptually illustrated in Figure 2.3. Such an architecture enables clean separation and separate optimization of these two main components, and also lets the designer easily analyze potential performance issues by examining the flow rate and backpressure in the communication queues.

Beyond decoupling memory accesses and computation, a similar principle of *latency-insensitive design* [5] in the form of *synchronous elastic architectures* [9] can be applied to system design at a finer-grained level. Namely, the system can be decomposed into multiple parallel components which communicate via FIFO queues. The requirement from each component is that it can be *stalled with backpressure*, i.e., when one or more FIFOs that it wants to write to are full. As long as each component consumes available elements from its input FIFOs as quickly as possible, the entire system will self-schedule and naturally process data at the highest throughput permitted by the slowest component. This design paradigm was shown to be successful for construction of FPGA accelerators by the Stream Computations Organized for Reconfigurable Execution (SCORE) project [6]. Both decoupled access-execute and latency-insensitive design have served as inspiration for the accelerator architectures in this thesis.

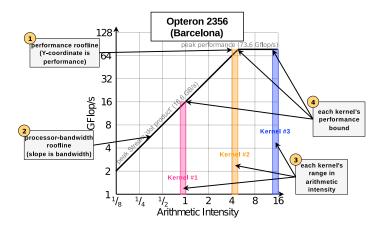

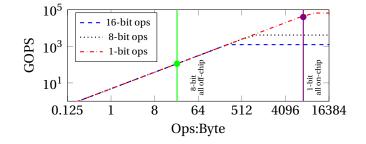

#### 2.5. The Roofline Model

The roofline [39] is a well-known visual performance model that provides an upper bound on the performance of a particular computational kernel when running on a particular computer architecture. The key property that must be known about the computational kernel is the *arithmetic intensity*, which is the ratio of computation to communication measured in compute operations per byte read from off-chip memory. For the architecture that this computation will be run on, the peak off-chip memory

#### 2.5. The Roofline Model

Figure 2.4.: Example of a roofline model. Reproduced from [4].

bandwidth and the peak compute capability for the kinds of operations used in the kernel must be known. With these numbers available, the roofline model can be constructed as illustrated in Figure 2.4. The model considers two principal performance bounds, computation and communication, and considers the execution time of the application bounded by each of these to determine which of them will be the bottleneck, and how much performance may be attained. In the visual model, the sloping part of the roofline is the communication-bound region, whereas the flat part is the compute-bound region. When a vertical line corresponding to the arithmetic intensity of the computational kernel in question is drawn, it will intersect the roofline in one of these regions, indicating what will be the performance bottleneck for this kernel.

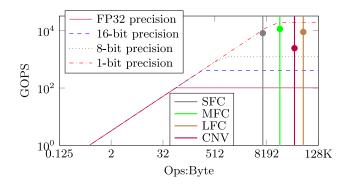

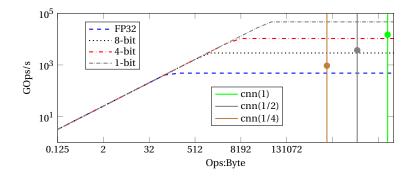

Since it considers platform and kernel characteristics at a quite abstract level, the roofline model is also useful for estimating performance for accelerators. It is used in Part C of this thesis to help estimate the performance gains from quantization for deep neural networks.

### 3. Research Summary

This section provides an overview of the research articles included in this thesis, how they relate to each other and to general computing concepts. It is intended to serve as a roadmap that helps place the articles included in the thesis into the bigger picture. After the articles have been presented, the final part of this thesis will present a synthesis of the contributions from individual articles into a larger whole.

#### 3.1. Overview

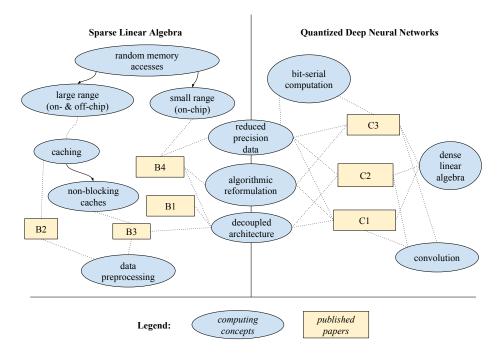

As discussed in Section 1.2, this thesis explores the acceleration of two distinct domains. It includes seven papers, four on sparse linear algebra in Part B, and three on deep neural networks in Part C. Each paper is identified with the part name and number (B1, B2, C1, C2...) and will be referred to as such for brevity in the rest of the discussion.

Figure 3.1 presents a mind map linking computing concepts to papers in the thesis in order to provide a visual overview of how the papers align with different themes, and with each other. It can be observed that although the two domains are distinct, a number of common themes such as algorithmic reformulation, reduced precision operations and decoupled hardware architectures are recurring themes in papers in both domains. The following sections provide brief summaries of each paper, and their relationships to each other.

#### 3.2. Articles on Sparse Linear Algebra

The articles in Part B discuss how sparse linear algebra, in particular the Sparse Matrix– Vector Multiplication (SpMV) and Sparse Matrix–Sparse Vector Multiplication (SpM-SpV) kernels, can benefit from acceleration on reconfigurable logic. The key aspect of the investigation here is the memory system and how it can be made efficient, since sparse kernels are known to be bottlenecked by random, indirect memory accesses. As the sparsity structure that determines the memory accesses becomes known only at runtime, it is challenging to devise a single architecture that works well for all sparse

#### 3. Research Summary

Figure 3.1.: A mind map of publications that are part of this thesis and their relations to computing concepts.

#### 3.2. Articles on Sparse Linear Algebra

matrices. We use lightweight data preprocessing to adapt to the sparsity structure at hand, taking advantage of the flexibility of reconfigurable logic. We also explore the applicability of accelerated sparse linear algebra to graph algorithm primitives, taking advantage of data layout changes and reduced precision representations to further increase efficiency.

#### Paper B1: An Energy Efficient Column-Major Backend for FPGA SpMV Accelerators

By Yaman Umuroglu and Magnus Jahre In Proceedings of the 2014 IEEE 32nd International Conference on Computer Design (ICCD) IEEE, 2014 [31]

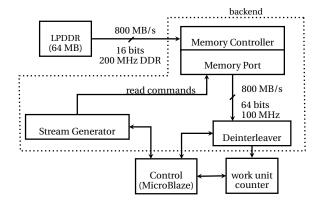

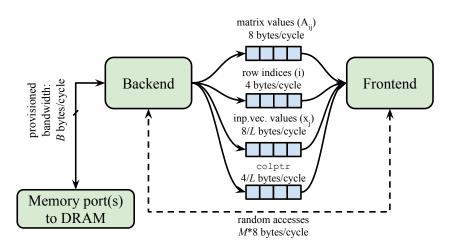

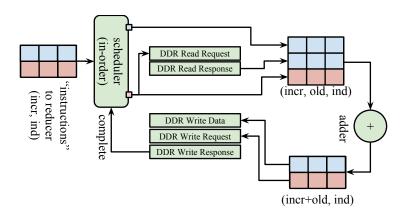

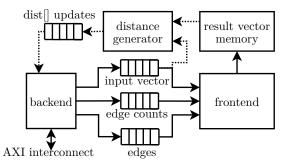

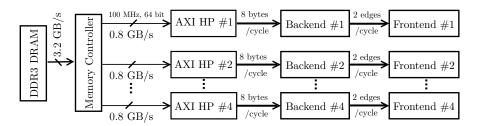

This work presents a design strategy for SpMV accelerators in the spirit of decoupled access-execute, where the memory and computation are handled by two decoupled units (backend and frontend) with matched throughput. This modular design is ad-opted by all other articles on sparse linear algebra in this thesis. Focusing on the sequential memory accesses by the backend component, experimental results are presented that indicate that even the sequential memory access component can suffer from degraded external memory bandwidth utilization due to many parallel requests. An alternative, interleaved data layout is then presented to increase DRAM bandwidth and power efficiency for FPGA SpMV accelerators. An SpMV accelerator backend design that uses this layout is proposed and evaluated on a suite of sparse matrices to characterize the performance and efficiency benefits,

#### Paper B2: A Vector Caching Scheme for Streaming FPGA SpMV Accelerators

By Yaman Umuroglu and Magnus Jahre In Proceedings of the 2015 International Symposium on Applied Reconfigurable Computing (ARC) Springer International Publishing, 2015 [30]

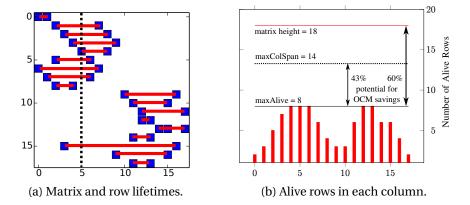

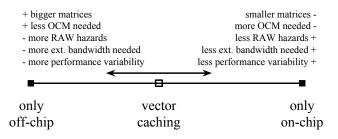

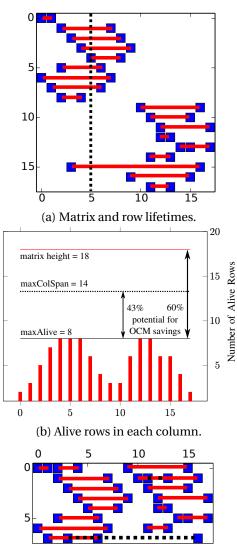

In terms of the modular SpMV design strategy presented in Paper B1, this paper focuses on the frontend and the random memory access problem. A hardware-software caching scheme for handling the SpMV random access component is presented. The

#### 3. Research Summary

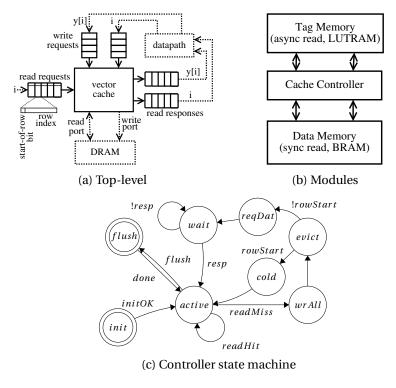

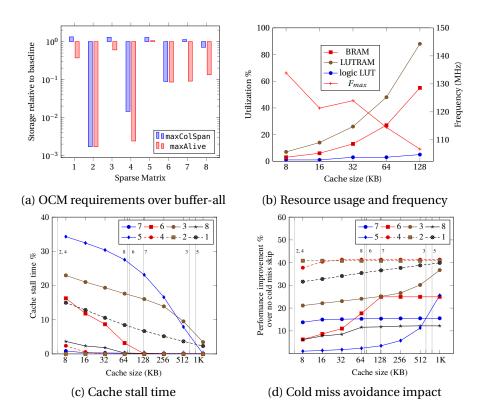

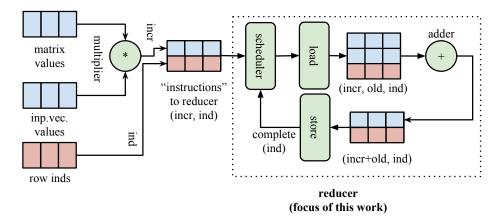

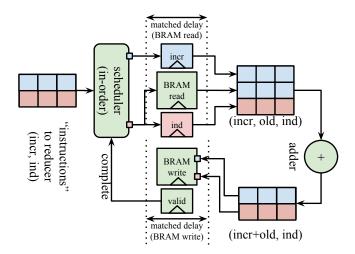

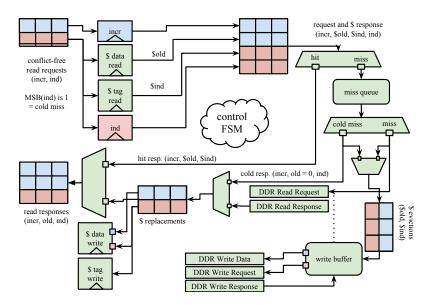

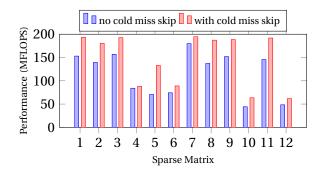

essence of the technique is to increase the resource efficiency and performance of the hardware cache by using lightweight data preprocessing in software to extract relevant access pattern information. The software part of the scheme involves preprocessing the sparse matrix to extract the required cache capacity for stall-free acceleration, and adding a single bit of information for each matrix row to avoid cold misses in the cache. In turn, the proposed hardware cache can be resized to the determined capacity (which is typically much smaller than keeping the entire random access component on-chip), and is able to use the extra information to avoid cold misses. The merits of the hardware-software caching approach are validated with a range of sparse matrices.

#### Paper B3: Random Access Schemes for Efficient FPGA SpMV Acceleration

By Yaman Umuroglu, Donn Morrison and Magnus Jahre In Microprocessors and Microsystems, volume 47 part B Elsevier, 2016 [32]

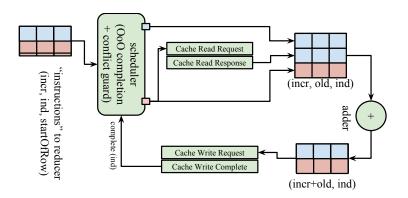

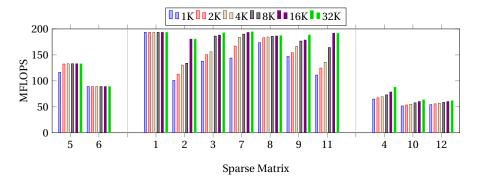

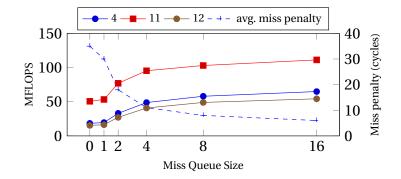

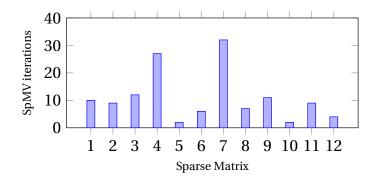

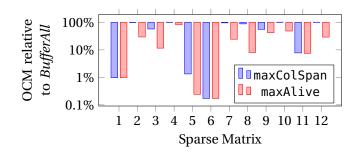

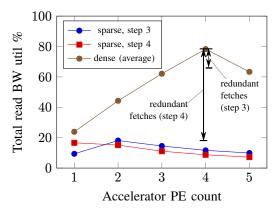

This work is an invited journal paper extension of Paper B2, offering deeper insights into the problem, improving the caching technique and providing more results. How prior work has handled the random memory access component in SpMV is discussed and grouped under three alternatives (all on-chip, all off-chip, caching). The hardware-software vector caching scheme for SpMV from Paper B2 is combined with nonblocking caches, a classical memory system technique in out-of-order processors that is used to extract more Memory-Level Parallelism (MLP) and increase bandwidth utilization. The improved caching technique is validated with extensive experiments, demonstrating how multiple outstanding requests can increase SpMV performance. The cost of pre-processing is also factored into the overall performance, showing how the performance gains from preprocessing outweigh the time cost of preprocessing in relatively few iterations.

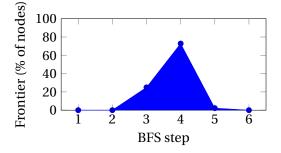

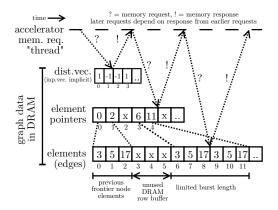

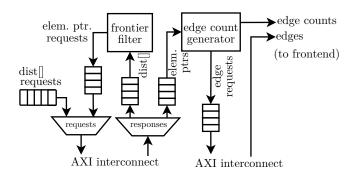

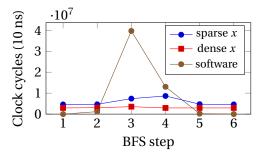

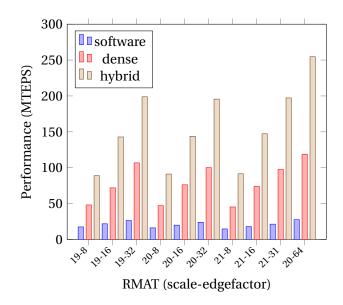

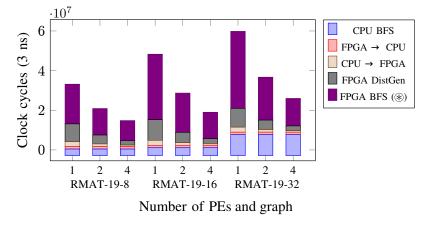

#### Paper B4: Hybrid Breadth-First Search on a Single-Chip FPGA-CPU Heterogeneous Platform

By Yaman Umuroglu, Donn Morrison and Magnus Jahre In Proceedings of the 2015 25th International Conference on Field Programmable Logic and Applications (FPL) IEEE, 2015 [34] The acceleration of the Breadth-First Search (BFS) graph traversal kernel is studied on a single-chip FPGA-CPU system. By using the *matrices over semirings* concept, BFS can be viewed as SpMV or SpMSpV on the Boolean semiring. This makes it possible to apply insights from papers B1 and B2 to offer significant acceleration on BFS. This work also describes how a simple algorithmic reformulation can be used to make the random access range much smaller. Namely, the distances to the root node can be generated with an additional step instead of on-the-fly, effectively decoupling the distance generation from the traversal, thus keeping the OCM footprint for random accesses very small. Additionally, a computational property of BFS on small-world graphs is exploited for hybrid execution, where some iterations of the kernel are processed on the CPU, and the remainder on the FPGA. The resulting BFS implementation is more efficient (over twice as efficient compared to prior work) in terms of utilizing the external memory bandwidth.

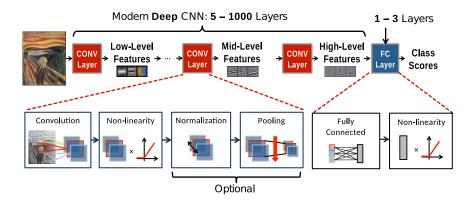

#### 3.3. Articles on Deep Neural Networks

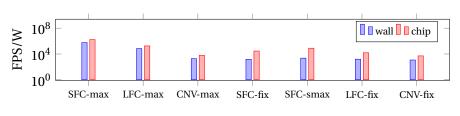

The articles in Part C explore how to apply reconfigurable logic to deep neural network inference. Due to their inherent memory footprint and resource benefits over floating point networks, we focus on Quantized Neural Networks (QNNs), quantifying and demonstrating the performance and energy benefits of QNN inference on FPGAs using roofline models and prototypes with adjustable throughput according to user requirements. By applying our approach on larger networks and FPGAs, we identify on-chip memory storage and bandwidth as the key limitations to scalability. We also study how QNN inference can be performed efficiently on commodity CPUs using bit serial arithmetic, provide performance measurements, and observe that FPGAs have significant performance benefits over CPUs in this regard.

#### Paper C1: FINN: A Framework for Fast, Scalable Binarized Neural Network Inference

By Yaman Umuroglu, Nicholas J. Fraser, Giulio Gambardella, Michaela Blott, Philip Leong, Magnus Jahre, and Kees Vissers In Proceedings of the 2017 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA) ACM, 2017 [29]

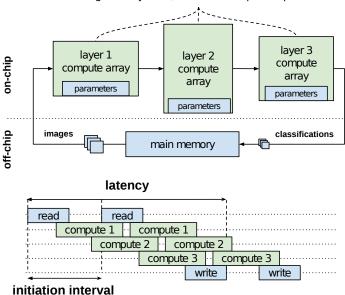

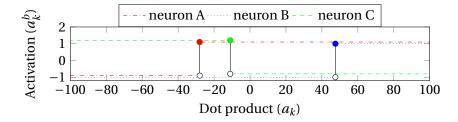

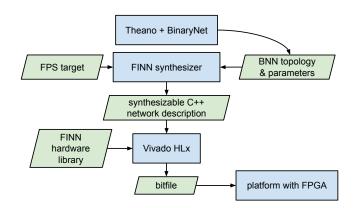

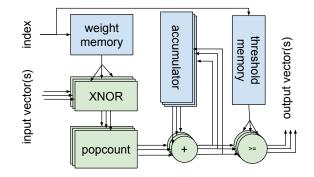

This paper explores inference with Binarized Neural Networks (BNNs), the most extreme form of QNNs, on FPGAs. We quantify the potential of BNNs on FPGAs via the

#### 3. Research Summary

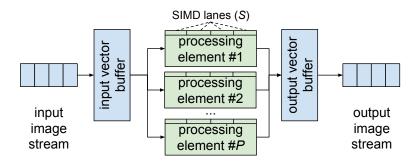

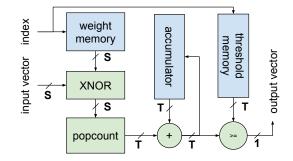

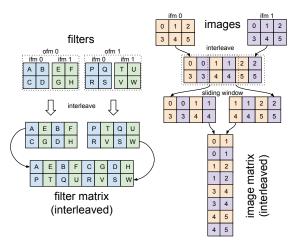

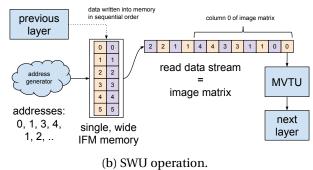

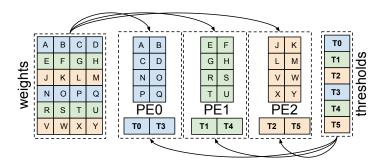

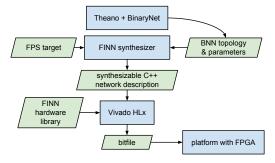

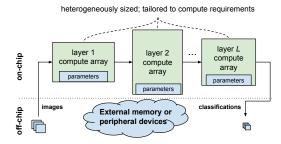

roofline model, and present the FINN framework for building BNN accelerators. FINN composes hardware blocks implementing fully-connected, convolutional and pooling layers according to user-specified throughput requirements. The composed architecture is *streaming* in that it executes all layers of the network in parallel, and *heterogeneous* in that each layer's hardware allocation reflects its computational requirements. A mathematical simplification to absorb floating point batch normalization layers into thresholding activations is also presented, which further lowers resource cost. At the time of its publication, FINN was generating the lowest-latency, highest-throughput and highest-energy-efficiency Deep Neural Network (DNN) image classification accelerators in literature. This performance is possible owing to a combination of massive parallelism, low-precision computations and high arithmetic intensity.

#### Paper C2: Scaling Binarized Neural Networks on Reconfigurable Logic

By Nicholas J. Fraser, Yaman Umuroglu, Giulio Gambardella, Michaela Blott, Philip Leong, Magnus Jahre, and Kees Vissers In Proceedings of the 8th Workshop and 6th Workshop on Parallel Programming and Run-Time Management Techniques for Many-core Architectures and Design Tools and Architectures for Multicore Embedded Computing Platforms (PARMA-DITAM) ACM, 2017 [12]

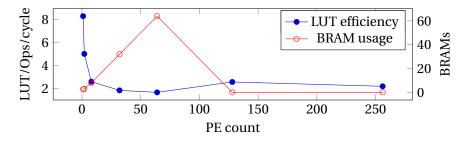

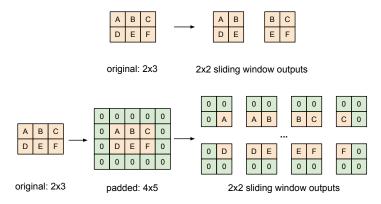

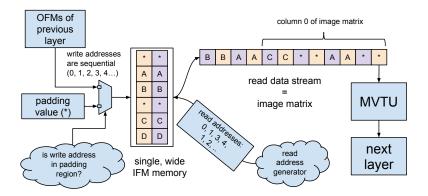

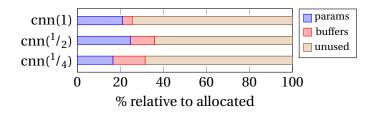

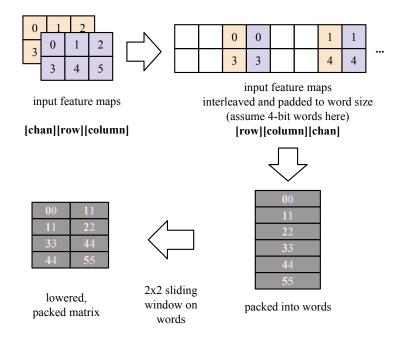

This work builds upon Paper C1 investigates how BNN performance and accuracy scales on larger FPGAs and larger networks. We first show how binary convolutions can be padded with -1 values to increase the accuracy in image recognition tasks, and implement this with minor changes to the Sliding Window Unit from Paper C1. An accelerator classifying the CIFAR-10 dataset with close to state-of-the-art accuracy using a large BNN and 12 thousand frames per second is demonstrated, and the obtained performance is compared to predictions from the roofline models. One of the key findings regarding the limitations in scaling is the utilization of OCM, which is revealed to be relatively poor due to the way in which matrix-matrix multiplications are implemented. A matrix-multiple vectors engine is proposed as a potential solution to the OCM utilization problem.

3.4. Other Articles

#### Paper C3: Streamlined Deployment for Quantized Neural Networks

By Yaman Umuroglu and Magnus Jahre In The 2017 International Workshop on Highly Efficient Neural Networks Design (HENND), part of ESWEEK arXiv:1709.04060 [33]

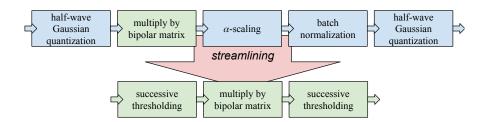

Trained QNNs still contain some floating point parameters and computation. In this work, we extend and generalize the transformation proposed in Paper C1 to QNNs by moving, collapsing and absorbing linear transforms into thresholding layers. This transformation is called *streamlining* and simplifies the trained network at compile time. Additionally, we explore how bit-serial processing can be used to run QNN inference efficiently on existing CPUs. Although this work evaluates the presented techniques on CPUs and not FPGAs, these techniques are directly applicable to FPGA accelerators as well. Namely, the simplification by streamlining prevents floating point computation from taking up valuable logic and DSP slice resources for FPGA accelerators. Additionally, the proposed bit-serial processing technique is also suitable for applying on FPGAs, supplementing the binary matrix primitives proposed in Paper C1 with the ability to support arbitrary integer quantization at runtime. Finally, this work establishes a CPU baseline which further highlights the benefits of FPGA acceleration for QNNs, since the resulting CPU performance is orders of magnitude worse than the accelerators proposed in Papers C1 and C2.

#### 3.4. Other Articles

Several research articles that were produced during the PhD work are not included in this thesis, either due to their extended versions being included instead, or because of their focus falling outside the scope of the thesis.

- Yaman Umuroglu and Magnus Jahre. "Work-in-Progress: Towards Efficient Quantized Neural Network Inference on Mobile Devices". In Proceedings of the 2017 International Conference on Compilers, Architecture and Synthesis for Embedded Systems (CASES).

- Michaela Blott, Thomas Preusser, Yaman Umuroglu, Miriam Leeser, Nicholas Fraser, Kenneth O'Brien and Giulio Gambardella. "Scaling Neural Network Performance through Customized Hardware Architecture". In *Proceedings of the 2017 IEEE International Conference on Computer Design (ICCD).*

- 3. Research Summary

- Yaman Umuroglu, Nicholas J. Fraser, Giulio Gambardella and Michaela Blott. "A C++ Library for Rapid Exploration of Binary Neural Networks on Reconfigurable Logic". Presented at *The Second International Workshop on Heterogeneous Highperformance Reconfigurable Computing (H2RC) at Supercomputing 2016 (SC).*

# Bibliography

- [1] K. Asanovic, R. Bodik, B. C. Catanzaro, J. J. Gebis, P. Husbands, K. Keutzer, D. A. Patterson, W. L. Plishker, J. Shalf, S. W. Williams et al. *The landscape* of parallel computing research: A view from Berkeley. Tech. rep. Technical Report UCB/EECS-2006-183, EECS Department, University of California, Berkeley, 2006.

- [2] J. Bachrach, H. Vo, B. Richards, Y. Lee, A. Waterman, R. Avižienis, J. Wawrzynek and K. Asanović. 'Chisel: constructing hardware in a Scala embedded language'. In: *Proc. of the Design Automation Conference*. 2012.

- [3] D. F. Bacon, R. Rabbah and S. Shukla. 'FPGA programming for the masses'. In: *Communications of the ACM* 56.4 (2013), pp. 56–63.

- [4] D. H. Bailey, R. F. Lucas and S. Williams. *Performance tuning of scientific applications*. CRC Press, 2010.

- [5] L. P. Carloni, K. L. McMillan and A. L. Sangiovanni-Vincentelli. 'Theory of latency-insensitive design'. In: *IEEE Transactions on computer-aided design of integrated circuits and systems* 20.9 (2001), pp. 1059–1076.

- [6] E. Caspi, M. Chu, R. Huang, J. Yeh, J. Wawrzynek and A. DeHon. 'Stream computations organized for reconfigurable execution (SCORE)'. In: *FPL*. Springer. 2000, pp. 605–614.

- [7] E. S. Chung, P. A. Milder, J. C. Hoe and K. Mai. 'Single-chip heterogeneous computing: Does the future include custom logic, fpgas, and gpgpus?' In: *Proceedings of the 2010 43rd Annual IEEE/ACM International Symposium on Microarchitecture*. IEEE Computer Society. 2010, pp. 225–236.

- [8] J. Cong, V. Sarkar, G. Reinman and A. Bui. 'Customizable domain-specific computing'. In: *IEEE Design & Test of Computers* 28.2 (2011), pp. 6–15.

#### Bibliography

- [9] J. Cortadella, M. Kishinevsky and B. Grundmann. 'Synthesis of synchronous elastic architectures'. In: *Proceedings of the 43rd annual Design Automation Conference*. ACM. 2006, pp. 657–662.

- [10] C. De Schryver, I. Shcherbakov, F. Kienle, N. Wehn, H. Marxen, A. Kostiuk and R. Korn. 'An energy efficient FPGA accelerator for monte carlo option pricing with the heston model'. In: *Reconfigurable Computing and FPGAs* (*ReConFig*), 2011 International Conference on. IEEE. 2011, pp. 468–474.

- H. Esmaeilzadeh, E. Blem, R. S. Amant, K. Sankaralingam and D. Burger.

'Dark silicon and the end of multicore scaling'. In: *Computer Architecture (ISCA), 2011 38th Annual International Symposium on*. IEEE. 2011, pp. 365–376.

- [12] N. J. Fraser, Y. Umuroglu, G. Gambardella, M. Blott, P. Leong, M. Jahre and K. Vissers. 'Scaling Binarized Neural Networks on Reconfigurable Logic'. In: Proceedings of the 8th Workshop and 6th Workshop on Parallel Programming and Run-Time Management Techniques for Many-core Architectures and Design Tools and Architectures for Multicore Embedded Computing Platforms. Vol. 2017. 2017.

- J. C. Hoe. 'Technical Perspective: FPGA Compute Acceleration is First About Energy Efficiency'. In: *Commun. ACM* 59.11 (Oct. 2016), pp. 113– 113. DOI: 10.1145/2996866. URL: http://doi.acm.org/10.1145/ 2996866.

- [14] T. Instruments. *OMAP Applications Processors*. 2013. URL: http://www.ti.com/product/OMAP4470.

- [15] Z. István, G. Alonso, M. Blott and K. Vissers. 'A flexible hash table design for 10gbps key-value stores on fpgas'. In: *Field Programmable Logic and Applications (FPL), 2013 23rd International Conference on*. IEEE. 2013, pp. 1–8.

- [16] R. C. Larsen and O. Janbu. Introduction to EFM32 Microcontrollers. URL: http://cdn.energymicro.com/dl/pdf/efm32\_introduction\_ white\_paper.pdf.

- P. R. Luszczek, D. H. Bailey, J. J. Dongarra, J. Kepner, R. F. Lucas, R. Rabenseifner and D. Takahashi. 'The HPC Challenge (HPCC) benchmark suite'. In: *Proceedings of the 2006 ACM/IEEE conference on Supercomputing*. 2006, p. 213.

- [18] J. Preshing. A Look Back at Single-Threaded CPU Performance. Feb. 2012. URL: http://preshing.com/20120208/a-look-back-at-singlethreaded-cpu-performance.

- [19] Qualcomm. *Qualcomm Snapdragon Processors*. 2013. URL: http://www.qualcomm.com/snapdragon.

- S. Rixner, W. J. Dally, U. J. Kapasi, P. Mattson and J. D. Owens. 'Memory access scheduling'. In: ACM SIGARCH Computer Architecture News. Vol. 28.

2. ACM. 2000, pp. 128–138.

- [21] Samsung. Samsung SGH-D500 Service Manual. Nov. 2004. URL: http: //www.manualslib.com/manual/261262/Samsung-Sgh-Sgh-D500. html?page=8#manual.

- [22] R. R. Schaller. 'Moore's law: past, present and future'. In: *Spectrum, IEEE* 34.6 (1997), pp. 52–59.

- [23] L. Semiconductor. iCE40 LP/HX Family Data Sheet. Oct. 2017. URL: http://www.latticesemi.com/~/media/LatticeSemi/Documents/ DataSheets/iCE/iCE40LPHXFamilyDataSheet.pdf.

- [24] D. E. Shaw, M. M. Deneroff, R. O. Dror, J. S. Kuskin, R. H. Larson, J. K. Salmon, C. Young, B. Batson, K. J. Bowers, J. C. Chao et al. 'Anton, a special-purpose machine for molecular dynamics simulation'. In: ACM SIGARCH Computer Architecture News. Vol. 35. 2. ACM. 2007, pp. 1–12.

- [25] J. E. Smith. 'Decoupled access/execute computer architectures'. In: ACM SIGARCH Computer Architecture News. Vol. 10. 3. IEEE Computer Society Press. 1982, pp. 112–119.

- [26] O. O. Storaasli. *Accelerating genome sequencing 100-1000X with FPGAs.* Tech. rep. Oak Ridge National Laboratory (ORNL), 2008.

- [27] M. Taylor. 'A Landscape of the New Dark Silicon Design Regime'. In: vol. PP. 99. 2013, pp. 1–1. DOI: 10.1109/MM.2013.90.

- [28] J. Teich. 'Hardware/software codesign: The past, the present, and predicting the future'. In: *Proceedings of the IEEE* 100.Special Centennial Issue (2012), pp. 1411–1430.

- [29] Y. Umuroglu, N. J. Fraser, G. Gambardella, M. Blott, P. Leong, M. Jahre and K. Vissers. 'FINN: A Framework for Fast, Scalable Binarized Neural Network Inference'. In: *Proceedings of the 2017 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays*. ACM. 2017, pp. 65–74.

#### Bibliography

- [30] Y. Umuroglu and M. Jahre. 'A Vector Caching Scheme for Streaming FPGA SpMV Accelerators'. In: *Applied Reconfigurable Computing*. Vol. 9040. 2015.

- [31] Y. Umuroglu and M. Jahre. 'An Energy Efficient Column-Major Backend for FPGA SpMV Accelerators'. In: *Computer Design, IEEE Int. Conf. on.* 2014.

- [32] Y. Umuroglu and M. Jahre. 'Random Access Schemes for Efficient FPGA SpMV Acceleration'. In: *Microprocessors and Microsystems* 47 (2016), pp. 321–332.

- [33] Y. Umuroglu and M. Jahre. 'Streamlined Deployment for Quantized Neural Networks'. In: *arXiv preprint arXiv:1709.04060* (2017).

- [34] Y. Umuroglu, D. Morrison and M. Jahre. 'Hybrid Breadth-First Search on a Single-Chip FPGA-CPU Heterogeneous Platform'. In: *Field Programmable Logic and Applications (FPL), 2015 25th International Conference on.* 2015.

- [35] Wikipedia. Nokia 9000 Communicator. Feb. 2013. URL: http://en. wikipedia.org/wiki/Nokia\_9000\_Communicator.

- [36] Wikipedia. Nokia N810. Sept. 2013. URL: http://en.wikipedia.org/w/ index.php?title=Moto\_X.

- [37] Wikipedia. Nokia N810. Aug. 2013. URL: http://en.wikipedia.org/ wiki/Nokia\_N810.

- [38] Wikipedia. Treo 650. Feb. 2013. URL: http://en.wikipedia.org/wiki/ Treo\_650.

- [39] S. Williams, A. Waterman and D. Patterson. 'Roofline: an insightful visual performance model for multicore architectures'. In: *Communications of the ACM* 52.4 (2009), pp. 65–76.

- [40] Xilinx Inc. 'Vivado Design Suite User Guide: High-Level Synthesis'. In: *White Paper* (2016).

# Part B

# Part B.

# Sparse Linear Algebra

# 1. Introduction

# 1.1. On Sparsity

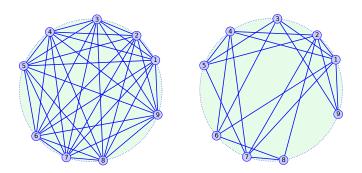

Viewing the universe that we live in as entities and their interactions is a useful model [9] for analyzing it. At the non-quantum scale, the myriad entities in our universe –be they physical objects or abstract concepts– are often *sparsely connected*: not everything directly interacts with (or is directly related to) everything else. For instance, the human brain contains approximately  $9 \cdot 10^7$  neurons, but each neuron is connected to only 7000 other neurons on average [26]. Similarly, Wikipedia had 2.3 million articles but an average of about 24 links per article in 2008 [24].

Figure 1.1 illustrates the concepts of dense and sparse connections using two ninenode graphs. Sparse structures are often represented as sparse matrices where zero entries correspond to unconnected entity pairs, as exemplified in Figure 1.2. Sparse matrix representations can be found in many contexts and domains, including in neural networks [42], graph and network analysis [15], computational biology and chemistry, electronic design automation, N-body simulations and structural mechanics [22].

Figure 1.1.: Examples of dense and sparse connections, illustrated as graphs.

#### 1. Introduction

Figure 1.2.: Sparsity patterns of six example matrices from [22].

# 1.2. Sparse Kernels

Although any sparse structure can be represented as an equivalent dense structure with zero-weight links and computed as such, sparse representation presents a much smaller memory footprint and requires less computation, making it possible to scale to larger problem instances. In many cases, the part of the computation that operates directly on sparse data is similar and can be viewed as a pattern of computation and communication –a *sparse linear algebra kernel*– in the spirit of the Berkeley Dwarfs [3].

As sparse kernels arise in a variety of important domains, it is beneficial to be able to handle them in a fast and efficient manner. However, their idiosyncratic computational properties (discussed further in Section 2.3) align poorly with the design choices of general-purpose computers, which leads to underutilization of hardware resources when processing sparse linear algebra kernels on general-purpose CPUs. This makes sparse linear algebra a good match with the criteria for choice of acceleration domains specified in Part A Section 1.2, and justify its selection as a focus area in this thesis.

# 2. Background

### 2.1. Sparse Matrix–Vector Multiplication

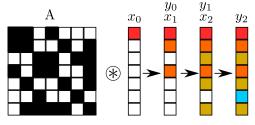

*Sparse Matrix–Vector Multiplication (SpMV)* is a fundamental operation in sparse linear algebra, and an important computational kernel used in numerous areas of science and engineering. Perhaps the most well-known usage area for the kernel is the iterative solving of sparse linear systems that arise from the modeling of physical phenomena, where SpMV operations dominate the execution time [70]. The SpMV operation  $\vec{y} = \mathbf{A} \cdot \vec{x}$  consists of multiplying an  $m \times n$  sparse matrix  $\mathbf{A}$  with *NZ* nonzero elements by a dense vector  $\vec{x}$  of size n to obtain a result vector  $\vec{y}$  of size m. A more specialized case of SpMV occurs when the vector  $\vec{x}$  is also sparse, which is deemed *Sparse Matrix–Sparse Vector Multiplication (SpMSpV)*. In this thesis, SpMV is studied both as a stand-alone kernel and as a pattern or building block for other algorithms and applications.

The sparse matrix is commonly stored in a format which allows storing only the nonzero elements of the matrix. This can be done via a variety of different storage formats; here we only present the widely-adopted Compressed Sparse Row (CSR) format. The CSR format, which is exemplified in Figure 2.1b, consists of three one-dimensional arrays: a values array to store the nonzero values in row-major order, a colind array to store the column index of each nonzero, and a rowptr array which points to the start of each row in the values array. Many other formats also exist, which try to take advantage of particular shapes that may exist in the sparsity pattern [40, 65]. The vectors  $\vec{x}$  and  $\vec{y}$  are stored as standard one-dimensional arrays x and y, unless they are sparse, in which case a CSR-like representation may be used for them as well.

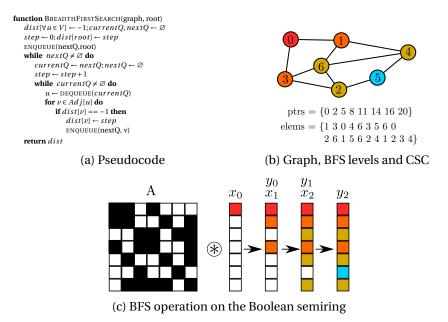

## 2.2. Breadth-First Search as Sparse Linear Algebra

The "matrices over semirings" concept [38] can be used to express graph processing operations as sparse linear algebra operations, thereby increasing the range of applications that a sparse linear algebra accelerator can address. We now give a brief overview of how this can be done for BFS. BFS is a key building block for exploring

#### 2. Background

|                                                 |     |     | rowptr={0 1 3 5}             |

|-------------------------------------------------|-----|-----|------------------------------|

| $\begin{bmatrix} 1.1 \\ 0 \\ 4.4 \end{bmatrix}$ | 0   | 0 ] | values={1.1 2.2 3.3 4.4 5.5} |

| 0                                               | 2.2 | 3.3 | colind={0 1 2 0 2}           |

| 4.4                                             | 0   | 5.5 |                              |

(a) Sparse matrix

(b) CSR representation

$$\begin{bmatrix} 1.1 & 0 & 0 \\ 0 & 2.2 & 3.3 \\ 4.4 & 0 & 5.5 \end{bmatrix} \cdot \begin{bmatrix} 0 \\ -1 \\ 2 \end{bmatrix} = \begin{bmatrix} 0 \\ 4.4 \\ 11.0 \end{bmatrix}$$

(c) The SpMV operation.

| [1.1 | 0   | 0   | [0] |   | [ 0 ]                                        |  |

|------|-----|-----|-----|---|----------------------------------------------|--|

| 0    | 2.2 | 3.3 | -1  | = | -2.2                                         |  |

| 4.4  | 0   | 5.5 | 0   |   | $\begin{bmatrix} 0\\ -2.2\\ 0 \end{bmatrix}$ |  |

(d) The SpMSpV operation.

Figure 2.1.: Sparse matrix representations, SpMV and SpMSpV.

graphs, and is fundamental to a variety of graph metrics such as counting connected components, calculating graph diameter and radius [18]. Consider an undirected, unweighted graph of the form G = (V, E) with sets of |V| vertices (nodes) V and |E| edges E. A BFS begins at a root node  $v_r$  contained within the largest connected component  $V_c$  and traverses each edge  $e_{rj}$  for every neighbor  $v_j$ . As such, the graph is traversed in *levels*, where all nodes at each level are explored before the next level is processed. Here, we consider the variant of the kernel that produces the distance array (dist of each visited node from the root node as the output. Large real-world networks are generally sparse, meaning that most nodes are not neighbors. To take advantage of this, the graph is typically stored in a sparse adjacency matrix form such as CSR as illustrated in Figure 2.2a.

The core idea in bridging BFS and sparse linear algebra is to substitute the number data type and the operators for multiplication and addition in linear algebra to express a variety of algorithms as matrix-vector operations. Specifically, we make use of the matrix-times-vector operation on the Boolean semiring to perform BFS. In practice, this operation "multiplies" a binary matrix and a binary vector, with the regular multiply and add operations substituted with the Boolean AND and OR operators, respectively. To disambiguate from regular matrix-vector multiply over real numbers, we use  $\circledast$  to denote this operator. As illustrated in Figure 2.2b, each  $y_t = A \circledast x_t$  operation

#### 2.3. Computational Properties

$\begin{array}{l} \mathrm{ptrs} = \{ 0 \ 2 \ 5 \ 8 \ 11 \ 14 \ 16 \ 20 \} \\ \mathrm{elems} = \{ 1 \ 3 \ 0 \ 4 \ 6 \ 3 \ 5 \ 6 \ 0 \\ 2 \ 6 \ 1 \ 5 \ 6 \ 2 \ 4 \ 1 \ 2 \ 3 \ 4 \} \end{array}$

(a) Graph, BFS levels and CSR representation

(b) BFS operation on the Boolean semiring

Figure 2.2.: Two representations of the breadth-first search algorithm.

corresponds to a breadth-first step, and each result vector  $y_t$  is the representation of the visited nodes in the graph after step t. The matrix A in the operation is the adjacency matrix of the graph, while the initial input vector  $x_0$  is initialized to all zeroes, except a single 1 at the location of the root node. The result vector  $y_t$  is used as the input vector  $x_{t+1}$  of the next step, which in turn generates more visited nodes in its result vector until the result converges (i.e., no more nodes can be visited).

# 2.3. Computational Properties

Sparse linear algebra is a well-studied acceleration target on a variety of architectures, including multi-core CPUs [70], General-Purpose Graphics Processing Units (GPGPUs) [10] and FPGAs [25]. The general computational properties of sparse linear algebra as reported by prior work can be summarized as follows:

• Low arithmetic intensity. Arithmetic intensity is a measure of how many computational operations are performed for every byte read from memory. Sparse computations have typically much lower arithmetic intensity [71] compared to dense ones, which makes their performance dependent on memory bandwidth. This is partially due to the way sparsity is represented (i.e., the positions of the

#### 2. Background

connections need to be specified, in addition to values), and partially due to sparsity itself (i.e., a read element will not be re-used many times, since it does not have many connections).

- **Sparsity-dependent, complex memory access patterns.** The sparsity pattern decides where memory accesses will take place. For structured sparsity, this will translate into strided accesses, whereas irregular sparsity will result in seemingly random accesses, which the memory system must cope with [68].

- **Dynamic behavior.** The sparsity pattern will also influence the dependencies and amount of work available in the computation. For instance, when traversing a small-world graph, the amount of work that can be done in parallel changes every iteration in a sparsity-dependent manner [8]. From a parallel computing perspective, this makes workload distribution and load balancing more difficult.

- **Dependent on large, external memory.** Sparse data can be very large in size and has tended to grow even larger over time, in part due to the Big Data trend [15]. Sparse computation therefore requires access to a large, external memory. Combined with irregular memory accesses and low arithmetic intensity, this creates a significant challenge in designing memory systems for sparse computation, since today's external memory devices are optimized for sequential accesses.

- Iterative. Most applications that make use of SpMV do so in an iterative fashion, multiplying the same sparse matrix with many different vectors. A typical example is iterative solving of sparse linear systems, where each iteration involves multiplying the same sparse matrix with a different vector [70]. This makes it possible to ameliorate the cost of preprocessing the sparse matrix across multiple iterations, if each iteration becomes faster as a result of the preprocessing.

# Paper B1

An Energy Efficient Column-Major Backend for FPGA SpMV Accelerators

Yaman Umuroğlu and Magnus Jahre

Published in Proceedings of the 2014 IEEE International Conference on Computer Design (ICCD)

# B1. An Energy Efficient Column-Major Backend for FPGA SpMV Accelerators

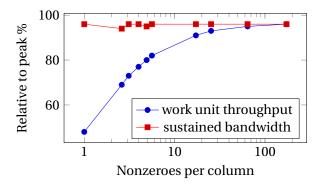

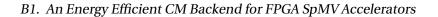

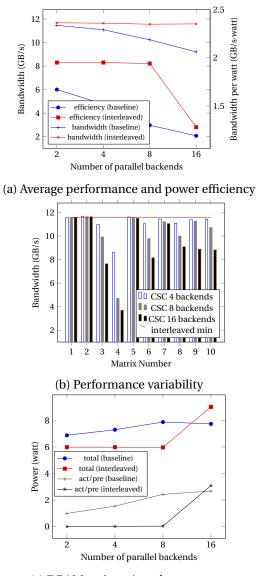

Abstract. FPGAs are promising candidates for energy efficient acceleration of sparse matrix-vector multiplication (SpMV), a kernel with important applications in scientific computing and engineering. SpMV is characterized by matrix-dependent performance and high external memory bandwidth demands, which makes bandwidth utilization an important performance indicator. Existing FPGA SpMV accelerators focus on datapath optimizations instead of memory behavior, and exhibit matrix-dependent bandwidth utilization. In this work, we propose to decouple the SpMV computation and memory behavior, and focus on the backend which handles the latter. We describe a scalable backend architecture that exploits column-major traversal and interleaving to achieve high bandwidth utilization. Our experiments show that a single backend is able to sustain 96% of its assigned memory port bandwidth on average, and scales well with increased bandwidth by instantiating multiple parallel units. Compared to a baseline scheme, our scheme offers up to 1.5x higher DRAM power efficiency and up to 20% higher aggregate bandwidth. The results indicate that our scheme improves the average bandwidth utilization of existing FPGA SpMV accelerators by 15 to 77%.

# **B1.1.** Introduction

With the phenomenon of dark silicon limiting the performance increase for microprocessors [57], specialized accelerator architectures are becoming a popular enhancement to computing systems. These accelerators can offer high energy efficiency and performance for the computational kernels they target. Sparse matrix-vector multiplication (SpMV) is an important computational kernel used in numerous areas of science and engineering. Perhaps the most well-known usage area for the kernel is

#### B1. An Energy Efficient CM Backend for FPGA SpMV Accelerators

the iterative solving of sparse linear systems that arise from the modeling of physical phenomena, where SpMV operations dominate the execution time [70]. Despite its prevalence, SpMV is notorious for its poor performance on microprocessors, which can be mainly attributed to the following properties of the kernel [29]:

- 1. *Memory-to-computation ratio:* SpMV has a low ratio of floating point operations per byte since it performs  $O(n^2)$  operations on  $O(n^2)$  amount of data. This property makes the kernel memory-intensive and sensitive to memory bandwidth.

- 2. *Irregular memory accesses:* The most popular way of storing sparse matrices is to store only the nonzero entries, which causes irregular accesses to the vector and makes the performance sensitive to the distribution of nonzeroes of the matrix.

Additionally, the input data size used in the aforementioned applications can be very large and is typically stored in high-latency high-capacity external DRAM [30], which magnifies the effects of performance sensitivity to input patterns and bandwidth. These challenges have made SpMV a popular research topic, and numerous methods for increasing performance on general-purpose microprocessors have been proposed [66, 70].

With large memory bandwidth and latency-hiding multithreading techniques, GP-GPUs were shown to be a viable candidate for accelerating SpMV [11]. FPGA-based implementations are another strong candidate for efficient SpMV acceleration, as one can create a customized architecture that aligns well with the requirements of the kernel. Competitive floating-point performance, ample parallelism and high external bandwidth owing to the large pin count are additional motivators for FPGA SpMV accelerators. A number of FPGA SpMV accelerators have already been proposed [31, 34, 39, 75] and demonstrate the potential of FPGAs as an SpMV acceleration substrate. However, many of these works focus on developing efficient floating-point accumulators and not on memory behavior. As a result, they under-utilize the available external memory bandwidth and suffer from matrix-dependent performance.

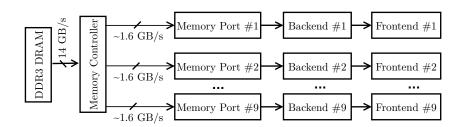

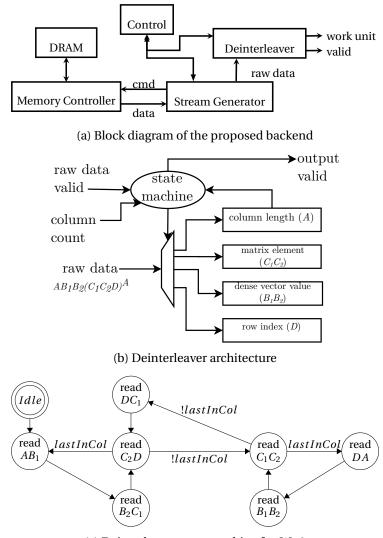

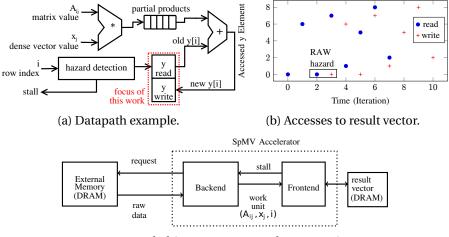

The key observation in this work is that SpMV accelerators should be designed with focus on the main performance bottleneck: memory bandwidth. In order to achieve this, we decouple the computation from the memory behavior and choose columnmajor matrix traversal to ensure sequential access patterns on the input data. We analyze SpMV–DRAM interaction with regard to parallelism and data layout. Based on our observations, we propose an architecture that is able to exhibit consistently high bandwidth utilization and good scaling with increasing DRAM banks. Our experiments show that the proposed scheme can consume 96% of the memory bandwidth, with improvements of up to 1.5x in power efficiency and 20% in bandwidth utilization compared to the baseline.

This work makes the following contributions:

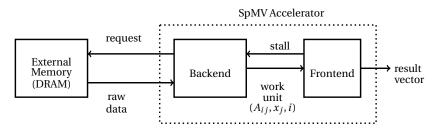

- We introduce a component-based design strategy for SpMV accelerators, with a *frontend* handling the computation and a *backend* for the memory behavior to enable independent optimization.

- We analyze SpMV memory behavior with the compressed sparse column layout and show that SpMV exhibits matrix- and parallelism-dependent performance.

- We design a scalable backend architecture that utilizes an interleaved data layout, and present its experimental evaluation to show it achieves up to 96% in average DRAM bandwidth utilization and up to 1.95 GB/s·watt in power efficiency.

## **B1.2. Background**

An SpMV operation  $\vec{y} = \mathbf{A} \cdot \vec{x}$  consists of multiplying an  $m \times n$  sparse matrix  $\mathbf{A}$  with NZ nonzero elements by a dense vector  $\vec{x}$  of size n to obtain a result vector  $\vec{y}$  of size m. The sparse matrix is commonly stored in a format which allows storing only the nonzero elements of the matrix. This can be done via a variety of different storage formats; here we only present the widely-adopted Compressed Sparse Row (CSR) format [29], and its column-major counterpart Compressed Sparse Column (CSC). The CSR format, which is exemplified in Figure B1.1b, consists of three one-dimensional arrays: a values array to store the nonzero values in row-major order, a colind array to store the column index of each nonzero, and a rowptr array which points to the start of each row in the values array. The CSC format is the column-major equivalent of CSR and is shown in Figure B1.1c. The vectors  $\vec{x}$  and  $\vec{y}$  are stored as one-dimensional arrays x and y.

We define two basic data types, *ValueType* and *IndexType*, that are used in a CSC or CSR SpMV operation. *ValueType* is typically a double-precision floating-point value, representing each element of the *values* array of the matrix and vectors. *IndexType* is for expressing element indices or counts in the storage structures, such as the *rowptr* or *colind* arrays. A four-byte integer is sufficient for indexing matrices of up to  $2^{32}$  nonzeroes. In line with previous work [29, 30], we assume *sizeof(ValueType)* = *ValSize* = 8 and *sizeof(IndexType)* = *IndSize* = 4 throughout the rest of this paper.

B1. An Energy Efficient CM Backend for FPGA SpMV Accelerators

rowptr={0 1 3 5} [1.1 0 0 values={1.1 2.2 3.3 4.4 5.5} 2.2 3.3 0 colind={0 1 2 0 2} 0 5.5 4.4 (a) Sparse matrix (b) CSR representation colptr={0 2 3 5} values={1.1 4.4 2.2 3.3 5.5} rowind={0 2 1 1 2} (c) CSC representation

Figure B1.1.: CSR and CSC representations of a sparse matrix.

#### **B1.2.1. Memory Access Patterns**

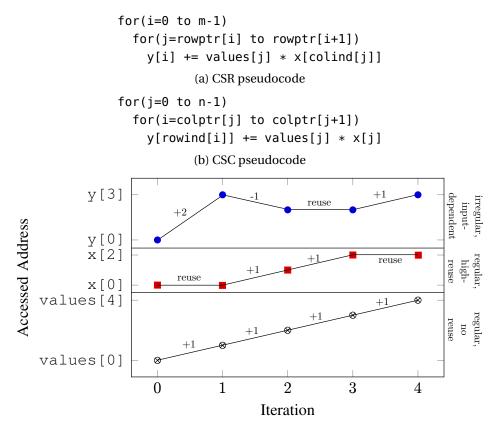

The SpMV kernel exhibits different memory access patterns on its working set. The input matrix representation is accessed in a sequential manner, although there is no temporal reuse for this data due to the properties of the kernel [29]. The vector accesses are dependent on the traversal type: one vector can be accessed sequentially and with maximum temporal locality, whereas the other vector requires indirect, input-dependent memory accesses for every operation. This can be observed from the pseudocode in Figures B1.2a and B1.2b. For column-major traversal, the result vector y is accessed based on the rowind array data and x is accessed sequentially; the converse is true for row-major access. Since these indirect access patterns are unknown prior to runtime, they may be considered *random accesses* from the perspective of the accelerator. The column-major accesses, the sequential maximum-reuse x accesses and the pattern-dependent y accesses can be observed.