# Vectorized Benchmarks for the Berkeley Dwarfs

**Christian De Frene**

Master of Science in Computer ScienceSubmission date:July 2017Supervisor:Magnus Jahre, IDICo-supervisor:Juan Manuel Cebrian Gonzalez, Barcelona Supercomputing Center,<br/>Spain

Norwegian University of Science and Technology Department of Computer Science

## Problem description

## Vectorized Benchmarks for the Berkeley Dwarfs

Benchmarking is the standard method for conducting scientific experiments in computer science. Researchers decide on a selection of benchmarks which are a representative of applications of interest. These benchmarks are studied in detail to uncover generalized insights that can then be applied to real computer systems. It is critical that the selected benchmarks cover a wide range of software applications to ensure that the uncovered insights have high validity.

Cebrian et al. (ISPASS 2014) observed that vectorized benchmarks change key architectural trade-offs compared to scalar implementations. For this reason, they proposed ParVec which consists of vectorized versions of a subset of the well-known PARSEC benchmarks. Unfortunately, ParVec and PARSEC only partly cover the classes of widely deployed parallel programs (as exemplified by the Berkeley Dwarfs). This is the main motivation for the SIMDwarfs effort which aims to provide the research community with a set of SIMD-enabled applications and kernels that cover the Berkeley Dwarfs.

The student will contribute to the SIMDwarfs effort by adding vectorized benchmark implementations for selected Berkeley Dwarfs. The missing dwarfs are "N-Body Methods", "Dynamic Programming", "Backtrack and Branch-and-Bound", "Graphical Models" and "Finite State Machines". For each added benchmark, the student should evaluate its performance and scalability as well as identify potential architectural bottlenecks. When possible, the student should improve the benchmark implementation to reduce the impact of the identified bottleneck.

#### Advisor: Magnus Jahre, IDI

Co-advisor: Juan Manuel Cebrián González, Barcelona Supercomputing Center (BSC)

## Abstract

In order to guide development of new hardware that meet ever increasing needs, researchers and system designers need high quality performance evaluation tools. In computer science, benchmarking has emerged as one of the most important methods for this purpose. Multiple benchmarks that collectively evaluate a system for a wide range of characteristics in a specific area of interest are compiled into benchmark suites. The purpose is to increase the chances that insight of high validity can be leveraged, i.e. the insight is of high enough accuracy to be applied to real computer systems. The Berkeley dwarfs taxonomy, which are 13 computational patterns in widespread use in the fields of science and engineering, can be used for this purpose.

From the start of the 21st century, as conventional instruction-level parallelism has failed to provide further microprocessor performance increases, the industry has been looking for ways to exploit other types of parallelism as well. One of these is datalevel parallelism, found in the single input multiple data (SIMD) computer organization. Research shows that using vectorization can offer more benefits, e.g. increased energy efficiency. However, while SIMD is seeing increased adoption today, [Cebrian, Jahre, et al. 2014] noticed that SIMD-aware benchmarking tools are not as widely available, which they argue can cause SIMD designers to under/over estimate the impact of their contributions. For this reason, they proposed SIMDwarfs, aiming to offer the research community with a SIMD-aware benchmark suite covering all 13 Berkeley dwarfs.

In this thesis we have contributed to SIMDwarfs by analyzing four retrieved, vectorized benchmark implementations from three uncovered dwarfs: nbody from n-body methods, nqueens from backtrack and branch-and-bound, and NW and SWat from dynamic programming. All implementations were evaluated using non-vectorized configurations and configurations utilizing SSE and AVX SIMD extensions. The results indicated that while vectorization offered improved performance, the hardware used for the evaluations limited further performance increases. With these implementations added, SIMDwarfs now cover 10 of 13 dwarfs.

## Sammendrag

For å veilede utviklingen av ny maskinvare som møter stadig økende behov, trenger forskere og systemdesignere høyverdige ytelsesevalueringsverktøy. I datavitenskapen har benchmarking trådd frem som en av de viktigste metodene til dette formålet. Flere benchmarks som sammenlagt evaluerer et system for et bredt spekter av egenskaper i et bestemt område av interesse, blir samlet inn i benchmark-suiter. Hensikten er å øke sjansene for at innsikt av høy validitet kan utnyttes, dvs. innsikt er av høy nok nøyaktighet til å kunne brukes på ekte datasystemer. Berkeleys dvergetaksonomi, som er 13 beregningsmønstre i utbredt bruk innen vitenskap og industri, kan brukes til dette formålet.

Fra begynnelsen av det 21. århundre, da konvensjonell instruksjonsnivå parallellisme har sluttet å gi ytterligere ytelseøkninger for mikroprosessorer, har industrien vært på utkikk etter måter å utnytte andre typer parallellisme. En av disse er data-nivå parallellisme, funnet i single input multiple data (SIMD) datamaskinorganisasjonen. Forskning viser at bruk av vektorisering kan tilby flere fordeler, f.eks. økt energieffektivitet. Imidlertid, mens SIMD ser økt utbredelse i dag, merket [Cebrian, Jahre, et al. 2014] at SIMD-bevisste benchmarkingverktøy ikke er allment tilgjengelige. Dette hevder de kan føre til at SIMD-designere under- eller overestimerer virkningen av deres bidrag. Av denne grunn foreslo de SIMDwarfs, med sikte på å tilby forskningsmiljøet en SIMD-bevisst benchmark-suite som dekker alle 13 Berkeley-dvergene.

I denne oppgaven har vi bidratt til SIMDwarfs ved å analysere fire funnede, vektoriserte benchmarkimplementeringer fra tre udekkede dverger: nbody fra n-body methods, nqueens fra backtrack and branch-and-bound, og NW og SWat fra dynamic programming. Alle implementeringer ble evaluert ved hjelp av ikke-vektoriserte konfigurasjoner og konfigurasjoner ved bruk av SSE- og AVX SIMD-utvidelser. Resultatene viste at mens vektorisering tilbød forbedret ytelse, hindrer maskinvaren som brukes til evalueringene, ytterligere ytelsesforbedringer. Med disse implementasjonene lagt til, dekker SIMDwarfs nå 10 av 13 dverger.

# Preface

This is the outcome of my master thesis in Computer Science at NTNU. It is a continuation of my specialization project that I worked on during fall 2016.

# Acknowledgements

I would like to thank my two advisors, Magnus Jahre and Juan Manuel Cebrián González, for all their valuable insight and helpful suggestions on the theoretical and technical aspects of both this thesis and the specialization project that led up to it.

# Table of contents

| $\mathbf{Pr}$ | oble                                                                                                      | m Description                                                                                                                        | i                                                                               |

|---------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Ał            | ostra                                                                                                     | ct (English)                                                                                                                         | ii                                                                              |

| Ał            | ostra                                                                                                     | ct (Norwegian) i                                                                                                                     | iii                                                                             |

| Pr            | eface                                                                                                     | e i                                                                                                                                  | iv                                                                              |

| Ac            | knov                                                                                                      | vledgements                                                                                                                          | iv                                                                              |

| Ta            | ble c                                                                                                     | of Contents                                                                                                                          | vi                                                                              |

| Lis           | st of                                                                                                     | Figures vi                                                                                                                           | iii                                                                             |

| Lis           | st of                                                                                                     | Tables                                                                                                                               | ix                                                                              |

| Lis           | st of                                                                                                     | Listings                                                                                                                             | x                                                                               |

| Ał            | obrev                                                                                                     | viations                                                                                                                             | xi                                                                              |

| 1             | $     \begin{array}{r}       1.1 \\       1.2 \\       1.3 \\       1.4 \\       1.5 \\     \end{array} $ | 2.1.4       SIMD in heterogeneous systems       1         Benchmarking       1         2.2.1       Benchmark Requirements       1    | <b>1</b><br>1<br>3<br>6<br>6<br>6<br><b>8</b><br>8<br>9<br>13<br>13<br>14<br>14 |

|               | 2.3                                                                                                       | Other Benchmark Suites       1         2.3.1       Suites used by SIMDwarfs       1         2.3.2       Miscellaneous suites       1 | 16<br>16<br>17                                                                  |

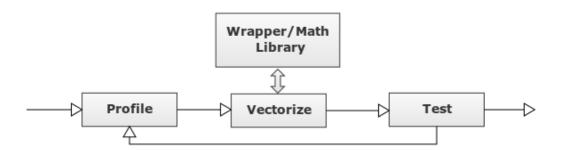

| 3             | Met<br>3.1<br>3.2<br>3.3<br>3.4                                                                           | Profiling   1     Wrapper Library   2     ParVec Framework   2                                                                       | 19<br>20<br>23<br>24                                                            |

|          |            | 3.4.1          | Input parameters                        | 24         |

|----------|------------|----------------|-----------------------------------------|------------|

|          |            | 3.4.2          | Experimental setup                      | 24         |

|          |            | 3.4.3          | Evaluation data                         | 24         |

| <b>4</b> | Ben        |                | 0 0                                     | <b>27</b>  |

|          | 4.1        | Algorit        | thm and Vectorization                   | 27         |

|          | 4.2        | Result         | s and Discussion                        | 28         |

|          |            | 4.2.1          | Runtime, Cycle and Instruction Count    | 29         |

|          |            | 4.2.2          | Stalls                                  | 30         |

|          |            | 4.2.3          | Cache Performance                       | 31         |

|          | 4.3        | Potent         | ial for Further Performance Improvement | 32         |

| <b>5</b> | Ben        | chmar          | k Analysis: N-queens                    | 34         |

|          | 5.1        |                | thm and Vectorization                   | 35         |

|          | 5.2        |                | s and Discussion                        | 36         |

|          |            | 5.2.1          | Runtime, Cycle and Instruction Count    | 36         |

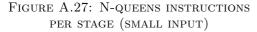

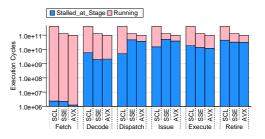

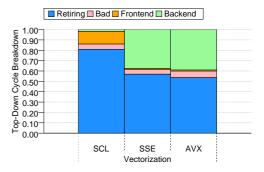

|          |            | 5.2.2          | Stalls                                  | 38         |

|          |            | 5.2.3          | Cache Performance                       | 39         |

|          | 5.3        | 0.2.0          | ial for Further Performance Improvement | 40         |

| 6        | Ben        | chmar          | k Analysis: NW and SWat                 | 41         |

| U        | 6.1        |                | thm and Vectorization                   | <b>4</b> 1 |

|          | 6.2        |                | Results and Discussion                  | 42         |

|          | 0.2        | 6.2.1          | Runtime, Cycle and Instruction Count    | 42<br>42   |

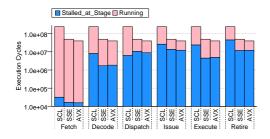

|          |            | 6.2.1          | Stalls                                  | 44<br>44   |

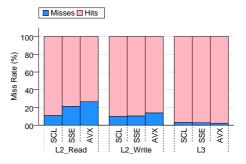

|          |            | 0.2.2<br>6.2.3 |                                         |            |

|          | <i>c</i> 9 | 0.2.0          | Cache Performance                       | 45         |

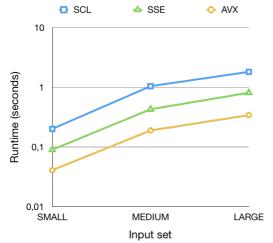

|          | 6.3        |                | Results and Discussion                  | 45         |

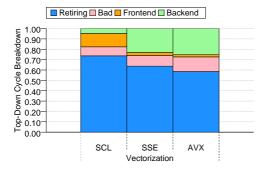

|          |            | 6.3.1          | Runtime, Cycle and Instruction Count    | 46         |

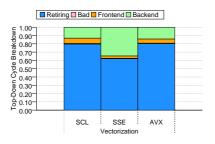

|          |            | 6.3.2          | Stalls                                  | 47         |

|          | ~ .        | 6.3.3          | Cache Performance                       | 48         |

|          | 6.4        | Potent         | ial for Further Performance Improvement | 49         |

| 7        | Con        |                |                                         | 50         |

|          | 7.1        | Future         | Work: Towards Complete Coverage         | 50         |

|          |            | 7.1.1          | Combinational Logic                     | 50         |

|          |            | 7.1.2          | Graphical Models                        | 51         |

|          |            | 7.1.3          | Finite State Machines                   | 51         |

|          | 7.2        | The Fu         | uture of SIMD Extensions                | 51         |

| Bi       | bliog      | raphy          |                                         | 53         |

| Aı       | open       | dices          |                                         | 58         |

| _        | -          |                | n Curell and Lange Transfe              | 00         |

| A        | -          |                | 8 I                                     | 60         |

|          | 1.1        |                | у                                       | 60         |

|          | 1.2        | -              | ens                                     | 64<br>62   |

|          | 1.3        |                | man-Wunsch                              | 68         |

|          | 1.4        | Smith-         | Waterman                                | 72         |

# List of Figures

| 1.1          | A comparison of the SIMD and MIMD organizations     |

|--------------|-----------------------------------------------------|

| 1.2          | Relative Performance Per Cycle                      |

| 1.3          | The Five 'Categories of Vectorization'              |

| 1.4          | Chapter Dependencies In This Thesis                 |

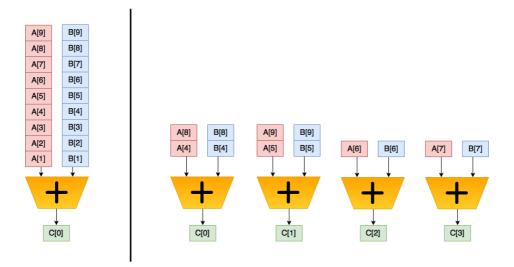

| 2.1          | Scalar vs. Vectorized Operations                    |

| 2.2          | Vector Operation Using One Lane and Four Lanes      |

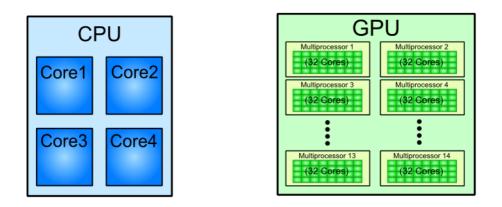

| 2.3          | Comparison of a typical CPU and GPU organization    |

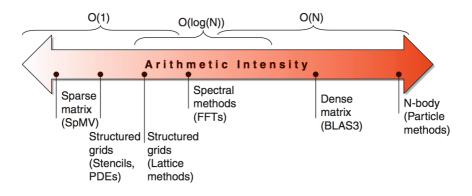

| 2.4          | Arithmetic Intensity                                |

| 3.1          | Verification process of SIMDwarfs benchmarks 19     |

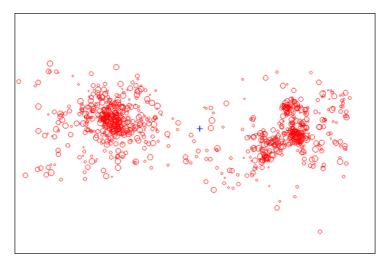

| 4.1          | 2D N-Body Simulation                                |

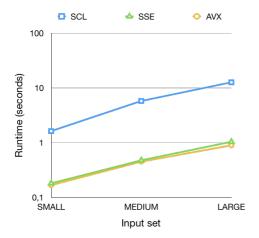

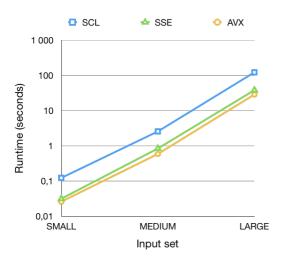

| 4.2          | N-Body Running Times for Three Input Sizes          |

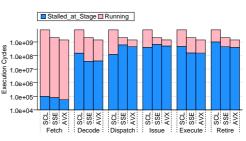

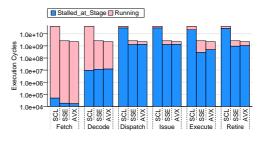

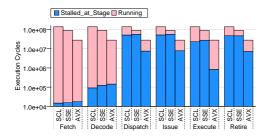

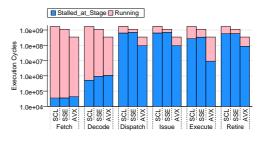

| 4.3          | N-Body Execution Cycles                             |

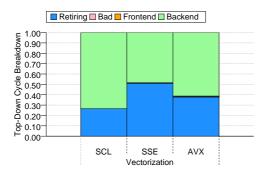

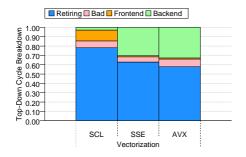

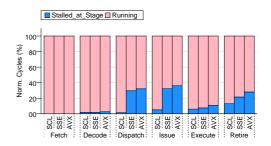

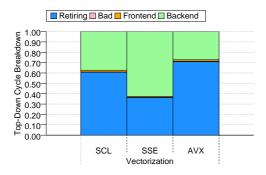

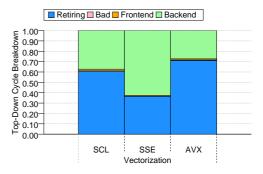

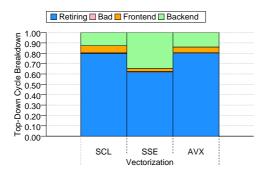

| 4.4          | N-Body Top-Down Cycle Breakdown                     |

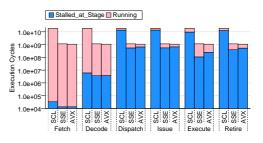

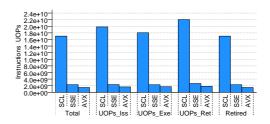

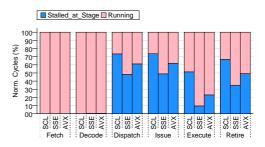

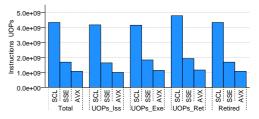

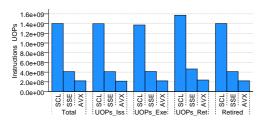

| 4.5          | N-Body Instructions Per Stage                       |

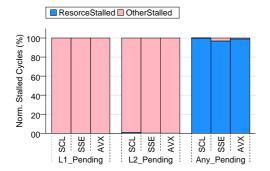

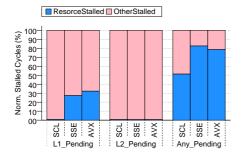

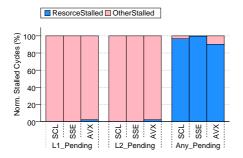

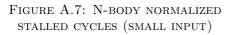

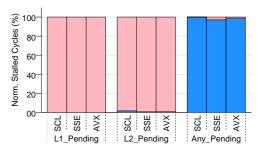

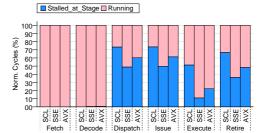

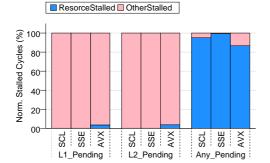

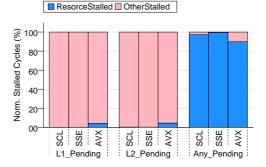

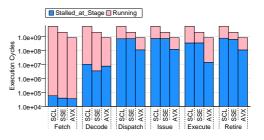

| 4.6          | N-Body Normalized Stalled Cycles                    |

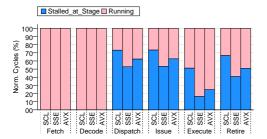

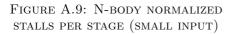

| 4.7          | N-Body Normalized Stalls Per Stage                  |

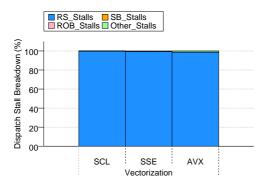

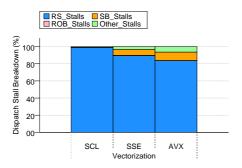

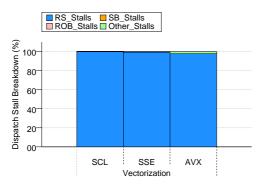

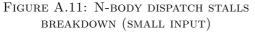

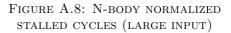

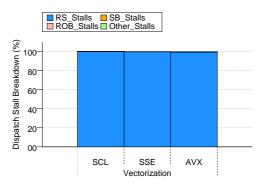

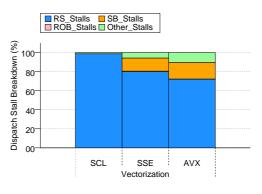

| 4.8          | N-Body Dispatch Stalls Breakdown                    |

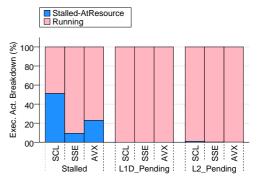

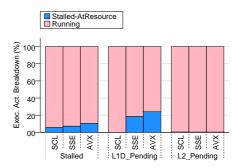

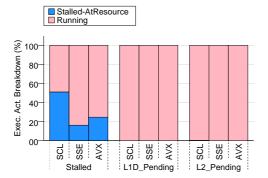

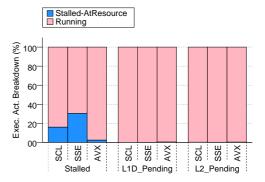

| 4.9          | N-Body Execution Activity Breakdown                 |

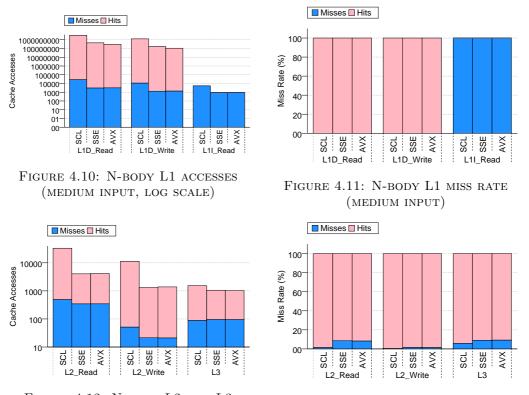

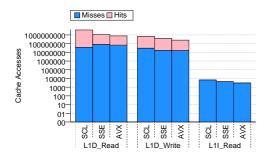

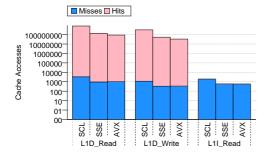

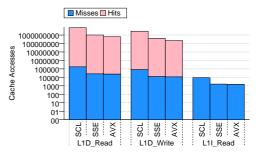

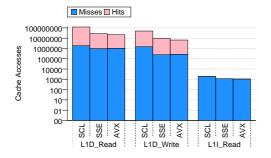

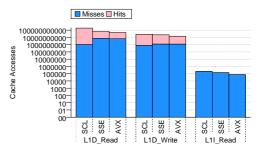

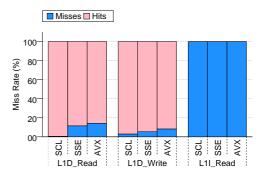

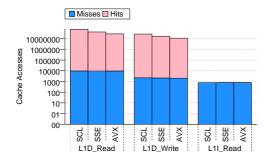

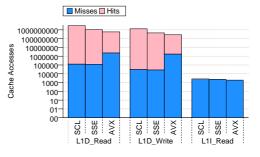

| -            | N-Body L1 Accesses                                  |

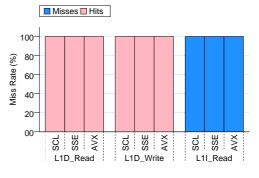

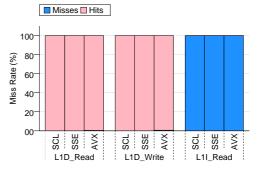

|              | N-Body L1 Miss Rate                                 |

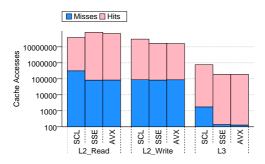

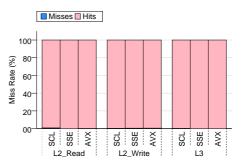

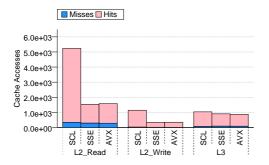

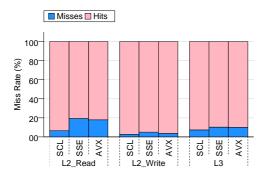

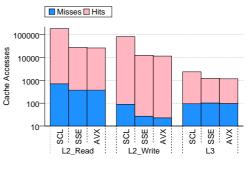

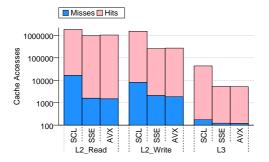

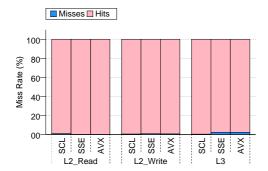

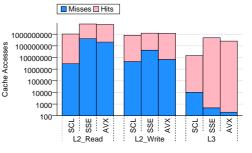

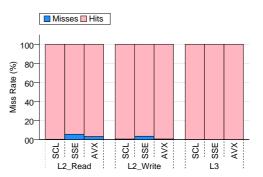

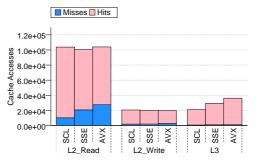

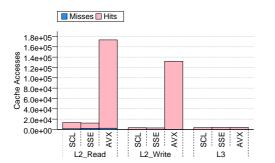

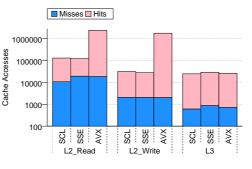

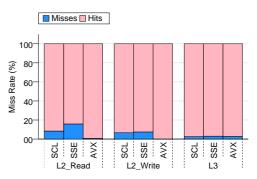

|              | N-Body L2 and L3 Accesses                           |

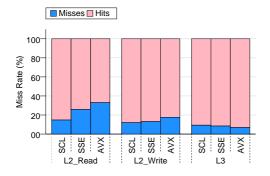

|              | N-Body L2 and L3 Miss Rates                         |

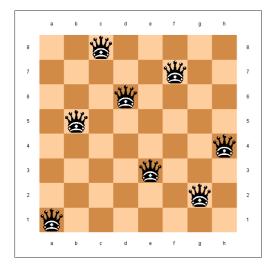

| 5.1          | 8-Queens Solution                                   |

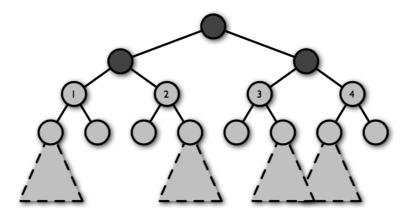

| $5.1 \\ 5.2$ | Computation Tree After Partial Breadth-First Search |

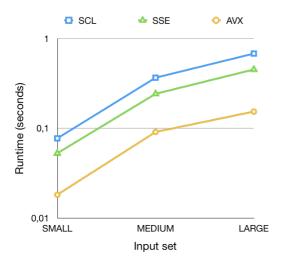

| 5.2<br>5.3   | N-Queens Running Times for Three Input Sizes        |

| $5.3 \\ 5.4$ | N-Queens Kunning Times for Three input Sizes        |

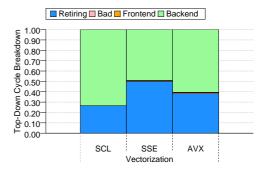

|              | U J                                                 |

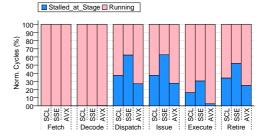

| 5.5          | N-Queens Top-Down Cycle Breakdown                   |

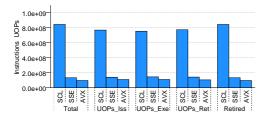

| 5.6          | N-Queens Instructions Per Stage                     |

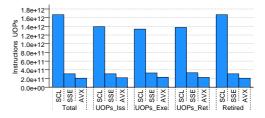

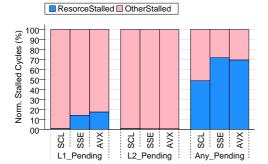

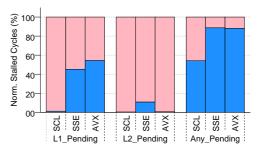

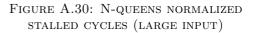

| 5.7          | N-Queens Normalized Stalled Cycles                  |

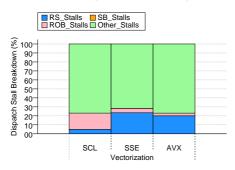

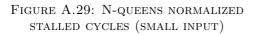

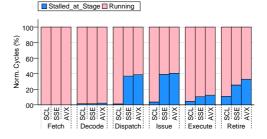

| 5.8          | N-Queens Normalized Stalls Per Stage                |

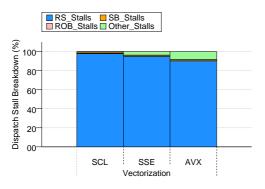

| 5.9          | N-Queens Dispatch Stalls Breakdown                  |

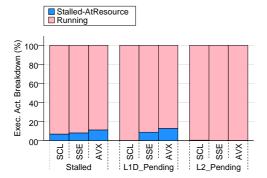

|              | N-Queens Execution Activity Breakdown               |

|              | N-Queens L1 Accesses                                |

|              | N-Queens L1 Miss Rate 39                            |

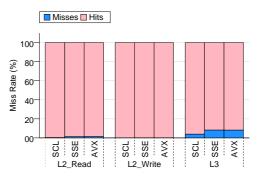

|              | N-Queens L2 and L3 Accesses                         |

| 5.14         | N-Queens L2 and L3 Miss Rates 39                    |

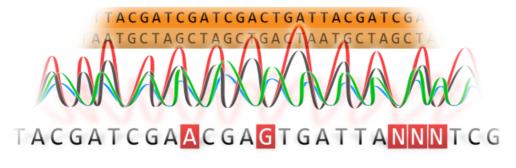

| 6.1          | Sequence Alignment                                  |

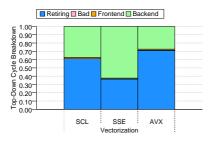

| 6.2          | NW Running Times for Three Inputs                   |

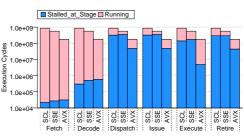

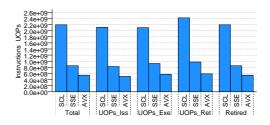

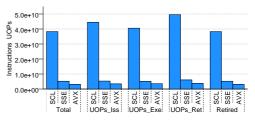

| 6.3  | NW Execution Cycles                 | 43 |

|------|-------------------------------------|----|

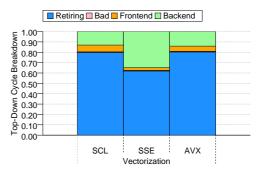

| 6.4  | NW Top-Down Cycle Breakdown         | 43 |

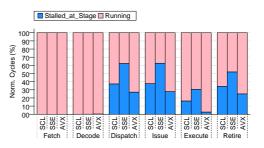

| 6.5  | NW Instructions Per Stage           | 43 |

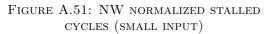

| 6.6  | NW Normalized Stalled Cycles        | 44 |

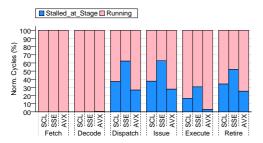

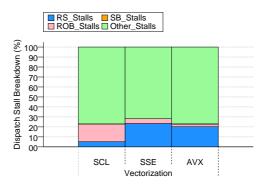

| 6.7  |                                     | 44 |

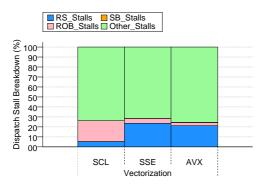

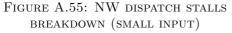

| 6.8  | NW Dispatch Stalls Breakdown        | 44 |

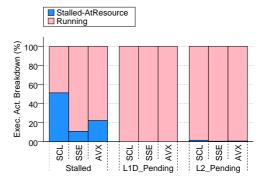

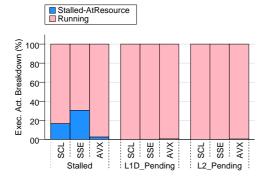

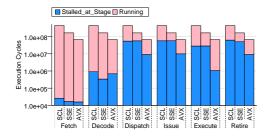

| 6.9  | NW Execution Activity Breakdown     | 44 |

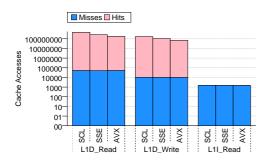

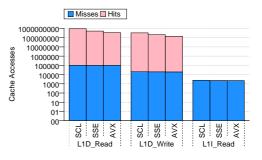

| 6.10 | NW L1 Accesses                      | 45 |

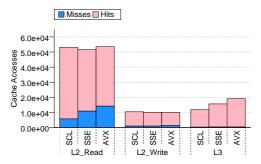

| 6.11 | NW L1 Miss Rate                     | 45 |

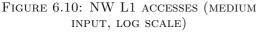

| 6.12 | NW L2 and L3 Accesses               | 45 |

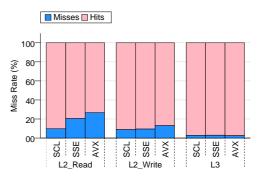

| 6.13 | NW L2 and L3 Miss Rates             | 45 |

| 6.14 | SWat Running Times for Three Inputs | 46 |

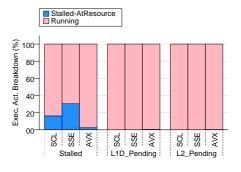

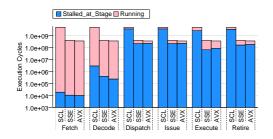

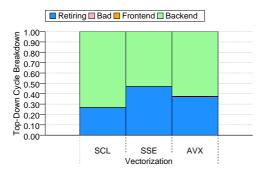

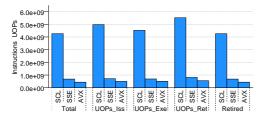

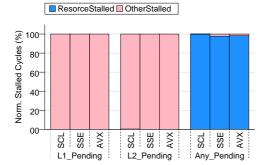

| 6.15 | SWat Execution Cycles               | 46 |

| 6.16 | SWat Top-Down Cycle Breakdown       | 46 |

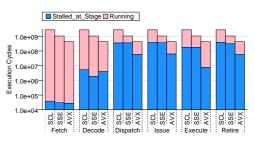

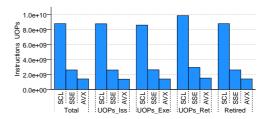

| 6.17 | SWat Instructions Per Stage         | 46 |

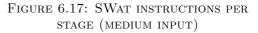

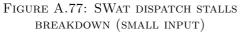

| 6.18 | SWat Normalized Stalled Cycles      | 47 |

|      |                                     | 47 |

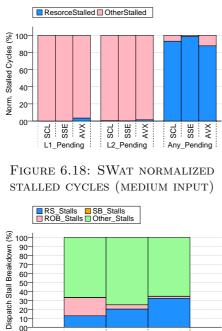

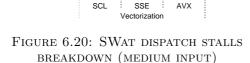

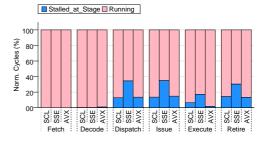

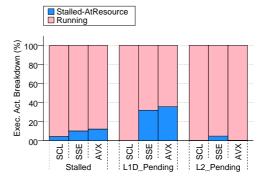

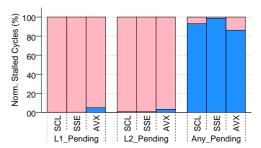

| 6.20 | SWat Dispatch Stalls Breakdown      | 47 |

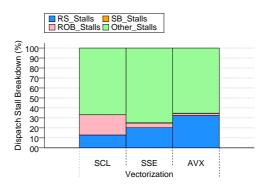

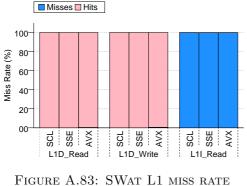

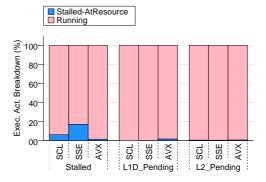

| 6.21 | SWat Execution Activity Breakdown   | 47 |

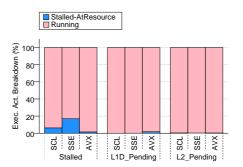

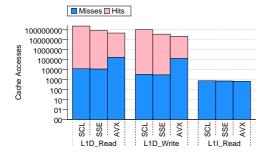

| 6.22 | SWat L1 Accesses                    | 48 |

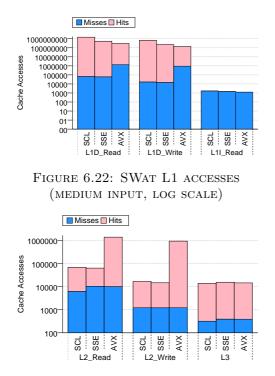

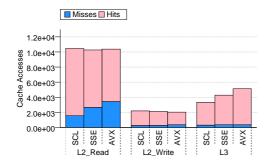

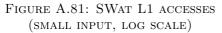

| 6.23 | SWat L1 Miss Rate                   | 48 |

| 6.24 | SWat L2 and L3 Accesses             | 48 |

| 6.25 | SWat L2 and L3 Miss Rates           | 48 |

# List of Tables

| 1.1 | Berkeley Dwarfs Table                               | 5  |

|-----|-----------------------------------------------------|----|

| 2.1 | Other Benchmark Suites' Dwarf Coverage              | 18 |

| 3.1 | Input Parameters For the Evaluated Benchmarks       | 24 |

| 4.1 | Runtime for Original and Improved Nbody Application | 28 |

| 5.1 | N-Queens Solutions up to N=22                       | 34 |

# List of Listings

| 1 | Code Using Intel's AVX Intrinsics     | 21 |

|---|---------------------------------------|----|

| 2 | ParVec Wrapper Library Contents       | 22 |

| 3 | Code Using the ParVec Wrapper Library | 22 |

| 4 | Using the Parsecmgmt Script           | 23 |

## Abbreviations

- **API** Application Programming Interface. A set of methods enabling communication between software components.

- AVX Advanced Vector eXtensions. 256-bit vector extensions for the x86 architecture.

- CPU Central Processing Unit. The main processor in a traditional microprocessor.

- **DLP** Data-Level Parallelism. Parallelism achieved by performing the same operation on independent data.

- GCC GNU Compiler Collection.

- **GPGPU** General-Purpose Graphics Processing Unit. Running conventional microprocessor applications on a GPU.

- **GPU** Graphics Processing Unit. An external or integrated processor specialized for graphics operations.

- **HPC** High-Performance Computing. Performing advanced computations efficiently, reliably and quickly.

- **ICC** Intel C++ Compiler.

- **ILP** Instruction-Level Parallelism. Parallelism achieved by performing multiple instructions independently.

- **ISA** Instruction Set Architecture. The set of instructions for a certain computer architecture.

- KNL Knights Landing. Code name for Intel's second generation Xeon Phi products.

- **MIMD** Multiple Input Multiple Data. Computer organization used in a typical multiprocessor.

- MMX MultiMedia eXtensions. 64-bit vector extensions for the x86 architecture.

- MIC Many Integrated Core. Architecture from Intel aimed at supercomputing.

- MVL Maximum Vector Length.

- **NW** Needleman-Wunsch. Algorithm for global sequence alignment.

- **ROB** Re-Order buffer. Helps perform out-of-order execution.

- ${\bf RS}\,$  Reservation Station. Enables fast access to newly computed data values.

- **SB** Store buffer. Allows the processor to speculate on store operations.

- SCL Scalar.

- **SIMD** Single Input Multiple Data. Computer organization used for GPUs and vector processors.

- SSE Streaming SIMD Extensions. 128-bit vector extensions for the x86 architecture.

- **SVE** Scalable Vector Extension. Novel SIMD extensions technology from ARM for their architectures.

- **SWAR** SIMD Within A Register. Packing processor words with multiple data values that can be operated on in parallel.

- SWat Smith-Waterman. Algorithm for local sequence alignment.

- **UOP** Micro-Operation. Detailed, low-level instruction derived from the processors input, the macro-operation.

# Chapter 1: Introduction

## 1.1 Motivation

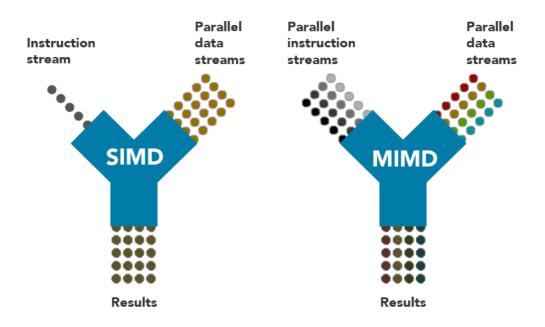

Flynn's taxonomy [Flynn 1972] defines four types of computer organizations based on their utilization of streams, i.e. instruction or data sequences that are operated on by the processor. The four organizations are single input single data (SISD), single input multiple data (SIMD), multiple input, single data (MISD) and multiple input multiple data (MIMD). Time has rendered both the SISD (uniprocessor) and MISD organizations obsolete, in favor of the more efficient, parallel organizations of SIMD and MIMD. An illustration of the workings of these two is shown in Figure 1.1. SIMD exploits data-level parallelism (DLP), defined by [David A. Patterson et al. 2014, sec. 6.3] as parallelism achieved by performing the same operation on independent data. MIMD has the ability to perform multiple, independent operations on separate data.

FIGURE 1.1: A COMPARISON OF THE SIMD AND MIMD ORGANIZATIONS

From the 1970's until the early 1990's, SIMD was widely deployed in supercomputers [Stringer 2016]. Various factors, including the rapid performance increase of commodity microprocessors in the 1980's, coupled with the advent of massive parallelism and distributed memory, high energy demands of large supercomputers, as well as lower prices, contributed to a shift in the industry from SIMD, using a few, powerful processors, to MIMD, using a higher number of less powerful processors that overall achieved higher performance [National Research Council and others 2005]. This move is still visible to-

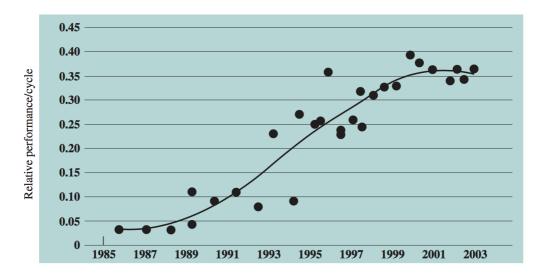

FIGURE 1.2: COMBINED CPU BENCHMARK RESULTS AND CLOCK FREQUENCIES OF INTEL HARDWARE. SOURCE: [STALLINGS 2013, SEC. 18.1]

day, with MIMD being found in most conventional general purpose microprocessors. In addition, [David A. Patterson et al. 2014] suggest that techniques such as instruction-level parallelism (ILP), which has helped deliver steady performance increases, has traditionally disinterested the industry outside of high-performance computing (HPC) to explore other computer organizations.

However, starting from the 2000's, using only ILP has not been able to further increase microprocessor performance. This is shown in Figure 1.2 which graphs the extent to which performance improvement is due to increased exploitation of ILP. Furthermore, Dennard scaling, which state that MOSFET power usage scale downward as we shrink the area, was discredited around 2006 due to current leakage and excess heat buildup severely limiting chip utilization [Esmaeilzadeh et al. 2011]. This has caused the industry to favor energy efficiency in contrast to performance for microprocessors, and an increasing number of system architects are starting to embrace SIMD because, as [Cebrian, Jahre, et al. 2014] explain, SIMD capabilities are a key component to maximize performance per watt in highly computational intensive applications.

The increased interest in SIMD products and technologies, such as graphics processing units (GPUs), have driven a rapid performance increase that now makes certain SIMD-type processors able to significantly outperform general purpose processors for some tasks [Lee et al. 2010]. This has also led to new developments in existing technologies that enable (limited) SIMD processing on MIMD-type microprocessors, new application programming interfaces (APIs) for GPUs that make them able to perform general purpose computations (GPGPUs), as well as the emergence of heterogeneous systems that try to combine the benefits or SIMD and MIMD, e.g Intel's Xeon Phi products.

One of the most important methods for performance evaluation of computing systems is *benchmarking*. A benchmark is a program chosen to measure performance and resource utilization in specific area of interest, and can provide insight that can be leveraged by scientists to aid the design of new and improved systems [Bienia 2011]. Multiple benchmarks are compiled into benchmark suites to evaluate various characteristics and behaviors of a system. However, despite the rising popularity of SIMD, fully SIMDenabled benchmarking tools have been mysteriously absent. [Cebrian, Jahre, et al. 2014] argue that SIMD applications exhibit different behavior than what can be leveraged from existing benchmarking tools, making it hard for the computer architecture community to propose novel techniques. For this reason, they developed the ParVec benchmark suite [Cebrian, Jahre, et al. 2015] by extending a subset of the benchmarks from the PARSEC benchmark suite [PARSEC n.d.] with SIMD capabilities.

Wishing to guide the development of hardware, software, and programming models that efficiently utilize parallelism, a group of computer scientists at Berkeley identified 13 computational patterns, called *dwarfs*, especially important within the fields of science and engineering [Asanovic et al. 2006]. This is a great foundation for a benchmark suite: by covering all dwarfs in this taxonomy, i.e. having at least 13 benchmarks each exhibiting a separate computational pattern, our benchmarking data offers a greater chance to provide us with insight of *high validity*. That is, the data provides a level of accuracy high enough to be applied to the real world.

Since ParVec does not provide complete coverage of the Berkeley dwarfs, Cebrian et al. decided to initiate the SIMDwarfs project<sup>1</sup> with the following goal: provide the research community with a set of SIMD-enabled applications and kernels that cover all 13 Berkeley Dwarfs. Previously, we have contributed to SIMDwarfs by performing a literature survey of benchmarks covered by the missing dwarfs. The subsequent sections of this chapter summarize what work was done previously, and how we continued the work over the course of this thesis. More information on SIMD, benchmarking and the Berkeley dwarfs can be found in Chapter 2.

## 1.2 Dwarf Coverage Table

Leading up to this thesis, we carried out a specialization project [De Frène 2016] whose aim was to survey benchmarks covered by dwarfs that we did not have any vectorized benchmark implementations for. The selected benchmarks originated from other, wellknown benchmark suites that only partly cover all 13 dwarfs, further discussed in Section 2.3. One of the outcomes of this project was a table that presents each dwarf and what benchmarks are covered by it. Each analyzed benchmark was assigned a 'category of vectorization', ranging from 1 to 5. This number was based on what efforts had been made by others regarding vectorized implementations and literature, thus illustrating the perceived ease or difficulty of adding this benchmark to SIMDwarfs. The analysis focused only on vectorization, and not other types of parallelism that may be present.

A revised version of the table can be found in Table 1.1. Specifically, two revisions have been made: (1) we have included some new benchmarks, and (2) we have updated the categories of some existing ones. The first revision is based on discovering that new benchmarks had been added to the benchmark suites that inspired SIMDwarfs. We decided to include them in the table, but have not assigned them a category since we have not surveyed them yet. The second revision is based on upgrading the benchmarks that was analyzed in this thesis, and downgrading some benchmarks that was incorrectly considered implemented. These revisions have been marked in the table with a  $\star$  and a  $\dagger$ , respectively, with a  $\rightarrow$  showing if the change resulted in an adjustment of the highest

<sup>&</sup>lt;sup>1</sup>no documents available yet

- Category 1: No software has been found

- Category 2: Software exists, including original implementation, but without any vectorization

- Category 3: Vectorized software exists using manual, automatic or user-directed\* vectorization

- Category 4: Vectorized software exists, and uses a wrapper library for vectorization

- Category 5: Vectorized implementation added to SIMDwarfs

$\ast$  using tools such as OpenMP and Cilk Plus

FIGURE 1.3: THE FIVE 'CATEGORIES OF VECTORIZATION'

category for one of the dwarfs. We have also rephrased the wording of category 3 to better reflect the multiple ways vectorization can be found in a program. The updated 'categories of vectorization' can be found in Figure 1.3.

#### TABLE 1.1: THE BERKELEY DWARFS AND THE BENCHMARKS ENVISIONED FOR SIMDwarfs. Categories have been updated for some benchmarks based on the New Information obtained from this thesis.

| Dwarf                                                                                                                                    | Description                                                                                          | Category          | Benchmarks                                                                                                             |  |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------|--|

| Dense Linear Algebra                                                                                                                     | Classic vector and matrix opera-<br>tions where data is stored in array<br>format                    | 5                 | LU Decomposition, Kmeans, BlackScholes, Dense Matrix Multiplication, Streamcluster, Reduction $\oplus$ , x264 $\oplus$ |  |

|                                                                                                                                          |                                                                                                      | 3                 | Vector Operation <sup>†</sup>                                                                                          |  |

|                                                                                                                                          |                                                                                                      | 2                 | Bodytrack<br>†, Strassen<br>†, K-Nearest Neighbors<br>†, Facesim<br>†<br>$\oplus$ Ferret $\oplus$                      |  |

|                                                                                                                                          |                                                                                                      |                   | Gaussian Elimination*                                                                                                  |  |

| Sparse Linear Algebra                                                                                                                    | Operations on matrices where<br>most elements are zero                                               | 5                 | Fluidanimate⊕                                                                                                          |  |

|                                                                                                                                          |                                                                                                      | 3                 | SPMV†                                                                                                                  |  |

|                                                                                                                                          |                                                                                                      | 2                 | Facesim†⊕                                                                                                              |  |

| Spectral Methods                                                                                                                         | Data operations in the spectral (frequency) domain                                                   | 5                 | Fluidanimate $\oplus$ , FFT                                                                                            |  |

|                                                                                                                                          |                                                                                                      | $3 \rightarrow 5$ | GPUDWT*                                                                                                                |  |

| N-Body Methods                                                                                                                           | N-Body Methods Calculations that depend on in-<br>teractions between (multiple) dis-<br>crete points |                   | N-Body†                                                                                                                |  |

|                                                                                                                                          |                                                                                                      | 2                 | LavaMD, GEM                                                                                                            |  |

| Structured Grids                                                                                                                         | Operations on regular, multidi-<br>mensional grids                                                   | 5                 | Leukocyte, Heart Wall, HotSpot, SRAD1, SRAD2,<br>Particle Filter, Vips, 2D Convolution                                 |  |

|                                                                                                                                          |                                                                                                      | 2                 | Myocyte†, 3D Stencil†                                                                                                  |  |

|                                                                                                                                          |                                                                                                      |                   | Hotspot3D*                                                                                                             |  |

| Unstructured Grids                                                                                                                       | Modelling objects with irregular geometric definitions                                               | 5                 | Histogram, Canneal                                                                                                     |  |

|                                                                                                                                          |                                                                                                      | 4                 | Back Propagation                                                                                                       |  |

|                                                                                                                                          |                                                                                                      | 2                 | CFD Solver                                                                                                             |  |

|                                                                                                                                          |                                                                                                      | 1                 | Unstructured 3D Stencil†                                                                                               |  |

| MapReduce (previously Monte<br>Carlo)                                                                                                    | Repeated, independent executions<br>of a function, aggregating results<br>at the end                 | 5                 | Swaptions, Raytrace, Histogram, Reduction $\oplus$                                                                     |  |

|                                                                                                                                          |                                                                                                      |                   | AMCD*                                                                                                                  |  |

| Combinational Logic                                                                                                                      | ombinational Logic Operations exploiting bit-level<br>parallelism to achieve high<br>throughput      |                   | CRC†                                                                                                                   |  |

| Graph Traversal                                                                                                                          | Traversing objects and examining characteristics                                                     | 5                 | BFS, B+Tree, Merge Sort                                                                                                |  |

|                                                                                                                                          |                                                                                                      | 3                 | Quick Sort <sup>†</sup>                                                                                                |  |

|                                                                                                                                          |                                                                                                      | 2                 | Freqmine⊕                                                                                                              |  |

|                                                                                                                                          |                                                                                                      | 1                 | Fibonacci†                                                                                                             |  |

|                                                                                                                                          |                                                                                                      |                   | MUMmerGPU*, Hybrid Sort*                                                                                               |  |

| Dynamic Programming                                                                                                                      | Computing solutions by solving sub-problems                                                          | $3 \rightarrow 5$ | NW†, Swat†                                                                                                             |  |

|                                                                                                                                          |                                                                                                      | 2                 | Pathfinder                                                                                                             |  |

| Backtrack and Branch-and-<br>Bound Branch-and-<br>Bound Dividing the search space into<br>regions and then discarding un-<br>suited ones |                                                                                                      | $3 \rightarrow 5$ | NQueens†                                                                                                               |  |

|                                                                                                                                          |                                                                                                      | 2                 | Astar                                                                                                                  |  |

| Graphical Models                                                                                                                         | Graph data operations, where<br>nodes are variables and edges are<br>conditional probabilities       | 3                 | НММ                                                                                                                    |  |

| Finite State Machines                                                                                                                    | Operations on an interconnected<br>set of states                                                     | 3                 | x264 $\oplus$ , Dedup                                                                                                  |  |

|                                                                                                                                          |                                                                                                      | 2                 | Freqmine $\oplus$ , Ferret $\oplus$ , TDM                                                                              |  |

|                                                                                                                                          |                                                                                                      |                   | Huffman*                                                                                                               |  |

|                                                                                                                                          |                                                                                                      |                   |                                                                                                                        |  |

$\oplus$  Benchmark with different phases, covering multiple dwarfs

$\dagger$  Benchmark that changed category compared to previous table version

$\star$  Benchmark newly added and not surveyed

## 1.3 Research Tasks

The aim of this thesis is to perform analysis of the vectorized benchmark implementations we found during the survey, and then add them to SIMDwarfs. We have formulated the following tasks in order to carry this out:

# Select one retrieved benchmark implementation from the uncovered dwarfs.

- T1 (Mandatory) Detail how vectorization is applied

- T2 (Mandatory) Determine benchmark performance and scalability

- T3 (Mandatory) Identify potential architectural bottlenecks

- T3.1 (Optional) Detail strategies to reduce the impact of the identified bottleneck

- T3.2 (Optional) Improve the implementation based on the mitigation strategy

- ${\bf T3.3} \hspace{0.1 cm} ({\rm Optional}) \hspace{0.1 cm} {\rm Determine \ improved \ benchmark \ performance \ and \ vector \ scalability}$

- ${f T4}$  (Mandatory) Upload analyzed benchmark to the SIMDwarfs github repository

#### Repeat as long as we have time left.

From the specialization project, we have previously selected the *nbody* benchmark from the N-body methods dwarf, and performed a performance and scalability evaluation. We noticed a possible bottleneck, and laid out a mitigation strategy involving approximating a calculation (more on this in Chapter 4). Following the tasks in this thesis, we have thus completed T2, T3 and T3.1, and are ready to perform T1 and then proceed on to T3.2 and T3.3.

## 1.4 Contribution

The main contribution of this thesis is adding vectorized implementations covering three previously uncovered dwarfs to SIMDwarfs: n-body methods, backtrack and branch-andbound, and dynamic programming. Four implementations, nbody, nqueens, NW and SWat have been analyzed for performance and scalability for three configurations: without vectorization, and vectorized using the SSE and AVX SIMD extensions. nbody has also been improved by approximating a high-latency operation. The implementations were ported to the ParVec wrapper library and stored in the SIMDwarfs github repository, which means the code will be reusable for any new ISA that is added to the wrapper in the future.

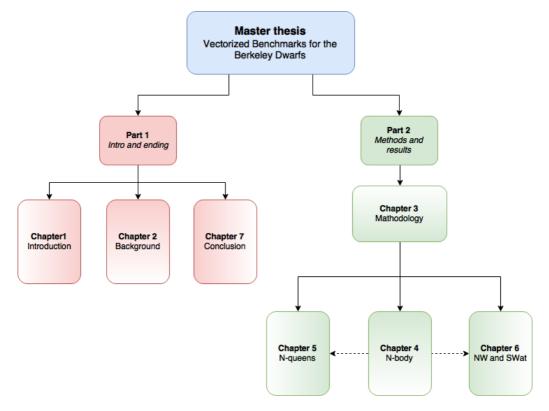

## 1.5 Thesis Outline

**Chapter 1** introduces the motivation behind this thesis, the need for SIMD-aware benchmarking tools. It also presents work we did on this topic previously, as well as defining research tasks and contributions of this thesis.

**Chapter 2** goes in depth on SIMD and vectorization, benchmarking and what characteristics to evaluate for, as well as presenting other benchmarking suites that inspired SIMDwarfs.

Chapter 3 presents the process we have followed in order to evaluate the benchmarks, what hardware and software was used, and what data we obtained.

Chapter 4, 5 and 6 introduces each benchmark that was evaluated, outlines how vectorization is applied, and discusses the results from the evaluation.

**Chapter 7** concludes this thesis, presents what efforts remain in order for SIMDwarfs to achieve full dwarf coverage, and presents some emerging SIMD technologies.

FIGURE 1.4: CHAPTER DEPENDENCIES IN THIS THESIS. CHAPTER 1, 2 AND 7 CAN BE READ WITHOUT MUCH KNOWLEDGE OF OTHER CHAPTERS. CHAPTER 3 PRESENTS THE DATA THAT IS DISCUSSED IN THE FOLLOWING CHAPTERS, AND CHAPTER 4 INCLUDES SOME GRAPH AXIS DETAILS THAT HAVE NOT BEEN REPEATED IN CHAPTER 5 AND 6.

## Chapter 2: Background

This chapter presents the underlying material the work in this thesis is based on. We start by explaining the features of SIMD and vectorization, and their impact. Then we detail requirements for computer benchmarking in order to help system designers in their work. Moving on, we discuss what types of general characteristics are important to evaluate for, such as the Berkeley dwarfs, and then present some SIMD-specific characteristics. Finally, we present some alternative, but lacking, benchmark suites that have been used as an inspiration for SIMDwarfs.

## 2.1 SIMD and Vectorization

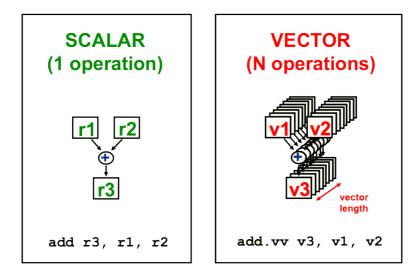

Efficient exploitation of DLP relies on the data streams being identically structured. One solution is structuring data inside similarly sized *vectors*, exposing DLP and allowing us to operate on multiple data elements simultaneously. This idea is illustrated in Figure 2.1. In a *scalar* architecture, used in a conventional uniprocessor, one computation outputs one processed data element. While there are multiple ways to increase the throughput rate, this operational pattern stays the same. By exploiting DLP using *vectorization*, a suitable processing element is able to perform the same computation on N individual data elements inside the vector at the same time, also called the *vector length* or *SIMD width*. We will detail various hardware that supports vector processing later on.

[David A. Patterson et al. 2014] corroborate that SIMD works best when the code contains arrays in for loops. Using a for loop that operates on multiple arrays allows us to unroll the loop and specify operations for each individual array. Thus, given that the arrays contain identically structured data without data dependencies, exploiting DLP can be done effectively. However, there are several factors that can limit SIMD performance. Patterson et al. proceed to state that SIMD is weakest when the code contains case or switch statements where different operations must be performed. They explain that this can cause some execution units to end up containing wrong data, meaning they must be disabled in order for the units with proper data to continue. [Smith et al. 2000] argue that for higher degrees of vectorization, you should vectorize the loops containing these conditional operations, and suggest that performing operations under a mask can help alleviate this issue. Other factors, such as data structure conversions and using slow, horizontal operations (operations on data elements inside the same vector) can also negatively impact the SIMD efficiency.

#### 2.1.1 SIMD advantages and disadvantages

Research shows that SIMD offers multiple advantages. From Figure 2.1 we observe that while both computations require one add operation, the vectorized computation has a throughput rate equal to its SIMD width, compared to the scalar computation's throughput rate of 1. This is a substantial advantage of SIMD, as a lower instruction count reduces both cache and pipeline pressure compared to scalar operations [Cebrian, Jahre, et al. 2014].

Moreover, SIMD can offer higher energy efficiency than scalar architectures when

FIGURE 2.1: SCALAR VS. VECTORIZED OPERATIONS. SOURCE: [POZZI ET AL. 2012]

DLP is present. [David A. Patterson et al. 2014, sec. 6.3] mention three characteristics of using vectors that can help save energy: (1) a reduced instruction count means fewer fetch and decode operations, (2) the cost of the latency to main memory is reduced due to fetching whole vectors at a time, and (3) it requires less data hazard checks, since checks are performed for whole vectors and not for each individual data element. [Cebrian, Natvig, et al. 2012] show that applications running on Intel processors dissipate roughly the same average power independently of how many bits were used from the SIMD registers, meaning that there exists an energy saving potential. Furthermore, estimates by [Hennessy et al. 2012, sec. 4.1], assuming an expected biyearly increase of two cores per chip and a doubling of SIMD width every four years, show that towards 2023 the potential speedup from SIMD parallelism is twice that of MIMD parallelism. Based on these results, they argue that SIMD parallelism is at least as important to understand as MIMD parallelism.

Lastly, [Pozzi et al. 2012] state that programming in SIMD allows software developers to achieve parallelism while still thinking sequentially, something that is harder to do when programming in MIMD. This can speed up development times since non-sequential programming requires programmers to adopt a different mindset, which can often be time-consuming.

However, there are some prominent limitations to SIMD. Firstly, it can be arduous to exploit DLP in some algorithms, meaning that SIMD would not be beneficial here. Due to the large amounts of data processed, memory bandwidth needs to be increased, which can lead to greater chip power dissipation when underutilized. There also exists some low-level optimization challenges, e.g. relating to data alignment, that needs to be rectified by hardware manufacturers.

### 2.1.2 Applications of SIMD

Three applications of SIMD have traditionally had the most impact, as covered by [Hennessy et al. 2012]: vector architectures using large vectors that could be operated on in

a non-contiguous fashion, SIMD extensions enabling selected vector operations on short, special vector registers, and GPUs which are mainly used as accelerators for graphics intensive applications.

#### Vector architectures

Vector architectures is an early example of SIMD utilization, and quickly became the cornerstone of supercomputing [National Research Council and others 2005]. The first machines supporting a vector architecture started appearing in 1972. This design primarily consists of vector registers, memory that holds the vectors, and fully pipelined vector functional units to process them. Vectors are fixed to a certain size, called the *maximum vector length* (MVL), but a vector register can hold multiple vectors [Pozzi et al. 2012]. Other critical components are registers for scalar values and a combined scalar/vector load/store unit that could operate non-contiguously, meaning that strided accesses were possible. One of the most well-known machines using a vector registers and eight 64-bit scalar registers. This computer delivered large amounts of computing power at a price competitive with the most economical computing systems of the day, costing approximately the same as an Apple II [National Research Council and others 2005].

However, the large data processing requirements caused machines with vector architectures to feature large containers to store the memory banks in near vicinity to a few, but powerful, custom made vector processors. This ultimately led to the architecture's downfall. Starting from the 1980's, an influx of cheap and increasingly powerful single-chip microprocessors started to influence the market. This same period also saw improvements to massive parallelism technologies, meaning that it became possible to combine the processing capabilities of thousands of commodity microprocessors that were much easier to scale and both cheaper to buy and operate compared to vector machines. These multiissue configurations was able to exploit ILP as a substitute for DLP [Koopman 1998], resulting in substantial performance increases. [David A. Patterson et al. 2014] explain that it therefore generally has been few reasons to face the risks of embracing another architecture style such as SIMD.

#### SIMD extensions

A more complex approach to SIMD that nonetheless has proved more popular is SIMD within a register (SWAR), found in the SIMD extensions included on many modern processors. Also called subword parallelism, this technique consists of modifying the CPU to perform select, optimized SIMD operations on relatively short, fixed-sized registers. This is done by a vector unit found inside the processor, exploiting the fact that the processor word size is large enough include multiple data elements that can be processed simultaneously. Support for this unit is added as extensions to the instruction set, which decides what operations are possible. The more prominent utilizations today are the MMX, SSE and AVX extensions developed by Intel for the x86 architecture, and the advanced SIMD extensions (NEON) developed by ARM for their products. Originally called multimedia extensions, these extensions started being included in microprocessors in the late 1990's as a way to increase graphics processing capabilities before external or integrated GPUs became commonplace.

SWAR is more intricate, and offer less flexibility than a vector architecture: data

FIGURE 2.2: COMPUTING THE VECTOR OPERATION A+B=C USING ONE LANE (LEFT) AND FOUR LANES (RIGHT). SOURCE: [DAVID A. PATTERSON ET AL. 2014, SEC. 6.3]

usually need to be loaded as contiguous, whole registers at a time, and there are also fewer operations available. Furthermore, each SWAR opcode need to strictly specify both data type, number of data operands and vector operation, in contrast to vector architectures which had one vector instruction and vector registers that configured automatically based on the data types loaded into it. In the recent years, SWAR developers have tried to incorporate some of these features by adding new operations supporting multiple data type and SIMD width configurations.

Despite the increased complexity compared to operating on a vector architecture, SIMD extensions have become popular in the industry. [Hennessy et al. 2012, sec. 4.3] cite five reasons why, including low cost of implementation and small memory bandwidth requirements in contrast to vector architectures. This interest have caused both register size and quantity to steadily increase each time a new technology has been brought to market: MMX (1997) uses eight 64-bit registers, SSE (1999) utilizes 8 128-bit registers, AVX (2011) can make use of 16 256-bit registers, and the newest AVX-512 (2016) supports up to 32 512-bit registers. Utilizing all registers in the latter two requires a 64-bit system; 32-bit systems support a maximum of 8 registers, regardless of configuration. The latest update to NEON (2015) adds support for 32 128-bit registers, up from 32 64-bit registers previously (2009). [Hennessy et al. 2012, sec. 4.1] state that for computers using the x86 architecture, they expect the register sizes to double every four years. According to [Cebrian, Jahre, et al. 2014], there is a potential for overall speedup directly caused by increasing the SIMD width, known as VL-time performance. Other improvements include the incorporation of multiple pipelined vector functional units, also called *vector lanes.* This concept can be seen in Figure 2.2: by structuring the vectors horizontally, in contrast to vertically, we can compute multiple data elements simultaneously, reducing execution time as well as load/store operations. However, as [Hennessy et al. 2012, sec. 4.1] explain: programmers must be sure to align all the data in memory to the width of the lanes on which the code is run to prevent the compiler from generating scalar

FIGURE 2.3: COMPARISON OF A TYPICAL CPU AND GPU ORGANIZATION. SOURCE: [CPU/GPU ARCHITECTURE COMPARISON N.D.]

instructions for otherwise vectorizable code.

#### GPUs

A prominent application of SIMD in the recent years is GPUs. Driven by the big rise in graphical intensive programs such as video games, this product has emerged separate from microprocessor developments and has been motivated by different goals. Today, commodity GPUs are mainly used as accelerators for offloading graphics processing from the CPU. For this reason, most CPUs are designed to be general purpose, while most GPUs are designed to be specialized. GPUs have a focus on throughput rather than latency, manifested in the form of increased computational and memory bandwidth, and favors multithreading rather than employing a multilevel cache hierarchy [David A. Patterson et al. 2014, sec. 6.6]. The result is a processor with better multithreading capabilities across a higher number of processors than what is found in a traditional MIMD CPUs, as shown in Figure 2.3. In a way, GPUs resemble vector processors. Every processor core employ multiple, parallel functional units that process SIMD instructions simultaneously, called SIMD lanes, and structure the data in vectors, though other terms are used, e.g. warps on Nvidia products. In addition, they employ multithreading which can complement SIMD: multithreading allows parallelizing work over multiple cores, while SIMD allows parallelizing work within a single core [Microsoft n.d.].

Evaluations show that GPUs significantly outperform CPUs for certain tasks. [Lee et al. 2010] investigated claims that this GPU speedup could reach over 100 times that of the CPU by running 14 kernels on an Nvidia GTX280 GPU and an Intel Core i7 960 CPU. They found that the GPU had a modest, average performance advantage of 2.5x, and suggests that using differing hardware and software, e.g. a mobile CPU with unoptimized code vs. a high-performance GPU with optimized code, can contribute to these abnormally large speedups. Regardless, they argue that software optimizations on the respective platforms are critical to fully utilize compute and bandwidth resources for both CPUs and GPUs, and state that in the absence of such optimizations, CPU implementations are sub-optimal in performance and can be orders of magnitude off their attainable

performance. By using careful multithreading, reorganizing memory access patterns, and applying SIMD optimizations, they found the performance on both CPUs and GPUs is mainly limited by memory bandwidth. Being more bandwidth-focused than CPUs, GPUs have started being employed in the industry for performance purposes.

### 2.1.3 Auto-vectorization

An active research topic in modern compilers is auto-vectorization. As the vectorization capabilities of compilers have advanced, tools that aim to insert vector instructions where it seems practical have emerged. However, while writing manual vector code is a time consuming and error-prone task, auto-vectorization technologies found in modern compilers are not yet able to match the level of vectorization provided. [Maleki et al. 2011] showed this by analyzing the auto-vectorization abilities of the GCC, ICC, and XLC compilers on both synthetic and real applications, and show that 45-71% of the synthetic loops, and only 13-18% of the real application loops were automatically vectorized. It was also found that manual vectorization provided a mean speedup of 2.1x compared to auto-vectorization. In this thesis we have used applications that have been vectorized manually, as this allows us to have better control of which operation are used where, and ensures that SIMD performance is independent of your choice of compiler. Thus, we will not focus further on the aspect of auto-vectorization.

#### 2.1.4 SIMD in heterogeneous systems

A system utilizing components that specialize on certain tasks is known as a *hetereogeneous* system. Lately, new heterogeneous systems for high performance computing have appeared that try to incorporate SIMD. One example of these products is general purpose GPUs (GP-GPUs), that use special APIs, e.g. OpenCL and CUDA, to program GPUs to perform computations traditionally done by the CPU.

Another novel heterogeneous technology is Intel' Xeon Phi products for high performance computing. At the center of the system architecture, called many integrated core (MIC), is a Xeon Phi co-processor. This enables manycore processing, a new class of multiprocessing that aim to offer higher degrees of parallelism than what was previously possible. The latest generation of Xeon Phi, codenamed Knights Landing (KNL), released in 2016, consists of 72 cores each containing two 512-bit vector units, and is the first product that support AVX-512 SIMD extensions. Intel state that it is capable of handling a wider variety of tasks than traditional accelerators such as GPUs, as well as computing them faster [Intel n.d.(a)].

[Hennessy et al. 2012, sec. 4.1] estimate that combined MIMD and SIMD will yield the highest parallel speedup in 2023, at more than one order of magnitude higher than what individual SIMD and MIMD is able to achieve.

## 2.2 Benchmarking

To design better systems that meet ever increasing needs, system designers and computer scientists use benchmarking, which has become the standard method of performing experiments in computer science [Bienia 2011]. The benchmark results then are studied in detail to uncover generalized insights that can then be applied to real computer systems. A benchmark can take many forms, although [Hennessy et al. 2012, sec. 1.8] argue that

only real-world applications can deliver results of high validity. Other variations, such as kernels (small, key pieces of real applications), toy programs and synthetic benchmarks (applications made to simulate the behavior of a real-world program) are all discredited by researchers, as they make it easy to optimize the hardware and software for these specific operations and thus gain an unfairly high score.

### 2.2.1 Benchmark Requirements

[Weicker 1990] define four requirements of a good benchmark: (1) it is written in a highlevel language for portability, (2) it is representative for some kind of programming style, (3) it can be measured easily, and (4) it has wide distribution. Hennessy et al. explain how using compiler flags and source code modifications could be misused, and why they should be considered carefully. They also argue how a guiding principle of reporting performance measurements should be reproducibility, i.e. how other researchers can duplicate the results.

It is critical that the selected benchmarks cover a wide range of software applications, or *workloads*, with various behaviors as to ensure that the uncovered insights have high validity. For this reason, benchmarks of interest are compiled into benchmark suites. [Bienia 2011] define five requirements that should be satisfied in a multithreaded benchmark suite. The first requirement is that the applications should be parallelized, proving that you need to tailor your benchmark suite to an area of interest. The rest are general rules that can be applied to all benchmark suites in general: (2) it should utilize new types of applications that have emerged because of faster hardware, (3) it should contain diverse applications running on a variety of platforms and with different usage models, (4) it should apply state-of-the-art algorithms, and (5) it should be used by researchers.

### 2.2.2 Suitable Evaluation Characteristics

Fully SIMD-aware benchmarking tools have not yet seen wide adoption. By continuing to use benchmarks that provide sub-optimal data and fail to adapt to changes in the industry, system designers can end up doing themselves a disservice. [Cebrian, Jahre, et al. 2014] argue that if benchmarks do not cover the most common architectural features, architects may end up under/over estimating the impact of their contributions. While one issue of designing a SIMD-aware benchmarking tool is that the benchmarks support SIMD, the real challenge lies in determining what features, i.e. characteristics, to evaluate for.

#### System-specific characteristics

[Rabaey et al. 2008] present the problems caused by developing new hardware and software based on extrapolations of existing applications and old data. They argue by doing so, the application community might miscalculate or misinterpret the capabilities of the hardware and software platforms of the future and be lured into dead-ends. A better solution might be formulating new benchmarks that better reflect emerging workloads. Four emergent application areas are presented, as an attempt to fuel development of these 'workloads of the future.' The areas are (1) high-performance computing tasks in scientific fields such as climate research and particle physics, (2) societal IT systems, e.g. relating to automotive or avionic safety and traffic-flow management, (3) personalized, low latency feedback by societal IT systems and (4) perceptual processing, e.g. voice and virtual reality interfaces that feel natural to the user.

[Dubey 2005] present the Intel Recognition, Mining, Synthesis (RMS) classification, a set of three fundamental processing capabilities Intel deemed necessary for their tera-scale computing platform. The classifications describe how computing systems should *recognize* mathematical models in data sets using machine learning, *mine* the data model in order to extract the relevant data, and then *synthesize* the mined data to draw conclusions that necessarily cannot be found in the model. This classification formed the basis of the PARSEC benchmark suite, which ParVec is a variation of.

A more thorough work on this subject, which was used as the basis of SIMDwarfs, is the Berkeley dwarfs taxonomy. This research stretches back to 2004, when [Colella 2004] defined the *seven dwarfs of high-performance computing*, which were numerical methods important for science and engineering. A dwarf was defined as a an algorithmic method that captures a pattern of computation and communication, specified at a high level of abstraction to so that it can cover a broad range of applications as possible. [Asanovic et al. 2006] based themselves on this taxonomy, and added six more dwarfs by studying three emerging application domains: machine learning, database software, and computer graphics and games. They state that the point of this project is not to identify the low hanging fruit that are highly parallel, but to identify the kernels that are the core computation and communication for important applications in the upcoming decade, independent of the amount of parallelism. The outcome was 13 dwarfs that they hope will guide the development of hardware, software, and programming models that efficiently utilize parallelism. Section 2.3 detail other benchmark suites, in addition to SIMDwarfs, that include benchmarks covering some of the dwarfs.

#### Application-specific characteristics

[S. Williams et al. 2009] define the roofline model, a visual tool to compares floating-point and memory performance, and arithmetic/operational intensity (AI). The AI specifies the ratio of floating-point operations per byte of memory accessed, as shown in Figure 2.4. A few example kernels are mapped out on this scale, showing for which of them the intensity scales with problem size (right), and for which the intensity is independent of problem size (left). We recognize many of these kernels as Berkeley dwarfs or as benchmarks considered for SIMDwarfs. This tool can be used to determine which of them are most computationally expensive, which in turn can be used to determine their suitability in a benchmark suite. The roofline model can be used to determine if benchmark performance is *compute-bound*, meaning that processor efficiency will need to be improved in order to increase performance, or *memory-bound*, meaning that the memory subsystem will need to be improved.

[Blem et al. 2011] argue that to sustain the increasing performance developments in GPU processing, architects must continue to address the performance of challenging workloads, instead of using benchmarks that perform well on GPUs. They contribute to this mission by providing and evaluating a list of 'challenge benchmarks' that strain the hardware, and map the key performance limitations. The benchmarks come from existing benchmark suites such as GPGPU-Sim, Rodinia and PARSEC. Benchmarks such as N-queens and Needleman-Wunsch, which have been analyzed in this thesis, as well as benchmarks considered for SIMDwarfs, was deemed sufficiently challenging for GPUs. The authors expect that these results apply to other many-core technologies and vector extensions like Intel's AVX.

Figure 2.4: Roofline model, arithmetic intensity. Source: [Hennessy et al. 2012, sec. 4.3]

## 2.3 Other Benchmark Suites

In order to select benchmarks for SIMDwarfs that are covered by one or more Berkeley dwarfs, we have drawn inspiration from other, widely adopted benchmark suites. This section focus on four suites, which have supplied the largest amount of potential benchmarks for SIMDwarfs. While all incorporates the dwarf taxonomy to some extent, no one benchmark suite covers all 13 dwarfs. There are also minimal to non-existent SIMD support, meaning the suites all are far from fully SIMD-aware. This section briefly explains their primary purpose and the number of dwarfs covered, with Table 2.1 showing which suites cover which dwarfs. Finally, we mention some miscellaneous suites that have also been considered.

#### 2.3.1 Suites used by SIMDwarfs

The Princeton Application Repository for Shared-Memory Computers (PARSEC) benchmark suite [PARSEC n.d.] was released in 2007 in response to the emergence of chip multiprocessors. It was developed as a joint effort between researchers at Princeton and at Intel. The latest version contains 13 parallelized implementations written in C/C++(10 applications and 3 kernels) covering 8 dwarfs, and has been designed according to the five requirements for benchmark suites defined by [Bienia 2011] in Section 2.2.

[Rodinia n.d.] is intended as a benchmarking tool for heterogeneous systems, aiming to provide insight on accelerators, which no benchmark suite had done before. Released in 2010, it contains benchmarks designed with OpenMP, OpenCL and CUDA. The latest version contains 23 applications, covering 8 dwarfs.

[OpenDwarfs n.d.(a)] provides a benchmark suite consisting of different dwarfs, where the target architectures are multi-/many-core and GPU systems. Benchmarks are realized in OpenCL, and the suite was first made available in 2012. The latest version contains 14 applications covering 12 dwarfs.

The Mont-blanc benchmark suite [Rajovic, Rico, Vipond, et al. 2013] has been made to benchmark the Mont-blanc prototype [Rajovic, Rico, Mantovani, et al. 2016, an HPC system built with commodity hardware. The suite contains 11 applications covering 8 dwarfs, designed with OpenMP and OpenCL.

### 2.3.2 Miscellaneous suites

Additional benchmark suites covering a wide range of disciplines were surveyed. SPLASH-2, SPEC OMP2001 and NAS Parallel Benchmarks (NPB) contain parallel workloads, but with a focus on HPC. SPEC CPU2006 use a wide range of real workloads focusing on processor, memory subsystem and compiler. SPEC CPU2017 is an updated version of CPU2006 including additions such as OpenMP support and energy metrics. Linpack measures floating-point performance, Parboil focus on throughput, and SHOC is used for stress testing and measuring performance of heterogeneous systems. SPEC MPI2007 focus on message passing interface (MPI) parallel applications running on various hardware and software architectures.

We also looked at suites covering specific fields: ALPBench contains parallelized multimedia workloads, and supports vectorization with SSE. BioParallel includes bioinformatic workloads, NU-MineBench measures data mining performance and PhysicsBench is used for computer game physics simulations.

Finally, we looked at the Recursive Benchmark Suite [Ren et al. 2015], which includes recursive, task-parallel benchmarks that have been transformed in order to exploit DLP. Eight applications are included, ranging from microbenchmarks to kernels, that all have been manually vectorized with SSE and AVX-512 intrinsics. This suite includes the nqueens benchmark, which is analyzed in Chapter 5.

| Dwarf                                    | Rodinia                                                                                              | PARSEC                                                                 | OpenDwarfs                  | Mont-blanc                                                        |

|------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------|