# Low Power Electronic Paper Display Driver with Unipolar Driving Waveform

Mattis Spieler Asp

Master of Science in Electronics Submission date: June 2017

Supervisor: Per Gunnar Kjeldsberg, IES

Co-supervisor: Snorre Aunet, IES

Øystein Moldesvor, Disruptive Technologies

Norwegian University of Science and Technology Department of Electronic Systems

| NORWECTAN | TIMINEDSITV | OF SCIENCE | AND | TECHNOI | $\mathbf{OCV}$ |

|-----------|-------------|------------|-----|---------|----------------|

Low Power Electronic Paper Display Driver with Unipolar Driving Waveform

# Mattis Spieler Asp

Master thesis

Faculty of MTEL

Department of Electronics and Telecommunications

June 2017

# **Problem Description**

New types of displays allow for extremely small power dissipation as long as the image is static. These types are often referred to as "electronic paper displays". Such displays are interesting for IoT applications, as they would allow display of images or messages when little power is available.

.Implementation of a level shifter for an electronic paper display driver.

An important part of the low-power electronic paper display (EPD) driver is the level shifter. The level shifter converts logical input to analog output. This is the analog input for the horizontal (source) and vertical (gate) lines in the electronic paper display. In the case of an EPD, this analog output is discrete. The EPD requires a minimum voltage of 5 volt over the electrodes to drive the pixel between states. A common practice is to attach one electrode on every pixel to a common ground and vary the other electrode above or below ground to change between black and white color. It is the duration of the applied voltage that variates the pixel gray level in any specified voltage domain. The voltage, if above minimum, can be varied to reach a higher level of color intensity/extreme in the black/white domain.

A master thesis carried out in the spring 2016, and a project thesis carried out in the fall the same year, analyzed in depth the feasibility of an alternative unipolar driving waveform for the pixel electrodes. It showed that the unipolar waveform can potentially save 73% power in a 360X480 sized display. The unipolar driving waveform exploits a second compliment level shifter connected to the common electrode, replacing ground. To switch color, the compliment level shifter will be the inverse of the source voltage. With this second level shifter, each level shifter can reduce the output voltage by two, and still keep the minimum voltage required to change pixel state.

The assignment will start with a study of different level shifter concepts. Based on the specific requirements of an EPD, a low power level shifter shall then be designed and simulated in a design environment of choice. The power consumption of the level shifter

shall be estimated and compared with state of the art solutions.

Co-supervisor: Øystein Moldsvor, Disruptive Technologies

Co-supervisor: Professor Snorre Aunet, NTNU

Supervisor: Professor Per Gunnar Kjeldsberg, NTNU

### NORWEGIAN UNIVERSITY OF SCIENCE AND TECHNOLOGY

## Abstract

# $\label{eq:faculty} \mbox{ Faculty of MTEL}$ Department of Electronics and Telecommunications

Master thesis

by Mattis Spieler Asp

Electronic paper display (EPD) has reached a position of great maturity. Due to its capability of bistability and great reflectivity it can display an image without any flowing current. Today, sensors and regulators are being placed out to monitor the real world, and are often battery powered without a display. With the introduction of electronic paper displays these units can be given a display without a significant increase in power. There is however still very limited power available, and power reduction is considered increasingly important.

A theoretical and practical analysis of EPD, Thin-Film Transistor, and level shifters have been used to investigate power reduction techniques. The area of interest is the sub circuits where level shifters are adopted. These sub circuits typically carry over 60% of the total power consumption during an electronic paper write cycle. Practical experiments and simulations have been used to find new power saving level shifters for these sub circuits.

The simulations have been successfully used to show different level shifters performing and running at two different frequencies (10MHz and 2Hz) using commercially available 180nm technology. The results from the simulations in Cadence Virtuoso have shown that the proposed circuits perform about 80% - 85% better in terms of power at high frequency (10MHz). The results also show that the proposed circuits perform about 65% - 150% worse in terms of power at low frequency (2Hz).

From the results we have concluded that the proposed circuits are not better in low frequency applications such as electronic paper displays. However storage capacitors can be added to electronic paper pixels which can potentially speed up the scan process, thereby making these results more applicable.

# **Preface**

The presented dissertation is created by Mattis Spieler Asp.

The idea behind the project came from a specialization project in the NTNU subject TFE4520, conducted in the Autumn semester of 2017. In this specialization project, a circuit board capable of driving electronic paper was created. The results showed that it was possible to achieve a remarkable power stringent electronic paper driver saving up to 75% of the previously used power given a worst case image update. In collaboration with professor Per Gunnar Kjeldsberg at NTNU, professor Snorre Aunet at NTNU, and Øystein Moldesvor at Disruptive Technologies AS the idea was further developed. The results were a simulation on chip of the major sub components of the electronic paper driver.

The required software for the simulation was not accessible before one week before deadline. Four trials were conducted with full implementation in the software during the semester, and significant delays where encountered due to software malfunction. The project continued as a literature study, and without any supporting software five new circuits were developed manually. These circuits were closely based on previous articles found during literature study. When the simulation worked, two of the circuits showed excessive power usage and malfunction in the specific process environment, however three remained successful and the results where presented.

Trondheim, 2016-06-28

Mattis Spieler Asp

Mattis Spieler Ag/

# Acknowledgements

I would first like to offer my special thanks to my supervisor Per Gunnar Kjeldsberg for taking the time to guide the project in this period. Per Gunnar has contributed by giving me guidance on the overall report structure, as well as reviewing my progress through the semester.

I am particularly grateful for the extra support given by my co-supervisor Snorre Aunet on circuit advice and motivating me throughout this project. Snorre Aunet has been available for questions, and helped me concerning circuit problems.

My special thanks goes to Øystein Moldesvor, and his team of engineers at Disruptive Technologies AS for their advisory in this project. Øystein has helped me with architectural design, as well as supported me with a workplace during the last part of the semester.

I would like to express my very great appreciation to Simon L'orange for his time spent with me to teach Cadence software.

# Contents

| Pı | roble       | Description                                        | iii          |

|----|-------------|----------------------------------------------------|--------------|

| A  | bstra       | į.                                                 | $\mathbf{v}$ |

| Ρı | reface      | •                                                  | vii          |

|    | . 02010     |                                                    |              |

| A  | cknov       | ledgements                                         | ix           |

| Li | ${f st}$ of | ligures                                            | ΧV           |

| Li | st of       | Tables x                                           | ix           |

| A  | bbre        | ations                                             | xi           |

| 1  | Intr        | duction                                            | 1            |

|    | 1.1         | Problem Description                                | 2            |

|    | 1.2         | Motivation                                         | 2            |

|    | 1.3         | Project Goals                                      | 2            |

|    | 1.4         | Chapter Outline                                    | 3            |

|    | 1.5         | Main Contributions                                 | 4            |

| 2  | Intr        | ducing the Electrophoric Display                   | 5            |

|    | 2.1         | History of Electrophoric Paper Display             | 5            |

|    | 2.2         | Operating Principle                                | 6            |

|    | 2.3         | EPD Driving Circuitry                              | 7            |

|    |             | 2.3.1 Control Unit                                 | 7            |

|    |             | 2.3.2 Voltage Converter                            | 8            |

|    |             | 2.3.3 Source Driver                                | 8            |

|    |             | 2.3.4 Gate Driver                                  | 8            |

|    |             | 2.3.5 Electrophoric Display Structure              | 8            |

|    | 2.4         | Principles Of The Electrophoric Display Addressing | 9            |

|    | 2.5         | 1 0                                                | 11           |

|    | 2.6         | The Voltage Domain                                 | 13           |

|    | 2.7         | TFT-properties                                     | 14           |

|    |             | 2.7.1 a-Si:H TFT                                   | 15           |

|    |             | 2.7.2 poly-Si·H TFT                                | 16           |

*Contents* xii

| 3 | $\mathbf{Pre}$ | vious Work                                                  | 19 |

|---|----------------|-------------------------------------------------------------|----|

|   | 3.1            | Power consumption investigation                             | 20 |

|   | 3.2            | Low Power Electrophoretic Display Module                    | 21 |

|   |                | 3.2.1 Source Driver Power - Digital Part                    | 22 |

|   |                | 3.2.2 Source Driver Power - Analog Part                     | 22 |

|   | 3.3            | Configurable timing controller for AM EPD                   |    |

|   | 3.4            | Low power Electrophoric Display - Specialization project    | 24 |

|   | 3.5            | Power Reduction in D-RAM Technology                         | 25 |

|   |                | 3.5.1 Reverse Bias Leakage Reduction                        | 25 |

|   |                | 3.5.2 Refresh operation                                     | 26 |

|   | 3.6            | Conventional Level Shifter                                  | 27 |

|   | 3.7            | Capacitor Coupled Level Shifter                             | 27 |

|   |                | 3.7.1 Transient Response                                    |    |

|   | 3.8            | Positive and Negative Level shifter                         | 29 |

| 4 | Nev            | w Architectural Level Shifter                               | 31 |

|   | 4.1            | Proposed Negative Capacitor Coupled Level Shifter           | 31 |

|   |                | 4.1.1 Steady State                                          |    |

|   |                | 4.1.2 Transient State                                       |    |

|   |                | 4.1.3 Power Characterization                                |    |

|   | 4.2            | Optimizing for CMOS technology                              | 34 |

|   | 4.3            | Refresh Operation                                           | 35 |

|   | 4.4            | •                                                           | 36 |

| 5 | Gat            | e-driver                                                    | 37 |

|   | 5.1            | TFT threshold voltage                                       | 37 |

|   | 5.2            | A Research Into I-V Characteristics of Electrophoric Paper  | 38 |

|   | 5.3            |                                                             | 39 |

| 6 | Res            | sults and Discussion                                        | 43 |

|   | 6.1            | Simulation Analysis                                         | 43 |

|   | 6.2            | ·                                                           | 44 |

|   |                | 6.2.1 Steady State                                          | 44 |

|   |                | •                                                           | 45 |

|   | 6.3            | CCLS                                                        | 47 |

|   |                | 6.3.1 Steady State                                          | 47 |

|   |                | 6.3.2 Steady State to Transient                             | 50 |

|   |                | 6.3.3 Transient                                             | 51 |

|   | 6.4            | Negative CCLS                                               | 52 |

|   |                | 6.4.1 Steady State                                          | 53 |

|   |                | 6.4.2 Steady State to Transient                             | 55 |

|   |                | 6.4.3 Transient                                             | 56 |

|   | 6.5            | Optimized Negative Capacitor Coupled Level Shifter (ONCCLS) | 58 |

|   |                | 6.5.1 Steady State                                          | 58 |

|   |                | ·                                                           | 60 |

|   |                |                                                             | 62 |

|   | 6.6            |                                                             | 65 |

| Contents | xiii |

|----------|------|

|          |      |

|              | 6.7   | Discussion              | 70        |

|--------------|-------|-------------------------|-----------|

| 7            | Con   | clusion and Future Work | <b>73</b> |

|              | 7.1   | Conclusion              | 73        |

|              | 7.2   | Future Work             | 74        |

|              |       |                         |           |

| $\mathbf{A}$ | Gho   | osting effect           | 75        |

| Bi           | bliog | graphy                  | 77        |

# List of Figures

| 2.1  | Principle of electronic inc [1]                                                                           | 6             |

|------|-----------------------------------------------------------------------------------------------------------|---------------|

| 2.2  | Simple driving circuit for the EPD                                                                        | 7             |

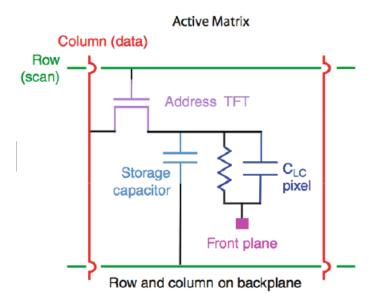

| 2.3  | EPD pixel modeled with a TFT-gate and storage capacitor                                                   | 9             |

| 2.4  | a-Si display connected to source and gate driver                                                          | 10            |

| 2.5  | A pixel connected to a thin-film transistor [2]                                                           | 10            |

| 2.6  | Sequential addressing of TFT display                                                                      | 11            |

| 2.7  | Vertical transitions in an image [2]                                                                      | 11            |

| 2.8  | Internal components of the EPD driver                                                                     | 12            |

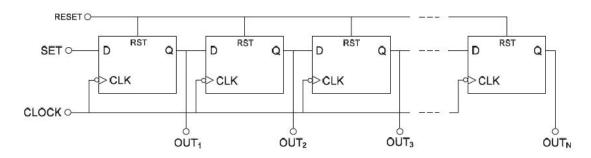

| 2.9  | Shift register circuit [3, P.223]                                                                         | 13            |

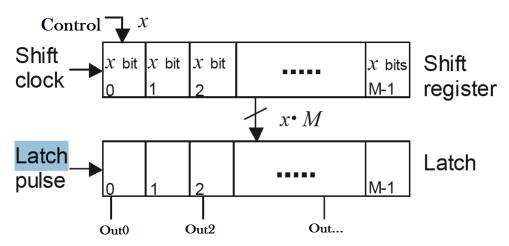

| 2.10 | Block Diagram of a shift register connected to a latch [3, P.131]                                         | 13            |

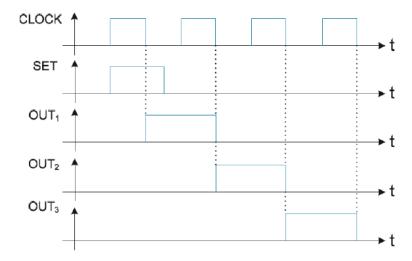

| 2.11 | Shift register; walking one [3, P.223]                                                                    | 14            |

| 2.12 | level-converting logical input voltage to pixel driving voltage                                           | 14            |

| 2.13 | Cross-section of a basic tft [3, P. 147]                                                                  | 15            |

| 2.14 | Drain current versus gate-source voltage for an n-channel a-Si TFT with                                   |               |

|      | , , , , , , , , , , , , , , , , , , , ,                                                                   | 16            |

| 2.15 | Drain current versus gate-source voltage for an n-channel Poly-Si TFT                                     |               |

|      | with W/L=10 $\mu$ m/5 $\mu$ m [3, P. 151]                                                                 | 16            |

| 3.1  | Breakdown chart for power usage [4]                                                                       | 20            |

| 3.2  | Power as function of font type [4]                                                                        |               |

| 3.3  | Power as function of black pixels for image transition [4]                                                |               |

| 3.4  |                                                                                                           | $\frac{1}{2}$ |

| 3.5  |                                                                                                           | 23            |

| 3.6  | Unipolar driving scheme [5]                                                                               |               |

| 3.7  | • •                                                                                                       | 24            |

| 3.8  | Oscilloscope measurements at the Electrophoric Display, showing an avg                                    |               |

|      |                                                                                                           | 25            |

| 3.9  | Concepts for creating high $V_t$ [7, P.153]                                                               | 26            |

| 3.10 | Conventional level shifter [3]                                                                            | 27            |

|      |                                                                                                           | 28            |

|      | INPUT and INPUT toggle                                                                                    | 28            |

| 3.13 | A digital buffer, which combines two level-shifters of opposite polarity [3]                              | 30            |

| 4 1  |                                                                                                           |               |

| 4.1  | The Author proposes this level shifter to achieve negative levels in the capacitor coupled level shifter. | 32            |

| 4.2  | Optimized negative level-shifter with two capacitors instead of three, and                                | <u>ع</u> 2    |

| 4.2  |                                                                                                           | 34            |

| 4.3  |                                                                                                           | 35            |

| 1.0  | The possible realinge carreins from from the Quantum Collection                                           | -             |

List of Figures xvi

| 4.4        | Reverse Bias P1 to limit leakage from source to drain                                                    | 36 |

|------------|----------------------------------------------------------------------------------------------------------|----|

| 5.1<br>5.2 | Current measurements provided by a single experiment                                                     | 38 |

| <b>F</b> 0 | at maximum value                                                                                         | 39 |

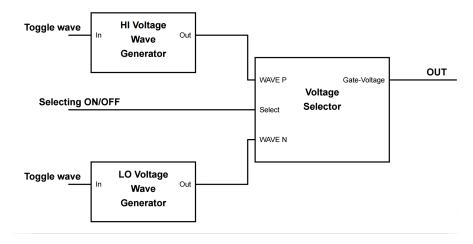

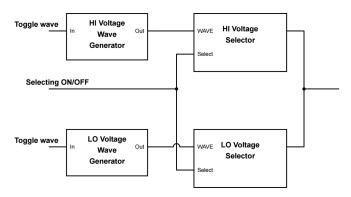

| 5.3        | The two states of the gate driver                                                                        | 40 |

| 5.4        | A quad level shifter block diagram                                                                       | 41 |

| 5.5        | Using the ONCCLS as a waveform generator                                                                 | 41 |

| 5.6        | A quad level shifter block diagram                                                                       | 42 |

| 5.7        | Selecting output depending on Source Driver output Voltage                                               | 42 |

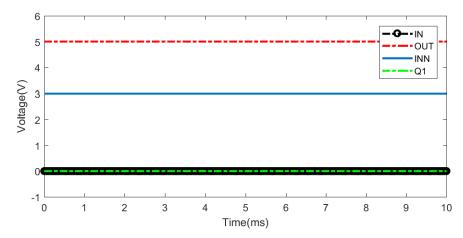

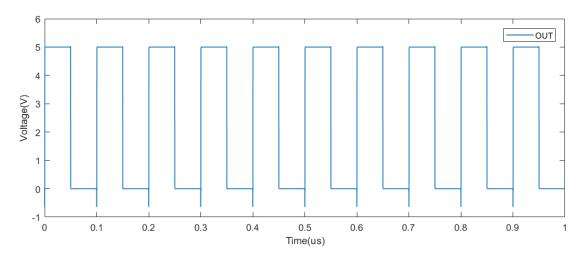

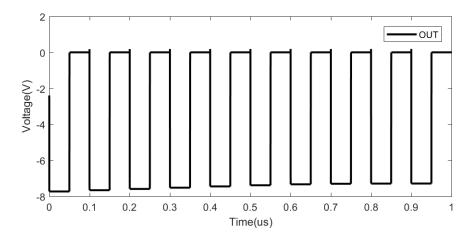

| 6.1        | Steady State INPUT voltage in the conventional level shifter for $10\mathrm{ms}$                         | 44 |

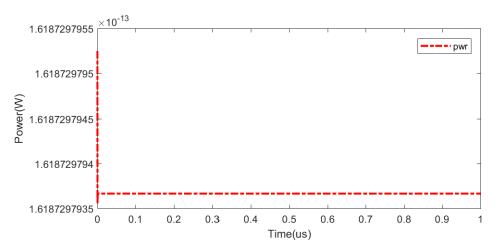

| 6.2        | Power usage during steady state for a conventional level shifter                                         | 45 |

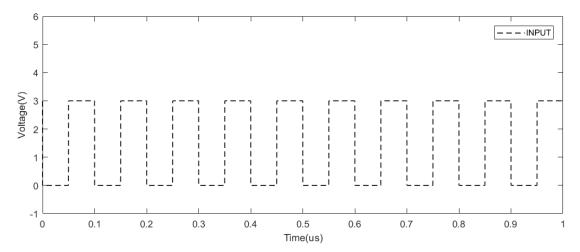

| 6.3        | INPUT signal in a conventional level shifter running at 10MHz $ \ldots  \ldots $                         | 45 |

| 6.4        | OUTPUT signal in a conventional level shifter running at 10MHz                                           | 46 |

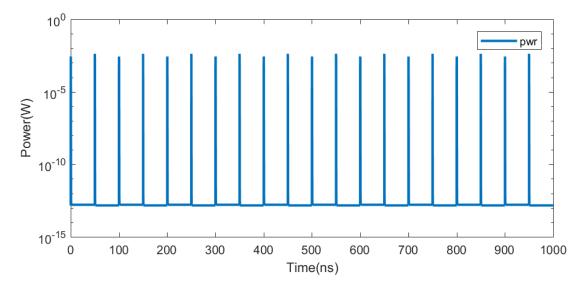

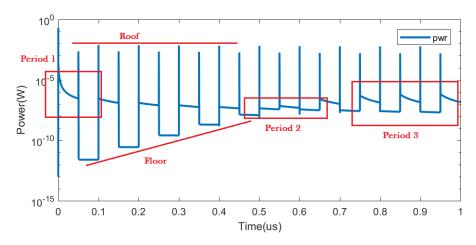

| 6.5        | Power consumption during a transition in the conventional level shifter . $\boldsymbol{.}$               | 46 |

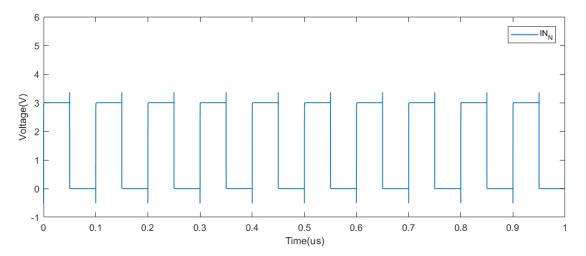

| 6.6        | INPUT INVERTED signal in a conventional level shifter running at $10\mathrm{MHz}$                        | 46 |

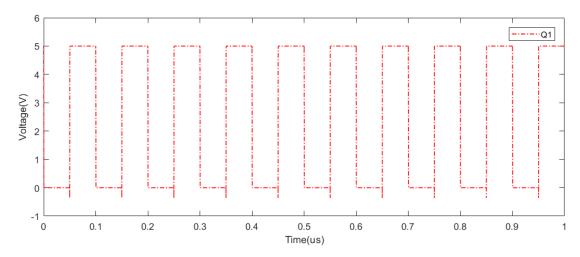

| 6.7        | Q1 signal in a conventional level shifter running at 10<br>MHz                                           | 47 |

| 6.8        | Capacitor Coupled Level Shifter [8]                                                                      | 47 |

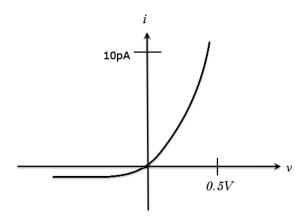

| 6.9        | V-I characteristics of a silicon diode [9]                                                               | 48 |

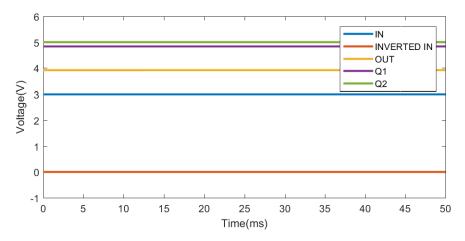

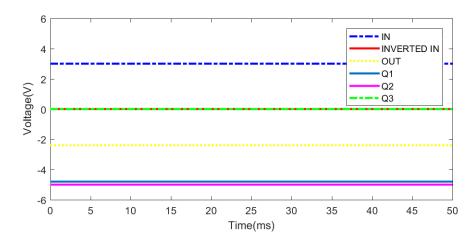

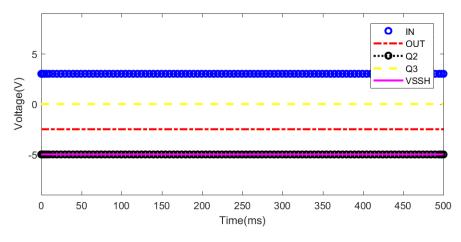

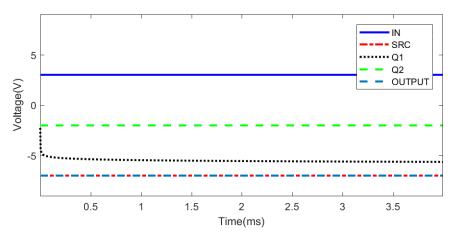

| 6.10       | Merged plot of all signals in CCLS during HIGH INPUT DC voltage for                                      |    |

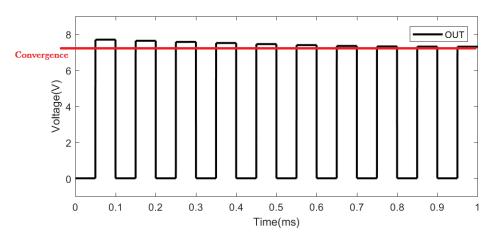

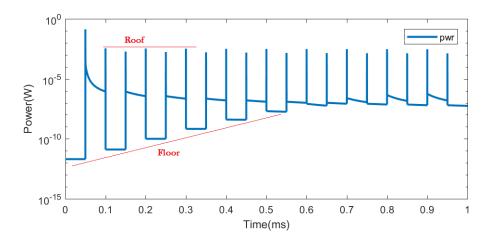

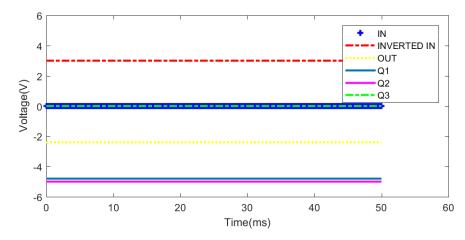

|            | 50ms                                                                                                     | 49 |

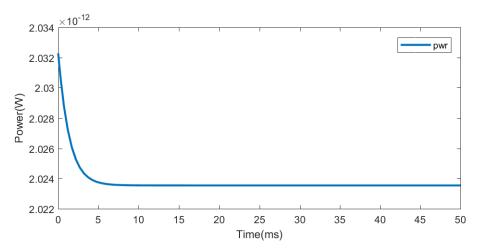

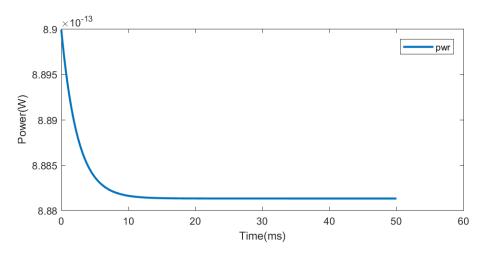

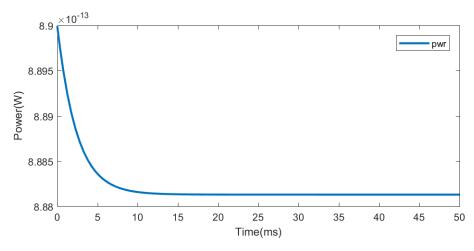

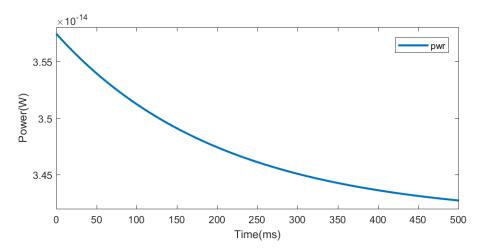

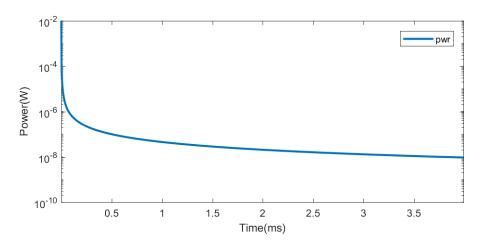

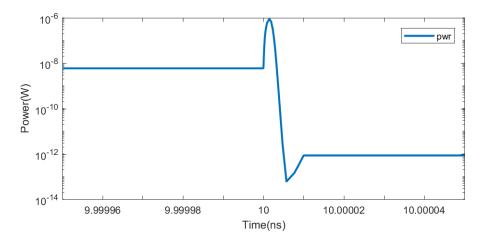

|            | Power plot in CCLS during HIGH INPUT DC voltage for 50ms                                                 | 49 |

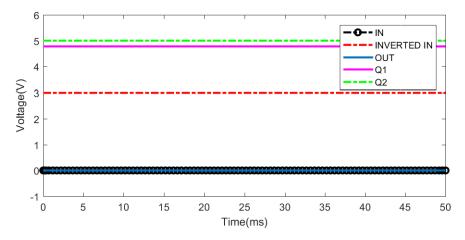

| 6.12       | Merged plot of all signals in CCLS during LOW INPUT DC voltage for                                       | 10 |

| C 19       | 50ms                                                                                                     | 49 |

|            | Power plot in CCLS during LOW INPUT DC voltage for 50ms                                                  | 50 |

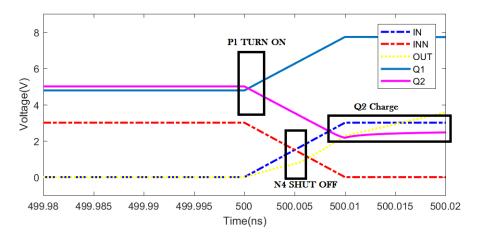

| 0.14       | Merged plot of all signals in CCLS during LOW INPUT Steady State to Transient                            | 50 |

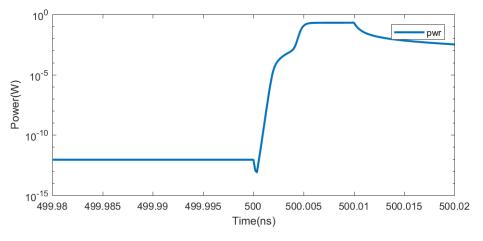

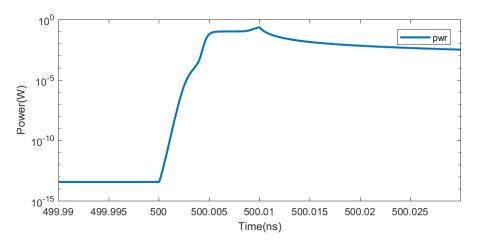

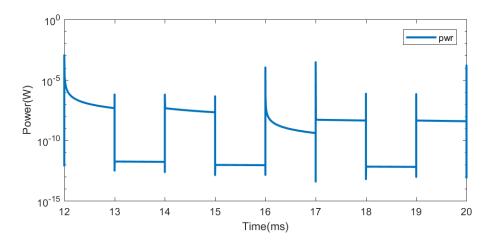

| 6.15       | Logarithmic power plot in CCLS during LOW INPUT Steady State to                                          | 00 |

| 0.20       | Transient                                                                                                | 51 |

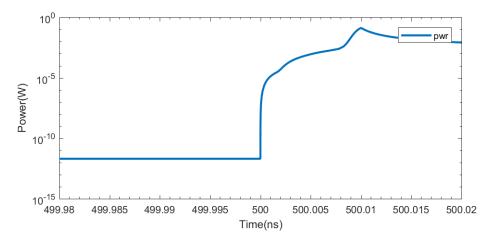

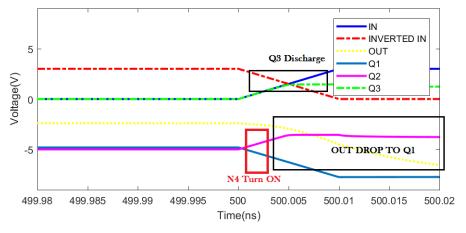

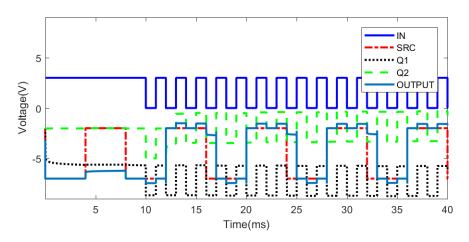

| 6.16       | Merged plot of all signals in CCLS during transient                                                      | 51 |

| 6.17       | Plot of OUT signal in CCLS during transient                                                              | 52 |

| 6.18       | Logarithmic power plot in CCLS during transient                                                          | 52 |

| 6.19       | The Author proposes this level shifter to achieve negative levels in the capacitor coupled level shifter | 53 |

| 6.20       | Merged plot of all signals in Negative CCLS during LOW INPUT DC                                          | 00 |

| 0.20       | voltage for 50ms                                                                                         | 53 |

| 6.21       | Power plot in Negative CCLS during LOW INPUT DC voltage for 50ms .                                       | 54 |

|            | Merged plot of all signals in Negative CCLS during HIGH INPUT DC                                         |    |

|            | voltage for 50ms                                                                                         | 54 |

|            | Power plot in Negative CCLS during HIGH INPUT DC voltage for 50ms                                        | 54 |

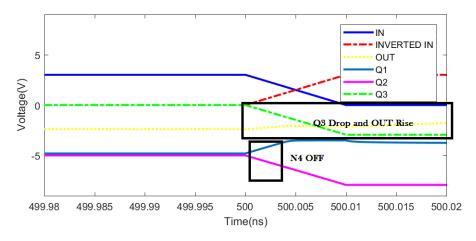

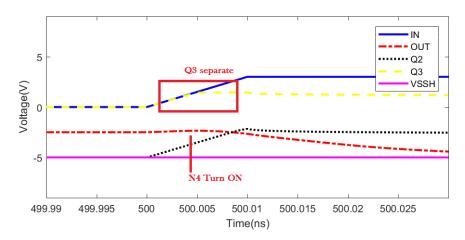

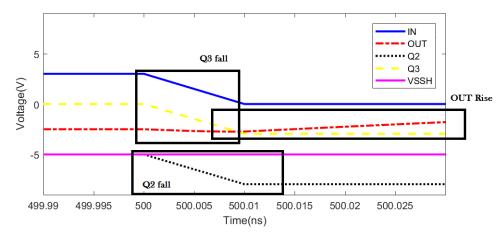

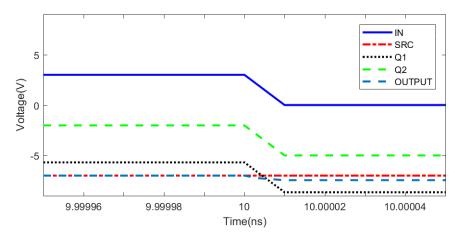

|            | Transition Mergeplot                                                                                     | 55 |

|            | Power plot Transition                                                                                    | 55 |

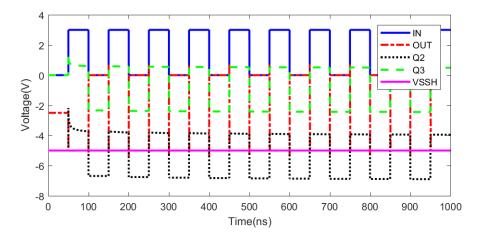

|            | Mergeplot Transient                                                                                      | 56 |

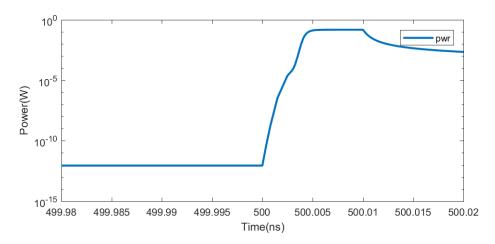

|            | Power plot Transient                                                                                     | 56 |

|            | Transition Mergeplot                                                                                     | 57 |

|            | OUTPUT signal in a transient waveform                                                                    | 57 |

| 6.30       | Power plot Transition                                                                                    | 57 |

List of Figures xvii

| 6.31 | Optimized negative level-shifter with two capacitors instead of three, and no $\overline{\text{INPUT}}$                                   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 6.32 | Merge Plot in Steady State of NCCLS                                                                                                       |

|      | Power Plot in Steady State of NCCLS                                                                                                       |

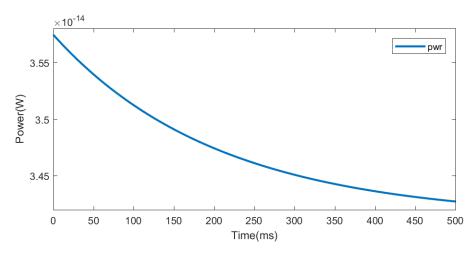

|      | Merge Plot in Steady State of NCCLS                                                                                                       |

|      | Power Plot in Steady State of NCCLS                                                                                                       |

|      | Merge Plot in Steady State to Transient of NCCLS 61                                                                                       |

|      | Power Plot in Steady State to Transient of NCCLS 61                                                                                       |

|      | Merge Plot in Steady State to Transient of NCCLS 61                                                                                       |

| 6.39 | Power Plot in Steady State to Transient of NCCLS 62                                                                                       |

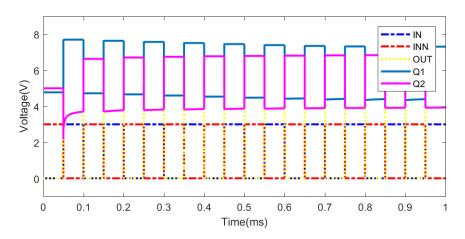

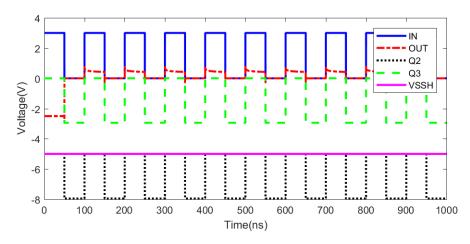

| 6.40 | Merge Plot in Transient of NCCLS                                                                                                          |

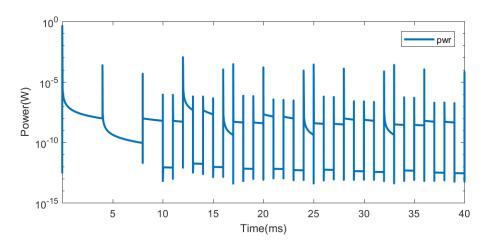

| 6.41 | Power Plot in Transient of NCCLS                                                                                                          |

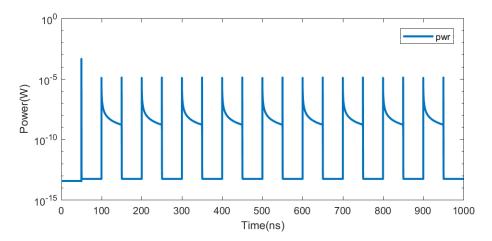

| 6.42 | Merge Plot in Transient of NCCLS                                                                                                          |

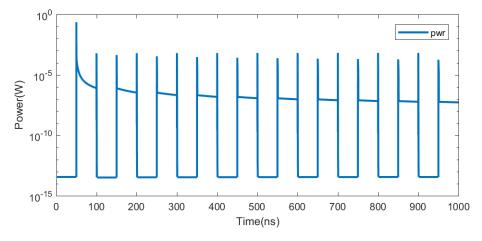

| 6.43 | Power Plot in Transient of NCCLS                                                                                                          |

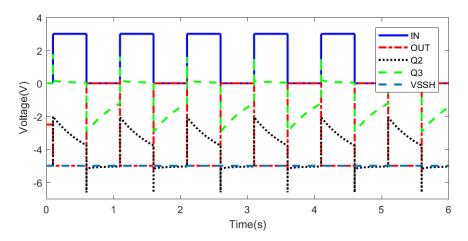

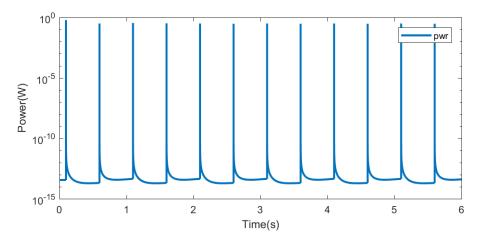

| 6.44 | Merge plot of signals in transient, where NMOS transistor N1 and N2                                                                       |

|      | is replaced with a single PMOS, running for 6seconds and a period of 1                                                                    |

|      | second                                                                                                                                    |

| 6.45 | Power plot in transient, where NMOS transistor N1 and N2 is replaced with a single PMOS, running for 6seconds and a period of 1 second 65 |

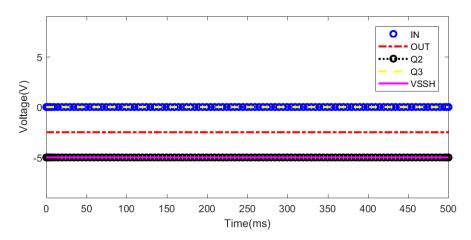

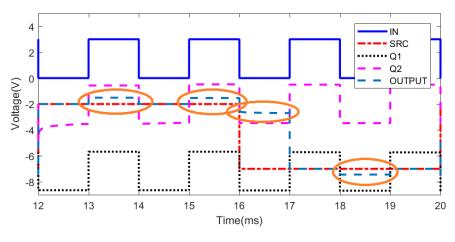

| 6 46 | Selecting output depending on Source Driver output Voltage 65                                                                             |

|      | Merge plot of signals in steady state,                                                                                                    |

|      | Power plot in steady state,                                                                                                               |

|      | Merge plot of signals in steady state transition to transient 67                                                                          |

|      | Power plot in steady state transition to transient                                                                                        |

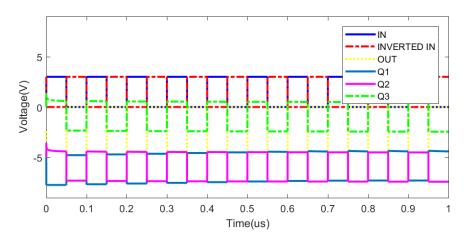

|      | Merge plot of signals in transient                                                                                                        |

|      | Power plot in transient                                                                                                                   |

|      | Merge plot of signals in transient                                                                                                        |

|      | Power plot in transient                                                                                                                   |

| A.1  | Figure                                                                                                                                    |

| A.2  | Figure                                                                                                                                    |

| A.3  | Figure                                                                                                                                    |

# List of Tables

| 6.1 | ${\bf Results\ From}$ | $\operatorname{design}$ | analysis | with | Cadence | Virtuoso |     |       |      |     |  | 71 |

|-----|-----------------------|-------------------------|----------|------|---------|----------|-----|-------|------|-----|--|----|

| 6.2 | Results From          | design                  | analysis | with | Cadence | Virtuoso | Rui | nning | at : | 2Hz |  | 72 |

# **Abbreviations**

OLED Organic Light Emitting Display

LDO Low Dropout

MCU Microcontroller Unit.

PARC Palo Alto Research Center

PCB Printed Circuit Board.

SOC System On Chip.

SOP System On Panel.

PM Passive Matrix

RAM Random Access Memory.

TFT Thin Film Transistor.

SPI Serial Peripheral Interface.

IoT Internet of Things.

RTL Resistor Transistor Logic.

CCLS Capacitor Coupled Level Shifter.

IC Integrated Circuit.

I/O Input / Output

DC Direct Current

AM Active Matrix PM

Passive Matrix

VCOM Voltage Common

GND Ground

# Chapter 1

# Introduction

Today computers are the backbone of society, largely due to the display which gives a straightforward way of operating a wide spread of tasks on the computer. The reason for the display popularity is that it can completely rearrange colors, text, and figures to fit the task the operator requires. Lately there has been a steady increase of low power computer chips which operate tasks such as sensors, motors, and communication. The frequency of the interactions with computer chips are low, ranging from hourly to monthly which is why they often run on battery and are placed remotely often without display to save power.

The dominating display on the market is the Liquid Crystal Display (LCD) [10, P.14]. This type of display generally needs high refresh rates and backlighting, which makes them unsuitable for low power devices. An alternative that dates back to the early 1970s is called the Electrophoric Paper Display (EPD). This display uses the reflectiveness of the particles in the pixels to display the image. The EPD is completely independent of an external power source once the image is formed which is known as bistable behaviour. Because of the low power properties of EPD, it would be interesting to integrate it with low power computer chips.

This chapter will give an introduction to the topic area for this thesis. The project motivation is first presented, which explains the reason why this work is important for designing a low power display driver. The project goal is then presented to set the expectations or aim for this thesis. The chapter outline will go through the chapters, and should help the reader navigate through this thesis. Lastly the main contributions has been added from the work done by the author.

Introduction 2

### 1.1 Problem Description

Adding a display to small sensors and controllers powered by computer chips have been desired in Internet of Things (IoT) applications for several reasons. These devices operate remotely, and may fail, be reconfigured, and should be inspected. Adding a display will give these devices an opportunity to be identified, and can display messages and figures that helps the operator. A tradeoff between lifetime and operational convenience will usually end up prioritizing the lifetime because the intended lifetime is several years. For this reason the display will rarely be implemented because of its significant power increase.

### 1.2 Motivation

A new type of display called the Electrophoric Display (EPD) has reached a remarkable state of maturity. The image quality is high and operating voltage has reached a low of 5V. The larges benefit of the Electrophoric display is known as the bistable property, and allows images to be contained with no flowing current. Because the electrophoric display is already considered very low power, most publications are leaned to higher refresh rate, and better image quality [11] [12] [13] [14] [15]. This thesis will investigate the use of unipolar driving waveform to achieve lower power consumption. Unipolar voltage means that voltage over a load, drop from a positive voltage  $v_1$  to an equal but negative voltage  $v_2$ . Such that  $||v_1|| = ||v_2||$  but  $v_1 \neq v_2$ . Unipolar waveform means that the polarity over the load can change in a waveform, such that  $v_1$  changes to negative and  $v_2$  changes to positive voltage. The design focus is to achieve a new architecture capable of unipolar output, that occupies small area and use low power.

## 1.3 Project Goals

Before the display driver may be implemented on chip the submodules of the driver should be investigated. With consideration of the new driving waveform (unipolar), various requirements and limitations of the display driver will be reviewed. The overall project goal is to prepare a unipolar display driver for integration on chip. The level shifter which holds an integral part of the display driver should be considered for power optimization. The tasks listed below highlight the areas of interest:

• Investigate and define the operation of a display driver.

Introduction 3

• Use the information to describe the most power consuming parts of the display driver.

- Investigate level shifters that can replace conventional level shifters with less power consumption.

- Consider how a unipolar architecture will affect the gate driver.

- Model the subcircuits in Cadence Virtuoso to find the improvements.

### 1.4 Chapter Outline

The first **Chapters 2 to 3** is based on a literature study, where the background and working principles of EPD are described. **Chapter 4 and 5** is a collection of new low power sub circuits that will support unipolar driving waveform.

Chapter 2 introduces the principles of the electrophoric display and how it is electrically driven.

Chapter 3 will assess papers and books that has covered the electrophoric display and related issues. The electronic paper display has been around for several decades [16], and there has been many contributions over the years in this field. This chapter covers many topics which form a basis for the thesis. The contributions help define which part of the driver should be subject to optimization.

Chapter 4 is considered the main topic of this thesis. A low power source driver is obtained by reducing power consumption in level shifters. Three level shifters have been described in this chapter.

Chapter 5 investigate the gate driver in the circuit, which is affected by the change to a unipolar driving waveform. The gate driver is responsible for allowing or stopping current from entering the pixel, which is closely connected with the source driver.

Chapter 6 will present and discuss the results of a simulation of five level shifters. This is done in three steps, (1) steady state, (2) transition from steady state to transient, and (3) transient. The last part of this chapter will present the gate driver.

Chapter 7 The project goals are concluded. Further Work is presented.

Introduction 4

## 1.5 Main Contributions

The main contributions made by the author is listed below.

- Negative Capacitor Coupled Level Shifter(CCLS) (Chapter 4.1)

- Optimizing the level shifter for CMOS technology (Chapter 4.2)

- Discovered gate driver properties which is optimized for unipolar driving waveform (Chapter 5.3)

- Current Properties in Electrophoric Display (Chapter 5.2)

- A new gate driver for Electrophoric Display (Chapter 5.3)

- Modeling sub circuits and presentation of results 6

# Chapter 2

# Introducing the Electrophoric Display

The electrophoric display (EPD) was introduced firstly to mimic the need for ordinary ink on paper. It has the benefit of good reflectivity, wide viewing angle, being thin, lightweight and having high power efficiency [12]. This chapter will present some general information of the electronic display.

## 2.1 History of Electrophoric Paper Display

The 'electronic paper display' is dated back to 1970s [16], first created in Xerox's Paolo Alto Research Center (PARC). The paper display was patented by Nick Sheridon, and the technology was called Gyricon. The Gyricon uses the principle of rotating beads encapsulated in an oil-filed cavity.

In the late 1980s, the personal computer and printer started to hit the marked. A consequence of this was an increase in the total paper consumption, and researchers began to see the need for electric paper. The Gyricon was thought of as a good candidate to replace ordinary ink on paper. In 1997, E-Ink Corporation was founded and they introduced the worlds first active matrix EPD display in 2001, this was later named E-Ink Vizplex [17]. Where Gyricon relied on rotating beads, the E-ink technology was based on the movement of electrically charged particles. This was considered an upgrade. Today we can see e-paper technology in many consumer products such as smart watch, e-readers, and shelf-labels.

### 2.2 Operating Principle

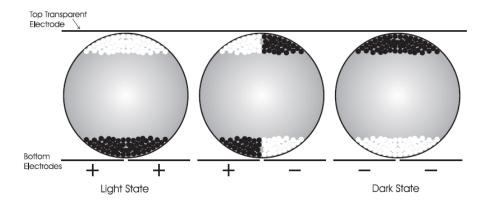

The electronic ink consist of small microcapsules bound together with a material such as silicon resin [12]. Figure 2.1 shows a schematic cross-section of the electronic ink known as the electrophoric display.

The microcapsules in the figure contain tiny charged particles suspended in a solvent. Currently, they are using dodecylbenzene dyed with anthoraquinon blue for the solvent. There are two types of particles in the solvent, positive[white] and negative[black], with opposite charge. The particles may rearrange when an electric field is applied [1, P.17]. This is what forms the image. One of the properties of EPD is its zero field stability, also known as bistability behaviour. This means that after the image is formed, even if the electric field is removed, the particles will remain at their current position. This behaviour can be traced back to the particles internal charge. The particle placement

## Cross Section of Electronic Ink Microcapsules

Figure 2.1: Principle of electronic inc [1]

is dependent on two factors, the electric field strength and the duration of the applied electric field. Because the system inside the electronic paper is complex, models are based on the chemical and physical process ??. As a first approximation, it is assumed that charged particles follow a normal(Gaussian) model. This is in good accordance with reality [11]. Moving the particles are given by Stokes' theorem (Equation 2.1) [5] [18].

$$v(t) = qE(t)/(6\pi\eta a) \tag{2.1}$$

where q is the charge of the particle, E(t) is the effective electrical field at time t,  $\eta$  is the viscosity of the solvent, a is the particle radius. Based on this equation the moving

distance D, is given by  $D = v(t) \cdot w$ , where w is the response time of the system. The distance D between two plates are usually about  $100\mu$ m appart [11]. Even with voltages over 10V, it can take up to 500ms to reach a full optical contrast [2].

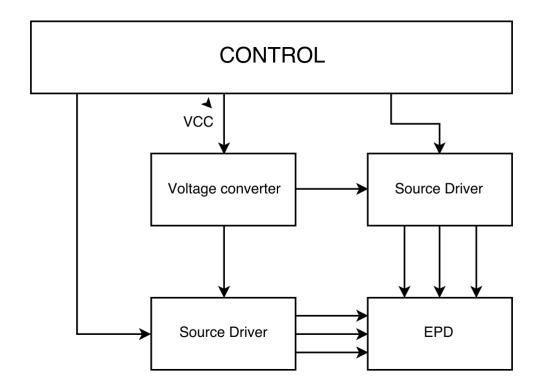

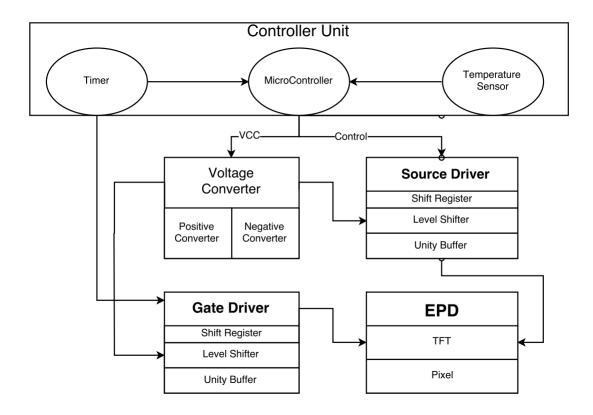

### 2.3 EPD Driving Circuitry

The EPD driving circuit can be created with five main elements, the control unit, the voltage converter, gate driver, source driver, and the electrophoric display [6]. Figure 2.2 show a schematic overview of a simple EPD driving circuit.

FIGURE 2.2: Simple driving circuit for the EPD

### 2.3.1 Control Unit

The control unit initializes the image write, it keeps track of the previous image, and ensures correct behaviour of the voltage converter, gate driver and source driver. It may include a timer to prevent race conditions between the gate driver and source driver. The EPD is largely dependent on temperature [19], so it may also include a temperature sensor.

### 2.3.2 Voltage Converter

If the display run on a different voltage domain then the rest of the system, the voltage converter can supply a separate voltage for those parts of the system. The voltage converter supply the gate and source driver with the driving voltage for the EPD. Voltage converters can convert up, down, and invert.

### 2.3.3 Source Driver

The source driver is responsible for setting all pixels in the EPD. It applies a voltage for a certain duration to every pixel, which forces the pixel reflectivity (black to white or white to black) to change.

#### 2.3.4 Gate Driver

The gate driver works as a gatekeeper, and can "open and close" the gate. The gate is a transistor, when in an "open" state it allows the source lines to write the pixel. The use of a gate is common in many displays, and the technique is referred to as active addressing. The use of a gate driver is however not required i.e. passive addressing. E-Ink, which is the largest distributor of electronic paper displays, delivers one type of segmented display without gates. These have low resolution and require extensive wiring to passively address all the pixels. A very low resolution display of 30 x 30 pixels would need to escape 900 wires to passively address all the pixels. For this reason this thesis will present active addressing technique which requires less wiring.

### 2.3.5 Electrophoric Display Structure

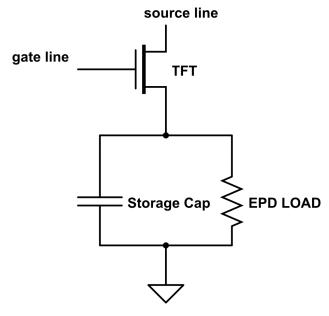

The material of the EPD is discussed in Section 2.2. To form a display, newer electrophoric material is coated on a thin film transistor (TFT) backplane [20]. The TFT is the gate driven by the gate driver. The use of TFT allows the gate and source driver to perform addressing.

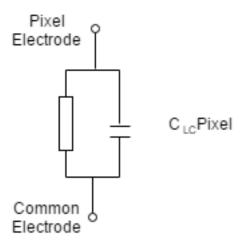

The electronic paper pixel is usually modeled by a very large resistor in the range of giga ohms [2, P.47] [21, P.3], this is visualized in Figure 2.3. A storage capacitor may optionally be added. With a storage capacitor, the display driver can quickly write a pixel by charging up the capacitor, and then move on while the pixel will be driven by the capacitor. The system inside an electronic paper pixel has a very high electrochemical complexity [11, P.1]. This paper will not try to model the electronic pixel, but simple

current characteristics are of interest. The current is given by the total number of charged particles, that is present inside the pixel, weighted with their velocity [11, P.54].

FIGURE 2.3: EPD pixel modeled with a TFT-gate and storage capacitor

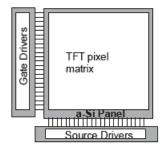

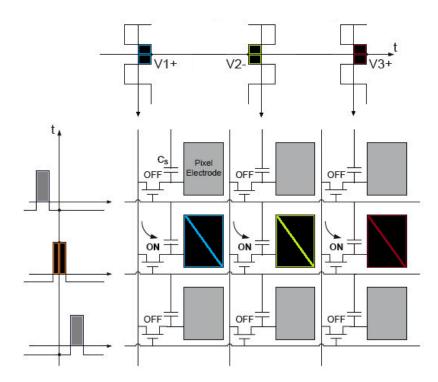

## 2.4 Principles Of The Electrophoric Display Addressing

The electophoric display share many similarities with other displays like Liquid Crystal Display(LCD), and the Organic Light-Emitting Diode(OLED) to name a few. For an m x n sized LCD/OLED display, containing m rows times n columns of pixels, every row would be connected to a gate line, and every column is connected to a source line. A common way of driving LCD/OLED display is by utilizing an active matrix driving scheme. Although there exists other ways of driving a display, such as the passive and direct addressing schemes, the mobile marked and computer display has embraced the active matrix addressing as its standard. This is mainly due to the stability of threshold-voltage [19] and the scalability in the active matrix addressing. Figure 2.4 shows an overview of an TFT (a-Si type) display connected to the source and gate driver. This is similarly true for the electrophoric display, and the EPD driving circuit could for this reason be based on the same LCD/OLED driving circuit.

### **Active Matrix Addressing**

In active matrix addressing each pixel has its own dedicated TFT, allowing the column lines to access the pixel. The gate drive will scan each row sequentially so that the source driver only write to the current activated row. In Figure 2.5 a LCD pixel  $C_{LC}$

FIGURE 2.4: a-Si display connected to source and gate driver

is modeled by a capacitor and a resistor connected to an address TFT. The optional storage capacitor is also included in the figure.

FIGURE 2.5: A pixel connected to a thin-film transistor [2]

### Top to Bottom Topology

The gate driver scans each row sequentially from top to bottom, during the scan time the source lines can write the pixel. Figure 2.6, shows a gate drive activating one row while the source lines write that row. In order to ensure correct behaviour, a timer can be integrated to monitor and control to the gate and source driver. This will avoid any potential race conditions.

### **EPD Addressing**

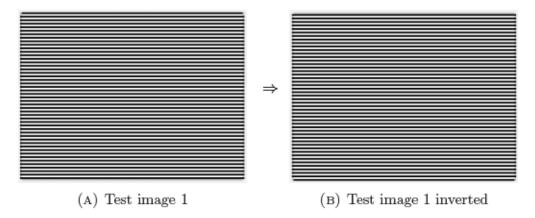

The active matrix addressing display driver is well suited for driving the EPD. The difference from an active matrix LCD is that the source lines now also carry negative voltage while LCD source lines only carry positive voltage. To adjust for this, the gate driver must also support resultant voltages which are negative, and the voltage on the TFT gate must follow. If a row is originally turned OFF when the source driver is positive, it might turn ON if the source lines suddenly turn negative. This will typically

FIGURE 2.6: Sequential addressing of TFT display

happen in images with many vertical transitions. Vertical transitions is known as an image pattern with alternating black and white horizontal lines as seen in Figure 2.7.

Figure 2.7: Vertical transitions in an image [2]

## 2.5 EPD Driver Architectural Topology

Building a basic TFT-EPD driver involves the sub components found in Figure 2.8. It shows the same setup as the simple driving circuit for the EPD, as well as revealing the internal components in the display driver.

Figure 2.8: Internal components of the EPD driver

### Voltage Converter

A lot of development has already been put into creating voltage converters, many companies such as Texas Instruments, and Linear Technology deliver complete DC/DC chip solutions. Key design qualities to look for with voltage-converters are, degree of voltage-setting accuracy, load-current delivering capability, stability of the output voltage, power consumed by the converter itself, and cost of implementation. It is encouraged to use complete chip solutions for embedded systems. There exist no EPD specific voltage converters, for this reason it is considered beyond the scope of this thesis, and is left to the designer.

### Source Driver Topology

The source driver consists of a shift-register (serial to parallel) as seen in Figure 2.9, connected to a latch to hold off the output until all the bits are set. Figure 2.10 shows a block diagram of the shift register connected to a latch. The output from the latch is then sent to the level shifter. This is where the voltage rises from the low control voltage to the high voltage required by the EPD. Not to be confused with a digital convention for LOW and HIGH voltage meaning zero or one. The last function in the source driver is the unity buffer also known as digital buffer. This is an electrical component where the input is isolated from the output. It draws very low current from the input because

of the very high impedance, but can apply the output with higher current options from a different source. It is also called a unity input buffer because the gain is 1.

#### Gate Driver Topology

The process is similar for the gate driver, however instead of parallel output, the gate driver utilizes a shift register to scan the rows sequentially. The gate driver will use the shift register without a latch, this output is seen forming a walking 1 waveform as in Figure 2.11. The output of the shift-register is inserted into the level-shifter, again raising the voltage level, this time to the appropriate gate voltage, which may be different from source voltage. It is then asserted into the unity buffer before turning ON the thin-film transistor If the timing is correctly performed for the source and gate driver, an image will form on the TFT-EPD.

Figure 2.9: Shift register circuit [3, P.223]

FIGURE 2.10: Block Diagram of a shift register connected to a latch [3, P.131]

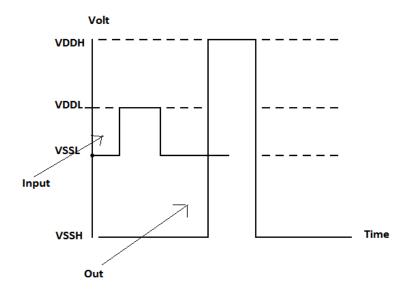

## 2.6 The Voltage Domain

In any high voltage system where the input is not in the same voltage domain, a level shifter is required before communication can continue. If the general system is powered by VDDL and VSSL, then the source lines would be powered by VDDH and VSSH.

Figure 2.11: Shift register; walking one [3, P.223]

Figure 2.12 show how the source-driver will convert a logical pulse signal to an appropriate driving voltage level for the pixel. The pixel is usually driven by voltages between  $\pm (5-15)V$ , but this could vary dependent on the response time of the pixel, and the driving waveform.

FIGURE 2.12: level-converting logical input voltage to pixel driving voltage

## 2.7 TFT-properties

The thin-film-transistor (TFT) was introduced as a switch for active matrix addressing. It exhibits poorer properties than the MOSFET in terms of switching speed and

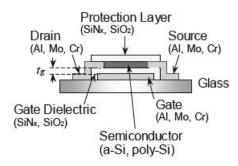

conductance, but has the advantage of being transparent. The TFT is implemented on an insulating substrate, such as glass og polymer substrate, and therefore lack the body or bulk found in conventional MOSFET [3, P.146]. It has the three terminals named Drain (D), Gate (G), and Source (S). The gate-source voltage,  $v_{gs}$ , determines the TFT ON/OFF condition. The n-channel TFT operates similarly as the n-channel MOSFET. A cross-section of the TFT is presented in figure 2.13,

FIGURE 2.13: Cross-section of a basic tft [3, P. 147]

#### 2.7.1 a-Si:H TFT

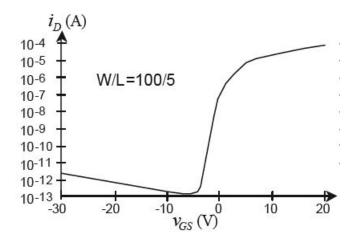

The most common layer used in the integration of TFT on glass is with a-Si:H amorphous silicon. The fabrication is easier due to low-temperature process. The main difference between a-Si:H TFT and the Si MOSFET is the electron mobility. 0.2- $1.5cm^2/Vs$  while the crystalline Si has more than  $1800cm^2/Vs$ . For this reason the a-Si:H TFTs are unfit for use in analog and high-speed digital processing, however they are usefull as a switch (ON/OFF) with frequencies around 60HZ. A problem that arises because of this low mobility is the very large aspect ratio needed. This will reduce the aperture-ration, i.e. only a portion of the pixel's area will be visible through the TFT. To adjust for this problem, it is shown that the transconductance is also dependent on the gate-source overdrive, so the TFT can be driven by a high voltage, typically 20V. The a-Si:H TFT shows poor stability and can be modified by strong illumination and charge carrier injections, therefore it must be covered from light. Another issue with the a-Si:H TFT is its temperature dependence, where  $V_{th}$  is dependent on two temperature parameters. The shift is not a problem for ON/OFF operations, but becomes impairing when static noise margin decreases in digital circuits. The shift has different polarities at ON/OFF state, at zero volts, a partial cancellation occurs as in Figure 2.14.

Transistor OFF region lies in negative [5 to 7]V and ON state is found at positive [5 to 10]V. In each case, a practical design must take into account a threshold tolerance level.

FIGURE 2.14: Drain current versus gate-source voltage for an n-channel a-Si TFT with W/L=100  $\mu$ m/5  $\mu$ m [3, P. 151]

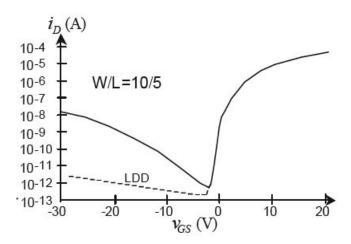

#### 2.7.2 poly-Si:H TFT

Polycrystaline Silicon is an alternative material used to realize the TFT. The advantage is the ability to make both p-type and n-type devices as well as higher carrier mobility (up to two orders of magnitude). The high carrier mobility, means smaller TFT-area (1/10 of its a:Si counterpart), which makes them suitable for CMOS-like systems, rising the idea of system on glass (SOG). The preparation of Polysilicon is more complicated then a-Si TFT, in turn adding an extra cost to the end product [3]. The additional cost is one reason why a-Si TFT is more popular the Poly-Si:H. Figure 2.15 shows the Drain current for Polysilicon versus the gate-source voltage. It can be seen that OFF leakage currents are higher the a-Si TFT.

FIGURE 2.15: Drain current versus gate-source voltage for an n-channel Poly-Si TFT with W/L=10  $\mu$ m/5  $\mu$ m [3, P. 151]

Comparing both Poly-Si and a-Si TFT shows that displays with high pixel density is best addressed with Polysilicon. Currently E-INK together with Epson is experimenting on Polysilicon in their EPD [22], and may have used this with their product. This detail

is not available throught E-Ink's own datasheet, however the datasheet of E-Ink Carta is indicating that this is optional [23].

# Chapter 3

# Previous Work

There has been several contributions in recent years to improve the EPD, in terms of efficiency [24], quality, speed [19], and removal of unwanted effects such as the ghosting effect [25]. Modifications in updating sequence, software modifications and hardware are all possible techniques to save energy. Although all the properties listed above will be reflected in the total power consumption, this thesis focus on the hardware based approach to gain a power efficient electronic paper.

This chapter covers previous work in six major topics which will be described in the following order.

- Power Consumption Investigation Breaking down the parts of the EPD which use power is considered important if the solution should become low power.

- Low Power Electrophoric Display Module The unipolar driving waveform is presented and the source driver is broken into two categories that will help the low power discussion in later chapters.

- Configurable timing controller for AM EPD describes a more detailed view of the unipolar driving waveform.

- Low Power Electrophoric Display gives an overview of the possible power savings using unipolar driving waveform.

- Power Reduction in D-RAM Technology shows how leakage currents can be handled to acheive better performance in transistor technology.

- Capacitor Coupled Level Shifter describe a new level shifter with very low power consumption. Note: Article description is inconsistent with results, the section is described as the article presents it.

### 3.1 Power consumption investigation

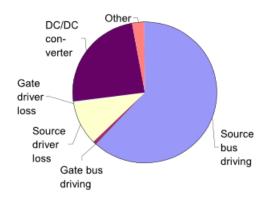

In 2002, Pitt [4] published a detailed investigation of power in the electrophoric display, together with Philips Mobile Display Systems and E-Ink Corporation. Under a constantly switching worst case situation of the updating sequence, and using  $\pm 15$ V to update the image, it was found that the largest part of the power consumption comes from driving the source lines. A breakdown chart of the power consumption is shown in Figure 3.1.

To understand the power consumption, consider driving the column signals (source lines) for electronic ink. Energy is **only** consumed by the capacitive components when the source voltage changes. With the additional high voltage used for driving the display, the power usage is considered highest in the level shifter and buffer, both of which are regulating high voltage.

FIGURE 3.1: Breakdown chart for power usage [4]

To determine typical power consumption during continuous operation, a sample of different text images was analysed. Figure 3.2 shows the results. In normal text mode, approximately 10% of the pixels are black, this proportion increases somewhat for larger fonts, up to 20%. There is interestingly not an increase in power because of this, because it is dependent on the number of vertical transitions.

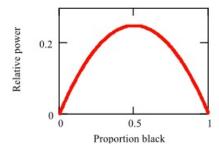

In cases of graphic data, the power consumption will be dependent on the type of image displayed. Images having a large portion of horizontal lines or dotted lines will have a much larger power level then images with same color tone. To simulate this, an image consisting of random placement of black and white pixels was created. The power as a function of black pixel density is shown in Figure 3.3. The simulation assumes that the number of black pixels are the same for the old and new image. The highest power level

Figure 3.2: Power as function of font type [4]

FIGURE 3.3: Power as function of black pixels for image transition [4]

is found when the portion of black pixels are at 50%, in this case the power consumption is at 25% of the maximum value of the power level.

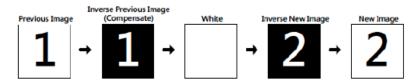

## 3.2 Low Power Electrophoretic Display Module

A Low Power Electrophoretic Display Module was developed by S. Gunnerød, as a master thesis in 2016 [2]. Based on an analysis of the sub modules in the electrophoric display driving circuit, Gunnerød presented a method for power reduction. Given a pixel such as in Figure 3.4, the common electrode in the EPD is traditionally fixed at 0V, while the pixel electrodes are switched between +15V and -15V called bipolar driving waveform.

If the common electrode instead is set at the opposite polarity as the pixel electrode then the total voltage span will be 30V. This is called a unipolar driving waveform.

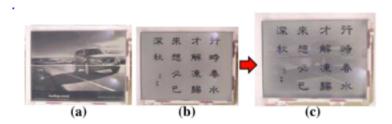

For e-reader applications and large size EPDs, the biggest gain in using a unipolar waveform is to reduce image updating time, ghosting effect and flicker. An explanation

FIGURE 3.4: Modeling a Pixel

of ghosting effect and flickering is available in appendix A. Because the focus for small EPD and low power consumption is of priority, a second compelling aspect can be exploited. The voltage can potentially be reduced to half of what is used in bipolar driving waveform. In cases where the display is only updated on occasional basis, a 5V over the pixel electrode can be used, and the driving voltage can be reduced to  $\pm 2.5V$ . Because the voltage has a quadratic relationship to power then this will have a substantial effect over the power consumption.

#### 3.2.1 Source Driver Power - Digital Part

The digital part of the source driver consists of latches and shift registers. The architecture of a shift register is area consuming, and increases for larger displays. The typical data flip-flop is twice the size of a latch because of the additional clock signal. Since N flip-flops are required for a display with n columns, there will typically be N flip-flops and 2N latches in a traditional source driver. The power dissipation is proportional to the clock scan frequency and its total capacitance. The power dissipation can be reduced by sampling bits on both edges of the clock [3][P. 225]. The total power consumption can thereby be reduced by a factor of two. For a typical LCD source driver, the digital part's power dissipation is close to 10% of the total [3][P. 218]. An EPD source driver is expected to have similar properties.

#### 3.2.2 Source Driver Power - Analog Part

This is the part of the source driver related to high voltage, and accounts for the remaining 90% of the total power dissipation [3][P. 218]. There are two main reasons for power dissipation in the analog part, static power related to leakage, and dynamic power.

Static power dissipation occurs all the time, as transistors are always leaking current through Gate, Drain and Source, and also by short circuiting. When transistors are changing state, a short circuiting may occur because both transistors are partly active. However dynamic power dissipation is considered most significant. Dynamic current draw occurs when the parasitic capacitance in the transistors is charged up and down due to state changes.

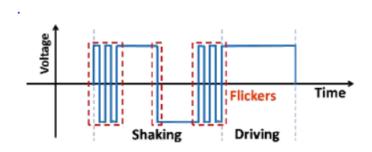

### 3.3 Configurable timing controller for AM EPD

A configurable timing controller provides an easy way to modify waveforms under different design requirements [5]. To facilitate design changes, an EPD timing controller should be configurable. The article describes important design considerations: (a) The activation sequence of charged particles. (b) The movement of charged particles for displaying desired gray level, and (c) the bistable properties and the image erase sequence. The driving waveform is difficult to correctly produce, since timing is set by driving the pixel to a state and measuring the reflectance.

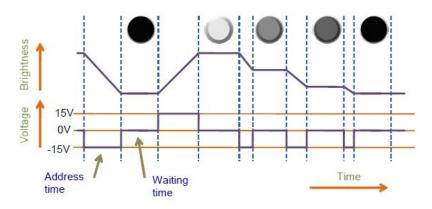

FIGURE 3.5: Bipolar driving scheme [5]

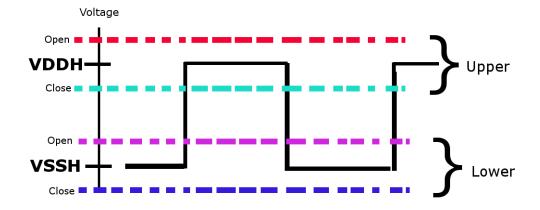

There exist no good models for accurately predicting the movement of particles. Figure 3.5 show a waveform called bipolar driving in this paper. The common electrode is set at 0V and the pixel electrode is set at  $\pm 15V$ . The voltage difference is 15V and the gray level is controlled by giving different voltage pulses.

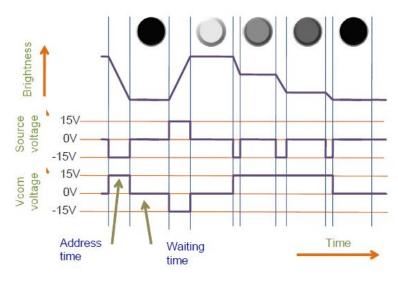

An alternative approach is called unipolar driving waveform, this utilizes the common electrode to hold the opposite polarity as the pixel electrode. Because the voltage difference becomes 30V, this will speed up the particle state transition as seen in Figure 3.6.

FIGURE 3.6: Unipolar driving scheme [5]

### 3.4 Low power Electrophoric Display - Specialization project

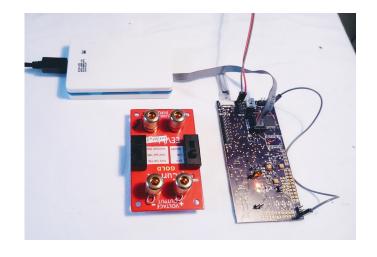

(A)

Segmented display

showing black segments [6]

(B) Circuit board (purple), programmer (white), and  $\mu$ current tool (red) [6]

Figure 3.7: Specialization Project

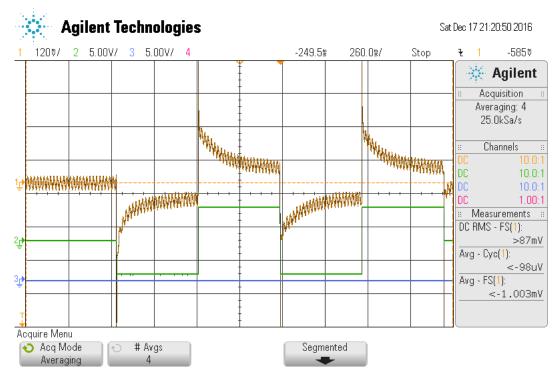

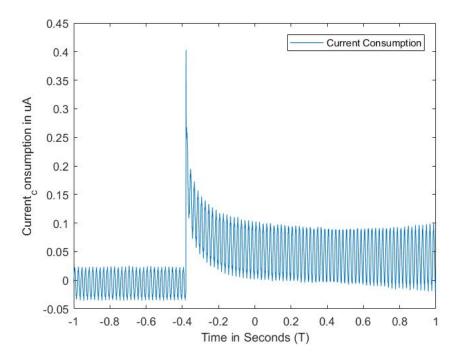

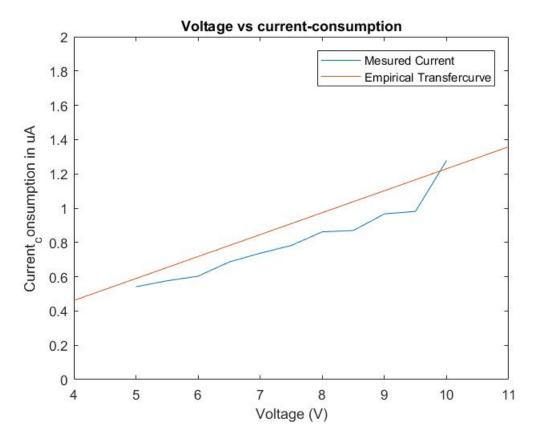

A specialization project was carried out in the fall of 2016 by Mattis Spieler Asp [6]. The main purpose was to evaluate and give a working example of unipolar driving in a real EPD. A segmented display bought from E-INK seen in Figure 3.7(A) was used together with a self designed unipolar display driver seen in Figure 3.7(B) as the purple PCB. The display was running on 5V, and using unipolar drivers of  $\pm 2.5$ V. Calculations based on the results show that for a regular 7" display, given the worst case update scenario, power can be reduced by almost 75% using this technique. Measurements also show that a segmented display consumes about  $0.6\mu\text{W}/\text{cm}^2$  in a state change (black to white/white to black). Figure 3.8 shows the impulse response of the current going into

the EPD when alternating the unipolar voltage, this is the same as switching between black and white color. The current swing can reach up to 420nA per segmented display. Which is 30nA per segment.

FIGURE 3.8: Oscilloscope measurements at the Electrophoric Display, showing an avg current draw of 86.9nA [6]

## 3.5 Power Reduction in D-RAM Technology

Level shifters have been used in the past together with D-RAM to adjust resultant voltage levels, ensure stable operation, and retention characteristics [7]. The voltage level shifter is a required part of D-RAM and flash memories. For this reason many power reduction schemes has been developed for D-RAM level shifters.

To realize low-voltage RAMs, subthreshold leakage of both RAM cells and peripheral circuits must be reduced. Through various reverse bias schemes one can achieve higher threshold value for the transistor, thus minimizing leakage current. [7, P.151].

#### 3.5.1 Reverse Bias Leakage Reduction

The leakage current of MOSFET (i.e subthreshold current) can be expressed by [7, P.152]

$$i \propto e^{\pm \frac{V_{GS} - V_t - K(\sqrt{\pm V_{BS} + 2\Psi} - \sqrt{2\Psi}) + \lambda V_{DS}}{S/ln10}} \cdot (1 - e^{\pm \frac{qV_{DS}}{kT}})$$

(3.1)

where the upper sign refers to the NMOS and lower sign refers to the PMOS transistor.  $V_t$  is the actual threshold value, S is the subthreshold swing, K is the body effect coefficient, q is the electronic charge, k is the Boltzmann constant and T is the absolute temperature. Leakage is usually decreased with a factor of 10 with a  $V_t$  increment of 0.1 volt for a bulk MOSFET with  $S \cong 100 \text{mV/decade}$  at  $100^{\circ}\text{C}$ . The best way to reduce leakage current is to increase  $V_t$ . There are categorically two ways of getting high  $V_t$  from a low  $V_t$ . The first is enhancing the actual  $V_t$  by increasing the doping level of the substrate, the second to raise the effective  $V_t$  by applying reverse-biasing schemes. The basic concepts for reverse-biasing can be viewed in Table 3.9.

| Modified voltage(s)                 |                                          | nMOST                                                                                   | pMOST                                                                                                                                 |  |

|-------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| (A) V <sub>GS</sub> reverse biasing | (A1) $V_S$ : self-reverse biasing        | $0 \xrightarrow{G} \begin{bmatrix} V_{DD} \\ B \\ S \\ +\delta \end{bmatrix}$           | $V_{DD} \overset{\mathbf{G}}{=} \begin{matrix} \mathbf{S} & V_{DD} - \delta \\ \mathbf{B} & V_{DD} \\ \mathbf{D} & 0 \end{matrix}$    |  |

|                                     | (A2) $V_G$ : offset gate driving         | $-\delta \xrightarrow{G} \begin{bmatrix} V_{DD} \\ B \\ S \end{bmatrix}_0^{V_{DD}}$     | $V_{DD} + \delta \xrightarrow{\mathbf{G}} \begin{bmatrix} \mathbf{S} & V_{DD} \\ \mathbf{B} & V_{DD} \\ \mathbf{D} & 0 \end{bmatrix}$ |  |

| (B) V <sub>BS</sub> reverse biasing | (B1) V <sub>B</sub> : substrate driving  | $0 \xrightarrow{G} \begin{bmatrix} V_{DD} \\ B \\ S \end{bmatrix}_{0}^{V_{DD}}$         | $V_{DD} \stackrel{\mathbf{G}}{=} \begin{matrix} \mathbf{S} & V_{DD} \\ \mathbf{B} & V_{DD} + \delta \\ \mathbf{D} & 0 \end{matrix}$   |  |

|                                     | (B2) $V_S = V_G$ : offset source driving | $ \begin{array}{c c} D & V_{DD} \\ \hline G & B & 0 \\ \hline S & +\delta \end{array} $ | $\begin{array}{c c} S & V_{DD} - \delta \\ \hline S & B & V_{DD} \\ \hline D & 0 \end{array}$                                         |  |

| (C) $V_{DS}$ reduction              |                                          | $0 \xrightarrow{G} \begin{bmatrix} V_{DD} - \delta \\ B \\ S \end{bmatrix}_{0}$         | $V_{DD} \overset{\mathbf{G}}{=} \begin{matrix} \mathbf{S} & V_{DD} \\ \mathbf{B} & V_{DD} \\ \mathbf{D} & + \delta \end{matrix}$      |  |

Table. 3.9: Concepts for creating high  $V_t$  [7, P.153]

The table represents (A)  $V_{GS}$  reverse-biasing, (B)  $V_{BS}$  substrate-driving, and (C)  $V_{DS}$  reduction.

They can be split into basically two categories; static or dynamic with relation to threshold values of the transistor. The selective use of high  $V_t$  MOSFET in a low  $V_t$  circuit decreases the leakage current of the circuit. The static high  $V_t$ , also known as dual- $V_t$ , is used to combine high and low  $V_t$  together in circuits. The CMOS dual- $V_t$  in which the low  $V_t$  is only used for the critical path will effectively lower the leakage-current, while simultaneously achieving the high speed requirements. It should be noted that extensive reverse biasing may lead to race-conditions in the circuit.

#### 3.5.2 Refresh operation

After a cell is written in D-RAM the high voltage decays over time, charge losses are due to leakage currents,  $\alpha$ -particles or cosmic-ray neutron irradiation. At some time before the voltage falls below the high-voltage read-limit, voltage must be restored by a refresh operation. This is done by reading the word on the cell and reinstating the same voltage.

#### 3.6 Conventional Level Shifter

The conventional level shifter is regularly used for generating waveforms such as the one suggested in Figure 2.12 [3]. A conventional level shifter can be seen in Figure 3.10. The circuit consists of a CMOS inverter, M1 - M2, supplied from VSSL and VDDL and two latches. The latch, M3 - M6, supplies the negative supply, and M7-M10 supplies the positive latch.

Figure 3.10: Conventional level shifter [3]

The conventional level shifter is considered fast, and uses little area [3] [26]. An undesired limitation with this circuit occurs when the circuit is switching, the **cross-conduction** current (flowing from positive supply rail to negative) occurs because the transistors change their logical state and are momentarily ON due to a delay in their signal [3]. Although it occurs at a brief moment, the actual current may be significant because only the **ON resistance** of the transistor is limiting the magnitude. The biggest disadvantage with the conventional level shifter is related to the feedback loop. Every transition in IN will require that stored energy in the circuit is fully committed to ground [6]. This is a result of a former charge buildup in the internal capacitance of the transistor.

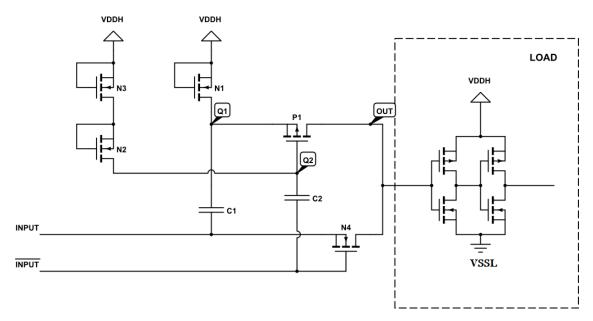

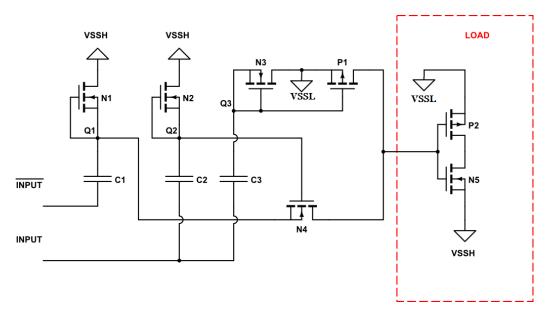

## 3.7 Capacitor Coupled Level Shifter

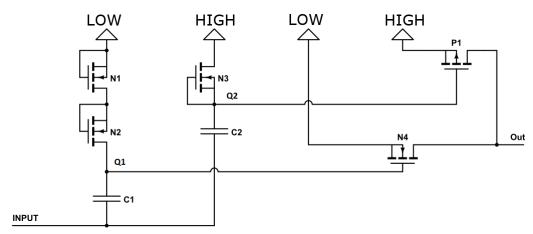

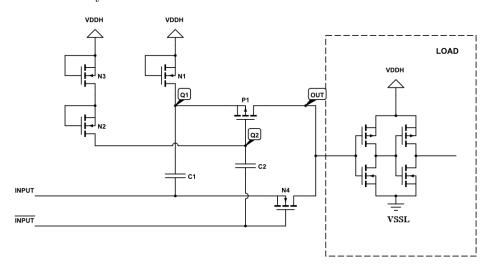

The capacitor coupled level shifter (CCLS)[8] can produce a positive drive output. It was introduced to limit the number of transistors sourcing ground on transitions between VDDH and VSSH in the feedback loop. The CCLS is composed of two coupling capacitors, three diode-connected transistors, two switches and a load. Transistor N4 pulls down to the voltage of INPUT, whereas P1 pulls the voltage of the node OUT up to the voltage of node Q1. N4 has low voltage logic inputs, whereas P1 has high voltage nodes connected. The design in Figure 3.11 is motivated by an offset voltage formed by

two capacitors C1, C2, and the identical diode-connected transistors N1, N2 and N3.

FIGURE 3.11: Capacitor Coupled Level Shifter [8]

#### 3.7.1 Transient Response

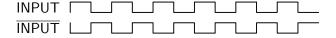

Assuming INPUT toggle as in Figure 3.12.

FIGURE 3.12: INPUT and  $\overline{\text{INPUT}}$  toggle.

Initially when INPUT is LOW(VSSL) and hence  $\overline{\text{INPUT}}$  is HIGH(VDDL), C1 is charged to the voltage VDDH- $V_{th}$  by the diode connected transistor (N1) where  $V_{th}$  is the threshold voltage of the N-channel transistor. When INPUT is HIGH(VDDL), C2 charged to the voltage of VDDH- $2V_{th}$  by the diode connected transistor (N2 and N3). A falling LOW INPUT and hence OUT rise to (VDDL), would pull the voltage on Q2 down because a capacitor voltage cannot change instantly. When INPUT rise, it would drive the voltage on Q1 with it. The following properties exist after each transition.

• When INPUT = VDDL

$$\diamond Q1 = VDDH - V_{th} + VDDL$$

$$\diamond \ \mathrm{Q2} = VDDH - 2 \cdot V_{th}$$

$$\diamond$$

OUT =  $VDDH - V_{th} + INPUT$

• When INPUT = VSSL

$$\diamond Q1 = VDDH - V_{th}$$

$$\diamond Q2 = VDDH - 2 \cdot V_{th} + VDDL$$

$$\diamond$$

OUT =  $VSSL$

#### **Power Consumption**

The simulated results showed that the power consumption of the proposed and the conventional level shifters were  $29\mu W$  and  $86\mu W$ , respectively. The power consumption of the proposed level shifter could be reduced by about 66% compared to that of the conventional one for an 3.3V input and 10V output operating at 25KHz frequency.

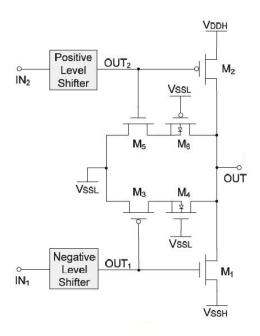

## 3.8 Positive and Negative Level shifter

The output waveform in Figure 2.12 shows that both VDDH and VSSH are positioned higher and lower than the input VDDL and VSSL, respectively.

A possible architecture for achieving both the positive and negative output levels is presented in Figure 3.13 [3]. The schematic combined the two level shifters with the half-bridge stage M1-M2, which drives the output lines with proper current capability. The transfer gate-section M3-M6 has the function of precharging (discharging) the output lines to the intermediate voltage level VSSL when rising (falling) output transitions, this has the purpose of saving power consumption.

FIGURE 3.13: A digital buffer, which combines two level-shifters of opposite polarity [3]

# Chapter 4

# New Architectural Level Shifter

This chapter presents the largest contributions by the author. Three architectural designs are created by the author in the effort of supplying a unipolar driving waveform. The power characterization is included and based on performed simulation and information from previous papers where applicable.

The architectural design is focused on the level shifter, which is a major contributor to achieve unipolar output voltage.

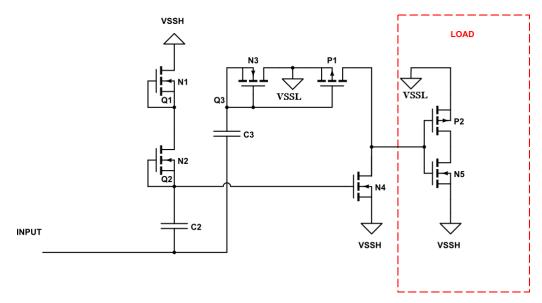

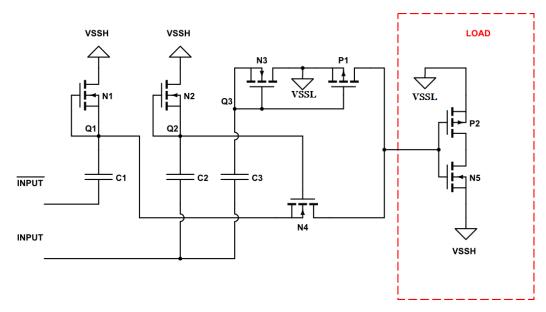

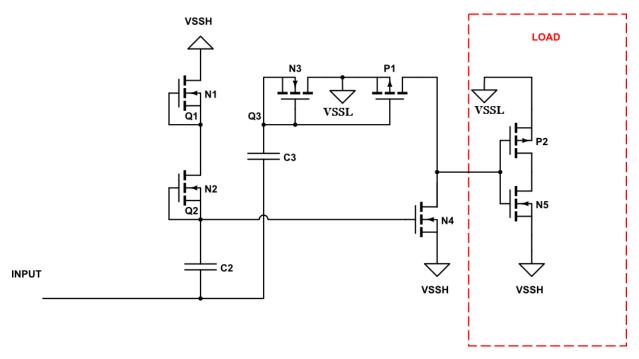

## 4.1 Proposed Negative Capacitor Coupled Level Shifter

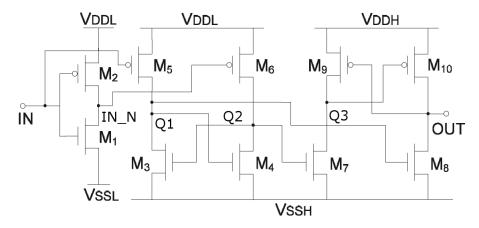

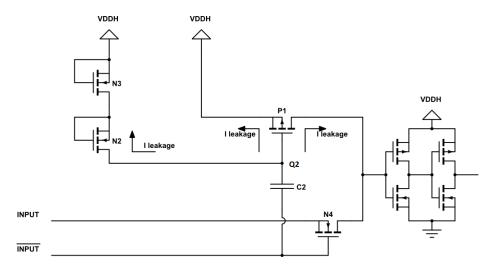

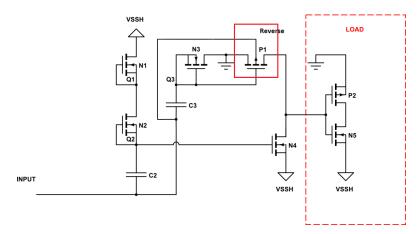

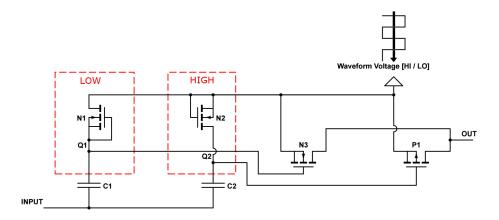

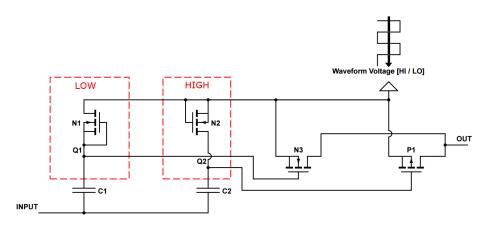

Since the capacitor coupled level shifter presented in Chapter 3.7 does not support negative level output values, the author propose the solution presented in Figure 4.1. The new circuit is based on the same principles as the CCLS. To verify the circuit the design is described in two parts, first the steady state will be described, followed by a description of transient state.

#### 4.1.1 Steady State

#### INPUT = VSSL

When INPUT is LOW (VSSL) then  $\overline{\text{INPUT}}$  will be HIGH (VDDL). Leakage current through transistor P1 and N4 will drive the node Q1, Q2 and Q3 low. When Q1 is higher than VSSH+V<sub>th</sub> the transistor N1 will turn ON and Q1 charges down to VSSH+V<sub>th</sub>. Transistors N2 and N3 work on the same principle as N1, Q2 will reach the voltage VSSH+V<sub>th</sub> and Q3 will not be higher then V<sub>th</sub>. Since Q3 already is VSSL which

FIGURE 4.1: The Author proposes this level shifter to achieve negative levels in the capacitor coupled level shifter.

is lower then  $V_{th}$ , it will be stable at that voltage. The voltage drop of  $V_{GS}(P1)$  is  $Q2 - Q1 = V_{th}$ . The two transistors P1 and N4 display the following properties:

- Transistor P1

- $\diamond V_{GS} \geq V_{th}$

- ♦ P1 stay OFF

- Transistor N4

- $\diamond V_{GS} \leq V_{th}$

- ♦ N4 stay OFF

Because both transistors are OFF the OUTPUT will be floating. To solve this a pull-up resistor could be added to achieve a desired stable state.

#### 4.1.2 Transient State

This circuit will charge the capacitor C1, C2 and C3 with the diode-connected transistors N1, N2, and N3 respectively. INPUT is directly connected to capacitor C2 and C3, while C1 is connected to  $\overline{\text{INPUT}}$ . IF INPUT starts at low, the nodes Q1 and Q2 will be charged to  $VSSH + V_{th}$ . Q3 is unaffected by INPUT until INPUT rises, then the diode-connected transistor N3 will partake to re-stabilize Q3 at  $+V_{th}$ . During the rise event, Q1 will fall down to  $VSSH + V_{th} - VDDL$ , and the voltage is trapped in

node Q1 because N1 will block current in that direction. Simultaneously Q2 will rise to  $VSSH + V_{th} + VDDL$ , N2 will quickly counteract the sudden rise and re-stabilize Q2 back to  $VSSH + V_{th}$ . The voltage difference on N4's gate-source is VDDL and OUTPUT will become Q1.

#### Controlling P1

When the INPUT **falls** once again this will force Q3 down to  $-VDDL+V_{th}$  because the transistor C3 cannot change instantly. The diode connected transistor N3 will block current from ground into the node Q3, and thus Q3 will be pumped down to  $-\|VDDL\|+V_{th}$ . Q3 is applied to the gate of P1, and will control ON/OFF states. When INPUT is **high** (low) P1 will turn OFF (ON).

#### Controlling N4

Q1 and Q2 behave similarly, but because C1 is attached to  $\overline{\text{INPUT}}$  and C2 is attached to INPUT, they will always have opposite states during a period. Q2 is applied to the gate of N4 and will control ON/OFF states. Q1 is applied to the source of N4 and will be connected to the load when INPUT is **high**. When INPUT is **high** (**low**) N4 will turn ON (OFF).

#### Requirements

There are some requirements for this circuit to function correctly.

- (1) INPUT or VDDL must be equal to or higher than  $2V_{th}$ , this can be seen from node Q3 where P1 will not turn completely ON if the threshold voltage is unreached.

- (2) The capacitances of C1, C2, and C3 are responsible for holding the potential on Q1, Q2 and Q3. Eventually the nodes will fall back to steady state because leakage current is always discharging the capacitor. The size of the capacitors will be responsible for the duration a single state can exist.

#### 4.1.3 Power Characterization