# Realization of sigma-delta DAC for audio application on FPGA

Håkon Tobias Jøsok

Master of Science in ElectronicsSubmission date:June 2017Supervisor:Kjetil Svarstad, IESCo-supervisor:Lars Sundell, Nordic Semiconductors

Norwegian University of Science and Technology Department of Electronic Systems

# **Problem Description**

Candidate name: Håkon Tobias Jøsok

Assignment title: Realization of Sigma-Delta DAC for audio application on FPGA

Assignment text: By reducing the analog circuitry at the expense of more digital circuitry, the Sigma-Delta DACs are able to get high dynamic range with only a two level signal on the output. This makes it very suitable for implementation on a FPGA for testing and development. The main goal of this task is to implement a complete solution for a Sigma-Delta DAC for audio application on a FPGA. The task will consist of making an interpolation filter for the proposed Sigma-Delta modulator solution made in an earlier project, and to implement the the complete solution on to a FPGA for testing. If necessary, methods for removing non-linear effects in the Sigma-Delta modulator such as dithering could be tried out to enhance its performance. The final solutions should be compared to a PWM solution.

#### Assignment proposer / Co-supervisor:

Lars Sundell E-mail: lars.sundell@nordicsemi.no

Supervisor: Kjetil Svarstad

### Abstract

Today, data converters are extensively used in embedded systems for a large number of applications. Data converters can have a big impact on power consumption on small embedded systems. Thus, designing data converters with lower power consumption and high performance is an important subject.

In this thesis, a proposed solution for a complete Sigma-Delta (S-D) digital to analog converter (DAC) for audio application is presented. The DAC is implemented on a field programmable gate array (FPGA), and the audio performance of the implementation is tested. A single sided pulse width modulation (PWM) DAC is implemented in register transfer level (RTL) code, and used as a comparison to the S-D DAC implementation. Both the S-D and PWM DAC is synthesized in TSMC's 55-nm technology, and a power estimation on the netlists is performed.

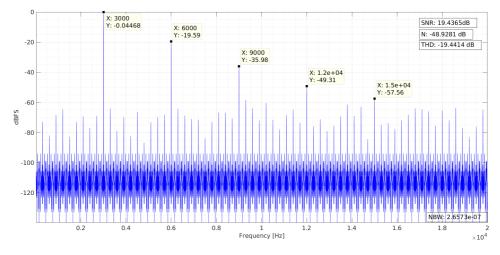

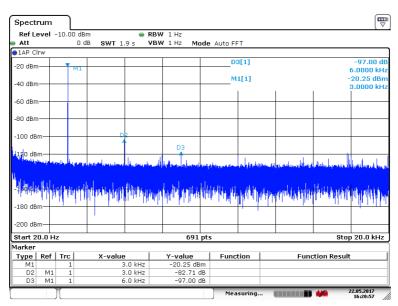

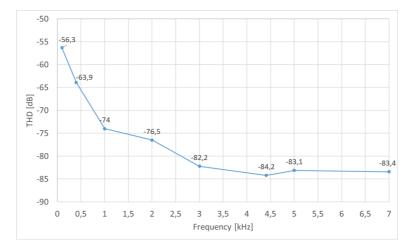

The S-D DAC implementations worked as expected, and successfully played music on an audio system. The performance of the S-D DAC implementation is limited by poor switching characteristics of the digital pad on the FPGA and Intersymbol interference (ISI). A total harmonic distortion (THD) of -82.2dB was measured at 3kHz using 16 bit samples. This is equivalent to an effective number of bits (ENOB) of 13.4 bits. The harmonic distortion varied depending on the input frequency, and increased for the lower frequencies. At 100Hz, a THD of -56.3dB was measured, equivalent to an ENOB of 9.1 bits.

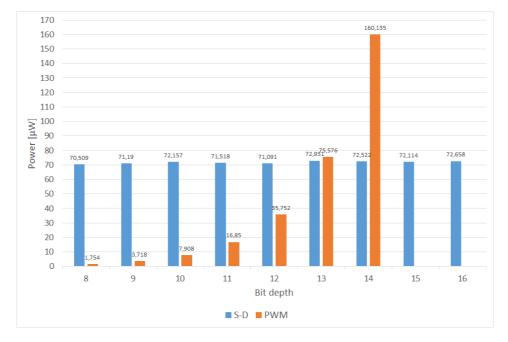

In scenarios where the single sided PWM scheme and the designed S-D DAC are both applicable, the PWM DAC used up to 40 times less power. Suggestions for reducing the S-D DAC's power consumption are presented, which could reduce this power gap. The S-D DAC has a clearly better audio performance than the single sided PWM DAC. In scenarios where both are applicable, the choice is between a good audio performance or a low power consumption.

# Preface

This report is the result of the work with my master thesis, and is written on behalf of Nordic Semiconductors at the Norwegian University of Science and Technology (NTNU), Department of Electronics and Telecommunications.

Starting this project back in August of 2016, as a project assignment, my knowledge of data converters in general, was limited. The learning curve has been steep, but also very educational. The thesis combined theory and practical work, which suited me well. The final result from my work was a working DAC for audio, and it was exciting to actually hear the results from my work.

I want to thank my supervisor Lars Sundell at Nordic Semiconductors, and Kjetil Svarstad from NTNU for the help and guidance with my thesis. I also want to thank Lars Lundheim at NTNU for the help with the digital signal processing (DSP) related work, and Tore Fotland for the proofreading. A special thanks to my girlfriend Mathilde for the support throughout my work with the thesis.

\_\_\_\_\_

# **Table of Contents**

| Pr | oblen                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           | i                                                          |

|----|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Ał | ostrac                   | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | iii                                                        |

| Pr | eface                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | v                                                          |

| Ta | ble of                   | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                              | vii                                                        |

| Li | st of T                  | ables                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | xi                                                         |

| Li | st of H                  | ligures                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xiii                                                       |

| Li | st of A                  | bbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                          | xv                                                         |

| 1  | 1.1<br>1.2<br>1.3<br>1.4 | Deduction         Motivation         The thesis and previous work         Main contributions         Thesis Organization                                                                                                                                                                                                                                                                                                                                              | <b>1</b><br>1<br>2<br>2                                    |

| 2  | <b>Back</b> 2.1          | Acground         DACs in general         2.1.1         Bits and resolution         2.1.2         Sampling rate         2.1.3         Dynamic range         2.1.4         dBFS         2.1.5         Total harmonic distortion (THD)         2.1.6         THD+N         2.1.7         Signal to noise ratio (SNR)         2.1.8         Effective number of bits (ENOB)         2.1.9         DAC settling time         2.1.10         Intersymbol interference (ISI) | <b>3</b><br>3<br>3<br>4<br>4<br>4<br>4<br>4<br>5<br>6<br>6 |

|    | 2.2<br>2.3<br>2.4        | PWM DACs       Sigma-Delta DACs         Sigma-Delta DACs       Sigma-Delta DACs         Implementing interpolation filters for audio Sigma-Delta DACs       Sigma-Delta DACs                                                                                                                                                                                                                                                                                          | 6<br>8<br>8                                                |

|   |      | 2.4.1  | Interpolation filters and specifications             | 9  |

|---|------|--------|------------------------------------------------------|----|

|   |      | 2.4.2  | FIR and IIR filters                                  | 10 |

|   |      | 2.4.3  | Interpolation filter partitioning                    | 11 |

|   |      | 2.4.4  | Interpolation filter structures                      | 12 |

|   |      | 2.4.5  | Half-band filter                                     | 14 |

|   |      | 2.4.6  | Cascaded integrator-comb (CIC) filter                | 16 |

|   |      | 2.4.7  | Coefficient sharing                                  | 17 |

|   |      | 2.4.8  | Finite wordlength effects                            | 18 |

|   |      |        | 2.4.8.1 Fixed-point versus floating-point arithmetic | 19 |

|   |      |        | 2.4.8.2 Quantization of filter coefficients          | 19 |

|   |      |        | 2.4.8.3 Round-off noise                              | 19 |

|   |      |        | 2.4.8.4 Overflow errors                              | 20 |

|   |      | 2.4.9  | Filter implementation strategies                     | 21 |

|   |      |        | 2.4.9.1 Direct implementation                        | 21 |

|   |      |        | 2.4.9.2 MAC implementation                           | 21 |

|   | 2.5  | ZedBo  | ard                                                  | 22 |

|   |      |        |                                                      |    |

| 3 | Desi | 0      | Implementation                                       | 25 |

|   | 3.1  | -      | and implementation of interpolation filter           | 25 |

|   |      | 3.1.1  | Specifications                                       | 25 |

|   |      | 3.1.2  | Implementation                                       | 26 |

|   |      |        | 3.1.2.1 Partitioning                                 | 26 |

|   |      |        | 3.1.2.2 Filter classes                               | 28 |

|   |      |        | 3.1.2.3 Design and testing in Matlab                 | 28 |

|   |      |        | 3.1.2.4 Generating Verilog code                      | 30 |

|   |      |        | 3.1.2.5 RTL optimization                             | 31 |

|   |      | 3.1.3  | Summary of interpolation filter design               | 33 |

|   | 3.2  | Design | and implementation of Sigma-Delta modulator IP       | 33 |

|   |      | 3.2.1  | External interface                                   | 34 |

|   |      | 3.2.2  | Design implementation                                | 35 |

|   |      | 3.2.3  | Testing and verification                             | 35 |

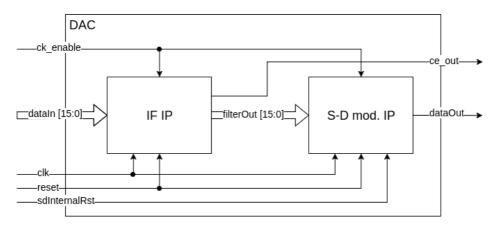

|   | 3.3  | Design | and implementation of DAC IP                         | 36 |

|   |      | 3.3.1  | External interface                                   | 36 |

|   |      | 3.3.2  | Design implementation                                | 36 |

|   |      | 3.3.3  | Testing and verification                             | 37 |

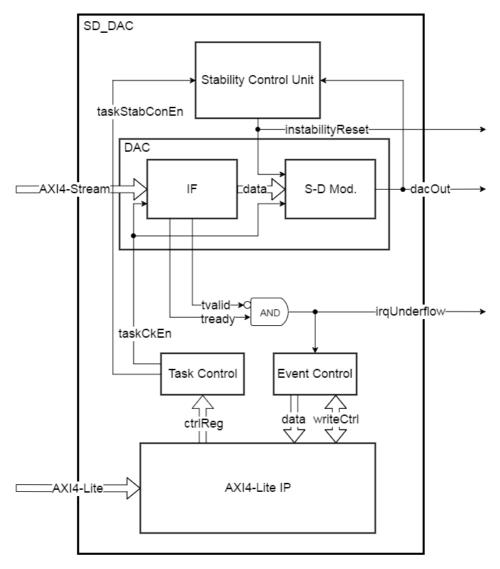

|   | 3.4  | Design | and implementation of Sigma-Delta DAC IP for FPGA    | 38 |

|   |      | 3.4.1  | Specifications                                       | 38 |

|   |      | 3.4.2  | External interface                                   | 39 |

|   |      | 3.4.3  | Design implementation                                | 40 |

|   |      |        | 3.4.3.1 AXI4-Lite IP                                 | 41 |

|   |      |        | 3.4.3.2 Task control IP                              | 41 |

|   |      |        | 3.4.3.3 Event control IP                             | 41 |

|   |      |        | 3.4.3.4 Stability control unit IP                    | 41 |

|   |      |        | 3.4.3.5 DAC IP                                       | 41 |

|   |      | 3.4.4  | Verification                                         | 42 |

|   | 3.5  | Compl  | ete FPGA implementation                              | 42 |

| end                        | ix     |                    |                                            | 73                              |

|----------------------------|--------|--------------------|--------------------------------------------|---------------------------------|

|                            |        |                    |                                            |                                 |

| eren                       | ces    |                    |                                            | 71                              |

| 5.2                        | Future | work               |                                            | 70                              |

|                            |        |                    |                                            | 69                              |

| Conclusion and Future Work |        |                    |                                            |                                 |

|                            |        | 4.2.2.2            | Power consumption comparison               | 65                              |

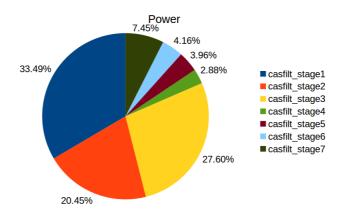

|                            |        | 4.2.2.1            | Sigma-Delta DAC power consumption          | 64                              |

|                            | 4.2.2  |                    | sults                                      | 64                              |

|                            | 4.0.0  | 4.2.1.2            | PWM DAC                                    | 63                              |

|                            |        | 4.2.1.1            | Sigma-Delta DAC                            | 62                              |

|                            | 4.2.1  |                    | ults                                       | 62                              |

| 1.2                        |        | -                  | estimation                                 | 61                              |

|                            | 4.1.3  |                    | sting                                      | 61                              |

|                            | 410    | 4.1.2.4            | Noise performance versus frequency         | 60                              |

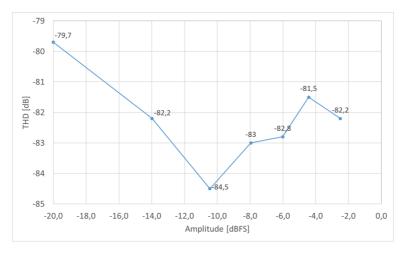

|                            |        | 4.1.2.3            | Noise performance versus amplitude         | 60                              |

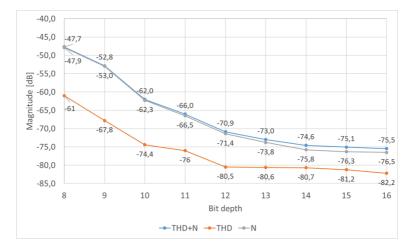

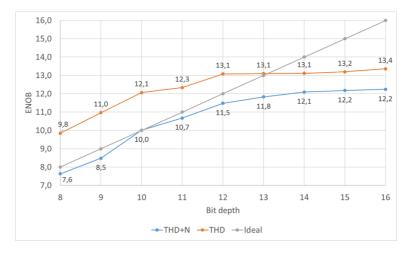

|                            |        | 4.1.2.2            | Noise performance versus bit depth         | 58                              |

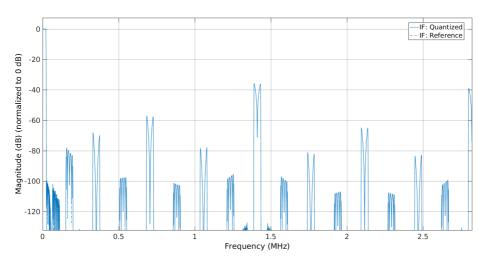

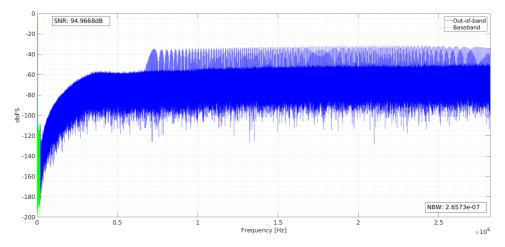

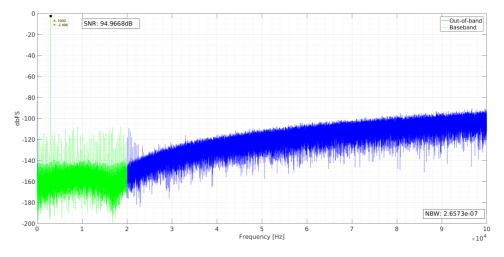

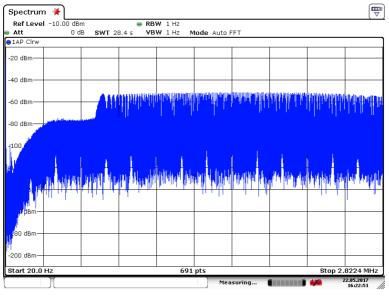

|                            |        | 4.1.2.1            | Sigma-Delta DAC spectrum                   | 56                              |

|                            | 4.1.2  |                    | elta DAC performance                       | 56                              |

|                            | 4.1.1  |                    | formance of the digital pad                | 54                              |

| 1.1                        | -      |                    | C measurements                             | 53                              |

| Resu                       |        | D L D              |                                            | 53                              |

|                            |        |                    |                                            |                                 |

|                            | 3.6.4  |                    | nd verification                            | 50                              |

|                            | 3.6.3  |                    | mplementation                              | 50                              |

|                            | 3.6.2  |                    | interface                                  | 49                              |

|                            | 3.6.1  |                    | ution                                      | 49                              |

| 8.6                        | Design |                    | ementation of PWM test IP                  | 49                              |

|                            | 3.5.4  |                    | nd verification                            | 49                              |

|                            |        | 3.5.3.2            | Main function                              | 47                              |

|                            | 5.5.5  | 3.5.3.1            | S-D DAC driver                             | 47                              |

|                            | 3.5.3  |                    | ng system design                           | 46                              |

|                            |        | 3.5.2.7            | Synthesis and implementation               | 46                              |

|                            |        | 3.5.2.6            | DAC output                                 | 46                              |

|                            |        | 3.5.2.4            | AXI4-Lite bus system       Debugging cores | 45<br>45                        |

|                            |        | 3.5.2.3<br>3.5.2.4 | Data streaming                             | 43<br>45                        |

|                            |        | 3.5.2.2            | Processing system core configuration       | 45<br>45                        |

|                            |        |                    | Clock and reset                            | 43                              |

|                            | 3.5.2  | -                  |                                            | 43                              |

|                            |        | -                  |                                            | 43                              |

|                            |        | 3.5.1<br>3.5.2     | 1                                          | 3.5.2 Programmable logic design |

| B | Detailed Power Estimation Results |                 |    |  |  |  |

|---|-----------------------------------|-----------------|----|--|--|--|

|   | <b>B</b> .1                       | PWM DAC         | 79 |  |  |  |

|   | B.2                               | Sigma-Delta DAC | 80 |  |  |  |

# **List of Tables**

| 3.1  | Summary of IF specifications                                                  | 26 |

|------|-------------------------------------------------------------------------------|----|

| 3.2  | Input sample rate, passband, transition-band, and stopband for each IF stage. | 26 |

| 3.3  | Stopband attenuation summary                                                  | 27 |

| 3.4  | Summary of the final IF configuration                                         | 28 |

| 3.5  | Quantized coefficients                                                        | 29 |

| 3.6  | Output wordlength of each filter stage                                        | 29 |

| 3.7  | IF filter resource utilization on Zedboard                                    | 31 |

| 3.8  | IF filter resource utilization on Zedboard after RTL optimization             | 33 |

| 3.9  | Summary of the implemented IF                                                 | 33 |

| 3.10 | Generic interface of the S-D modulator IP                                     | 34 |

| 3.11 | Signal interface of the S-D modulator IP                                      | 34 |

| 3.12 | Signal interface of the DAC IP                                                | 36 |

| 3.13 | Singal interface                                                              | 39 |

| 3.14 | Register interface                                                            | 39 |

|      | Post implementation utilization                                               | 46 |

| 3.16 | Generic interface PWM IP                                                      | 49 |

| 3.17 | Singal interface PWM IP                                                       | 50 |

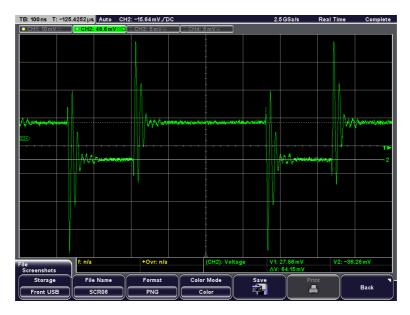

| 4.1  | Measurements of DAC output in time domain                                     | 55 |

| 4.2  | DAC IP area results                                                           | 62 |

| 4.3  | PWM IP area result                                                            | 63 |

| 4.4  | DAC IP power estimation with 16 bit samples                                   | 64 |

| 4.5  | Bit depth versus clock rate for PWM IP                                        | 66 |

| B.1  | PWM DAC IP power estimations                                                  | 79 |

| B.2  | S-D DAC IP power estimation with 8 bit samples                                | 80 |

| B.3  | S-D DAC IP power estimation with 9 bit samples                                | 80 |

| B.4  | S-D DAC IP power estimation with 10 bit samples                               | 81 |

| B.5  | S-D DAC IP power estimation with 11 bit samples                               | 81 |

| B.6  | S-D DAC IP power estimation with 12 bit samples                               | 81 |

| B.7  | S-D DAC IP power estimation with 13 bit samples                               | 82 |

| B.8  | S-D DAC IP power estimation with 14 bit samples                               | 82 |

| B.9  | S-D DAC IP power estimation with 15 bit samples                               | 82 |

|      | S-D DAC IP power estimation with 16 bit samples                               | 83 |

|      |                                                                               |    |

# **List of Figures**

|                                                                              | 5      |

|------------------------------------------------------------------------------|--------|

| 2.2 Glitch area measurement, from [1]                                        | 6      |

| 2.3 Block diagram of a <i>N</i> -bit PWM DAC                                 | 6      |

| 2.4 Sawtooth wave and PWM output                                             | 7      |

| 2.5 Block diagram of S-D DAC                                                 | 8      |

| 2.6 The process of oversampling in the time and frequency domain, from [     | 2]. 9  |

| 2.7 Interpolation with cascade filters, adapted from [2]                     | 12     |

| 2.8 FIR filter direct-form structure, adapted from [2]                       | 12     |

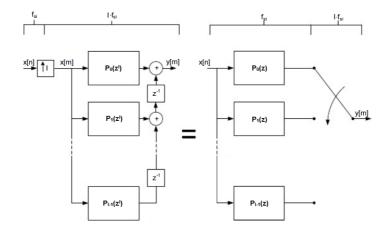

| 2.9 General polyphase FIR-filter structure and its transpose, adapted from   | [2] 13 |

| 2.10 The multirate identity for an upsampling system                         | 13     |

| 2.11 Efficient realization of the polyphase IF, adapted from [2]             | 14     |

| 2.12 Frequency response of half-band filter, from [3]                        | 15     |

| 2.13 Impulse response of half-band filter with an order $M = 18$ , from [3]. | 15     |

| 2.14 CIC IF, adapted from [4]                                                |        |

| 2.15 CIC filter, compensation FIR filter, and the composite filter frequency | re-    |

| sponse.                                                                      |        |

| 2.16 Symmetrical FIR filter with coefficient sharing, from [2]               |        |

| 2.17 Linear noise model of qutanzation process in FIR filter, adapted from [ | 3]. 20 |

| 2.18 Direct implementation of FIR filter, from [2]                           |        |

| 2.19 MAC implementation of FIR filter, from [2]                              | 22     |

| 2.20 Xilinx Zynq-7000 SoC overview, from [5]                                 | 23     |

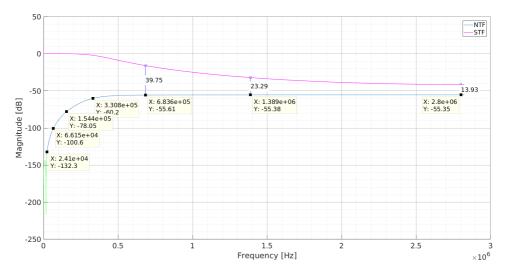

| 3.1 NTF and STF of S-D modulator, with the stopband edge of each fil         | lter   |

| marked.                                                                      |        |

| 3.2 Frequency response of the final IF                                       |        |

| 3.3 Passband ripple for final IF                                             |        |

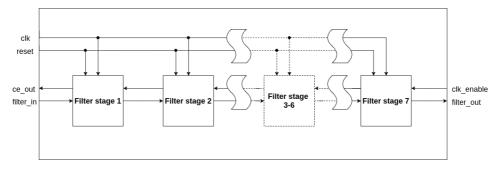

| 3.4 Block diagram of IF top module                                           | 30     |

| 3.5 Signal interface of the filter stages                                    |        |

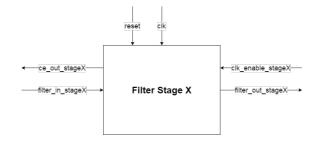

| 3.6 C code of S-D modulator from [6]                                         |        |

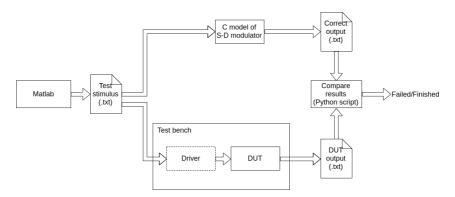

| 3.7 Testing environment for S-D modulator IP                                 |        |

|                                                                              | 37     |

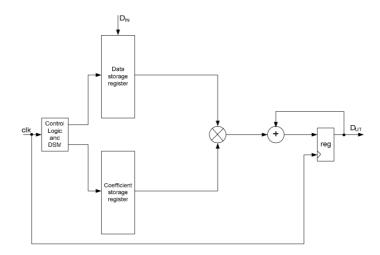

| 3.8 Block diagram of DAC IP                                                  |        |

| 8                                                                            | 37     |

|                                                                              |        |

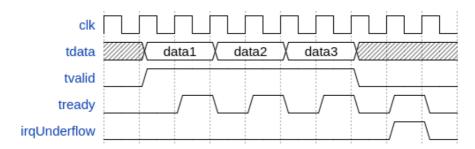

| 3.12 | Timing diagram of AXI4-Stream transaction and interrupt generation | 42 |

|------|--------------------------------------------------------------------|----|

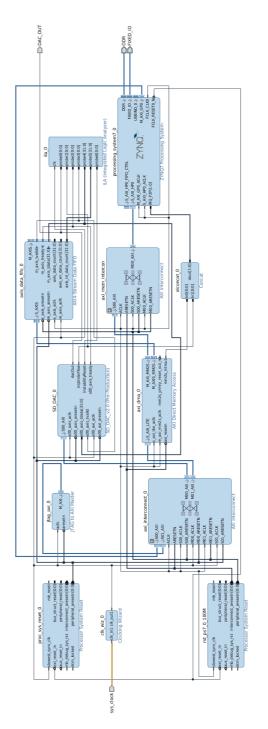

| 3.13 | Block diagram of the complete PL implementation                    | 44 |

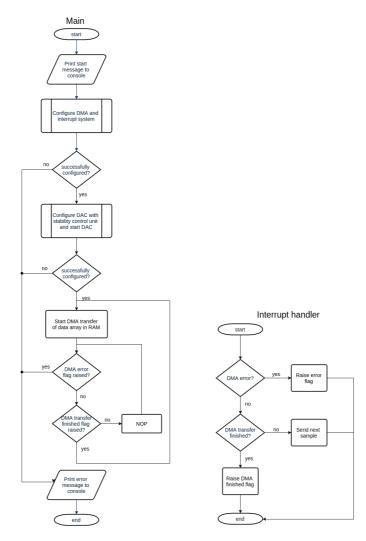

| 3.14 | Flowchart of main function and interrupt handler                   | 48 |

| 3.15 | Ideal spectrum of the PWM IP with a 3kHz sine wave                 | 51 |

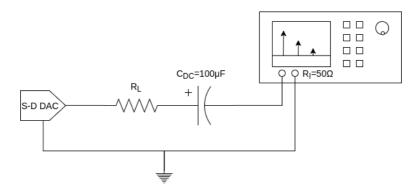

| 4.1  | Measurement setup                                                  | 53 |

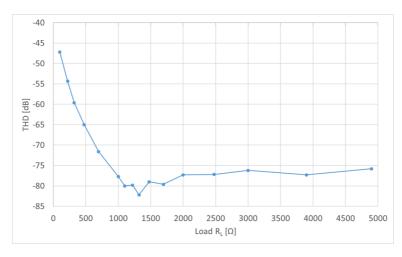

| 4.2  | THD versus output load                                             | 54 |

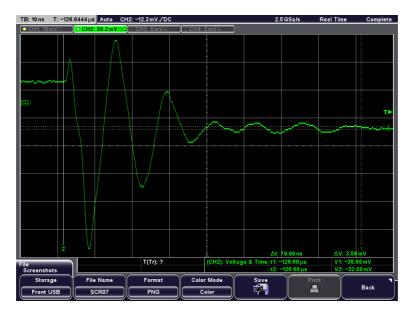

| 4.3  | Snapshot of DAC output in the time domain                          | 55 |

| 4.4  | Meassurement of DAC settling time                                  | 56 |

| 4.5  | Measured spectrum of S-D DAC                                       | 57 |

| 4.6  | Measured baseband spectrum of S-D DAC                              | 57 |

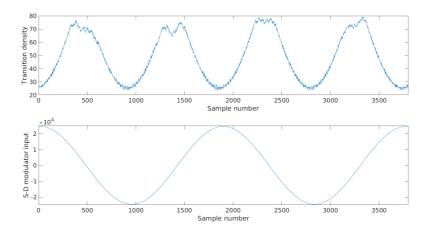

| 4.7  | Transition density and input of S-D modulator                      | 58 |

| 4.8  | THD, N and THD+N versus bitdepth                                   | 59 |

| 4.9  | ENOB versus bitdepth                                               | 59 |

| 4.10 | THD versus amplitude                                               | 60 |

| 4.11 | THD versus frequency                                               | 61 |

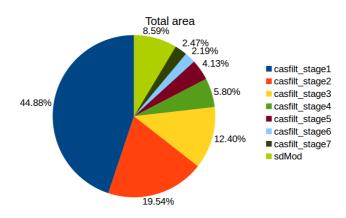

| 4.12 | Total area usage of DAC IP                                         | 63 |

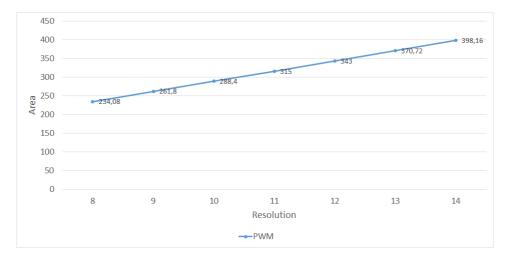

| 4.13 | Area usage versus bit depth for PWM DAC                            | 64 |

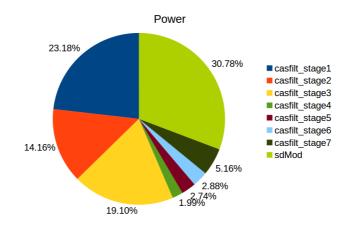

| 4.14 | S-D DAC power consumption with 16 bit samples                      | 65 |

|      | IF power usage with 16 bit samples                                 | 66 |

|      | Power consumption versus bit depth for DAC and PWM IP              | 67 |

# **List of Abbreviations**

AMBA Advanced Microcontroller Bus Architecture ASIC Application-Specific Integrated Circuit AUX Auxiliary Port CD-DA Compact Disc Digital Audio CIC Cascaded Integrator-Comb CMOS Complementary Metal-Oxide-Semiconductor **D-F** Direct-Form DAC Digital to Analog Converter dBFS Decibels relative to Fulls Scale **DDR3** Double Data Rate type three **DMA** Direct Memory Access **DR** Dynamic Range **DSP** Digital Signal Processing **DUT** Device Under Test **ENOB** Effective Number Of Bits FF Flip Flop FFT Fast Fourier Transform FIFO First In First Out FIR Finite Impulse Response FLAC Free Lossless Audio Codec **FPGA** Field Programmable Gate Array

- GPIO General-Purpose Input/Output

- HDL Hardware Description Language

- **IF** Interpolation Filter

- **IIR** Infinite Impulse Response

- ILA Integrated Logic Analyzer

- **IP** Intellectual Property

- **ISI** Intersymbol Interference

- JTAG Joint Test Action Group

- LPF Low Pass Filter

- LUT Look Up Table

- MAC Multiplier-Accumulator

- NTF Noise Transfer Function

- NTNU Norwegian University of Science and Technology

- **OS** Operating System

- **OSR** Oversampling Ratio

- PC Personal Computer

- PL Programmable Logic

- **PS** Processing System

- **PSD** Power Spectral Density

- PWM Pulse Width Modulation

- QSPI Quad Serial Peripheral Interface

- **RMS** Root Mean Square

- **ROM** Read-Only Memory

- **RTL** Register Transfer Level

- S-D Sigma-Delta

- SDK Software Development Kit

- SNR Signal to Noise Ratio

- SoC System on Chip

- STF Signal Transfer Function

- THD Total Harmonic Distortion

# Chapter 1 Introduction

### **1.1 Motivation**

Because of the vast use of battery-powered embedded systems, it has become essential to make energy efficient designs. Embedded systems are used in a wide range of applications, including ones that can require a cross between the digital and analog domain. This requires efficient data converts which are suited for the specific task. An example of this is audio generation on a microcontroller. Which usually requires a digital to analog converter (DAC) with high dynamic range (DR) and low power consumption, a feature which can be difficult to achieve.

Two types of DAC's which can be used in microcontrollers are the pulse width modulation (PWM) and sigma-delta (S-D) DAC's. The S-D DAC is widely used today because of its reduced analog circuitry compared to conventional Nyquist-rate DACs. The analog circuitry is the most critical part of the DAC, and can easily limit the performance of the DAC [7]. The S-D DAC uses less analog circuitry at the cost of more digital logic. Using the concepts of oversampling and noise shaping, the S-D DAC is able to achieve high DR using only a 1-bit internal DAC. The most essential part of the S-D DAC is the S-D modulator, which performs the noise shaping. The design of the S-D modulator is crucial, since it impacts the overall complexity and power consumption of the S-D DAC.

The PWM DAC works by generating square pulses on its output, where the average *on* time of the square pulse represent the desired voltage level. The PWM DAC is easy to implement on a microcontroller using a simple binary counter, but this implementation can have severe harmonic distortion and is not suited for high end audio conversion.

### **1.2** The thesis and previous work

In this thesis a S-D DAC is implemented on a field programmable gate array (FPGA) to test what audio performance can be achieved. The S-D DAC solution will also be compared to a PWM DAC solution in terms of power and audio performance.

In the previous work [6], a S-D modulator was designed and implemented in C code. The modulator was designed with the compact disc digital audio (CD-DA) format as a standard for the performance goal. The S-D modulator is therefore designed for 16 bit samples with a sample rate of 44.1kHz. The C model was extensively simulated for a large range of frequencies and amplitudes. The results from the simulations showed that the modulator remained stable for inputs lower then -2.5 decibels relative to fulls scale (dBFS), and had a DR> 96dB.

This thesis uses the modulator designed in [6], and proposes a solution for a complete S-D DAC implementation on a FPGA. The design process in this thesis uses an iterative design method.

### **1.3 Main contributions**

- 1. Designed an interpolation filter (IF) with an oversampling ratio (OSR) of 128, which is compatible with the CD-DA format, and implemented the IF in register transfer level (RTL) code.

- 2. Implemented the S-D modulator from [6] in RTL code, and connected the S-D modulator to the IF.

- 3. Designed and implemented a S-D DAC intellectual property (IP) for a FPGA implementation, with a control register and a data streaming interface compatible with the advanced microcontroller bus architecture (AMBA) AXI4 bus system.

- 4. Implemented the S-D DAC IP on a Zynq-7000 system on chip (SoC), and measured the audio performance of the implementation with a spectrum analyzer.

- 5. Compared the performance, area and power consumption of the S-D DAC solution to a PWM DAC solution.

### **1.4 Thesis Organization**

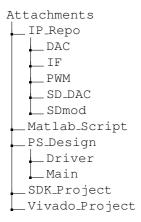

Chapter 1 presents the motivation, this thesis and previous work, the main contributions, and the thesis organization. Chapter 2 presents the background on DAC's in general, PWM DAC's, S-D DAC's, IF design and a overview of the ZedBoard. Chapter 3 describes the design flow for implementing the complete S-D DAC solution on the FPGA, and the design of a PWM DAC used for testing. Chapter 4 presents the measurements of the S-D DAC implementations, and the results from the power estimations of the S-D DAC and the PWM DAC. In chapter 5, the conclusions and future work is presented. Appendix A lists the source code attached to this work, and appendix B shows the detailed reports from the power estimations.

### Chapter 2

# Background

### 2.1 DACs in general

General DAC theory will be explained in the next subsections.

#### 2.1.1 Bits and resolution

DACs are generally specified by the N bits on the input, also called the resolution of the DAC. The bits on the input represent the number of voltage levels which the DAC can generate. A N-bit DAC can generate  $2^N$  voltage levels ranging from zero to its full scale value  $V_{FS}$  [7]. The resolution of the DAC is sometimes defined as the smallest analog value the DAC can generate, but in this thesis it is defined as the number of bits on the DAC input.

#### 2.1.2 Sampling rate

The Nyquist criteria for sampling say that the sampling frequency  $f_s$  must be minimum twice the signal frequency  $f_B$  to avoid aliasing [1]. This criteria limits the signal bandwidth to  $f_B = f_s/2$  for a DAC, where  $f_s$  represent the maximum sample rate where the DAC can generate the correct value on its output.

A signal is oversampled if it is sampled with a higher frequency then the Nyquist frequency  $f_N = 2 \cdot f_B$ , given by the Nyquist criteria. How much the signal is oversampled can be specified by the oversampling ratio (OSR). The OSR is the ratio between the sample frequency  $f_s$  and the Nyquist frequency  $f_N$ , and is defined in equation (2.1).

$$OSR = \frac{f_s}{f_N} = \frac{f_s}{2f_B}$$

(2.1)

#### 2.1.3 Dynamic range

The DR of a DAC is the ration between the largest and smallest signal it can generate. A N-bit DAC has a theoretical DR given by equation (2.2) [8].

$$DR = 6.02N + 1.76 \,[dB] \tag{2.2}$$

In practice the theoretical DR in equation 2.2 is not achievable, due to nonlinearities and semiconductor noise sources in the DAC [8].

#### 2.1.4 dBFS

dBFS is a unit measurement used in digital signal processing (DSP) for amplitudes. Zero dBFS is at the full scale or maximum amplitude of the signal, and smaller amplitudes are negative values.

#### 2.1.5 Total harmonic distortion (THD)

Total harmonic distortion (THD) is the ratio between the root mean square (RMS) value of the fundamental signal, and the RMS sum of all its harmonic components. In practice only the first 5 harmonics are included in the measurement since the rest of the harmonics have minor contributions to the result [1]. THD is defined in equation (2.3).

$$THD = \frac{\sum_{\infty}^{n=2} \text{harmonics}}{\text{fundamnetal}}$$

(2.3)

#### 2.1.6 THD+N

THD plus noise is the ratio between the RMS value of the fundamental signal and the RMS sum of all its harmonic and noise components. THD+N is defined in equation (2.4).

$$THD + N = \frac{\sum_{\infty}^{n=2} \text{harmonics} + \text{noise}}{\text{fundamnetal}}$$

(2.4)

#### 2.1.7 Signal to noise ratio (SNR)

Signal to noise ratio (SNR) is defined as the ration between the RMS value of the signal, and the total RMS noise in baseband. If the THD+N is measured in baseband the SNR can be defined as equation (2.5).

$$SNR = \frac{\text{fundamnetal}}{\sum_{\infty}^{n=2} \text{harmonics} + \text{noise}}$$

(2.5)

#### **2.1.8** Effective number of bits (ENOB)

Effective number of bits (ENOB) is a way of expressing the SNR of a DAC in terms of bits. The theoretical limit for DR expressed in equation (2.2) is also the theoretical limit

for the SNR of the DAC. Solving equation (2.2) for N, and replacing N with ENOB and DR with SNR gives the following expression, represented by equation (2.6).

$$ENOB = \frac{SNR - 1.76}{6.02}$$

(2.6)

#### 2.1.9 DAC settling time

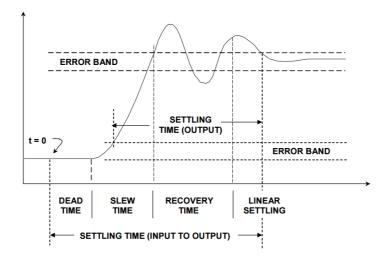

The input to output settling time is defined as the time between the digital input code changes, to the output is stable in a defined error band [1]. In figure 2.1 a DAC transition is shown where the four periods of the settling time is characterized.

Figure 2.1: Settling time for DAC, from [1]

The first period is the *dead time*. Here the digital logic is switching but there is no change on the output. The second period is the *slew time*, where the rate of change on the output is limited by the DAC's slew rate. The third period is the *recovery time*. In this period the DAC is recovering from its fast slew rate, and may overshoot and/or undershoot. The fourth period is the *linear settling time*, where output converges to its final value defined within an error band [1].

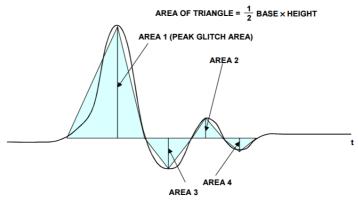

Ideally, the transition of the DAC from one value to another should happen monotonically, but in practice it will overshoot and/or undershoot during the settling time [1]. This uncontrolled movement on the output, when the DAC is transitioning, is called a glitch. Glitches is often characterized by the glitch impulse area, which is the net area of the glitch [1]. A measurement of the glitch area is show in figure 2.2.

As can be seen in figure 2.2, the net glitch area can cancel out when the glitch has equal amount of under- and overshoot.

NET GLITCH IMPULSE AREA ≈ AREA 1 + AREA 2 - AREA 3 - AREA 4

Figure 2.2: Glitch area measurement, from [1]

#### 2.1.10 Intersymbol interference (ISI)

Intersymbol interference (ISI) is the error produced by the non-idealities when the DAC is transitioning. This can be caused by asymmetric switching, clock skew and capacitive memory effects [9]. A ISI error is dependent on the value of the previous symbol, since two consecutive equal symbols will not produce the switching non-idealities. A ISI error sequence is therefore dependent on the switching pattern of the DAC, and is nonlinear quantity [9]. ISI is a major source of distortion for S-D DAC [9].

### 2.2 PWM DACs

The PWM DAC is a type of a DAC where the idea is to modulate a stream of square pulses, and filter them in an analog low pass filter (LPF). Each square pulse has a time period  $T_s$  where the square pulse can either be on or off. The time period  $T_s$  is given by the sample rate of the input signal, and is equal to  $T_s = 1/f_s$ . The average time the square pulse is on in the time period  $T_s$ , is called a duty cycle. The duty cycle is decided by the digital input code. The pulse stream is filtered with a LPF to remove noise in the out-of-band frequencies, and to smoothen out the square pulses. Figure 2.3 show a block diagram of a PWM DAC where the N bit digital input code is called DAC<sub>IN</sub>.

Figure 2.3: Block diagram of a N-bit PWM DAC

There are several differrent PWM schemes, but in this thesis only the single sided PWM scheme will be used. The single sided PWM scheme is the simplest scheme to

implement, but also the one with the worst harmonic distortion [10]. There are ways of reducing the harmonic distortion with signal processing algorithms called predistortion, but these are not explored in this thesis.

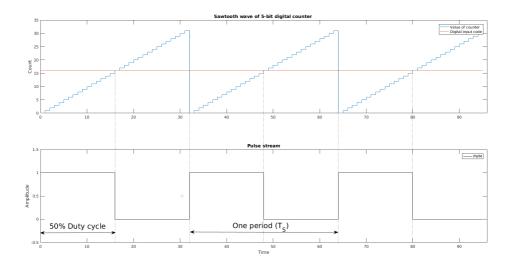

The single sided PWM scheme can be implemented by comparing a sawtooth wave from a simple binary counter to the digital input code. An example of this implementations, using a 5-bit binary counter, is shown in figure 2.4. The sawtooth wave from the binary counter is shown in the top plot, with a red line representing the value of input data code. The lower plot in figure 2.4 is the pulse stream out of the PWM block in figure 2.3. The x-axis of both the plots in figure 2.4 is time, with one integer step equal to a period of the binary counter's clock,  $T_c = \frac{1}{f_c}$ . In this example the period  $T_s$  of the PWM block is equal to the time the 5-bit counter uses to reach its max value. Thus, one period is equal to  $T_s = 2^5 T_c$ . In this example the digital input code is equal to 16, and represents a duty cycle of 50%, as shown in figure 2.4.

Figure 2.4: Sawtooth wave and PWM output

When a binary counter is used to implement the singled sided PWM scheme, the counter's clock frequency will limit what bit depth and signal bandwidth which is possible for the PWM DAC. The relationship between the sampling frequency  $f_s$ , bit depth N and the frequency of the counter clock  $f_c$  is shown in equation (2.7).

$$f_c = f_s \cdot 2^N \tag{2.7}$$

The clock frequency of the digital counter doubles for every extra bit of bit depth, and is also linearly dependent on the sampling frequency. Because of this property, the PWM DACs are in practice not capable of generating high end audio due to the extreme clock rate and switching capacities needed [10].

### 2.3 Sigma-Delta DACs

The most critical part of a DAC is the analog circuitry. The analog circuitry can limit the resolution and speed of the DAC because of component mismatch and nonlinearities, drift and aging, and parasitics to mention a few [7]. The S-D DACs uses less analog circuitry at the expense of more digital circuitry compared to the Nyquist rate DACs. This is done using the concepts of oversampling and noise shaping.

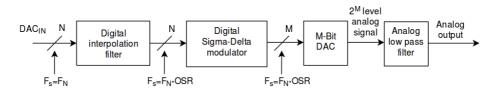

In figure 2.5 a block diagram of a S-D DAC is shown. The digital parts of the S-D DAC are the IF and the digital S-D modulator, while the analog parts are the *M*-bit internal DAC, and the analog LPF.

Figure 2.5: Block diagram of S-D DAC

The first block in figure 2.5 is the IF. The IF's task is to raise the sampling frequency from  $F_S$  to  $F_S \cdot OSR$ , and suppress the spectral replicas. The digital S-D modulator in the next block quantizes the N-bit word on its input, to usually 1-6 bits on its output [11]. This produces high amounts of quantization noise, which the S-D modulator filters out of baseband and up to the out-of-band frequency. This is done without significantly affecting the baseband spectrum in the process, and the whole process is called noise shaping. The S-D modulator can become unstable, and the input magnitude must be limited to a stable input range to avoid this [11]. This usually a few dB under the full-scale range of the S-D modulator [11]. The next block in figure 2.5 is the internal DAC. The internal DAC is usually 1-6 bits, depending on the output of digital S-D modulator in the previous block. If a 1-bit DAC is used, its output is a two level analog signal and the DAC will be a very simple structure. The last block in figure 2.5 is the analog LPF. The LPF's task is to remove all the out-of-band noise produced by the S-D modulator, without affecting the baseband signal in the process. Ideally the spectrum on the output of the LPF is the same as the input to the S-D DAC, without added noise or distortion.

### 2.4 Implementing interpolation filters for audio Sigma-Delta DACs

The IF is an essential part of the S-D DAC and can have a big impact on the overall power consumption and performance of the DAC. The design space for a IF is large with many methods for improving the efficiency of the design. The next sections will go through background for the most common design and implementation strategies for IFs.

#### 2.4.1 Interpolation filters and specifications

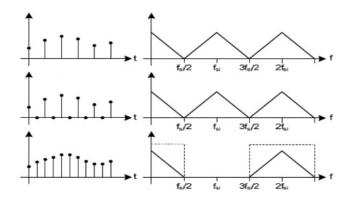

Oversampling of a discrete-time signal by an integer factor I consists in principle of two processes. The first process raises the sampling frequency  $f_{si}$  by the integer factor I to  $f_{so} = f_{si} \cdot I$ . This is done by inserting (I - 1) zeros between the existing signal samples, and is called zero-stuffing. The second process suppresses the spectral replicas which is centered at  $k \cdot f_{si}$ , where k = [1..(I - 1)] [11]. This is done by filtering the signal with a digital LPF. The two processes are combined using an IF. The oversampling process with a factor of I = 2 is shown in figure 2.6. The original signal is at the top, the zero-stuffed signal is in the middle, and the final filtered signal, with the digital LPF's frequency response stippled, at the bottom.

Figure 2.6: The process of oversampling in the time and frequency domain, from [2]

Oversampling is a lossless process, and ideally the output signal only contains the spectral content of the input signal. The frequency response of an ideal IF is categorised by equation (2.8) [2]:

$$H_{\rm IF}(f) = \begin{cases} 1, & 0 < f < \frac{f_{si}}{2} \\ 0, & \frac{f_{si}}{2} \le f < \frac{I \cdot f_{si}}{2} \end{cases}$$

(2.8)

This frequency response gives an impulse response equal to equation (2.9) [2]:

$$h_{\text{IF}}[n] = \operatorname{sinc}\left[\frac{n}{I}\right] \quad , n \in \langle -\infty, \infty \rangle$$

(2.9)

This impulse response is infinite and non causal, and is not realizable for a real filter. The frequency specter of a real IF will therefore deviate from its ideal counterpart. These deviations are noticeable in the transition width, passband ripple, and stopband attenuation of the filter [2]. Depending on the IF's application, specifications must be set which describe the amount of deviation which is allowed for the particular IF.

The specification for a typical IF used in a S-D DAC are somewhat diffuse. The S-D DAC will not have subsequent sampling, which will lead to aliasing of the spectral replicas into baseband. Therefore, the LPF after the zero-stuffing could theoretically be omitted

[2]. The large content of high-frequency energy would however have a negative impact on the performance of the S-D DAC, by saturating the S-D modulator, and by making the internal DAC very jitter sensitive [2]. The amount of high-frequency energy the S-D modulator tolerates on its input, depends on the modulator design. The S-D modulator produce a high amount of high-frequency energy on its output, and if the spectral images are attenuated under the noise floor of the modulator, they will not affect the internal DAC and analog LPF [2]. The required attenuation of the spectral replicas at the higher frequencies are therefore reduced, and can be exploited to make more efficient IFs.

The CD-DA format, which was used as a performance goal in the design of the S-D modulator in [6], uses a sample rate of 44.1kHz. The passband for this format is defined to be at the presumable audible limit at 20kHz, and the stopband usually is defined from 24.1kHz [2].

The passband ripple should be under the audible limit, and for a typical high-end converter this usually ranges from 0.001dB to 0.0001dB [2]. The requirements for the stopband attenuation are as mentioned a little diffuse for IFs used in S-D DACs, but for a typical high-end converter it usually ranges from 75dB to 120dB [2].

#### 2.4.2 FIR and IIR filters

When designing an IF one the first things to consider is if the LPF should be a finite impulse response (FIR) filter, or a infinite impulse response (IIR) filter. The FIR filter is a filter with a finite duration impulse response, and the output of the filter is only dependent on previous input values [12]. The output of a  $N^{\text{th}}$  order FIR filter with a impulse response h[n], and a arbitrary input sequence x[n] is equal to the convolution sum of the two. The convolution sum for a FIR filter is shown in equation (2.10) [12]. The  $b_m$  in equation (2.10) is the  $m^{\text{th}}$  coefficient of the filter, and determines the locations of the FIR filters zeros in the z-domain.

$$y[n] = h[n] * x[n] = \sum_{m=0}^{N} b_m x[n-m]$$

(2.10)

The IIR filter has in contrast to the FIR filter an infinite duration impulse response, and the output of the filter is dependent on both previous input and output values. The output response of a IIR filter with a impulse response h[n], and an arbitrary input sequence x[n] is a convolution of the two. This convulsion is shown in equation (2.11) [3]. The  $b_m$  in equation (2.11) is the coefficient which determines the zeros of the IIR filter in the z-domain. The  $a_k$  in equation (2.11) is the  $k^{\text{th}}$  feedback coefficient of the filter, and determines the locations of the IIR filter poles in z-domain.

$$y[n] = h[n] * x[n] = \sum_{m=0}^{N} b_m x[n-m] - \sum_{k=1}^{M} a_k x[n-k]$$

(2.11)

Since the FIR filter output is only dependent on previous input values, all FIR filters with bounded coefficients will be bounded-input bounded-output (BIBO) stable [12]. The IIR filter is not necessarily BIBO stable. To ensure that an IIR filter is BIBO stable, the poles of the filter must be inside the unit circle.

An important characteristic of the FIR filter is the ability to precisely manage the phase response of the filter. This attribute is often used to make a linear phase response, which gives a perfectly flat group delay [12]. This means that the waveform of the signal is preserved in the filtering process, which is important when filters are used in applications like audio where frequency dependent propagation delay cannot be tolerated [2]. The IIR filter in comparison cannot easily manage the phase response, and can only approximate linear phase characteristics.

FIR filters are most commonly used in S-D DAC's, since they easily can be designed with linear phase response, in addition to the fact that the hardware can be clocked at the input frequency of the IF [11]. The IIR has the advantage over FIR filters in that they can have a higher stopband attenuation with a lower hardware complexity. Regardless of this, they are not commonly used for S-D DAC's [11]. The S-D DAC designed in this thesis is for an audio application. Since filters with a constant group delay is desired for audio DACs [2], the linear phase FIR filter will be used in this paper.

#### 2.4.3 Interpolation filter partitioning

When implementing an IF with a large interpolation factor I, the IF can in principle raise the sampling frequency to  $f_{so} = f_{si} \cdot I$  in one step, but this will not be an efficient implementation. When the interpolation factor I is large, the passband and transition band of the filter will become very small. This will require a long FIR filter with a large number of computations, since the FIR filters increase in order with the inverse of the transition band [3]. This would also require all the digital circuitry of the FIR filter to function at this high clock rate, and thereby dissipate an unnecessarily large amount of power [11].

The sampling frequency is usually raised in multiple stages, where most of the computations is done at lower sampling frequencies [11]. This can be done by cascading interpolation filters with low interpolation factors, which together raise the sampling frequency to the desired interpolation factor I. An example of multistage filtering is shown in figure 2.7 with three IFs, each with an interpolation factor of  $I_i = 2$ , which cascaded together gives an interpolation factor of I = 8.

The first filter in a multistage IF has the most demanding requirements, because of the small transition band needed to remove the adjacent spectrum image, which can be very close to the passband [11]. For each subsequent filter, the transition band will increase since the spectral replicas will be further and further apart [2].

For an IF in a S-D DAC, the required attenuation of the spectral replicas is highest for the first filter, and is relaxed for each subsequent filter as discussed in section 2.4.1. The requirements for short transition band and high attenuation, causes the first filter to become the most computational heavy filter, but it is also the filter with the lowest clock rate. Each subsequent filter is less computational heavy as the clock rate increases. This reduces the number of computations compared to a single stage IF, and causes most of the computations to be done at a the lower clock rates, which reduces the power consumption of the digital logic.

Figure 2.7: Interpolation with cascade filters, adapted from [2]

#### 2.4.4 Interpolation filter structures

Every practical realizable digital filter can be described by a set of difference equations. These difference equations can be used to realize the filter into a filter structure. The filter structure is basically a pictorial block diagram of the difference equations represented by adders, multipliers and delays [3].

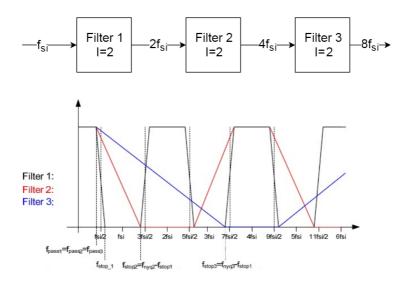

The convolution sum in equation (2.10) is the difference equation of the FIR filter, and can be directly realized into an filter structure [2]. This filter structure is called the direct-form structure. The direct-form structure is shown in figure 2.8 with a zero-stuffing block at the beginning of the filter, implying that filter is part of an IF with an oversampling factor *I*.

Figure 2.8: FIR filter direct-form structure, adapted from [2]

However, the direct-form structure is not an efficient implementation of an IF. The direct-form requires N multiplications for every output sample for a filter with length N, but only the  $I^{th}$  sample in the delay pipeline in figure 2.8 will be nonzero at any given time because of the zero-stuffing. This means there will be many redundant multiplications for every output sample, when the direct-form structure is used in a IF [2].

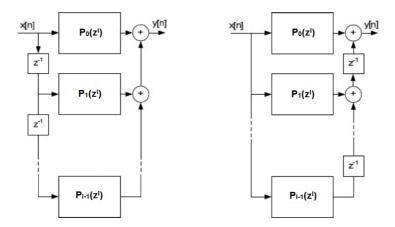

The polyphase structure is widely used to simplify the implementations of IFs, and uses the fact that only the  $I^{th}$  sample in the filter will be nonzero to its advantage [3]. The polyphase decomposition groups the impulse response of the IF into I subfilters of length M, where I is the interpolation factor of the IF [3]. The general form of the polyphase decomposition of a filter H(z) in the z-domain, with I subfilters  $P_k(z)$  is defined as equation (2.12) below [3]:

$$H(z) = \sum_{k=0}^{I-1} z^{-k} P_k(z^I)$$

(2.12)

where:

$$P_k(z) = \sum_{k=0}^{M-1} p_k[n] z^n$$

(2.13)

and:

$$p_k[n] = \sum_{k=0}^{I-1} h[nI+k]$$

(2.14)

This grouping of subfilters can be exploited in the realization of the polyphase structure. The realized direct-form polyphase structure and its transpose, with I subfilters are showed in figure 2.9. The two structures in figure 2.9 are equivalent [2].

Figure 2.9: General polyphase FIR-filter structure and its transpose, adapted from [2]

The multirate identity for an upsampling system states that the filter can interchange with the zero-stuffer, if the filter is properly modified [3]. This principle is shown in figure 2.10.

Figure 2.10: The multirate identity for an upsampling system

Applying the multirate identity on the transposed polyphase structure in figure 2.9 will change the subfilters system function from  $P_k(z^I)$  to  $P_k(z)$ , and the subfilters will now run at the input frequency  $f_{si}$  [3]. The zero-stuffing and delay operations can now be replaced by a commutator as shown in figure 2.11. The commutator operates at the output sample rate  $I \cdot f_{si}$ , and start at  $y_0[n]$  and sequentially picks up I samples for each input sample, by doing a full rotation counter clock wise [3].

Figure 2.11: Efficient realization of the polyphase IF, adapted from [2]

The number of computations per input sample are the same as for the direct-form implementation, but the advantage of the polyphase structures is that the filter is operating at input sample rate  $f_{si}$ . This reduces the number of computations per second by I times for an IF with an interpolation factor of I, compared to the direct-form implementation [2].

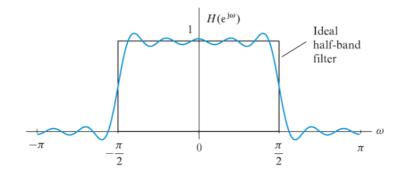

#### 2.4.5 Half-band filter

The half-band filter is a subclass of the linear-phase FIR filter, and is widely used in multirate systems. The half-band filter is characterized by its symmetric frequency response. The passband and stopband are equally wide with the center of the transition band at exactly at half the Nyquist frequency  $\frac{f_{si}}{2}$  [3]. The passband and stopband ripple is also symmetric [3]. This symmetric frequency response of an ideal and a real half-band filter is shown in figure 2.12.

The impulse response of the ideal half-band filter is characterized by [3]:

$$h_{\frac{1}{2}}[n] = \frac{1}{2} \operatorname{sinc}\left[\frac{n}{2}\right] \quad , n \in \langle -\infty, \infty \rangle \tag{2.15}$$

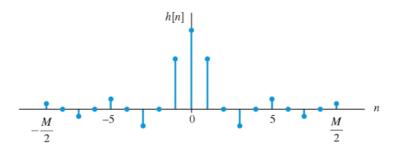

The ideal half-band filter cannot be realized in practice, because it has an infinite impulse response and is non causal. The half-band filter must be limited to a finite length N = M + 1, where M is the order of the half-band filter. The impulse response for a half-band filter with an order M = 18 is shown in figure 2.13.

Figure 2.12: Frequency response of half-band filter, from [3].

Figure 2.13: Impulse response of half-band filter with an order M = 18, from [3].

Since the impulse response is a sinc function all the even coefficients of the filter, except for  $h_{\frac{1}{2}}[0]$ , will be equal to zero. This can also be observed in the impulse response in figure 2.13. Thus, the half-band filter have about half the number of computations compared to an arbitrary FIR filter with the same length [2].

A causal half-band filter can efficiently be realized in the polyphase structure when it is used as part of an IF. Consider an IF with an interpolation factor of I = 2. Since the polyphase decomposition in equation (2.12) will group the impulse response into subfilters of even and odd terms, the impulse response of the half-band filter in the z-domain is equal to equation (2.16).

$$H(z) = \sum_{k=0}^{I-1} z^{-k} P_k(z^I) = P_0(z^2) + z^{-1} P_1(z^2) = h_{\frac{1}{2}}[0] + z^{-1} P_1(z^2)$$

(2.16)

Thus the combination of half-band filter with polyphase structure has about a quarter of the computations per second, compared to an arbitrary IF filter of same length.

#### 2.4.6 Cascaded integrator-comb (CIC) filter

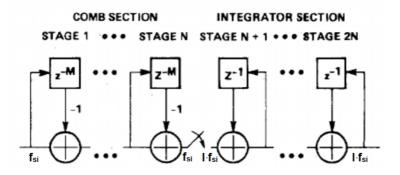

When implementing a conventional FIR filter in hardware, most of the resources will be used in the multiplications. The cascaded integrator-comb (CIC) filter is a subclass of linear phase FIR filters for decimation and interpolation, which uses no multiplication and limited storage [4]. This makes it very economical to use compared to conventional FIR filters for some applications.

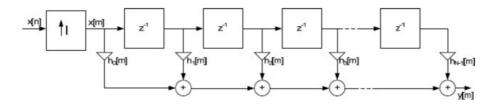

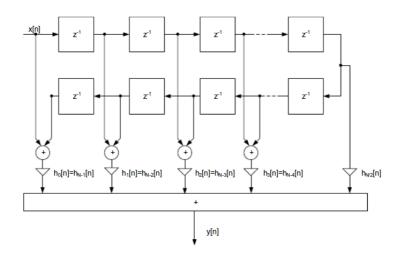

As the name implies, the CIC filter consists of cascaded ideal integrator stages, and an equal number of comb stages which together produce a uniform FIR. Figure 2.14 shows the basic structure of the CIC IF.

Figure 2.14: CIC IF, adapted from [4].

The N number of comb stages are operating at the lower sampling rate  $f_{si}$  of the filter, and each stage has a differential delay of M. This differential delay is in practice usually held to M = 1 or 2 [4]. The system response of a single comb stage is equal to equation (2.17) reference to the high sampling rate  $f_{so}$  of the CIC IF [4].

$$H_C(z) = 1 - z^{-IM} (2.17)$$

The N integrators stages are operating at the output sampling rate  $f_{so} = I \cdot f_{si}$  of the filter, where I is equal to interpolation factor. Each integrator stage is implemented with a system function shown in equation (2.18) [4]:

$$H_I(z) = \frac{1}{1 - z^{-1}} \tag{2.18}$$

Between the comb and integrator section is a zero-stuffer which increases the sample rate on the input of the integrator section. Combining equation (2.17) and (2.18) the system function for the complete CIC filter is produced, and is shown in equation (2.19) referenced to the high sample rate [4].

$$H(z) = H_I^N(z)H_C^N(z) = \frac{(1-z^{-IM})^N}{(1-z^{-1})^N} = \left[\sum_{k=0}^{IM-1} z^{-k}\right]^N$$

(2.19)

The frequency response of the CIC filter is given by equation (2.19) evaluated at  $z = e^{j2\pi f/I}$ , where f is referenced to the low sample rate of the filter. Using this, the frequency magnitude response can be showed to be equal to equation (2.20) [4].

$$H(e^{j2\pi f}) = \left|\frac{\sin\left(\pi Mf\right)}{\sin\left(\pi f/I\right)}\right|^{N}$$

(2.20)

The CIC filter has a low-pass frequency response, and from equation (2.20) it is evident that the frequency response of the CIC filter is fully determined by the three integer factors M, I and N. This will limit the range of possible filter characteristics. To increase the attenuation of the spectral replicas, the differential delay M and order N of the filter can be increased at the cost of more hardware adders and increased passband drop. Another penalty is the increased gain of the filter, which is exponential with the order of the filter. For an interpolating CIC filter the net gain can be shown to be equal to equation (2.21) [13].

$$G = \frac{(MI)^N}{I} \tag{2.21}$$

Another downside with high order CIC filter is the data word-length. The CIC filters generally use full precision to remain stable, and this gives a large data word-width penalty for high order filters [13]. Given a number of bits  $B_{in}$  on the input, the output data word-width is given by equations (2.22) [4].

$$B_{max} = [N \log_2 (IM) + B_{in} - 1]$$

(2.22)

The gain and increased data word-width may require the signal to be attenuated and/or truncated depending on the applications after the CIC filter.

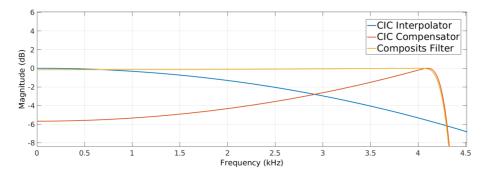

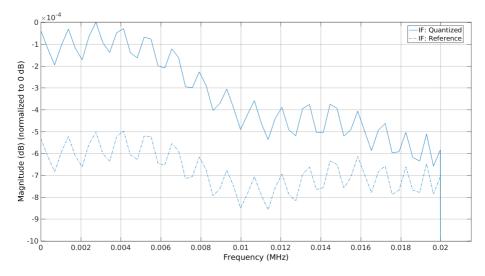

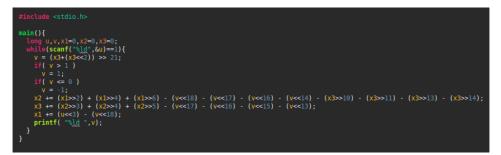

The CIC filter has a passband drop, which increases with the order and differential delay of the CIC filter. This effect is generally unwanted when interpolating a signal for audio, since this can be audible. This effect can be compensated by using a compensation FIR filter in cascade with the CIC filter, which ideally is an inverted version of the CIC filter over the passband. An example of this concept is shown in figure 2.15 with the frequency response of a CIC filter, a compensation FIR filter , and the composite filter. In this example the passband is 4kHz, and the magnitude is normalized to 0 dB.

The inverse sinc filter is a FIR filter subclass which can be used to compensate for the passband drop. The passband response of the inverse sinc filter is a slight rise, similarly to the compensation filter in 2.15, and the transition- and stopband can be configured like any arbitrary FIR filter.

#### 2.4.7 Coefficient sharing

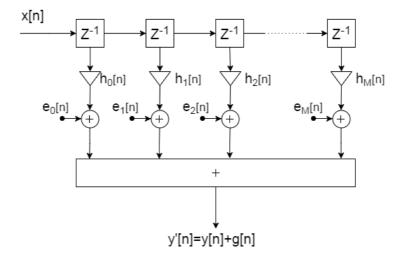

Since linear phase FIR filters has a symmetric or anti symmetric impulse response, the coefficients on each side of the center tap will be equal or have inverted sign [3]. This can be exploited by halving the number of stored coefficients, and by using the coefficient sharing structure illustrated in figure 2.16 [2]. This implementations will halve the number of multiplications in comparison to the a direct-form structure.

Figure 2.15: CIC filter, compensation FIR filter, and the composite filter frequency response.

Figure 2.16: Symmetrical FIR filter with coefficient sharing, from [2].

The number of delays and additions remains the same as for a direct-form structure [2]. The coefficients sharing structure can also be used in a polyphase subfilter, provided that the subfilter has symmetric or anti symmetric coefficients.

#### 2.4.8 Finite wordlength effects

When implementing a practical digital filter, all the data in the filter must be represented by a finite number of bits. This means that; the filters coefficients must be quantized, and a number format to represent the coefficients and data must be chosen. The finite wordlength arithmetic inside the filter can also require intermediate multiplication results to be quatized, and may cause overflow errors. The finite wordlength effects may introduce unacceptable errors in the filter, and must be taken into consideration when implementing the filter.

#### 2.4.8.1 Fixed-point versus floating-point arithmetic

The first choice to make in the quantization process is if filter coefficients and data should be formatted in fixed-point or floating-point arithmetic. In many cases this will be a choice between the filters performance and its computational load. The floating-point arithmetic gives a high numerical precision, but is more computationally heavy then the fixed-point arithmetic [3]. When implementing a filter with low cost and resource usage, the fixed-point arithmetic must be used [3].

#### 2.4.8.2 Quantization of filter coefficients

When the number format is chosen, the filter coefficients are quantized in this format. This is a one time operation, which causes the poles and zeros of the filter to move [2]. This happens since the quantization changes the coefficients infinite precision values, and is dependent on the quantization error. This changes the filter characteristics from its ideal values, and is noticeable in the frequency response, and/or its stability [3]. How much the filter characteristics changes depends on the filter structure, and the number of bits used to represent the coefficients [3]. If the filter characteristics of the new quantized filter violates the design specifications, the coefficients must be quantized using more bits until the specifications are satisfied. Using higher precision on the coefficients increases the length of the multiplications in the filter, and thus the filters computational load. There is a trade off between resource usage and performance, when choosing the precision of the coefficients [2].

#### 2.4.8.3 Round-off noise

The round-off noise is caused by the quantization of intermediate multiplication results in the filter, which might need to be quantized to avoid the wordlength growing to much through the filter structure [2]. The quantization causes the filter to become a nonlinear system, which is challenging to understand an analyze theoretically [3]. The effects can be approximated by using a linear model of the quantization process to make educated design choices. However the most efficient way to analyze the effects is to simulate the filter, and examine the performance [3]. How the filter responds to the quantization of the internal variables is dependent on the filter structure [2].

A linear model of the quantization process, where the quantization is replaced by a additive white noise source on a direct-form FIR filter structure, is shown in figure 2.17. In figure 2.17 each intermediate multiplication result is quantized.

The quantization noise source  $e_k[n]$  is assumed to be a wide-sense stationary white noise process with a zero mean. The quantization interval is uniformly distributed and given by  $\Delta = 2^{-B}$ , where B is the number of bits used in the quantization. Assuming that all the noise sources  $e_k[n]$  are uncorrelated with a variance  $\sigma_e^2$  expressed by equation (2.23).

$$\sigma_e^2 = \frac{\Delta^2}{12} = \frac{2^{-2B}}{12} \tag{2.23}$$

Figure 2.17: Linear noise model of quanzation process in FIR filter, adapted from [3].

It can be shown that quantizing each intermediate multiplication result in the filter to B + 1 bits, the total quantization noise power will be equal to equations (2.24) [3].

$$\sigma_g^2 = (M+1)\frac{\Delta^2}{12} = (\frac{M+1}{3})2^{-2(B+1)}$$

(2.24)

If a double length 2(B + 1) accumulator is available, the final result can be quantized on the output of the filter. With the same assumptions as before it can be shown that this quantization noise power will be equal to equations (2.25) [3]:

$$\sigma_g^2 = \frac{\Delta^2}{12} = \frac{1}{3} 2^{-2(B+1)} \tag{2.25}$$

Equation (2.25) show that the quantization noise will not increase proportionally with the number of coefficients M, as for the intermediate quantization used in equation (2.24). Thus the quantization noise will be lower for a FIR filter of arbitrary length M when using the second method. However, the computational load of the filter is increased, since all the accumulators are now double length 2(B + 1), in comparison to the single length B + 1 accumulators in figure 2.17.

#### 2.4.8.4 Overflow errors

Overflow errors is large errors due to addition overflow, which causes the accumulator to wrap around or saturate. When an accumulator wrap around, a two's compliment number will change sign and thereby introduce large errors. When a accumulator saturates, the output saturate at the maximum or minimum number that the accumulator can represent. An accumulator that saturates will need more digital logic than an accumulator which wrap around. The overflow errors can be prevented by properly scaling the numbers to be added.

#### 2.4.9 Filter implementation strategies

There are several different filter implementation strategies which can be used when implementing digital filters in hardware. The next sections will discuss the direct implementation and the multiplier-accumulator (MAC) implementation, which is two of the most common filter implementation strategies.

#### 2.4.9.1 Direct implementation

The direct implementation, also called fully parallel implementation, is a direct implementation of the direct-form filter structure [2]. The direct implementation is shown in figure 2.18.

Figure 2.18: Direct implementation of FIR filter, from [2].

The advantage of this implementations is that it computes the output in one clock period, and can thus be very fast. The disadvantage of this implementations is the high amount of resource usage, caused by the large amount of delay elements, multiplications and additions. The worst case timing path through the hardware structure can also become very long for high order filters, and can cause the filter to not fulfill the timing constrains. However, for multiplier-free filters like the CIC filter this can be an efficient hardware implementation, since its the multipliers that use most of the resources [2].

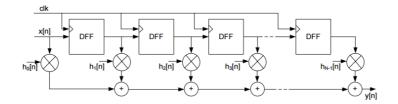

#### 2.4.9.2 MAC implementation

The MAC implementation, also called fully serial implementation, is a serialized implementation of the direct-form filter structure. In this implementation the coefficients are stored in a read-only memory (ROM), and is consecutively multiplied with the corresponding input sample [2]. The result from each multiplication is added up by a accumulator, and set to the output when all the multiplications are done. The input samples are stored in a register which inputs a new sample every time the filter computations are done, and rotates the stored input samples one step higher in the registers. In every rotation of the register, the last stored sampled in the chain is simply dismissed. Figure 2.19 show the MAC implementation of a FIR filter.

The MAC-implementation requires only one multiplier and one accumulator regardless of the filter order, but also requires two N length register to store the coefficients and the input samples for a  $N^{\text{th}}$ -order FIR filter. The resource usage is substantially reduced in comparison to the direct implementation, since the its the multipliers which uses

Figure 2.19: MAC implementation of FIR filter, from [2].

most of the resources in a hardware implementation [2]. The disadvantage with the MACimplementation is that the hardware must run N times faster than the sample rate to complete all the computations before receiving a new input sample. The MAC-implementation is therefore most suited for low speed operations, and is the most dominant implementation for IF used for audio applications [2].

## 2.5 ZedBoard

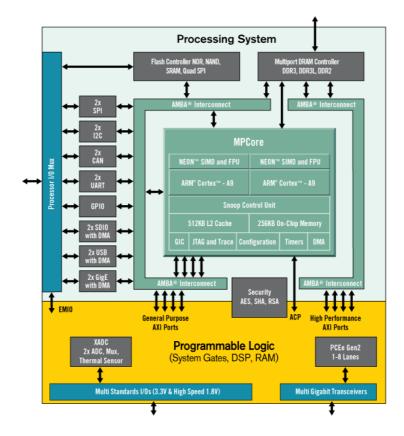

The complete S-D DAC solution is to be implemented on a FPGA, and therefore a target FPGA platform must be chosen. For this project the ZedBoard development board was chosen. The ZedBoard is a development board which is based on the Xilinx Zynq-7000 All Programmable SoC. The Zynq-7000 combines a dual Cortex-A9 processing system (PS), and 85.000 Series-7 programmable logic (PL) cells which are coupled together [14]. The ZedBord also features 512MB double data rate type three (DDR3) memory, 256Mb quad serial peripheral interface (QSPI) flash, and a range of interfaces like an USB-JTAG and an USB-UART bridge which the Zynq-7000 can utilize [14]. Figure 2.20 show a overview of the Zynq-7000 SoC.

The Zynq architecture enables software programming on the PS and implementation of custom logic on the PL. The PS can communicate with PL cores using the ABMA AXI4 bus interface. The PS can be configured to provide clock sources and reset signals to the PL cores. The PL can also run independent of the PS by using the 100 MHz oscillator on the ZedBoard as a clock source. The dual Cortex-A9 on the PS is capable of running a range of operating system (OS) like Linux and FreeRTOS<sup>TM</sup>, but can also run a a bare-metal single-threaded environment which provides basic features.

Figure 2.20: Xilinx Zynq-7000 SoC overview, from [5]

# **Chapter 3**

# **Design and Implementation**

## **3.1** Design and implementation of interpolation filter

The first task is to design and implement a IF for the S-D modulator from the project assignment in [6]. The specifications for an IF in a S-D DAC is, as mentioned in section 2.4.1, quite diffuse, and the design space is large with many parameters to consider. The IF is designed using the well known design and implementation techniques described in 2.4, and a limited time is used to explore a wide range of design configurations. The final solution is implemented in RTL code, in the Verilog language. In the following sections the design and implementation of the IF for the S-D DAC is described.

#### 3.1.1 Specifications

The sample rate and bit depth on the input of the IF is given by the CD-DA format, which was used as the standard when designing the S-D modulator. This gives a sample rate of 44.1kHz, and a bit depth of 16 bits on the input.

The interpolation factor I of the IF is given by the OSR of the S-D modulator, which in this case is 128. The output wordlength of the IF is set by the input wordlength on the S-D modulator, and is 16 bits.

The passband ripple should not be audible, and for a typical high-end DAC it is usually ranging from 0.001dB to 0.0001dB, as discussed in section 2.4.1. Using this as a guideline, the specification for the maximum allowed passband ripple is set to the lower end of this at 0.001dB.

The specifications for the phase response of the IF is set to a linear phase response, in accordance with standard used for audio filters.

The finite wordlength arithmetic in the filter will add quantization noise to the signal, and this noise should be audible. The design goal for maximum added distortion in the baseband is set to 1dB.

The requirements for attenuation of the spectral replicas is set with a IF partitioning implementation in mind. The spectral replicas should be attenuated under the noise floor of the S-D modulator, but for the spectral replicas close to the passband where the S-D

modulators noise floor is very low, a maximum attenuation of 100dB is set. This is in the middle range of the attenuation used by a typical high-end DAC, as discussed in section 2.4.1. The general specifications for the IF is summarized in table 3.1.

| OSR | Input sample rate | Input & output<br>wordlength | Passband ripple | Distortion |

|-----|-------------------|------------------------------|-----------------|------------|

| 128 | 44.1kHz           | 16 bits                      | <0.001dB        | <1dB       |

Table 3.1: Summary of IF specifications

## 3.1.2 Implementation

The implementations of the IF was done by using well known theory and design methods as a starting point, and then using the DSP toolbox in Matlab for testing and finding a suitable solution. The hardware description language (HDL) coder in Matlab is used to generate Verilog code of the IF. The HDL coder has some limitations in the implementations available for the IF, so the generated Verilog code is manually optimized, making the IF much more efficient. In the attachment to this thesis, the complete Matlab script used when designing the IF filter is available.

#### 3.1.2.1 Partitioning