### Reservoir Computing in the Spiking Domain Using Developmental Cellular Automata Machines

Øyvind Robertsen

Master of Science in Computer Science Submission date: June 2017 Supervisor: Gunnar Tufte, IDI

Norwegian University of Science and Technology Department of Computer Science

## Abstract

As computer systems and networks grow in size and complexity, traditional top-down engineering techniques are quickly beckoming inadequate for achieving the desired results. Designing such systems that are robust and resilient, are able to adapt and self-regulate, can self-reproduce and learn autonomously is a tremendously hard task. These features are however present in many biological organisms, wherein they emerge through evolution and development. In the fields of unconventional and biologically inspired computing, these techniques are used to create computing systems with the same type of complexity as that found in biological systems. Cellular Automata (CAs) are an example of a biologically inspired computing system that can achieve complex, global computation through local interaction between simple cells at a vast scale.

While the computational capabilities of CAs have been researched extensively, they have not seen mainstream adaption as a computational paradigm. Programmability and encoding/decoding of input/output are two major challenges facing cellular computing systems. Manually specifying the functionality of each cell in such a way that the desired emergent global behavior of the CA as a whole is achieved, is infeasible for non-trivial systems. Problem input is usually encoded in the initial state of the system, and output is decoded from the state after the system has been simulated some amount of time.

The Cellular Automata Research Platform (CARP) is an FPGA-based implementation of a developmental cellular architecture, aiming to facilitate research into use of artificial development and evolution to create cellular computing systems. At an abstract level, it implements a dynamical system with dynamical structure (DS)<sup>2</sup>, a system for which both behavior and structure are emerging properties. Behavior influences further structural development and vice versa.

In this thesis, the platform is extended to incorporate the developmental CA into a reservoir computing architecture. Reservoir computing (RC) is a novel approach to machine learning in which temporal input is imposed as perturbations on a dynamic reservoir and output is read out by performing a linear classification of the reservoir state some time after the initial perturbation. By combining RC and developmental CAs, the CARP system solves many of the issues relating to programming of and I/O encoding/decoding with cellular computing systems. It also opens up new possibilities for the developed organisms to adapt and learn based on their environment. The CARP platform has been extended with a reconfigurable readout layer implemented as a spiking neural network (SNN) that classifies the dynamics of the reservoir, the developmental CA. An SNN is chosen to allow the system operate entirely in the spiking domain, as input data and the dynamic behavior of the reservoir is already spiking in nature.

The extended platform has been verified through extensive testing, both in simulation and end-to-end on actual hardware.

## Sammendrag

Etter hvert som datasystemer og nettverk vokser i størrelse og kompleksitet, er tradisjonelle topp-ned teknikker raskt blitt utilstrekkelige for å oppnå de ønskede resultatene. Å designe robuste systemer som er i stand til å tilpasse seg og selvregulere, som kan selvreprodusere og lære autonomt er en utrolig vanskelig oppgave. Disse egenskapene er imidlertid tilstede i mange biologiske organismer, hvor de fremkommer gjennom evolusjon og utvikling. I forskningsområdene ukonvensjonell og biologisk inspirert databehandling brukes disse teknikkene til å lage beregningsarkitekturer med samme type kompleksitet som det som finnes i biologiske systemer. Cellulære Automata (CA) er et eksempel på et biologisk inspirert datasystem som kan oppnå komplisert, global beregning gjennom lokalt samspill mellom enkle celler i stor skala.

Mens beregningsevnen til CAer har blitt forsket på over lengre tid, har de ikke blitt tatt i bruk som et beregningsmessig paradigme i stor skala. Programmerbarhet og koding/dekoding av data inn og ut er to store utfordringer for cellulære datasystemer. Manuell spesifisering av funksjonaliteten til hver celle på en slik måte at den ønskede fremtredende globale oppførselen til CAen som helhet oppnås, er praktisk ugjennomførbart for ikke-trivielle systemer. Input data til problemet er vanligvis kodet i systemets innledende tilstand, og data ut dekodes fra tilstanden etter at systemet har blitt simulert over tid.

Cellular Automata Research Platform (CARP) er en FPGA-basert implementasjon av en cellulær arkitektur, med sikte på å fasilitere forskning på bruk av kunstig utvikling og evolusjon for å skape cellulære datasystemer. På et abstrakt nivå implementerer plattforment et dynamisk system med dynamisk struktur  $(DS)^2$ , et system hvor både oppførsel og struktur er fremvoksende egenskaper. Atferd påvirker videre strukturell utvikling og omvendt.

I denne oppgaven blir plattformen utvidet til å inkorporere kunstig utviklede CAer i en reservoir computing arkitektur. Reservoir Computing (RC) er en ny tilnærming til maskinlæring hvor temporal inndata påføres som forstyrrelser på et dynamisk reservoar, og data leses ut ved å utføre en lineær klassifisering av reservoar-tilstanden en stund etter den første forstyrrelsen. Ved å kombinere RC og utviklings-CA, løser CARP-systemet mange av problemene knyttet til programmering av og I/O enkoding/dekoding av cellulare beregningsarkitekturer. Det åpner også nye muligheter for de utviklede strukturene til å tilpasse seg og lære basert på deres miljø. CARP-plattformen er utvidet med et rekonfigurerbart avlesingslag implementert som et spiking neural network (SNN) som klassifiserer dynamikken i reservoaret, en cellulær struktur under utvikling. En SNN er valgt for å tillate at systemet opererer helt i spiking-domenet, ettersom data inn og den dynamiske oppførelsen av reservoaret allerede er spikes.

Den utvidede plattformen har blitt verifisert gjennom omfattende testing, både i simulering og ende-til-ende på faktisk maskinvare.

## Preface

This master's thesis has been conducted at the Department of Computer Science at the Norwegian University of Science and Technology under supervision of Professor Gunnar Tufte.

The thesis counts for 30 credits and is the continuation of a 15-credit specialization project conducted fall 2016. It concludes a 5-year master of science in Computer Science.

I would like to thank Gunnar Tufte for introducing me to an exciting field of research and for invaluable guidance and inspiration throughout the work on this thesis.

Øyvind Robertsen 2017 June 9th

## Table of Contents

| Ab                           | ostrac                                  | t                                                                  | i                                                                          |  |  |

|------------------------------|-----------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|

| Sa                           | mmer                                    | ndrag                                                              | iii                                                                        |  |  |

| Preface<br>Table of Contents |                                         |                                                                    |                                                                            |  |  |

|                              |                                         |                                                                    |                                                                            |  |  |

| Li                           | st of F                                 | ïgures                                                             | xiv                                                                        |  |  |

| 1                            | <b>Intro</b><br>1.1                     | duction<br>Outline                                                 | 1<br>3                                                                     |  |  |

| 2                            | Back<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Evolution2.1.1Genetic Algorithm2.1.2Genetic ProgrammingDevelopment | <b>5</b><br>5<br>6<br>6<br>7<br>7<br>9<br>10<br>12<br>12<br>12<br>12<br>13 |  |  |

| 3                            | <b>Prev</b> 3.1                         | <b>ious Work</b><br>Djupdal                                        | <b>15</b><br>15                                                            |  |  |

|    | 3.2                                             | Aamodt                                                                                                                                                                                           | 17                                                                               |

|----|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|    | 3.3                                             | Støvneng                                                                                                                                                                                         | 18                                                                               |

|    | 3.4                                             | Lundal                                                                                                                                                                                           | 19                                                                               |

| 4  | <ul><li>4.2</li><li>4.3</li><li>Imple</li></ul> | Convey Wolverine WX-2000 Application Accelerator                                                                                                                                                 | 21<br>21<br>22<br>22<br>24<br>25                                                 |

|    | 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7          | General overviewCommunicationReadoutReadoutCellular AutomatonMiscelaneous Modules5.5.1Readout Sender5.5.2Decode5.5.3Information SenderParameterizationSoftware API5.7.1Communication5.7.2Readout | 27<br>27<br>30<br>33<br>35<br>35<br>35<br>35<br>35<br>36<br>36<br>36<br>37<br>38 |

| 6  | 6.1                                             | icationTests6.1.1Unit Tests6.1.2Functional TestsExample                                                                                                                                          | <b>41</b><br>41<br>41<br>41<br>41                                                |

| 7  | 7.2                                             | Ission<br>Resource Usage                                                                                                                                                                         | <b>47</b><br>47<br>47<br>48                                                      |

| 8  | Conc                                            | lusion                                                                                                                                                                                           | 51                                                                               |

| Bi | bliogra                                         | aphy                                                                                                                                                                                             | 53                                                                               |

| A  | A.1                                             | face Specifications         Advanced Peripheral Bus (APB)         MemPort Bus                                                                                                                    | <b>57</b><br>57<br>59                                                            |

| B  | Instru                                          | uction Set Architecture                                                                                                                                                                          | 61                                                                               |

| С  | Speci                                           | alization Project Report                                                                                                                                                                         | 109                                                                              |

#### D Project Readme

## List of Tables

| 5.1 | List of parameters for the CARP hardware                  | 37 |

|-----|-----------------------------------------------------------|----|

| 7.1 | FPGA Resource usage of the CARP system                    | 48 |

|     | Signals and buses in the Advanced Peripheral Bus protocol |    |

## List of Figures

| 2.1  | Genetic Algorithm process                                   | 6  |

|------|-------------------------------------------------------------|----|

| 2.2  |                                                             | 7  |

| 2.3  | Wolframs rule classes mapped onto Langtons $\lambda$ -space | 8  |

| 2.4  | Development of multicellular organism                       | 9  |

| 2.5  | Growth rules for a cellular developmental system            | 0  |

| 2.6  | Basic overview of an RC system                              | 1  |

| 2.7  | RC system with developmental cellular reservoir             | 1  |

| 2.8  | Common spike response function shape 1                      | 2  |

| 2.9  | TrueNorth neurosynaptic core architecture                   | 3  |

| 2.10 | The Google Tensor Processing Unit                           | 4  |

| 3.1  | General system design                                       | 5  |

| 3.2  | Djupdal's hardware design                                   | 6  |

| 3.3  | Aamodt's hardware design                                    | 7  |

| 3.4  | Støvneng's hardware design 1                                | 8  |

| 3.5  | Lundal's hardware design                                    | 9  |

| 4.1  | Convey Wolverine Accelerator architecture                   | 2  |

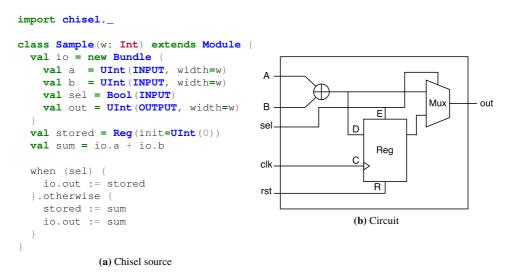

| 4.2  | Chisel source and corresponding circuit                     | 23 |

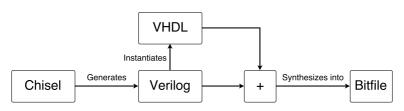

| 4.3  | Build process overview                                      | 4  |

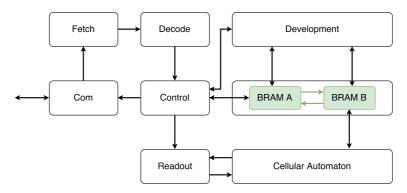

| 5.1  | CARP architecture extended with a readout layer             | 25 |

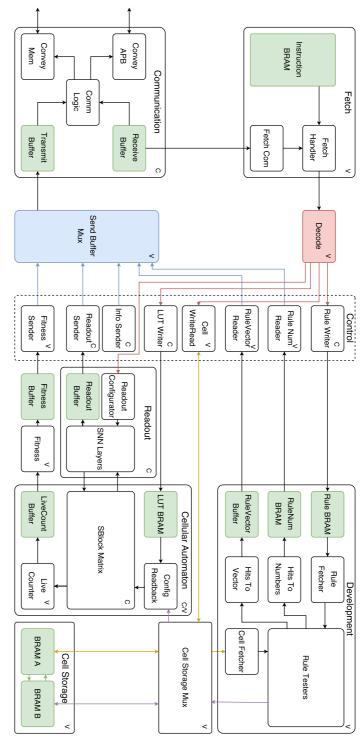

| 5.2  | Detailed system architecture diagram                        | 6  |

| 5.3  | Convey Application Engine architecture                      | 8  |

| 5.4  | CARP platform implemented in the AE architecture            | 8  |

| 5.5  | Communication module                                        | 9  |

| 5.6  | Communication module state machine                          | 9  |

| 5.7  | Readout module                                              | 0  |

| 5.8  |                                                             | 1  |

| 5.9  | Neuron                                                      | 2  |

|      |                                                             |    |

| 5.11<br>5.12<br>5.13<br>5.14<br>5.15 | <ul> <li>Weight addressing scheme</li> <li>Cellular Automaton Module</li> <li>Cellular Automaton FeedbackCells</li> <li>CA state machine</li> <li>Readout Sender</li> <li>CARP Software API</li> <li>Host-Coprocessor communication flow</li> </ul> | · · · · · · · · · · · · · · · · · · · | 32<br>33<br>34<br>34<br>35<br>37<br>39 |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------|

| 6.1<br>6.2                           | Example CA configuration                                                                                                                                                                                                                            |                                       | 42<br>43                               |

## Chapter ]

## Introduction

In recent years, research into computation using non-traditional physical mediums and paradigms, so called unconventional computing, has seen increased interest. With challenges currently facing traditional architectures, such as the von Neumann bottleneck and ensuring continued scalability and reliability, unconventional computing presents possible solutions from a new perspective. Biologically inspired computing is one approach to unconventional computating. It seeks to apply evolution, developement and other biological processes onto the design of both computer architectures and artificial intelligence systems. A common trait for many biological systems is that complex behaviour emerges from local interactions between simple units, whereas traditional computer architectures have been designed in a top-down fashion, composing complex modules and directing how information should flow between them. Alongside complex emergent behavior, biological systems often exhibit abilities such as self-reproduction, self-regulation and strong adaptability. These are desireable properties in computing systems, but they are hard to implement.

Cellular computing, introduced by Sipper in [34], is one example of a paradigm utilizing a bottom-up design methodology. Consisting of three core principles; simplicity, vast parallelism and locality, cellular computing seeks to harness the emergence of complex global behaviour from local interaction between simple cells at a large scale. One of the central problems with the paradigm is how one should go about designing/programming cellular systems. Specifying the functionality and potentially the connectivity of each cell manually while ensuring that the desired behaviour is achieved at a global level, is infeasible, so a different approach is needed. A potential solution is to automate the design through artificial evolution [35].

The POE-model, introduced by Sanchez et al [33], is a taxonomy commonly used to describe bio-inspired design methodologies using three categories: phylogeny, ontogeny and epigenesis. Phylogenesis relates to evolution, ontogeny encompasses systems that mimic biological development and epigenetic systems adapt to environmental change. These categories are not mutually exclusive. The use of artificial evolution to program a cellular computing system is an example of an phylogenetic system.

In artificial evolution, an individual represents a potential solution to some problem. In the case of using evolution to design cellular computing systems, the individual, or genome, has to encode both the behavior of each cell as well as the system, or organism, as a whole in order to represent a complete solution. This means that the size of the genome grows linearly with the size of the organism. In natural evolution, the genome has a different role. It serves as a set of rules governing the growth and development of cells at a local level, based on the types of surrounding cells and environmental feedback. This can be incorporated into the cellular computing paradigm as an ontogenetic aspect [41]. By evolving the developmental rules instead of the system as a whole, arbitrarily large and complex organisms can develop from a single cell based on a genome of fixed size. Systems that separate growth and behavior in this manner are called dynamical systems with dynamical structure  $(DS^2)$  [42].

The Cellular Automata Research Platform (CARP) is a long-running project at NTNU, dedicated to developing hardware that facilitates research into artificial evolution and development of cellular computing architectures. Based on the Virtual SBlock architecture presented by Haddow and Tufte [13], the system consists of programmable cells laid out in a regular one-, two- or three-dimensional grid, where each cell is connected to the cells in the von Neumann neighborhood around it. Cells can be in one of two states, either alive or dead. Based on their type, cells are programmed with a look-up-table (LUT) governing the transition between states based on the states of neighboring cells and the state of the cell itself. All cells are updated synchronously in discrete time steps. Development is simulated as a separate process, wherein cells transition between types using a LUT of development rules, taking both states and types of neighboring cells as input. This process also happens synchronously and in descrete development steps.

The CARP system is implemented on reconfigurable hardware, an FPGA, and is controlled by a program running on a host computer. Typically, the host program will implement the phylogenetic aspect of the system by evolving a population wherein each individual is a set of developmental rules. The CARP hardware is used to assess the fitness of each individual through development and simulation of the cellular organism.

Reservoir Computing (RC) is an exciting, new field of research within machine learning and intelligent systems. RC-systems work by imposing input data as perturbations on a dynamic system (the reservoir), and performing a linear classification of the reservoir state some time after the initial perturbation. Feedback from the classifier is routed back into the reservoir to allow it to regulate and adapt based on its own performance. In the specialization project leading up to this thesis, a proof of concept of a cellular reservoir and a readout layer implemented as a spiking neural network was simulated in software, with positive results. A common problem with cellular computing systems is that due to their very nature, it is often hard to formulate problems correctly and to interpret the dynamics of the system as answers to those problems. Combining the developmental, cellular architectures of the CARP system with the abstract computational concept of the RC paradigm will yield a more consistent framework for applying cellular computing to real-world problems.

In this thesis, the CARP system has been extended to include epigenetic aspects into the design and development of cellular architectures. This is done by adding a trainable readout-module based on spiking neural networks which processes the dynamic behavior of cells in real-time and feeding its output back into the cellular reservoir. The system has also been ported to run on new hardware and the codebase has been partially ported to Chisel, a hardware definition domain specific language implemented in Scala.

#### 1.1 Outline

This thesis is organized in the following chapters:

- **Chapter 2 Background**: An overview of theoretical concepts on which the work presented in this thesis is built upon. Also gives an introduction to FPGA technology as well as an overview of some related work.

- Chapter 3 Previous Work: A review of the history of the CARP project.

- **Chapter 4 Platform**: Information regarding the physical hardware used to run the platform and the toolchains used to develop the project.

- Chapter 5 Implementation: An overview of the implemented system and its constituent parts.

- Chapter 6 Verification: Descriptions of tests used to verify system functionality.

- **Chapter 7 Discussion**: A review of challenges with the system implemented in this thesis and possible future work.

- Chapter 8 Conclusion: Conluding remarks.

- Appendices

# Chapter 2

## Background

#### 2.1 Evolution

In nature, evolution is the process governing change and preservation of hereditary traits in populations of biological organisms. It allows species to adapt to their environment over generations through reproduction, variation and survival of the fittest [6].

Artificial evolution seeks to harness the powerful adaptive capabilities of natural evolution and apply them to general problem solving and learning. While research on the subject has branched into many different sub-areas, the general concept of optimizing a population of individuals with respect to some fitness function using mechanisms inspired by natural evolution, is referred to using the umbrella term Evolutionary Computation (EC) [2].

One of the greatest strengths of EC is how universally applicable it is. Evolutionary algorithms have successfully been applied to many different problem domains, such as robotics [10], bioinformatics [18], medicine [9] and many more.

#### 2.1.1 Genetic Algorithm

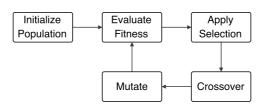

The most common type of EA is the Genetic Algorithm (GA) [12]. GAs use, as shown in 2.1, genetic operators such as mutation, crossover and selection to evolve a population of potential solutions to a problem, subject to some fitness function. The fitness function deems how fit an individual is, and thereby how likely it is to be selected for reproduction. It is a measure of how well the indivual performs as a solution to the problem at hand. The algorithm continues until an individual with a fitness higher than some predetermined threshold is found. Individuals are represented as genomes, commonly with a genotype encoded as a bitstring which serves as a blueprint to create the solution, the phenotype.

Figure 2.1: Genetic Algorithm process.

#### 2.1.2 Genetic Programming

Genetic Programming (GP), introduced by John Koza [19], is a technique attempting to automate the programming of computers. This is done by evolving a population of programs whose fitness is evaluated by executing them and comparing to the desired results. Programs are encoded in genotypes as tree structures, as opposed to as binary strings. This allows crossover and mutation operators to be implemented in such away that the resulting programs are structurally sound.

#### 2.2 Development

Biological development is the natural process that allows complex multi-cellular organisms to be built starting from a single cell using instructions encoded in the DNA of the organism. The most easily recognizable example is the development of humans from a single cell, the zygote, containing the combined genetic material of the parents, through cell division and differentiation. The human genome does not contain an exhaustive description and blueprint of each individual human. Rather, it consists of instructions governing how cells should divide and differentiate based on their surrounding cells and feedback from the environment.

Developmental processes in nature have many properties that make them desireable to mimic through artificial development. For instance, the number of cells in the human body is orders of magnitudes larger than the amount of information encoded in our DNA [3]. In general, the performance of GAs and GP implementations decline as the size of the genome increases, as mutations are more likely to be detrimental with regards to fitness. By introducing development as an indirect mapping between genotype and phenotype, programs and structures that scale to arbitrary dimensions can be produced while still maintaining a search space that the EA method in question can efficiently explore. Systems that combine evolution and development in this way are often referred to as EvoDevo systems [14].

Where evolution allows a species to adapt over the span of generations, development is an ongoing process throughout the lifetime of each individual, allowing for adaption based on changes to the environment [40]. This makes EvoDevo particularily well suited in the design of robust and adaptive artificial intelligence agents.

#### 2.3 Cellular Computing

Most computing devices in use today have been developed on the foundation of the von Neumann architecture [44], a single complex processor performing one complex task at a time. Recently, the field of cellular computing has seen growing interest. Cellular computing, as described by Sipper in [34], is built on three principles: simplicity, vast parallelism and locality. It seeks to exploit emergent computational capabilities between large numbers of locally connected simple cells. Sipper presents cellular computing as an abstract framework, within which many variations of the paradigm can exist based on a number of properties. These include cell type (which types of values a cell can take; discrete or continuous), cell definition (how the behavior of cells is specified), cell mobility (wether or not cells can move within their environment), cell connectivity (how cells are connected to eachother; regular grid, (un)directed graph), topology of underlying environment (if any), connection lines (what information to transmit between connected cells), temporal dynamics (asynchronous vs. synchronous updating schemes), uniformity (in cell type and connectivity) and determinism. Some well known examples of paradigms that fit within the framework of cellular computing are Random Boolean Networks (RBNs) and Cellular Automata (CAs).

#### 2.3.1 Cellular Automata

The most well known example of cellular computing is the Cellular Automaton (CA). Consisting of cells connected in a regular grid that transition between discrete states based on the states of the cells in their neighborhood <sup>1</sup>. While each cell is not capable of much on their own, the behavior emerging from interactions between cells can give rise to complex dynamics. Figure 2.2 shows the behavior over eight timesteps of a simple, 1-dimensional, uniform CA starting from a single cell, with each time-step shown on a new line. The rule governing state transitions is shown in the boxes to the right in the figure. Each box gives the neighborhood conditions on the top row and the resulting state on the bottom.

Figure 2.2: Eight timesteps for a uniform 1-dimensional CA. The boxes to the right show the rule with which the cells are configured, Rule 90.

Research into the computational capabilities of CAs can be said to have started in the 1940s, with John von Neumann and Stanislaw Ulam designing a 2D CA capable of self-reproduction [34]. Moving forward, the dynamics and behavior of specific CA rules was

<sup>&</sup>lt;sup>1</sup>The von Neumann-neighborhood, consisting of cells directly north, east, south and west of a cell, is a common choice.

examined in detail. For instance, the rule used in Game of Life, introduced by mathematician John Conway in 1982, was proven to be capable of universal computation [5]. Stephen Wolfram shifted focus from studying specific rules, to investigating characteristics of groups of rules, resulting in his classification of the CA rulespace:

- 1. Rules leading to homogenous state for all cells. Regardless of the initial configuration of the cells, they all converge to the same state after a transient period.

- 2. Rules leading to stable or periodic structures.

- 3. Rules leading to chaotic patterns.

- 4. Rules leading to complex, long-lived structures. This is the only class that contains non-trivial automata.

Wolfram proposed that the rules capable of universal computation, such as Game of Life, reside in Class 4.

$$\lambda = 1 - \frac{q}{tot} \tag{2.1}$$

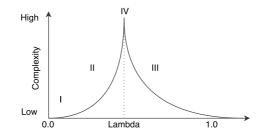

Like Wolfram, Christopher Langton has performed quantitative and qualitative studies of the CA rulespace [20]. He hypothesized that it is more likely to find rules capable of complex computational behavior in regions of the rulespace where there is a phase transition between ordered and chaotic dynamics. He introduced the  $\lambda$ -parameter as a measure of heterogeneity for a rule. It is calculated, as shown in 2.1, where q is the number of transitions in a rule that lead to a chosen quiescent, or dead, state, and *tot* is the total number of transitions. For a CA with N possible states and a neighborhood-size of K, the total number of transitions is  $K^N$ . A  $\lambda$ -value of 0 indicates an entirely homogenous rule, where all possible neighborhood configurations result in a transition to the quiescent state. Maximally heterogenous rules will have a  $\lambda$  of 1-1/N. Figure 2.3 shows how Wolframs 4 classes map onto Langtons  $\lambda$ -space, with Class 4 coinciding with phase transition between ordered and chaos behavior, the so called Edge of Chaos.

**Figure 2.3:** Wolframs rule classes mapped onto Langtons  $\lambda$ -space.

#### 2.3.2 Developmental Cellular Architectures

One of the major challenges faced by cellular computing systems is how to program one. Manually programming the functionality and connectivity of each cell to achieve the desired emergent properties is both exceptionally time-consuming and hard to do when the problem to be solved involves global coordination. Sipper proposes to automate the programming of cellular systems through an adaptive process such as an EA. In [27], Mitchell et al. use a GA to evolve CA rules for solving problems requiring global coordination. Each individual is a bitstring representing the next-states for all possible neighborhood configurations. With a neighborhood size of 7, each genome is  $2^7 = 128$  bits long yielding a search space size of  $2^{128}$ . The authors are able to successfully evolve CAs that solve the problems for which they where created.

A different approach is taken by Sipper [35] in order to evolve non-uniform CAs. Where Mitchell et al. evolve a population of rules, doing this for a non-uniform CA would require an exceptionally large genome in order to specify the rule for each cell, increasing the search space exponentially, making it infeasible to search through using a standard GA. Sipper instead works with a single CA initialized with a random rule in each cell. The fitness of each cell is accumulated over some number of simulations of the CA starting from different initial state configurations, after which evolutionary mechanisms are applied in a local manner, between connected cells. Through this method, Sipper is able to evolve non-uniform CAs that outperform the uniform ones evolved by Mitchell et al. on the same tasks.

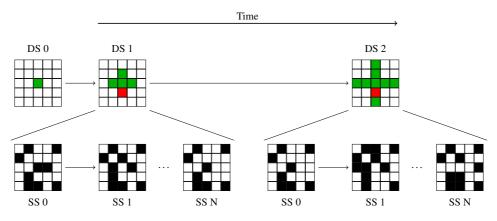

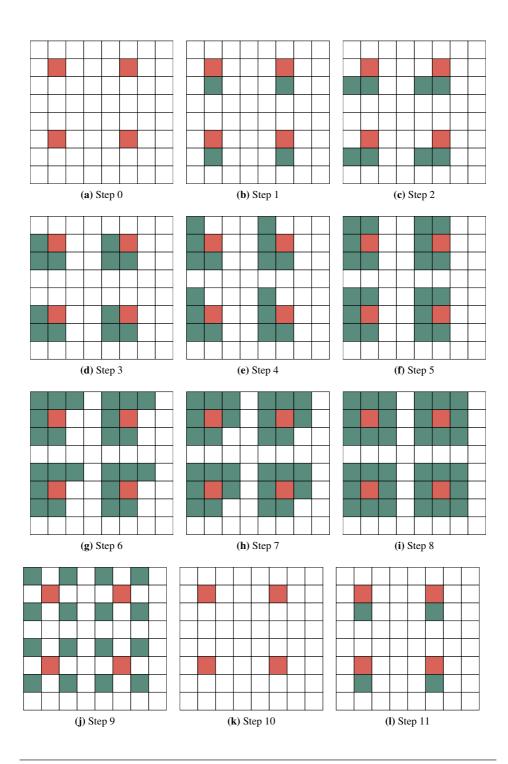

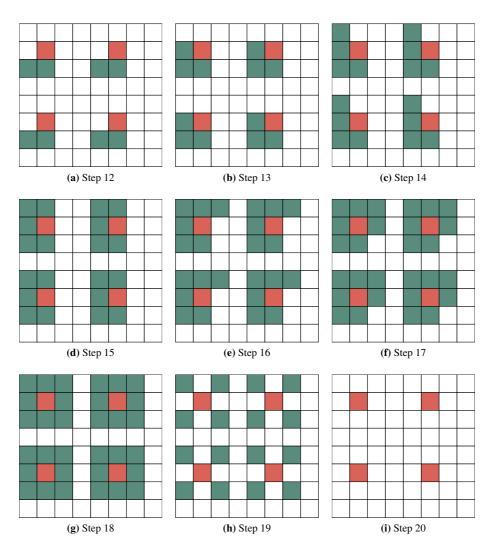

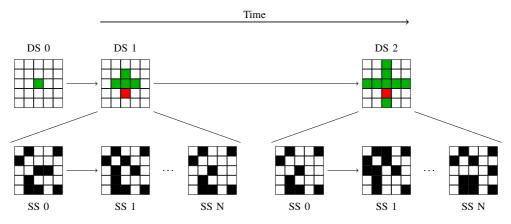

Figure 2.4: Development starting from a single green cell using the growth rule in Figure 2.5.

A third approach to the design of cellular computing systems is presented by Haddow and Tufte in [41]. The authors use a developmental model to allow complex non-uniform CAs to grow from a single cell, as shown in Figure 2.4. Development occurs in discrete time steps, so called development steps (DS). Between each DS, a number of state steps (SS) occur, simulating the behavior of the organism developed so far as a CA. The rules governing the development process, the genome, take both cell type and state into consideration when deciding how to proceed. This means that the behavioral dynamics of the organ

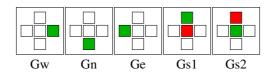

Figure 2.5: Growth rules for a cellular developmental system where cells are either empty or of the green type.

ism being developed regulates the developmental process. This type of coevolution of both structure and functionality is often referred to as dynamical systems with dynamical structure  $(DS)^2$  [37].

While the three approaches to programming of cellular computating systems outlined above achieve positive results, the task is still hard. In the case with the developmental approach taken by Tufte, creating developmental rules is as difficult as manually specifying type and functionality for each cell. Combining development with evolution is possible [29], but the genome size needed to express all regulatory possibilities in the genome is so large that the resulting size of the search space makes it hard for the EA to reliably converge. There is in other words still a ways to go before programming of cellular computing systems can be considered a solved problem.

Another challenge faced by such systems is how to formulate problems and encode/decode their inputs and outputs. In the works by Sipper and Mitchell, problem input is encoded as the initial state of the CA, and the output is interpreted from the state of cells after a number of state steps. This approach takes away from the generality of cellular systems, as an evolved/developed system will only be able to work specifically for the problem and encoding scheme it was initially designed around. Adapting a system to apply to different problems or to slight variations in input encoding will almost always require it to be developed from scratch.

#### 2.4 Reservoir Computing

Artificial Neural Networks (ANNs) are a commonly used computational model in machine learning and bio-inspired computing. Simple, feed forward ANNs lend themselves well to problems were data can be spatially correlated, such as classification. Many real world problems however, are temporal in nature. Recurrent neural networks (RNNs) have been shown to be powerful tools for solving temporal problems such as stock market prediction [21], learning context free/sensitive languages [11] and speech synthesis [45]. Training RNNs is computationally expensive and often requires application specific adaptions of generalized training algorithms in order to reliably converge [15]. Several techniques have been proposed that circumvent problems related to training, such as Echo State Networks [16] (ESNs), Liquid State Machines [24] (LSMs) and Backpropagation Decorrelation learning [38]. These all share the common feature of only training weights of the output layer of the network, while leaving the hidden layers of the network untrained or

simply subject to weight scaling. In [43], Verstraeten et al. propose that systems based on this idea should be unified under the term reservoir computing (RC).

In general, reservoir computing as a term describes any computational system where a dynamic reservoir is excited by input data and output is generated by performing classification/regression over reservoir state. Figure 2.6 shows the basic architecture of any reservoir computing system. With its origins in research on various types of recurrent neural networks and training thereof, the reservoir in RC systems is often represented as an RNN [43]. However, any dynamic system capable of eventually forgetting past perturbations and of responding distinctly to different perturbations, can in principle be used. Snyder et al. [36] investigate using Random Boolean Networks, Yilmaz uses Cellular Automata [46] and Fernando et al. use a bucket of water [8].

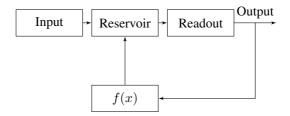

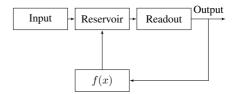

Figure 2.6: Basic overview of an RC system.

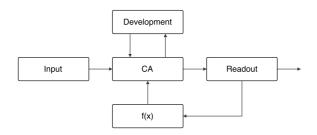

As outlined in Section 2.3 cellular computing systems are capable of complex, vast parallell computing. Combined with artificial development they are also highly adaptive. In this thesis we combine reservoir computing and developmental cellular automata in an attempt to provide a framework allowing for easier use and development of cellular systems. Figure 2.7 shows how input data perturbs the behavioral part of the reservoir, the emerging CA, and output is extracted by using the readout layer to classify the dynamics in the CA. RC systems provide a layer of abstraction between I/O encoding/decoding and the computation occurring in the CA. With this approach the goal of development and evolution is not to create a CA configuration that is able to solve a specific problem under specific I/O conditions, but rather to develop CAs with strong general computation capabilities and strong ability to adapt to different input perturbations. A CA that is general enough, could be used in many different contexts simply by swapping out the readout layer.

Figure 2.7: RC system with developmental cellular reservoir.

#### 2.4.1 Spiking Neural Networks as Readout Layers

Artificial neural networks can be grouped into three generations, based on the characteristics of their base computational unit, the neuron. The first generation, based on McCulloch-Pitts neurons [26], simple threshold gates, allows for universal computation on digital input/output values. In the second generation, neurons apply a non-linear, continuous activation function on the weighted sum of their inputs.

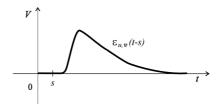

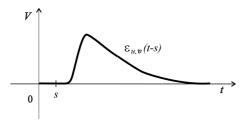

The third generation of networks bases itself on spiking neurons, which model the interaction between biological neurons more closely. In this model, a neuron v fires when its potential  $P_v$  exceeds a threshold  $\theta_v$ . The potential is, at any time, the sum of the postsynaptic potentials, resulting from firing of presynaptic neurons. The contribution of a spike from presynaptic neuron u at time s to the potential  $P_v$  of postsynaptic neuron vis given by  $w_{u,v} \cdot \varepsilon_{u,v}(t-s)$ , where  $w_{u,v}$  is a weight representing the strength of the synapse connecting u and v, and  $\epsilon_{u,v}(t-s)$  models the response of the spike as a function of time passed since the spike occurred. A synapse can be both excitatory and inhibitory, meaning that its contribution to the total potential  $P_v$  can be both positive and negative. A biologically plausible response function is shown in figure 2.8. From a machine learning perspective, the trainable part of a spiking neural network, is the weight  $w_{u,v}$ , determining to what degree spikes from a neuron u influences the potential of neuron v.

Figure 2.8: Common spike response function shape, figure taken from [23].

Spiking Neural Networks (SNNs) are of particular interest in the context of a cellular RC system, where the reservoir dynamics are spiking in nature (i.e. a cell can be either alive or dead). By using a spiking neural network as a readout layer, data can flow through the RC-system as spikes from end to end. In the specialization project leading up to this thesis, experiments to examine the viability of SNNs as readout layers in RC system were carried out with successful results (see Appendix C).

#### 2.5 Related Work

#### 2.5.1 IBM Truenorth

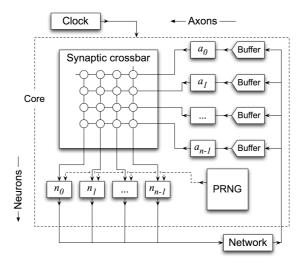

The IBM Truenorth is a modular, non-von Neumann, ultra-low power computer simulating a massive network of biologically plausible spiking neurons <sup>2</sup>. It consists of 4096

<sup>&</sup>lt;sup>2</sup>http://www.research.ibm.com/articles/brain-chip.shtml

neurosynaptic cores, each simulating 256 neurons and  $256 \times 256$  synapses, resulting in a total of 1 million neurons being simulated. The cores are connected using an on-chip mesh network, allowing the core-count to be scaled without adding extra circuitry. During operation the platform consumes < 100 mW and is capable of 46 billion synaptic operations per second, per watt.

Figure 2.9: Conceptual architecture of a neurosynaptic core used in the TrueNorth chip. Reprint from [30].

IBM has implemented an ecosystem of algorithms, libraries, simulators, a programming language and an integrated development environment to support the platform. Several applications for the chip has also been developed, such as a multi-object detection and classification system operating on  $240 \times 400$  pixel, 3-color video input at 30 frames per second.

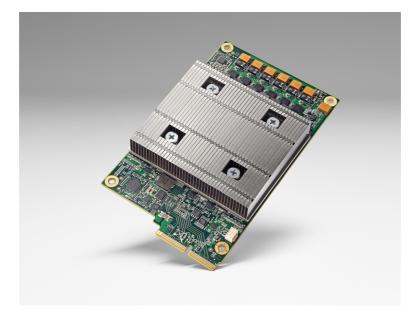

#### 2.5.2 Tensor Processing Unit

To accelerate training and utilization of machine learning models implemented using their TensorFlow<sup>3</sup>, Google have designed an Application Specific Integrated Circuit (ASIC), the Tensor Processing Unit (TPU)[17]. Designed to provide exceptionally fast matrix mutliplication, the TPU is built around a Matrix Multiply Unit (MMU) capable of 2<sup>16</sup> 8-bit multiply-and-add operations on signed/unsigned integers per cycle. The rest of the logic on the chip is dedicated to moving and organising data in such a way that the MMU is maximally utilized.

When compared with its contemporary CPU and GPU competitors, the TPU operates approximately 15-30x faster, and with 30-80x higher TeraOps/Watt.

<sup>&</sup>lt;sup>3</sup>https://www.tensorflow.org/

<sup>&</sup>lt;sup>4</sup>https://cloudplatform.googleblog.com

Figure 2.10: The Google Tensor Processing Unit. Reprinted from <sup>4</sup>

## Chapter 3

### Previous Work

The work presented in this thesis extends the Cellular Automata Research Platform (CARP), an FPGA-based system implemented specifically to support and accelerate research into growth and evolution of developmental systems based on cellular automata. The original implementation was done by Djupdal in 2003. Over the years, the system has been extended as well as optimized to run on newer hardware through a series of master theses. The following sections provide an overview of the evolution of the system.

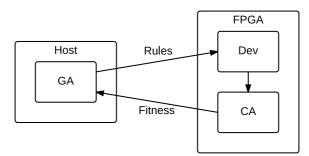

Figure 3.1 shows the original overall design of the system, indicating how the host program is responsible for evolving genotypes, while developing genotypes into phenotypes and simulating their behaviour in the CA is implemented on the FPGA.

Figure 3.1: General system design. Figure reprinted from [22].

#### 3.1 Djupdal

The original design of the CARP system was made by Djupdal in 2003 [7], to support further research into elvolvable hardware based on the SBlock-architecture proposed by Tufte and Haddow [13]. The system was implemented on a NallaTech BenERA FPGA-board communicating over a Parallell Component Interconnect (PCI) bus with a CompactPCI host-computer.

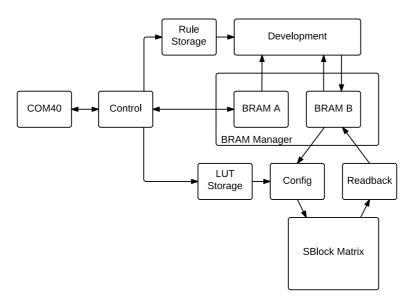

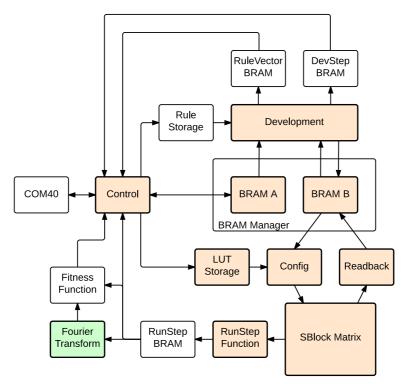

Figure 3.2 shows the overall architecture of the resulting hardware platform. It consists of the SBlock Matrix (SBM), Block RAM (BRAM) for storing the state and type of each cell, a development unit, control logic, and a PCI communication unit.

**Figure 3.2:** High-level block diagram of the hardware platform as implemented by Djupdal. Figure taken from [22].

A host computer, running a genetic algorithm exploring the space of possible development rules, controls the system. Each genotype is transferred to the system and developed into its phenotype before the SBM is stepped some number of times. New states and types can then be transferred back to the host to calculate a fitness score.

A genotype consists of a set of initial cell states and types, development rules and LUTs corresponding to the cell types possible. Upon initializing the system with a new genotype, states and types are written to BRAM A, while development rules and LUTs have their own separate BRAMs. During development, cells are read from BRAM A, tested against development rules and written back to BRAM B, now possibly changed as a result of "hitting" a rule. The development unit tests 8 rules on 2 cells each cycle in raster order. This means that for sets of rules larger than 8, several sweeps over the cells is necessary. For these additional sweeps, cells are read from BRAM B so as not to overwrite the result of a rule hit in a previous sweep if no rules hit in the later ones. The two BRAMs can be swapped logically, avoiding having to transfer between the two in order to start a new development step.

Based on the cell types stored in BRAM A, the SBM can be configured. Each cell type

corresponds to a LUT stored in the LUT storage BRAM, with which the SBlocks corresponding to cells of that type is configured. State steps can then be performed either one at a time, writing each new set of states back to BRAM B, or in batches, writing only the final set of states back.

#### 3.2 Aamodt

In Djupdal's design it was necessary to transfer cell states to the host to calculate fitness. To avoid this bottleneck, Aamodt extended the system with an on-board fitness module in 2005 [1]. Additionally, to gain further insight into the development process, he added logging-modules for the development unit.

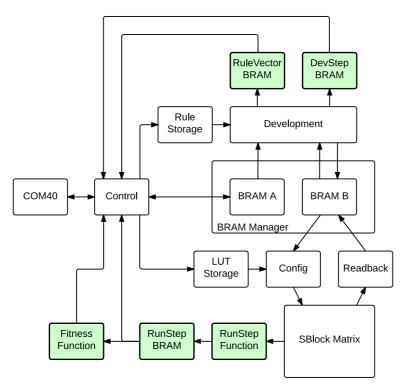

Figure 3.3 shows the overall system as implemented by Aamodt. The modules added are as follows; a Run-Step Function (RSF) that calculates the number of live cells, a BRAM module to buffer these numbers, a fitness function and the two logging modules from the development unit.

**Figure 3.3:** High-level block diagram of the hardware platform after Aamodt's work. Additions are highlighted in green. Figure taken from [22].

The two BRAMs added to the development module logs information regarding the devel-

opment process. The Development Step BRAM stores which rules were triggered for all cells during the most recent development step, while the Rule Vector BRAM stores which rules were triggered overall for the last 256 development steps. The RSF is a large adder tree, calculating the total number of live cells in the SBlock matrix after each state step. These totals are buffered in the RunStep BRAM before being processed by the fitness function.

#### 3.3 Støvneng

In 2014, the system was further extended and optimized by Støvneng [39], in expectation of new FPGAs aquired by NTNU. In addition to rewriting existing modules to better utilize the resources available on the new chips, he also modified the SBlock matrix to allow for 3D CAs and implemented an on-chip Discrete Fourier Transform (DFT) for processing the cell count from the RSF-module into the frequency domain.

Figure 3.4: High-level block diagram of the hardware platform after Støvneng's work. Additions are highlighted in green, and optimizations and 3D modifications in orange. Figure taken from [22].

Figure 3.4 shows how the DFT module is added to the overall design, as well as which modules have been optimized and rewritten to support 3D CAs. Overall, the optimizations made to the system yielded a 4x speedup for most operations. The design as a whole was

also made more parameterized and portable by removing many hard coded constants and rewriting modules relying on features specific to the old FPGA.

As the new hardware did not arrive in time, Støvneng was unable to test his changes on the actual FPGA, but the design in its entirety was verified through simulation.

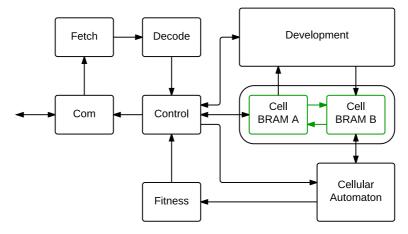

#### 3.4 Lundal

After Støvneng finished his work, it became clear that the new hardware would be delayed yet again. To allow for further development and testing of the platform on actual hardware, a development board with a similar FPGA as the one in the anticipated new hardware was ordered. As this newer line of FPGAs has removed support for PCI in favor of PCIe, both the communication module on the hardware platform and the software side driver had to be updated. While testing the new communication module, several issues with the current implementation were uncovered, such as commands not functioning according to specification and extensive use of outdated FPGA features. This led to the decision of rewriting the platform from scratch, a job undertaken by Lundal in 2015 [22].

Figure 3.5: Overview of the reorganized hardware platform as implemented by Lundal. Figure taken from [22].

Through his work, Lundal focused on making the hardware platform more modular, easier to configure and coherently structured. All dependencies on specific hardware features were removed in favor of letting the synthesizer infer based on which resources are available on the targeted chipset. Support for both 2D and 3D SBMs was implemented by Aamodt as two separate designs. Lundal unified this into one design, utilizing the fact that all 2D CAs can be implemented as one-high 3D CAs. The software API was also made more complete and user-friendly, by implementing abstractions that allow the end user to focus more on the code related to the experiment being performed and less on the technicalities necessary to operate the hardware platform.

Since Djupdal's original design, the development module has remained largely unchanged, implementing a developmental model based on research by Haddow and Tufte [41]. In this model two types of developmental rules are considered; growth-rules indicating how an organism develops spatially, and change rules describing how existing cells can change their type. Both rule types consist of a condition and a result. Conditions take into account the types of the cells in the von Neumann neighborhood around the target cell and the type of the target cell itself. The result of a growth rule is the direction in which the target cell should grow. For a change rule, the result is the new type of the target cell. Change rules can only affect cells that have already been grown into and growth rules can only grow into cells that are empty.

Lundal implemented a simpler development module based on Tufte and Nicheles research [28]. Here, all rules are effectively change rules and all rules are evaluated for all cells. The functionality of growth rules in the old design can still be implemented within this scheme. Where the differentiation of growth and change in the old design is closer to the type of cell development that happens in biological systems, the new system is more applicable to generic dynamical systems.

Lundal verified the reimplemented CARP platform both through simulation and end-toend integration tests with the synthesized design .

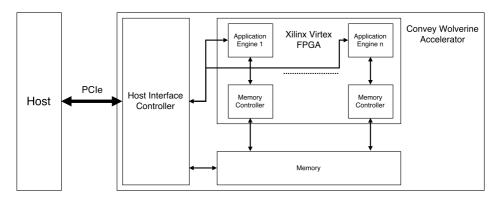

## Platform

In 2016, the long anticipated new hardware was finally installed and was ready to be used for the CARP project. The new machine contains four Convey Wolverine Application Accelerators, coprocessors aimed at accelerating key parts of algorithms in high-performance computing through reconfigurable hardware. Each accelerator is equipped with a state-of-the-art Xilinx FPGA and large, high-bandwidth on-chip memory.

The following sections describe the Wolverine accelerator architecture, the toolchain used to synthesize the hardware design and finally the toolchain used for the software API.

#### 4.1 Convey Wolverine WX-2000 Application Accelerator

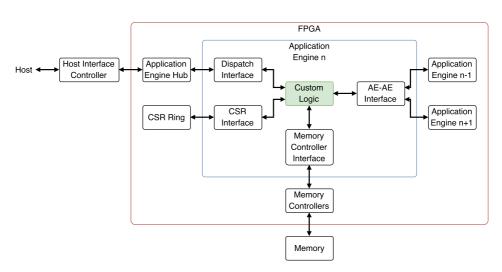

The Convey Wolverine WX-2000 is a PCIe-mounted coprocessor equipped with a Xilinx Virtex-7 XC7V2000T FPGA and four DDR3 SO-DIMM slots allowing for up to 64 GB of on-chip memory. Figure 4.1 shows how a Wolverine coprocessor is organized at a high level. The host computer communicates with the card over a Peripheral Component Interconnect Express (PCIe) bus at a max bandwidth of 8 GB/s. On the coprocessor, the Host Interface controller (HIX) is responsible for decoding the data sent from the host. Data can either be stored in the on-board memory, or passed directly to the FPGA. The FPGA is divided logically into Application Engines, the number of which can be configured before synthesis. This is the entrypoint into which a custom FPGA design is inserted. The Convey Personality Development Kit (PDK) provides each AE with interfaces to the HIX, the AEs memory controller and the other AEs.

With 2 million logic cells, 46 MB of BRAM and up to 2.8 Tb/s serial bandwidth, the XC7V2000T is one of Xilinx' higher end FPGAs. Earlier, FPGAs have been scaled monolithically following Moore's Law, in the same way conventional processors have been scaled. With the XC7V2000T however, Xilinx has opted to combine 4 separate dies

into one large virtual FPGA with their Stacked Silicon Interconnect (SSI) technology [32]. Each die, or Super Logic Region (SLR), has its own clocking and configuration circuitry. For monolithic designs, these signals would have to be routed throughout the entire die in complex ways to avoid critical paths that are too long. With this circuitry replicated in each SLR, the resources required for routing clocking and configuration signals is significantly lower, opening up the possibility to use these resources to interconnect the SLRs instead. This, along with advances in manifacturing techniques has allowed Xilinx to scale their FPGAs even further and opening up new use cases for them. Programming FPGAs using SSI is no different from any other FPGA. The Xilinx design flow toolchain distributes designs across multiple SLRs if needed.

Figure 4.1: High level overview of the Convey Wolverine Accelerator architecture.

#### 4.2 Hardware Toolchain

All previous iterations of the CARP hardware platform have been implemented entirely in VHDL. At the start of this project, the decision was made to start porting the codebase to Chisel, a hardware construction DSL implemented in the Scala programming language.

#### 4.2.1 Chisel

Chisel<sup>1</sup> is an open-source hardware construction language developed at UC Berkeley. Where many other hardware design tools implemented in high-level programming languages are of the "C-to-gates" variety, tools that try to automagically infer hardware based on a description of the desired computation, Chisel is based upon using the computational tools in Scala to describe how a circuit should be wired. Leveraging Scalas typesystem and functional programming tools, Chisel encourages code reuse, genericity and designing systems that are highly parameterizable.

https://chisel.eecs.berkeley.edu/

Figure 4.2: Chisel source and corresponding circuit.

Listing 4.2a shows how to implement the circuit in Figure 4.2b. The io bundle defines the inputs and outputs of the module. In this case a boolean input signal and three unsigned integer signals, two inputs and an output, all of whose bitwidth is determined by the w parameter passed to the module when it is instantiated. **val** s = Module(new Sample(32)) will create an instance of the Sample module with 32-bit wide UInts.

When executed, a Chisel program creates a internal graph representation of the circuit described by the program. Depending on the parameters given to the program, the program will output either Verilog or a C++ simulator of the circuit. To create a fully functional FPGA-image the Verilog output can be incorporated into an FPGA design flow.

To avoid having to start entirely from scratch, it was decided that porting the CARP hardware platform to Chisel would be done in a top-down fashion. That is, starting by instantiating Lundal's toplevel module as a blackbox in the Chisel design and implement downward in the module hierarchy as needed when extending the functionality of the platform. Figure 4.3 gives an overview of the build process. All parameterization is gathered in the Chisel part of the design and passed on into the VHDL modules when they are instantiated in the resulting Verilog.

For further details regarding the development setup for the hardware part of the CARP project, see Appendix D.

Figure 4.3: Build process overview.

#### 4.3 Software Toolchain

The software API is written in C, compiled on CentOS 6.5, Linux kernel version 2.6.32-431 with GCC version 4.4.7. Outside of the C standard library, the API has only one dependency; the Convey Personality Development Kit. It is included via the wmd\_user.h header and provides functions and routines related to communicating with the Convey coprocessor.

# Chapter 5

## Implementation

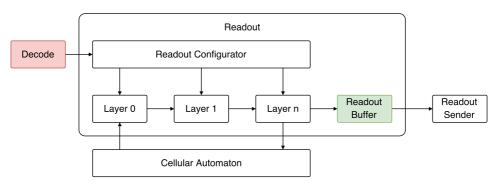

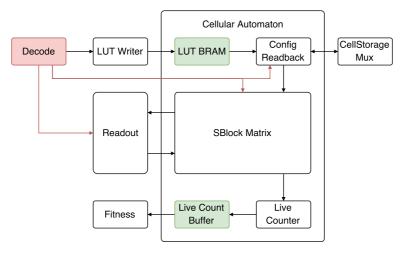

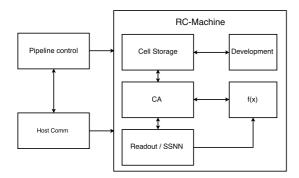

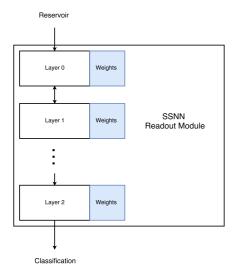

Figure 5.1 shows a high level overview of the CARP hardware platform extended with a readout module. While the system has been extended with new functionality and partially ported to Chisel, the overall architecture of the system has been largely preserved. In Figure 5.2, a more detailed view of the system is shown. Modules are annotated with either a C(hisel) or a V(HDL) in the upper right corner to indicate their porting status. The top level logic and wiring gluing all the modules together is all done in Chisel.

Figure 5.1: Block diagram of the CARP hardware architecture extended with a readout layer.

and detailed interfaces are ommited for clarity. annotated are implemented in the same language as their parent modules. Signals indicate flow of data or direction of communication, control signals in the upper right corner are implemented in / have been ported to Chisel, while those annotated with a V are implemented in VHDL. Child modules not Figure 5.2: Modified reprint from [22] showing a detailed overview of the CARP architecture and its constituent modules. Modules annotated with a C

#### 5.1 General overview

The CARP hardware system executes instructions in a a Fetch, Decode, Execute loop. Instructions transferred from the host program controlling the coprocessor are placed in the Receive Buffer. The Fetch module reads instructions one at a time from the Receive buffer and either stores them for later use in the Instruction BRAM, or passes them on to the Decode module. The Decode module is responsible for parsing instructions, extracting parameters and orchestrating control signals throughout the rest of the system. In the Execute phase, different modules perform work depending on the type of instruction. The major players in the Execute phase are the Development, Cellular Automaton and Readout modules.

The system operates in a pipelined fashion, with Fetch, Decode and Execute being separated stages. Since few of the modules in each stage complete in the same number of clock cycles, modules are interlocked to ensure consistency and to avoid hazards. At the top level, this is implemented using two signals, Run and Done. Each module receives the Run signal as an input, indicating wether or not it is safe to execute. When a module is completes its work, it sets its Done signal high. To interlock a group of modules, the run signal is determined by the logical And operation of the done signals of all the modules.

Cell types and states are stored in the Cell Storage BRAMs, ready to be used either in development, where they are used to determine further growth and change to the organism they constitute, or in the cellular automaton, which simulates the behavior of the organism.

The following sections describe the additions and changes made to the system to add support for a reconfigurable Readout module based on a spiking neural network.

#### 5.2 Communication

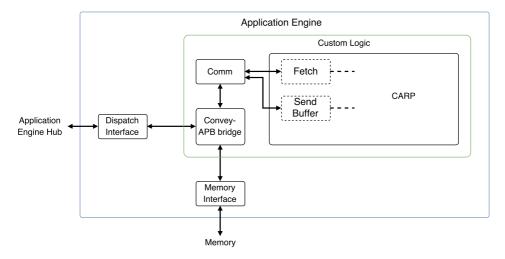

As outlined in section 4.1, the FPGA on the Convey coprocessor is logically divided into Application Engines within which any custom logic can be implemented. Each AE can communicate with the host, the on-board memory and other AEs through various interfaces implemented by the Convey PDK, shown in Figure 5.3. To be able to run the CARP hardware platform on the coprocessor, the communication module has been reimplemented to utilize these interfaces for data transfer.

Figure 5.4 shows how the CARP hardware is implemented within the Convey AE architecture. The communication module has been moved out of the main CARP module and rewritten from scratch. In an effort to decouple the CARP platform from the underlying hardware and its communication interfaces, the new module exposes two very generic interfaces facing "outward," an Advanced Peripheral Bus (APB) <sup>1</sup> and a memory bus, as shown in Figure 5.5. These are specified fully in Appendix A. Using generic interfaces with established conventions that are easy to connect to other communication interfaces

<sup>&</sup>lt;sup>1</sup>http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ihi0024c/ index.html (Requires registration)

Figure 5.3: Overview of the Convey Application Engine architecture.

makes it easy to move the system to a different platform, should the Convey coprocessors become obsolete or defunct.

Figure 5.4: Implementation of the CARP platform within the AE architecture.

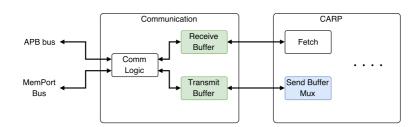

To avoid having to rewrite the Fetch and Send Buffer Mux modules inside CARP, the new communication module provides the same interface towards them as the old one did; two data buffers, transmit and receive, buffer count signals and read/write enable signals. Both data buffers are implemented as FIFO-queues with counter registers and ready-valid access interfaces.

Figure 5.6 shows the state machine controlling the operation of the communication mod-

**Figure 5.5:** The communication module interfaces with the CARP platform through two buffers, transmit and receive. Outwards, the communication module exposes two buses, an APB bus and a generic memory interface.

Figure 5.6: State machine controlling the communication module.

ule. From the idle state, a transition to either the Write or Read states can be triggered by asserting the PSEL signal on the APB bus. Depending on wether or not the PWRITE signal is asserted, the state machine will transition into the corresponding state. In this case, write refers to writing data from the host to the receive buffer, and read refers to reading data from the transmit buffer to the host. In the Write state, three bits in the PADDR signal is used to further determine what is to happen. The possible actions are as follows:

- 1. Write PWDATA to Receive Buffer. Transition to Idle state.

- 2. Set starting address register to PWDATA. Transition to Idle state.

- 3. Set end address register to PWDATA. Transition to Idle state.

- 4. Prepare to start transferring data from memory to Receive Buffer. Transition to Write Memory state.

In the Write Memory state, read requests are generated on the MemPort bus and received data is stored into the Receive Buffer. The Read and Read Memory states have similar functionality, but writes data from the Transmit Buffer either directly to the APB bus or to memory. In general, transfers of five 32-bit words or less are done via the APB, while larger transfers go via memory. This is however something that is specified in the SDK, not implemented in hardware. That means that the system can be implemented to run on platforms without on-board memory, as the MemPort interface can simply be tied off in that case.

The ConveyApbBridge-module serves, as the name implies, as a bridge between the in-

terfaces provided by the Convey PDK and the Communication module. The Dispatch interface drives the APB bus, while the Memory Controller interface is wired against the MemPort.

#### 5.3 Readout

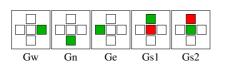

The Readout module extends the CARP platform with a reconfigurable Spiking Neural Network operating in a data-driven fashion, synchronized to the clock of state steps performed in the Cellular Automaton. Each layer of the network is implemented as a stage in a pipeline. With every step of the CA, new input is fed to the input layer and its output is fed as input to the next layer and so on throughout the network. In other words, the number of state steps it takes for data to propagate through the readout module as a whole is equal to the number of layers in the network. The output from the final layer is routed back into the CA. It is also stored in the Readout Buffer, from where it can be read back to the host.

Figure 5.7: Logical overview of the Readout module.

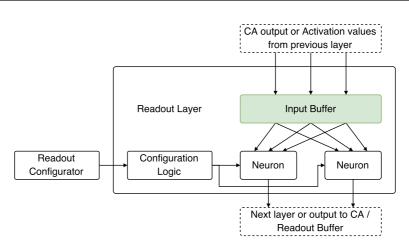

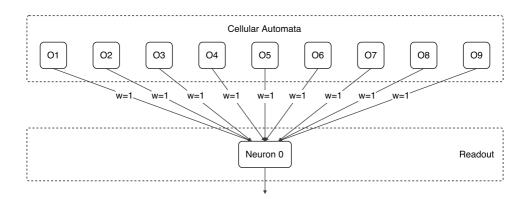

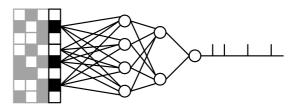

Figure 5.7 shows, at a high level of abstraction, how the Readout module is connected to the CARP system as whole. A subset of cell states are routed out of the CA and into the Readout module as input to the first layer of the network, the input layer. Within each layer, a number of neurons process the input to the layer, as shown in Figure 5.8. Based on this input, they update their activation values, which again are fed to the next layer to be used as input to those neurons in the next step.

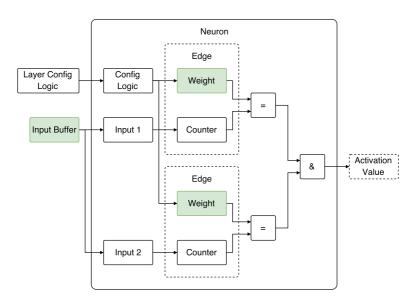

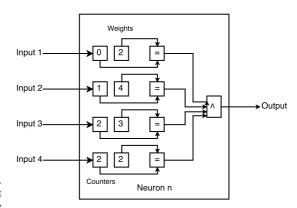

The activation value of a neuron can be either 0 or 1, based on a very simple calculation, as shown in Figure 5.9. For each of its incoming edges, a neuron has a pair of registers, the edge weight and a counter. The counter keeps track of how many spikes the neuron has received via the corresponding edge, and the weight is a threshold, indicating how many spikes must arrive via the edge before the neuron can fire. When all counters values are equal to or greater than their weights, the neuron fires and the counters are reset.

To reduce the amount of resources required for the implementation, some restrictions apply with regards to which network topologies are possible to implement. All networks must

Figure 5.8: Logical overiew of one network layer in the Readout module.

be entirely feed-forward, that is they can not contain any recurrent connections, the total number of neurons can not exceed  $2^{16} - 1$  and the final layer must contain only a single neuron. The topology of a network is given as a parameter to the module at synthesis time, and can not be reconfigured while the system is running. It describes how many layers the network consists of and how many neurons each of them consist of. Networks are also implemented fully connected, all neurons in a layer are connected to all neurons in the previous layer.

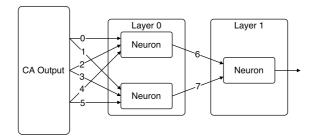

The module can be in one of two states, the default Processing state and the Configuration state. In the Processing state, data flows through the network in the manner described above. As mentioned, the topology of the network is defined at synthesis time. The weights however, can be reconfigured while the system is running. This allows for rapid exploration of networks with different characteristics. The transition to the Configuration state is triggered when the Readout module receives a WriteWeight instruction from the Decode module. Accompanying the instruction is a payload consisting of a 16-bit address and an 8-bit weight value. Figure 5.10 shows an example of how edges and their corresponding weight registers are addressed, starting from address 0 in the top left, increasing top to bottom between the CA output and the first layer, then continuing from the top in the next.

A WeightWrite instruction completes the same clock cycle it is received, returning the module to the Processing state in the subsequent cycle. This is done by wiring the weight bus directly into each neuron and decoding the address value using entirely combinatorial logic to decide which weight should be updated. At the top level, the address is used to decide into which layer the weight should be written. That layer then receives a high write enable signal and the address of the weight within the layer. Similarily, the targeted layer, uses this address to find the neuron to which the targeted weight belongs and passes the write enable signal into it along with the address of the weight within that neuron. The neuron asserts write enable for the targeted register which will then contain the new weight value the subsequent clock cycle.

Figure 5.9: Logical overview of a single neuron in the Readout module.

Figure 5.10: Example of how edges/weights are addressed counting from left to right, top to bottom.

With the configuration in Figure 5.10 as an example; a WriteWeight instruction arrives with the address 7 in the payload. At the top level, the module knows that addresses in the range [6,7] belong to Layer 1. The address of the targeted weight within that layer is found by subtracting the total number edges between all previous layers from the global address, i.e. 7 - 6 = 1. Inside that layer, the correct neuron is found by utilizing the fully connected nature and calculating *Addr* div *NeuronsPreviousLayer*. The address of the weight within that neuron is calculated with *Addr* mod *NeuronsPreviousLayer*. In this example, the only neuron in the layer receives the weight address 1 and updates the correct weight accordingly.

#### 5.4 Cellular Automaton

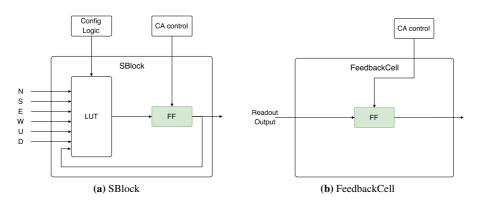

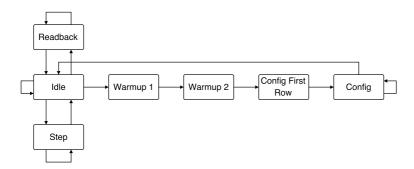

Alongside the Development and Readout modules, the Cellular Automaton module forms the core of the CARP system. It is responsible for simulating the dynamic behavior of and interaction between cells. The CA module has been partially ported to Scala and modified to support routing live cell states out of the SBlock Matrix and feedback from the Readout Module back in. To achieve this, the top-level logic responsible for orchestrating configuration of the SBlock Matrix and the matrix itself have been reimplemented from scratch in Chisel, while the Live Count related modules remain unchanged and are still implemented in VHDL.

Figure 5.11: The Cellular Automaton module and surrounding modules.

As shown in Figure 5.11, the central part of the CA module is the SBlock Matrix, a 2D/3D matrix of modules connected in a regular grid. The modules can be either an SBlock or a FeedbackCell. An SBlock uses the states of the the cells in its von Neumann neighborhood as input to a configurable Look-Up-Table (LUT) and updates its own state, stored in a Flip-flop (FF), with the output from the LUT. A FeedbackCell on the other hand, receives only the output from the Readout module as input and updates its state with this value. Both are shown in Figure 5.12. State updates happen synchronously throughout the matrix, all cells march in step so to speak. At synthesis time, the SBlock Matrix utilizes two lists of coordinates, one indicating which cells should be FeedbackCells, and one indicating which cells should be routed out of the module to be wired as input to the Readout module. All cells not in the FeedbackCells list will be instantiated as SBlocks.

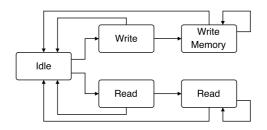

The state machine in Figure 5.13 controls the operation of the CA module. Starting from the Idle state, the module can transition into one of three states based on instructions received from the Decode module. In the Configuration state, the SBlocks in the SBlock Matrix are configured one row at a time. LUTs are configured with different values depending on the cell type of the cell the SBlock simulates. FeedbackCells are not configurable and can not develop into a different cell type, so they are simply ignored with regards to LUT

Figure 5.12: Detailed view of the SBlock and FeedbackCell modules used in the SBlock Matrix.

configuration. The state of each cell is also read from Cell Storage and configured into FFs.

In the Readback state, the state of each cell is read back to the Cell Storage. Similar to configuration, this happens row by row.

The Step state is the core functionality of the CA module. Here, all cells/SBlocks synchronously update their states. The instruction also includes a 16-bit number in its payload, indicating how many steps to perform in bulk. When a step has completed, a signal is sent to the Readout module indicating that it should perform one step of its pipeline, and start processing the new cell states it has received.

Figure 5.13: State machine controlling the operation of the CA module.

While the Live Count and Fourier Transform modules implemented by Lundal have not been used in the work presented in this thesis, they have been left unchanged and functional for possible future use.

#### 5.5 Miscelaneous Modules

In addition to the major additions and changes to the system outlined in the previous sections, several smaller changes have been made throughout the system to accomodate the new functionality.

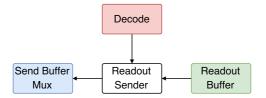

#### 5.5.1 Readout Sender

The Readout Sender is a small module added to facilitate transferring Readout output data from the Readout Buffer to the host. It receives instructions from the Decode module and places data in the Transfer Buffer of the Communication module via the Send Buffer Mux. A single ReadReadout instruction causes 32 words to be transferred.

Figure 5.14: The readout sender orchestrates transfers of readout-data to the host.

#### 5.5.2 Decode

The Decode module is responsible for parsing instructions, setting control signals and passing instruction parameters to modules. It has been extended to support the two new instructions. For the ReadReadout instruction, it signals the Readout Sender to initialize a transfer, as well as setting the necessary control signals to the Send Buffer Mux to allow data from the Readout Sender to pass through to the Transfer Buffer. In the case of a WriteWeight instruction, the address and weight value parameters are extracted from the instruction payload passed on to the Readout module along with the control signals indicating that a weight should be updated.

#### 5.5.3 Information Sender

Parameterization has been used extensively throughout the CARP hardware system to allow for as much flexibility as possible. To avoid having to update the software API every time the system is synthesized with new parameters, Lundal introduced the Information Sender, a module that allows the API to query the hardware for information. When a Read-Information instruction is issued, it places a number of system parameters into Transfer Buffer; CA size, wether or not wrapping is enabled, number of bits per cell state and type, control flow counter sizes, maximum number of development rules and information about the fitness module. The module has been extended to also include information relating to the Readout module. The added parameters are; number of network layers in the Readout topology, number of output cells from the CA, and the number of neurons in each network layer. Since the system can be synthesized with any number of network layers, the total size of the payload generated by the Information Sender will depend on this number.

#### 5.6 Parameterization

Many aspects of the CARP hardware platform are parameterized. With the introduction of the Readout module, a few new parameters have been added. Readout Buffer size, Readout Weight Bits and Readout Address Bits are integer values controlling bus widths and buffer sizes. The CA Output Cells and CA Feedback Cells parameters are lists of (z, y, x) coordinate triplets indicating the location of output and Feedback cells respectively. The Readout Topology parameter determines the number of network layers and number of neurons in each. For instance, Readout Topology value of (10, 5, 3, 2, 1) will result in a 5 layer network with 10 neurons in layer 0, 5 in layer 1, 3 in layer 2, 2 in layer 3 and 1 neuron in the output layer. A full list of parameters is given in Table 5.1.

To leverage the strengths of Chisel and the Object-Oriented aspects of the underlying Scala, parameters have been organized into an interface (or trait in Scala jargon), CarpParameters. This allows for more flexibility in expressing the more complicated parameters such as CA Output Cells and CA Feedback Cells.

#### 5.7 Software API

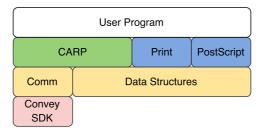

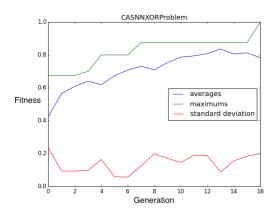

The CARP software API provides a clean and structured interface into controlling and utilizing the functionality implemented in the hardware part of the system. Figure 5.15 shows how the API is structured. The main part, indicated in green, provides functions for connecting to, resetting, sending instructions to and receiving data from the platform. The two optional modules, Print and PostScript, provide utilities for visualizing the datastructures used in the API.