## Implementation of a Hardware Ray Tracer for digital design education

Jonas Agentoft Eggen

Master of Science in Electronics Submission date: June 2017 Supervisor: Øystein Gjermundnes, IES

Norwegian University of Science and Technology Department of Electronic Systems

# Assignment text

- Examples of how to efficiently implement a large range of mathematical operations in hardware.

- Understanding how the Hardware Ray Tracer can be integrated into a larger SoC together with CPU, display controller and memory controller.

#### Project thesis "Design of a Hardware Ray Tracer for digital design education"

In the project thesis "Design of a Hardware Ray Tracer for digital design education" submitted December 2016 by NTNU student Jonas Agentoft Eggen modelling and design exploration of a hardware ray tracer was described. Through extensive design exploration with constant refinement of the model Eggen arrived at a proposal for the architecture, instruction set and microarchitecture for a scalable multicore ray tracer. As a part of this work, Eggen carried out analysis of numeric precision, throughput, and scalability of the multicore system.

#### Master thesis description

In this master thesis, the goal is to refine the microarchitecture for the ray tracer core proposed in the project thesis, propose an interconnect that scales well with the number of cores, write RTL code, verify the design and synthesize the design targeting a Xilinx Zynq-7000 FPGA. Extract examples from the thesis work that helps demonstrating important aspects of digital design.

## Abstract

Digital design is a large and complex field of electronic engineering, and learning digital design requires maturing over time. The learning process can be facilitated by making use of a single learning platform throughout a whole course.

A learning platform built around a hardware ray tracer can be used in illustrating many important aspects of digital design. A unified learning platform allows students to delve into intricate details of digital design while still seeing the bigger picture. Effects of changing parameters at a low level in the ray tracer design can be seen at the top-level straight away. This kind of fast feedback can help keep students motivated through the learning process.

Throughout this thesis, many interesting examples of both assignments and student discussions are presented. These cover topics such as technology dependent optimisations, low power design techniques, verification and means of accelerating the design process. The combination of these examples and the implementation effort in this thesis is a good starting point for a learning platform.

Ray tracing is a parallel problem well suited for processing in a multi-core architecture. Here, a system that can be synthesised with a parameterisable number of processing cores is proposed. Each of the cores interleave processing of rays using fine-grained multithreading. Large parts of the system have been implemented using the SystemVerilog hardware description language. Tools used in exploring the impact of architectural changes have been developed and results from these are discussed. The implementation is verified through simulations and partly using formal methods. Synthesis results for a Xilinx Zynq SoC are presented and discussed.

Simulation and synthesis results indicate that the ray tracer can render a VGA frame at 25 frames per second in a 32-core configuration. This configuration utilises  $\sim 77~\%$  of the LUTs on the target FPGA, leaving room for additional logic on the device.

iv

# Sammendrag

Digitaldesign er et stort og komplekst felt innen elektronikk. Det å lære digitaldesign krever modning over tid. Læringsprosessen kan lettes ved å benytte én enkelt læringsplattform gjennom et helt emne.

En læringsplattform bygget rundt en raytracer kan brukes til å illustrere mange viktige aspekter ved digitaldesign. En enhetlig læringsplattform gjør det mulig for studenter å fordype seg i intrikate detaljer innen digitaldesign samtidig som de kan ha et overblikk over hele systemet. Resultater av parameterendringer på et lavt nivå i raytracerens design kan ses på toppnivå med en gang. Slike raske tilbakemeldinger kan hjelpe studenter med å holde motivasjonen oppe gjennom læringsprosessen.

Gjennom hele oppgaven presenteres mange interessante eksempler på både oppgaver og studentdiskusjoner. Disse dekker emner som teknologiavhengige optimaliseringer, energisparingsteknikker, verifisering og metoder for å effektivisere designprosessen. Kombinasjonen av disse eksemplene og arbeidet med implementasjonen i denne oppgaven gir et godt utgangspunkt for en læringsplattform.

Raytracing er et parallelliserbart problem godt egnet for prosessering med en flerkjernearkitektur. Her foreslås et system som kan syntetiseres med et parameteriserbart antall kjerner. Hver kjerne prosesserer stråler (rays) med finkornet (fine-grained) multithreading. Store deler av systemet er blitt implementert i SystemVerilog. Verktøy for å undersøke virkninger av arkitektoniske endringer er utviklet og resultater fra disse diskuteres. Implementasjonen er verifisert gjennom simuleringer og delvis ved hjelp av formelle metoder. Synteseresultater for en Xilinx Zynq SoC presenteres og diskuteres.

Resultater fra simuleringer og syntese indikerer at raytraceren kan generere 25 bilder i sekundet gitt en 32-kjerners konfigurasjon. Denne konfigurasjonen bruker $\sim 77\,\%$ av LUTene på FPGA<br/>en. Dette betyr at det er plass til øvrig logikk på enheten.

vi

# Preface

This master's thesis has been written during the spring semester of 2017 at the Department of Electronic Systems, Norwegian University of Science and Technology (NTNU). The work has been done in collaboration with ARM. The thesis accounts for the full workload of the final semester at NTNU.

The interesting nature of digital design and computer graphics has been a major motivation in my work with this thesis. These are both areas that have experienced huge growth the last few decades, and will continue to play an important role in the world for many years to come. Furthermore, I have found working with the technical intricacies encountered very rewarding. I hope the teaching platform will trigger some of the same feelings in students once it is finished.

I would like to thank my supervisor Øystein Gjermundnes for his support and continued enthusiasm regarding technical problems of any size as well as results I have presented throughout this last year.

Thanks to Silja for being so nice.

viii

# Contents

| 1        | Intr | roduction & Motivation 1                                                                                |

|----------|------|---------------------------------------------------------------------------------------------------------|

|          | 1.1  | Main contributions                                                                                      |

|          | 1.2  | Thesis outline                                                                                          |

| <b>2</b> | Bac  | kground 5                                                                                               |

|          | 2.1  | Ray tracing                                                                                             |

|          | 2.2  | Number representations $\ldots \ldots 7$ |

|          |      | 2.2.1 Fixed-point representation                                                                        |

|          |      | 2.2.2 Floating-point representation                                                                     |

|          | 2.3  | Design                                                                                                  |

|          |      | 2.3.1 Design process                                                                                    |

|          |      | 2.3.2 Clock gating                                                                                      |

|          |      | 2.3.3 False paths                                                                                       |

|          | 2.4  | Verification                                                                                            |

|          | 2.5  | ZedBoard                                                                                                |

|          | 2.6  | Interconnect                                                                                            |

|          |      | 2.6.1 AXI                                                                                               |

|          |      | 2.6.2 APB                                                                                               |

|          |      | 2.6.3 Ready/valid handshaking $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 11$       |

| 3        | Req  | uirements 13                                                                                            |

| <b>4</b> | Pro  | ject thesis summary 17                                                                                  |

|          | 4.1  | Top-level system block diagram                                                                          |

|          | 4.2  | Ray tracer block diagram 19                                                                             |

|          |      | 4.2.1 Ray datapath                                                                                      |

|          | 4.3  | Project thesis results                                                                                  |

|          | 4.4  | Future work                                                                                             |

| <b>5</b> | Des | ign pr  | ocess                                      | <b>23</b> |

|----------|-----|---------|--------------------------------------------|-----------|

|          | 5.1 | Syster  | m-level design                             | 24        |

|          |     | 5.1.1   | Ray tracer                                 | 24        |

|          |     | 5.1.2   | Dual core array                            | 25        |

|          |     | 5.1.3   | Dual core                                  | 27        |

|          |     | 5.1.4   | Instruction memory                         | 28        |

|          |     | 5.1.5   | Object buffer                              | 28        |

|          | 5.2 | Threa   | d interleaving                             | 31        |

|          | 5.3 | Ray c   | ore                                        | 34        |

|          |     | 5.3.1   | Commands and statuses                      | 34        |

|          |     | 5.3.2   | Ray request handler                        | 36        |

|          |     | 5.3.3   | Ray result handler                         | 36        |

|          | 5.4 | Ray d   | latapath                                   | 37        |

|          |     | 5.4.1   | Instruction set                            | 37        |

|          |     | 5.4.2   | Fixed-point to floating-point conversion   | 42        |

|          |     | 5.4.3   | Floating-point to integer conversion       | 43        |

|          |     | 5.4.4   | Further optimisations                      | 43        |

|          |     | 5.4.5   | Block diagram                              | 44        |

|          | 5.5 | Floati  | ing-point unit                             | 46        |

|          |     | 5.5.1   | Required features                          | 46        |

|          |     | 5.5.2   | Modelling                                  | 47        |

|          | 5.6 | Imple   | mentation                                  | 48        |

|          |     | 5.6.1   | RTL                                        | 48        |

|          |     | 5.6.2   | Assembler                                  | 49        |

|          |     | 5.6.3   | Verification strategy                      | 50        |

|          | 5.7 | Synth   | esis                                       | 54        |

|          |     | 5.7.1   | Floating-point units                       | 54        |

|          |     | 5.7.2   | False path elimination                     | 55        |

|          |     | 5.7.3   | Synthesis of dual core array               | 56        |

|          |     | 5.7.4   | Increasing clock frequency                 | 58        |

|          |     | 5.7.5   | Summary                                    | 59        |

|          | 5.8 | Perfor  | rmance and scalability                     | 60        |

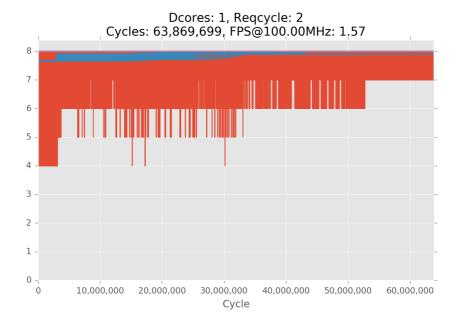

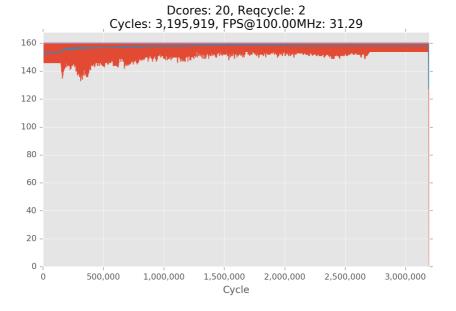

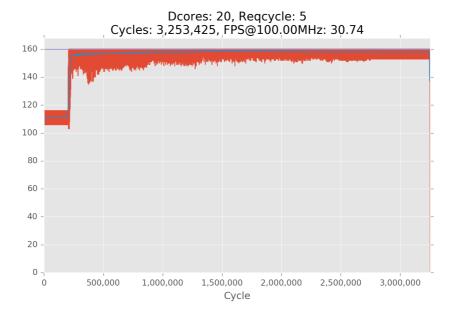

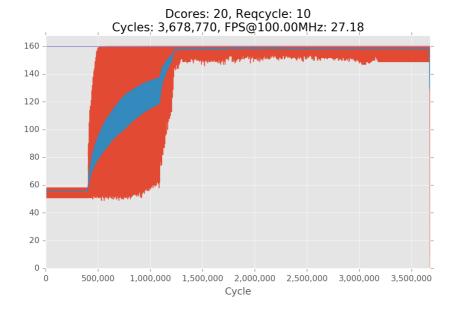

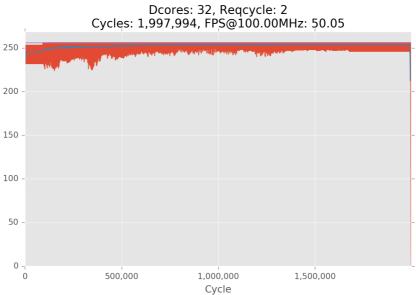

|          |     | 5.8.1   | Thread activity over time                  | 61        |

|          |     | 5.8.2   | Effects of varying ray manager performance | 64        |

|          |     | 5.8.3   | System performance                         | 67        |

| 6        | Lea | rning ] | platform viability                         | 69        |

|          | 6.1 | Regist  | ter file example                           | 70        |

| 7        | Cor | nclusio | n                                          | 71        |

|          | 7.1 | Future  | e work                                     | 72        |

х

| CONTENTS |

|----------|

|----------|

| Bi           | bliog                           | raphy                                                                                                                | 75                              |

|--------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Α            | A.1<br>A.2                      | hitecture specification         Data structures         Message formats         Ray manager control/status registers | 81                              |

| В            | Ass                             | embly code                                                                                                           | 83                              |

| С            | C.1                             | ulation and synthesis results<br>Simulation results                                                                  |                                 |

| D            | Atta                            | achment overview                                                                                                     | 107                             |

|              | D.2<br>D.3<br>D.4<br>D.5<br>D.6 | Design files                                                                                                         | 108<br>108<br>109<br>109<br>110 |

| $\mathbf{E}$ | Cov                             | erage report                                                                                                         | 111                             |

xi

### CONTENTS

xii

# List of Figures

| 2.1  | Ray tracing visualised                                                 | 6  |

|------|------------------------------------------------------------------------|----|

| 2.2  | Example of fixed-point format                                          | 7  |

| 2.3  | IEEE Standard 754 Single-precision floating-point format               | 8  |

| 2.4  | Example used in illustrating a false path                              | 9  |

| 2.5  | Ready/valid handshaking example                                        | 11 |

| 4.1  | Top-level system block diagram                                         | 18 |

| 4.2  | Old ray tracer block diagram                                           | 19 |

| 4.3  | Old core datapath                                                      | 21 |

| 4.4  | Scene rendered using ISA-simulator                                     | 22 |

| 5.1  | Ray tracer block diagram                                               | 24 |

| 5.2  | Dual core array                                                        | 25 |

| 5.3  | Dual core                                                              | 27 |

| 5.4  | Instruction memory interface example waveform                          | 28 |

| 5.5  | Block diagram of object buffer                                         | 29 |

| 5.6  | Object buffer interfaces example waveform                              | 30 |

| 5.7  | Ray core block diagram                                                 | 34 |

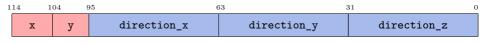

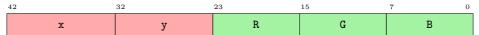

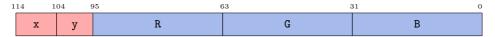

| 5.8  | Ray request format                                                     | 36 |

| 5.9  | Ray result format                                                      | 36 |

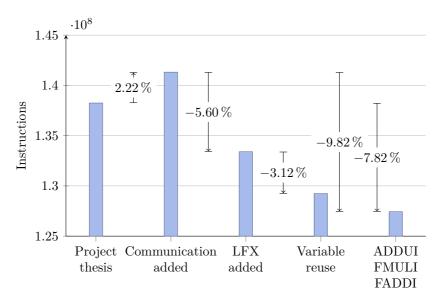

| 5.10 | Comparison of different ISA revisions                                  | 41 |

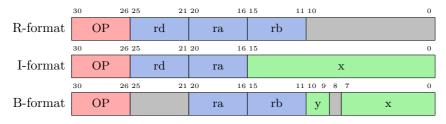

| 5.11 | Instruction formats                                                    | 42 |

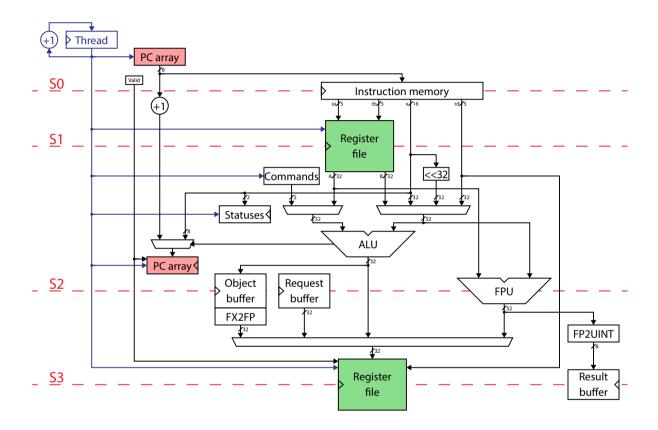

| 5.12 | Ray datapath                                                           | 45 |

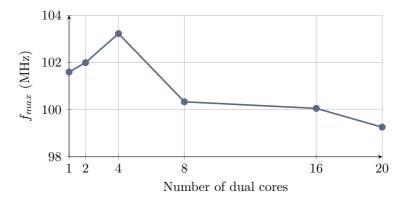

| 5.13 | Maximum clock frequency for different number of cores                  | 56 |

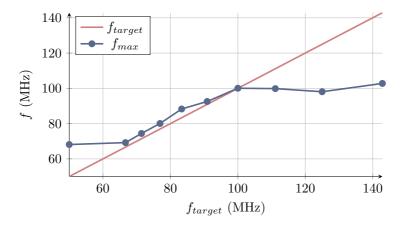

| 5.14 | Maximum clock frequency for different target frequencies               | 57 |

| 5.15 | Illustration of new pipeline stage placement                           | 58 |

| 5.16 | Instructions executed per pixel                                        | 60 |

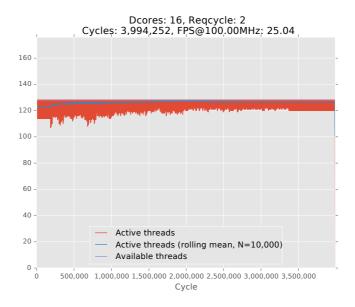

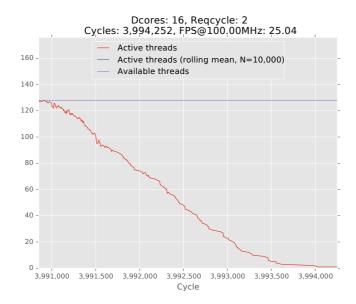

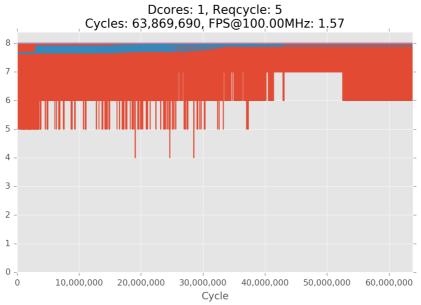

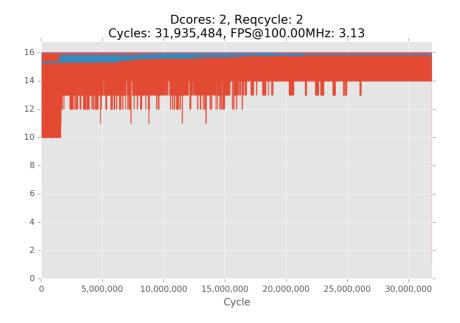

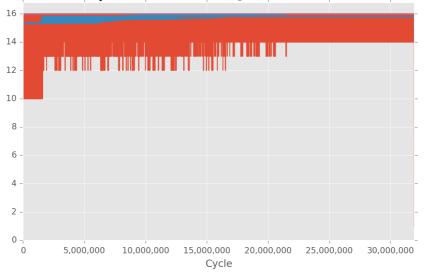

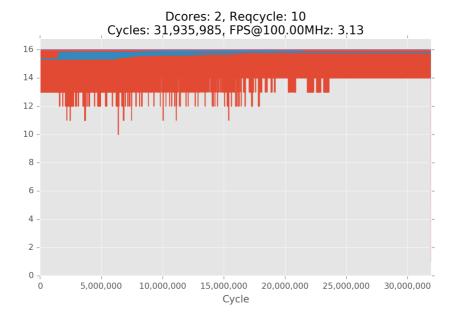

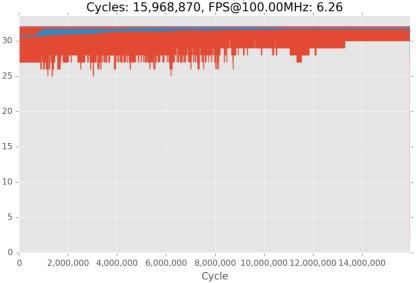

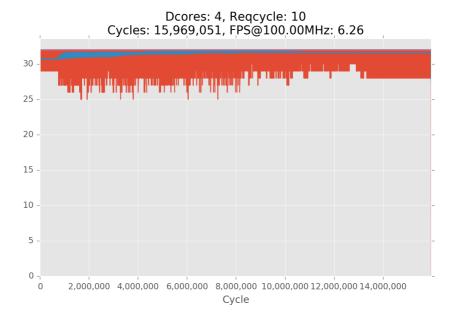

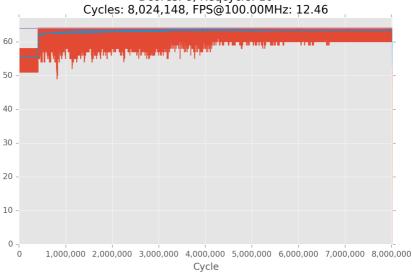

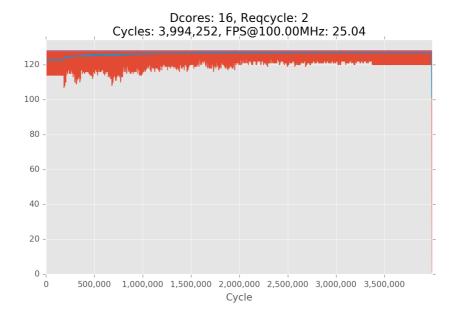

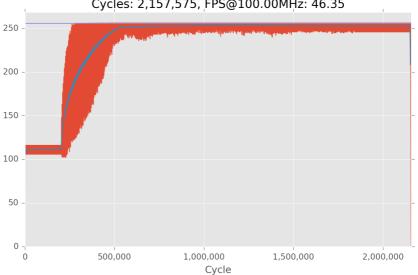

| 5.17 | Number of active threads vs. time for 16 dual cores                    | 62 |

| 5.18 | Number of active threads vs. time for 16 dual cores (zoomed) $\ . \ .$ | 63 |

|      |                                                                        |    |

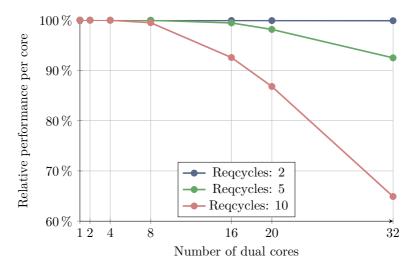

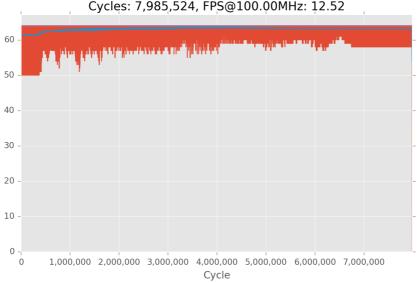

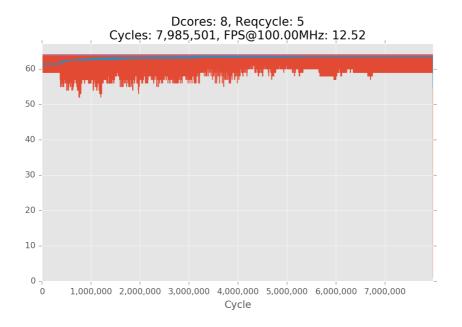

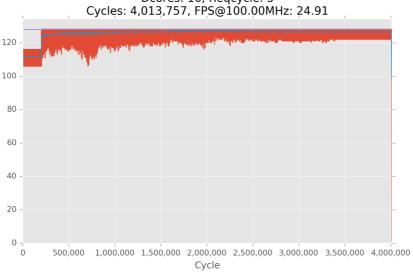

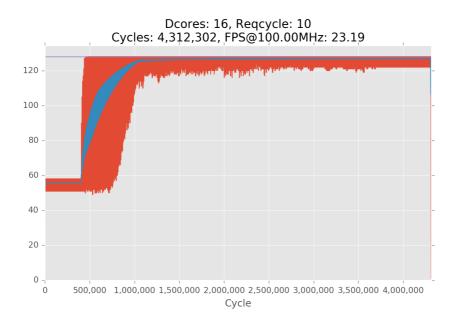

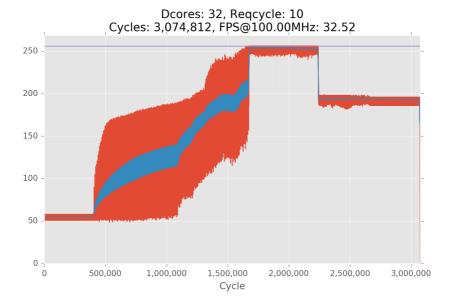

| 5.19 | Relative performance per core given different 'reqcycles' 66 |

|------|--------------------------------------------------------------|

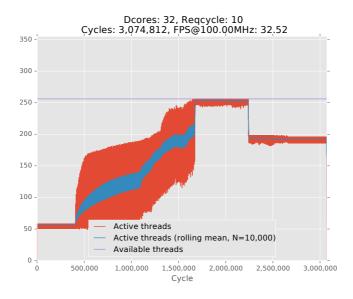

| 5.20 | Number of active threads vs. time for 32 dual cores          |

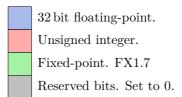

| A.1  | Data structures legend                                       |

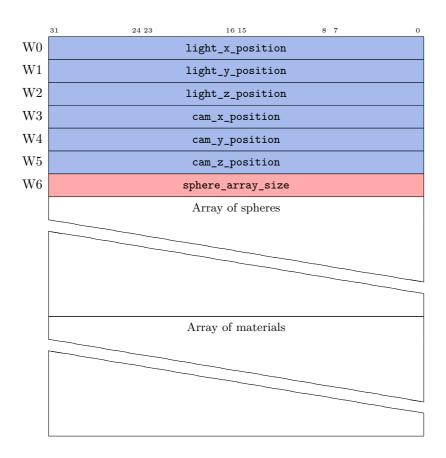

| A.2  | Scene descriptor                                             |

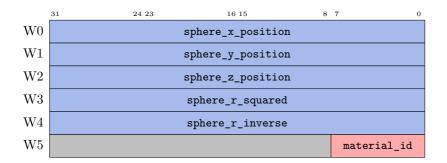

| A.3  | Sphere descriptor                                            |

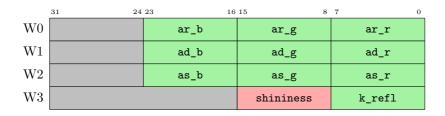

| A.4  | Material descriptor                                          |

| A.5  | Object buffer memory layout 80                               |

| A.6  | Ray request                                                  |

| A.7  | Ray response                                                 |

| A.8  | Command register                                             |

| A.9  | Status register                                              |

| A.10 | Scene address register                                       |

| C.1  | Legend for all plots of active threads vs. time              |

# List of Tables

| 3.1 | Legend for requirement tables                             | 3 |

|-----|-----------------------------------------------------------|---|

| 3.2 | Requirements for the specification document               | 4 |

| 3.3 | Requirements for the Hardware Ray Tracer                  | 5 |

| 4.1 | Old instruction set                                       | 0 |

| 5.1 | Illustration of thread interleaving                       | 2 |

| 5.2 | Commands                                                  | 5 |

| 5.3 | Statuses                                                  | 5 |

| 5.4 | Table for thread state tracking                           | 5 |

| 5.5 | Instruction set                                           | 8 |

| 5.6 | Alterations of instruction set                            | 9 |

| 5.7 | Resource usage of synthesised dual core array 5           | 6 |

| 5.8 | FPS per dual core                                         | 7 |

| B.1 | Comparison of different ISA revisions                     | 3 |

| C.1 | Number of clock cycles needed to render one VGA frame 9   | 3 |

| C.2 | Number of LUTs for different target frequencies           | 5 |

| C.3 | Synthesised frequency for different target frequencies 10 | 5 |

|     |                                                           |   |

xvi

# List of Learning examples

| 5.1  | Avoiding routing congestion   | 26 |

|------|-------------------------------|----|

| 5.2  | Performance density           | 27 |

| 5.3  | Improving energy efficiency 2 | 29 |

| 5.4  | Dependency removal            | 32 |

| 5.5  | Register file implementation  | 32 |

| 5.6  | Assertions                    | 35 |

| 5.7  | Hardware/software codesign    | 13 |

| 5.8  | Decrement and branch          | 14 |

| 5.9  | Sign of add/sub result        | 17 |

| 5.10 | Technology independence 4     | 18 |

| 5.11 | Behavioural models            | 19 |

| 5.12 | Single source of constants 4  | 19 |

| 5.13 | Formal verification           | 51 |

| 5.14 | Limitations of code coverage  | 53 |

| 5.15 | Resource sharing 5            | 55 |

| 5.16 | False path elimination 5      | 55 |

| 5.17 | Proper analysis               | 34 |

LIST OF TABLES

xviii

## Acronyms

ALU arithmetic logic unit.

APB Advanced Peripheral Bus.

ASIC application-specific integrated circuit.

AXI Advanced eXtensible Interface.

${\bf BRAM}\,$  block RAM.

${\bf CPU}$  central processing unit.

**DSP** digital signal processing.

EDA electronic design automation.

**FF** flip-flop.

${\bf FPGA}\,$  field-programmable gate array.

${\bf FPS}\,$  frames per second.

${\bf FPU}$  floating-point unit.

${\bf FSM}$  finite-state machine.

HDL hardware description language.

HDMI high-definition multimedia interface.

**IC** integrated circuit.

Acronyms

**IP** intellectual property.

**IRQ** interrupt request.

**ISA** instruction set architecture.

**LSB** least significant bit.

${\bf LUT}$  look-up table.

LUTRAM LUT/distributed RAM.

MAC multiply-accumulate.

$\mathbf{MADD}$  multiply-add.

NaN not a number.

**PC** program counter.

$\ensuremath{\mathbf{PPA}}$  power, performance and area.

**RAW** read after write.

**RGB** red, green, blue.

${\bf RTL}\,$  register-transfer level.

${\bf SoC}\,$  System on Chip.

**STA** static timing analysis.

${\bf TLM}\,$  transaction-level modeling.

VFPU vector floating-point unit.

**VHDL** VHSIC hardware description language.

**VHSIC** Very High Speed Integrated Circuit.

$\mathbf{X}\mathbf{X}$

## Chapter 1

# Introduction & Motivation

Digital design is a field within electronics that has experienced great growth since the first integrated circuits (ICs) were introduced in the 1960s. Since then, ICs have become ubiquitous, and found in virtually all electronic devices. Competent engineers are vital to keep up the progress in the field. Educating these engineers can be facilitated by making use of one single learning platform throughout a whole course on digital design.

Computer graphics is another field that has come to take a huge part of people's lives. Since the term was first coined in 1960 [The+08], it has found applications in computer aided design, medical imaging, scientific visualisation, video games, special effects in movies and more. Now, with virtual reality on the rise, the demand for more powerful hardware is not showing any sign of decline.

Because of this, designing a learning platform for digital design around a hardware ray tracer is a natural choice. The system complexity is kept at a moderate level, while still demonstrating key concepts of digital design. The learning platform guides students through the phases of digital design, resulting in a system that offers a visual output. A visual output can help motivate students to really understand how the system works, and thus learn digital design. Students that in a few years will be important in defining the technology of tomorrow.

The benefit of a platform of this complexity is that it can be used as an example throughout a whole course. It can be used to demonstrate everything from 'requirement capture, architecture exploration and modelling, specification writing, RTL implementation [to] finally creating a working prototype.' ([Gje17])

This thesis is a continuation of the project thesis 'Design of a Hardware Ray Tracer for digital design education' [Egg16]. In that thesis, a high level functional model was provided [Gje17]. This model was analysed and broken down into more specialised models. The result of this was a system that was partitioned in a way that had a parameterisable number of processing cores. This allowed for scalable performance, and it was found that achieving a frame rate of 24 frames per second (FPS) at VGA resolution required 74 cores when running at 50 MHz. The project thesis concluded by recommending improvements to the design in order to make implementation feasible.

In this master's thesis, improvements to the architecture proposal from [Egg16]. Models developed during the project thesis have been adapted, and used in both performance analyses and in verifying correctness of the register-transfer level (RTL) implementation. RTL for a large part of the system, including the processing elements and their interconnect, has been implemented using SystemVerilog. The RTL has been synthesised for a field-programmable gate array (FPGA) target. The impact of varying important design parameters has been analysed through simulations and synthesis.

## **1.1** Main contributions

The main contributions of this thesis are:

- The specification from [Egg16] has been improved and extended.

- Devised a multi-core architecture where cores are fully utilised due to the use of fine-grained multithreading.

- Implemented RTL for large parts of the system and made an assembler for the instruction set architecture (ISA).

- Simulated and synthesised the RTL.

- Verification of the implementation through simulation.

- Analyses of expected system level performance.

- Learning examples and proposal for use of presented material in a course on digital design.

## 1.2 Thesis outline

Some necessary background theory is given in Chapter 2. It gives an introduction to ray tracing, number representation formats, the digital design process, the targeted development board and interconnect design. Chapter 3 lists the requirements for both the hardware ray tracer and its specification documents. Some of the requirements were addressed during the work on the project thesis, and some are entirely new. Important results from the project thesis are summarised in Chapter 4. Chapter 5 describes the design process of the ray tracer system. Results of design choices are also found in this chapter. This presentation method is chosen as it is in accordance with the design process of a digital system. Anecdotal learning examples are scattered around in this chapter, providing the author's view on various themes. Chapter 6 discusses the viability of this system as a learning platform. An example of how one of the modules in the system can be integrated into a digital design course is also given. Finally, Chapter 7 sums everything up, and lists work that remains before the hardware ray tracer can be used in digital design education.

## Chapter 2

# Background

This chapter presents some background theory that is necessary for the understanding of Chapters 4 and 5. The ray tracing algorithm is introduced. Basics of the fixed-point and floating-point number representations are presented. A short introduction to a typical design flow is given. The ZedBoard development board and interconnects in digital systems are introduced. Sections 2.1 and 2.2 has been taken directly from [Egg16].

## 2.1 Ray tracing

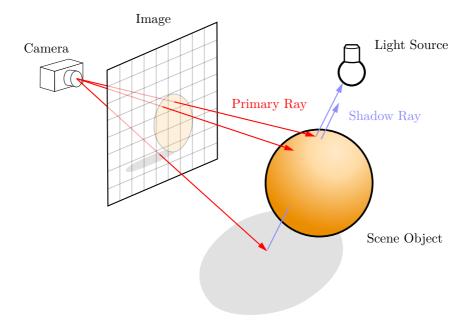

Ray tracing is a rendering algorithm that can produce realistic looking images. It achieves this by tracing light through the image plane, and simulates their interaction with the objects in the scene. A scene refers to a description of objects to be rendered, lighting, camera viewpoint amongst other parameters. The ray tracing algorithm can simulate many optical effects like reflection, refraction, scattering and dispersion.

Figure 2.1 illustrates the basic concepts of the ray tracing algorithm. A primary ray is cast from the camera position through a pixel in the image. Intersection tests against the objects in the scene are performed in order to find the closest intersecting object. A shadow ray is traced towards the light source, to determine if the object is in shadow. A local illumination model is then applied for the hit object. In recursive ray tracing, reflection and refraction rays can then be generated and are traced in the same way. The contributions from each term is then summed and the final pixel colour is returned.

Figure 2.1: Ray tracing visualised [Hen08]

The recursive ray tracing algorithm has been around since 1980 [Whi80]. Since then, a lot of effort has been put into making ray tracing more efficient and feature-rich [Suf07]. The work has mainly focused on improving the runtime of the algorithm in scenes with a large number of objects. A naive implementation of the algorithm will try to intersect any ray with all objects in the scene. This is very inefficient for large scenes, and has been solved by subdividing the scene objects into data structures of objects that are cheap to perform intersection tests on. These data structures allow for a major reduction in the number of needed intersection tests.

### 2.2 Number representations

There exist many ways to represent numbers in digital systems. The choice of representation has a big impact on the design, performance etc. of the system. Here, only fixed-point and floating-point numbers will be considered due to the popularity of those representations. Also, no literature recommending any other number formats for use in ray tracing have been found. For more in-depth coverage of fixed-point and floating-point numbers, refer to [EL04].

#### 2.2.1 Fixed-point representation

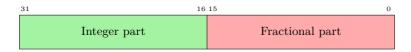

Figure 2.2: Fixed-point format with 16 bit reserved for the integer part, and 16 bit for the fractional part.

Fixed-point numbers represent real numbers using a fixed number of bits before and after the binary point. Figure 2.2 shows a fixed-point format with 16 bit reserved for the integer part, and 16 bit for the fractional part. For signed numbers, one can choose signed number representation freely (i.e. sign-magnitude, two's complement, etc.).

#### 2.2.2 Floating-point representation

Floating-point numbers also represent real numbers. As opposed to fixed-point numbers, the binary point can *float*. This allows for a great dynamic range at

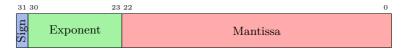

Figure 2.3: IEEE Standard 754 Single-precision floating-point format

the cost of less precision, rounding errors and relatively complex implementation [EL04]. In defining a floating-point system, there are many parameters that must be determined. The IEEE Floating-point Standard 754 [IEEE08] defines the format, rounding modes, special values, operations, gradual underflow and more. The format of a single-precision floating-point number is shown in Figure 2.3.

For normalised values, the number, x, represented by the floating-point format is:

$$x = (-1)^s \times 1.f \times 2^{e-e_0}, \tag{2.1}$$

where s is the sign, f is the mantissa and e is the exponent.  $e_0$  is a bias defined in [IEEE08]. In single-precision numbers  $e_0 = 127$ . For denormal numbers, zero, infinity and NaN, refer to [EL04].

To minimise the complexity of the implementation, one can choose to not implement some features of the standard. Gradual underflow, an expensive treatment of very small numbers, can be avoided by *flushing-to-zero*. Special values like *infinity* and *not a number (NaN)* can also be avoided [VB08]. Choosing a single rounding mode and not implementing exceptions will also keep the cost of implementation low. These optimisations will not only benefit the implementation cost, but the area of the implementation should also be smaller.

For details regarding implementation of floating-point operators, refer to [IEEE08; EL04; Mul+10].

## 2.3 Design

Here, some important aspects of digital design that are covered in this thesis are introduced.

#### 2.3.1 Design process

In designing a digital system, a typical design process often starts with requirement capture. In this phase, requirements for the system are gathered. The results

#### 2.3. DESIGN

of this are both high-level product requirements as well as low-level engineering requirements. Once the requirements are set, an iterative phase of architecture exploration starts. Here, high-level analyses of different possible system architectures are performed. The most promising architectures are then analysed further by e.g. modelling in high-level programming languages. The results from this phase is the high-level models, block diagrams and specifications.

Using the specification from the architecture exploration, RTL code is written. The functional correctness of this code is verified using the methods that will be discussed in Section 2.4. In order to measure the power, performance and area (PPA) of the design, synthesis and simulation of the RTL is performed in this phase.

#### 2.3.2 Clock gating

During the design process, low power design techniques can be applied. A common and easily implemented technique is clock gating. This lowers dynamic power consumption of the design by avoiding excess toggling.

#### 2.3.3 False paths

In static timing analysis (STA), a false path is a timing path that never will be exercised in the final design. Should a false path be one of the critical paths in the system, this can potentially lead to routing congestion and reduced performance.

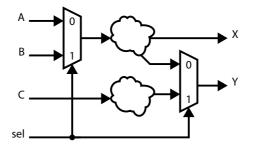

Figure 2.4 can be used to illustrate what a false path is. As the multiplexers in the system are both controlled by the same signal, sel, the path from B to Y is a false path.

Figure 2.4: Example used in illustrating a false path

## 2.4 Verification

Functional verification of the design is an important part of the design process. Following a verification plan, various aspects of the design are exercised. Different techniques are often used in verifying different parts of the design. Simulation based verification uses logic simulation with predefined or randomised inputs to exercise the design. Formal verification is a method where stated properties of the design are mathematically proven to be correct.

For simulation, there exist several metrics that say something about the extent to which the design has been exercised. Code coverage says something about how well various parts of the *code* has been exercised by the testbench, and is supported by most logic simulators. While 100 % code coverage means that all the code in the design has been executed, it does not necessarily imply that all functionality has been fully tested. In verifying this, functional coverage can be used. Functional coverage tells us how well the *functionality* has been exercised. SystemVerilog, and thus most electronic design automation (EDA) tools, implement support for functional coverage.

## 2.5 ZedBoard

The ZedBoard is a development board featuring a Xilinx Zynq System on Chip (SoC) [Avn14]. In addition to this, it is fitted with useful peripherals like 512 MB DDR3 memory, an HDMI transmitter and more.

The SoC on the board is an XC7Z020CLG484-1. This is divided into a *processing* system and a *programmable logic* section [Xil16]. The processing system holds a dual core ARM CPU running at up to 667 MHz. The CPU has a vector floating-point unit (VFPU) for accelerating vector operations. The programmable logic is a regular field-programmable gate array (FPGA). A high-bandwidth AXI interconnect between the sections allows for tight coupling of the two.

### 2.6 Interconnect

In designing or choosing an interconnect, the main goals are often performance and scalability. There are often trade-offs between latency and throughput of the interconnect.

#### 2.6. INTERCONNECT

There are many parameters to a bus protocol. Width of the address, data and control lines play an important role in the performance of the interconnect. Additionally, transfer modes, topologies and arbitration schemes must be designed.

#### 2.6.1 AXI

Advanced eXtensible Interface (AXI) is a high-performance bus standard by ARM. All of Xilinx's intellectual property (IP)-blocks have AXI interfaces. It is often used as the main interconnect in high performance SoCs.

#### 2.6.2 APB

'The APB bus standard defines a bus that is optimized for reduced interface complexity and low power consumption' ([PD10]). Advanced Peripheral Bus (APB) is mainly used for modules with low bandwidth requirements, e.g. status/control registers for peripherals.

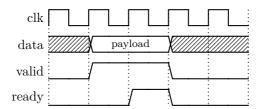

#### 2.6.3 Ready/valid handshaking

Ready/valid handshaking is a commonly used handshaking method in digital systems. It is for instance used in the AXI standard [ARM13]. In the AXI standard, there are many rules for how the handshaking process should go down, but these are not universal for any ready/valid interface. The most important feature of this handshaking method is that data is transferred if the slave is *ready* and the master has *valid* data at a clock edge. This event is referred to as a transaction, whereas the term *accept* refers to both ready and valid being asserted. An example transaction is illustrated in Figure 2.5.

Most blocks in this thesis use ready/valid handshaking for their interfaces.

Figure 2.5: Ready/valid handshaking example

## Chapter 3

# Requirements

Tables 3.2 and 3.3 list the requirements for the specification document and the ray tracer itself. Most of the requirements are taken directly from the project thesis. REQ\_DELIV\_001 and REQ\_DELIV\_002 are the only new requirements in this thesis. The tables indicate whether the requirements have been addressed or not and in which thesis they are addressed. A legend for the symbols used is shown in Table 3.1

Table 3.1: Legend for requirement tables

| Symbol | Description                                                                                                                              |

|--------|------------------------------------------------------------------------------------------------------------------------------------------|

|        | Requirement addressed during project thesis.                                                                                             |

|        | Requirement addressed during project thesis. No additional work done during master to address the requirement.                           |

| •      | Requirement addressed during master's thesis.<br>Requirement addressed during master's thesis. Improvements over<br>project thesis work. |

Table 3.2: Requirements for the specification document

| Requirement ID    | Description                                                                                                                                                                                                                                                                                                    | Project | Master              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------|

| REQ_ARCH_001      | The specification must list all the requirements for the Hardware Ray Tracer.                                                                                                                                                                                                                                  |         | ○ Ch. 3             |

| REQ_ARCH_002      | All datastructures for primitives, colors, rays and materials must be specified.                                                                                                                                                                                                                               |         |                     |

| REQ_ARCH_003      | The specification must explain what Ray Tracing is.                                                                                                                                                                                                                                                            |         | $\bigcirc$ Sec. 2.1 |

| REQ_BSPEC_001     | The specification must describe the functionality of the engine.                                                                                                                                                                                                                                               |         |                     |

| REQ_BSPEC_002     | Microarchitecture must be specified. Use block diagrams and other figures.                                                                                                                                                                                                                                     |         | $\bigcirc$ Ch. 5    |

| $REQ\_BSPEC\_003$ | Interfaces must be described.                                                                                                                                                                                                                                                                                  |         | $\bullet$ Sec. 5.1  |

| REQ_BSPEC_004     | The specification must contain an analysis of performance, quan-<br>tization effects, and scalability. This analysis may involve addi-<br>tional modelling effort. Data from this analysis must prove that<br>the proposed microarchitecture is likely to meet the functional and<br>performance requirements. |         | ○ Sec. 5.8          |

| REQ_ISA_001       | A suitable Instruction Set Architecture (ISA) must be specified.                                                                                                                                                                                                                                               |         | $\bigcirc$ Sec. 5.4 |

| REQ_LEARN_001     | One or more submodules with different complexity that are suitable<br>as examples of various challenges and problems in digital design must<br>be identified.                                                                                                                                                  |         |                     |

| REQ_LEARN_002     | One or more problems regarding the development of the Ray Tracer<br>that has been solved by modelling must be presented.                                                                                                                                                                                       |         | $\bigcirc$ Ch. 5    |

| REQ_LEARN_003     | Propose two solutions for the design of one of the submodules.<br>Explain why one is better than the other.                                                                                                                                                                                                    |         |                     |

| Requirement ID | Description                                                                                                            | Project | Master  |

|----------------|------------------------------------------------------------------------------------------------------------------------|---------|---------|

| REQ_LEARN_004  | Identify or deliberately design sub-optimal performance in the system.<br>Create an assignment/case-study out of this. |         |         |

| REQ_LEARN_005  | Create learning examples for interesting problems encountered during<br>the work with the thesis.                      |         | • Ch. 5 |

### Table 3.3: Requirements for the Hardware Ray Tracer

| Requirement ID | Description                                                                                                                                                                                                                                                                    | Project | Master           |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|

| REQ_FUNC_001   | The Ray Tracer must be able to execute the ray tracer algorithm given by the python model.                                                                                                                                                                                     |         | ○ Ch. 5          |

| REQ_FUNC_002   | The Hardware Ray Tracer must be programmable. It must be easy<br>to change the ray tracer program that is running on the Hardware.                                                                                                                                             |         | $\bigcirc$ Ch. 5 |

| REQ_FUNC_003   | The Ray Tracer must implement the ISA.                                                                                                                                                                                                                                         |         | $\bigcirc$ Ch. 5 |

| REQ_FUNC_004   | The Ray Tracer must support primitives such as spheres and planes<br>as defined in the architecture specification.                                                                                                                                                             | •       |                  |

| REQ_FUNC_005   | The Ray Tracer must support simple animation of frames.                                                                                                                                                                                                                        |         |                  |

| REQ_PERF_001   | The Ray Tracer performance must have a scalable performance from 10 frames per second up to 60 frames per second for scenes with one plane and one sphere rendered with VGA resolution. (This could e.g. be achieved through a system with a parameterizable number of cores). |         | ○ Sec. 5.8       |

| Table 3.3: Requirements | for the | e Hardware Ray | Tracer | (continued) | ) |

|-------------------------|---------|----------------|--------|-------------|---|

|                         |         |                |        |             |   |

| Requirement ID                 | Description                                                                                                                                                                                                                                       | Project | Master                   |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------|

| REQ_PERF_002                   | The utilization of all functional units should be as high as possible<br>and preferably above $50\%$ while the ray tracing algorithm is running.<br>This ensures a high performance to area ratio and an efficient use of<br>available resources. |         |                          |

| REQ_TECH_001                   | The target technology is high end Xilinx FPGAs. The design may contain technology specific optimizations.                                                                                                                                         |         | ○ Ch. 5                  |

| REQ_DELIV_001<br>REQ_DELIV_002 | Write SystemVerilog RTL code for the processing core.<br>Propose an interconnect that scales well with the number of cores.                                                                                                                       |         | ● Sec. 5.6<br>● Sec. 5.1 |

## Chapter 4

# Project thesis summary

This chapter will give a short summary of the project thesis [Egg16]. A lot of the content in this chapter is taken directly from the project thesis. However, all figures are updated for consistency with the rest of the thesis. The architecture specification, where data structures, message formats and control/status registers are specified, can be found in Appendix A. For more details, refer to [Egg16].

The project thesis takes the reader through the process of designing a hardware ray tracer for educational purposes. Ray tracing is a parallel problem, and is well suited for implementation in hardware. This specific ray tracer is not very feature-rich, but still demonstrates important aspects of digital design. An initial Python model was provided by [Gje17] as a starting point for further development. The model was simplified by removing certain features such as refraction and support for rendering other objects than spheres. This reduces the complexity of the system while keeping the educational value.

In order to model different aspects of the system, two additional models were developed. A transaction-level modeling (TLM) model was created to see how well the partitioned system worked. To verify that the ISA could execute the algorithm, an ISA-simulator along with an assembled version of the algorithm was developed. The models and tools developed during the project thesis have been used extensively throughout the work on both the project and master's thesis.

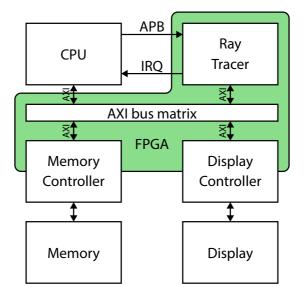

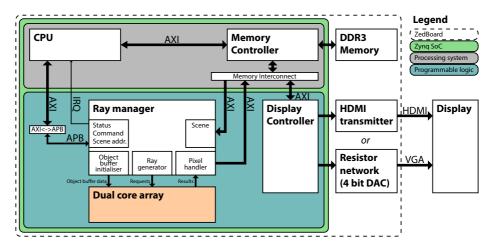

### 4.1 Top-level system block diagram

During the work with the project thesis, the foundation for this master's thesis was laid. An important result is the top-level system block diagram shown in Figure 4.1. This diagram shows the system that the ray tracer will be a part of. Blocks that are contained within the green area will be implemented on the FPGA. Blocks partly in the green area may need to be implemented using additional hardware.<sup>1</sup>

Figure 4.1: Top-level system block diagram

The central processing unit (CPU) generates scenes to be rendered by the ray tracer and saves them in memory. The CPU then commands the ray tracer to render the scene. As the ray tracer renders a scene, the pixels are buffered in memory. Once finished rendering, the display controller will fetch the frame from memory and output it to a display. The CPU can control and read the status of the ray tracer over APB (see commands/statuses in Appendix A.3).

<sup>&</sup>lt;sup>1</sup>This is clarified in Section 5.1.1.

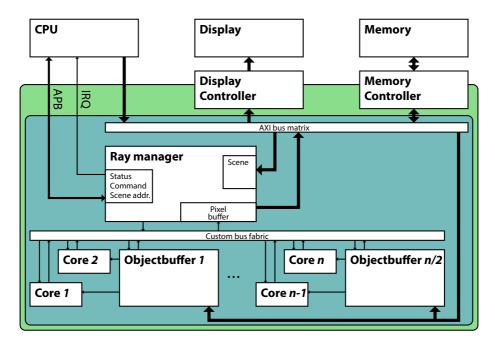

### 4.2 Ray tracer block diagram

Figure 4.2 shows the system-level block diagram designed in [Egg16]. All blocks from Figure 4.1 are still shown, the only difference being that the internals of the ray tracer are displayed in the dark cyan area. The partitioning is a result of inspecting the high-level model. Initial rays are generated by the ray manager, and assigned to the cores that perform the actual ray tracing. During ray tracing, the cores read scene data from the object buffers as needed (see Appendix A.1 for data structures). The ray tracer has a parameterisable number of cores in order to have a scalable performance.

Figure 4.2: Ray tracer block diagram as of [Egg16]. Blocks contained in the green area will be implemented on the FPGA. Blocks contained in the dark cyan area represent the ray tracer.

As discussed, the ray tracer starts rendering once the CPU commands it to start. The CPU does that by telling the ray manager where the scene is located in memory and issuing a *run*-command. Using the scene data, the ray manager will command the object buffers to fetch all objects in memory. When the object buffers are filled, the ray manager will start issuing rays to the cores in the system

using the messages defined in Appendix A.2. Once cores finish tracing a ray, they send the resulting pixel back to the ray manager. The ray manager buffers up a few pixels before sending them to the frame buffer located in memory. After all rays have been traced, the ray manager sends an interrupt request (IRQ) to the CPU. The CPU will then tell the display controller to display the frame before starting the process over for the next frame.

### 4.2.1 Ray datapath

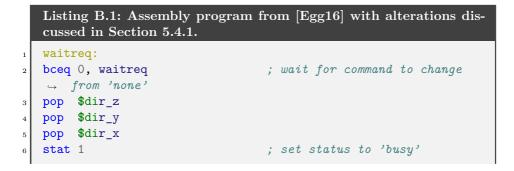

By inspecting the high-level model and taking the partitioning described in Section 4.2 into account, the instruction set shown in Table 4.1 was designed. This was shown to be sufficient to execute the ray tracing algorithm fairly efficiently. Loading of fixed-point data from the object buffers were done in software. Square roots and inverse square roots as well as exponentiations were approximated in software as well. The instruction set is later altered in Section 5.4.1.

| Name                 | Assen  | nbly  |        |      | Operation                                                                                             |

|----------------------|--------|-------|--------|------|-------------------------------------------------------------------------------------------------------|

| Add                  | add 3  | \$rd, | \$ra,  | \$rb | R[rd] = R[ra] + R[rb]                                                                                 |

| Subtract             | sub S  | \$rd, | \$ra,  | \$rb | R[rd] = R[ra] - R[rb]                                                                                 |

| Shift left logical   | sll S  | \$rd, | \$ra,  | x    | $R[rd] = R[ra] \ll x$                                                                                 |

| Shift right logical  | srl S  | \$rd, | \$ra,  | x    | R[rd] = R[ra] >> x                                                                                    |

| Load upper immediate | lui S  | \$rd, | x      |      | $R[rd] = \{x, 16b0\}$                                                                                 |

| Or immediate         | ori S  | \$rd, | \$ra,  | x    | $R[rd] = R[ra] \mid \{16b0, x\}$                                                                      |

| Subtract immediate   | subi S | \$rd, | \$ra,  | x    | R[rd] = R[ra] - x                                                                                     |

| Multiply immediate   | muli S | \$rd, | \$ra,  | x    | R[rd] = R[ra] * x                                                                                     |

| Load word            | lw S   | \$rd, | x[\$ra | ]    | R[rd] = M[R[ra] + x]                                                                                  |

| Load byte            | lb S   | \$rd, | x[\$ra | ]    | $R[rd] = \{24'b0, M[R[ra] + x]\}$                                                                     |

| Floating-point add   | fadd S | \$rd, | \$ra,  | \$rb | $R[rd] = R[ra] \stackrel{FP}{+} R[rb]$                                                                |

| Floating-point sub   | fsub S | \$rd, | \$ra,  | \$rb | $R[rd] = R[ra] \stackrel{FP}{-} R[rb]$                                                                |

| Floating-point mul   | fmul S | \$rd, | \$ra,  | \$rb | $\mathbf{R}[\mathbf{rd}] = \mathbf{R}[\mathbf{ra}] \stackrel{\mathrm{FP}}{*} \mathbf{R}[\mathbf{rb}]$ |

| Branch if equal      | beq S  | \$rd, | \$ra,  | x    | PC = x if $R[rd] = R[ra]$                                                                             |

| Branch if positive   | bpos S | \$rd, | x      |      | $PC = x \text{ if } R[rd] \ge 0$                                                                      |

| Branch if negative   | bneg S | \$rd, | x      |      | PC = x  if  R[rd] < 0                                                                                 |

Table 4.1: Instruction set from [Egg16]

The instruction set has been shown to be executable using the datapath shown in Figure 4.3. An ISA-simulator modelling this datapath was created in [Egg16].

An assembled version of the ray tracing algorithm was successfully run using this ISA-simulator.

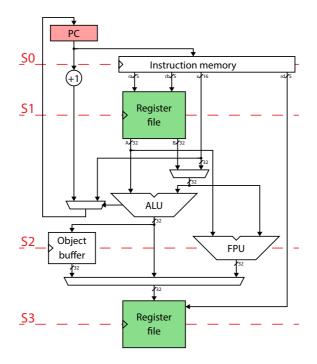

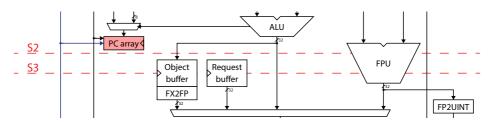

Figure 4.3: Core datapath from [Egg16]. The dotted red lines represent pipeline registers for all signals that pass through them. The two register file blocks represent reading and writing to and from the same physical register file.

### 4.3 Project thesis results

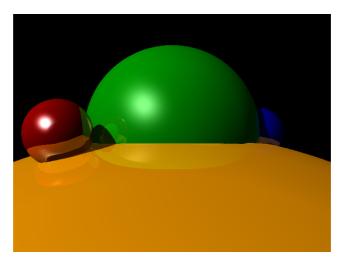

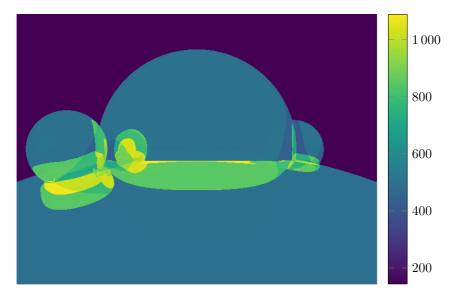

Using the mentioned models, data used to predict system performance has been extracted. By analysing this data, it was found that achieving a frame rate of 24 FPS at VGA resolution requires 74 cores when running at 50 MHz. Implementing this many cores on an FPGA will present problems in terms of area and design of interconnect. Figure 4.4 shows an example of a scene rendered using the ISA-simulator.

Figure 4.4: Scene rendered using ISA-simulator

### 4.4 Future work

A proposal for future work was described at the end of the project thesis. The most important points from this list were:

- System-level design. Examine the ZedBoard and Zynq, and determine how system-level blocks maps to the resources on these.

- Analyses and design of thread interleaving scheme.

- Interfaces and interconnect between ray cores and ray manager.

- Interfaces and interconnect between object buffers and ray cores.

- Interfaces and interconnect between object buffers and ray manager.

- Improvements to the ISA.

- Deciding upon final instruction formats.

- Deciding whether to implement the ray manager as a dedicated hardware unit or using a general-purpose processor.

- Implementing a fixed-point to floating-point instruction.

- Implementing the system in RTL.

- Synthesising the RTL for the target FPGA.

## Chapter 5

# Design process

In this chapter, large parts of the ray tracer will be designed, implemented and tested. This work builds upon what was presented in Chapter 4. System-level design will be discussed in Section 5.1. Here, implementation on the Zynq SoC, as well as refinement of ray tracer blocks will be discussed. Sections 5.2 to 5.4 will go through the design of the thread interleaving scheme, communication protocols and the ISA. Design and modelling of floating-point operators will be covered in Section 5.5. Sections 5.6 to 5.8 cover implementation, verification, synthesis and performance analysis.

The ray tracing algorithm is very parallelisable. In this system, one initial ray is cast per pixel, and these rays are traced by independent threads. Due to this, the terms *thread*, *ray* and *pixel* will be used interchangeably, depending on what suits the situation best.

Rendering of VGA frames at 24 FPS should be assumed where nothing else is explicitly stated. The system is designed around the ZedBoard [Avn14], that features a Xilinx Zynq SoC [Xil16]. This thesis will mainly focus on digital design, and thus the programmable logic part of the SoC.

### 5.1 System-level design

In [Egg16], the communication between the ray manager and the cores were not fully specified. Figure 4.2 showed a custom bus matrix as well as some wiring between the ray manager and the cores. By itself, this is not enough to enable communication, as the cores themselves has no way of receiving or sending any data. Addressing this issue, this section will focus on interfaces and interconnects.

### 5.1.1 Ray tracer

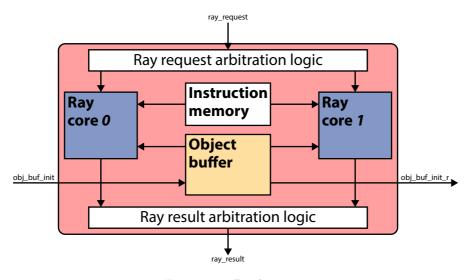

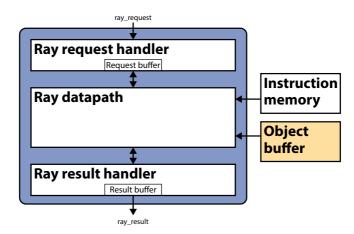

In Figure 5.1, the first step towards a working interface between the ray manager and cores is shown. This figure abstracts away the ray cores and their interconnect, as the dual core array will be discussed in Section 5.1.2. Ray requests are generated by the ray generator and sent over a ready/valid interface to the dual core array. As results are calculated, they are sent back to the pixel handler over another ready/valid interface. These interfaces will be discussed in Section 5.3. In this thesis, only the dual core array and its submodules will be implemented, while performance of the ray manager will be analysed.

Figure 5.1: Ray tracer block diagram.

As seen from the figure, many components have been moved around and some are added when compared to Figure 4.2. As opposed to that block diagram, this maps directly to resources available on the ZedBoard and Zynq [Avn14; Xil16]. Some

24

#### 5.1. SYSTEM-LEVEL DESIGN

other changes within the programmable logic section have also been performed. In [Egg16], each object buffer had an AXI interface in order to fetch data from memory. It was pointed out that this was far from optimal, as each object buffer will fetch the same data. To make this more efficient, propagation of the data was mentioned as a better alternative. This has now been implemented into the design using the object buffer initialiser. This module initialises all object buffers in the dual core array. The object buffer initialisation will be discussed in Section 5.1.5.

As mentioned in [Egg16], the ray manager could be implemented in the CPU, potentially accelerating development. This is possible as the ray manager is a relatively low-throughput module. Performance analyses considering this will be performed in Section 5.8.2.

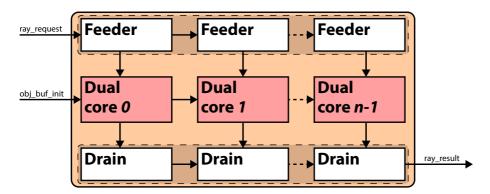

### 5.1.2 Dual core array

As mentioned, the dual core array is used to abstract away the ray cores and their interconnect. Figure 5.2 shows the dual core array. It consists of a chain of feeder elements that is the interconnect feeding requests to the cores, as well as a chain of drain elements that routes results out of the array. The dual cores are also chained together, allowing for initialisation of object buffers (see Section 5.1.5).

Figure 5.2: Dual core array. Each dual core holds two ray cores, one instruction memory and one object buffer.

Internally, the feeder elements register incoming requests, and passes them on to either a dual core or the next feeder element the next clock cycle. This given that the dual core or the next feeder element is ready to accept a new request. In case both are ready, the dual core has the highest priority. The way this is designed, requests reaching the end of the feeder chain will be stuck waiting for dual core n-1. This could have been overcome by looping requests back to the start of the chain. However, as shown by Figure 5.18 in Section 5.8.1, system performance is not greatly affected by this.

The drain elements work in the same way, accepting results from either a dual core or the previous drain in the chain. The result is registered and propagated to the next drain element the next clock cycle. Also here, dual cores are prioritised. Dual cores are given the highest priority as this guarantees that the dual core can start processing a new ray. The dual cores themselves will be further discussed in Section 5.1.3.

Registering the requests and results in the feeder and drain elements helps the synthesis tool avoid routing congestion on the FPGA. The elements break timing in the forward direction (i.e. the valid and payload signals). In Section 5.7.4, experiments with also breaking timing in the reverse direction (i.e. the ready signal) are conducted. The widths of the request and result buses are equal to the width of the messages transmitted over them. This helps in simplifying the design process. The message formats are shown in Sections 5.3.2 and 5.3.3. Internally in the dual core array, all interfaces use ready/valid handshaking.

#### Learning example 5.1: Avoiding routing congestion

By inserting register slices on the request and result buses, the fan-out of the ray generator is reduced<sup>a</sup>. This lowers the burden of place and route for the synthesis tool by avoiding routing congestion on the FPGA. Had register slices not been used, and purely combinatorial arbitration between the cores applied, the ray generator would have to drive each of the ray cores directly. For this to meet timing, the synthesis tool would have to place all ray cores physically close to the ray generator. In configurations with many cores, this is not physically possible, and would result in the synthesis tool giving up, giving a low operating frequency for the system.

As mentioned, only the ready and payload signals are registered, while a combinatorial ready-path through all register slices are still present. It is assumed that this might become a problem, and register slices that break timing in the reverse direction have been designed. Experiments with these are performed in Section 5.7.4.

$<sup>^</sup>a{\rm Also}$  the fan-in of the pixel handler is reduced. The same arguments as for the fan-out of the ray generator are valid for this.

### 5.1.3 Dual core

Making dual cores a separate entity was a natural choice. In [Egg16] it was pointed out that block RAM (BRAM) on Xilinx FPGAs are dual ported [Xil13], and to fully utilise this, each instruction memory and object buffer should be shared by two ray cores. As shown in Figure 5.3, a purely combinatorial 'arbitration' between the two cores is used. The core labelled *Ray core*  $\theta$  has the highest priority for both requests and results. The ray core will be discussed in Section 5.3. The instruction memories and object buffers will be discussed in Sections 5.1.4 and 5.1.5, respectively.

Figure 5.3: Dual core

#### Learning example 5.2: Performance density

Performance density is a measure of the performance delivered per unit area. Keeping this high is a goal for most digital systems. Here performance density is increased by sharing the same physical instruction memory and object buffer between two ray cores.

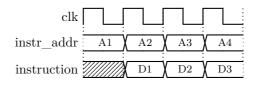

### 5.1.4 Instruction memory

The instruction memory has a simple interface. It performs a synchronous read of the instruction memory every clock cycle. In order for it to map to dual ported BRAM, it has two independent read ports. As instructions are read every clock cycle, no read enable is needed. Figure 5.4 shows an example timing diagram for the instruction memory.

Figure 5.4: Instruction memory interface example waveform

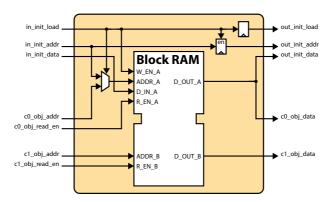

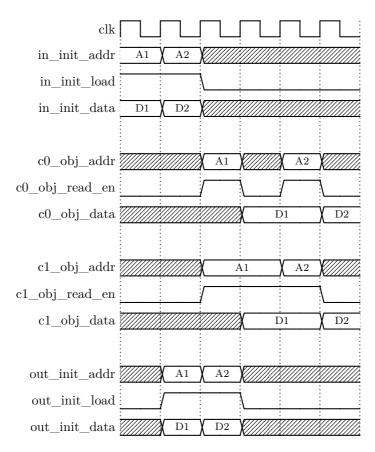

### 5.1.5 Object buffer

The object buffers play the same role in this system as caches hold in more complex systems: keeping frequently used data readily available to the processing elements. The only difference is that the data held by the object buffers is constant for a whole frame. This is because the simple scenes this system is designed to render are small enough to be stored in their entirety in BRAM close to the ray cores. The object buffer memory layout is shown in Figure A.5.

The read interfaces are simple. Inputs are the object address and a read enable, while the read data is available at the output the following clock cycle. Just like the instruction memory, two cores share the same object buffer in order to increase performance density. The read enable signal is used to increase energy efficiency (see learning example 5.3). In Figures 5.5 and 5.6, signals c0\_obj\_addr and c1\_obj\_addr holds the addresses from ray cores 0 and 1, respectively. c0\_obj\_read\_en and c1\_obj\_read\_en are the read enable signals, while c0\_obj\_data and c1\_obj\_data holds the read data.

As seen from Figures 5.2 and 5.3, all object buffers are chained together. This chain is used in propagating initialisation data to all object buffers in the system. The object buffer initialiser (from Figure 5.1) pushes data to the first object buffer in the chain, that stores the data and propagates it onward to the next object buffer and so on. The data on in\_init\_data is stored to the address in\_init\_addr when the signal in\_init\_load is high. These signals are all pipelined through to the next object buffer in the chain using the signals out\_init\_data, out\_init\_addr

28

#### 5.1. SYSTEM-LEVEL DESIGN

and out\_init\_load. By chaining and pipelining object buffers, routing congestion is avoided (remember learning example 5.1).

This is all implemented using one BRAM, one multiplexer, a register and a flip-flop (FF). The BRAM is set to write-first synchronisation [Xil13], eliminating the need for registering that as well. As seen in Figure 5.5, port A of the BRAM is shared between the initialisation interface and core 0's read interface. This means that reading and writing using these at the same time is not possible. This is not a problem, as the system architecture specifies that object buffer initialisation is never to occur at the same time as ray tracing.

Figure 5.5: Block diagram of object buffer

#### Learning example 5.3: Improving energy efficiency

In digital circuits, dynamic power is consumed when signals toggle (remember Section 2.3.2). Due to this, unnecessary toggling of signals should be avoided. In this section, a read enable was added to the object buffer, keeping the output of the BRAM unchanged when no read is needed. We even have a clock enable on the register for the address, further improving energy efficiency (see Figure 5.5).

Figure 5.6: Object buffer interfaces example waveform

### 5.2 Thread interleaving

In the ray datapath presented in [Egg16] (Figure 4.3), both data hazards and control hazards pose a problem. [Egg16] proposed interleaving of 4 threads in a round-robin fashion to overcome the data hazard, while the control hazard was not discussed. However, the control hazard is also eliminated by interleaving in the way that was proposed. This multithreading technique is commonly referred to as *interleaved multithreading* [LGH94], a variant of *fine-grained multithreading* [HP12].

As previously mentioned, all threads are independent. This is what enables thread interleaving to be effective in eliminating the hazards. Both hazards will be discussed, starting with the data hazard.

The data hazard in this architecture is a read after write (RAW) data hazard [HP12; PH14]. A RAW hazard occurs when an instruction tries to access a result of a previous instruction, where the result is not yet calculated or available in the register file. Utilising thread interleaving, this situation is avoided by interleaving processing of independent threads. By interleaving a sufficient number of threads, it can be guaranteed that the result of an instruction is stored in the register file by the time the next instruction in the same thread fetches its operands. This does however require storing multiple program counters (PCs) and register file segments.

In the datapath shown in Figure 4.3, operands are read in stage S1 and stored in S3. This means that interleaving of two threads would be enough to eliminate the RAW hazard. However, [Egg16] specified that the register file was to be implemented in BRAM. To map directly to BRAM, data written is not available for reading before the next clock cycle. Xilinx refers to this mode of read/write synchronisation as read-first [Xil13]. This means that one will have to interleave at least three threads to avoid the data hazard. This has been rounded up to four, allowing for a 2 bit thread id to keep track of the thread executing in each pipeline stage. This id is used in selecting the thread PC and register file segment. The effects of using write-first synchronisation or even LUTRAM is discussed in learning example 5.5.

The control hazard is also a result of the architecture shown in Figure 4.3. The PC is read in S0, and updated in S2. This means that interleaving of two threads is enough to eliminate also this hazard.

Table 5.1 illustrates how different threads are being executed in the different pipeline stages. The PC of each thread is also shown, demonstrating how it is updated in S2 (but first visible in S3).

|                | #0 | #1 | #2 | #3 | #4 | #5 | #6 | #7 |

|----------------|----|----|----|----|----|----|----|----|

| S0             | Τ0 | T1 | T2 | Т3 | Τ0 | T1 | T2 | Т3 |

| $\mathbf{S1}$  |    | T0 | T1 | T2 | T3 | T0 | T1 | T2 |

| S2             |    |    | T0 | T1 | T2 | T3 | T0 | T1 |

| $\mathbf{S3}$  |    |    |    | T0 | T1 | T2 | T3 | T0 |

| PC0            | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 2  |

| PC1            | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  |

| $\mathbf{PC2}$ | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  |

| PC3            | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

Table 5.1: Illustration of thread interleaving. #N indicates the Nth clock cycle. S corresponds to the stages in Figures 4.3 and 5.12. T is for thread and PC refers to the different program counters.

#### Learning example 5.4: Dependency removal

Thread interleaving is one method that can be applied to remove the effects of pipeline dependencies. What other methods are there, and could they be used in this system? How would using these methods impact the performance and complexity of the system?

Alternatives to thread interleaving include code scheduling, pipeline stalling and operand forwarding. By using operand forwarding, only the data hazard is resolved. The control hazard could then have been solved by e.g. branch prediction or a branch delay slot [PH14]. Thread interleaving was chosen as it completely eliminates the need for stalling, giving higher and predictable performance.

In considering other methods, the performance (density) impact of these would have to be evaluated. Analyses using pen and paper as well as simulations would be the way to go.

### Learning example 5.5: Register file implementation

There are many different properties to consider when implementing the register file. In [Egg16], a BRAM mapped register file with read-first synchronisation was specified. Here, a short comparison of the different alternatives is presented. Where adding pipeline stages is discussed, these are to be placed between the read and write of the register file (i.e. between

S1 and S3 in Figure 4.3).

- Keeping the implementation from [Egg16] is naturally the first possibility.

- Keeping the register file as it is, but introducing another pipeline stage could improve performance of the system.

- Changing the synchronisation mode to write-first. This would require some additional logic in the register file. Using this synchronisation mode gives two alternatives:

- Add two additional pipeline stages, potentially increasing  $f_{max}$  significantly.

- Go down to only interleaving two threads.

- Implementing the register file using LUTRAM and using asynchronous read. This gives the same alternatives as BRAM with write-first synchronisation gave.

The effects of implementing these alternatives would have to be analysed and simulated in order to conclude which is 'best'. Performance and area are important keywords in this analysis.

### 5.3 Ray core

The ray core is essentially a wrapper for the ray datapath, providing ready/valid interfaces for incoming ray requests and outgoing results. It manages and keeps track of each of the four threads in the ray datapath. A block diagram showing the ray core is shown in Figure 5.7.

Figure 5.7: Ray core block diagram

The ray request handler accepts ray requests into the request buffer and assigns them to idle threads. The ray datapath then starts tracing the ray from the request. Once finished tracing, the ray datapath loads the resulting pixel colour into the result buffer, and the ray result handler sends the colour out on the result interface. The following sections will describe these interfaces in more depth.

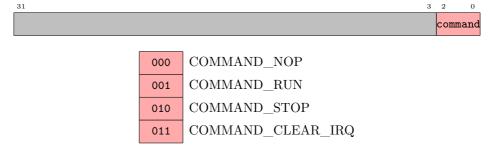

### 5.3.1 Commands and statuses

Communication between the ray core and the ray datapath is facilitated by the use of command and status registers for each thread in the system. The legal commands and statuses are shown in Tables 5.2 and 5.3, respectively.

34

| Command                                    | Encoding | Description                                     |

|--------------------------------------------|----------|-------------------------------------------------|

| NONE                                       | 00       | The core should keep doing what it is doing     |

| START                                      | 01       | The core should start processing a ray          |

| $\operatorname{RESBUF}_\operatorname{GNT}$ | 10       | The core is granted access to the result buffer |

Table 5.2: Commands

Table 5.3: Statuses

| Status        | Encoding | Description                                   |

|---------------|----------|-----------------------------------------------|

| IDLE          | 00       | The core is idle                              |

| BUSY          | 01       | The core is tracing a ray                     |

| $RESBUF\_REQ$ | 10       | The core requests access to the result buffer |

The commands are issued by the request and result handlers, while statuses are reported by the ray datapath. The state of each thread is made up of a command, a status and the coordinates of the pixel being rendered by that thread. This is all held in a table used for tracking the state of the individual threads. An example of this is shown in Table 5.4.

Table 5.4: Table for thread state tracking. The table holds example data.

| Thread   | x  | у  | Command    | Status     |

|----------|----|----|------------|------------|

| 0        | 12 | 20 | NONE       | BUSY       |

| 1        | 12 | 28 | RESBUF_GNT | RESBUF_REQ |

| <b>2</b> | 12 | 30 | NONE       | RESBUF_REQ |

| 3        | 12 | 19 | START      | IDLE       |

#### Learning example 5.6: Assertions