## Experimental Investigation of Operational Reliability of Silicon Carbide MOSFETs

Fredrik Tomas Bjørndalen Wergeland Göthner

Master of Energy and Environmental EngineeringSubmission date:June 2017Supervisor:Dimosthenis Peftitsis, IELCo-supervisor:Magnar Hernes, SINTEF Energi

Norwegian University of Science and Technology Department of Electric Power Engineering

### Abstract

As the performance of silicon power semiconductors is close to the theoretical limit, other semiconductor materials are sought to improve power electronics system efficiency. Devices made with the wide bandgap material silicon carbide (SiC) are promising due to the possibility of significantly improved system efficiency and reduced system volume and weight. However, reliability is still a key issue to be dealt with before wide-spread use of the devices may take place.

In this thesis two of the largest reliability concerns of the SiC MOSFET are evaluated by investigating discrete devices. The issues are the threshold voltage instability and the reliability of packaging of the devices. Dedicated test benches were established to study the issues. The tested devices indicate that the drift of the threshold voltage is still an issue for SiC MOSFETs.

The methodology of performing power cycling tests was investigated. This accelerated life time stress test can be utilized to evaluate packaging reliability. The tests were performed by using the  $V_{\rm SD}(T)$ -method to evaluate the junction temperature.

Several devices were tested, all of which indicated failure by bond-wire lift off. The results furthermore indicate that power cycling of SiC MOS-FETs is affected by the threshold voltage instability. In particular, a reduction of the on-state voltage was observed at the beginning of almost all the tests, which was attributed to the instability of the threshold voltage. The results call for a discussion as to how power cycling of SiC MOSFETs ought to be performed, in order to reduce the influence of the threshold voltage drift. A suggestion for reducing the influence of the latter is also given.

### Sammendrag

Krafthalvledere laget av silisium har nesten nådd sin teoretiske ytelsesgrense. Andre materialer har derfor blitt undersøkt for å forbedre effektiviteten til kraftelektronikksystemer. Blant disse er silisiumkarbid (SiC) funnet å være lovende, grunnet muligheten for å forbedre systemkarakteristikker som effektivitet, volum og vekt. Påliteligheten til krafthalvledere av SiC er imidlertid et viktig område som må utbedres før storskala kommersialisering av komponentene kan gjennomføres.

I denne masteroppgaven blir to av de fremste pålitelighetsproblemene for SiC MOSFET studert. Disse problemene er drift av terskelspenning og påliteligheten til pakningen. Dedikterte testoppsett ble laget for å evaluere pålitelighetsproblemene. De testede komponentene indikerer at drift fremdeles er et et problem for SiC MOSFET-komponenter.

Metodikken for å gjennomføre power cycling-tester ble evaluert. Denne testen, som er en akselerert levetidstest, kan bli brukt for å teste påliteligheten til pakningen av komponenter. Testene ble gjennomført ved å bruke  $V_{\rm SD}(T)$ -metoden for å estimere temperaturen på halvlederbrikken.

Alle de testede komponentene indikerte feil ved at en del av båndetrådene ble løftet av. Videre indikerte resultatene at drift av terskelspenningen påvirker hvordan power cycling-testen blir gjennomført; en reduksjon i ledespenningen over testobjektet ble observert i starten av nesten alle testene, noe som ble tilskrevet en endring av terskelspenningen. Disse resultatene tilsier at metodikken for power cycling av SiC MOSFET-er bør klargjøres, for å unngå drift av terskelspenningen under testen. En forenklet metode for å gjøre dette er videre foreslått.

### **Problem Description**

Silicon Carbide (SiC) MOSFETs are promising candidates for being utilized in medium and high voltage applications, due to its potential of drastically reducing system size and losses. However, the present status for SiC MOSFETs is that they suffer from threshold voltage instability and bipolar degradation. This, in addition to possible power cycling reliability issues related to the packaging, call for investigations similar to those normally applied for IGBT devices.

In order to investigate these issues, experimental work will be carried out. In particular, test methodology should be investigated and power cycling experiments of SiC test objects should be performed, the latter with reference to methodologies used for IGBT devices.

### Acknowledgements

This master's thesis has been carried out as a part the ReliPE project at SINTEF Energy. Both the partners in the project and the employees at SINTEF Energy have been supportive and given valuable feedback. I would therefore like to thank everyone involved in the project.

In particular, I would like to extend my gratitude to Ole Christian Spro for his invaluable help. His help, both with the practical set-up as well as in discussions, has been decisive for the outcome of the thesis.

I would also like to thank Atle Rygg for his important feedback regarding both the practical set-up and discussions regarding the results.

I would like to thank my co-supervisor Magnar Hernes for valuable discussions and feedback throughout the project.

I am also thankful for the help I have received from Sven Clausner regarding the practical set-up. I would further like to thank Weinan Chen at TU Chemnitz for doing the SAM analysis. Moreover, I would like to thank Professor Dr.Ing. Josef Lutz for valuable feedback on the use of the  $V_{\rm SD}(T)$ -method.

I would also like to thank Justin Hwa for his help with improving the general language of the thesis.

Finally, I would like to extend my gratitude to my supervisor, Associate Professor Dr. Dimosthenis Peftitsis. He has provided support and crucial feedback throughout the thesis, for both of which I am truly grateful.

Last, but certainly not least, I would like to thank my wife, Ingrid Wergeland Göthner, for her love and support throughout my studies at NTNU, and during this thesis in particular.

Fredrik Tomas Bjørndalen Wergeland Göthner

Trondheim 14.06.2017

## Contents

| Li            | List of Figures xiv |                                                                                   |   |  |

|---------------|---------------------|-----------------------------------------------------------------------------------|---|--|

| $\mathbf{Li}$ | List of Tables xvi  |                                                                                   |   |  |

| Al            | obrev               | viations xvii                                                                     | i |  |

| 1             | Intr                | roduction                                                                         | 1 |  |

|               | 1.1                 | Motivation                                                                        | 1 |  |

|               | 1.2                 | Background                                                                        | 2 |  |

|               | 1.3                 | Outline of Thesis                                                                 | 3 |  |

| <b>2</b>      | SiC                 | MOSFET                                                                            | 4 |  |

|               | 2.1                 | Silicon Carbide Material Properties                                               | 4 |  |

|               | 2.2                 | Silicon Carbide Devices                                                           | 6 |  |

|               |                     | 2.2.1 PiN Diode                                                                   | 6 |  |

|               |                     | 2.2.2 MOSFET                                                                      | 7 |  |

|               | 2.3                 | Particular SiC MOSFET Reliability Issues                                          | 9 |  |

|               |                     | 2.3.1 Threshold Voltage Instability                                               | 9 |  |

|               |                     | 2.3.2 Bipolar Degradation                                                         | 0 |  |

|               | 2.4                 | Packaging Technology 1                                                            | 1 |  |

|               |                     | 2.4.1 Discrete Packages                                                           | 1 |  |

|               |                     | 2.4.2 Power Modules                                                               | 1 |  |

|               | 2.5                 | Estimation of Junction Temperature                                                | 2 |  |

|               |                     | 2.5.1 $V_{\rm SD}(T)$ -Method                                                     | 4 |  |

| 3             | Eva                 | luation of Threshold Voltage Instability 19                                       | 9 |  |

|               | 3.1                 | Threshold Voltage Instability Test Set-Up 19                                      | 9 |  |

|               |                     | 3.1.1 Principles of the Test 19                                                   | 9 |  |

|               |                     | 3.1.2 Test Bench                                                                  | 1 |  |

|               |                     | 3.1.3 Current Source                                                              | 2 |  |

|               |                     | 3.1.4 Temperature Dependency                                                      | 2 |  |

|               | 3.2                 | Evaluation of the $V_{\rm GS(th)}$ Instability                                    | 3 |  |

|               |                     | 3.2.1 Test Object $2$                                                             | 3 |  |

|               |                     | 3.2.2 Test Object 3 $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 2^4$ | 4 |  |

|          | 3.3              | Conclusions and Possible Improvements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25        |

|----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 4        | Power Cycling 20 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

|          | 4.1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26        |

|          | 4.2              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28        |

|          | 4.3              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30        |

|          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| <b>5</b> | Pov              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>34</b> |

|          | 5.1              | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34        |

|          | 5.2              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35        |

|          |                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 37        |

|          |                  | 5.2.2 DUT gate driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38        |

|          | 5.3              | Control of Set-Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40        |

|          |                  | 5.3.1 Control Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40        |

|          |                  | 5.3.2 Control Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 41        |

|          | 5.4              | e de la companya de la compa | 42        |

|          | 5.5              | Electrical Characterization of Test Objects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44        |

|          |                  | 5.5.1 Threshold Voltage Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44        |

|          |                  | 5.5.2 Gate Leakage Current Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44        |

|          |                  | 5.5.3 Blocking Voltage Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45        |

|          |                  | 5.5.4 On-State Voltage Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46        |

|          | 5.6              | Estimation of the Virtual Junction Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46        |

|          |                  | 5.6.1 Establishing a Calibration Curve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46        |

|          |                  | 5.6.2 Virtual Junction Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48        |

|          | 5.7              | Device Operating Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49        |

| 6        | Res              | Its from Power Cycling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51        |

|          | 6.1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52        |

|          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52        |

|          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54        |

|          |                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 55        |

|          | 6.2              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57        |

|          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57        |

|          | 6.3              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59        |

|          |                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 59        |

|          |                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61        |

|          | 6.4              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62        |

|          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63        |

|          | 6.5              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65        |

|          | -                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| 7        | Dis              | ussion and Further Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 66        |

|          | 7.1              | Evaluation of the $V_{SD}(T)$ -method $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66        |

|          |                  | 7.1.1 Threshold Voltage Instability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66        |

|          |                  | 7.1.2 Stability and Reliability of the TSEP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67        |

|                                            |                                                                   | 7.1.3  | Bipolar Degradation                       | 67 |  |

|--------------------------------------------|-------------------------------------------------------------------|--------|-------------------------------------------|----|--|

|                                            |                                                                   |        |                                           | 68 |  |

|                                            |                                                                   |        |                                           | 68 |  |

|                                            | 7.2.2 Mitigating Drift of $V_{\rm GS(th)}$ During Power Cycling 7 |        |                                           |    |  |

|                                            | 7.3                                                               | Result | s of Power Cycling                        | 71 |  |

|                                            |                                                                   | 7.3.1  | Failure Mode                              | 71 |  |

|                                            |                                                                   | 7.3.2  | Lifetime of Devices                       | 72 |  |

|                                            | 7.4                                                               | Recon  | mended Further Work                       | 73 |  |

|                                            |                                                                   | 7.4.1  | Changing the DUT Gate Driver              | 73 |  |

|                                            |                                                                   | 7.4.2  | Improving the Sensing Current Source      | 74 |  |

|                                            |                                                                   | 7.4.3  | Estimation of $T_{vi}$                    | 74 |  |

|                                            |                                                                   | 7.4.4  | Reducing the Size of DUT Heat Sink        | 75 |  |

|                                            |                                                                   | 7.4.5  | Monitoring Voltages of Auxiliary Switches | 75 |  |

|                                            |                                                                   | 7.4.6  | Improving Cooling for Auxiliary Switches  | 75 |  |

|                                            |                                                                   | 7.4.7  | Expanding the Test Bench                  | 75 |  |

| 8                                          | Con                                                               | clusio | n                                         | 76 |  |

| References 73                              |                                                                   |        |                                           | 78 |  |

| Appendix                                   |                                                                   |        |                                           | 83 |  |

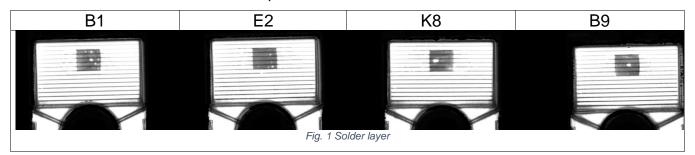

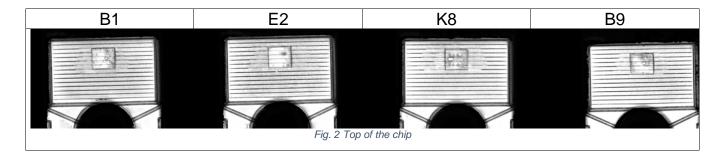

| A Scanning Acoustic Microscopy Analysis 84 |                                                                   |        |                                           | 84 |  |

## List of Figures

| 2.1  | Structure of the PiN diode $[1, p. 525] \dots \dots \dots \dots \dots$                | 6  |

|------|---------------------------------------------------------------------------------------|----|

| 2.2  | Shielded planar inversion-mode n-MOSFET [2, p. 236]                                   | 8  |

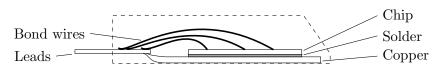

| 2.3  | Discrete TO package [3, p. 349]                                                       | 11 |

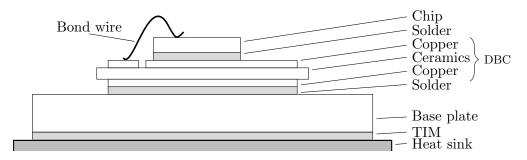

| 2.4  | Standard power module with corresponding layers [3, p. 354]                           | 12 |

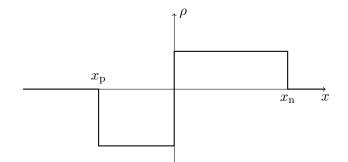

| 2.5  | Space charge distribution of an abrupt pn-junction                                    | 15 |

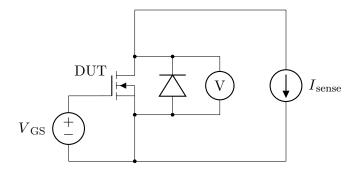

| 2.6  | Schematic drawing of the $V_{SD}(T)$ -method                                          | 18 |

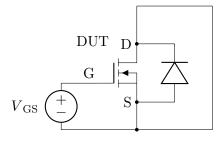

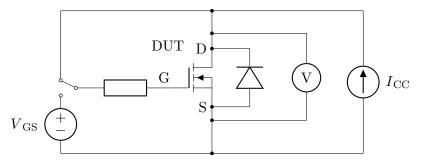

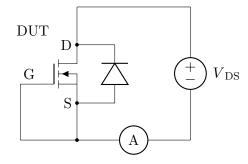

| 3.1  | Set-up for testing threshold voltage instability                                      | 20 |

| 3.2  | Constant Current method for measuring threshold voltage                               | 20 |

| 3.3  | Electric circuit of stress mode.                                                      | 21 |

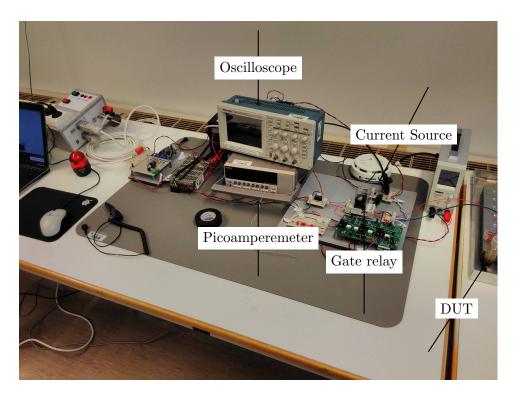

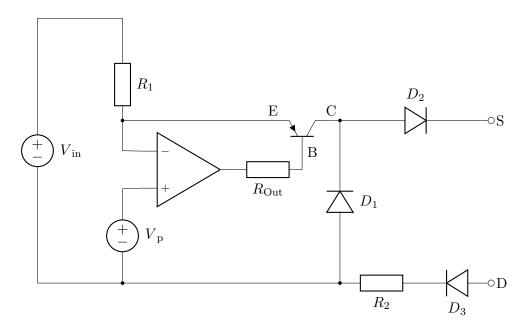

| 3.4  | Test set-up for threshold voltage instability testing                                 | 21 |

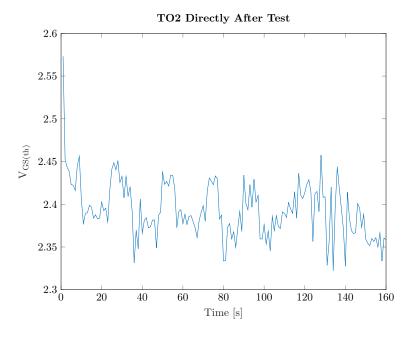

| 3.5  | Threshold voltage of TO2 directly after test                                          | 23 |

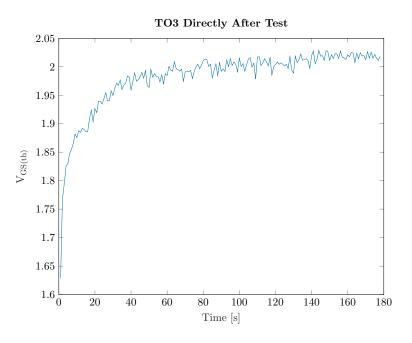

| 3.6  | Threshold voltage of TO3 directly after test                                          | 24 |

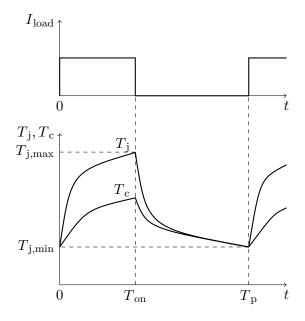

| 4.1  | Power cycling procedure [4]                                                           | 27 |

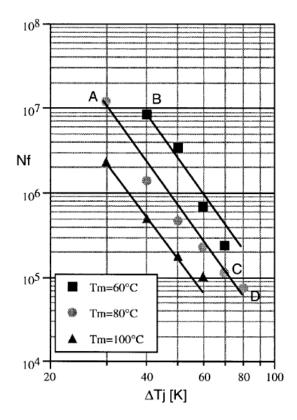

| 4.2  | Results from the LESIT project [5]                                                    | 29 |

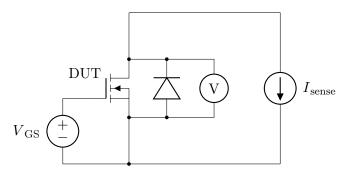

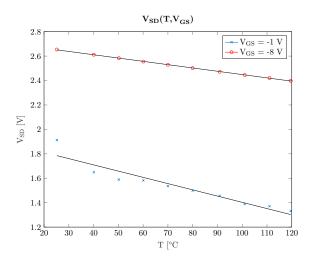

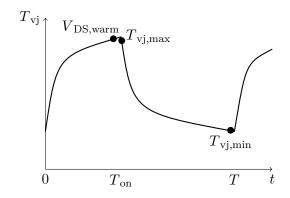

| 4.3  | Schematic drawing of $V_{\rm SD}(T)$ -method                                          | 31 |

| 4.4  | Test of whether channel is closed at $V_{\rm GS} = -1 \mathrm{V}$                     | 31 |

| 4.5  | Test of whether channel is closed at different gate voltages                          | 32 |

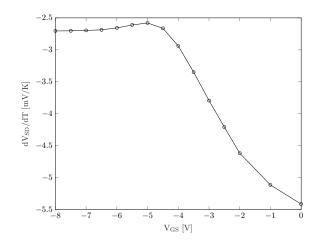

| 4.6  | Slope of $V_{\rm SD}(T)$ plotted against $V_{\rm GS}$                                 | 33 |

| 5.1  | Cree C3M0075120K SiC MOSFET [6]                                                       | 34 |

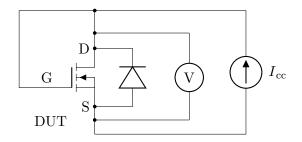

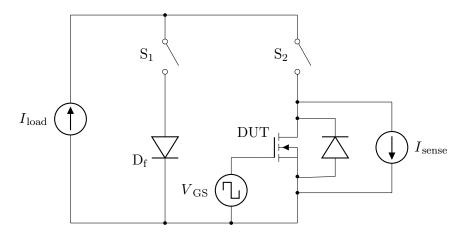

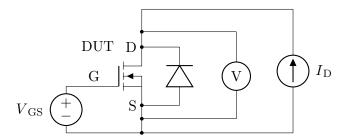

| 5.2  | Electrical circuit for performing power cycling of SiC MOSFET                         | 35 |

| 5.3  | Load current source                                                                   | 36 |

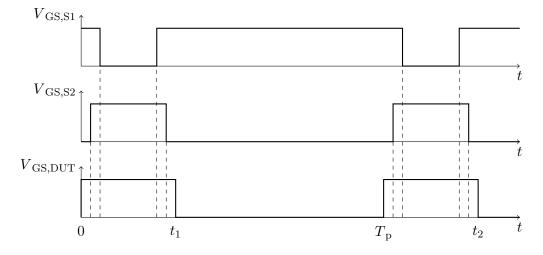

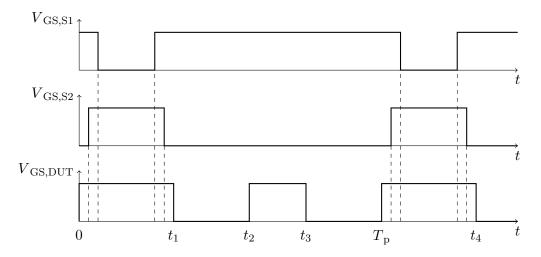

| 5.4  | Timing diagram for power cycling                                                      | 37 |

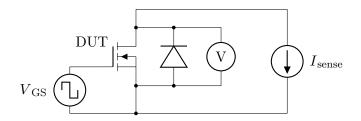

| 5.5  | Simplified schematic diagram of the sensing current source                            | 38 |

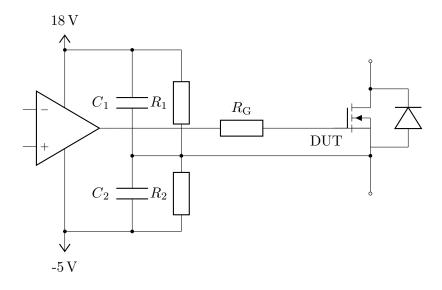

| 5.6  | Simplified schematic diagram of the gate driver                                       | 39 |

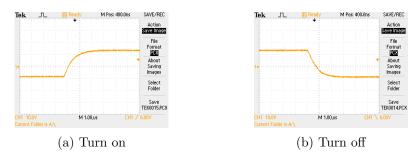

| 5.7  | Switching waveforms of DUT                                                            | 40 |

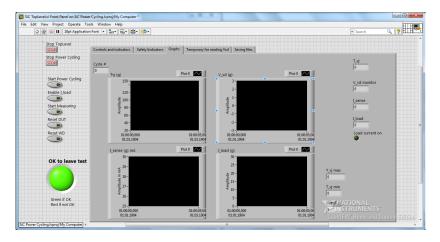

| 5.8  | Front panel of top level VI                                                           | 41 |

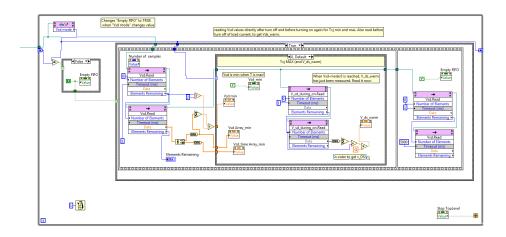

| 5.9  | Block Diagram of top level VI                                                         | 41 |

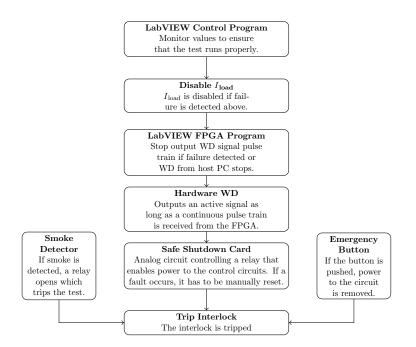

| 5.10 | Safe shutdown flow diagram                                                            | 43 |

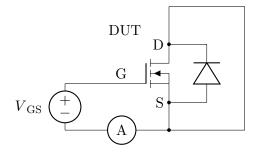

| 5.11 | Schematic diagram for characterization of the threshold voltage $% \mathcal{A}^{(n)}$ | 44 |

| 5.12 | Schematic diagram for characterization of the gate leakage                            |    |

|      | current                                                                               | 45 |

| 5.13 | Schematic diagram for characterization of the blocking voltage               | 45 |

|------|------------------------------------------------------------------------------|----|

| 5.14 | Schematic diagram for characterization of the on-state voltage               | 46 |

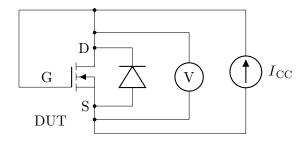

| 5.15 | Schematic diagram of $V_{SD}(T)$ -method                                     | 47 |

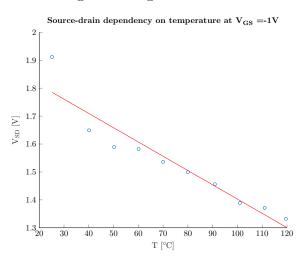

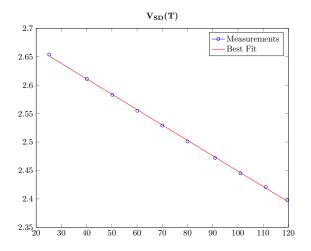

| 5.16 | Calibration procedure with $V_{\rm SD}$ plotted against temperature          | 47 |

| 5.17 | Points of measurement during power cycling                                   | 48 |

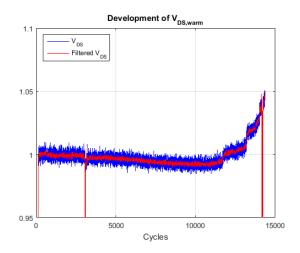

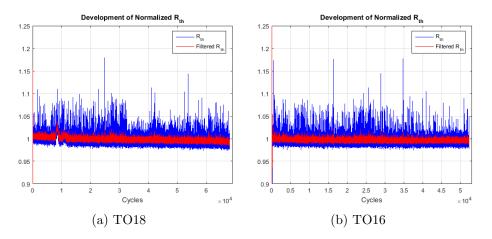

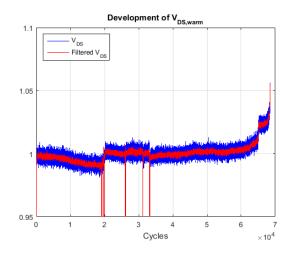

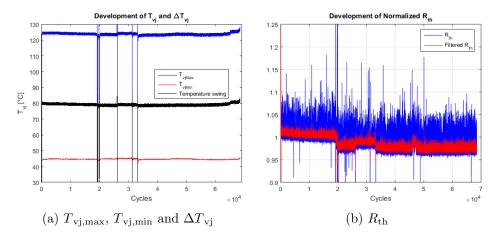

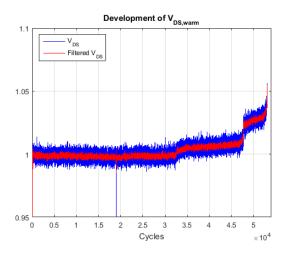

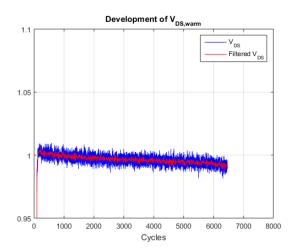

| 6.1  | Development of normalized $V_{\text{DS,warm}}$ for TO20                      | 52 |

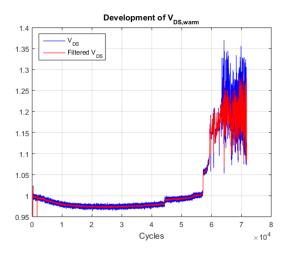

| 6.2  | Development of normalized $V_{\text{DS,warm}}$ for $1020$                    | 53 |

|      | · · · · · ·                                                                  |    |

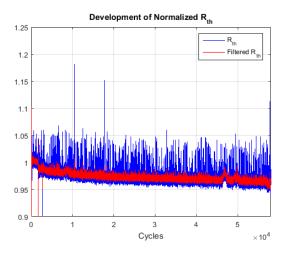

| 6.3  | Development of normalized $R_{\rm th}$ for TO20                              | 53 |

| 6.4  | Development of normalized $V_{\text{DS,warm}}$ for TO17                      | 54 |

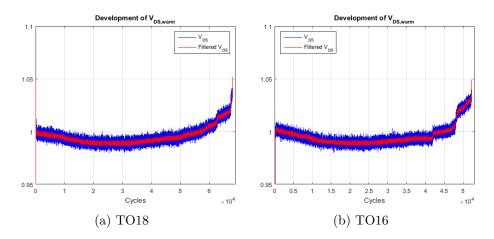

| 6.5  | TO17 Development                                                             | 55 |

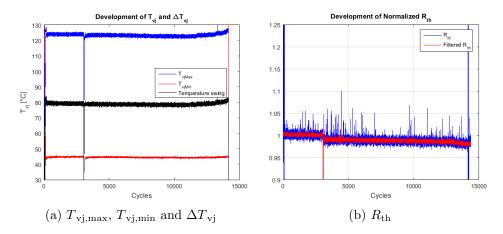

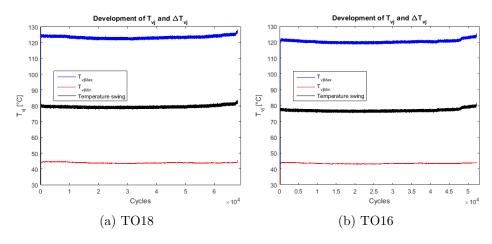

| 6.6  | Development of normalized $V_{\text{DS,warm}}$                               | 56 |

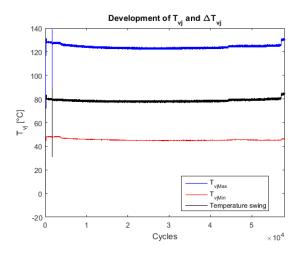

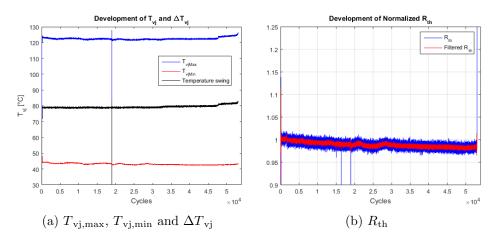

| 6.7  | Development of $T_{\rm vj, max}$ , $T_{\rm vj, min}$ and $\Delta T_{\rm vj}$ | 56 |

| 6.8  | Development of normalized $R_{\rm th}$                                       | 57 |

| 6.9  | Development of normalized $V_{DS,warm}$ for TO15                             | 58 |

| 6.10 | TO15 Development                                                             | 59 |

| 6.11 | Development of normalized $V_{DS,warm}$ for TO21                             | 60 |

|      | TO21 Development                                                             | 60 |

| 6.13 | Development of normalized $V_{DS,warm}$ for TO25                             | 62 |

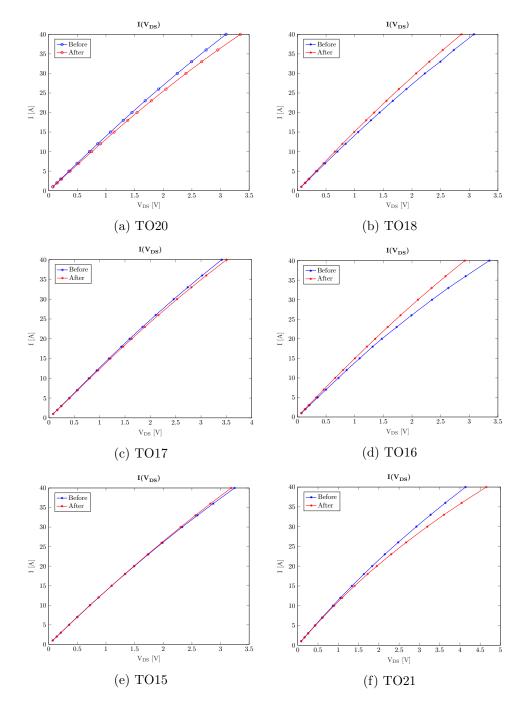

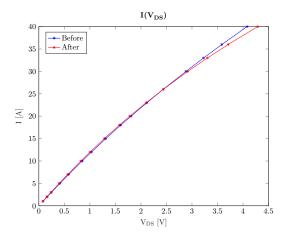

| 6.14 | On-state characteristics of DUT before and after power cycling               | 64 |

| 6.15 | Development of normalized $V_{\text{DS,warm}}$ for TO22                      | 65 |

| 7.1  | Possible switching sequence for reducing threshold voltage drift             | 71 |

## List of Tables

| 2.1 | Comparison of Material Properties Between Si and SiC [7, 8]. | 5  |

|-----|--------------------------------------------------------------|----|

| 3.1 | Test Description for TO2                                     | 23 |

| 3.2 | Test Description for TO3                                     | 24 |

| 5.1 | Cree SiC MOSFET Maximum and Minimum Parameters               | 35 |

| 5.2 | Test Parameters For First Batch                              | 50 |

| 5.3 | Test Parameters For Second Batch                             | 50 |

| 6.1 | Overview of Test Results                                     | 51 |

| 6.2 | Characterization of Test Objects                             | 62 |

| 7.1 | Cycle Parameters During Power Cycling                        | 69 |

| 7.2 | Number of Cycles to Failure                                  | 72 |

| A.1 | Labels for Test Objects                                      | 84 |

## Abbreviations

**BJT** Bipolar Junction Transistor **BPD** Basal Plane Dislocation **CTE** Coefficient of Thermal Expansion **DBC** Direct Bonded Copper  $\mathbf{DUT}$  Device Under Test FIFO First In First Out FPGA Field Programmable Gate Array  $I_{\mathbf{D}}$  Drain Current IGBT Insulated Gate Bipolar Transistor  $I_{load}$  Load Current  $I_{sense}$  Sensing Current JFET Junction Field Effect Transistor **MOSFET** Metal Oxide Semiconductor Field Effect Transistor **NI** National Instruments  $N_{\mathbf{f}}$  Number of Cycles to Failure **PiN** Positive intrinsic Negative  $P_{\mathbf{V}}$  Power Dissipated in DUT  $R_{DS,on}$  Drain-Source on-state resistance

ReliPE Reliability and Ruggedness of High Power High Voltage Power Electronics

- $R_{\rm th}$  Thermal Resistance

- SAM Scanning Acoustic Microscopy

- SiC Silicon Carbide

- $T_{\mathbf{c}}$  Case Temperature

${\bf TIM}\,$  Thermal Interface Material

$T_{\mathbf{j}}$  Junction Temperature

$T_{\mathbf{off}}$  Power Cycling Off-Time

$T_{\mathbf{on}}$  Power Cycling On-Time

$T_{\, {\bf p}}\,$  Cycle Period During Power Cycling

**TSEP** Thermo-Sensitive Electrical Parameter

$T_{{\bf v}{\bf j}}$ Virtual Junction Temperature

$V_{\mathbf{DS}}$ Drain-Source Voltage

$V_{\mathbf{DS},\mathbf{warm}}$ Drain-Source Voltage in Warm State During Power Cycling

$V_{{\bf GS}}$ Gate-Source Voltage

$V_{\mathbf{GS(th)}}$  Gate Threshold Voltage

**VI** Virtual Instruments

$V_{SD}(T)$  Source-Drain Voltage Dependency on Temperature

**WBG** Wide Bandgap

$\mathbf{W}\mathbf{D}$ Watchdog

### Chapter 1

## Introduction

### 1.1 Motivation

One of the major challenges currently facing the planet is climate change, due to greenhouse gas emissions resulting to a large extent from the use of fossil fuels [9]. In order to reduce emissions, more renewable energy sources and more efficient power conversion are necessary, both of which heavily depend on power electronics.

Power electronics systems are indispensable in a wide range of applications, such as electric vehicles, power supplies and industrial equipment [10]. The major contributor to losses in such systems is the power semiconductor, and since the conventional silicon power semiconductors have almost reached their theoretical limits [11], it is becoming increasingly difficult to achieve further efficiency increase without resorting to a different power semiconductor.

One option for another semiconductor material is silicon carbide (SiC), being one of the most prominent Wide Bandgap (WBG) materials. SiC devices have several advantages over the conventional silicon semiconductors, enabling high efficiency and compact converters. Among others, these advantages include higher temperature operation, higher voltage ratings for a given chip thickness, lower on-state voltage drops as well as higher thermal conductivity [12]. The SiC MOSFET has been particularly attractive for the market [13], due to having a high blocking voltage capability while retaining the fast switching capability owing to being a unipolar device. In fact, even faster switching may be expected in SiC MOSFETs, due to shorter drift regions in SiC [14].

Many of the benefits of using SiC devices are well established in the literature, as are some of the reliability concerns that the devices are currently facing [15]. Thorough testing of the reliability issues are necessary before widespread use of the device will be possible [16]. Moreover, current reliability testing of SiC MOSFETs in particular has to a large extent focused on challenges related to the threshold voltage and the internal body diode of the device. The reliability of packaging and encapsulation has not been dealt with to the same extent. These are important issues, considering that the main cause of failure in high power converters is failure of the semiconductor [17].

Reliability is a key concept throughout this work, and is defined by Lutz et. al as "the ability of a system or component to perform its required functions under stated conditions for a specified period of time" [3, p. 380]. Consequently, for a power electronics system to operate reliably, it must be able to operate over time in spite of a certain amount of degradation. This is a challenging task due to the relatively long expected lifetime of power electronic systems.

Reliability is thus a complex subject, as it comprises a wide range of degradation effects, being related to thermal, mechanical and electrical properties of the device. It has therefore been decided to restrict the attention of this master's thesis to reliability issues related to packaging. Although being important for the long-term reliability of a power semiconductor, aspects such as robustness and ruggedness will not be discussed. Moreover, the bipolar degradation of the device will not be covered in detail, as the time did not allow performing testing of this in addition to the threshold voltage instability and power cycling.

The aim of this master's thesis is to evaluate how reliability testing of the packaging may be performed. More specifically, the thesis will evaluate how the accelerated lifetime stress test called power cycling may be utilized to test the reliability of SiC MOSFETs. This has been a challenge due to the threshold voltage instability, which has complicated estimating the temperature of the device during the test. Therefore, the threshold voltage drift will also be investigated. The thesis will evaluate the use of the recently proposed  $V_{\rm SD}(T)$ -method [18], and perform power cycling on discrete devices using this approach.

### 1.2 Background

This master's thesis is written in conjunction with SINTEF Energy's project Reliability and Ruggedness of High Power High Voltage Power Electronics (ReliPE) [19]. The project aims to improve the reliability of high power converter systems, in addition to getting a better understanding of fault mechanisms in order to develop models for lifetime estimation during operation. As such, the goal of the thesis is to contribute to deepening the knowledge on reliability challenges of SiC MOSFETs, and how these might be tested.

In the course of the thesis, a test bench for performing power cycling on SiC MOSFETs has been developed. Some parts of the physical set-up has been reused from a previous a set-up developed by M.Sc. Øyvind B. Frank in his master's thesis [20]. That set-up was used in order to evaluate the power cycling capability of single chips from a press-packed IGBT module, and thus, several modifications were necessary.

### 1.3 Outline of Thesis

The outline of the thesis is provided in the following.

Chapter 2 presents advantages and disadvantages of SiC devices in general, and the SiC MOSFET in particular. Packaging of the device and how the junction temperature may be estimated are also presented.

In Chapter 3, the test rig for testing threshold voltage drift of the SiC MOSFET is presented. The results from the test are also provided.

The conventional power cycling procedure as well as the procedure for performing power cycling of SiC MOSFETs are presented in Chapter 4. Chapter 5 presents the test rig for performing power cycling on SiC MOS-FETs.

Chapters 6 and 7 present the results and discusses these, respectively. Finally, the conclusion of the thesis is given in Chapter 8.

# Chapter 2 SiC MOSFET

The potential advantages of using silicon carbide semiconductor devices have been known for several decades [21, p. 4], yet it was not until the previous decade that some of the SiC devices became commercially available [22]. In this chapter, some of the main advantages and disadvantages for SiC devices will be elaborated on. Moreover, the diode and MOSFET structures will be presented, in addition to the most common packaging types for MOSFETs. Lastly, a method for estimating the junction temperature of a pn-junction will be introduced, as this explains how the  $V_{\rm SD}(T)$ -method may be utilized to obtain the junction temperature of the SiC MOSFET.

### 2.1 Silicon Carbide Material Properties

The advantages of SiC devices are well documented in the literature. In the following, therefore, only the main advantages will be described. For a more thorough description of the properties of SiC, see e.g. [21].

Table 2.1 compares some of the most important material properties between silicon and SiC. SiC has several stable polytypes, meaning that the material has numerous stable crystal structures [21, p. 11]. These include amongst other 3C-SiC, 4H-SiC and 6H-SiC. Although 3C-SiC and 6H-SiC have been used for making power semiconductors, 4H-SiC is the current polytype of choice for power semiconductor manufacturers [14]. Therefore, SiC from now on refers to 4H-SiC.

One of the main advantages of SiC over silicon is the wider bandgap. This yields lower intrinsic carrier densities for any given temperature than what is possible for silicon [1, p. 661], leaving pn-junctions effective at much higher temperatures. Thus, SiC devices are able to operate at much higher temperatures for the same doping levels. Furthermore, significantly reduced leakage currents can also be obtained due to the larger bandgap, provided that the production quality is sufficiently good.

Another major advantage is the order of magnitude higher critical elec-

| Table 2.1: Comparison of Material Properties Between Si and SiC [7, 8]. |

|-------------------------------------------------------------------------|

|-------------------------------------------------------------------------|

| Property                                 | Silicon | Silicon Carbide (4H-SiC) |

|------------------------------------------|---------|--------------------------|

| Bandgap [eV]                             | 1,12    | 3,2                      |

| Critical Electric Field $[MV  cm^{-1}]$  | 0,3     | 3                        |

| Thermal Conductivity $[W m^{-1} K^{-1}]$ | 1,3     | 5                        |

| CTE [ppm/K]                              | 3       | 4,3                      |

| Youngs Modulus [GPa]                     | 152     | 501 (Anisotropic)        |

tric field. Not only does this reduce the length of the drift region by the same factor [14], but furthermore the specific on-state resistance is drastically reduced [1, p. 662], finally resulting in more than three orders of magnitude reduction of the on-state resistance [23]. This fact has enabled unipolar devices with considerably larger rating in SiC than what is feasible for their silicon counterparts. Moreover, in conjunction with reduced carrier lifetimes in SiC [1, p. 662], the shorter drift region reduces the amount of charge that needs to be moved during switching, hence allowing considerably faster switching [14].

The higher thermal conductivity of SiC devices allows a higher power throughput for the same junction temperature, or lower junction temperature for the same power throughput. Thus, this factor is expected to contribute to reduced losses. However, the higher thermal conductivity also leads to a higher temperature at the edges of the chip [8], which potentially could increase the stress on the underlying solder layer.

SiC has a larger coefficient of thermal expansion (CTE), meaning that for a given rise in temperature, SiC will expand more than silicon. Whether this is advantageous or not depends on the adjacent materials that are utilized in the device package. Generally, if the CTE of adjacent materials are similar, it means that they expand at a similar rate, which leads to reduced stress as opposed to if the CTEs are further apart. Two materials which often are found close to the chip is aluminum oxide and copper. Since the CTE of SiC is closer to their CTE than that of silicon, the SiC CTE is considered to be somewhat better [8].

On the other hand, the much larger Youngs Modulus is a clear disadvantage, as it renders SiC more than 3 times stiffer than Si. In fact, Herold et al. argues that this disadvantage is so crucial that it outweighs the advantages in CTE and thermal conductivity [8]. The increased Youngs modulus yields significant stress on the solder beneath the chip during power cycling, and can lead to drastically reduced reliability compared to silicon counterparts.

In conclusion, it seems like the SiC power semiconductors outperforms the traditional silicon devices in terms of electrical characteristics. However, mechanical properties indicate that silicon devices are preferable [8]. That being said, Herold et. al argues that if state of the art technology is utilized, these disadvantages may be mitigated, thereby achieving the desired reliability [8].

### 2.2 Silicon Carbide Devices

This section will briefly explain the PiN diode and MOSFET structures. The structure of SiC devices is largely identical to what is found in silicon devices [14], and hence, most of this section will be based on literature explaining silicon devices. Whenever there is a difference, however, the particularities of SiC will be emphasized.

### 2.2.1 PiN Diode

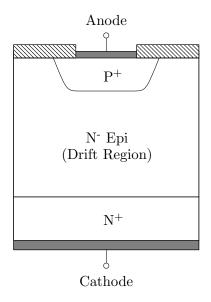

The structure of PiN (Positive intrinsic Negative) diode is displayed in fig. 2.1. The + indicates a highly doped region, whereas the - indicates a moderately doped region. The drift region in the centre of the structure is thus several orders of magnitude lower in doping, however it is not truly intrinsic as its name may allude to [21, p. 287].

Figure 2.1: Structure of the PiN diode [1, p. 525]

Since both the density of free holes and electrons decrease when approaching the  $P^+N^-$  junction, both carriers will diffuse across it, which causes a potential barrier at the same junction. This potential barrier results in a region called the depletion layer, which is depleted of any charge carriers, except those that are generated by thermal ionization. The latter are however immediately swept away from the depletion layer due to the electrical field caused by the potential barrier. Moreover, the potential barrier impedes

any current flow, as the drift and diffusion currents sum to zero for both the holes and the electrons [1, p. 516].

Applying a negative anode-cathode voltage enlarges the potential barrier, such that the device is blocking any current conduction. This is termed reverse bias. If a positive anode-cathode voltage is applied, the potential barrier is reduced and the device is said to be forward biased [1, p. 515]. When in this state, holes diffuse from the P<sup>+</sup>-region into the drift region. Once the injection of holes is sufficiently large, electrons from the N<sup>+</sup> layer are attracted into the same region. This finally results in considerably improved conductivity of the drift region, and is termed conductivity modulation [1, p. 532].

### 2.2.2 MOSFET

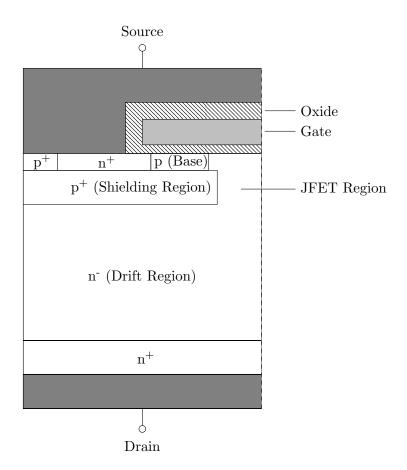

There exists several variations of the Metal Oxide Semiconductor Field Effect Transistor MOSFET structure, the major ones being the planar and the vertical MOSFET. Currently, planar devices are commercialized [24], while vertical devices, more specifically trench MOSFETs, are announced for mass production [25], and thus likely close to being commercialized. Since the literature mainly has focused on devices using the planar structure [2, p. 236], this will be considered in the following. Therefore, unless stated otherwise, MOSFET now refers to the planar device type.

The structure of the SiC MOSFET is largely identical to that of the Si MOSFET, except that the base doping is reduced and that a heavily doped shielding layer is added to the conventional silicon D-MOSFET structure [2, p. 236]. This can be seen in fig. 2.2, in which a simplified view of one half of the structure is presented. The larger SiC bandgap would cause excessive threshold voltages, which necessitates the reduction of doping of the base region. Reducing the latter could potentially lead to reach-through problems due to the high critical electric field in SiC. Without the shielding layer, a trade-off between large threshold voltages and small breakdown voltages would have to be made. However, by including it, reasonable threshold voltages can be maintained while at the same time not compromising on breakdown voltage levels.