## Analysis and Visualisation of Clock Tree Power in a full-chip-design

Hans Jørgen Myrvang Ro

Electronics System Design and Innovation Submission date: June 2014 Supervisor: Snorre Aunet, IET Co-supervisor: Jan Egil Øye, Nordic Semiconductor

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# Analysis and Visualisation of Clock Tree Power in a full-chip-design

Hans Jørgen Ro

June 2014

MASTER THESIS

Department of Electronics and Telecommunication Norwegian University of Science and Technology

Supervisor 1: Snorre Aunet Supervisor 2: Jan Egil Øye

## Preface

This thesis is the final work of my masters degree in digital circuit design at NTNU. The project was suggested by Jan Egil Øye at Nordic Semiconductor. I have worked together with him and other engineers in the digital design department at Nordic in the design of this tool. My advicor Snorre Aunet has guided me in writing this report.

Trondheim, 2014-06-07

Hans Jørgen Ro

## Acknowledgment

I would like to thank the following persons for their great help during my thesis:

- Jan Egil Øye, my adviser at Nordic Semiconductor for suggesting the project and giving feedback with great enthusiasm. It really helped to achieve a useful tool. Your insight on the problems and your constructive feedback has helped me immensely in writing an interesting and useful thesis.

- Snorre Aunet, my adviser at NTNU for giving me feedback on the writing of this thesis. Keeping a fun project academically relevant is hard without a guide.

- Nordic Semiconductor for giving me a good work environment to focus on me thesis in, and everyone at the digital design group for being interested in what i have been doing.

H.J.R

## Summary

In this thesis a tool to graph power density in a chip by combining placement data with power estimation results has been made for Nordic Semiconductor. The goal was to utilize the data generation power of the power estimation tool, preserving the detail of the data instead of looking at averages and totals. Extra focus was put on displaying power from clock trees, as they are generated in a part of the design process where power estimation data based on placement and routing is available. This thesis presents results from a tool able to graph power consumption over the chip area, a feature not seen in commercial tools. A thorough description of the features, how they were obtained and why they were needed is also included. The tool was developed with continuous feedback from the engineers that will be using it. It was implemented in the design phase for Nordic Semiconductor chip currently in progress to gain insight in the clock trees. The tool showed that several test benches used for estimating clock power were in fact printing the exactly the same output, meaning they were redundant.

The tool transform power estimation reports to frames optimized to be joined together for animations. It can process reports with an average run time of 1.5 seconds per report when each report contains 40 000 cells. Rendering each frame takes an average of 2.1 seconds. The tool helps the designer to gather information on ineffective layout in reports that were previously deemed too large to be useful. Visualizing data over the chip surface shows rich information in a intuitive way, which can be useful for other domains.

## Contents

|   | Pref | nce                                                 |

|---|------|-----------------------------------------------------|

|   | Ack  | nowledgment                                         |

|   | Sun  | mary                                                |

| 1 | Intr | oduction 1                                          |

|   | 1.1  | Background                                          |

|   | 1.2  | The goal of the thesis    2                         |

|   |      | 1.2.1 Meaningful visual representation 3            |

|   | 1.3  | Outline                                             |

|   |      | 1.3.1 Theory 3                                      |

|   |      | 1.3.2 Method                                        |

|   |      | 1.3.3 Results                                       |

|   |      | 1.3.4 Discussion                                    |

| 2 | The  | ory 5                                               |

|   | 2.1  | Ultra Low Power challenges                          |

|   |      | 2.1.1 Problems with scaling                         |

|   |      | 2.1.2 Clock skew and power aware clock generation 6 |

|   | 2.2  | Clock tree design process                           |

|   |      | 2.2.1 Current workflow                              |

|   |      | 2.2.2 Adittional file generation                    |

|   |      | 2.2.3 Issues with static power analasys             |

|   | 2.3  | Relevant tools used in the design process           |

|   |      | 2.3.1 Synopsis IC-compiler 10                       |

|   |      | 2.3.2 Synopsis Primtetime PX                        |

|   | 2.4  | User centered design                                |

|   | 2.5                        | Regular expressions        |                                            |    |  |  |

|---|----------------------------|----------------------------|--------------------------------------------|----|--|--|

| 3 | Met                        |                            | 15                                         |    |  |  |

|   | 3.1                        | Reque                      | est from Nordic                            | 15 |  |  |

|   |                            | 3.1.1                      | Quick analyze tool                         | 15 |  |  |

|   |                            | 3.1.2                      | Graphing power density                     | 16 |  |  |

|   | 3.2                        | Choo                       | sing a language                            | 16 |  |  |

|   | 3.3                        | Input                      | data and quick analysis tool               | 17 |  |  |

|   |                            | 3.3.1                      | Input data                                 | 17 |  |  |

|   |                            | 3.3.2                      | Power report analysis                      | 20 |  |  |

|   | 3.4                        | Graph                      | ning tool                                  | 21 |  |  |

|   |                            | 3.4.1                      | Program work flow                          | 22 |  |  |

|   |                            | 3.4.2                      | Constructing data for surface plots        | 23 |  |  |

|   |                            | 3.4.3                      | Circuit layout visualization               | 25 |  |  |

|   |                            | 3.4.4                      | Problems when visualizing circuit macros   | 28 |  |  |

|   |                            | 3.4.5                      | Showing the total power used in each frame | 30 |  |  |

|   |                            | 3.4.6                      | Identifying points of interest             | 32 |  |  |

|   |                            | 3.4.7                      | Logarithmic plotting                       | 34 |  |  |

|   |                            | 3.4.8                      | Excel print                                | 35 |  |  |

|   | 3.5                        | View                       | area                                       | 35 |  |  |

|   |                            | 3.5.1                      | The surface plot                           | 36 |  |  |

|   |                            | 3.5.2                      | Categories plot                            | 36 |  |  |

|   |                            | 3.5.3                      | Top 10 peaks                               | 38 |  |  |

|   |                            | 3.5.4                      | Animation                                  | 38 |  |  |

|   | 3.6 Testing the visualizer |                            | ng the visualizer                          | 39 |  |  |

|   |                            | 3.6.1                      | Real life application test                 | 39 |  |  |

| 4 | Res                        | ults                       |                                            | 41 |  |  |

|   | 4.1                        | Key to                     | o the output graphs                        | 41 |  |  |

|   | 4.2                        | 4.2 Test in design process |                                            |    |  |  |

|   | 4.3                        |                            |                                            |    |  |  |

|   | 4.4                        |                            | ario plotting                              | 55 |  |  |

|   |                            |                            |                                            |    |  |  |

| 5 | Discussion                 |                           |                                                   |    |  |

|---|----------------------------|---------------------------|---------------------------------------------------|----|--|

|   | 5.1                        | 5.1 Merits of visualizing |                                                   |    |  |

|   | 5.2 Analyzing test results |                           |                                                   | 60 |  |

|   |                            | 5.2.1                     | Utilizing clock visualization in the design phase | 60 |  |

|   |                            | 5.2.2                     | Animated graphs from time based estimation        | 61 |  |

|   |                            | 5.2.3                     | Graphing scenarios                                | 63 |  |

|   | 5.3 Future work            |                           |                                                   | 63 |  |

|   |                            | 5.3.1                     | Keeping uniform chip temperature                  | 63 |  |

| 6 | Conclusion                 |                           | 65                                                |    |  |

| A | A Acronyms                 |                           |                                                   | 67 |  |

| B | B Quick user guide         |                           |                                                   |    |  |

| C | C The code                 |                           |                                                   | 73 |  |

## **Chapter 1**

## Introduction

This thesis describes the design and test process of a graphing tool made on a request from Nordic Semiconductor. The tool visualizes when and where on a chip power is consumed by combining reports from the Primetime PX' power estimation tool with location information from the IC compiler. The aim is to use it to improve the understanding of the generated clock trees so they can be made more efficient.

## 1.1 Background

Nordic Semiconductor is a Norwegian company that focuses on ULP(Ultra Low Power) chips for short range wireless communication. These chips can be found in battery driven wireless products produced around the world ranging from computer mice to heart rate monitors. In the ULP wireless chip industry reducing power is always important. This thesis was suggested by Jan Egil Øye to gain new tools for reducing power consumed by the clock tree. The clock tree is a significant source of power consumption, often taking up as much as 40% of the total power[1]. Clock tree power consumption will only be harder to limit as circuits scale down, and it is along with leakage power one of the main hurdles of chip scaling[3]. Many different power reduction techniques for clock trees have been proposed[1]. Understanding the power consumption is key to using the right methods of reducing it, and there is currently no commercial tools to visualize power density over a circuit surface over time. The idea of using a power

consumption density plot to understand the circuit builds on a graph of IR drop made by Martin Olsson. It was made in relation to his work with Jhonny Phil who now works at Nordic and Per Larsson-Edefors, a professor at Chalmers[8]. The graph was a 2 minute animation that showed IR drop over 2 clock periods, and sparked interest in future

## 1.2 The goal of the thesis

The goal of this thesis is to give the designer a tool that can enrich data from estimation so that he or she can better evaluate the changes done to the clock tree. This should be achieved by a visualization tool that can combine location data from the placement and routing tool with detailed power data from the estimation into a power density plots. The plots should clearly show power density over the circuit surface, which is much more informative than the total power sum currently used. The location and detailed power data are not used in the current design process, but are easily produced by the tools already in use. The graphing tool should not add significantly to the data generation time, and be optimized for finding interesting data in the reports. The project caught my eye, as I had some experience with parsing reports for graphing. During my last summer internship I gained relevant experience by making a tool for running simulations on the newest build and graphing the history of the results to a web page. The opportunity to write for a well known company was also very tempting.

The basic request was to create a program able to parse reports containing power consumed per cell, resulting from from power estimations on the circuit. This was to be combined with placement data gathered from IC Compiler, a layout tool from synopsis, to create a new data set showing power density. The power density data was to be plotted in a three dimensional graph over the circuit layout and should also be able to animate variations over time. The specification of this graph was quite loose, and I worked together with the engineers who will use the tool in order to define the visual representation. By doing this I got very useful feedback, and was able to make sure the tool would have the features the designers would want. This way the program would fulfill its purpose and will be able to help engineers reduce power consumption in the clock tree by evaluating more detailed data.

### 1.2.1 Meaningful visual representation

Finding out what information is interesting and how to display it is a big part of this thesis. The system designers can easily generate vasts amount of data, but it is difficult to get access to rich data that is also simple to read. The graphs should help the engineers find the vital data points, and separate them clearly from the rest of the data. To achieve this you need to test the program with the engineers to figure out what questions are being raised, and how to find the answers in the data.

## 1.3 Outline

## 1.3.1 Theory

Gives the reasons to put focus on power consumption of clock trees. Covers how they are generated in the design process, and how the power usage is analyzed. Shows work flow of the tool is supposed to fit into, and how that will happen. Covers the programs used to generate the data needed to create the graphs.

### 1.3.2 Method

Describes the design process done in cooperation with the engineers at Nordic Semiconductor. Program features are explained with motivation of why they are needed. The program flow, and the explanation of each feature should ease the design process for someone wishing to make a similar tool tailored to other domains. Also describes how the program was included in the design process for final testing.

### 1.3.3 Results

What the graphs contain is presented in a clear manner. Presents graphs from the tool from several different user cases where points of interest are pointed out.

### 1.3.4 Discussion

The discussion goes through the results point by point and compares the result with the goal of the thesis. Special attention is put on how the features of the program highlights important data. The reader can also see how to further improve the work flow around the program as well as suggestion for other work.

## **Chapter 2**

## Theory

To understand how to build a tool that can help designers create better clock trees, you have to look at how they create the current clock trees. This chapter will present the environment for clock generation to help show the motivation. The tool itself is a programming issue, and high performance has not been in focus, as it is not necessary in this particular domain. The theory part is focused on the application of the tool for Nordic Semiconductor, and why it is needed. A lot of the insight in this chapter is based of meetings with Jan Egil Øye, where he explained the designing process.

## 2.1 Ultra Low Power challenges

The Internet of things is a term many use to predict the next step in technological advancement. I the current state a Internet of computers and smart phones exists, connecting people together for easy communication. The Internet of things describes object communicating with each other automatically to improve information flow. For objects to communicate they need wireless components to send messages. Ultra low power technology is vital to this idea, as many objects are not normally connected to power, so they need to be powered by batteries. There are many ways to extend battery life. The easiest way is to lower performance and removing features. Wireless chips are focused communication though certan wireless standards, so the performance and features are set by requirements of the standard used. The other way to reduce power use is to reduce wasteful switching and unnecessary activity. This means optimized placement and routing, and cutting off the power of inactive modules on the circuit. By gating the clock tree, you can also stop the clock from being propagated to the inactive modules. When the circuit is idle nearly the entire circuit will be cut from power. 7

#### 2.1.1 Problems with scaling

As technology advances, the systems get more advanced, and the circuit elements become smaller. Scaling down circuits is great for the power used per computational power, but since the systems are becoming larger and more complex, this effect is not enough. New challenges and unexpected power consumers appear when the scale becomes smaller and circuits become larger. The paper "Impact of technology scaling in the clock system power" [3] concludes that clock tree power consumption will increase as circuits scale down. Together with leakage power, it will be one of the main challenges in keeping power consumption from scaling badly with size.

#### 2.1.2 Clock skew and power aware clock generation

One of the main contributors to clock trees consuming power is that as the systems become larger, the clock trees have to be more complex. This has its roots in that the distance the clock signal has to travel increases relatively to its clock frequency. The distance the clock signal travels will result in a delay. Since clock signals are the time keeping mechanism of the circuit, a delay in the clock signal can result in signals arriving at incorrect times, ending in a circuit that does not work. The faster the clock frequency, the smaller delay is tolerable. To counter this, clock trees have to be balanced properly, making sure every part of the clock tree has traveled approximately the same distance. Clock tree generation is often handled by place and route tools like IC Compiler[12](more in section 2.3.1). Since the 80s the scientific community have been aware that the clock tree power consumption would need attention when planning clocks[10]. Since then, progress has been made on techniques that generate clock trees with a goal to minimize power in addition to keeping requirements to clock skew[1].

## 2.2 Clock tree design process

Through meetings with Jan Egil, I have gained insight in the part of the circuit design process where clock trees are generated. I will present the current design process, and where the tool in this paper fits in.

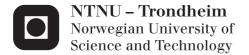

Figure 2.1: Current workf low for clock tree generation.

#### 2.2.1 Current workflow

A flowchart showing the work flow used in Nordic Semiconductor can be found in Figure 2.1. After the Verilog description of the circuit is finalized, the Verilog net list is sent to Synopsis IC Compiler. IC Compiler is a place and route tool that will create a layout of the circuit that includes a balanced clock tree connected to all the circuit elements. There are restrictions on the clock tree that the designer can modify. From IC compiler to Primetime PX there are two paths. They both use the layout of the chip and the parasitic data. The parasitic data includes the resistance of every cell and the impedance of the following wires. The quick path to Primetime PX uses constraints from IC Compiler to generate static reports on the clock tree. These constraints include definitions for each clock pulse, which can be used as switching data. The other path needs a test bench to create actual switching activity dumps(value change dump: vcd), which is used for more accurate analysis. The reports from the power analysis are evaluated, and the designer will then modify restrictions for the clock tree. This cycle continues until the designer is happy with the resulting clock tree. This whole work flow happens in the time intensive sign off phase right before the chip is sent to tape out. This means that the designer has a limited time window to optimize the clock tree, as a delay in prototyping is costly.

**Understanding the prototype** When the prototyped chip returns from production, it will be tested and measured. At this time circuit test benches are ready. Then the optional path through simulation seen in figure 2.1 is used. This is a less time critical phase, and the increased accuracy in the power analysis is valuable. When the prototype is ready, small adjustments can still be made to the clock tree but major changes are avoided. It is however still possible to reduce clock tree power consumption though minor tweaks.

#### 2.2.2 Adittional file generation

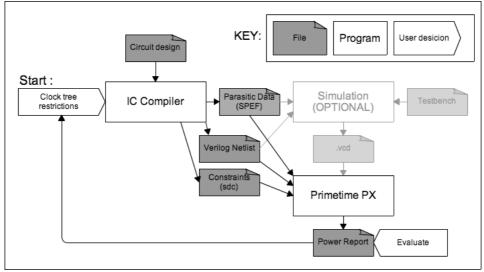

For the current work flow, the designers use a single total power number to judge the merits of the clock tree. To create a power density graph, additional information is needed. Extracting this is easily implemented in the work flow already in use. Figure 2.2 shows the target work flow planned after the tool has been constructed. The following files need to be generated:

**Location files** The location of every cell can be printed out from the IC Compiler once the layout is done.

**Power per cell** The reports giving power per cell can be generated by the Primetime PX power simulation.

#### 2.2.3 Issues with static power analasys

Since most of the clock tree generation happens in a time critical phase power estimates has to be done quickly. The estimation is based of a simple toggle mode. Every clock source is set to toggle constantly and the signal is propagated

Figure 2.2: Desired work flow for clock tree generation including thesis contributions.

through the buffers, gates and registers. Static power analysis is mostly used for estimating leakage power[2], as you don't need activity data as you would for active power. Since a clocks main trait is that it switches constantly, static analysis can be conducted with a pure toggle function on the clock(contained in the sdc file in figure 2.1). For a circuit with a single clock and no possibility to shut down parts of the circuit, this would be quite accurate. With more advanced circuits, there are certain features which will make this inaccurate. Jan Egil Øye mentioned these as main error sources through our meetings:

**Clock gating** Not all parts of the circuit are used in every mode. When starting up or loading a program, the wireless transmitter for example will not need any power. Some modules might have high down time. With clock gating, the branch of the clock tree connected to the module will not consume any power during downtime. In the static power estimation this will not be visible.

**Changing clock frequencies** Some modules in the circuit might be able to run on different clock frequencies. The correct frequency will be gated in, and the other one will be blocked. With static power estimation, both frequencies will be active in that area at the same time. This will inflate the power spent in that area.

To simulate clock gating, additional power estimations can be run where a gate will reduce all power spent behind it with a certain percent. By doing several estimations with different percentages, you can get an idea of how much the gates are helping. This does not include the actual down time behind every gate, so it can be misleading.

## 2.3 Relevant tools used in the design process

#### 2.3.1 Synopsis IC-compiler

According to the Synopsis website[12]:"IC Compiler is a single, convergent, chiplevel physical implementation tool that enable designers to implement today's high-performance, complex designs on schedule". The IC-compiler has several tools for optimizing the circuit layout, and tools for generating clock trees. More information can be found on the synopsis web page.

Clock Tree Synthesis, CTS, can be performed in IC-compiler by adding specific clock tree constraints in different scenarios. By adding these constraints, the clock tree implementation can be optimized for skew, insertion-delay and power-dissipation. Some of the more important constraints used by Nordic include:

**Transition-time requirement** Sets the maximum transition time allowed within each clock tree domain (typically rise time). This means that the transition time on the output of each individual clock tree buffer inserted during CTS will meet the target transition time requirement, typically in the order of 0.5-1 ns.

**Insertion-delay** Maximum time-delay from the clock source pin through the clock tree and to the target clock sink pin. Typically, this parameter defaults to "0" meaning the CTS-implementation will target minimum possible insertion delay. Sometimes a target insertion delay is necessary to constraint because two or more on-chip clocks must be balanced to each other to obtain better timing in clock-domain-crossing scenarios.

**Exclusion points** Certain parts of the circuit may only have internal connections and can be excluded from the global clock tree constraints. This means that clock sink pins behind these exclude-points will not be balanced with respect to skew and insertion-delay as part of the CTS. Adding such exclusion points can simplify the clock tree implementation and thus save power dissipation but it must be used with care.

**Transition time beyond exclusion points** When part of the clock tree has been excluded from the CTS-implementation by introducing exclusion-points, a local requirement can be set to ensure that transition time is still maintained behind the exclusion point although there will not be any balancing with respect to clock skew.

**Target skew** Allows the designer to slack the requirements of low skew. A less strict constraint on the target skew can simplify the clock tree implementation by reducing the number of buffers required and thus reduce power. The penalty may be that it will be more difficult to meet overall timing-closure but this will be a trade-off individual for each chip.

**S** ome of these parameters may be set globally for the whole design like global transition-time requirements and zero insertion-delay and skew. However, clock-tree-specific transition-time and exclusion points are examples of important user-defined constraints that gives the designer the opportunity to use her or his detailed knowledge of the circuit to improve the clock tree implementation and thus improve power dissipation.

#### 2.3.2 Synopsis Primtetime PX

Synopsis Primetime[13] is a tool made for use during the sign-off phase; the final phase before delivering the plans to production(called tape-out). It aims to help find faults in the circuit before it is too late to fix them. Primetime has a subprogram called Primetime PX which can do power analysis on the circuit. You can get power analysis based of simulation dumps, or choose a static estimation as described in 2.2.3. Primtime PX uses switching activity, parasitic data and the layout to do accurate power analysis.

**Static power estimation** Static power estimation fetches its activity data from the constraints file from IC compiler. These constraints are much quicker to analyze as you only need a single power number as a result. This method only works for the clock tree as the switching activity for the clock tree is static. This estimation of a never changing clock is deemed good enough for the time sensitive sign off phase, but the problems are mentioned in 2.2.3.

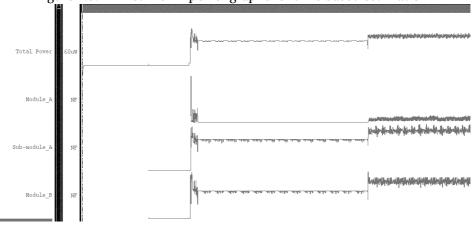

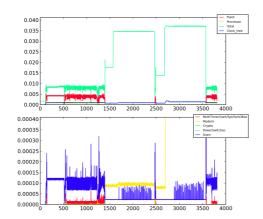

**Time based power analysis** Time based power analysis is based on simulation. The circuit layout, the parasitic data and a test bench driving all the in-signals is required for the simulaton. The resulting activity dump(vcd file) can be used instead of the constraints (sdc) file used in the static analysis, as seen in figure 2.1. The power analysis based on these files will result in a time based view of how much power is used in the entire circuit. You can also choose to highlight separate modules seen in figure 2.3. These types of graphs where the modules are separated are used later in the design process when the circuit power consumption is measured in the lab. The power measurements only show the total power consumption over time, so the estimations help the designers understand what is using the power in the chip. With the time based estimations a user can choose to generate a series of reports each containing the average power for each cell within consecutive time frames. This will make each frame a sampling point, and you can see what cells consume power in each time frame.

Figure 2.3: Primetime PX power graphs for time based estimation

## 2.4 User centered design

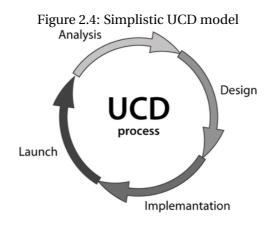

When developing a tool it is helpful to have a clear design methodology in mind. In this project the initial requirements for the tool were quite few, and there were a lot of design decisions to make. User Centered Design (UCD) is a process which put heavy emphasis on the needs the user of the final product[4]. The user can be involved in every state of the design process from identifying the problem to validating the solution. Reaching out to the user is often part of the problem, but when working alongside the user the process can be split into four repeating phases:

**Analyze** Involves finding the problem, identifying exactly what needs to be fixed. This can be done through interviews, questioneers or discussion with the user.

**Design** Finding a solution to the problem. This involves brainstorming, setting up different strategies, and choosing a plan of action. Users can be contacted for ideas in brainstorming or help decide upon the best strategy to solve the problem.

**Implementation** Implementation phase means carrying out the plan of action. Users are less part of this process, but if the implementation is not straight forward and changes has to be made to the plan of action, they can help modify the strategy.

**Launch** Testing is important to see if the problem identified is actually fixed. Launch is showing the customer what the next iteration of the product looks like. Users can best identify if the solution is successful. Once one problem has been fixed, other problems might arise.

**T** his feedback loop continues until the product is ready for release, and will continue for further patch updates in sowftware production.

## 2.5 Regular expressions

Regular expessions(Regex) is a standard for searching in strings[11]. The standard allows a string made by the user to produce matches when used on strings or texts. By following the rules, you can make advanced searches with just a single input string. There are boundless regular expression resources online, and the technique is widespread in programming after it got known in the linux terminal based program grep. Now many languages support i in their native libraries, like for example python[9].

## **Chapter 3**

## Method

The program for this project was developed in close collaboration with my adviser at Nordic Semiconductor and other engineers working in the digital design group. The idea of the program was quite general and the features were not set so they needed to be decided as part of the thesis. This ended in a user centric design process where the engineers had direct influence over how the tool was to display the data, and how it would fit into the design work flow. This chapter describes the path from a loose set of requirements to a finished product. It also encompasses the testing scheme.

## 3.1 Request from Nordic

The programs are based of the initial requests from Nordic Semiconductor. In order to improve their basis for decision on generated clock trees, they wanted a quick analyze tool, and a graphing tool. In this section the basic requirements and intentional use will be presented.

### 3.1.1 Quick analyze tool

The quick analyze tool is intended to run on extended reports in the first phases of setting constraints on the clock tree algorithm. It is intended to get a quick overview over what types of elements in the clock tree the power is spent. This can give an easy to use, but rough pointer at what to adjust in the constraints to get a more efficient clock.

#### **Design requirements**

- Low run time

- Give an overview of the report

- Allow user set categories and search terms

### 3.1.2 Graphing power density

The main goal of the thesis is to make a tool able to combine power data with location data to create a power density plot. The goal is to used it for optimizing clock trees and understanding the circuits power consumption in general.

### **Design requirements**

- 3-Dimensional graph displaying power density

- Automatically construct data from two types of reports:

- Power used per cell

- (x,y) location for each cell

- · Visual representation of circuit to improve readability

- Allow for animated graphs based on several consecutive reports, to graph density over time

- Keep the program as generic as possible to allow for other uses

## 3.2 Choosing a language

To start programming, I had to choose a programming language. I chose Python as it is a language I am familiar with, it also has many attributed which fits the project well.

**Widespread** - Python is a popular and established language so it is easy to find someone who can follow up on the code when I am done with the thesis.

**Open Source** - With no licence fee distributing it around the company is painless. Compared to plotting in Matlab.

**Good for prototyping** - Python has many libraries that help the programmer get something up and running fast. Therefore it is well regarded for its strength in prototyping. This is a strong argument when using User Centered Design. Python has good tools for all the tasks needed in this project, allowing the whole work flow to be gathered in a single language:

**Graphing library** - Matplotlib is a long running graphing library for Python[6]. It allows gnuplot style graphing directly from Python.

Easy file handling - Reading and writing to files is trivial in Python.

**P** ython and other scripting languages are regarded as slower than compiled languages like C. This is the strongest argument against using Python for this thesis. The programming challenge is not very complex, so I decided that the extra run time would be less significant to the project than the ease of use. If run time should be a problem, alternative interpreters like pypy[7] can greatly improve run time.

## 3.3 Input data and quick analysis tool

In this section I will first present the form factor of the input data tool is supposed to graph. I will then move through the solution created for the quick analysis tool.

#### 3.3.1 Input data

The input data consists of two files. The report from the power simulation and a location report, telling where on the circuit each cell is situated. The size of these files can vary a lot. Circuits can have several hundred thousand cells, but in this section we will only show a few example lines, as the length of the file does not change the complexity of reading it.

#### **Power reports**

The power reports are the results of the power simulation. The quality of the simulation can vary greatly. The report under is a dummy report showing the structure. The names of each cell has been simplified. It is important to note that each cell name string is unique. The hierarchy of names will show what part of the circuit the cell is, and the cell name at the end will show what type of cell it is. What identifies a cell might be an abbreviation for the technology name or simply the string reg as shown in the example power report in listing 3.1.

| Listing 3.1: Exa | mple power | report from | Primetime |

|------------------|------------|-------------|-----------|

|------------------|------------|-------------|-----------|

```

*****

Report : Averaged Power

-cell_power

-leaf

-sort_by cell_internal_power

-power_greater_than

0

-nosplit

Design : name

Version: G-2012.06-SP3

Date : Sat Feb 8 06:51:52 2014

******

Attributes

_____

a - Annotated internal & leakage power

b - Black-box (unresolved) cell

c - Clock pin internal power only

d - Does not include clock pin internal power

h - Hierarchical cell

Internal Switching Leakage Total

Power Power Power ( \ Attrs

Cell

_____

hierarchy/structure/cell1reg 3.905e-06 8.377e-06 1.437e-10 1.228e-05 ( 0.18%)

hierarchy/structure/cell2gate 3.835e-06 6.768e-06 1.435e-10 1.060e-05 ( 0.15%)

hierarchy/structure/cell3buffer 3.722e-06 2.144e-06 1.437e-10 5.866e-06 ( 0.08%)

....(80 000+ lines skipped)

hierarchy/structure/cell3reg 1.032e-09 6.677e-08 3.145e-11 6.577e-08 ( 0.00%)h

_____

Totals (85793 cells) 7.537e-04 1.114e-03 5.134e-03 7.002e-03 (100.0%)

```

1

The lines we are interested in are listed between the to dashed lines. Each line is simply a string followed by different numbers. Each number is separated by a space and represents internal power, switching power, leakage power, total power and percentage power. Exceptions of this rule happen in the percentage field, where a space can come within the parenthesis. Sometimes a letter will follow at the end of the numbers as in the last line of the example report. This letter represents a certain attribute shown in the attribute list. As a more sporadic exception there would sometimes be a line break behind the cell name instead of a space, effectively splitting the interesting data over two lines.

#### Location file

The location file is generated by extracting only the location data from the ICcompiler. The example file in listing 3.2 shows the standard for the location files that we have to parse.

Listing 3.2: Example input for cell location data

```

hierarchy/structure/cell1register;register_type4;3401.000 2631.000

hierarchy/structure/cell2gate;gate_type1;3380.000 2823.000

hierarchy/structure/cell3buffer;buffer_type3;3369.000 2762.000

....(80 000+ lines skipped)

hierarchy/structure/cell3register;register_type4;824.800 1749.52

```

The file is a comma-separated values(CSV)[15] file with semicolons as separators. This type of file is possible to open directly in excel. The fields contain unique cell name, reference name and a (x,y) tuple split by a space. The (x,y) tuple gives the location of the cell.

#### Parsing the files

Parsing files for information is a trivial problem with Python, especially when they are as simple as these. You can take in a file line by line and handle them with functions in the string library. I will quickly explain the way I did it for this project, but this will be different for any other report. The important thing is to know what data you need to come out of the parser. For the power report simply ignore any lines outside of the two dashed lines. To avoid the problem of the extra space in the "% of total power" field, you can remove all instances of "(" and "( ". To separate the last letter that sometimes appear at the end of the line replace "%)" with space. Then you can use tools as string.split() to separate words so you have the names and numbers in separate strings as a list. You can then pick the fields in the list you are interested and cast the number strings to float. Python handles casting directly from scientific notation strings to float. From the power file the parser return a list where each item contains the data for each cell. Each data element is again a list with the name as the first element, and the power from the different power categories following as floats. It is important to add a way to ignore the letter that may show up at the end of the line. This can be done by always only returning the first 6 elements of the list for each line.

From the location file we are not interested in the reference name, but the cell name and the x and y position of the cell. Python has good a built in library for parsing .csv files. However since the x and y positions are in the same field, it has to be split with space as a separator before being cast to floats.

#### 3.3.2 Power report analysis

The power reports contain the power for each cell, with tens of thousands to hundreds of thousand lines the files are practically too big to use without any tools. The files do contain total power at the bottom, but this summary could be more detailed. A more useful summary would not only show total power, but also differentiate between what types of cells consumed the power. This is achieved by allowing the user to define a file with several categories. Each category can have several search words that will add the power of a cell name matching the search word to that category. I found out that the engineers were all quite used to using regular expressions to search files. A simple configuration file for this tool would look like this:

Listing 3.3: Example configuration file for quick analyze tool

```

----Buffers

^.*buffer.*$

----Gates

```

The quadruple dash signifies a new category, while the the regular expressions in between gives the search phrases that should mach the cells that fit in that category. A user can also add a list of specific names for cells to the category since some cells might be hard to match within their right category with a more general regular expression. The program will output reports in the following format:

| U            |                   |                    |                  | -              |                   |                |   |

|--------------|-------------------|--------------------|------------------|----------------|-------------------|----------------|---|

| Element type | Internal Power(W) | Switching Power(W) | Leakage Power(W) | Total Power(₩) | (%)of total power | #Cells matched | ï |

| Buffers      | 9.365402e-05      | 2.551691e-04       | 2.584510e-08     | 3.488645e-04   | 5.654000e+01      | 796            | ï |

| Gates        | 7.189660e-05      | 3.805332e-06       | 3.942009e-08     | 7.574141e-05   | 1.217000e+01      | 170            | ï |

| Registers    | 1.043306e-04      | 6.061721e-06       | 1.216321e-07     | 1.105144e-04   | 1.784000e+01      | 11026          | ï |

| Others       | 2.064204e-05      | 6.144012e-05       | 5.521876e-08     | 8.213404e-05   | 1.324000e+01      | 2761           | ī |

| Total        | 2.905233e-04      | 3.264763e-04       | 2.421161e-07     | 6.172544e-04   | 9.979000e+01      | 14753          | ī |

|              |                   |                    |                  |                |                   |                |   |

Figure 3.1: Screen shot from terminal output from summarizer

Any cells that cannot be matched by the different categories are put in the "Others" category. In this particular example, only a simple category file is present, and all exceptions from the simple naming scheme end up in others. The program runs within a second, so refining the categories file with additional categories is possible. This tool tool turned out to be uninteresting once the graphing tool was finished. The graphing tool was suspected to be slower and not usable for fast summaries. However, as you will see in this chapter, the aspect of user defined categories were included in the graphing tool in a similar manner, and the run times were unproblematic.

## 3.4 Graphing tool

The graphing tool is a larger project than the analysis tool. The amount of data involved is significantly higher and the result more refined. It is supposed to be able to take in several consecutive reports, and graph the power consumption over the surface of the chip in a animated graph. This chapter goes through the features of the program in the order they were designed. This represents the user centered design methodology followed in this project. Each new feature was added after feedback with the users after they saw the newest prototype at work.

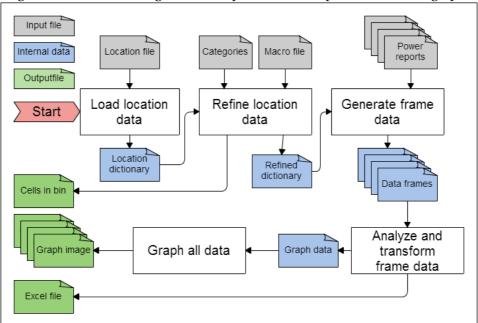

### 3.4.1 Program work flow

The work flow of the program is not similar to the order tasks are presented in this section. To get a grip of where in the work flow each feature is added, I will first quickly present the final work flow of the program as seen in figure 3.2. The introduction will be brief, as every feature is explained in more detail in their own section.

Figure 3.2: Work flow diagram for the process from reports to finalized graphs

**Load location data** Reads location data from a file and stores it in a dictionary sorter by cell name.

**Refine location data** Finds the right bin for every cell, and figures out what categories each cell belong to. Prints out the file containing the cell names held in each bin.

**Generate frame data** Reads the power reports and creates a data set for every frame by adding the power number for each cell to the correct bin.

**Analyze and transform frame data** Finds maximum values in each frame and transforms the data to logarithmic plotting.

Draws all graphs Reads all the graph data and sequentially draws each frame.

#### 3.4.2 Constructing data for surface plots

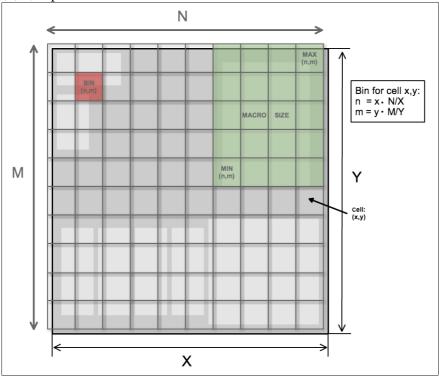

This is the core function of the program. The data needed to make a single image for the animation needs to be gathered and constructed from two different data sets. The plot data needs to be a N\*M matrix containing the amount of power used in total within the area of the chip corresponding to each n,m bin. For each time slice there will be a unique power report, resulting in an unique data plot. N and M are numbers chosen by the user.

The way the tool creates this power density data changed a few times during the course of the project. The way I describe the process here is a result of optimization over several iterations. From the programs first version to its last, the time the program used to construct the data was reduced by 75%. However I judged that software optimization and effective algorithms were not the main focus of this thesis, so the progress in run times are not highlighted as results. There are probably still room for improvement, but the work flow is thought out to avoid unnecessary repetition.

#### Loading location data

The locations of each cell stays the same for every report on the same chip. A design decision was made to make the program only able to remember one chip at the time, meaning you would have to run it two times for two separate chip designs. Since the cell locations stay the same the entire program, the program

first loads these. The run time added to the program from loading the cell locations is not dependant on number of reports. In the power reports the cell names are not sorted. To quickly find the correct location for each cell, I chose to load the cell locations directly to a dictionary before the program loads the power reports. This way the program can very quickly look up the correct location of any cell name. The dictionary data structure has a key and a value, the cell name is used as a key, and the x,y location of each cell is stored in the value. A requirement for dictionaries are unique keys. This is fulfilled as all cell names are unique.

Figure 3.3: How the grid represents the chip area. Capital N,M,X and Y refers to the maximum number for each dimension. n, m, x and y represents specific values within the limits. Macros are defined by the minimum and maximum (n,m) tuples.

#### **Refining location data**

The value in the dictionary is an instance of a location class. The location class allows the user to access the x,y coordinates, calculate n,m coordinates for each cell if given X,Y and M,N. In order to find X,Y the location dictionary has to be searched for the highest x and y value. N and M are specified by the user. When the class has N,M;X,Y and x,y it can calculate n, and m as seen in figure 3.3. This is done before the report data is loaded to minimize the time used to place each cell power in the correct bin, as seen in the work flow in figure 3.2.

#### Loading power data

The reports are parsed one by one, loading the name and power usage of the cell in a unsorted list. The list is then traversed, looking up every cell name in the dictionary and adding the power to the bin the dictionary provides for that cell. The NxM grid is stored in a class instance. One instance per frame, and all the instances are contained in a list. In order to have static scales in the animation, the limits for all the axes has to be the same for each frame. The data for each frame is therefore traversed to find the max power value for any bin in the entire animation.

#### 3.4.3 Circuit layout visualization

A design feature requested from Nordic was that the graphs was to have a drawing of the circuit visible under the plot, with a heat map showing exactly where on the circuit the power is used. A .pdf file with a visual representation of the circuit was given as a possible help. The two solutions described in this sections were early iterations. The third and final solution is described in section 3.4.4, as it is connected with extra input data.

#### Visualization by manually drawing

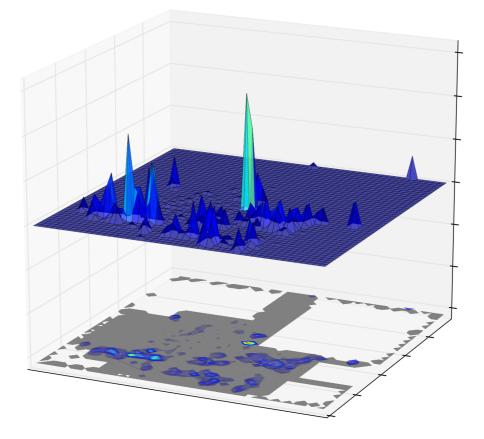

For the first iteration of this feature, a simple .png in black and white was made manually based of the contours of the circuit. The graphing tool then loaded the value of each pixel, and the picture was graphed as a heat map based of the png as seen in figure figure 3.4. The .png file also had to have the same MxN

Figure 3.4: Manually drawn layout visualization

resolution as the graph resulting in either fixed graph resolution, or the need for many .png files. This method was slow, both because of the amount of work done manually, and the extra work done by the program. A second problem was being sure that the data displayed matched the coordinates and axes of the picture. This required knowledge of both the circuit, the plot and the graphing tool to get right.

#### Visualization by cell density

With automation in mind, a new scheme was created. One of the data files that is used to create the graph data, is a location file of all cells, giving the coordinates of their power connection. By making a new data set that kept the value of how many cells are connected to each bin, you would get a data set showing density. The thought was that this might give a recognizable pattern of the circuit as seen in the middle of figure 3.5. It turned out to be better to simply

Figure 3.5: Automaticly generated layout visualization based on cell density

differentiate between two values, either there are one or more cells in the bin, or there are none. This method shows the recognizable outlines of macros such as flash, radio and ram. This solved the main concerns with the manual layout since the data is based of the same data that generates the graph the orientation is always correct. It is also based of the data you already have, so there is no extra work for the user. A third more visually pleasing version is described later in this chapter, but requires extra input. If that input is not present, this method is used instead.

## 3.4.4 Problems when visualizing circuit macros

When the initial tests with the clock tree reports were successful I reported that the program was written as general as possible to enable plotting different data. Jan Egil Øye wished to test the visualization tool on a power report from a new simulation, and included reports including the entire cell library, not only the cells belonging to the clock tree. When attempting to run the tool on the full report containing all cells, there would be huge spikes. I searched the reports for high numbers and found macros like flash, radio transmitter and memory that are designed separately and inserted as black boxes in the design. In some simulation modes a macro can stand for up to 50% of total power. These cells would create peaks dwarfing all data, meaning the surface would be flat except for a couple of spikes showing macro activity. In the clock tree there is no macros, but the concept of visualizing power data from the full circuit was interesting. At first I created an ignore file, allowing to simply remove the spikes that would make the surface plot unreadable. Figure 3.5 is made by ignoring data from the large macros. However Jan Egil and I agreed I should spend the extra time needed to make sure the program could show the power used by macros in a informative manner.

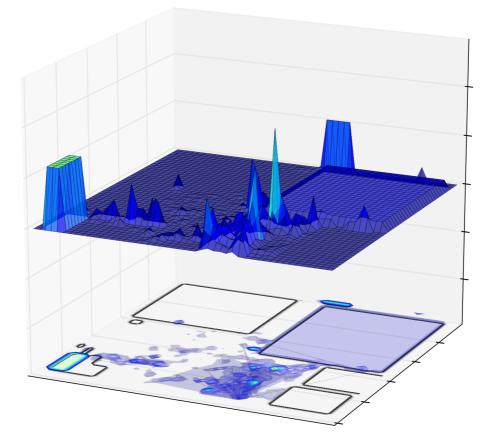

### Exceptions for macro data

In order to do this, more information about the macro cells is needed. I suggested to spread the power used in macros over several bins representing their actual size, as this would show an average power density in that area. The power is of course not dissipated uniformly in the entire macro, but since it is black boxed, it is a fair approximation. To do this correctly, additional information was needed for the macros. Printing a file similar to the location file but with cell name and bounding box instead of the location of the power connection is a small job. Deciding what macros are important to get on this list has to be done by the designer. However macros are decided early in a design, and does not change in a final phase where graphing is supposed to happen, so it is a one time job for each circuit. A new type of file was added with the format as seen in the example listing 3.4.

Figure 3.6: The surface plot area after the addition of bounding box for macros. Allows for showing power use in macro blocks and improves layout visualization

Listing 3.4: Example input file for macro bounding box data

memory1;memory\_unit;{2100.000 1900.000} {3000.000 3500.000}

storage1;storage\_unit;{100.000 120.000} {500.000 900.000}

radio1;radio\_unit;{600.000 450.000} {1500.000 900.000}

The bounding box file contains the name of the macro matching the cell name in both the location and power file. Like the location file, it also contains a reference tag which we do not use. The last field contains min\_x, min\_y, max\_x and max\_y for the macros. This file is parsed similarly like the location file. The bounding box file is not mandatory, but if it is included the location data for the cells mentioned in the file is updated. This is done through a function in the location class which sets a flag for the cell to mark it as a bbox, and calculates min\_n, min\_m, max\_n, max\_m and area. Similar formulas used to find m and n for normal locations is used. The area is given in number of bins the macro cover. The other change that needs to be done is to add a check when the power data is added to each frame. If the cell power added has the bbox flag high, it adds power divided by area to every bin it covers. The resulting surface will have box-like representing the macros as seen in figure 3.6. This representation actually helps separate macros from other power use, as they have quite different characteristics. The feedback on this was positive from the engineers, as they could easily identify activity such as reading from flash and the memory being used.

#### Using bbox to visualize circuit

In addition this macro data can be used to create a smoother visual representation of the circuit. By plotting a projection of a surface plot from 0.1 to 0.9 where 0 is the outside of macros, and 1 is the inside of macros, clear outlines can be made in the graphs as seen in figure 3.6. If a macro file is included, this technique is used instead of the density visualization described in section 3.4.3

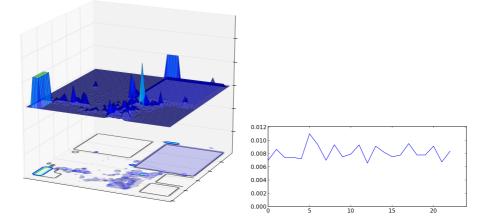

## 3.4.5 Showing the total power used in each frame

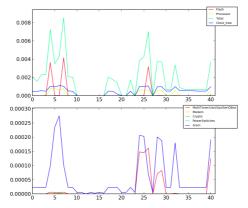

The surface plot can be animated to show change over time, however, there is no direct way of comparing power at two different time slices against each other. In order to give the user a concept of the power used in the circuit over time, the total of each frame is gathered when the power reports are loaded. The data is plotted in a separate graph with frame number on the x axis, and power value on the y axis. The graph was added based on feedback that they wanted something similar to the graphs the generated by time based simulation in Primetime PX as seen in figure 2.3. By having this graph visible, they could directly start looking closer at areas they had found interesting in those other tools. It also helps the designer to spot interesting frames like the highest total power use, and inactive periods and actually compare the total power spent in each frame.

Figure 3.7: The view for the user after adding a total power per frame graph. The graph on the right graphs total power on the y axis to report number on the x axis

#### Total power spent by categories

Once the total power graph was up, it was apparent that the visualization was useful. It gave a clear signal what phases of the simulation used the most power, and you could clearly distinguish the simulation shifting running modes. This inspired the idea of being able to set up a list of categories that would be plotted together with the total power plot. The idea was that you for example could set up a category for all cells that are part of the processor, and observe in what modes those are most active. The need is similar to the categorization in the power report analysis tool mentioned in section 3.3.2.

#### Implementation

The category file is loaded after the cell location dictionary is made. For each category every cell id in the location dictionary is traversed. If a cell id matches a regular expression that belongs to a category that category name is added to the information on the cell held by the dictionary. This results in every cell also has a list containing all categories it is a part of when the power file is loaded, the cell data also tells the program what categories to add the power use to. This

reduces the time the regular expressions has to be searched for to one, instead of once per report.

## Plotting category data

After plotting many categories in the same graph, it was obvious that the scales of the different data could vary greatly. As a default the graph was scaled after the total graph, meaning some minor power consumers would not be visible. We decided not to logarithmically scale the y axis, as you would loose resolution on the temporal difference in a single plot. Instead the graph was split in two, the top one scaled after the total power use, as this was easy to recognize from other simulations, the other contained all user defined graphs, scaled by one of those graphs set by the user. This improved the readability of the graph, and allowed the user to follow certain lines of interest closely. The category file works similar to the one in section 3.3.2, but with more tags to create new categories, to enable the new features:

- -\*[category name] marks the category that should be used to scale on the bottom plot

- -![category name] displays the category in the top graph together with the total power

- -[category name] displays the category in the bottom graph.

- -(mute)[category name] to hide the category from plotting, will still be printed in excel file as described in section 3.4.8.

As figure 3.8 shows, the different categories can give much more detailed understanding of the power used.

## 3.4.6 Identifying points of interest

As a design decision we agreed that the graph should give an intuitive view of the power use, not a detailed numerical view. For the details on specific cells and power, the engineers can search the report files. The graph should work as a way to find out where to look in those report files. When testing the program

Figure 3.8: Plots showing total power for user defined categories over time. Y axis: Power, X axis: time.

on some scenarios, different peaks appeared. Some static, and some sporadic. However it was hard to tell exactly what these spikes indicated, and what cells actually used the power. There was a need for a link between the graph and the report file, to quickly locate the right cells. To make this possible, first it had to be clear what exact n,m coordinates the peaks had. To display this, a list of peak positions n,m and what power they used was created for each frame. This was done by searching for the 10 highest values, and their indices in the N\*M grid. This is done as part of the analyzing and transforming frame data as seen in figure 3.2

#### Look up bin

When the programmer has the bin number he or she could calculate the approximate x,y position they were looking for, but to do this, you needed to know the limits of x,y,n and m. This was solved by printing out a file containing a grid, each bin containing the cell names that are contained in that bin. Thew file is read by a small program that prints out the cell names of whatever coordinates you input. The print results can easily be copied and used as regular expressions in a category file. This will result in a bin being plotted on its own. This can be useful for identifying how often a spike appears. You can also see what types of

cells are contributing to that spike, which is needed if you want to know if you can change the spike. By looking up the different cell names in the report, you can find the exact power drained in each cell for that time instance. This feature gives the designers a good bridge between the intuitive graphs and the detailed reports. The bridge allows them to use the impressions and ideas they get from the graphs to search the reports for key data.

## 3.4.7 Logarithmic plotting

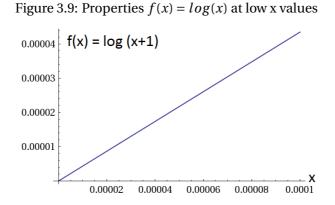

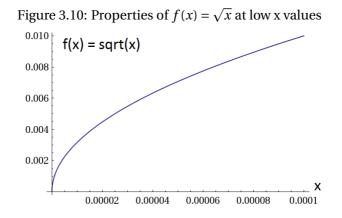

To identify details and small power usages even in graphs where there are also large spikes, logarithmic plotting is useful. It was a feature desired by the designers to get more visual details in certain plots. There is no automatic logarithmic plotting function for the surface graph, so this transformation had to be done on the data before it was graphed. Since the power numbers are in the magnitude from 1e-10 to 1e-4 using log(x) does not work as numbers between 0 and 1 become huge negative numbers. Reports can also sometimes contain negative numbers, which would result in complex numbers when put in a logarithmic function. The first attempt at fixing this included adding 1 to every number and then taking the logarithm giving f(x) = log(x+1). However when x varies from 1e-4 go 1e-10, the transformation is nearly linear as seen in figure 3.9. Instead

the program uses square root of x. This works for all positive numbers, so negative numbers are transformed to 0 with an error message, as Jan Egil Øye meant they were not interesting in the plot. The square root graph in figure 3.10 has the same properties as a logarithmic plot would have for values over 1. Therefore I chose f(x) = sqrt(x) to transform the surface plot data.

## 3.4.8 Excel print

As a design decision, we wanted to keep the plot view clear of too many numbers. These should be available if you were looking for them. The category graphs in figure 3.8 contain a lot of information, but you can only have the plots scaled after total and one other graph. When looking at plots from a data set, the user got an urge to see in more detail what happened in these graphs. An extra function was made to simply print out the data points in a .csv format that can be opened directly in excel. This way the designer can open the excel file afterwords and plot all, or some of the lines in the categories graphs. It is also a good way to check up exact numbers from the categories, and with this addition, the quick analyses tool (mentioned in section 3.3.2) is completely included as a feature the graphing tool. Excel is a tool the designers were used to using when handling data. This feature allows the user to use the data for other purposes, and look more closely on certain data points.

## 3.5 View area

The visualization in this project is done with the Python library Matplotlib[6]. This task is possible with other libraries, so in this section we focus on how the

data is presented rather than the graphing tool.

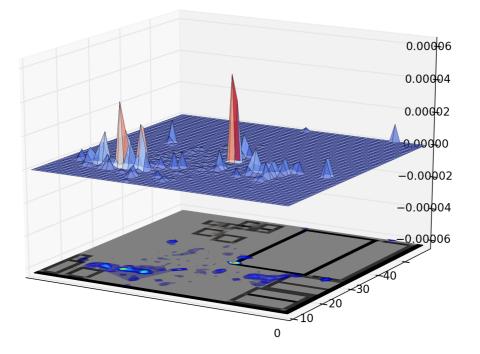

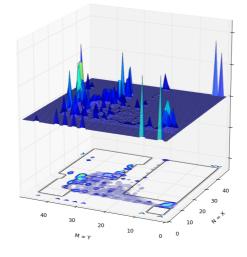

#### 3.5.1 The surface plot

The central plot of the visualization is the 3d surface plot showing where the power is spent. The graph contains 3 plots, based of two data sets. The data for a surface or contour plot has to be organized in a two dimensional array where each bin n,m contains a value. In the power data, this value represents the power used within the bin, while for the layout the value is 1 if there is a macro defined within the bin, otherwise 0. The plot area contains three different plots, as seen in figure 3.11.

**Surface plot of power used** The surface plot gives clear visualization of spikes, which is important to look for. It is plotted with a slight opacity so that a spike does not block all data behind it.

**Contour of the power used** The contour plot makes a heat map over the layout. This heat map represents where the power is spent and ties that information to the circuit layout. I chose not to plot any contour colors for bins that were exactly 0 as this improved the contrast between some power used and no power used and increased the visibility of the layout.

**Contour of the circuit layout** The contour data is graphed by excluding 0 and 1, and only graphing 0.01 to 0.99. This means you only get lines between the bins containing and bins not containing any macros.

## 3.5.2 Categories plot

In figure 3.12 you can see the plot showing the category data. The graphs shows the total power per slide, giving an idea of the temporal change in power if the graphs are sequential time slices as in firuge 4.9. If the data is based of scenarios like in figure 3.12 it shows an comparison between different scenarios. The plot on the top is total power used against time, and can include extra graphs set by the user for total power spent by a category. Time or slide number is on the x axis, and power used in watts are on the y axis. This main graph is

Figure 3.11: Three dimensional surface plot with circuit layout and heat map underneath

also accompanied by a second graph that can be filled categories that need a different scale than the total power graph. This allows the user to mark certain data or points as interesting and make them clear on the slides. The x and y axis are set to the same limits for all images in a series so only the line changes.

Figure 3.12: Plots showing total power for user defined categories in each frame. Y axis: Power, X axix: frame number. Each frame is for a differen scenario.

### 3.5.3 Top 10 peaks

In order to identify specific points of interest based on the data in the surface plot, a list of the 10 highest peaks is shown as seen in figure 3.13. This also displays the power used in that point, and gives a good way to read exact numbers out of the graphs and get an idea of the scale.

| top 10 peaks: |         |

|---------------|---------|

| (0,2):        | 0.19 mW |

| (0,8):        | 0.18 mW |

| (49, 4):      | 0.17 mW |

| (31,29):      | 0.15 mW |

| (19,39):      | 0.14 mW |

| (49, 2):      | 0.14 mW |

| (22,40):      | 0.13 mW |

| (41,49):      | 0.13 mW |

| (22,39):      | 0.13 mW |

| (15,40):      | 0.12 mW |

Figure 3.13: Example of visual style of the top 10 list.

## 3.5.4 Animation

Matplotlib has a function to create animated graphs. However with the old version of linux running on the servers, it was not compatible. Instead each report were made into a single image file, sequentially numbered. This way they could be animated through ffmpeg[5] by a one-liner in the linux command window. Ffmpeg can generate both gif and movies from a series of numerated images. This proved to be a good solution, as the designers then could animate if wanted, but otherwise scroll through the images in a photo viewer in windows. Generating one image at a time is not as time effective as generating an animation, as the animation optimizes by for example only rendering the changes in each frame. It also meant extra care when choosing what to plot to make sure the limits on the graphs stayed the same during the whole animation.

## 3.6 Testing the visualizer

Prototypes of the program was tested throughout the design process as is usual in user centered design. These tests had two types of results:

**Results for the design** These tests of the program allow us to find faults that need to be improved and find out what user cases we have not yet enabled. These types of results are discussed earlier in this chapter, as part of the design process

**Results interesting for the engineers** These results are presented in chapter 4 and discussed further in the discussion. Here are the types of data we decided to try the system on:

**Sequential power estimations** The reports are from power estimations based of simulation. They are time intensive to generate(4000 reports would take around a day), but give a detailed picture of the power. We wanted to test this to see how informative these graphs would be compared to more static graphs. The largest test done was 4000 consecutive images of a chip that already had simulation files ready for estimation. The results of these are presented in section 4.3.

**Categories** Static power estimations cannot give time consecutive reports. A single estimation run can however still give several reports. The different reports each represent a scenario meant to show different sides of the power consumption. The only change made to the program to handle this was to have a different limit for each power surface graph, instead of one for the entire run. This is because animating the graphs from scenarios does not make any sense. The resulting graphs that show this are presented in section 4.4

## 3.6.1 Real life application test

The goal of this thesis is to use visualizing to improve the understanding of clock trees in a design phase. The tool turned out to be done in time for use during the clock design phase of a Nordic Semiconductor chip on its way to tape out. A line was added in the script generating and simulating different clock trees to print out reports for all trees, allowing the program to be tested on a real user case by a real user. The test was handled by Jan Egil Øye, who was working on the clock tree. He used the graphs to look at the clock tree power using the static estimation report technique Nordic normally use, but with all cells printed instead of a single estimate number. He was then able to use the graphs as additional information about the clock tree. This was the main test for the program, as it is the exact user case it was meant to do.

## **Chapter 4**

# Results

The graphing tool was constructed and fulfills all specifications set by Nordic Semiconductor. In this chapter some chosen plots will be presented. The graphs displayed in the results have had information removed on request of Nordic as they are generated from competition sensitive data. This is done so the thesis can be open for the public. It is also important to note that it was a design choice to not have units on all graphs. The graphs are meant to give intuitive understanding, not exact information, as that can be found in the reports. This thesis results are the graphs themselves and not the data in them.

## 4.1 Key to the output graphs

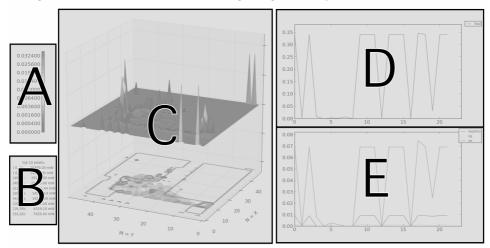

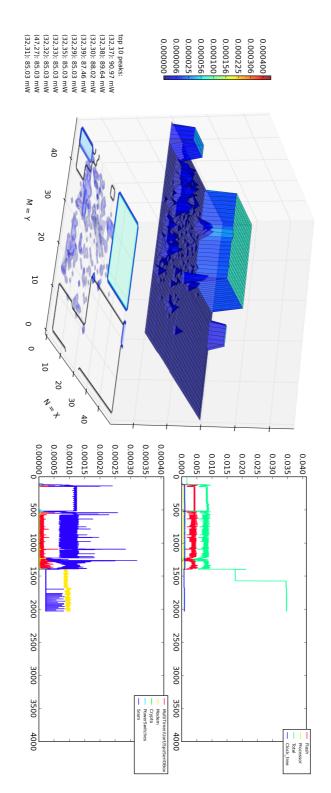

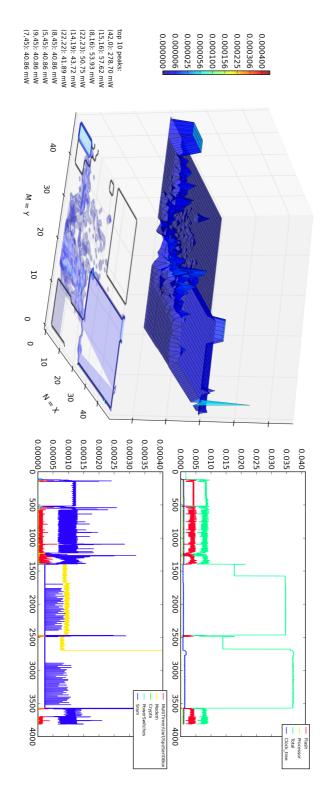

All graphs in this chapter have the same view area. If you choose to graph a folder of reports, there will be one resulting image for each report. Each image contains several graphs. Figure 4.1 indexes the different areas. They represent the following:

**A: Color reference bar** shows the approximate value the colors used in color coding of area C.

**B: Top 10 peaks** Displays the top 10 peaks in the current plot in the following format: (n,m) 0.0 mW, where n and m is the position of the bin containing the peak, and the power number represents the amount of power spent in that bin.

Figure 4.1: The areas of the resulting image file, explanation in section 4.1

All graphs except figure 4.2 to 4.4 were generated by an old version of this program which printed the power numbers several magnitudes too large. This is fixed in the tool, but the power files made to create these graphs are deleted, so recreating them is not possible.

**C: Surface plot** shows power density over the chip area. Underneath the surface plot is a plot representing the layout of the chip with the contours of the surface plot to show power density relative to the layout.

**D:** Total power and power per category is graphed with power on the Y axis and image number on the X axis. If the reports are from consecutive time intervals, the graph will represent total power consumed by chip over time. If the reports are from different scenarios, this plot simply shows total power consumed in each frame. The user sets the categories, with the names and what cells to go in them. The names of the categories are listed in the legend in the top right corner.

**E: Additional categories** can be put in this graph to have the scale of a specific category instead of the total power consumed scale. Otherwise it works exactly

the same as D

## 4.2 Test in design process

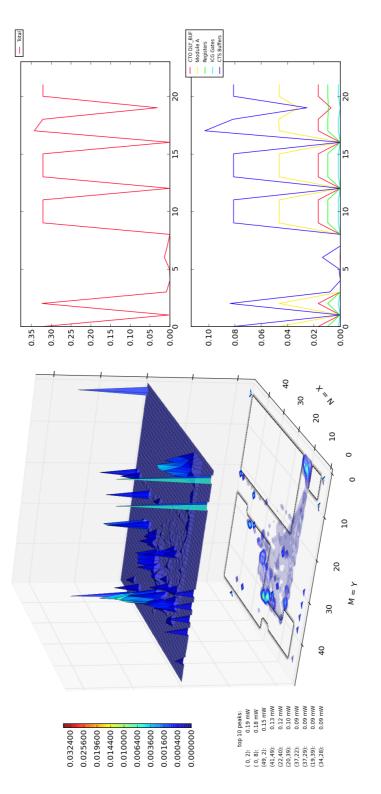

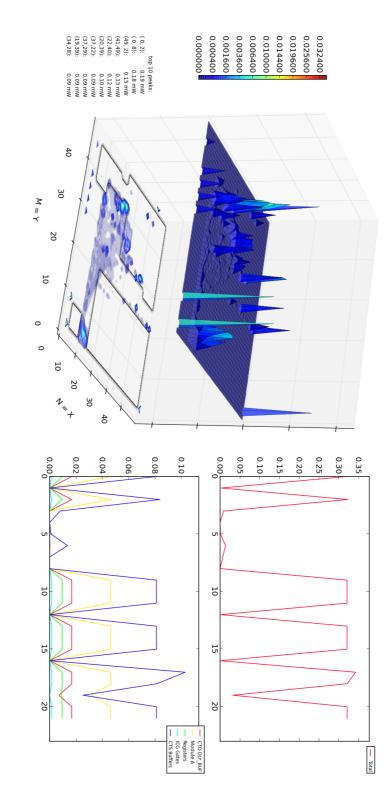

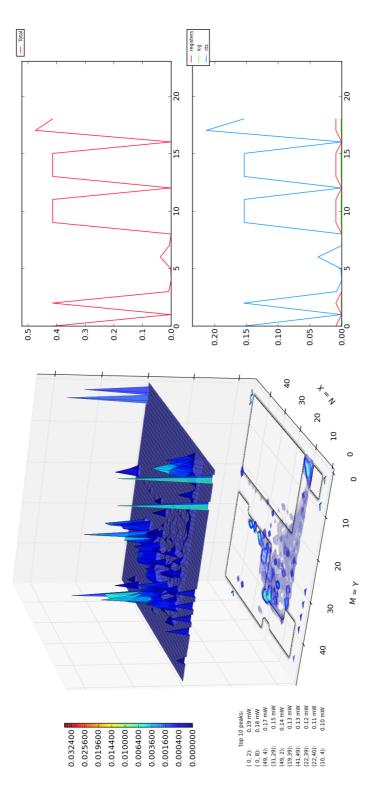

Figure 4.2, 4.3 and 4.4 are quite similar. They are all results of testing of the graphing tool in the actual design phase as explained in section 3.6.1. An extra line to execute the tool was added to the scripts that are already run to do power simulations. So there is no extra work in graphing these reports, they simply appear in a folder together with the original reports. This section contains images received back from Jan Egil Øye after the clock tree generation was finalized for tape out.

**Total power reduction** During the first to last iteration the clock tree power was reduced from 389 mW to 343 mW. A power cut of 11.8%.

**Run time** A run with 23 reports took 72 seconds to gather the data and draw 23 graphs. On average these reports contained ca 39 000 cells. The time used to gather the data was 25 seconds (1.1 second per report). The graphing took 46 seconds(2 seconds per graph).

**Figure 4.2** This is one of the graphs produced from an early iteration of the clock tree. There were 23 graphs produced for each iteration. One graph per scenario. On the total power graph, you can see that several of the scenarios produce exactly the same total power. The surface plots with the same total power were all completely identical to each other. The different scenarios were meant to represent different parts of the clock tree.

**Figure 4.3** This graph shows the same scenario as figure 4.2, but for the last iteration of the clock tree. The two graphs look very similar but some differences should be pointed out. The total power consumption is visibly lower than the previous graph. Comparing the two, you can see that the top peak (22,40) in figure 4.2 has been reduced from 0.20mW to 0.12mW. In the two "top 10 peaks" lists, there are several differences. Also note that the category graph for CTS Buffers is lower in figure 4.3 than figure 4.2.

**Figure 4.4** Shows the power scenario from the same estimation run as 4.3. It is the scenario that includes the most cells. It has slightly higher power consumption than the other graphs in this section, comparing the two, you can only see one difference. A spike at 25,45 that is there in figure 4.4 and not in figure 4.3.

Figure 4.2: Power consumption of clock tree on chip to be sent to tape out. Early iteration. The frame shown is image 21 of 23.

Figure 4.4: Power consumption of clock tree on chip to be sent to tape out. Final iteration. Full clock tree.

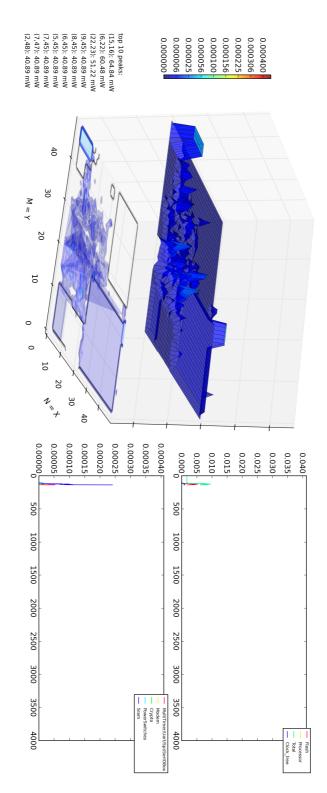

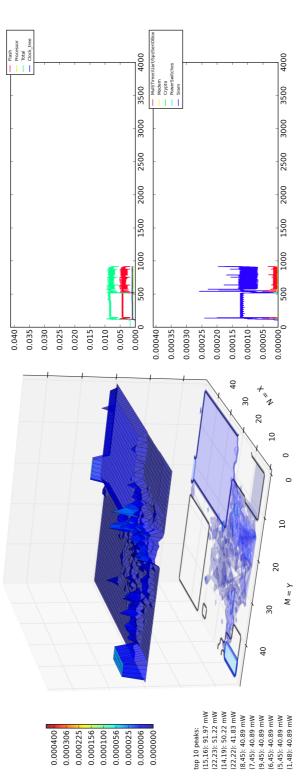

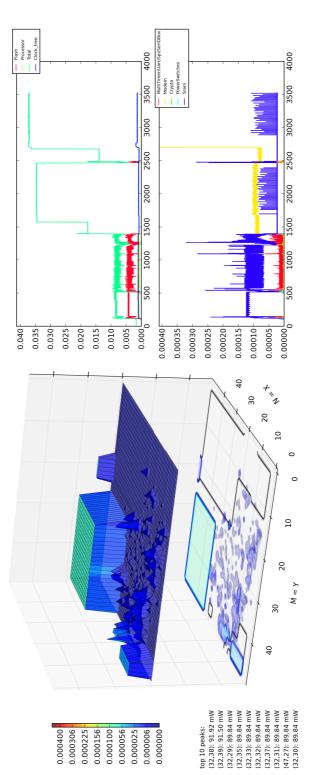

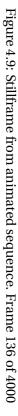

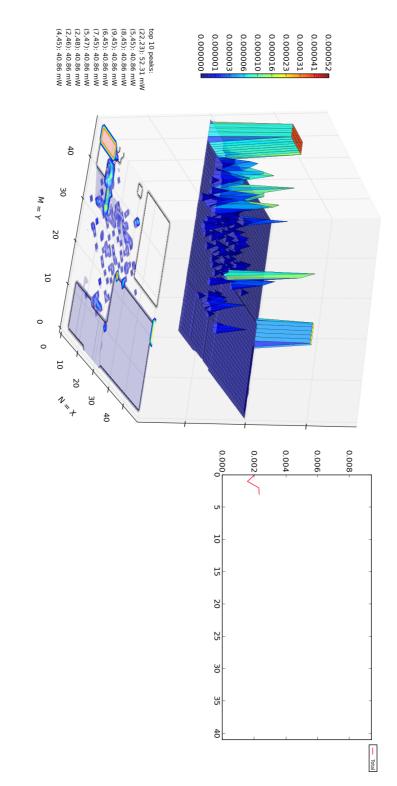

## 4.3 Animated graphs

Since displaying animations on paper is not possible, a few screen shots showing the progression of the animation is displayed. All figures 4.5 to 4.9 have incorrect data in the top 10 peaks list. The numbers are 1000 times larger than the actual values. The 5 screen shots are chosen out of the 4000 to show the surface plots of different modes the circuit run in. These graphs are based of reports of another circuit than the previous images. The power estimation these reports are from is time based, which means it is based on a simulation of a test bench. In this section the important parts of these figures will be noted. The notation (n,m) is used to describe points in the surface plot, and areas will be described by two points (nMin , mMin),(nMax , mMax) representing two opposite corners of a macro as seen in figure 3.3.