# Optimal Frequency of Silicon Carbide Power Correction Circuits for On-Board Chargers

Magnus Aune Johnsen

Master of Energy and Environmental Engineering Submission date: July 2016 Supervisor: Ole-Morten Midtgård, ELKRAFT

Norwegian University of Science and Technology Department of Electric Power Engineering

## Abstract

Compact high-efficiency power converters is a popular topic in electrical power engineering. So is also the case for electric and plug-in hybrid electric vehicle battery chargers. Increasing the switching frequency in the power converters will reduce the size of passive components, but this also results in lower efficiency. The progress being made in wide bandgap semiconductors introduce possibilities for lower loss, and thus improved efficiency at higher switching frequencies. Silicon carbide is such a semiconductor material, whose electrical and thermal capabilities trumps those of a classical silicon semiconductor.

To investigate whether utilizing a silicon carbide semiconductor in an on-board charger for electric and plug-in hybrid electric vehicles can provide lower switching loss, a silicon carbide (SiC) MOSFET is tested against a silicon (Si) MOSFET. The focus is on the hard switched application of the power supply's power factor corrector. A continuous-conduction mode DCDC boost converter is designed and used to perform the test. The converter is designed for an input voltage of 230V, output voltage of 350V and rated for 3500W. Emphasis has been made on parasitic elements and their effect on switching behavior.

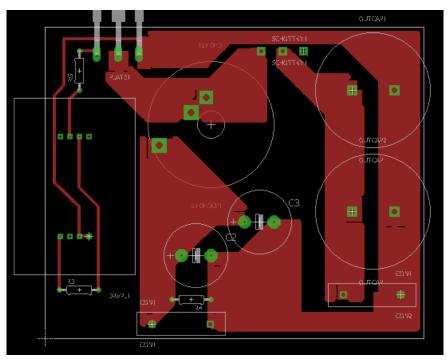

Three different circuits was developed through the course of the thesis, with improvements in layout implemented for each step. Significant improvements was seen in gate drive circuitry and the overall converter from the first design to the second, and improvements in the gate circuitry was seen from the second design to the third. From this, it is concluded that for best performance, the gate driver circuit should be as compact as possible, with short conduction paths and close to the MOSFET gate pin. The return form the MOSFET source to the gate driver ground should be as large as possible, and directly underneath the gate signal path. SMD components with low parasitic inductance and capacitance should be used in the gate driver circuit.

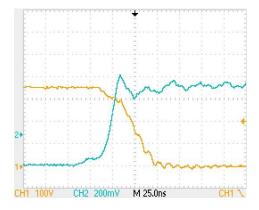

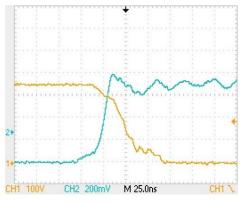

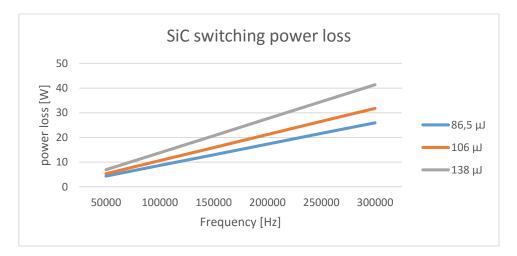

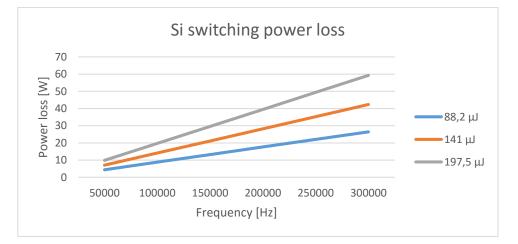

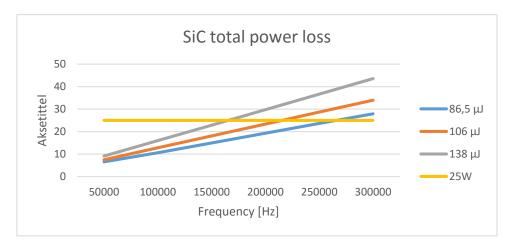

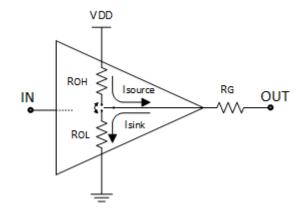

The Si and SiC MOSFET show different switching behavior. The main difference is at turnoff, regarding delay and voltage rise waveform. At the same gate resistance and gate voltage, the turn-off delay time for the Si MOSFET is almost three times longer than the SiC MOSFET delay time. While the SiC MOSFET turn-off voltage showed a linear increase the entire rising period, the Si MOSFET voltage rise was more exponential. Accurately determining losses in a MOSFET, and how well it is capable of operating, is a challenging exercise. Distortion caused by the probes while measuring, bandwidth limitations in the probes and oscilloscope, time delays in the probes and improper components and design can all contribute to erroneous results. Nevertheless, it was concluded that in this circuit, with these MOSFETs, the SiC MOSFET had a switching loss between 106  $\mu$ J and 138  $\mu$ J, which was between 0,7 and 0,75 times lower than the Si MOSFET switching loss. With the conduction loss for the MOSFETs taken into account, which was found to be 2,2 W for the SiC MOSFET and 7,5 W for the Si MOSFET, at nominal operation and a selected operating temperature of 125 °C, the optimal switching frequency was found to be between 165 kHz and 215 kHz. This is based on a power loss cap of 25 W.

# Preface

This Master's Thesis was prepared during the spring 2016 at the Norwegian University of Science and Technology (NTNU), Department of Electric Power Engineering. The topic of the thesis is power electronics, and is accomplished in cooperation with Valeo Powertrain Energy Conversion.

I would like to thank my supervisor, professor Ole-Morten Midtgård, for support and my cosupervisor doctoral candidate Ole Christian Spro for technical guidance through the work on this thesis. I would also like to thank Torbjørn Sørsdahl at Valeo for valuable support and constructive technical feedback. Acknowledgement also goes to the staff at the Department of Electric Power Engineering's Servicelab for technical assistance whenever needed, and to the Department of Electronics and Telecommunication's Elprolab (Electronics and Prototype Laboratory) for helpful and fast production of the printed circuit boards.

# Table of contents

| PREFACE       V         LIST OF FIGURES       X         LIST OF TABLES       XIV         ABBREVIATIONS       XVII         1       INTRODUCTION       1         1.1       SCOPE OF WORK       1         2       ON-BOARD CHARGER       3         2.1       GEN2 CHARGER       3         3.1       CONTINUOUS-CONDUCTION       8         3.2       BOOST CONVERTER       7         3.1       CONTINUOUS-CONDUCTION       8         3.2       BORDER BETWEEN CONTINUOUS AND DISCONTINUOUS.       9         3.3       DISCONTINUOUS-CONDUCTION MODE       11         3.4       CONVERTER PARAMETER SETTING       13         3.4.1       Output capacitance       13         3.4.2       Boost SWITCHING BASICS.       15         3.6       CIRCUIT PARASITIC ELEMENTS       20         3.6.1       Parasitic elements in circuit components.       20         3.6.2       Parasitic elements in circuit components.       20         3.6.1       Parasitic elements in physical layout       21         4       SILICON CARBIDE.       23         4.1.1       Bandgap energy.       23         4.1.2       Critical el                                                               | A | BST | RAC   | CT                                       | III  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-------|------------------------------------------|------|

| LIST OF TABLES       XIV         ABBREVIATIONS       XVII         1       INTRODUCTION       1         1.1       SCOPE OF WORK       1         2       ON-BOARD CHARGER       3         2.1       GEN2 CHARGER       3         2.1       GEN2 CHARGER       3         3       BOOST CONVERTER       7         3.1       CONTINUOUS-CONDUCTION       8         3.2       BORDER BETWEEN CONTINUOUS AND DISCONTINUOUS       9         3.3       DISCONTINUOUS-CONDUCTION MODE       11         3.4       CONVERTER PARAMETER SETTING       13         3.4.1       Output capacitance       13         3.4.2       Boost inductor       14         3.5       BOOST SWITCHING BASICS       15         3.6       CIRCUIT PARASITIC ELEMENTS       20         3.6.1       Parasitic elements in circuit components       20         3.6.2       Parasitic elements in physical layout       21         4       SILICON CARBIDE       23         4.1       MATERIAL PROPERTIES       23         4.1.1       Bandgap energy       23         4.1.2       Critical electric field       24         4.1.3                                                                                  | P | REF | FACE  | C                                        | V    |

| ABBREVIATIONS       XVII         1       INTRODUCTION       1         1.1       SCOPE OF WORK       1         2       ON-BOARD CHARGER       3         2.1       GEN2 CHARGER       3         2.1       GEN2 CHARGER       3         3       BOOST CONVERTER       7         3.1       CONTINUOUS-CONDUCTION       8         3.2       BORDER BETWEEN CONTINUOUS AND DISCONTINUOUS       9         3.3       DISCONTINUOUS-CONDUCTION MODE       11         3.4       CONVERTER PARAMETER SETTING       13         3.4.1       Output capacitance       13         3.4.2       Boost inductor       14         3.5       BOOST SWITCHING BASICS       15         3.6       CIRCUIT PARASITIC ELEMENTS       20         3.6.1       Parasitic elements in circuit components       20         3.6.2       Parasitic elements in physical layout       21         4       SILICON CARBIDE       23         4.1.1       Bandgap energy       23         4.1.2       Critical electric field       24         4.1.3       Electron saturation velocity       24         4.1.4       Thermal conductivity       24 <th>L</th> <th>IST</th> <th>OF I</th> <th>FIGURES</th> <th> X</th> | L | IST | OF I  | FIGURES                                  | X    |

| ABBREVIATIONS       XVII         1       INTRODUCTION       1         1.1       SCOPE OF WORK       1         2       ON-BOARD CHARGER       3         2.1       GEN2 CHARGER       3         2.1       GEN2 CHARGER       3         3       BOOST CONVERTER       7         3.1       CONTINUOUS-CONDUCTION       8         3.2       BORDER BETWEEN CONTINUOUS AND DISCONTINUOUS       9         3.3       DISCONTINUOUS-CONDUCTION MODE       11         3.4       CONVERTER PARAMETER SETTING       13         3.4.1       Output capacitance       13         3.4.2       Boost inductor       14         3.5       BOOST SWITCHING BASICS       15         3.6       CIRCUIT PARASITIC ELEMENTS       20         3.6.1       Parasitic elements in circuit components       20         3.6.2       Parasitic elements in physical layout       21         4       SILICON CARBIDE       23         4.1.1       Bandgap energy       23         4.1.2       Critical electric field       24         4.1.3       Electron saturation velocity       24         4.1.4       Thermal conductivity       24 <th>L</th> <th>IST</th> <th>OF 7</th> <th>TABLESX</th> <th>αv</th> | L | IST | OF 7  | TABLESX                                  | αv   |

| 1       INTRODUCTION       1         1.1       SCOPE OF WORK       1         2       ON-BOARD CHARGER       3         2.1       GEN2 CHARGER       3         3.1       CONVERTER       7         3.1       CONTINUOUS-CONDUCTION       8         3.2       BORDER BETWEEN CONTINUOUS AND DISCONTINUOUS       9         3.3       DISCONTINUOUS-CONDUCTION MODE       11         3.4       CONVERTER PARAMETER SETTING       13         3.4.1       Output capacitance       13         3.4.2       Boost inductor       14         3.5       BOOST SWITCHING BASICS       15         3.6       CIRCUIT PARASITIC ELEMENTS       20         3.6.1       Parasitic elements in circuit components       20         3.6.2       Parasitic elements in physical layout       21         4       SILICON CARBIDE       23         4.1       MATERIAL PROPERTIES       23         4.1.3       Electron saturation velocity       24         4.1.4       Thermal conductivity       24         4.2       SIC MOSFET       25                                                                                                                                                            |   |     |       |                                          |      |

| 1.1 SCOPE OF WORK       1         2 ON-BOARD CHARGER       3         3.1 GEN2 CHARGER       3         3 BOOST CONVERTER       7         3.1 CONTINUOUS-CONDUCTION       8         3.2 BORDER BETWEEN CONTINUOUS AND DISCONTINUOUS       9         3.3 DISCONTINUOUS-CONDUCTION MODE       11         3.4 CONVERTER PARAMETER SETTING       13         3.4.1 Output capacitance       13         3.4.2 Boost inductor       14         3.5 BOOST SWITCHING BASICS       15         3.6 CIRCUIT PARASITIC ELEMENTS       20         3.6.1 Parasitic elements in circuit components       20         3.6.2 Parasitic elements in physical layout       21         4 SILICON CARBIDE       23         4.1 MATERIAL PROPERTIES       23         4.1.1 Bandgap energy       23         4.1.2 Critical electric field       24         4.1.3 Electron saturation velocity       24         4.1.4 Thermal conductivity       24         4.2 SIC MOSFET       25                                                                                                                                                                                                                          | A |     |       |                                          |      |

| 2ON-BOARD CHARGER32.1GEN2 CHARGER33BOOST CONVERTER73.1CONTINUOUS-CONDUCTION83.2BORDER BETWEEN CONTINUOUS AND DISCONTINUOUS93.3DISCONTINUOUS-CONDUCTION MODE113.4CONVERTER PARAMETER SETTING133.4.1Output capacitance133.4.2Boost inductor143.5BOOST SWITCHING BASICS153.6CIRCUIT PARASITIC ELEMENTS203.6.1Parasitic elements in circuit components203.6.2Parasitic elements in physical layout214SILICON CARBIDE234.1MATERIAL PROPERTIES234.1.2Critical electric field244.1.3Electron saturation velocity244.1.4Thermal conductivity244.2SIC MOSFET25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 | Ι   | NTR   | ODUCTION                                 | 1    |

| 2.1 GEN2 CHARGER33 BOOST CONVERTER.73.1 CONTINUOUS-CONDUCTION83.2 BORDER BETWEEN CONTINUOUS AND DISCONTINUOUS93.3 DISCONTINUOUS-CONDUCTION MODE113.4 CONVERTER PARAMETER SETTING133.4.1 Output capacitance133.4.2 Boost inductor143.5 BOOST SWITCHING BASICS153.6 CIRCUIT PARASITIC ELEMENTS203.6.1 Parasitic elements in circuit components203.6.2 Parasitic elements in physical layout214 SILICON CARBIDE234.1 MATERIAL PROPERTIES234.1.2 Critical electric field244.1.3 Electron saturation velocity244.2 SIC MOSFET25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 1.1 | Sco   | DPE OF WORK                              | 1    |

| 3       BOOST CONVERTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2 | (   | )N-B  | OARD CHARGER                             | 3    |

| 3       BOOST CONVERTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 2.1 | GE    | N2 Charger                               | 3    |

| 3.1CONTINUOUS-CONDUCTION83.2BORDER BETWEEN CONTINUOUS AND DISCONTINUOUS93.3DISCONTINUOUS-CONDUCTION MODE113.4CONVERTER PARAMETER SETTING133.4.1Output capacitance133.4.2Boost inductor143.5BOOST SWITCHING BASICS153.6CIRCUIT PARASITIC ELEMENTS203.6.1Parasitic elements in circuit components203.6.2Parasitic elements in physical layout214SILICON CARBIDE234.1MATERIAL PROPERTIES234.1.2Critical electric field244.1.3Electron saturation velocity244.1.4Thermal conductivity244.2SIC MOSFET25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3 |     |       |                                          |      |

| 3.2       BORDER BETWEEN CONTINUOUS AND DISCONTINUOUS       9         3.3       DISCONTINUOUS-CONDUCTION MODE       11         3.4       CONVERTER PARAMETER SETTING       13         3.4.1       Output capacitance       13         3.4.2       Boost inductor       14         3.5       BOOST SWITCHING BASICS       15         3.6       CIRCUIT PARASITIC ELEMENTS       20         3.6.1       Parasitic elements in circuit components       20         3.6.2       Parasitic elements in physical layout       21         4       SILICON CARBIDE       23         4.1       MATERIAL PROPERTIES       23         4.1.1       Bandgap energy.       23         4.1.2       Critical electric field       24         4.1.3       Electron saturation velocity       24         4.1.4       Thermal conductivity.       24         4.2       SIC MOSFET       25                                                                                                                                                                                                                                                                                                          | 5 | L   |       |                                          |      |

| 3.3 DISCONTINUOUS-CONDUCTION MODE113.4 CONVERTER PARAMETER SETTING133.4.1 Output capacitance133.4.2 Boost inductor143.5 BOOST SWITCHING BASICS153.6 CIRCUIT PARASITIC ELEMENTS203.6.1 Parasitic elements in circuit components203.6.2 Parasitic elements in physical layout214 SILICON CARBIDE234.1 MATERIAL PROPERTIES234.1.2 Critical electric field244.1.3 Electron saturation velocity244.1.4 Thermal conductivity244.2 SIC MOSFET25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 3.1 |       |                                          |      |

| 3.4 CONVERTER PARAMETER SETTING       13         3.4.1 Output capacitance       13         3.4.2 Boost inductor       14         3.5 BOOST SWITCHING BASICS       15         3.6 CIRCUIT PARASITIC ELEMENTS       20         3.6.1 Parasitic elements in circuit components       20         3.6.2 Parasitic elements in physical layout       21         4 SILICON CARBIDE       23         4.1 MATERIAL PROPERTIES       23         4.1.1 Bandgap energy       23         4.1.2 Critical electric field       24         4.1.3 Electron saturation velocity       24         4.1.4 Thermal conductivity       24         4.2 SIC MOSFET       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 3.2 |       |                                          |      |

| 3.4.1       Output capacitance       13         3.4.2       Boost inductor       14         3.5       BOOST SWITCHING BASICS       15         3.6       CIRCUIT PARASITIC ELEMENTS       20         3.6.1       Parasitic elements in circuit components.       20         3.6.2       Parasitic elements in physical layout.       21         4       SILICON CARBIDE.       23         4.1       MATERIAL PROPERTIES       23         4.1.1       Bandgap energy.       23         4.1.2       Critical electric field       24         4.1.3       Electron saturation velocity       24         4.1.4       Thermal conductivity       24         4.2       SIC MOSFET       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 3.3 | Dis   | CONTINUOUS-CONDUCTION MODE               | .11  |

| 3.4.2Boost inductor143.5BOOST SWITCHING BASICS.153.6CIRCUIT PARASITIC ELEMENTS203.6.1Parasitic elements in circuit components.203.6.2Parasitic elements in physical layout.214SILICON CARBIDE.234.1MATERIAL PROPERTIES.234.1.1Bandgap energy.234.1.2Critical electric field244.1.3Electron saturation velocity244.1.4Thermal conductivity.244.2SIC MOSFET25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 3.4 | Cor   | NVERTER PARAMETER SETTING                | . 13 |

| 3.5 BOOST SWITCHING BASICS.       15         3.6 CIRCUIT PARASITIC ELEMENTS       20         3.6.1 Parasitic elements in circuit components.       20         3.6.2 Parasitic elements in physical layout.       21         4 SILICON CARBIDE       23         4.1 MATERIAL PROPERTIES       23         4.1.1 Bandgap energy.       23         4.1.2 Critical electric field       24         4.1.3 Electron saturation velocity       24         4.1.4 Thermal conductivity.       24         4.2 SIC MOSFET       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 3   | .4.1  | Output capacitance                       | . 13 |

| 3.6 CIRCUIT PARASITIC ELEMENTS203.6.1 Parasitic elements in circuit components203.6.2 Parasitic elements in physical layout214 SILICON CARBIDE234.1 MATERIAL PROPERTIES234.1.1 Bandgap energy234.1.2 Critical electric field244.1.3 Electron saturation velocity244.1.4 Thermal conductivity244.2 SIC MOSFET25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 3   | .4.2  | Boost inductor                           | . 14 |

| 3.6.1 Parasitic elements in circuit components.203.6.2 Parasitic elements in physical layout.214 SILICON CARBIDE.234.1 MATERIAL PROPERTIES234.1.1 Bandgap energy.234.1.2 Critical electric field244.1.3 Electron saturation velocity244.1.4 Thermal conductivity.244.2 SIC MOSFET25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 3.5 | Boo   | DST SWITCHING BASICS                     | . 15 |

| 3.6.2 Parasitic elements in physical layout.214 SILICON CARBIDE.234.1 MATERIAL PROPERTIES234.1.1 Bandgap energy.234.1.2 Critical electric field244.1.3 Electron saturation velocity244.1.4 Thermal conductivity.244.2 SIC MOSFET25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 3.6 | Cir   | CUIT PARASITIC ELEMENTS                  | . 20 |

| 4SILICON CARBIDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 3   | .6.1  | Parasitic elements in circuit components | . 20 |

| 4.1 MATERIAL PROPERTIES234.1.1 Bandgap energy234.1.2 Critical electric field244.1.3 Electron saturation velocity244.1.4 Thermal conductivity244.2 SIC MOSFET25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 3   | .6.2  | Parasitic elements in physical layout    | . 21 |

| 4.1.1Bandgap energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4 | S   | SILIC | CON CARBIDE                              | .23  |

| 4.1.1Bandgap energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 4.1 | MA    | TERIAL PROPERTIES                        | 23   |

| 4.1.2 Critical electric field244.1.3 Electron saturation velocity244.1.4 Thermal conductivity244.2 SIC MOSFET25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |     |       |                                          |      |

| 4.1.3 Electron saturation velocity244.1.4 Thermal conductivity244.2 SIC MOSFET25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |     |       |                                          |      |

| 4.1.4 Thermal conductivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |     |       |                                          |      |

| 4.2 SIC MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |     |       | -                                        |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |     |       | -                                        |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |     |       |                                          |      |

| 5 | MOSFET COMPARISON                             | 27 |

|---|-----------------------------------------------|----|

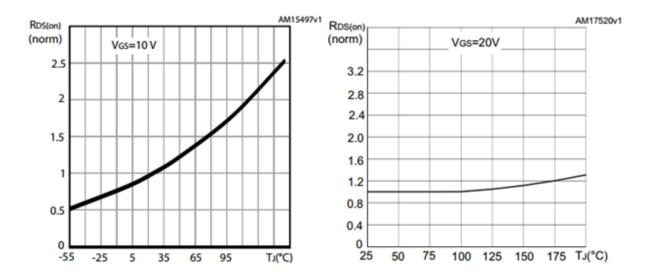

|   | 5.1 ON RESISTANCE (R <sub>DS(ON)</sub> )      | 27 |

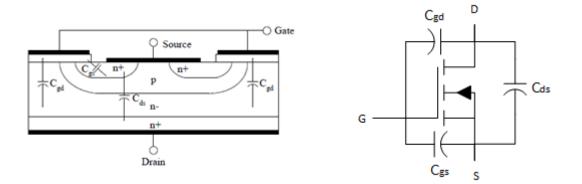

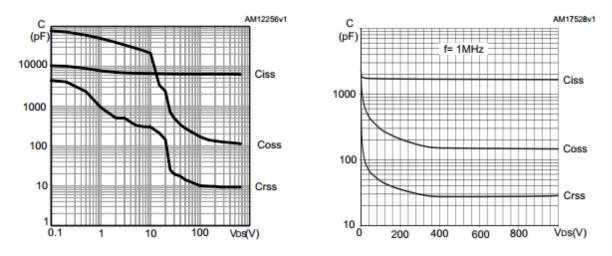

|   | 5.2 INTRINSIC CAPACITANCES                    | 28 |

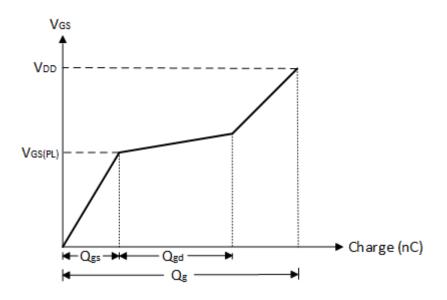

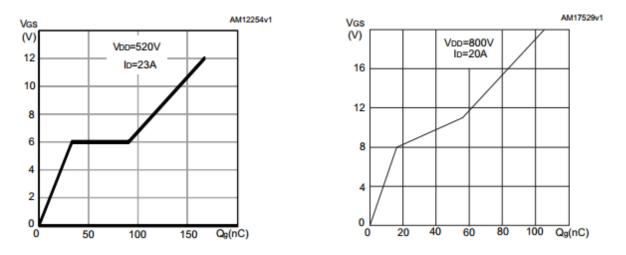

|   | 5.3 GATE CHARGE                               | 29 |

|   | 5.4 Loss calculations                         | 32 |

|   | 5.4.1 Datasheet energy loss                   | 32 |

|   | 5.4.2 Output capacitance and gate charge      | 33 |

|   | 5.4.3 Input and Miller capacitance            | 34 |

|   | 5.4.4 Loss summary                            | 35 |

|   | 5.4.5 Loss and switching time                 | 36 |

| 6 | LABORATORY TEST                               | 39 |

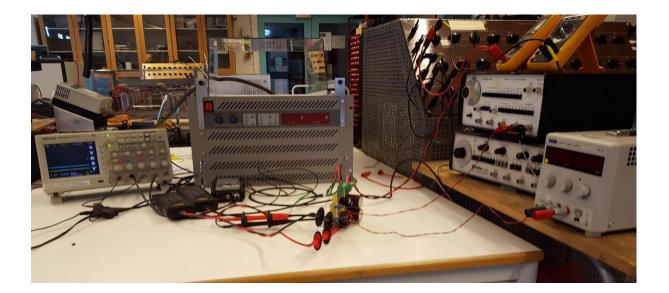

|   | 6.1 Set-up                                    | 39 |

|   | 6.1.1 Equipment                               | 40 |

|   | 6.1.1.1 Oscilloscope                          | 40 |

|   | 6.1.1.2 Voltage measuring                     | 41 |

|   | 6.1.1.3 Current measuring                     | 42 |

|   | 6.2 MEASUREMENT CONSIDERATIONS                | 43 |

|   | 6.3 TEST CIRCUIT                              | 44 |

|   | 6.4 CIRCUIT COMPONENTS                        | 44 |

|   | 6.4.1 Si MOSFET                               | 45 |

|   | 6.4.2 SiC MOSFET                              | 46 |

|   | 6.4.3 SiC Schottky diode                      | 47 |

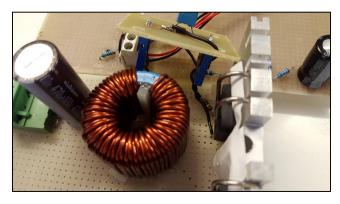

|   | 6.4.4 Boost choke inductor:                   | 47 |

|   | 6.4.5 Capacitors                              | 48 |

|   | 6.4.6 Gate driver                             | 48 |

|   | 6.4.7 Gate circuit components                 | 49 |

|   | 6.5 PARASITIC ELEMENTS IN THE BOOST CONVERTER | 50 |

| 7 | LABORATORY RESULTS                            | 53 |

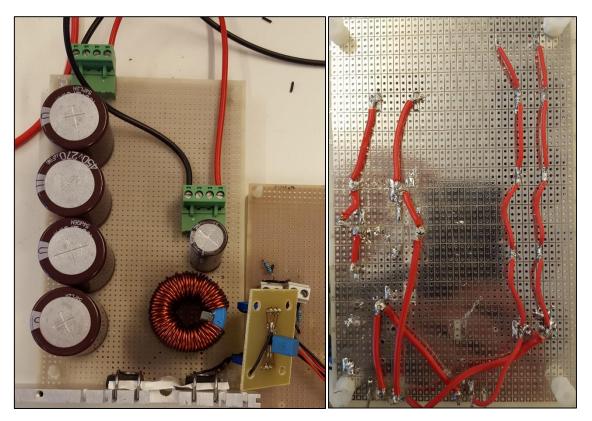

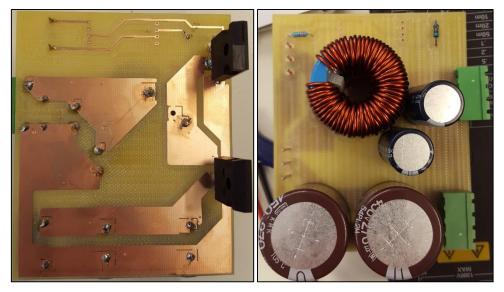

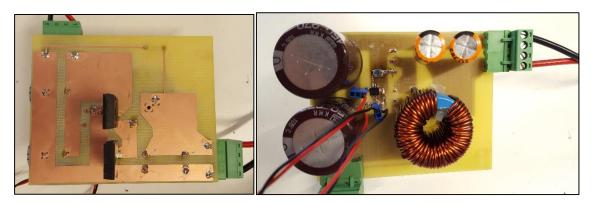

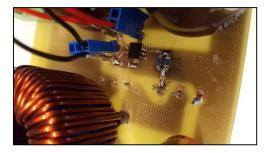

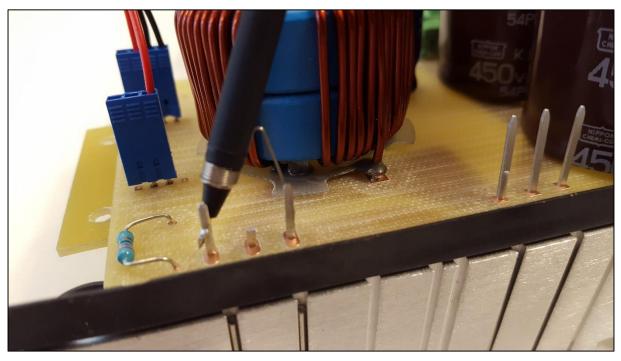

|   | 7.1 Veroboard                                 | 53 |

|   | 7.2 PCB LAYOUT                                | 54 |

|   | 7.3 SECOND PCB LAYOUT                         | 54 |

|   | 7.4 LOW FREQUENCY SHORT PULSE TEST            | 55 |

| 7.5 BC | OST CONVERTER TEST                                                               |

|--------|----------------------------------------------------------------------------------|

| 7.5.1  | SiC with UCC27531D gate driver and 20V gate voltage60                            |

| 7.5.2  | Si with UCC27531D gate driver and $11\Omega$ gate resistance                     |

| 7.5.3  | Si with FAN3224T gate driver and $11\Omega$ gate resistance                      |

| 7.5.4  | SiC with UCC27531D gate driver and 25V gate voltage                              |

| 7.5.5  | SiC with UCC27531D gate driver and $0\Omega$ gate resistance                     |

| 7.5.6  | Increased power with SiC, UCC27531D gate driver and $0\Omega$ gate resistance 69 |

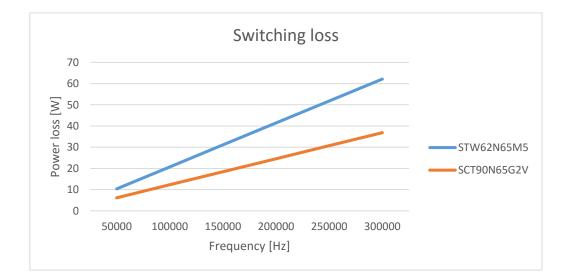

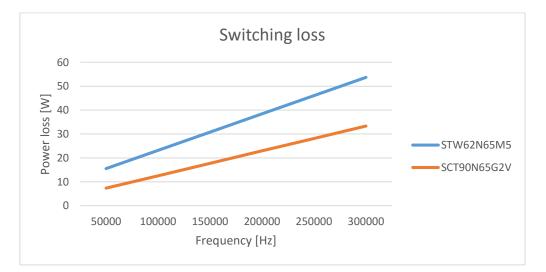

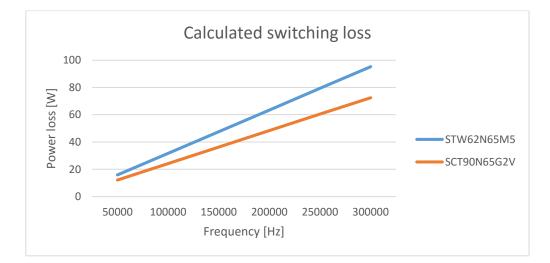

| 7.6 Sw | 71 TTCHING LOSS                                                                  |

| 7.6.1  | Oscilloscope energy loss71                                                       |

| 7.6.2  | Time-shifted waveforms energy loss                                               |

| 7.6.3  | Loss calculated based on theoretical inductive switching                         |

| 7.6.4  | Power loss                                                                       |

| 8 DISC | CUSSION                                                                          |

| 8.1 CI | RCUIT LAYOUT                                                                     |

| 8.2 M  | OSFET switching                                                                  |

| 8.3 M  | OSFET POWER LOSS                                                                 |

| 9 CON  | CLUSION                                                                          |

| 10 SUG | GESTIONS FOR FURTHER WORK 85                                                     |

| REFERE | NCES                                                                             |

| APPEND | IX A: LABORATORY SETUP                                                           |

| APPEND | IX B: CIRCUIT LAYOUTS                                                            |

| APPEND | IX C: PROBING WITH PASSIVE PROBE                                                 |

# List of figures

| Figure 1: Bridgeless Boost PFC converter                                            |

|-------------------------------------------------------------------------------------|

| Figure 2: Half-bridge LLC resonant converter with split resonant capacitor          |

| Figure 3: Frequency vs. output characteristics of an LLC resonant converter         |

| Figure 4: Conventional PFC topology7                                                |

| Figure 5: Simple boost converter7                                                   |

| Figure 6: Boost converter inductor voltage and current waveforms in CCM9            |

| Figure 7: Boost converter inductor voltage and current waveforms in Cr 10           |

| Figure 8: Boost converter inductor voltage and current waveforms in DCM             |

| Figure 9: Boost converter with simplified gate driver                               |

| Figure 10: Waveforms at turn-on in a boost converter                                |

| Figure 11: Current paths during the four time intervals at MOSFET turn-on           |

| Figure 12: waveforms at turn-off in a boost converter                               |

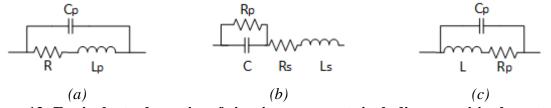

| Figure 13: Equivalent schematics of circuit components including parasitic elements |

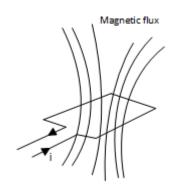

| Figure 14: Self-inductance principal sketch                                         |

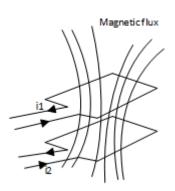

| Figure 15: Mutual inductance principal sketch                                       |

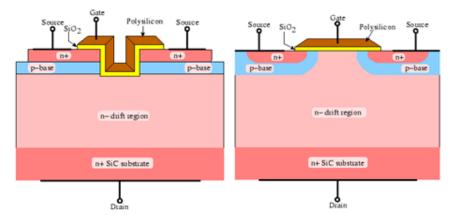

| Figure 16: SiC MOSFET cross section25                                               |

| Figure 17: Normalized drain-source on-resistance vs temperature                     |

| Figure 18: MOSFET intrinsic capacitance                                             |

| Figure 19: MOSFET gate charge vs gate-source voltage                                |

| Figure 20: Input, output and Miller capacitance vs drain-source voltage             |

| Figure 21: MOSFET gate charge vs gate voltage curve.                               | 31   |

|------------------------------------------------------------------------------------|------|

| Figure 22: Calculated switching loss from datasheet energy loss                    | 32   |

| Figure 23: Calculated MOSFET power loss from Equation 20.                          | 33   |

| Figure 24: Calculated switching loss from [5].                                     | 34   |

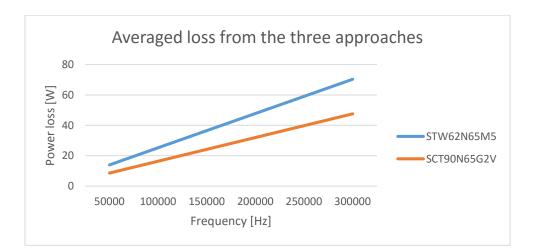

| Figure 25: Averaged switching loss from the three previous approaches              | 35   |

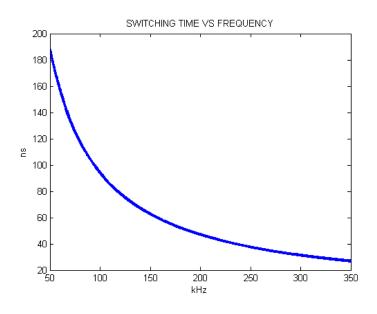

| Figure 26: Calculated maximum total switching time to achieve 25W MOSFET power los | s.36 |

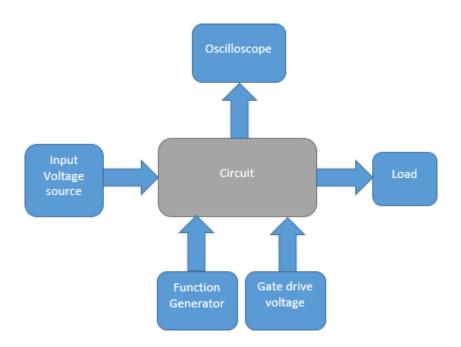

| Figure 27: Chart overview of laboratory set-up.                                    | 39   |

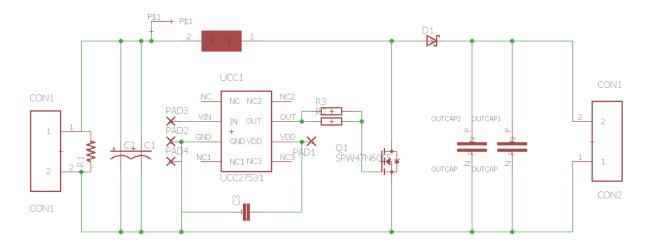

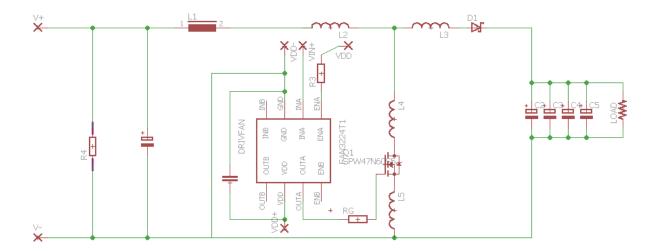

| Figure 28: Boost converter schematic                                               | 44   |

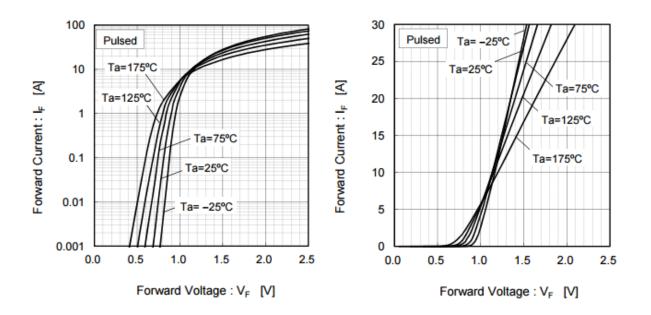

| Figure 29: Forward I-V characteristic of SCS220AE SiC SBD [29]                     | 47   |

| Figure 30: Boost choke inductor size comparison.                                   | 48   |

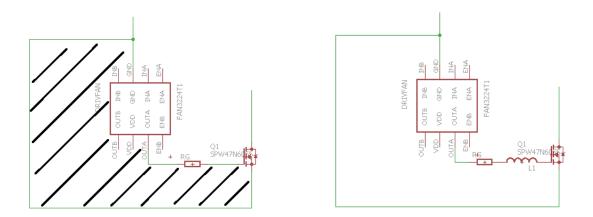

| Figure 31: Parasitic inductance in the boost converter.                            | 50   |

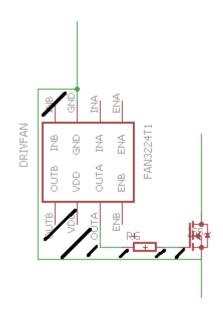

| Figure 32: Parasitic inductance in the gate driver.                                | 51   |

| Figure 33: Minimized parasitic inductance in the gate driver                       | 51   |

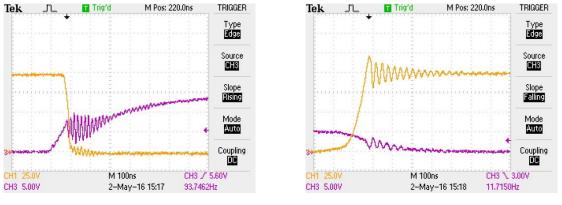

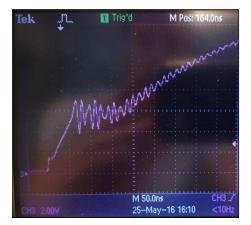

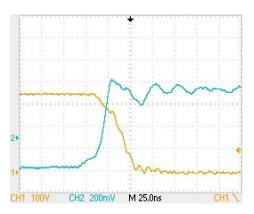

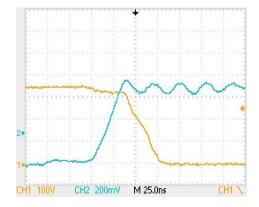

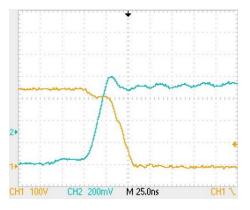

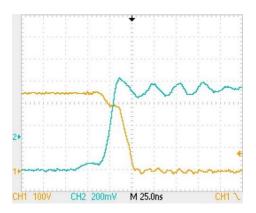

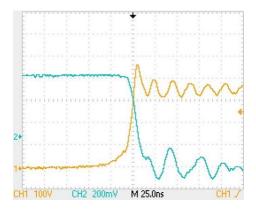

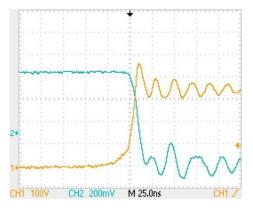

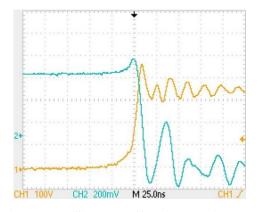

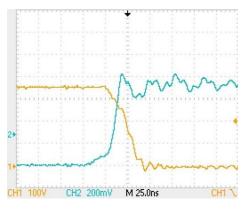

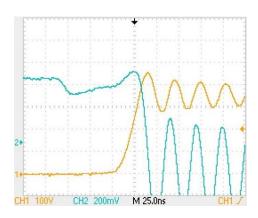

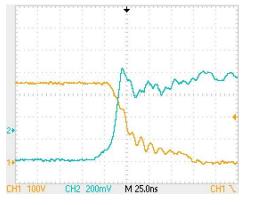

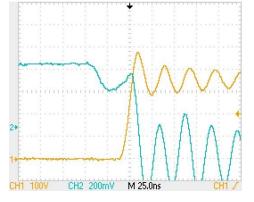

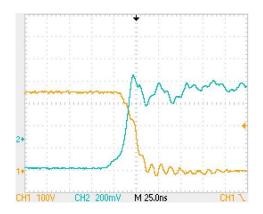

| Figure 34: Veroboard LF test turn-on.                                              | 55   |

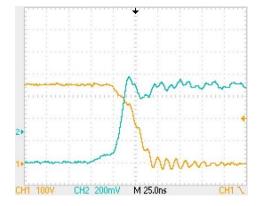

| Figure 35: Veroboard LF test turn-off                                              | 55   |

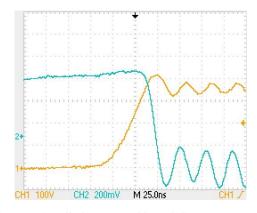

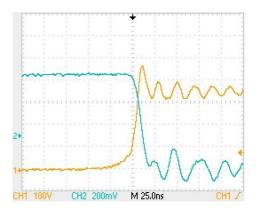

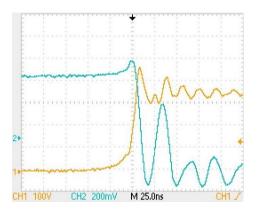

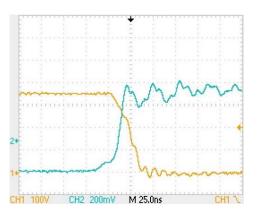

| Figure 36: First PCB LF test turn-on.                                              | 55   |

| Figure 37: First PCB LF test turn-off                                              | 55   |

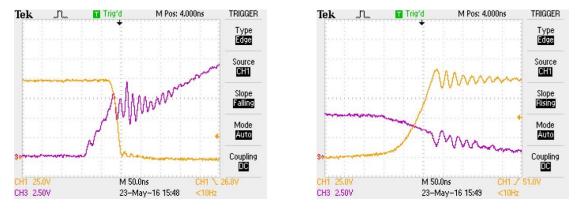

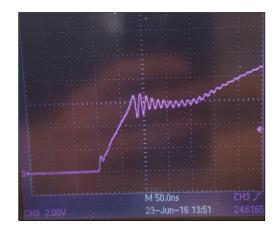

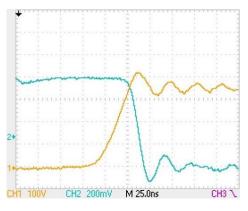

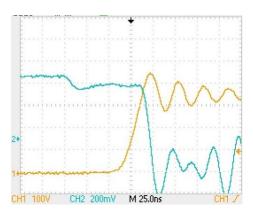

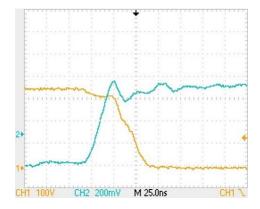

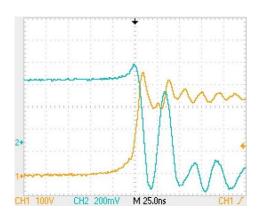

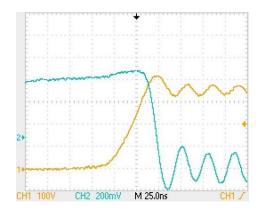

| Figure 38: Improved PCB LF test turn-on.                                           | 56   |

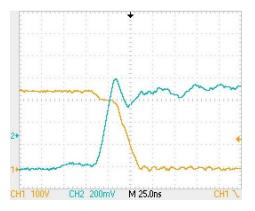

| Figure 39: Improved PCB LF test turn-off                                           | 56   |

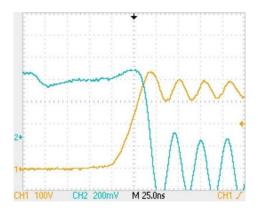

| Figure 40: First PCB gate voltage at turn-on measured with passive probe           | 56   |

| Figure 41: Final PCB gate voltage at turn-off measured with passive probe          | 56   |

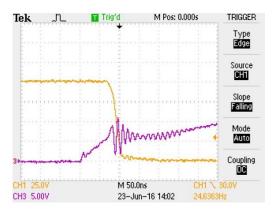

| Figure 42: SiC Turn-on. UCC27531D gate driver. Rg=11Ω. Vgs=20V       |  |  |  |  |

|----------------------------------------------------------------------|--|--|--|--|

| Figure 43: SiC turn-off. UCC27531D gate driver. Rg=11Ω. Vgs=20V60    |  |  |  |  |

| Figure 44: SiC turn-on. UCC27531D gate driver. Rg=7,5Ω. Vgs=20V60    |  |  |  |  |

| Figure 45: SiC turn-off. UCC27531D gate driver. Rg=7,5Ω. Vgs=20V60   |  |  |  |  |

| Figure 46: SiC turn-on. UCC27531D gate driver. Rg=5Ω. Vgs=20V60      |  |  |  |  |

| Figure 47: SiC turn-off. UCC27531D gate driver. Rg=5Ω. Vgs=20V60     |  |  |  |  |

| Figure 48: Si turn-on. UCC27531D gate driver. Rg=11Ω. Vgs=12V62      |  |  |  |  |

| Figure 49: Si turn-off. UCC27531D gate driver. Rg=11Ω. Vgs=12V62     |  |  |  |  |

| Figure 50: Si turn-on. UCC27531D gate driver. Rg=11Ω. Vgs=15V62      |  |  |  |  |

| Figure 51: Si turn-off. UCC27531D gate driver. Rg=11Ω. Vgs=15V62     |  |  |  |  |

| Figure 52: Si turn-on. UCC27531D gate driver. Rg=11Ω. Vgs=20V        |  |  |  |  |

| Figure 53: Si turn-off. UCC27531D gate driver. Rg=11Ω. Vgs=20V62     |  |  |  |  |

| Figure 54: Si turn-on. FAN3224T gate driver. Rg=11Ω. Vgs=12V64       |  |  |  |  |

| Figure 55. Si turn-off. FAN3224T gate driver. Rg=11Ω. Vgs=12V        |  |  |  |  |

| Figure 56: Si turn-on. FAN3224T gate driver. Rg=11Ω. Vgs=15V64       |  |  |  |  |

| Figure 57: Si turn-off. FAN3224T gate driver. Rg=11Ω. Vgs=15V64      |  |  |  |  |

| Figure 58: Si turn-on. FAN3224T gate driver. Rg=11Ω. Vgs=17,5V64     |  |  |  |  |

| Figure 59: Si turn-off. FAN3224T gate driver. Rg= $11\Omega$ 17,5V64 |  |  |  |  |

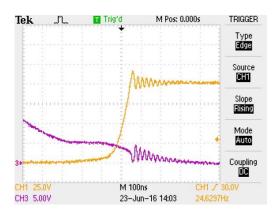

| Figure 60: SiC turn-on. UCC27531D gate driver. Rg=11Ω. Vgs=25V       |  |  |  |  |

| Figure 61: SiC turn-off. UCC27531D gate driver. Rg=11Ω. Vgs=25V66    |  |  |  |  |

| Figure 62: SiC turn-on. UCC27531D gate driver. Rg=7,5Ω. Vgs=25V      |  |  |  |  |

| Figure 63: SiC turn-off. UCC27531D gate driver. Rg=7,5Ω. Vgs=25V66        |  |  |  |  |

|---------------------------------------------------------------------------|--|--|--|--|

| Figure 64: SiC turn-on. UCC27531D gate driver. Rg=5Ω. Vgs=25V             |  |  |  |  |

| Figure 65: SiC turn-off. UCC27531D gate driver. Rg=5Ω. Vgs=25V            |  |  |  |  |

| Figure 66: SiC turn-on. UCC27531D gate driver. Rg=0Ω. Vgs=20V68           |  |  |  |  |

| Figure 67: SiC turn-off. UCC27531D gate driver. Rg=0Ω. Vgs=20V68          |  |  |  |  |

| Figure 68: SiC turn-on. UCC27531D gate driver. Rg=0Ω. Vgs=25V             |  |  |  |  |

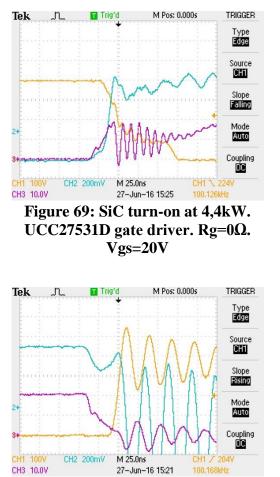

| Figure 69: SiC turn-on at 4,4kW. UCC27531D gate driver. Rg=0Ω. Vgs=20V69  |  |  |  |  |

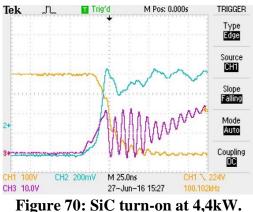

| Figure 70: SiC turn-on at 4,4kW. UCC27531D gate driver. Rg=0Ω. Vgs=25V69  |  |  |  |  |

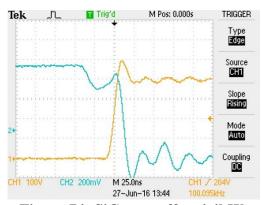

| Figure 71: SiC turn-off at 4kW. UCC27531D gate driver. Rg=0Ω. Vgs=20V     |  |  |  |  |

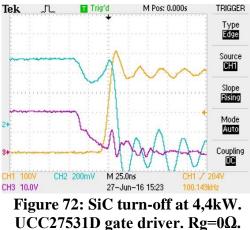

| Figure 72: SiC turn-off at 4,4kW. UCC27531D gate driver. Rg=0Ω. Vgs=20V   |  |  |  |  |

| Figure 73: SiC turn-on at 4,4kW. UCC27531D gate driver. Rg=0Ω. Vgs=25V70  |  |  |  |  |

| Figure 74: SiC turn-off at 4,4kW. UCC27531D gate driver. Rg=0Ω. Vgs=20V70 |  |  |  |  |

| Figure 75: Switching loss for SCT90N65G2C SiC MOSFET74                    |  |  |  |  |

| Figure 76: Switching loss for STW62N65M5 Si MOSFET74                      |  |  |  |  |

| Figure 77: Total power loss for SCT90N65G2V SiC MOSFET                    |  |  |  |  |

| Figure 78: Total power loss for STW62N65M5 Si MOSFET75                    |  |  |  |  |

| Figure 79: Conceptual sketch of a gate driver78                           |  |  |  |  |

# List of tables

| Table 1: Comparison of the effects of operational mode of the boost converter                           | . 13 |

|---------------------------------------------------------------------------------------------------------|------|

| Table 2: SiC properties compared to Si[13]                                                              | . 23 |

| Table 3: Capacitance and charge comparison of silicon and silicon carbide MOSFET                        | . 30 |

| Table 4: Datasheet energy loss and scaled energy loss                                                   | . 32 |

| Table 5: Calculated switching energy loss from Equation 20.                                             | . 33 |

| Table 6: Expected inductor and SBD power loss at rated power                                            | . 37 |

| Table 7: List of lab equipment.                                                                         | . 40 |

| Table 8: Tektronix TDS2014B oscilloscope parameters [22]                                                | . 41 |

| Table 9: Tektronix P5200A differential probe parameters [25]                                            | . 42 |

| Table 10: PEM CWT06 parameters [28].                                                                    | . 42 |

| Table 11: List of circuit components                                                                    | . 45 |

| Table 12: SWT62N65M5 parameters [18]                                                                    | . 45 |

| Table 13: Parameters of SCT90N65G2V SiC MOSFET [21].                                                    | . 46 |

| Table 14: Features of FAN3224T[30] and UCC27531D[31] gate driver ICs.                                   | . 49 |

| Table 15: Boost converter ratings.                                                                      | . 58 |

| Table 16: Measurements from SiC MOSFET switching transients with UCC27531D gate                         |      |

| driver. Vgs=20V                                                                                         | 61   |

| Table 17: Measurements from Si MOSFET switching transients with UCC27531D gate driver. Rg=11 $\Omega$ . | . 63 |

| Table 18: Measurements from Si MOSFET switching transients with FAN3224T gate drive                     | er.  |

| Rg=11Ω                                                                                                  | . 65 |

| Table 19: Measurements from SiC MOSFET switching transients with UCC27531D gate           |

|-------------------------------------------------------------------------------------------|

| driver. Vgs=25V67                                                                         |

| Table 20: SiC turn-on. UCC27531D gate driver. Vgs=25V    70                               |

| Table 21: SiC turn-off. UCC27531D gate driver. Vgs=20V.    70                             |

| Table 22: Switching energy loss based directly on oscilloscope readout.    72             |

| Table 23: Switching energy loss from oscilloscope with skewed time delay.    72           |

| Table 24: Fasted switching times and energy loss based on theoretical inductive switching |

| progression73                                                                             |

### Abbreviations

- **A** Ampere

- AC Alternating Current

- C Capacitance

- Cds Drain-source capacitance

- Cgd Gate-drain capacitance

- Cgs Gate-source capacitance

- Ciss MOSFET input capacitance

- Coss MOSFET output capacitance

- Crss MOSFET reverse transfer capacitance (Miller capacitance)

- **CCM** Continuous Conduction Mode

- CrM Critical Conduction Mode

- DC Direct Current

- **DCM** Discontinuous Conduction Mode

- $E_{off}$  Turn-on energy loss

- Eon Turn-off energy loss

- E<sub>sw</sub> Total switching energy loss

- ESR Equivalent Series Resistance

- EMI Electromagnetic Interference

- EV Electric Vehicle

- **F** Farad

- H Henry

- I Current

- **IC** Integrated Circuit

- MOSFET Metal Oxide Semiconductor Field-Effect Transistor

- **OBC** On-Board Charger

- PCB Printed Circuit Board

- PFC Power Factor Correction

- PHEV Plug-in Hybrid Electric Vehicle

- **Q** Charge [Coulomb]

- $Q_g$  Total gate charge

- $Q_{gd}$  Gate-drain charge

- $Q_{gs}$  Gate-source charge

- **SBD** Schottky Barrier Diode

- Si Silicon

- SiC Silicon Carbide

- SMD Surface Mount Device

- SFR Self-Resonant Frequency

- t<sub>fc</sub> Current fall-time

- tfv Voltage fall-time

- toff Turn-off time

- $t_{on}$  Turn-on time

- trc Current rise-time

- trv Voltage rise-time

- V Voltage

- Vds MOSFET drain to source voltage

- Vgs MOSFET gate to source voltage

- ZCS Zero Current Switching

- ZVS Zero Voltage Switching

## 1 Introduction

The master thesis is a continuation of the specialization project fall 2016. The topic is silicon carbide semiconductor for use in the on-board charger of electric and plug-in hybrid vehicles. The material properties of silicon carbide suggest faster switching and lower switching loss. Since the switching loss is proportional with the switching frequency, lower switching loss suggest the switching frequency can be increased, keeping the efficiency at an acceptable level. This is highly beneficial since a higher frequency equals smaller passive components in the circuit, which reduces the size and weight of the charger.

Electric and plug-in hybrid electric vehicles are becoming increasingly popular amongst new car buyers around the world. In Norway especially, thanks to the government incentives, sales have shot through the roof in recent years. The technology is improving rapidly, and the car manufacturers are continuously looking to increase the battery range and improve charging.

The On-Board Charger (OBC) is an essential part of the vehicle. Without it, the batteries could not be charged from your home. The AC voltage in the wall socket is converted into a regulated DC voltage that can charge the batteries in the car. The conversion is performed through power converters, and require semiconductor switches to work. These switches include loss. Apart from the voltage drop over the switch while it is conducting, high instantaneous power loss occur both then the switch turn on and off. This loss is proportional to the frequency of which the switch is operated.

Since the size of passive components is reduced, and power loss is increased, as the frequency is increased, designers must compromise between the total efficiency and the overall size of the OBC when setting the operating frequency. If the switching losses could be reduced, the frequency could be increased without compromising with efficiency. Thus, the size of the OBC could be reduced.

#### 1.1 Scope of work

The thesis will focus on the difference between silicon and silicon carbide MOSFET in hard switch application, as the power factor corrector in the charger.

To execute this, a DCDC step-up converter will be constructed. Since a conventional PFC converter is a diode bridge rectifier followed by a boost converter, this will be sufficient to study the behavior of the MOSFETs. The ultimate goal is for the boost converter to deliver 3500W power at 350V with an efficiency of 98%. The peak-to-peak current ripple is set to be no more than 2A.

The thesis include a theoretical description of the boost converter and its modes of operation, justifying the choice of approach. The switching behavior of the MOSFET in this circuit, and considerations needed to be taken when designing it, will be explained. A theoretical presentation of silicon carbide as a semiconductor material and its applications is included, as well as a comparison between silicon and silicon carbide MOSFETs parameters and loss calculations based on these parameters. Finally, the boost converter will be tested with both silicon and silicon carbide MOSFETs, and compared.

## 2 On-Board Charger

An On-board Charger (OBC) is a power conversion hardware. Its purpose is to charge the vehicle batteries at the correct DC voltage when power is drawn from the AC mains. The input is converted through two stages. A power factor corrector (PFC) converts the AC input to DC while keeping the input voltage and current sinusoidal and in phase, while a DCDC converter provides the desired voltage to the battery. The PFC is a crucial part of the OBC. Without it, the harmonic distortion in the current would violate the utility grid restrictions and the converter would have to be designed for much higher peak currents. Additionally, the OBC includes, among other, controllers, soft starter, measurements and CAN (Controller Area Network) bus for communication with the vehicle. This will however not be discussed further in this thesis.

A conventional PFC consist of DCDC converter, usually a step-up converter, preceded by a diode bridge rectifier. The step-up converter is often the preferred choice in active current shaping because when the switch is off, the input directly feeds the output. Additionally, when the output voltage is higher than the peak of the input, the converter is more stable and can handle both over- and undervoltages at the input [1].

#### 2.1 GEN2 Charger

Valeo PECs current charger, the GEN2 (generation 2), is a 3,5kW 350V output charger. Its power conversion is operated through a PFC at the input, and then through an LLC resonant converter, which outputs the desired voltage to the batteries. LLC stands for the two inductors, noted L, and one capacitor, noted C, which constitutes the resonant tank of this specific resonant converter.

The PFC in this charger is a bridgeless PFC. It utilizes two switches, one for each half cycle. This eliminates the need for a diode rectifier bridge at the input. This is beneficial in terms of efficiency, as it reduces the number of semiconductor devices in the conduction path from three to two.

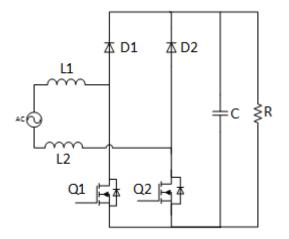

Figure 1: Bridgeless Boost PFC converter

Figure 1 shows a simple bridgeless PFC converter, patented in 1983. The switches alternate between operating as high frequency chopper and low frequency half-wave rectifier. When the sinusoidal input is on its positive half cycle, current flows from the input voltage through L1. When switch Q1 is off, current flow through D1 and to the output. When Q1 is on, current flows through it. The return path in both cases is through the antiparallel diode in Q2. When the switch is on its negative half cycle, current flow from the input through L2. When Q2 is off, the current flow through D2 to the output. When Q2 is on, the current flow through it. Here, the return path of the current is through the antiparallel diode in Q1.

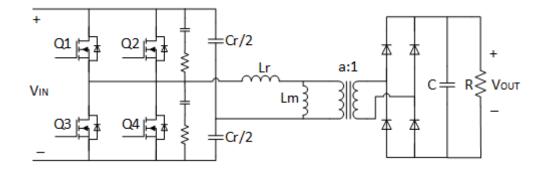

After the PFC is a DCDC converter. The solution here is an LLC resonant converter, which serves two functions. The first is to provide the correct output voltage at all times for all load conditions. The second is to provide a galvanic isolation between the input and output. A simplified model of the LLC converter in the charger is shown in Figure 2

The LLC converter is a popular choice in power conversion because of its high efficiency, high power density and low electromagnetic interference (EMI). The switching bridge generates a square waveform to excite the resonant tank (Cr, Lr, Lm). The resonant tank outputs a sinusoidal current that is scaled by the transformer and rectified by the rectifier bridge. The output capacitor filters the rectified AC current and outputs a DC voltage [2].

Figure 2: Half-bridge LLC resonant converter with split resonant capacitor

The specific topology used in this charger is a half-bridge resonant LLC with split resonant capacitor. This topology is especially useful at higher power levels as the current stress in each capacitor is reduced. It also makes the input current to the resonant tank look like that of a full-bridge converter. This reduces both the input differential mode noise and the stress on the input capacitor [3]. Additionally, this converter uses two parallel switches, which reduces the switching and conduction loss [4].

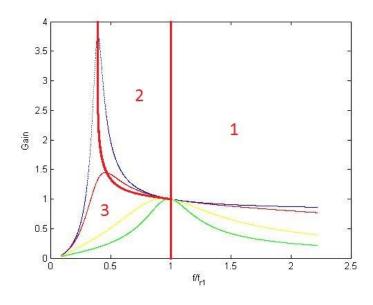

Figure 3: Frequency vs. output characteristics of an LLC resonant converter

Figure 3 show a typical gain characteristic for an LLC converter. The vertical axis show the input-to-output gain on the converter, and the horizontal axis show the normalized frequency. An LLC converter is normally designed to operate in area 1 and 2, shown in the figure. In these areas, the converter operates at zero voltage switching (ZVS), while in area 3, the converter

operates in zero current switching (ZCS). ZVS operation is usually preferred over ZCS as it shows higher efficiency and lower electromagnetic interference (EMI).

### 3 Boost Converter

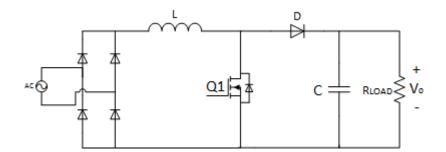

There are several types of PFC topologies. However, the most known and used topology is the conventional PFC in Figure 4. This is a boost converter preceded by a diode bridge rectifier, creating a rectified sinusoidal input.

Figure 4: Conventional PFC topology

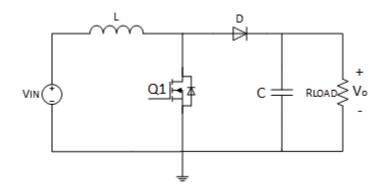

The boost converter in Figure 5, also known as a step-up converter, takes an input voltage and provide an output voltage higher than the input. How much higher the output will be compared to the input is determined by the switch duty cycle, which is defined as the on time divided by the length of the switching period. When the switch is turned on, the diode is reverse biased and the input supplies energy to the inductor. When the switch is turned off, the output receives energy from the input and the inductor. The converter has two distinct modes of operation: continuous- and discontinuous-conduction.

Figure 5: Simple boost converter

#### 3.1 Continuous-conduction

In continuous-conduction mode (CCM), the current through the inductor never reaches zero in steady state. Recognizing that, in steady state, the voltage over the inductor over one switching period must be zero, then for the ideal converter the relationship between input and output voltage can be expressed as in Equation 1.

$$V_o = \frac{1}{1-d} V_{in} \tag{1}$$

Where d is the duty cycle, and is defined in Equation 2.

$$d = \frac{t_{on}}{T_s} \tag{2}$$

The ideal converter is also lossless in terms of energy, so the relationship between input and output current is found as in Equation 3.

$$I_o = (1-d)I_{in} \tag{3}$$

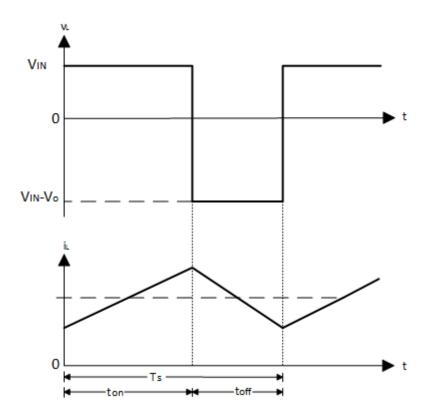

Figure 6: Boost converter inductor voltage and current waveforms in CCM

Figure 6 shows the steady state inductor waveforms for a CCM boost converter for one switching period. When the switch is on, the input voltage is applied over the inductor, and the current through the inductor rises. When the switch turn off, a negative voltage (Vin-Vo) is applied over the inductor, and the current decreases.

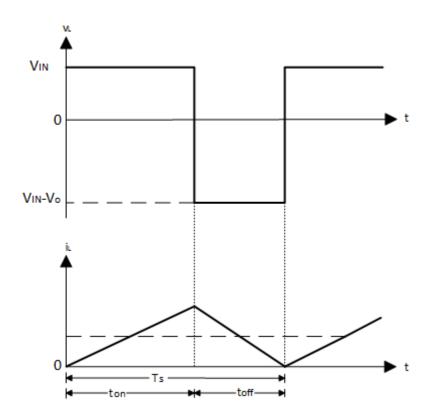

#### 3.2 Border between continuous and discontinuous

This is defined as the operation mode when the inductor current just reaches zero at the end of the off interval. It is also known as critical conduction mode (CrM). Even though it is called CrM, the current does not go below zero, so this is a special case of continuous mode of operation. Figure 7 shows the steady state waveforms of the inductor voltage and current in CrM. The average inductor current in this mode can be found by Equation 4.

$$I_{LB} = \frac{V_{in}}{2L} t_{on} = \frac{V_{in}d}{2Lf_s} = \frac{V_o}{2Lf_s} d(1-d)$$

(4)

This equation can also be used to find the peak-to-peak current ripple, which is valid for continuous conduction as well. Since, at the border, the average current is half of the peak current, the current ripple can be expressed as Equation 5.

$$\Delta i_L = \frac{V_{in}d}{Lf_s} \tag{5}$$

Since the inductor current is the same as the input current, the output current can be found using Equation 6

$$I_{oB} = \frac{V_o}{2Lf_s} d(1-d)^2$$

(6)

If the load current drops below this, the inductor current drops below  $I_{LB}$ , and the converter will be in discontinuous-conduction mode.

Figure 7: Boost converter inductor voltage and current waveforms in Cr

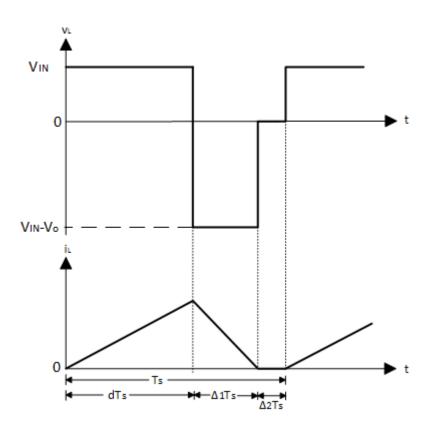

#### 3.3 Discontinuous-conduction mode

In this mode, the inductor current drops to zero, and stays at zero for a portion of the switching interval. There are thus three stages in this mode.

- When the switch is on and the diode is reverse biased. The inductor current rises. (dT<sub>s</sub>)

- When the switch is off and the diode is forward biased. The inductor current decreases.  $(\Delta_1 T_s)$

- When the switch is off and the diode is reverse biased. The inductor current is zero.  $(\Delta_2 T_s)$

Figure 8 shows the inductor voltage and current waveforms in a boost converter operating in discontinuous conduction mode (DCM).

Figure 8: Boost converter inductor voltage and current waveforms in DCM

Equating the time integral of the inductor voltage over one period, the relationship between input and output voltage is expressed in Equation 7, and current in Equation 8.

$$V_o = \frac{\Delta_1 + d}{\Delta_1} V_{in} \tag{7}$$

And

$$I_o = \frac{\Delta_1}{\Delta_1 + d} I_{in} \tag{8}$$

The average input (or inductor) current is

$$I_{in} = \frac{V_d}{2Lf_s} d(d + \Delta_1) \tag{9}$$

Inserting Equation 8 in Equation 9 gives the average output current in Equation 10.

$$I_o = \frac{V_d d\Delta_1}{2Lf_s} \tag{10}$$

Looking at the above equations it is clear that a DCM converter will have a much smaller inductor than a CCM converter. This is beneficial for a compact converter. However, the ripple in the current is a concern. For a 3500W converter, the average inductor current will be 15,2A. A converter operating on the border of continuous and discontinuous would then have peak currents above 30A, and even higher for discontinuous-conduction. This will have a large impact on the peak ratings of the components and the size of the output filter. Because of this, a converter at this power level should be designed as a continuous-conduction converter.

Table 1 summarizes and compare the effects that the different operational modes of the boost converter have on the circuit. While CrM and DCM have the benefits of small inductor size and essentially no turn-on losses, they have the disadvantage of large peak currents that introduce high turn-off losses and problems with filtering these currents. Even though the CCM converter has high turn-on losses, which can be intensified by the reverse recovery loss of the boost diode, the advantages of lower peak currents, lower turn-off losses and lower high frequency ripple that must be filtered, makes it a preferred choice in high power applications [5].

| Parameter      | ССМ      | CrM        | DCM        |

|----------------|----------|------------|------------|

| Current ripple | Lowest   | High       | Highest    |

| Inductor size  | Largest  | Small      | Smallest   |

| EMI filter     | Smallest | Large      | Largest    |

| Turn-on loss   | Highest  | Low (zero) | Low (zero) |

| Turn-off loss  | Lowest   | High       | Highest    |

Table 1: Comparison of the effects of operational mode of the boost converter.

#### 3.4 Converter Parameter setting

For proper and desired operation of the converter, the components must be properly dimensioned. The most important components are the boost inductor and the output capacitance. The main features of these are the current ripple in the converter and the output voltage ripple.

#### 3.4.1 Output capacitance

The output capacitance is decided from the desired output voltage ripple. Assuming that the ripple component of the current through the diode flows through the capacitor and its average value flows through the load resistor, the voltage ripple can be calculated using the charge difference.

$$\Delta V_o = \frac{\Delta Q}{C} \tag{11}$$

This charge is then equal to the average output current multiplied with the on-time of the switch.

$$\Delta Q = I_o t_{on} = I_o D T_s \tag{12}$$

Inserting Equation 12 in Equation 11 and rearranging the terms, the capacitance can be found based on the desired output voltage ripple in Equation 13. This is valid for a constant output current.

$$C = \frac{I_o D T_s}{\Delta V_o} \tag{13}$$

In addition to the capacitance of the output capacitor, the equivalent series resistance (ESR) of the capacitor is an important factor to consider, which is explained in more detail in Chapter 3.6.

#### 3.4.2 Boost inductor

The boost inductor is a crucial design step for the converter. The inductance for CCM boost converter is determined from the desired current ripple, and is calculated from Equation 5. Apart from the inductance, the inductor must be able to handle the currents without saturating the core, and its resistance should be as low as possible to minimize loss. The core material selection is also of great importance, as it must be able to operate properly at the selected frequency.

#### 3.5 Boost Switching Basics

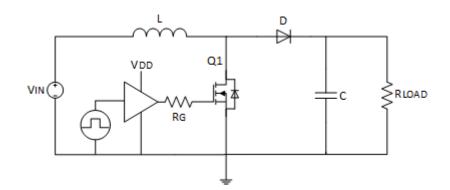

In order to design a good gate driver, one must understand what happens in the circuit at turnon and turn-off of the switch. Figure 9 show a boost converter with a simplified gate driver.

Figure 9: Boost converter with simplified gate driver

This circuitry is known as clamped inductive switching. Now the inductor L is assumed large enough to provide a constant current during the switching interval. When the MOSFET is turned on, the input voltage is applied over the inductor and the current ramps up to store energy. When the MOSFET turns off, the inductor current flows through diode D1, delivering energy to the output. The circuit waveforms at turn-on are illustrated in Figure 10 [6].

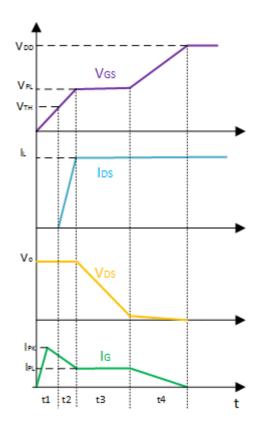

The turn-on of the MOSFET can be divided into four intervals. During the first interval, t1, the gate current charges the gate-to-source (Cgs) and gate-to-drain (Cgd) capacitances of the MOSFET to the gate threshold voltage Vth. Before these capacitances are charged to the threshold voltage, no current can flow through the MOSFET. This interval is therefore called the turn-on delay [6].

During the second interval, t2, the MOSFET start conducting current in the linear mode. Cgs and Cgd are charged to the plateau level as the drain current rises from zero to IL. The plateau level, known as the Miller plateau, is where the gate-source voltage remain constant for short time during the switching period. The drain-source voltage during this time interval is clamped at output voltage. The charge needed is Qgs, and the length of the time interval can be calculated as t2=Qgs/Ig [6].

Figure 10: Waveforms at turn-on in a boost converter

The third time interval starts as the MOSFET conducts the entire inductor current. As t3 starts, the gate current flow through Cgd and the MOSFET channel. The gate current discharges Cgd as the gate-source voltage remain at the Miller plateau, and the drain-source voltage fall. This interval last until the drain-source voltage reaches zero (or near zero), and is given by t3=Qgd/Ig [6].

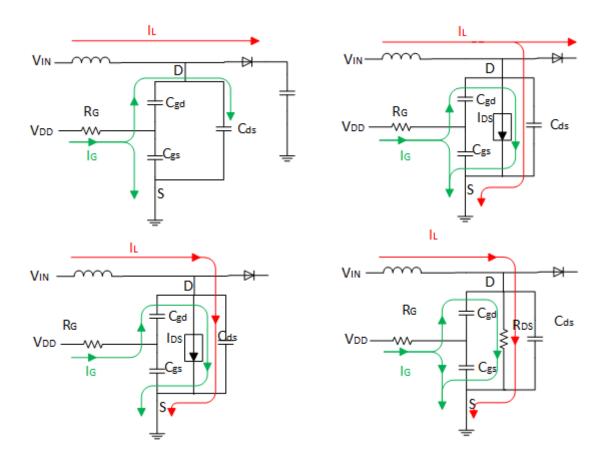

In interval four, the gate-source voltage rises from the plateau level to Vdd (or full driver voltage). Ig flow through a combination of Cgs, Cgd and the decreasing channel resistance. The current paths during turn-on of a MOSFET are shown in Figure 11 [6].

Figure 11: Current paths during the four time intervals at MOSFET turn-on. Top left: t1; top right: t2; bottom left: t3; bottom right: t4.

The switching loss during turn-on is related to time interval t2 and t3. During turn-off, the waveforms and current paths are much like the ones for turn-on, but in reverse order, as shown in Figure 12.

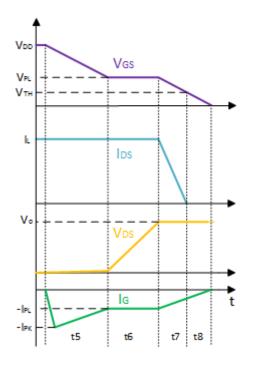

During interval t5, the gate current rises to discharge the gate-source voltage from Vdd to the plateau level. Vgs remain at this level during t6, while the drain-source voltage rises to the off-state voltage. The length of this time interval is found as t6=Qgd/Ig.

In t7, the drain current fall from IL to zero while the gate-source voltage falls to the threshold voltage. This time interval is calculated as t7=Qgs/Ig. During t8, the gate-source voltage is discharged to zero[6].

Figure 12: waveforms at turn-off in a boost converter

Turn-on or turn-off of a MOSFET can thus be divided into four time intervals. The length of these intervals is dependent on the parasitic capacitance, required voltage change across them and the available gate drive current. A thorough and careful selection of components is therefore important for a high efficiency and high frequency converter [6].

The switching loss during turn-on and turn-off can be estimated as in Equation 14 and 15 respectively [6].

$$P_{SW,ON} = \frac{V_D \cdot I_D}{2} \cdot f_s \cdot (t_2 + t_3) \tag{14}$$