# Verification of a Large Heterogeneous Many-core Computer

Eivind Gamst Edward Mitacc

Embedded Computing Systems Submission date: June 2016 Supervisor: Donn Morrison, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# Summary

The historical trend of steady increase in processor performance with each technology generation has slowed down during the last years due to power limitations. As transistor sizes reduce, the power density on a chip does not remain constant anymore, which is known as the end of Dennard scaling. This increase of power demand limits the number of transistors that can be used simultaneously without exceeding the power budget. This phenomenon, known as the Dark Silicon effect, can be mitigated by building heterogeneous systems containing processing elements of different performance and power characteristics. The SHMAC project at the NTNU aims to provide a platform for investigating heterogeneous systems at all abstraction levels.

Current verification strategies for verifying the hardware parts of the SHMAC platform include block-level and top-level testbenches, and bare-metal testing on FPGA. Both of them run directed tests that exercise specific features of the design, which are manually handcrafted by each SHMAC developer. This approach not only represents a tedious task for the designer, but also does not ensure to reach all corner cases within the design. In addition, these verification strategies lack of coverage metrics that measure verification progress and quality, and do not provide mechanisms to effectively identify and track bugs in the design.

This project proposes a new verification framework and methodology for the SHMAC platform using the Universal Verification Methodology (UVM). This new methodology is aimed to overcome the limitations of the existing verification strategies previously presented, and also is intended to provide highly reusable verification environments. The latter plays an important role in reducing the effort and time spent on creating new tests as the design complexity of the SHMAC platform increases and new extensions are implemented.

# Preface

This thesis is submitted to the Norwegian University of Science and Technology as a partial fulfillment of the requirements for a masters degree. The thesis is written as a part of the SHMAC research project by EECS, NTNU. The project researches challenges in heterogeneous computing systems, for improved energy efficiency.

The work was performed at the Department of Electronics and Telecommunications, Faculty of Information Technology, Mathematics and Electrical Engineering, NTNU, Trondheim, with Donn Morrison as supervisor.

We would like to thank Donn for useful feedback and a positive attitude. Our weekly meeting with Donn has helped as a motivation to keep up a consistent amount of work. It's much thanks to these meetings that this thesis is at the level it is now.

Eivind want to give a special thanks to Donn for allowing him to work remotely and have all the meetings through an online video service.

# Table of Contents

| Su | ımma    | ry      |                                | i   |

|----|---------|---------|--------------------------------|-----|

| Pr | reface  |         |                                | ii  |

| Ta | ble of  | Conter  | nts                            | v   |

| Li | st of ] | Tables  |                                | vii |

| Li | st of I | igures  |                                | ix  |

| A  | crony   | ms      |                                | x   |

| 1  | Intr    | oductio | n                              | 1   |

|    | 1.1     | Motiva  | ntion                          | 1   |

|    | 1.2     | Requir  | rements for the project        | 4   |

|    | 1.3     | Report  | structure                      | 5   |

| 2  | Bacl    | kground | 1                              | 7   |

|    | 2.1     | SHMA    | AC                             | 7   |

|    | 2.2     | Verific | ation                          | 8   |

|    |         | 2.2.1   | Directed test                  | 9   |

|    |         | 2.2.2   | Static Verification            | 10  |

|    |         | 2.2.3   | Dynamic Verification           | 10  |

|    |         | 2.2.4   | Electronic System-Level Design | 12  |

|    |         | 2.2.5   | Transaction-Level-Modeling     | 12  |

|    |         | 2.2.6   | SystemVerilog                  | 15  |

|    |         | 2.2.7   | Verification Methodologies     | 17  |

|    | 2.3     | UVM     |                                | 17  |

|    | 2.4     | System  | nC Modeling                    | 20  |

|    |         | 2.4.1   | Class concept for hardware     | 20  |

|    |         | 2.4.2   | Simulation Kernel              | 21  |

|    |         |         |                                |     |

|   |            | 2.4.3 Threads and Methods                                               | 21       |

|---|------------|-------------------------------------------------------------------------|----------|

|   |            | 2.4.4 Events, Sensitivity and Notifications                             | 22       |

|   |            | 2.4.5 Channels and interfaces                                           | 22       |

|   |            | 2.4.6 Modules and Hierarchy                                             | 22       |

|   |            | 2.4.7 Data types: Logic, Integers, Fixed point                          | 23       |

|   | 2.5        | UVMC                                                                    | 23       |

|   |            | 2.5.1 Enabling IP and VIP reuse                                         | 23       |

|   |            | 2.5.2 Key features                                                      | 23       |

|   |            | 2.5.3 Making UVMC Connections                                           | 23       |

|   |            | 2.5.4 Transaction Conversion                                            | 24       |

|   | 2.6        | Questasim                                                               | 24       |

| 3 | Rela       | ted work                                                                | 25       |

| 5 | 3.1        | Previous works in regards to verification of complex heterogeneous sys- | 40       |

|   | 5.1        | tems and SoCs                                                           | 25       |

|   | 3.2        | Industry verification approaches                                        | 23       |

|   | 3.2        | ARM verification                                                        | 28       |

|   | 3.3<br>3.4 |                                                                         | 28<br>29 |

|   | 5.4        | Summary                                                                 | 29       |

| 4 | SHN        | IAC verification methodology                                            | 31       |

|   | 4.1        | Analysis of the current verification strategies                         | 31       |

|   | 4.2        | Proposed verification methodology                                       | 32       |

|   |            | 4.2.1 Elaboration of a circuit description document                     | 32       |

|   |            | 4.2.2 Hardware design using design for verification practices           | 32       |

|   |            | 4.2.3 Elaboration of a verification plan document                       | 33       |

|   |            | 4.2.4 UVM-based functional verification                                 | 33       |

| 5 | SHN        | IAC verification framework                                              | 35       |

|   | 5.1        | SHA1 core test                                                          | 36       |

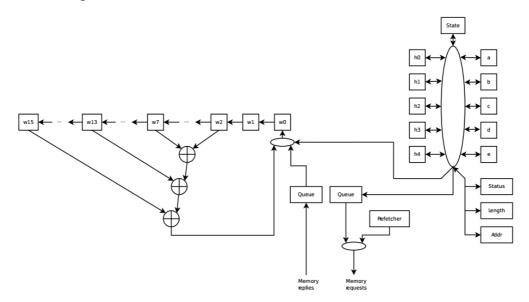

|   |            | 5.1.1 SHA1 SystemC reference model                                      | 37       |

|   |            | 5.1.2 SHA1 UVM-based verification environment                           | 38       |

|   | 5.2        | Router test                                                             | 42       |

|   |            | 5.2.1 Router single data transfer test                                  | 43       |

|   |            | 5.2.2 Router sequential data transfer test                              | 46       |

|   |            | 5.2.2 Router sequential data transfer test                              | 48       |

|   | 5.3        | SHA1 tile test                                                          | 50       |

|   | 5.5        | 5.3.1 SHA1 tile UVM-based verification environment                      | 51       |

|   | 5.4        | Top level test                                                          | 53       |

| ( |            | •                                                                       |          |

| 6 | Disc       | ussion/Evaluation                                                       | 57       |

| 7 |            | clusion and future work                                                 | 61       |

|   | 7.1        | Conclusion                                                              | 61       |

|   | 7.2        | Future work                                                             | 62       |

|   |            | 7.2.1 Attach the SHA1 SystemC reference model to the SHA1 verifica-     |          |

|   |            | tion environment                                                        | 62       |

| 7.2.2<br>7.2.3<br>7.2.4 | Create a SystemC router model             | 62<br>63 |

|-------------------------|-------------------------------------------|----------|

| Bibliography            |                                           | 6        |

| Appendix                |                                           | 6        |

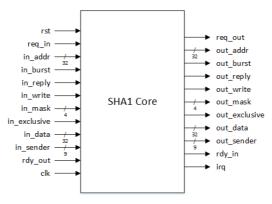

| Appendix A              | : SHA1 core circuit description           | 6        |

|                         | : SHA1 verification plan                  | 7        |

|                         | : Router circuit description              | 7        |

|                         | Router verification plan                  | 8        |

|                         | : Design for verification guidelines      | 8        |

|                         | : UVM coding guidelines                   | 8        |

|                         | : Survey conducted among SHMAC developers | 9        |

# List of Tables

| 1.1 | Requirements for the new verification framework of the SHMAC platform                   | 4  |

|-----|-----------------------------------------------------------------------------------------|----|

| 2.1 | SHMAC tiles                                                                             | 9  |

| 5.1 | Distribution of the bits of the SHA1 data signals                                       | 52 |

| 6.1 | Strategies implemented for meeting the requirements for the project listed in table 1.1 | 58 |

# List of Figures

| 1.1 | Historical growth in processor performance [27]                         | 2  |

|-----|-------------------------------------------------------------------------|----|

| 1.2 | ARM's big.LITTLE technology [40]                                        | 2  |

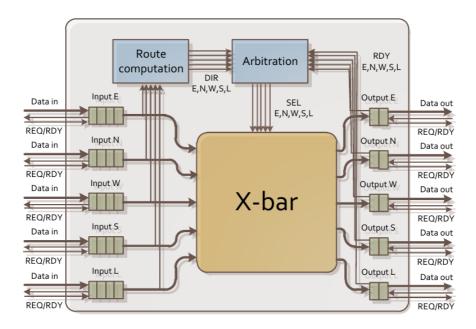

| 2.1 | Illustration of the high level architecture of the SHMAC processor [21] | 8  |

| 2.2 | Illustration of the increasing verification gap [13]                    | 9  |

| 2.3 | TLM blocking Transport [16]                                             | 14 |

| 2.4 | TLM non-blocking Transport [16]                                         | 15 |

| 2.5 | Development of methodologies [38]                                       | 18 |

| 2.6 | The organisation of the verification environment [18]                   | 19 |

| 2.7 | SystemC simulation kernel [8]                                           | 22 |

| 3.1 | Bus-based structure of IP standalone verification platform [41]         | 26 |

| 3.2 | AMBA APB UVM setup [26]                                                 | 29 |

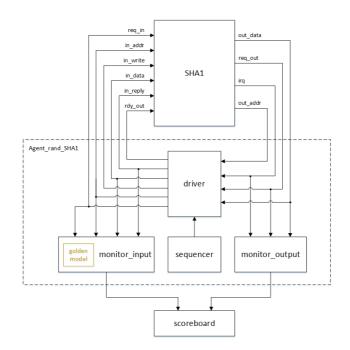

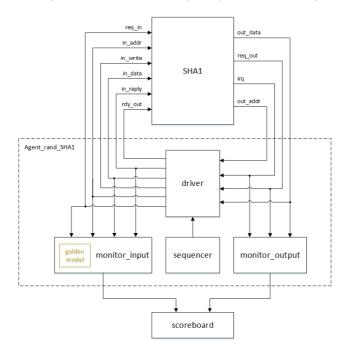

| 5.1 | Verification environment built for the SHA1 core                        | 39 |

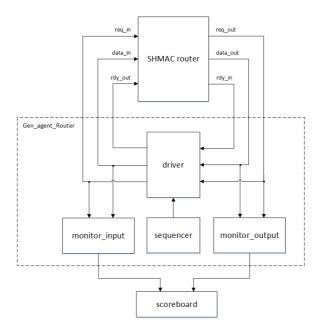

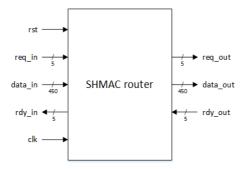

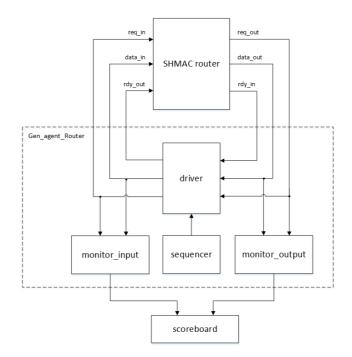

| 5.2 | Verification environment built for the SHMAC router                     | 43 |

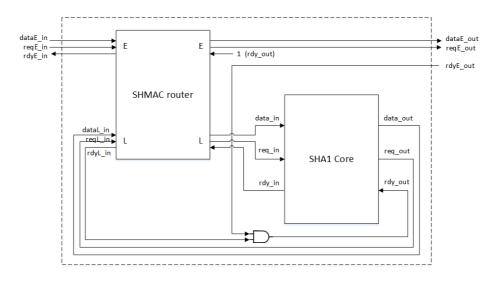

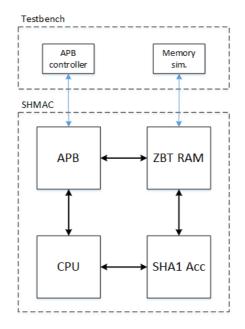

| 5.3 | Circuit which replicates the structure of a SHA1 tile                   | 51 |

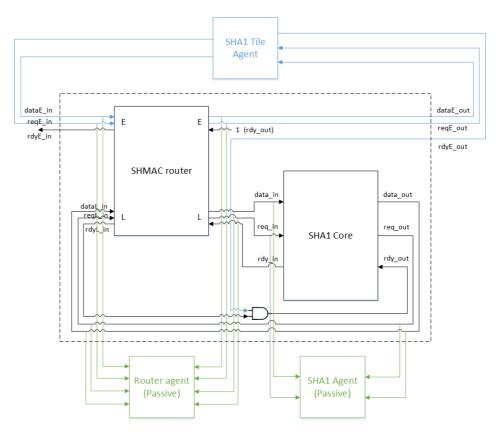

| 5.4 | Verification environment built for the SHA1 tile                        | 53 |

| 5.5 | Testbench built for the top level test                                  | 54 |

|     |                                                                         |    |

# Acronyms

| <b>VIP</b> = Verification IP |                       | Verification IP                             |

|------------------------------|-----------------------|---------------------------------------------|

| IP                           | Intellectual Property |                                             |

| SHMAC                        | =                     | Single-ISA Heterogeneous Many-core Computer |

| FPGA                         | =                     | Field-Programmable Gate Array               |

| UVM                          | =                     | Universal Verification Methodology          |

| EECS                         | =                     | Energy Efficient Computing Systems          |

| SoC                          | =                     | System on Chip                              |

| DUV                          | =                     | Device Under Verification                   |

| DUT                          | =                     | Device Under Test                           |

| HDL                          | =                     | Hardware Description Language               |

| HVL                          | =                     | Hardware Verification Language              |

| RTL                          | =                     | Register Transfer Level                     |

| VC                           | =                     | Verification Component                      |

| TLM                          | =                     | Transaction Level Modeling                  |

|                              |                       |                                             |

Chapter 1

# Introduction

## 1.1 Motivation

Computing system performance has grown at an impressive rate since the mid 1980s. Until the early 2000s, this increase in performance has followed Moore's law [35] with a growth of roughly 50% annually, as depicted in Figure 1.1. This was in part made possible because improvements in production technology adhered to the principle called Dennard scaling [15]. In a Dennard scaling process, transistor sizes are reduced while keeping the electric fields constant. This translates into a lower power consumption per transistor, which again was used to add more transistors to the same die area. The result is more transistors on a fixed chip area at a constant power consumption.

Dennard scaling keeps the electric fields constant by reducing the transistors supply voltage and threshold voltage. However, sub-threshold leakage currents increase exponentially when the threshold voltage is reduced, which has led to the end of Dennard scaling when production size decreased past the 130 nm level [30]. This means it is no longer possible to power more transistors without either increasing the power budget or leaving parts of the chip unpowered. The latter is associated with the concept of Dark Silicon Effect [24], which implies that only parts of a chip can be active simultaneously while others have to be powered off in order to stay within the power budget.

The Dark Silicon Effect is motivating the emergence of new fields of study, where different approaches for transistor utilization are explored. One such field is the area of heterogeneous processor design, where multicore processors are composed of cores that have different performance and power characteristics. The task at hand is to select the processing elements that will maximize performance for the current application under a fixed power budget (i.e. maximizing energy efficiency), while the remaining processing ele-

1978 1980 1982 1984 1986 1988 1990 1992 1994 1996 1998 2000 2002 2004 2006 2008 2010 2012

Figure 1.1: Historical growth in processor performance [27]

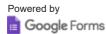

ments are powered off. ARM's big.LITTLE technology is an example of a heterogeneous computing architecture employed in the consumer market. It combines relatively slow, low-power processor cores (LITTLE) with relatively more powerful and power-hungry ones (big). Each processing task is dynamically allocated to a big or LITTLE core depending on the instantaneous performance requirement of that task, as shown in Figure 1.2, where A15 and A7 clusters are the big and LITTLE cores respectively.

Figure 1.2: ARM's big.LITTLE technology [40]

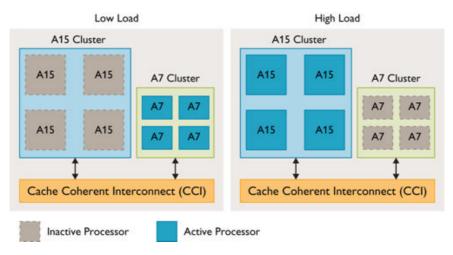

The EECS group at NTNU contributes to heterogeneous processors research with the Single-ISA Heterogeneous MAny-core Computer (SHMAC) project. SHMAC is an infrastructure for investigating heterogeneous systems at all abstraction levels. The key idea is to create a flexible framework in which different heterogeneous processors can be created from a collection of processing elements and accelerators. The SHMAC platform has a tile-based architecture, where processing elements are laid out in a rectangular grid with connections to their nearest neighbor. To facilitate software design space exploration, the programming model is kept constant across SHMAC-instances.

Functional verification is necessary to ensure the correctness of the SHMAC architecture. Current verification strategies for validating the functionality of the hardware parts of the SHMAC platform include block-level and top-level testbenches, and bare-metal testing on FPGA. The first ones run a set of tests on the SHMAC RTL, while the latter executes tests on a FPGA platform with a SHMAC bitfile. Both of them currently employ only predefined test cases, also referred as directed tests [29], which are hand-coded by each SHMAC developer. The main drawback of this approach is that each verification scenario has to be considered independently and human interaction is required to set up the complete verification environment, generating the necessary traffic and checking results for each test case. This represents a time-consuming and tedious task for the developer, and also often leads to verification incompleteness, since it requires detailed enumeration of all possible scenarios and corner cases.

Other deficiencies of the actual verification strategy for the SHMAC platform were identified by conducting a survey among SHMAC developers (see **Appendix G** for results). Some of them agreed that the existing Verilog testbenches and the framework for running bare-metal tests are not properly documented. Also, one of the main limitations they found was the absence of debugging mechanisms to effectively identify and analyze errors in the designs. This is particularly the weakest point of bare-metal tests since it is not possible to get access to the values of the internal nodes unless additional hardware is added. It was also confirmed that the limited error diagnosis capability is one of the major obstacles software developers of the SHMAC face, since it makes it difficult to distinguish between hardware and software bugs.

The current verification strategy has several limitations as described in the previous lines, and in order to be able to bring the current platform up to leading industrial quality standards as well as enable future upgrades and modifications to the platform to be quickly integrated and verified, a new verification strategy is needed. In addition to create an optimized verification environment, it is also important to provide guidance on how the SHMAC developers should implement the best verification practices. This includes the elaboration of templates for efficient design specifications documents and verification plans, as well as guidelines for implementing good design for verification practices.

This project is aimed at providing a new verification framework for the SHMAC platform which maximizes quality and reusability while reducing the effort and time spent on verification. This will be possible by employing the Universal Verification Methodology (UVM), which is a standardized methodology for verifying complex IP and SoC in the semiconductor industry. As UVM places an emphasis on reuse of the verification infrastructure, it will make it possible to save significant time in the verification process when new extensions or modifications are implemented on the SHMAC platform. The quality of verification will be ensured by providing guidelines for good verification practices to the SHMAC developers, as explained before.

## **1.2** Requirements for the project

Requirements are essential for systematically evaluating the success of the verification framework to be implemented. The following table presents the main requirements that the new verification framework must satisfy.

| Requirement ID | Description                                                                                                                                                                                                                                                             |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQ-Q1         | The verification strategy must clearly define which metrics<br>and level of those metrics that is needed in order to decide<br>when verification is complete. If different environments re-<br>quire different metrics to be collected, that must be clearly<br>stated. |

|                | Example metrics: raw line coverage for block level test-<br>benches must be higher than 95%. Explained (i.e. justified)<br>line coverage for block level testbenches must be 100%.                                                                                      |

| REQ-Q2         | The verification strategy must define the different types of<br>environments that should be implemented and high level fea-<br>tures of those environments such as stimuli generation strat-<br>egy and checking strategy.                                              |

| REQ-Q3         | The verification strategy must enable the user to do as effi-<br>cient debugging as possible.                                                                                                                                                                           |

| REQ-Q4         | The verification strategy must enable verification environ-<br>ments that are robust against future changes to the design<br>and that can easily be reused.                                                                                                             |

| REQ-Q5         | It must be easy to determine if the design has a HW bug.                                                                                                                                                                                                                |

| REQ-Q6         | Assuming a certain quality level has been achieved, the ver-<br>ification strategy must describe how the same level can be<br>maintained over time even if modifications to the RTL is on-<br>going.                                                                    |

| REQ-Q7         | The verification strategy must give guidance on how the team<br>should prioritize in order to get from the current state to the<br>new and improved way of doing verification.                                                                                          |

| REQ-Q8         | The full system contains both hardware and software. The verification strategy should also describe how hardware and software can be verified together.                                                                                                                 |

Table 1.1: Requirements for the new verification framework of the SHMAC platform

| REQ-Q9  | The verification strategy should also describe typical design<br>for verification guidelines that designers should follow when<br>writing RTL.                                                                                                      |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQ-Q10 | The verification strategy must list required documentation<br>needed before a verification engineer can efficiently start on<br>investigating how to e.g. verify a block. A outline of the<br>content of the necessary documents must be specified. |

| REQ-Q11 | The verification strategy must describe what document that<br>must be produced when architecting a new verification envi-<br>ronment and the content of those documents.                                                                            |

| REQ-Q12 | The verification strategy must describe how bugs will be managed and tracked.                                                                                                                                                                       |

# **1.3 Report structure**

The organization of this report into individual chapters is briefly described for the readers convenience:

**Chapter 2: Background** gives an overview of the SHMAC architecture, and explains key concepts regarding functional verification, UVM and SystemC.

**Chapter 3: Related work** describes the existing verification strategy for the SHMAC platform, as well as similar works regarding verification of complex processors and SoCs.

**Chapter 4: SHMAC verification methodology** includes an analysis of the limitations of the current verification strategy for the SHMAC, and presents a new verification methodology aimed at overcoming these deficiencies.

**Chapter 5: SHMAC verification framework** gives a description of the new UVM-based verification framework for the SHMAC, and explains how the verification environments were implemented.

**Chapter 6: Discussion/evaluation** presents an analysis of the contribution of this work to the continuous development of the SHMAC.

**Chapter 7: Conclusion and future work** provides concluding remarks and propositions for future work on this project.

Chapter 2

# Background

Parts of this chapter have been fully or partially reused from the project preceding this thesis, this is information of equal relevance to this dissertation [20].

## 2.1 SHMAC

The Single-ISA (Instruction Set Architecture) Heterogeneous MAny-core Computer is a research project by the Energy Efficient Computing Systems group at NTNU that tries to figure out how to make more energy efficient computers through a heterogeneous architecture [21]. The motivation for this comes as a result of the Dark Silicone effect.

The Dark silicon effect is a result of the fact that transistors are still shrinkable but the power consumption is not [24]. An increased amount of transistors per area and a fixed power per chip constraint, has resulted in that a lot of transistors has to be turned off during operation. Because of this a lot of alternative architectures has emerged. They rely on large-scale parallelism, heterogeneous cores, and accelerators to achieve performance and energy efficiency [9]. The challenge is to figure out which amount of smaller and bigger cores, with or without internal accelerators, and separate external accelerators that gives the largest performance increase on the smallest amount of power.

The architecture is a mesh of different tiles coupled together. The tiles have a common instruction set and architecture model, such that there is software portability across different SHMAC instances. There is a common router in all the SHMAC tiles that makes this possible. It is a uniform architecture, all processing tiles see the same memory map, but tile registers are per-tile, other memory locations are global. Every tile can be loaded with any type of logical unit. The tile communicates only with its neighbours, and the

Figure 2.1: Illustration of the high level architecture of the SHMAC processor [21]

mesh must be rectangular, but not necessarily square. Every SHMAC architecture must contain one and only one APB tile, and one and only one main memory tile [22]. The APB tile takes care of all the I/O in and out of the SHMAC mesh, and the memory tile, depending on the target FPGA it is emulated on, is either ZBT-RAM or DDR-RAM. In addition to these we also have processor tiles, scratchpad tiles, accelerator tiles and dummy tiles. The processor tiles are based around a modified RISCV sodor Z-scale core, but also includes a tile register block, a tile memory and glue logic to bind it all together. Additional internal accelerators are also possible to include on the processor tile. The cores can be implemented with a number of different energy/performance characteristics, and can be optimized with vector processing, Out-Of-Order (OOO) operation, Branch prediction, and etc. Cache sizes are also variable. The scratchpad tile is a RAM tile that provides extra memory to connected tiles. Accelerator tiles are external accelerators designed for a specific purpose, an example being an SHA1 core based on the SHA1 algorithm [22]. Dummy tiles are empty tiles, that only includes the router. These can be used in cases where it is impossible/impractical to have a functional tile, and is just used to create the rectangular shape of SHMAC. SHMAC tiles are summarized in table 2.1.

## 2.2 Verification

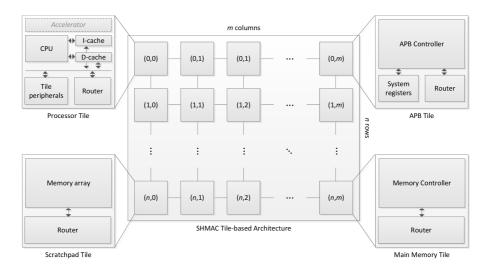

Since Moore's law was introduced in 1960 the amount of transistors on a chip has increased exponentially, and with it the complexity of the chip. With the increased complexity of today's processor designs, the time spent on verification has grown from 30-40% spent of the total effort in 1996 to 50-80% spent today [13]. This is illustrated in Figure

| Prefix | Tile type  | Amount allowed in the grid                     |

|--------|------------|------------------------------------------------|

| V      | I/O        | 1                                              |

| С      | CPU        | 0-9                                            |

| R      | Scratchpad | 0-8                                            |

| Ζ      | ZBT RAM    | 1, if synthesizing for the RealView PB11MPCore |

| D      | DDR RAM    | 1, if synthesizing for the Versatile Express   |

| S      | SHA1       | 0-8                                            |

| •      | Empty      | 0-9                                            |

Table 2.1: SHMAC tiles

2.2. As processor designs keep getting more and more complex, verification becomes a bigger and bigger part of the total effort spent on each design, and also the biggest delay in the time to market process.

Figure 2.2: Illustration of the increasing verification gap [13]

The process of verifying a design have evolved from simple directed testing to extensive verification libraries and methodologies. Directed tests are fast and easy to write for small designs but a thorough verification requires more detailed systems. UVM which is used for verification in this thesis, is a combination of different methodologies mostly based on SystemVerilog [38] and e [38].

Verification is a process used to make sure that a design does what it is specified to do. A test to an extent that it gives confidence in the correctness of the design. It is an observation of design response based on input stimuli that ideally reaches all possible states in a design. Most designs today are too large and too complex that to completely verify them, reach all possible states and to try all possible combinations, would take such a large amount of time, that it is practically impossible. That is why verification is normally done through simulation of either a behavioral model or a specific state/value of the design at a given time.

## 2.2.1 Directed test

Directed tests are simple tests, written from scratch, that directly targets expected signal transitions and requires little overhead. It is an efficient way of writing basic tests for

small designs, but becomes tedious and completely impossible to do for large designs. Tests derived from a black box test specification has been shown by experience to be insufficient to reach structural coverage targets [6]. Certain bugs in a system can be very hard to imagine for a human mind, and added to this is the lack of ability for directed tests to be reused to a larger degree. This calls for better and more efficient methods for verification.

## 2.2.2 Static Verification

Static verification, also known as formal verification/analysis, is a mathematical proof of a device under verification (DUV) [28]. A property to be studied is represented as a mathematical model, where a calculus is used to perform computations on the model [10].

It is normal to describe a circuit as a functional unit and compute its outputs based on its inputs and internal states, while avoiding timing constraints and the circuits electrical behavior. The calculus must prove or disprove the existence of a relation between the abstract models of the circuit specification and its implementation. Formal verification can therefore only ascertain the logic correctness of a circuit. It is independent of technological choices and cannot verify the design at a physical level. Model checking is the most common form of formal verification. It represents the DUV as a finite state machine where all sets of specified properties are mathematically proven for all input combinations, and across all execution paths.

Formal verification is heavily reliant on logic as a tool. That includes first-order predicates, higher order predicates and temporal logic. First-order predicates takes only individual constants/variables as arguments, memory elements and interconnection wires is described as time functions, gates is described as logical connectives. Higher order predicates have additional quantifiers and stronger semantics compared to the first-order predicates. Inputs and outputs are modeled as parameters, interconnection of components results from the conjunction of the predicates of the components, and wires are modeled as quantified variables in each predicate. What gives the logic a higher order is that functions and predicates can be arguments and results of other functions and predicates. Temporal logic is defined as a system which contains both linear and branching operators [7]. It is used to reason and represent propositions that are fitting in regards to time.

## 2.2.3 Dynamic Verification

Dynamic verification is verification done at the same time as test code is executed on the DUV. A model of the DUV has to be executed with applied input stimuli, compared to a specified behaviour, and flagged for differences [28]. Dynamic verification consists of three elements, stimulus generation, coverage measurements and analysis, and response checking.

#### **Stimulus generation**

Stimulus generation is to create and apply input patterns that fully exercise the DUV, with legal and useful stimulus.

- Legal stimuli, a particular data/temporal pattern that is not prohibited by the specification.

- Useful stimuli, a pattern that improves verification coverage, exercises corner cases and find bugs.

There are three common stimulus generation techniques:

- 1. Manual directed tests, a handwritten program that stimulates the DUV and checks its response.

- 2. Verification environments, application specific program that implements stimulus generation, response checking and coverage measurements in the same program.

- 3. Random test generators, tests of random functionality or behavior on the DUV to test for hidden holes in the verification coverage.

#### Coverage measurements and analysis

Coverage measurement is formally defined as how thoroughly a design has been exercised during verification [28]. Its primary coverage is code coverage, including integral coverage, and functional coverage, usually designed for and applied to both the specification and the implementation. The coverage measurement can be divided into two tasks:

- 1. Identification of DUV features

- 2. Coverage model that quantifies the behavioral space it has.

#### **Response checking**

Response checking is to apply stimulus to a DUV and then compare its response to its specified behavior [28].

- 1. Scoreboard, data structure that records expected DUV output and compares it to the observed response from the DUV after it responds to a particular stimulus.

- 2. Reference model, a program that reflects intended DUV behavior at a chosen abstraction level, providing portals or hooks to observe intended behavior.

3. Assertions, a statement containing a Boolean and/or temporal expression describing a liveness or safety property. A liveness property states something must eventually happen, while a safety property states that something must never happen.

### 2.2.4 Electronic System-Level Design

Electronic System-Level (ESL) Design is the use of a higher level of abstraction to solve the problem with the increasing design complexity in modern chip design[8]. This is to reduce development cost by creating a virtual system prototype that enables earlier development of software. The result of this is that it eases the communication between different design groups when they try to figure out the best trade off between hardware and software in terms of energy and performance.

## 2.2.5 Transaction-Level-Modeling

Transaction-Level-Modeling (TLM) is a technique to enable communication between blocks of different abstraction levels, [8]. It makes ESL models practical, as all important information that needs to be transferred in one turn is transferred as one single event or transaction. This opens up the possibility to refine interface blocks or communication blocks independently from the boxes they connect together. And makes for earlier development of software and an earlier and better functional verification of hardware. TLM use cases are architecture and algorithmic modeling, virtual software development platforms, and as reference models for functional verification.

#### **Architecture Modeling**

Architecture Modeling is concerned with the partitioning of hardware and software. It is to balance out which type of bus that is needed, how fast it needs to be and what kind of arbitration scheme that is sufficient, when estimating the size and cost compared to the goals of the model.

#### Algorithmic modeling

Algorithmic modeling is to figure out how to best implement application specific algorithms, whether in hardware and software or just software, and how precise the arithmetic calculations must be, to still have a functional algorithm. TLM is very useful here as it is easier to do refinements in software for an algorithm, than to debug it in RTL. In case parts of it is implemented in hardware the algorithm has to be refined from floating point to fixed point.

#### Virtual Software Development Platform

By using ESL and TLM software models a platform can be made to enable early development of system software. During which it can be examined if the hardware have the correct features, if the current architecture have enough control and status register, or if it enables the software to meet its timing budget.

#### **Functional Verification**

Since TLM enables communication at different levels of abstraction, TLM models can be fully or partly reused in functional verification of the RTL in question. This is very useful as the use of constrained random test stimuli generation requires the development of reference models in order to check the results of the randomized inputs.

#### Timing

There is three types of timing a TLM model can have, loosely timed, approximately timed, and un-timed [34]. Loosely timed models have a loose dependency between timing and data. Timing information and requested data is provided when a transaction is initiated. The loosely models are independent of time advancement to produce a response, but this also makes it possible to make them really fast. This makes them extremely useful for software development on virtual Platforms. Approximately timed models have a strong dependency between timing and data, and can depend on internal or external events getting invoked and/or time advancement to produce a response. Synchronizing transactions in correct order before processing is necessary to these models, and they also need to trigger simulations switches, which in turn results in worse performance for these models. Un-timed models are relics from TLM 1.0 and have been deprecated in TLM 2.0. It is possible to make untimed models in TLM 2.0 by using the constant SC\_ZERO\_TIME which represents 0 time, and is the equivalent of a delta-cycle.

#### Sockets

Sockets are used to connect paths going forward or backward between an initiator and a target [33]. Sockets supports both blocking and non-blocking transport, usually only one of them are used for one connection. They offer a very convenient way to make TLM2.0 connections. Default transaction type is tlm\_generic\_payload using the TLM base protocol semantics. The initiator socket is made to be used with an initiator to drive a target through the target socket [33]. The initiator must either implement a backward interface or use a simple initiator socket. The target socket is made to be used with a target to receive a transaction from an initiator [33]. The target must either implement a forward interface or

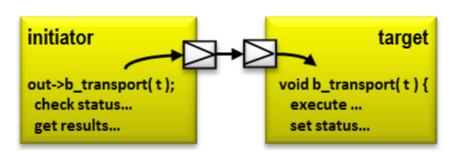

Figure 2.3: TLM blocking Transport [16]

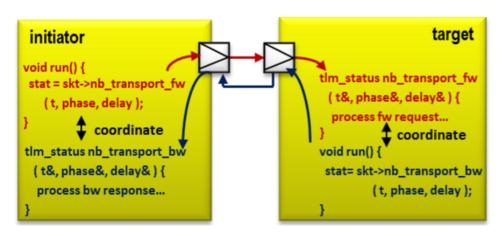

use a simple target socket where only the methods registered with the socket needs to be implemented. This is illustrated in figure 2.3 and figure 2.4.

#### Blocking and non-blocking transport

There are several interface methods used to pass transactions in TLM2.0, the most important ones being the blocking and the non-blocking interfaces [14]. They are designed to be used together with the generic payload, but can be used separately to model specific protocols [4].

The blocking interface is implemented with one method for targets, b\_transport(transaction , timeoffset), and is usually accompanied by the loosely timed coding style [14]. This method can call the SystemC wait function, which responds to time or an event. The time offset parameter will indicate when a transaction is valid in comparison to the current simulation time, when passed from initiator to target. The blocking transport methods pass a non-const reference to the transaction object and a timing annotation [4].

The non-blocking interface is implemented with two interfaces tlm\_fw\_nonblocking\_transport\_if and tlm\_bw\_nonblocking\_transport\_if, where one is used as a forward path from initiator to target and the other one as a backward path from the target to the initiator [4]. The approximately-timed coding style is what the non-blocking transport interface is intended for. This interface is suited to model detailed interaction sequences between initiator and target during each transaction. The non-blocking transport methods also pass a non-const reference to the transaction object and a timing annotation, but it also passes a phase to indicate the state of the transaction, and returns an enumeration value to indicate if the return from the function also represents a phase transition. Non-blocking transport also supports multiple phases within the lifetime of a transaction. Figure 2.3 shows a blocking interface and figure 2.4 shows a non-blocking interface.

Figure 2.4: TLM non-blocking Transport [16]

### **TLM Generic payload**

TLM2.0 has a standard transaction class, tlm\_generic\_payload with several attributes; command, address, data, data\_length, response\_status, byte\_enable and byte\_enable\_length [14] [33]. Command can be either a read, write or an ignore. Address is a base address, a reference point for other memory locations or addresses. Data is a data buffer, organized as an array of bytes. Data\_length specifies the number of valid byte-enables in the buffer. In TLM2.0 there is also a base protocol for execution of generic payloads over standard initiator and target sockets. The Generic payload is the default transaction in TLM2.0 for blocking and non-blocking transactions, it represents a generic read or write access to a bus.

## 2.2.6 SystemVerilog

SystemVerilog is a combination of a hardware description language and a hardware verification language. It is based on Verilog and the advanced verification features found in OpenVera [38]. SystemVerilog have four distinct language subsets; it is an object oriented language for functional verification libraries like UVM or OVM, a design language, an assertion language and a functional coverage language to assertion that a verification environment or a testbench have fully exerted and verified a design [32]. Because of this SystemVerilog spans a large range of domains. Netlists and RTL are covered by the design language subset, general programming is covered by the object oriented features, functional coverage is covered by its respected subset, testbenches are covered by all the subsets except the design subset, temporal properties are covered by the assertion language subset.

Systemverilog was created as a response to the need for a common, open verification lan-

guage [39]. Verification languages like OpenVera[38] and e[38] already existed but they were closed and cost money. A lot of companies did not want to pay for verification tools, so they used a lot of time to create their own. As the design outgrew the verification capabilities of Verilog, a productivity crisis emerged and resulted in the creation of Accellera [1]. Which in turn created SystemVerilog, and also later UVM.

SystemVerilog comes with a large range of different verification features; new data types, classes, constrained random generation, assertions and synchronization.

- New data types: All Verilog data types are included in SystemVerilog but new data types have also been added [39]. Verilog-1995 has two basic 4-state data types: variables and nets. These can be single or multi-bit, signed and unsigned, or floating point numbers. They can also be grouped into fixed size arrays. Systemverilog adds the logic type as an improvement over the old Verilog *reg* data type. The logic data type is a variable but can also be driven by continuous assignments, gates, and modules. It can be used anywhere a net is used except for modeling of bidirectional buses. For improved simulation performance and reduces memory usage, 2-state variables is added. The unsigned bit type, and four signed types, byte, shortint, int and longint. Systemverilog also introduces compact declaration of fixed-size arrays, array initialization using an array literal, dynamic arrays, and associative arrays, all with added array operations and methods. Lastly enumerate, strings, and queue data types are added, streaming operators, type conversion, type defining, structures and unions are included. All arrays and structures can be either packed or unpacked.

- Classes: To ease control and increase reusability in the verification environment, Systemverilog introduces classes. The classes organize functionality and support a single inheritance model. This is what qualifies System Verilog as an object-oriented program.

- Constraint-random: To remove the human fault factor and reach unthinkable states in a design being verfied, Systemverilog includes randomized input variables. These can be constrained by constraints. Constraints are used to exclude illegal values or to test specific parts. They can also be turned off to verify proper error handling of faulty input.

- Communication: Interfaces and modports are used to communicate between the RTL netlist and classes. I/O connections are bundled by the interface, this allows direct access through different levels of the hierarchy, and by that reduce the common issue of spaghetti code. Interfaces can also implement necessary functionality for bus transfer protocols to make bus communication more efficient. This is also the basis for Transaction Level Modeling (TLM).

- Synchronization: *Mailboxes* and *semaphores* are used to synchronize threaded TLM and the RTL signals so that they can be used together. Mailboxes are used for messaging and semaphores are used to control execution order and access to resources.

- Assertions: Methods for checking temporal and functional properties in a design.

The methods can be placed several places in the code for immediate or delayed checking of properties. Assertions are a good way to target specific behavior, by separately describing expected transitions or results for properties one want to verify. A part of SystemVerilog, SystemVerilog Assertions (SVA), is a standardized assertion language that provides a well defined system for assertions.

• Functional Coverage: Coverpoints and covergroups are used to easier track the progress and monitor what exactly has been tested. For random variables this is very important as it shows which functional parts of the design that has been exerted by the input and which parts that must be tested more thoroughly.

## 2.2.7 Verification Methodologies

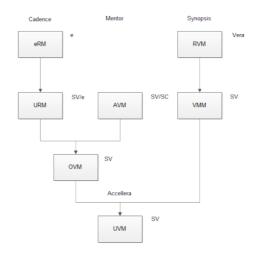

The first verification methodologies where based on different languages and created by different vendors to help increase their productivity in verifying designs. They where class based, focused on reusability, and only let the user modify tiny parts of the code. It all started with e Reuse Methodology (eRM), based on e, from Versity Design [38]. Cadence combined it with SystemVerilog and created Unified Reuse Methodology (URM). Synopsis created the Reference Verification Methodology (RVM), based on OpenVera, around the same time as eRM was created. This later became Verification Methodology Manual (VMM), now with OpenVera as a base for SystemVerilog verification. At the same time as URM and VMM was created, Mentor created the Advanced Verification Methodology (AVM) based on a combination of SystemC and SystemVerilog. URM and AVM where later combined into the Open Verification Methodology (OVM), now only with SystemVerilog. This later became combined with VMM to form the Universal Verification Methodology (UVM), which is the standard used today. This is illustrated in figure 2.5.

## 2.3 UVM

UVM is a common practice for verification which relies on reusing and combining unitlevel environments and then running real software on an SoC [19]. It provides a SystemVerilog base class library (BCL) and guidelines which supports the construction and deployment of verification components (VCs) and testbenches that dramatically reduces users coding effort and automatically enforces certain aspects of interoperability [12] [42].

Key concepts of the UVM [12]:

- A simple class hierarchy, rooted in UVM\_object, that makes it possible to implement key services.

- Components and data, the two distinct categories for classes in the UVM. Compo-

Figure 2.5: Development of methodologies [38]

nents are intended to model permanent, structural parts of a testbench (monitors and drivers). Data are intended to model stimulus, observed transactions, and other data flowing around the testbench.

- An object factory, that automatically creates objects based on either user specification or default settings based on the used classes or derived classes.

- A configuration or resource database, which is a structure that allow configuration values of any data type, including userdefined types, to be stored in a globally accessible table and later retrieved using a string name key.

- Interconnection of components, a SystemVerilog implementation of transactionlevel modelling (TLM), which allows VCs to be written to pass data through TLM ports and exports, without regard for the details of other VCs that may be connected to them.

- Sequences for stimulus generation, activity that is coordinated in sequence of random stimuli, both on individual ports and across multiple ports of the DUV. A lot of transactions are built upon the constrain-random functionality enabled by System Verilog.

- Automated code generation using macros, or routine coding tasks automated using macros.

- 1. Macros for factory registration, constructs a singleton instance of every object wrapper class, and can use these instances to create instances of user classes on demand.

2. Macros to automate the creation of utility methods, automatically creates utility methods for each derived UVM class created.

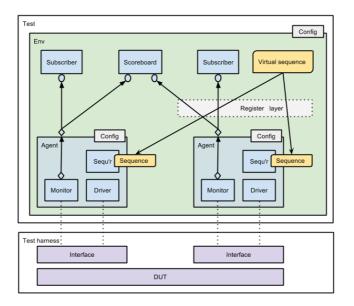

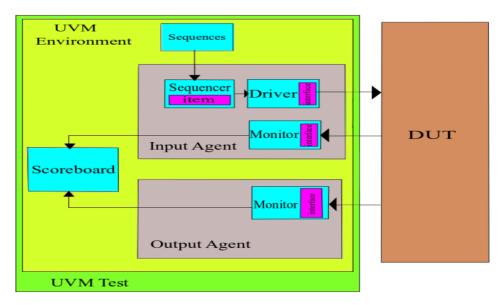

A typical UVM structure starts at a top level test, containing an environment. Inside the environment there are subscribers, agents, a scoreboard, and a virtual sequencer. The agents contains monitors, drivers and sequencers. Monitors and drivers connect to the DUT through interfaces, and the environment and agents can be configured by configurations. This is described in figure 2.6.

Figure 2.6: The organisation of the verification environment [18]

- Tests are top level components that control generation. This means that they can set the contents of configurations, override components, transactions and sequences by extending them, and start sequencers in specific components [5].

- Environments and agents are simply composed by their contained components.

- A subscriber is just a component with a built in analysis export [5].

- Monitors are components that can observe the communication between the DUT and a testbench, and send transactions to the verification environment [5].

- A sequencer is a component that runs sequences and sends transactions generated by those sequences to another sequencer or driver [5].

- A driver is a component that receives transactions from a sequencers and forwards this to a DUT through its interface [5].

## 2.4 SystemC Modeling

To make ESI models and TLM possible, SystemC has arisen as a perfect candidate. SystemC is a C++ class library, where the C++ language contains the ability to model software, and SystemC completes this ability by enabling modeling of hardware[8]. Together they are perfect to make ESL models. Many algorithms and applications are already implemented in C++ or in C and by wrapping them in a suitable SystemC wrapper, it can be a good ESI model. SystemC is an IEEE 1666 standard, which means that it is open to the industry and therefore have certain benefits, like access to commercial and freeware based tools, and support. Since SystemC is based on C++ it is fast enough to be used for early software development, but by using ESL models in SystemC, that part can be started sooner, which can make a design process more efficient, as software development can be finished faster. SystemC has a simulation kernel which supports parallel/concurrent executing, this is important since hardware runs concurrently. TLM gives SystemC the ability to communicate with other languages like SystemVerilog, and that also enables SystemC modules to be used as reference models in a SystemVerilog test-suit.

## 2.4.1 Class concept for hardware

SystemC have certain hardware-constructs that are required to model hardware in an environment mainly used for software development. The constructs are all implemented in C++, and enables concepts of time, hardware data types, hierarchy and structure, communications, and concurrency.

#### **Time Model**

SystemC uses the class sc\_time to obtain current time and to implement delays. The class has a 64bit resolution. It contains an enumerated type that defines natural time units like seconds, nanoseconds and the like. There is also a class called sc\_clock for models that require clocks.

#### Hardware data types

Hardware requires more flexibility in data types width than C++ has native, so SystemC has support for data types with explicit bit width for integral and fixed-point quantities. Both binary and non-binary representations, like tri-state and unknown, is supported.

#### Hierarchy and structure

To create a hierarchy SystemC uses module entities connected to other modules through channels. Module classes can be instantiated within other modules.

#### **Communications management**

The SystemC channel can represent both simple communication like wires or FIFOs and complex communication schemes to map to special hardware. The different channel implementations can be used interchangeably. The library has common software and hardware channels, like FIFOs, signals, mutex and semaphores, built in to it. Port classes are used to connect modules to other modules or channels.

#### **Concurrency model**

There is no true concurrency in hardware simulation, but single units execute until simulations of other units are required to continue with correct alignment in time. To determine this in the simulation code, events are used as switches. The simulator swaps between concurrent elements.

## 2.4.2 Simulation Kernel

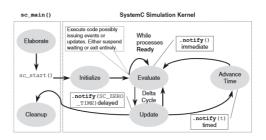

The SystemC Simulation Kernel has three phases, elaboration, execution, and post-processing or cleanup. Elaboration is where data structs are initiated, connections are established, and anything else needed to prepare for the next phase, execution. This is all the statements before the sc\_start() functions is called. In the execution phase the simulation kernel controls the execution of processes so that they appear to be concurrent. Figure 2.7 shows an overview of the simulation kernel. First the elaboration process, then sc\_start() is invoked and all simulation processes, minus a few exceptions, are initialized in an unspecified deterministic order. Then code will be continuously evaluated for events or updates while also advancing the simulation time when no processes needs to be evaluated. When there is no more processes to run, the simulation ends, and a cleanup is invoked.

## 2.4.3 Threads and Methods

Simulation processes in SystemC are member functions of sc\_module classes, registered with the simulation kernel, and the kernel is the only caller of these functions. Theses functions have no arguments and no return value. Other processes, that are not executed by the simulation kernel, are invoked as function calls within the simulation processes

Figure 2.7: SystemC simulation kernel [8]

of the sc\_module class, like C++ functions or class methods. There are three types of simulation processes SC\_METHOD, SC\_THREAD, and SC\_CTHREAD. SC\_METHOD is a timeless function with no arguments, no return value, and can be repeatedly be called by the simulation kernel. It is basically a C++ function. An SC\_THREAD can only be invoked once, but can self suspend and allow potential time to pass before continuing, similar to the execution of a software thread. SC\_CTHREAD is similar to a SC\_THREAD but is required to be clock sensitive.

### 2.4.4 Events, Sensitivity and Notifications

Events are caused by the event class member function, notify, and invokes SC\_METHODs and SC\_THREADs that are sensitive to the event. They are implemented as sc\_event and sc\_event\_queue SystemC classes. Sensitivity in SystemC is either static or dynamic. Dynamic sensitivity can change the simulation sensitivity during a process, while static can not. An SC\_METHOD or SC\_THREAD can switch between dynamic and static sensitivity during simulation.

### 2.4.5 Channels and interfaces

SystemC processes communicate using channels, events or through module boundaries. Modules connect through ports, and interconnects through channels. Certain channels and interfaces are finished implemented in SystemC. Worth mentioning is sc\_mutex, sc\_semaphore, sc\_fifo, and sc\_signal.

## 2.4.6 Modules and Hierarchy

SystemC separates interface and implementation, C++ header files(.h) are used for entities and C++ implementation files(.cpp) are used for architecture. Design components are represented as modules, which are classes inheriting from the sc\_module base class. Modules can contain other modules, channels, processes and ports.

## 2.4.7 Data types: Logic, Integers, Fixed point

SystemC supports all C++ data types, but also include support for non-binary hardware types as four-state logic (0,1,X,Z), and lets you define new data types. All the new data types have a large operator overload so they can be used almost as easily as C++ data types. Conversion from hardware to hardware or hardware to software data types, and all other necessary methods to use hardware data types, are provided in SystemC.

## 2.5 UVMC

UVM connect (UVMC) is a UVM open-source library made by Mentor Graphics [23]. It provides TLM1.0 and TLM2.0 connectivity to pass objects between SystemC and SystemVerilog models and components. A UVM Command API is also provided for access and control of the UVM simulation from SystemC.

### 2.5.1 Enabling IP and VIP reuse

UVMC enables use of SystemC models as reference models in UVM, or reuse of stimulus generation agents in SystemVerilog for verification of SystemC Modules [23]. This in turn enables more VIPs/IPs to be used, and leverage different strengths in each language. Through the UVM Command API, SystemVerilog UVM can be accessed from SystemC.

### 2.5.2 Key features

UVMC simplifies the connection between the languages by supporting standard UVM, not requiring models or transactions to inherit from a base class, supporting existing TLM models in both languages without modification, and therefore allowing independent models to be reused as they can communicate without being directly referred to each other [23].

### 2.5.3 Making UVMC Connections

To make cross language TLM connections, UVMC provides connect and connect\_hier functions [23]. In SystemVerilog TLM2.0 they are written like

uvmc\_tlm#(trans)::connect\_hier(port\_handle, "lookup"), and in SystemC TLM2 like uvmc\_connect/uvmc\_connect\_hier(port\_ref, "lookup"). Trans is only used for SystemVerilog to specify the unidirectional TLM transaction type. The port\_handle/ref is a handle or reference to the interface, port, export, imp or socket instance to be connected.

The lookup is an optional string used for matching ports together no matter the language used. When the string matches for two ports, those ports are being connected not dependent on if the components are of the same language or a different language.

### 2.5.4 Transaction Conversion

TLM generic payload is supported by UVMC, but if a different object is transferred a converter is required. UVMC use separate converter classes to pack and unpack transactions, which in turn allows converters to be defined independently from the transactions they operate on. UVMC defines default converter implementations that use the standard methodology for each language.

## 2.6 Questasim

Questasim is a simulator that has native support for SystemVerilog Testbenches, UPF, UCIS, OVM/UVM, and SystemC [25]. It includes mixed-language capabilities, advanced debugging capabilities, and a single simulation kernel that supports all standard verification languages.

# Related work

In the last couple of years there has been done much work in regards to verification of SoCs and heterogeneous systems. A summary of them will be presented here. Parts of this chapter have been fully or partially reused from the project preceding this thesis, since this is information of equal relevance to the dissertation [20].

# 3.1 Previous works in regards to verification of complex heterogeneous systems and SoCs

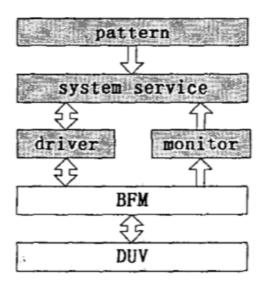

Institute of VLSI Design, Hefi University Of Tech, released a paper in 2004 about "Reuse Issues in SoC Verification Platform [41]" where they discuss the issues when reusing IP verification components on a SoC. There are two things to consider when verifying a SoC. Interconnections of IPs where focus is on behaviour in comparison with SoC specification, and unexpected interactions between IPs where focus is on chip integration. In the verification of a single IP, bus function models(BFMs) are used as high level models in replacement of real buses. The BFMs can be reused on other IPs with the same bus as it was originally intended for, but it can also be used on other buses with small modifications. In a SoC the BFMs are replaced by real buses. Monitors are used to transform events at pin-level into transactions, which are high-level abstractions that eases reuse and increases verification productivity. Monitors should be independent and not rely on input from other monitors. This to ease the reuse of the monitors. The monitors can be completely reused from IP to SoC verification as they are based on the same buses. But if they are reused, they should keep the internal signals used when testing in the synthesis process. Drivers are used to transform transactions to pin-level signals. If the driver is used as a peripheral module it can not be reused in SoC verification, but if it is connected to external pins, it can. Simulation patterns is a connection between the input signals to the IP and the system service. The system service contains system tasks, verification scripts, tools, and such. As long as the system tools is kept fairly similar from IP to SoC verification, the simulation patterns can be reused as stimuli, but may have to be modified. The strategy is to make the IP verification platform as similar to the SoC verification platform, so that reuse is fairly simple. Figure 3.1 presents the structure for verification of a single IP based on buses.

Figure 3.1: Bus-based structure of IP standalone verification platform [41]

The telecommunications laboratory at the National Technical University of Athens released a paper in 2003, "Verification of a complex SoC; the PRO<sup>3</sup> case-study [3]" where they presents some aspects, in the architecture design, used to support the observability and verifiability of a system. Minimization of the data paths is an important aspect as long data flows are time consuming, hard to observe, and poses a difficulty in identifying a source of error in case of failure. Shared packet buses are another important aspect to consider. In a shared packet all control information related to the SoC, such as destination, source, message type, and command, is integrated in the packet header. Shared interconnect structures eases observability since all data is transferred on the same bus. Lastly an embedded hardware block for monitoring a shared bus enables the ability to control and observe. Also described is a verification procedure where designers are told to write down detailed specification documents from the design specification. A verification is done on the documents to avoid misunderstandings and interface mismatches. Sophisticated test benches are used on the block level, and generic, intuitive test benches are used on the external level. In between these, a hierarchical verification is used on the integration of one block with other blocks, including all the interfaces and interconnects related to the blocks.

# 3.2 Industry verification approaches

In 2002 Guy Mosensoson from Verisity Design, Inc released a paper on "Practical Approaches to SoC Verification [36]" where he presents methods to approach SoC verification and the challenges in relation to this. He mentions the importance of reuse of verification IP/components to get fast, minimal effort, automation in the verification of an entire system. Good tools to ease the verification of the separate components is also of great importance. A verification component should be present for each component/unit in an SoC.

The unit verification component should check for internal blockers and provide stand alone coverage metrics, as these are useful for the full system verification. The old test plans for SoC where multiple sets of directed tests. These are very inefficient and inaccurate. To improve this, flexible and easily modifiable generic tests are used as a replacement.

Another thing to consider when verifying a SoC is the HW/SW co verification. This because of unexpected HW/SW sequencing bugs, HW/SW dependencies, and general increase in design time when doing verification of each part in sequence. To do this, real software is run on simulated HW. The simulated HW works as high level references, verification shadows, that the designed HW can be compared against when doing verification. Integration between components is one of the biggest challenges in verification of a SoC, blocks that where assumed verified show up with bugs, conflicts happen when accessing shared resources like memory, arbitration problems and deadlocks on the bus appears, and priority conflicts happens when exception handling is performed. To handle this the verification environment must focus on high level transactions, and be able to verify components in parallel streams, and check their transactions if they are on the same bus. Other things the paper mentions that a verification environment should have are high level abstract descriptions of every component that has to be verified and self checking of these. Also, changes done in the SoC when verifying should be done in the verification environment and should by that avoid changes in the tests.

A paper released in 2003 by Yves Mathys and Andr Chtelain on "Verification Strategy for Integration 3G Baseband SoC [31]" they mention the importance of verification on different levels when verifying a SoC. They use a top-down, bottom-up approach where they verify in different levels. At the IP level they focus on the functionality of a single IP, and use application stimulus to ensure correct behaviour in comparison with the system specification. At the RTL level SystemC models describing the system are used as reference to compare with. At the SoC level the platform integration for components are verified on all kinds of buses and connections. Worth mentioning are signals connectivity, memory mapping, data paths, DMA, interrupts and inter-process communication, as these are the most used connections and buses.

A practical and efficient SoC verification flow by reusing not only the IPs test bench but also the IPs test case, is presented in the paper "Practical and Efficient SoC Verification Flow by Reusing IP Testcase and Testbench [43]" written by researchers from Connec-

tivity Solutions. Because of this added reuse SoC verification and debugging becomes less complex and less difficult. This in turn increases verification throughput using less resources. The flow consists of two protocols interfaces, IF\_A connected to top chip pads and IF\_B, communicating between IPs inside the SoC. Also included in the flow is a System Control Interface, IF\_C, that consists of control signals. When either IF\_B or IF\_A is initiated a complementary verification IP (VIP), is created in the UVM testbench. VIP is a configurable verification component that is encapsulated and follows a consistent architecture for stimulus generation, coverage collection and protocol checking. For IF\_C a testcase or testbench is sufficient to generate stimuli for control signals. As long as IP testbenches and testcases are all designed for reuse, they can fully or partly be reused for the SoC testbenches and testcases. Reuse has to be planned for by both IP engineers and SoC engineers, but this collaborative work makes it easier to determine if an error is in the SoC design or the IP design. It also allows IP and SoC engineers to work in their specialized field without having to worry about details outside of their respective fields. There are three different ways to reuse verification component and test case files from IP level to SoC. The first one is in regards to IF\_A, where VIP and test files for the IP can be reused, without modification, for the protocol interface connected to the chip pads. Second, the IF\_B VIP have to be configured from Active to Passive mode to be reused in the testbench. This is due to the fact that the bus it was normally driving for one IP is now driven by another IP. It does however require a new SoC testcase, as the testcase for the IP is disabled in Passive mode. in the third case IF\_C is either controlled by the SoC and it's test case is used to drive the interface. Or it is controlled by another IP and it's VIP and testcase is reused to drive the interface, or it is connected to the top chip pads and the SoC testbench is used to drive and generate stimuli.

# 3.3 ARM verification

Verification libraries with common test codes, used in base functions to test building blocks in the DUV, are highlighted in "Verification Methodology of Heterogeneous DSP+ARM Multicore processors for Multicore System on Chip [11]" as it is the primary method for test development described in the UVM design test flow. Because test generators will pull a specific test code directly from the library, if needed in an individual test case, copies of a specific test code are prevented to appear in the test directory. In other words, the use of libraries ensures that there is only one copy of a test code. Automatic test generators can generate new test cases from existing test code and by doing this changes or modifications done to the existing test code will propagate to the new cases and update these. It works like a inheritance system where changes done to any test code used by other test cases will be present in all cases. This gives a reduced code effort. Elements from the library are used for test cases performed on the DUV, and consists of manipulators that causes a certain state to exists in a target, and checkers which either checks if data exists in a memory location, if data matches a specific pattern, or a sequence of patterns that can give proof of an event. The combination of manipulators and checkers are used for complex interactions. Test cases are classified in a library structure divided firstly into sub modules

and secondly into operation so that similar tests are kept in the same directory. Some classifications are, Smoke which are tests that give a basic indication of a working DUT, Functional which are tests which perform functional coverage, Performance which are tests to show the capabilities of the DUV for specific operations relevant to the DUV, Benchmarks which are test to generate standardized performance metrics, does not give any design coverage. Other things highlighted is that many test at unit level reduces the amount of tests at device level. This increases performance and speed of tests and reduces verification time. Also if several blocks are equal only one needs to be thoroughly verified, as this enhances simulation performance.

An example of an ARM Advanced Microcontroller Bus Architecture (AMBA) Advanced Peripheral Bus (APB), being verified using UVM is described in the journal "Design and Verification of AMBA APB Protocol" by Shankar, Dipti Girdhar and Neeraj Kr. Shukla at the ITM University, Gurgaon, India [26]. Here we can see the a standard UVM setup being used, with test, environment, scoreboard, sequences, sequencer, driver, monitors and agents. The design is assumed to be correct as it functional and code coverage is correct. Figure 3.2 shows the setup.

Figure 3.2: AMBA APB UVM setup [26]

# 3.4 Summary

To summarise all the highlights from the related works section, when it comes to SoC verification, we have that the verification results at unit level should be reusable in the verification of the interconnects and at a higher level, and the tests themselves should be

reusable at the unit level. The tests should work like a hierarchy where tests at any level are configurable and modifiable and also partly or fully reusable in other tests. Changes in the tests must automatically propagate to other tests throughout the design that uses something from these tests. This builds upon the common verification libraries which ensures that there is only one copy of a given test code, and that other test codes or test generators which pulls code from the library always are updated with the latest changes to any code. By using a high level description of the circuit at different levels, we have a platform to test software on and a reference design to compare the verified hardware to. This makes it possible to design HW and SW simultaneously, and to test efficiently. Many and thoroughly tests at unit level decreases testing effort at a higher level, also copies of a unit is not verified twice.

# Chapter 4

# SHMAC verification methodology

# 4.1 Analysis of the current verification strategies

The current verification strategies for the SHMAC platform present several limitations, which were identified and analyzed on the project preceding this thesis [20]. One of the main shortcomings involves the use of directed tests in both testbenches and baremetal testing on FPGA. Hand-coding all the possible test cases not only represents a timeconsuming and tedious task for the developers, but also usually leads to verification incompleteness. The reason for this is that not all the possible scenarios and corner cases can be easily anticipated by the designer and included as test stimulus.