# Ultra Low Leakage Memory

Kai Robert Liknes

Master of Science in ElectronicsSubmission date:June 2016Supervisor:Snorre Aunet, IETCo-supervisor:Bjornar Hernes, Disruptive Technologies

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# Ultra Low Leakage Memory

# Kai Liknes 10.06.2016

# Abstract

Three 64-byte memory systems were designed for a 0.18µm standard CMOS technology, one 6T-SRAM system and two D-Flip-Flop systems. The leakage current, read energy and write energy of these systems were determined by simulation. A set of extrapolation formulas for area, leakage current, read energy and write energy were designed to determine the characteristics of the systems as the size of the memory increases.

The simulations showed that the 64-Byte 6T-SRAM system had a 39% lower area, an 83% lower leakage current, an 89% lower write energy and an 82% lower read energy than the reference D-Flip-Flop memory system. The extrapolation formulas predicted that as memory sizes increases, SRAM becomes more and more favorable in terms of area, leakage current, write energy and read energy.

#

Norwegian University of Science and Technology

# Samandrag (Norwegian translation of abstract)

Tre 64-byte minnesystem vart utvikla for ein 0.18µm standard CMOS teknologi, eit 6T-SRAMminnesystem og to D-Vippe-minnesystem. Lekasjestraumen, leseenergien og skriveenergien til desse minnesystema vart simulerte. Eit sett med ekstrapolasjonsformlar vart utvikla for å avgjere korleis desse trekka til minnesystema oppfører seg når minnestørrelsane auker.

Simuleringane viste at 64-Byte 6T-SRAM-minnesystemet hadde eit 39% mindre brikkeområde, 83% lågare lekasjestraum, 89% lågare skriveenergi og 82% lågare leseenergi enn D-Vippe-minnesystemet. Ekstrapoleringsformlane føresåg at dersom minnestørrelsane auker, så blir brikkeområdet, lekasjestraumen, leseenergien og skriveenergien til SRAM-minnesystemet betre og betre i høve til D-Vippe-minnessystemet.

# **Problem description**

The following is a problem description taken from the NTNU DAIM system. The problem description is only partially representative of the focus of this dissertation.

## Ultra low leakage memory

In ultra low power ICs, the leakage current is an important contributor to power dissipation. The leakage can be reduced by switching off power supplies to modules that are inactive. However, some memory is required to store the state of the system. Using non-volatile memory may in some cases not be power efficient. Using low leakage RAM is therefore preferred in some cases.

The assignment will consist of the following tasks:

- •Study literature and identify solutions for low leakage memory

- •Investigate tradeoffs and compare the identified solutions

- •Select best approach and design key building blocks

- •Implementation of whole RAM

- •Layout

# Table of Contents

| Abstract   |                                                         | .1  |

|------------|---------------------------------------------------------|-----|

| Samand     | rag (Norwegian translation of abstract)                 | . 2 |

| Problem    | description                                             | . 2 |

| List of Fi | gures                                                   | .5  |

| List of ta | bles                                                    | .6  |

| List of te | rms, abbreviations and definitions                      | .7  |

| 1. Pre     | face                                                    | .8  |

| 2. Ack     | nowledgement                                            | .8  |

| 3. Intr    | oduction                                                | .8  |

| 4. The     | oretical background                                     | .9  |

| 4.1 Pr     | evious work                                             | .9  |

| 4.2 Le     | akage / Static energy consumption                       | .9  |

| 4.3 M      | emory Cells                                             | 10  |

| 4.3        | 1 6T SRAM cell                                          | 10  |

| 4.3        | 2 D-Flip-flop                                           | 11  |

| 4.4 TS     | MC standard cell library naming conventions             | 11  |

| 4.5 Dr     | ive strength                                            | 11  |

| 4.6 Ca     | dence Bus Notation                                      | 12  |

| 4.7 De     | egraded logic / pass transistors / short circuit power  | 12  |

| 5. Imp     | plementation                                            | 13  |

| 5.1 De     | esign specifications                                    | 13  |

| 5.1        | 1 Process / technology                                  | 13  |

| 5.1        | 2 Choice of default and minimum transistor sizes        | 14  |

| 5.2 Th     | e D-Flip-Flop memory system                             | 15  |

| 5.2        | 1 Read and write operations                             | 18  |

| 5.2        | 2 Sub-Cells                                             | 20  |

| 5.2        | 3 The reference D-Flip-Flop (REFDFF, DFCNQD1)           | 21  |

| 5.2        | 4 The C2MOS D-Flip-Flop (KHAN_DFF, D_FLIP_FLOP_KHAN_01) | 21  |

| 5.3 Th     | e 6T-SRAM memory system                                 | 22  |

| 5.3        | 1 Read and write operations                             | 24  |

| 5.3        | 2 Sub-Cells                                             | 26  |

| 5.3        | 3 Row driver circuit                                    | 31  |

| 5.3        | 4 Bit line driver circuitry                             | 32  |

| 5.3        | 5 Sense amplifier                                       | 33  |

| 5.3        | 6 6T-SRAM-Cell                                          | 34  |

| 5.3.7 Reset circuitry                                                     | 35 |

|---------------------------------------------------------------------------|----|

| 5.4 Extrapolator                                                          | 35 |

| 5.4.1 The gate count unit of measurement                                  | 35 |

| 5.4.2 Predicting the gate count and leakage current of the memory systems |    |

| 5.4.3 Predicting the read and write energy of the memory systems          |    |

| 5.4.4 Measuring average leakage current of standard cells                 |    |

| 5.4.5 Table of the cells' leakage current and gate count                  |    |

| 5.4.6 Calculating the amount of multiplexers, demultiplexers and buffers  | 40 |

| 5.4.7 Table of cell count prediction formulas                             | 41 |

| 5.5 Miscellaneous non-standard cell schematics                            | 41 |

| 5.6 Method of simulation                                                  |    |

| 5.6.1 Simulator                                                           |    |

| 5.6.2 Measuring read and write energy                                     | 45 |

| 5.6.3 Determining the worst case initial memory state                     | 46 |

| 5.6.4 64 Byte D-Flip-Flop simulation setup                                | 47 |

| 5.6.4 64 Byte SRAM Simulation setup                                       | 48 |

| 6. Results                                                                |    |

| 6.1 Simulation results                                                    | 49 |

| 6.2 Extrapolation results                                                 | 50 |

| 7. Discussion                                                             | 52 |

| 7.1 D-Flip-Flop implementation                                            | 52 |

| 7.2 6T-SRAM implementation                                                | 53 |

| 7.2.1 Sense amplifier                                                     | 53 |

| 7.2.2 Row/Column ratio                                                    | 54 |

| 7.2.3 Floating charge memory corruption                                   | 55 |

| 7.3 Extrapolator implementation                                           | 55 |

| 7.3.1 Address bus buffers                                                 | 55 |

| 7.3.2 Multiplexer/demultiplexer fan-outs                                  | 55 |

| 7.3.3 Leakage current prediction                                          | 56 |

| 7.3.4 State machine                                                       | 56 |

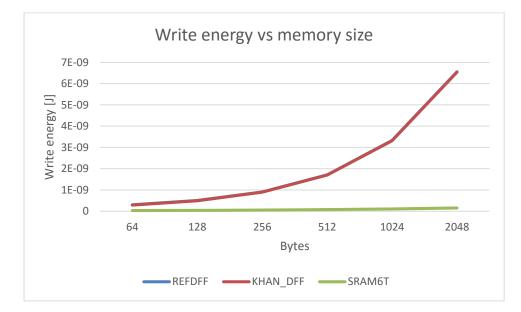

| 7.3.5 Read and Write energy prediction                                    | 57 |

| 7.4 Method of simulation                                                  | 57 |

| 7.4.1 Memory state                                                        | 57 |

| 7.4.2 Clock Frequency:                                                    | 58 |

| 7.4.3 SRAM bit line model:                                                | 58 |

| 7.5 Results                                                               | 58 |

|     | 7.6 I  | Final system comparisons                                                                 | 59 |

|-----|--------|------------------------------------------------------------------------------------------|----|

| 8.  | Con    | clusion                                                                                  | 59 |

| 8   | .1     | Future work                                                                              | 59 |

|     | 8.1.   | 1 Additional memory types                                                                | 59 |

|     | 8.1.2  | 2 Peripheral circuitry implementation                                                    | 60 |

|     | 8.1.3  | 3 SRAM sense amplifier                                                                   | 60 |

|     | 8.1.4  | 4 Extrapolation                                                                          | 60 |

| 9.  | Refe   | erences:                                                                                 | 61 |

| Арр | endix  | A: Simulations supporting the choice of initial memory state for the D-Flip-Flop system. | 62 |

| Арр | endix  | KB: Stim and Measure cell schematics                                                     | 63 |

| Арр | endix  | c C: MATLAB scripts used to generate ocean and stimulus files                            | 66 |

| D   | -Flip- | Flop stim script                                                                         | 66 |

| D   | -Flip- | Flip flop ocean script                                                                   | 68 |

| 6   | T-SRA  | AM stim script                                                                           | 69 |

| 6   | T-SRA  | AM ocean script                                                                          | 71 |

| A   | verag  | ge leak test ocean and stim script                                                       | 73 |

| Арр | endix  | CD: Simulation snapshots implying the validity of the memory systems                     | 75 |

# List of Figures

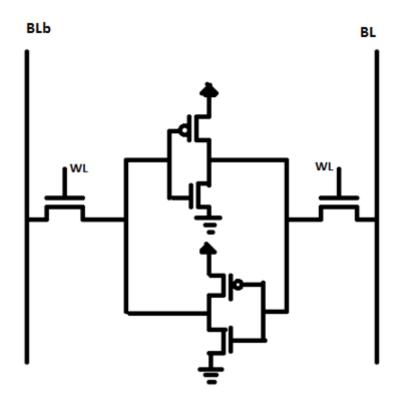

| Figure 1: A standard 6T SRAM cell1                                                              | 1 |

|-------------------------------------------------------------------------------------------------|---|

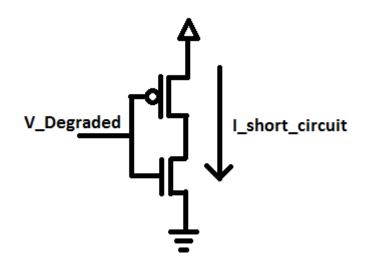

| Figure 2: An example of degraded logic causing a short circuit current                          | 2 |

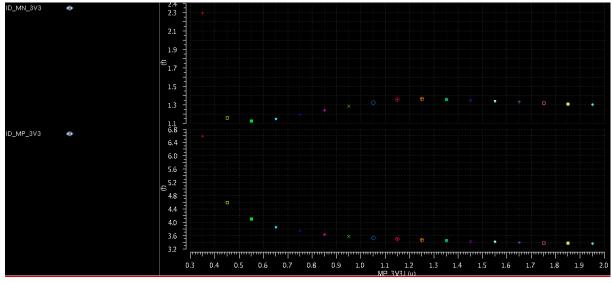

| Figure 3: Leakage current through an NMOS transistor (upper) and a PMOS transistor (lower) as a |   |

| function of transistor length. [2]1                                                             | 4 |

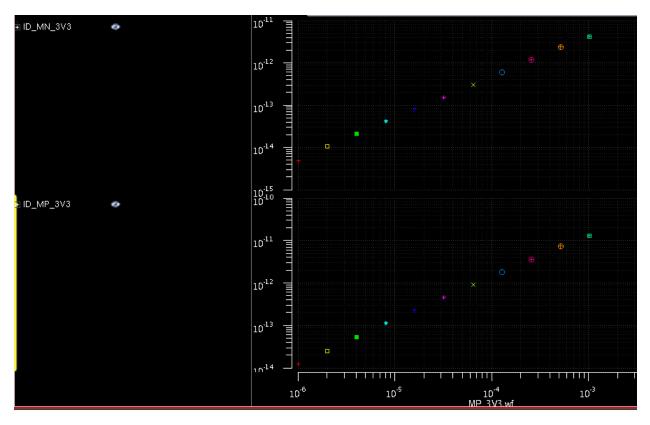

| Figure 4: Leakage current through an NMOS transistor (upper) and a PMOS transistor (lower) as a |   |

| function of transistor width. [2]1                                                              | 5 |

| Figure 5: The SIXTYFOURBYTE_DFF Cell1                                                           | 7 |

| Figure 6: A waveform showing a standard read operation in the D-Flip-Flop system1               | 8 |

| Figure 7: A waveform showing a standard write operation in the D-Flip-Flop memory system        | 9 |

| Figure 8: The EIGHTBYTE_DFF cell                                                                | 0 |

| Figure 9: The BYTE_DFF cell2                                                                    | 1 |

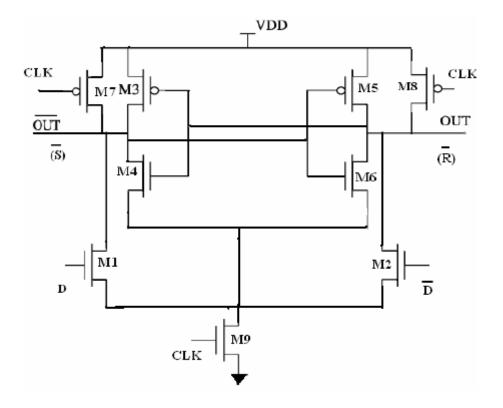

| Figure 10: The C2MOS Flip Flop (D_FLIP_FLOP_KHAN_01 / KHAN_DFF)2                                | 2 |

| Figure 11: The SRAM6T_64B_02 cell2                                                              | 3 |

| Figure 12: A waveform showing a standard read operation in the 6T-SRAM memory system2           | 5 |

| Figure 13: A waveform showing a standard write operation in the 6T-SRAM memory system           | 6 |

| Figure 14: The 8x8bitBox_01 cell2                                                               | 7 |

| Figure 15: The 8x8bitBox_Left_01 cell2                                                          | 8 |

| Figure 16: The 8x8bitBox_top_02 cell2                                                           | 9 |

| Figure 17: The 8x8bitBox_topleft_02 cell                                                        | 0 |

| Figure 18: The Row_WLDriver_01 cell used in the 6T-SRAM system                                  | 1 |

| Figure 19: The Column_Circuitry_04 cell, or bit line pair driver                                | 32   |

|-------------------------------------------------------------------------------------------------|------|

| Figure 20: The sense amplifier used in the SRAM system.                                         | 33   |

| Figure 21: The 6T SRAM cell                                                                     | 34   |

| Figure 22:The testbench for measuring the average leakage current of standard cells             | 37   |

| Figure 23: The testbench used to measure average leakage currents in the cells which make up th | ne   |

| peripheral circuitry                                                                            | 38   |

| Figure 24: A simplified solution of the sum of a geometric row 2 <sup>N-1</sup>                 | 40   |

| Figure 25: The DEMUX-1-2_02 cell                                                                | 41   |

| Figure 26: The DEMUX-1-4_01 cell                                                                | 42   |

| Figure 27: The DEMUX-1-8_02 Cell                                                                | 43   |

| Figure 28: The MUX_8-1_02 cell                                                                  | 44   |

| Figure 29: An example showing the calculation of the energy spent during a D-Flip-Flop system w | rite |

| operation                                                                                       | 45   |

| Figure 30: The TB_SIXTYFOURBYTE_REFDFF_01 testbench for the 64 Byte D-Flip-Flop memory          |      |

| system                                                                                          | 47   |

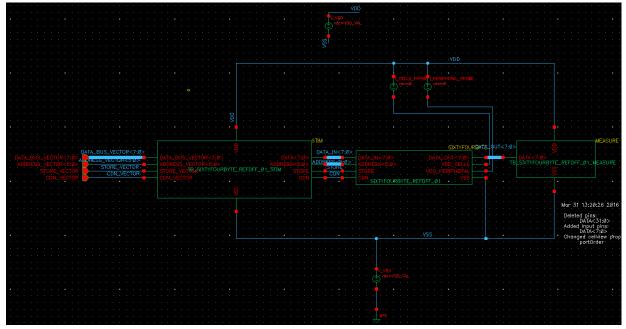

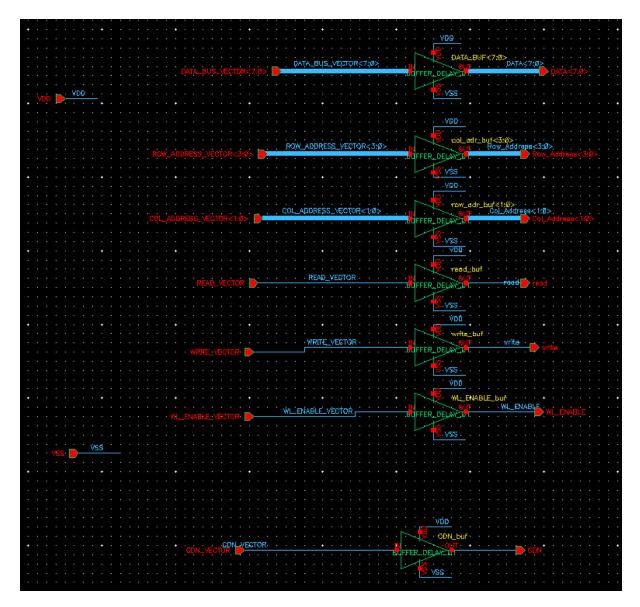

| Figure 31: The TB_SRAM6T_64B_02 testbench for the SRAM system                                   | 48   |

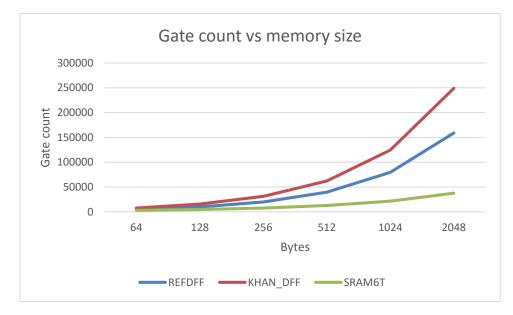

| Figure 32: Predicted gate count (normalized area) as a function of memory size [Byte]           | 50   |

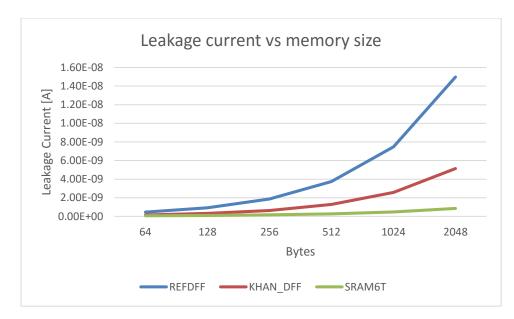

| Figure 33: Predicted leakage current as a function of memory size [Byte]                        | 51   |

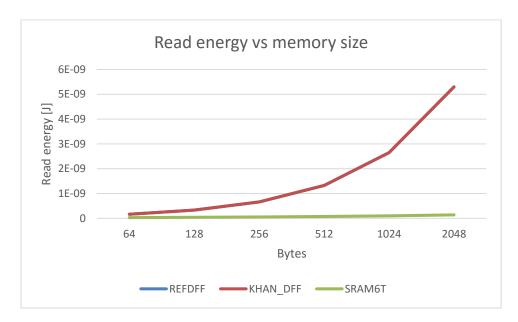

| Figure 34: Predicted read energy as a function of memory size [Byte]                            | 51   |

| Figure 35: Predicted write energy as a function of memory size [Byte]                           | 52   |

| Figure 36: An alternative sense amplifier presented in [12]                                     | 53   |

| Figure 37: The TB_SIXTYFOURBYTE_REFDFF_01_STIM cell                                             | 63   |

| Figure 38: The TB_SIXTYFOURBYTE_REFDFF_01_MEASURE cell                                          | 63   |

| Figure 39: The TB_SRAM6T_64B_02_STIM cell                                                       | 64   |

| Figure 40: The TB_SRAM6T_64B_02_MEASURE cell                                                    | 65   |

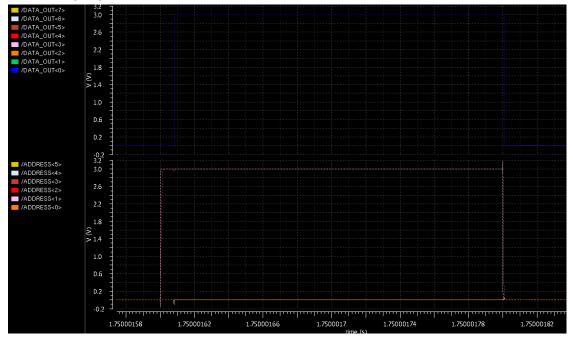

| Figure 41: A byte containing 0xFF is being read in the REFDFF system                            | 75   |

| Figure 42: A byte containing 0xFF being read in the 6T-SRAM system                              |      |

# List of tables

| Table 1: D-Flip-Flop truth table                                                                | 11    |

|-------------------------------------------------------------------------------------------------|-------|

| Table 2: Instructions decoded from the read   write codeword                                    | 24    |

| Table 3: The truth table for the Row_WLDriver_01 cell                                           | 31    |

| Table 4:The truth table for the Column_Circuitry_04 cell                                        | 33    |

| Table 5: Transistor sizes for the 6T SRAM cell                                                  | 35    |

| Table 6: Simulated leakage currents of various TSMC standard cells and the gate counts as spec  | ified |

| in the TSMC standard cell datasheet                                                             | 38    |

| Table 7: A table of calculated gate counts and leakage currents of non-standard cells           | 39    |

| Table 8: The formulas for calculating the number of cells contained within either a D-flip-flop |       |

| memory system or a 6T-SRAM memory system                                                        | 41    |

| Table 9: The truth table for the DEMUX-1-2_02 cell                                              | 42    |

| Table 10: The corresponding truth table for the DEMUX-1-4_01 cell                               | 42    |

| Table 11: The truth table corresponding to the DEMUX_1-8_02 cell                                | 44    |

| Table 12: The truth table corresponding to the MUX_8-1_02 cell                                  | 44    |

| Table 13: The non-default simulator settings used in all simulations.                           | 44    |

| Table 14: The stimulus applied to the TB_SIXTYFOURBYTE_REFDFF_01 testbench                  | 47 |

|---------------------------------------------------------------------------------------------|----|

| Table 15: The stimulus applied to the TB_SRAM6T_64B_02 testbench                            | 49 |

| Table 16: Leakage currents and read/write energies of the three 64 byte memories            | 49 |

| Table 17: calculated leakage currents and read/write energies per cel                       | 50 |

| Table 18: Predicted gate count (normalized area) as a function of memory size [Byte]        | 50 |

| Table 19: Predicted leakage current [A] as a function of memory size [Byte]                 | 51 |

| Table 20: Predicted read energy [J] as a function of memory size [Byte]                     | 52 |

| Table 21: Predicted write energy [J] as a function of memory size [Byte]                    | 52 |

| Table 22: A comparison of the predicted and simulated leakage currents of the three memory  |    |

| systems                                                                                     | 56 |

| Table 23: Leakage currents of an 8 byte memory utilizing reference flip flops (REFDFF)      | 62 |

| Table 24: Read and write energy of an 8 byte memory utilizing reference flip flops (REFDFF) | 62 |

| Table 25: Leakage currents of an 8 byte memory utilizing C2MOS Flip Flops (KHAN_DFF)        | 62 |

| Table 26: Read and write energy of an 8-byte memory utilizing reference C2MOS Flip Flops    |    |

| (KHAN_DFF)                                                                                  | 62 |

|                                                                                             |    |

# List of terms, abbreviations and definitions

CDN – clear data negative. Same as an active low reset.

WL – Write line. Used to open up a row of SRAM cells for either read or write.

BLb and BL - Bit Line bar and Bit Line. These are used in SRAM. BLb = 0 and BL = 1 indicates a logic '1'. BLb = 1 and BL = 0 indicates a logic '0'.

REFDFF – the reference D-flip-flop used as a baseline for measuring leakage current and read and write energies.

KHAN\_DFF – an alias for the C2MOS D-Flip-Flop

Memory system – A cell array which can be written to or read from given the right sequence of inputs, excluding the state machine which translates instructions to sequences of inputs.

Row – All 6T-SRAM cells connected to a single write line.

Column – A group of eight bit-line pairs.

Bit line pair – A pair of bit lines, BLb and BL, between which many SRAM cells are connected.

Design time – the amount of man-hours required to complete a design, and ready it for fabrication.

# 1. Preface

This master's dissertation is written for the Norwegian University of Science and Technology (NTNU) and Disruptive Technologies AS. Disruptive Technologies is a newly-started company that specializes in designing microchips for use in the Internet of Things industry.

The work presented in this report was done in cooperation with Disruptive Technologies, and the memory system designs were designed to be compatible with the company's choice of technology and design conventions.

The main supervisor was Snorre Aunet (NTNU) <snorre.aunet@iet.ntnu.no>, and the main company contact was Bjørnar Hernes (Disruptive Technologies) <bjornar@disruptive-technologies.com>.

The following sections are adapted from [1], a work by the same author: Section 3, 4.1, 4.2 and 4.3. The previous report might be requested by emailing the author at kaisemailaddress@gmail.com.

# 2. Acknowledgement

I would like to thank Bjørnar Hernes for being of great assistance in teaching me valuable lessons about the workings of the microchip industry, for helping me learn how to master the Cadence analog design suite, and for helping me proofread and tailor the implementation chapter of this dissertation.

I would further like to thank Snorre Aunet for proofreading the dissertation on such a short notice.

I would like to criticize Imran Ahmed Khan and Mirza Tariq Beg, the authors of [8], whose seemingly erroneous schematic cost me over 4 days of design time during the development phase.

# 3. Introduction

The Internet of Things (IoT) is a concept which is quickly gaining popularity and this causes the IC industry to gear towards designing microchips that are compatible with this concept. According to advocates of the Internet of Things concept [2], almost every physical object in use by people will eventually be connected to the internet. Microchips are designed to fit into even the most trivial applications such as clothes hangers. Sensor networks are created by spreading out a large amount of inexpensive sensors and having them communicate over the internet. In these cases, a change of batteries is impractical and therefore one must design to maximize the battery lifetime of the chip. In most applications in the Internet of Things, the chip is only active and computing/transmitting data a fraction of the time. This means the static power consumption (power leakage) will be the deciding factor in battery lifetime.

All IoT-chips will require some form of data storage. This report assumes a distributed shared memory (DSM), and that the memory is implemented as a single centralized memory cell array.

Memory accesses only happen when a chip is either computing or transmitting data, and because these actions are infrequent, memory accesses are also infrequent. Combined with the fact that the memory portion of a chip often makes up a large portion of the total chip area, this means that minimizing the power leakage of the memory is essential to reducing the static power consumption of the entire chip. In previous works, reducing power consumption meant reducing the active power consumption. Active power is the power required to switch transistors on and off. As stated, the leakage power of the design is much more of a concern in IoT-chips than other chips. Instead of designing for speed, area, or active power consumption, this report focuses primarily on the static power consumption of memory circuits.

# 4. Theoretical background

# 4.1 Previous work

Previous work in minimizing power in memory circuits focus mostly on Active power consumption, while not considering static power consumption.

The work put into improving D-Flip-Flop systems mostly focus on the flip flop cell itself, as D-Flip-Flops are rarely used to build memory arrays larger than 128 bytes. [3] introduces a D-Flip-Flop design built on C<sup>2</sup>MOS (C2MOS) latch design principles, and utilizes a sense amplifier in its design to achieve lower static and dynamic power consumption. The leakage current of the D-Flip-Flop is inferred to be 188pA at a supply voltage of 1.8V.

Some effort has been spent on improving the energy efficiency of SRAM circuits. [4] tries to minimize read and write power in the SRAM by splitting up bit line pairs into several sub-bit-line-pairs, which includes a local sense amplifier. [5] Uses the same approach of splitting up the SRAM into smaller nodes, but instead focuses on splitting up the SRAM into a binary tree structure. The two solutions have something in common: They both trade area for lower read and write power, and a larger area usually leads to a larger leakage current.

[1] is an unpublished work by the same author as this report. The previous report explores the viability of several types of memory in the context of designing a low leakage, low power memory system. The previous report also considers the limitations of designing a circuit for fabrication using a basic CMOS technology. Parts of the work presented in this report builds on the findings of the previous report. The previous report might be requested by emailing the author at kaisemailaddress@gmail.com.

# 4.2 Leakage / Static energy consumption

In CMOS technologies using a technology node of 90nm and larger, the most dominant source of static power is the subthreshold leakage power,  $P_{sub\_leak}$ . For a single-V<sub>dd</sub>-level circuit this is given as:

$$P_{sub\_leak} = V_{DD} * I_{sub\_leak} = \frac{V_{DD}^{2}}{R_{Vdd-gnd}}$$

Formula 1: Leakage power as a function of leakage current and supply voltage

Where  $I_{sub\_leak}$  is the current going from  $V_{DD}$  to ground, through the drain-source subthreshold channel of the transistors.  $R_{Vdd-gnd}$  is the equivalent resistance seen from  $V_{DD}$  to ground.

According to [14], the subthreshold leakage current through a single transistor can be approximated by the following function:

$$I_{DS,off}[nA] = 100 * \frac{W}{L} * 10^{-\frac{V_t}{S}}$$

Formula 2: A function approximating the leakage current through a transistor

Where W is the gate width, L is the gate length,  $V_t$  is the threshold voltage. S is the so-called *subthreshold swing*, given by:

$$S = \eta * 60 \text{mV} * \frac{T}{100}$$

Formula 3: The formula for subthreshold swing Where *T* is the temperature [K], and  $\eta$  is equal to:

$$\eta = 1 + \frac{C_{dep}}{C_{oxe}} \quad [4]$$

Formula 4: The formula for  $\eta$

Where  $C_{dep}$  is the channel-depletion capacitance and  $C_{oxe}$  is the channel-oxide capacitance.

## 4.3 Memory Cells

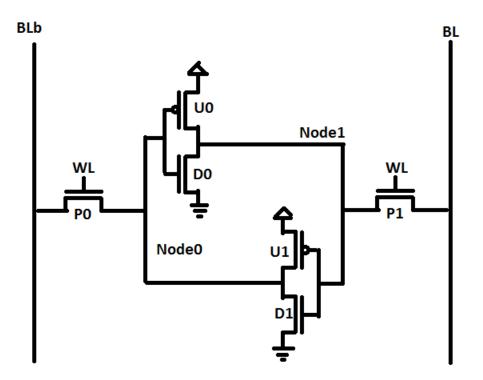

### 4.3.1 6T SRAM cell

A 6T-SRAM cell retains its data by having two inverters connected in a feedback loop. The first inverter inverts the input given from the second inverter, and sends that output to the input of the second inverter, which in turn inverts and sends back to the first inverter. This means the voltage from either VDD or GND from the output of the first inverter reinforces the charge on the input of the second inverter, and vice versa. This mutual reinforcement of charges on the gates of the transistors in each inverter is what retains the data.

To write to the SRAM, the charges stored on either side of the inverter loop must be forced to the desired value. To do this, the two bit lines are forced to the desired voltage, one will be VDD and one will be GND. The word line transistors are then opened. This will draw the charges out of the inverter loop and force the loop to store the new value instead.

The simplest way to read from an SRAM cell is simply to open the word line pass transistors and read the voltages on the bit lines. The bit lines have a large parasitic capacitance and will take some time to charge. Using a sense amplifier to quickly sense the difference in voltage on the bit lines will help solve this problem.

### 4.3.2 D-Flip-flop

A positive-edge-triggered D flip flop stores the value D only when the signal Clk transitions from low to high, a so called rising edge.

| Clk         | D | Qnext |

|-------------|---|-------|

| Rising edge | 0 | 0     |

| Rising edge | 1 | 1     |

| Non-rising  | X | Qprev |

Table 1: D-Flip-Flop truth table

### 4.4 TSMC standard cell library naming conventions

The standard cell library provided by TSMC for the TSMC18G process contains cells which follow a naming convention in the following format: |NAME|Y|D|x|. NAME is the abbreviated name of the cell. Y is the amount of inputs, and is only included if the cell has multiple versions with different amounts of inputs. D means drive strength, and x is an integer denoting the drive strength of the cell, and ranges from 0 to 10. Drive strength is explained in section 4.5. An example of this naming convention is the cell ND4D2, which is a 4-input NAND gate with a drive strength of 2.

## 4.5 Drive strength

Drive strength is how easily a transistor allows current to pass through itself when switched on. A large drive strength is required to charge nodes with a high capacitance. If an output-driving transistor has an insufficiently large drive strength, the time required to charge the output capacitance will increase. This will severely affect the speed of the circuit. The drive strength of a transistor is closely related to the W/L ratio of the transistor; a higher W/L ratio produces a higher drive strength.

Cells with a high drive strength often have a high input capacitance, making it necessary for the cell driving the high-drive strength cell to have a sufficient drive strength itself. A rule of thumb used in the design presented in this report is that a cell with a drive strength of N (see section 4.5) can drive a load of cells totalling a drive strength of N+2. A load of 2 cells of drive strength N is assumed to equal a load of a single cell of strength N+1. As an example, a cell with a drive strength 2 can drive one cell with a drive strength of 4, or 2 cells of drive strength of 3.

## 4.6 Cadence Bus Notation

For the Cadence Virtuoso software, a specific notation is used to denote either a collection of signals or cells, and if the same notation is used for both the signals and cells, the collection of signals will correspond to the collection of cells. The following is an example of the usage of bus notation: A denotation of Bus<3:0> will contain the signals Bus<3>, Bus<2>, Bus<1> and Bus<0>. Connecting the node Bus<3:0> to a single-input, single-output cell called Inverter<3:0> will cause Bus<3> to connect to Inverter<2> and so on.

## 4.7 Degraded logic / pass transistors / short circuit power

A degraded logic signal is a signal that is not fully charged to VDD (logic '1') or not fully discharged to VSS (logic '0). A degraded logic '1' is also called a 'weak' logic '1' as opposed to a 'strong' logic '1', and will have a voltage value which is less than VDD. When an NMOS transistor is placed between a node and VDD, turning on the transistor will not allow the node to completely reach a voltage value of VDD. The same applies for PMOS transistors placed between a node and VSS.

Pass transistors are commonly used in CMOS circuits, and the effect of voltage degradation may significantly influence the operation of the circuit. Using an NMOS pass transistor will cause an input of logic '1'/VDD to be degraded to a voltage of VDD-Vth on the output side of the pass transistor [6]. Vth is the threshold voltage of the NMOS pass transistor. Transmission gates solves the problem of degraded logic, but require two transistors and two complementary inputs as opposed to one.

#### Figure 2: An example of degraded logic causing a short circuit current.

Figure 2 shows an example of what might happen if a gate voltage value is degraded to the point where it lower than the threshold voltage for the PMOS transistor, and higher than the threshold

voltage for an NMOS transistor. The resulting current through both transistors will incur a very large short circuit power consumption and might overheat the circuit, permanently damaging it.

# 5. Implementation

Three different memory systems were implemented. Two versions of a D-Flip-Flop memory system were implemented, utilizing two different D-Flip-Flops. A 6T-SRAM system was also implemented, with the intention of comparing memory systems using D-flip-flops to systems using SRAM with focus on leakage current, power consumption and area. The size of the designed memory systems were 64 Bytes. The reason for this was that the simulations were done on servers owned by Cadence Design Systems, rented by Disruptive Technologies, and simulation time was limited. To mitigate the small size of the memory systems, a prediction formula was implemented in Microsoft Excel with the purpose of extrapolating the leakage currents, area and read and write energies for larger memory systems.

The cell names are sometimes misleading, as they are temporary names used in the design phase. The reason behind this is to allow Disruptive Technologies to continue using the designs if need be. To mitigate this, cells often go by multiple names in the report, and often both names are stated.

# 5.1 Design specifications

A number of design goals are considered when designing the memory systems. The following list contains design requirements by order of importance, 1 being the most important consideration:

- 1) Minimize leakage current

- 2) Minimize read energy

- 3) Minimize write energy

- 4) Minimize chip area

- 5) Minimize design complexity

Minimizing the leakage current is the most important consideration, as the memory most likely be idle most of the time. Reads are assumed to be more frequent than writes, and it is therefore more important to minimize read energy than to minimize write energy. Minimizing chip area is always an important consideration to minimize chip costs. Lastly, because the design is handed over to another designer, the complexity of the design should be minimized to allow a quick transfer of knowledge from designer to designer.

# 5.1.1 Process / technology

The purpose of the design is to be implemented using a 0.18µm standard CMOS technology from the Taiwan Semiconductor Manufacturing Company. The process name is TSMC18G.

## 5.1.2 Choice of default and minimum transistor sizes

Figure 3: Leakage current through an NMOS transistor (upper) and a PMOS transistor (lower) as a function of transistor length. [2]

Figure 3 shows the simulation results of leakage current through a NMOS and PMOS transistor as a function of transistor length. The simulations were done by applying a voltage across the transistor while the transistor was turned off ( $V_G$  = VSS for the NMOS,  $V_G$  = VDD for the PMOS). The following simulation parameters were used:

- Process: TSMC018

- gmin=1e-17

- *L*=0.35µm

- *W*=0.5µm

- *Temp*=27°C

- V<sub>DS</sub>=2.5V

- Transistor type: 3.3V.

The results imply that a length of 550nm will minimize the leakage current through an NMOS transistor. Using the same length for PMOS transistors will simplify the layout of the chip, saving

area. Many equations in the VLSI domain contain terms in this format:  $\frac{\frac{W_0}{L_0}}{\frac{W_1}{L_1}}$ . Choosing a standard

length would greatly simplify these equations, reducing design time. During the layout phase, in CMOS structures such as the basic inverter, the PMOS transistors are usually laid out in parallel lengthwise with the NMOS transistors [7]. Choosing different lengths would make the parallel PMOS and NMOS transistors not align with each other, complicating the layout engineer's job, increasing design time. Choosing the length of the PMOS to be longer would further limit leakage current, but would increase the area of the circuit considerably and would drastically increase design time. This lead to 550nm being chosen as the default length for all transistors in the design.

Figure 4: Leakage current through an NMOS transistor (upper) and a PMOS transistor (lower) as a function of transistor width. [2]

Figure 4 shows the simulation results of leakage current through an NMOS and PMOS transistor as a function of transistor width. The simulations were done by applying a voltage across the transistor while the transistor was turned off (Vg = VSS for the NMOS, Vg = VDD for the PMOS). The following simulation parameters were used:

- Process: TSMC018

- gmin=1e-17

- L=0.35µ

- W=0.5µ

- Temp=27°C

- V<sub>DS</sub>=2.5V

- Transistor type: 3.3V.

One can see that a larger width leads to a larger leakage current. Choosing a width as low as possible would minimize leakage current. However, choosing a width that is too close to the absolute minimum leads to greater susceptibility to fabrication errors (larger transistors leave much more room for error). If the design is very susceptible to fabrication errors, a larger amount of the finished microchips will not pass the physical verification process and the fabrication yield will decrease, increasing the cost of the chip. A minimum width of 300nm was chosen.

The simulations in figure 3 and 4 were provided by Disruptive Technologies.

# 5.2 The D-Flip-Flop memory system

The D-Flip-Flop memory system was implemented utilizing two different D-flip-flop cells. The first was the reference D-Flip-Flop, the second was the C2MOS Flip-Flop.

As opposed to SRAM, a D-Flip-Flop memory has no internal multiplexing (bit lines and write lines). This means that the fan-out of demultiplexers and multiplexers is much broader than for the SRAM system. This also means that the peripheral circuitry of the D-Flip-Flop is simpler.

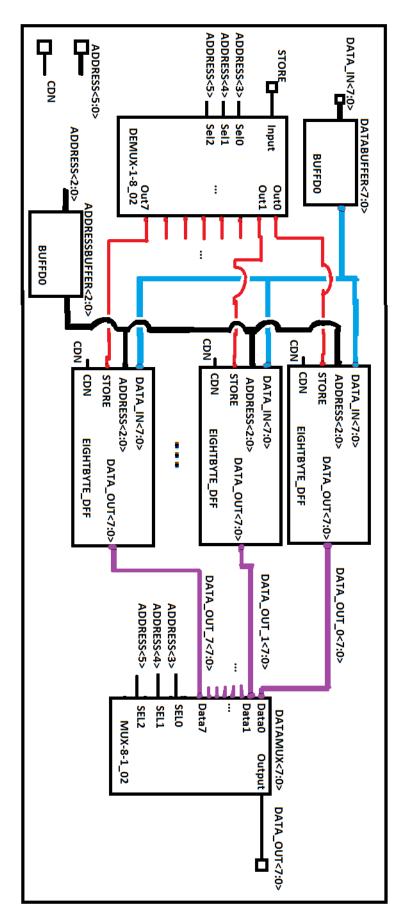

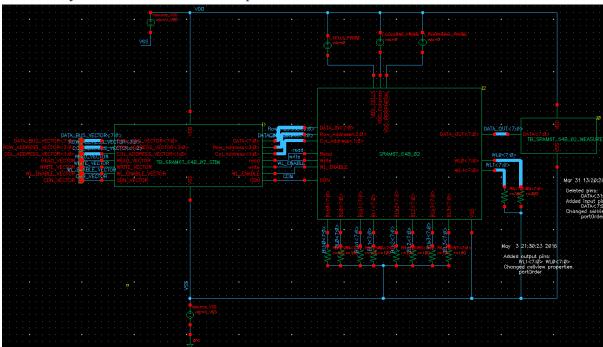

Figure 5: The SIXTYFOURBYTE\_DFF Cell

Figure 5 shows a completed 64 Byte D-Flip-Flop memory system, the same as the one used in the simulations presented in this report. The address bus is buffered as there are 8 8-1 demultiplexers connected to each wire on the bus (see figure 8), and that presents a significant load capacitance. The SIXTYFOURBYTE\_DFF cell is made up of 8 EIGHTBYTE\_DFF cells, which are explained in detail in section 5.2.2.

In the design, each flip-flop has its own set of peripheral circuitry cells. The peripheral circuitry used by one flip-flop cell is copied and the duplicated version is used when testing the other flip-flop cell. The peripheral circuitry cells are named with either the keyword 'KHAN' for the C2MOS flip flop, or 'REFDFF' for the reference D-Flip-Flop. The reason for copying the peripheral circuitry is to allow two separate testbenches for every cell, as well as to allow changes to the peripheral circuitry for each separate flip flop. As per this report, the peripheral circuits of the two flip flops are identical.

## 5.2.1 Read and write operations

## Input signal descriptions:

- Store: A positive flank of the store signal will perform a write of the specified value decided by the Data bus in the flip flop decided by the address bus.

- Address: A binary number which decides which byte in the memory to read from or write to.

- Data: An 8bit/1byte binary number, which is stored in the memory if the 'store' signal goes high.

- CDN: Clear Data Negative. When CDN is low, all flip flops in the memory are reset to a value of '0'.

## **Read operation:**

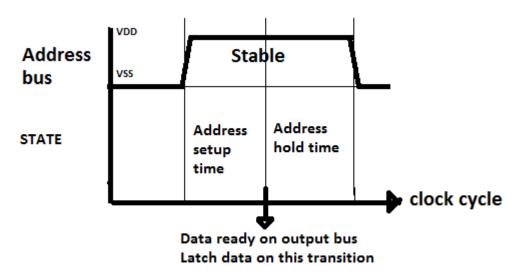

#### Figure 6: A waveform showing a standard read operation in the D-Flip-Flop system

Figure 6 shows a waveform explaining how to perform a read operation in the D-Flip-Flop system implemented in this report. The associated states of a yet-to-be-implemented state machine is also included in the waveform. The address setup and hold times are needed to. If the address bus is altered while the output is being latched onto the data bus, the latched data will be corrupted.

Write operation:

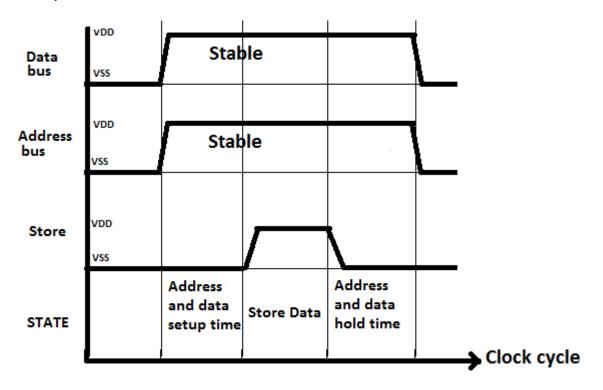

Figure 7: A waveform showing a standard write operation in the D-Flip-Flop memory system.

Figure 7 shows a waveform explaining how to perform a write operation in the D-Flip-Flop system implemented in this report. The associated states of a yet-to-be-implemented state machine is also included in the waveform. The address and data setup and hold times are needed to prevent a glitched store signal from corrupting the memory. If the address bus is altered while the store signal is not settled at a logic '0', other cells in the cell array will get a store signal pulse and will be corrupted.

5.2.2 Sub-Cells

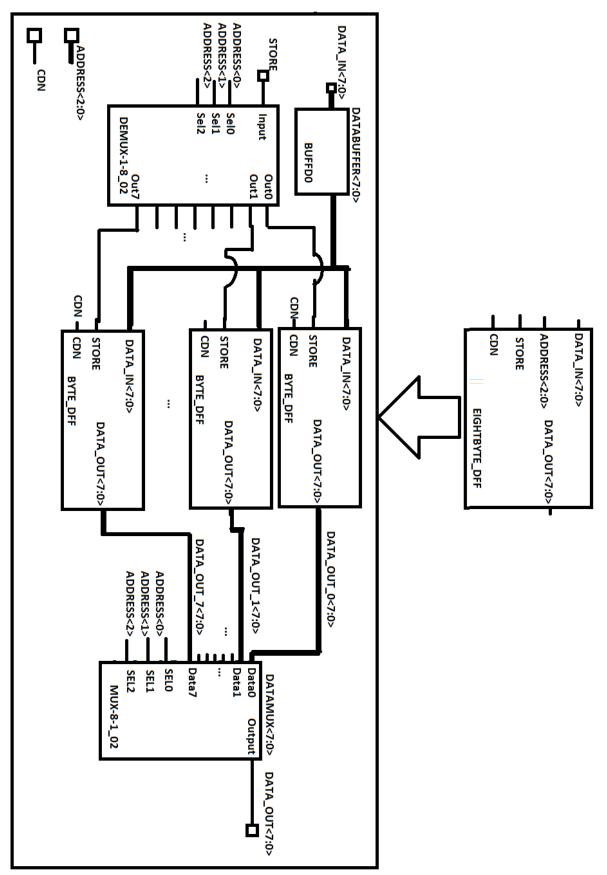

Figure 8: The EIGHTBYTE\_DFF cell.

Figure 8 shows the EIGHTBYTE\_DFF cell (in the design it is named EIGHTBYTE\_REFDFF\_02 for the reference D-Flip-Flop and EIGHTBYTE\_KHANDFF\_01 for the C2MOS D-Flip-Flop). The cell contains 8 cells of the kind BYTE\_DFF, for a total of 8 bytes or 64 bits/flip flops. The input data bus is buffered because the 8 D-Flip-Flop cells connected to each wire (see figure 9) present a significant load capacitance.

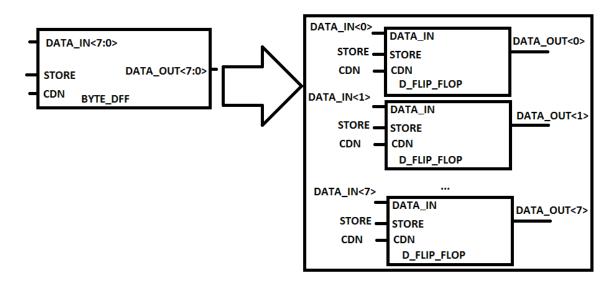

#### Figure 9: The BYTE\_DFF cell.

Figure 9 Shows the BYTE\_DFF cell. It contains a full byte made up of 8 D\_FLIP\_FLOP cells. The cells may be any kind of D-Flip-Flop. The C2MOS flip flop takes a STORE\_N (negated STORE) as input, meaning area and power could be saved by using negating demultiplexers and inverters at the last stage of demultiplexing to produce the two complementary signals, as negating demultiplexers use fewer transistors. This was not done in the design and the complementary signal is generated inside the flip flop cell itself.

# 5.2.3 The reference D-Flip-Flop (REFDFF, DFCNQD1)

The reference D-Flip-Flop is a positive edge triggered D-Flip-Flop from a standard cell library provided by TSMC for the TSMC18G process. The cell is referred to as REFDFF in the report, and in the standard cell library it is called DFCNQD1.

# 5.2.4 The C2MOS D-Flip-Flop (KHAN\_DFF, D\_FLIP\_FLOP\_KHAN\_01)

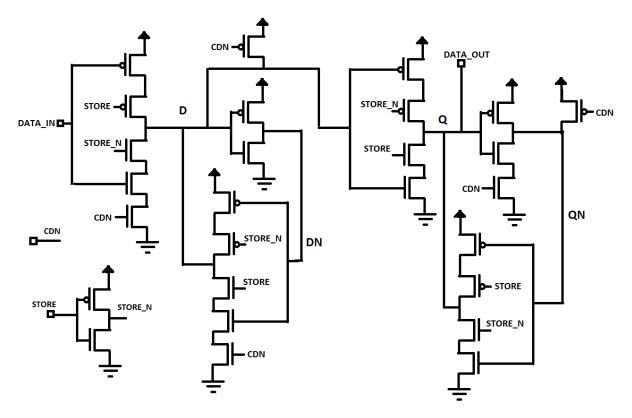

Many alternative flip flop designs were taken from [8], including the C2MOS flip flop. Most of the designs proved to be non-functional when simulated, or they consumed extreme amounts of power when simulated in a 180nm technology. The schematic presented in [8] for the C2MOS flip flop was erroneous, leading to a large amount of design time wasted when implementing the flip flop. The correct version of the C2MOS D-Flip-Flop was adapted from [9].

The C2MOS flip flop is a much bigger D-Flip-Flop than the reference D-Flip-Flop. There were two reasons for choosing this design over a smaller D-Flip-Flop. The first reason is that it does not utilize any pass transistor logic. Pass transistors introduce degraded logic which increase short circuit

power (see section 4.7). The second reason is the fact that the paths from VDD to GND in the cell often have a lot of transistors in series, increasing the effective length of transistors from VDD to GND, reducing leakage currents. The cell is referred to as either C2MOS or KHAN\_DFF in the report, and in the design it is named D\_FLIP\_FLOP\_KHAN\_01.

Figure 10: The C2MOS Flip Flop (D\_FLIP\_FLOP\_KHAN\_01 / KHAN\_DFF).

#### 5.2.4.1 Transistor sizing

In this section, please refer to figure 10. The lengths of all the transistors are 550nm. This is chosen because of the results presented in figure 3. The widths of all the transistors are 550nm, with the exception of the PMOS transistors whose gate is connected to CDN. The width of all the non-reset (CDN) transistors are set to a width of 550nm. The widths of the reset (CDN) PMOS transistors are set to 800nm, simply to have a greater drive strength than the inverters driving the inner nodes D and QN.

The reason behind the seemingly arbitrary choice of widths for the KHAN\_DFF is the disruption of the design phase caused by errors in [8], as explained in section 5.2.4.

## 5.3 The 6T-SRAM memory system

The 6T-SRAM memory system requires an entirely different peripheral circuit. The functionality of the 6T-SRAM is very different from a D-Flip-Flop, for more information, please see section 4.3.1.

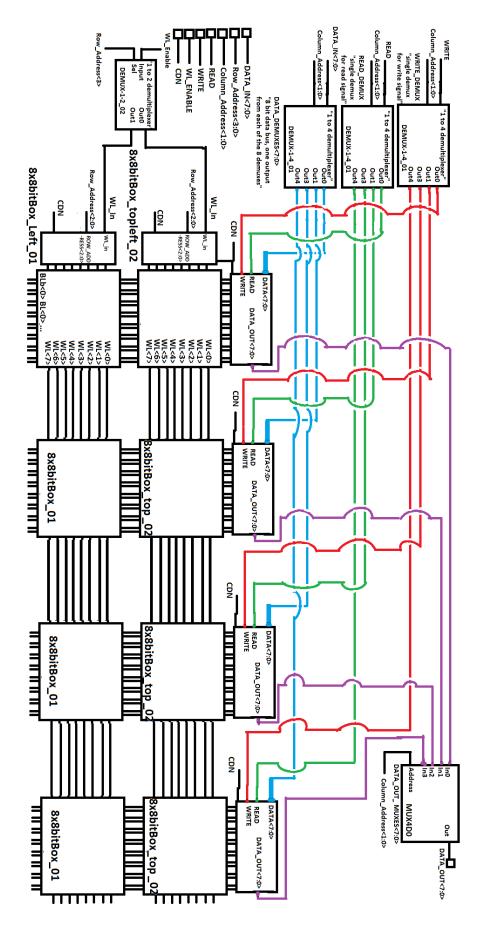

Figure 11: The SRAM6T\_64B\_02 cell

Figure 11 shows a fully built 64 Byte 6T-SRAM memory system. This 64-Byte system is the same as the one simulated in this report. All versions of the 8x8bitBox cell contain 8 rows and 8 bit-line pairs, for a total of 64 bits, or 8 bytes each. Scaling up further would simply mean adding more 8x8bitBox cells (and the appropriate border versions of the 8xbitBox cell) and adding the necessary demultiplexers, multiplexers and buffers. If one were to add two more rows of 8x8bitBox\_01 (and the appropriate border versions of the 8x8bitBox cell), a full 32x32bitBox chunk would be completed, containing a total of 128 Bytes. The 8x8bitBox\_01 cells are explained in section 5.3.2.

# 5.3.1 Read and write operations

## Input signal descriptions:

- *Col\_address*: A binary number which decides column in the memory to read from or write to.

- Row\_address: A binary number which decides which row in the memory to read from or write to. Row\_address in combination with Col\_address forms a complete address of a single byte in the memory.

- Data: An 8bit/1byte binary number, which is stored in the memory upon a write instruction execution.

- *WL\_enable* when *WL\_enable* is high, the pass transistors of all SRAM cells in a row decided by the *Row\_address* bus are opened, exposing the SRAM cells to the bit lines.

- CDN Clear Data Negative. When CDN is low, all 6T-SRAM cells are reset to the value '0'

- Read and write: read and write form a 2-bit instruction code-word which apply to all eight bit-line pairs in a single column, decided by the *Col\_address* bus. The decoded functions are described in the following table:

| Read | Write | Decoded instruction                                                                                                       |  |  |

|------|-------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| 0    | 0     | t lines disconnected from VDD and VSS.                                                                                    |  |  |

| 0    | 1     | Vrite - Charge one bit line (VDD), discharge the other bit line (VSS) according to the appropriate bit on the 'data' bus. |  |  |

| 1    | 0     | Read - Bit lines disconnected from VDD and VSS, activate sense amplifier.                                                 |  |  |

| 1    | 1     | Precharge – charge both bit lines (VDD).                                                                                  |  |  |

Table 2: Instructions decoded from the read | write code-word.

#### **Read operation:**

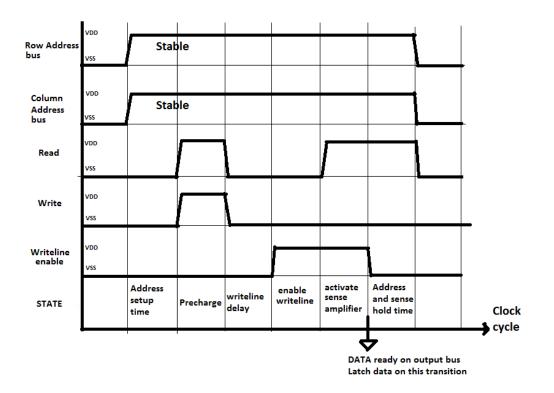

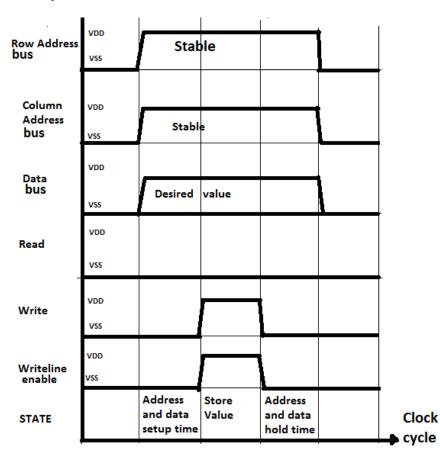

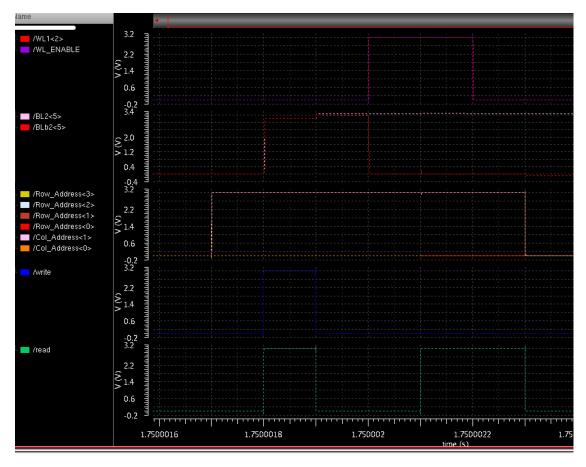

#### Figure 12: A waveform showing a standard read operation in the 6T-SRAM memory system

Figure 12 shows a waveform explaining how to perform a read operation in the 6T-SRAM system implemented in this report. The associated states of a yet-to-be-implemented state machine is also included in the waveform. The address setup time is needed to prevent non-intended bit line pairs from being charged when the precharge happens. The address and sense hold time is needed to prevent the data from being corrupted while it is being latched onto the output bus.

#### Write operation:

Figure 13: A waveform showing a standard write operation in the 6T-SRAM memory system.

Figure 13 shows a waveform explaining how to perform a write operation in the 6T-SRAM system implemented in this report. The associated states of a yet-to-be-implemented state machine is also included in the waveform. The address and data setup time is needed to prevent non-intended bit line pairs from being charged. The address hold time is needed to prevent other cells from being written to when the Writeline enable signal is still high. The data hold time is to prevent the cell's value from changing before the writeline enable signal goes low.

## 5.3.2 Sub-Cells

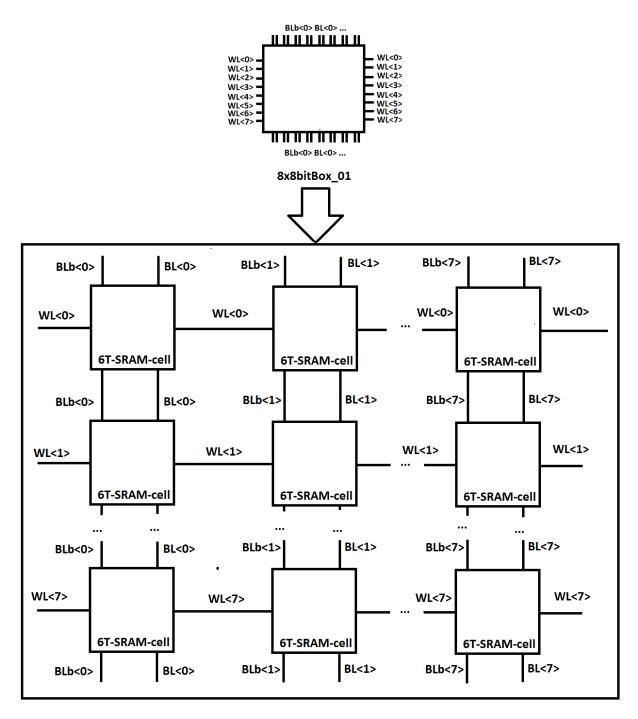

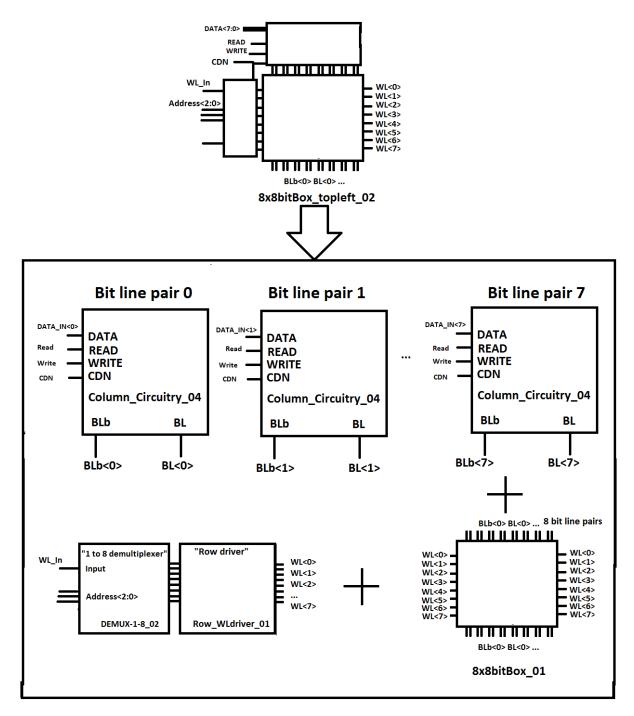

In order to simplify the process of expanding the 6T-SRAM system, a modular 'chunk' system was devised. In this system, chunks of 8x8 SRAM cells are lumped together in a block named 8x8bitBox\_01, for a total of 8 Bytes, where each row is a single byte. Each 8x8bitBox\_01 chunk is designed so that the designer can connect chunks together either vertically or horizontally by connecting the appropriate bit lines or write lines, respectively. The system is designed so that cells on the top or left edge of the cell array have either column circuitry, row circuitry or both built into the cells themselves. The advantage of this is that once a cell array becomes so big that adding individual row or column circuitry becomes tedious, bigger chunks can be created from the smaller ones and the same process of connecting together chunks can be utilized to cut down design time to a minimum. The following figures will explain the various modules in detail.

Figure 14: The 8x8bitBox\_01 cell

Figure 14 shows a symbol representing the 8x8bitBox\_01 cell as well as its expanded view showing the structure of 6T-SRAM cells within the cell.

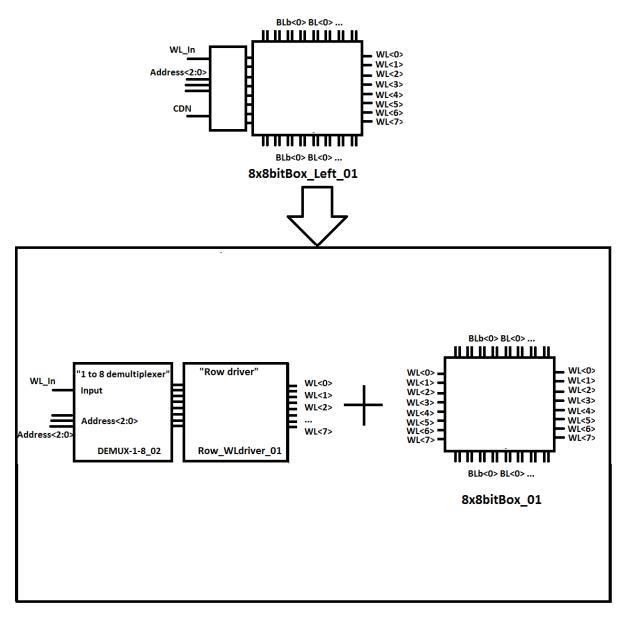

Figure 15 Shows the 8x8bitBox\_Left\_01 cell, which is a standard 8x8bitBox\_01 cell with added row circuitry to the left of the cell. The row circuitry consists of a 1 to 8 demultiplexer, also called a row decoder, and a row driver which drives one of the 8 write lines according to input from the demultiplexer.

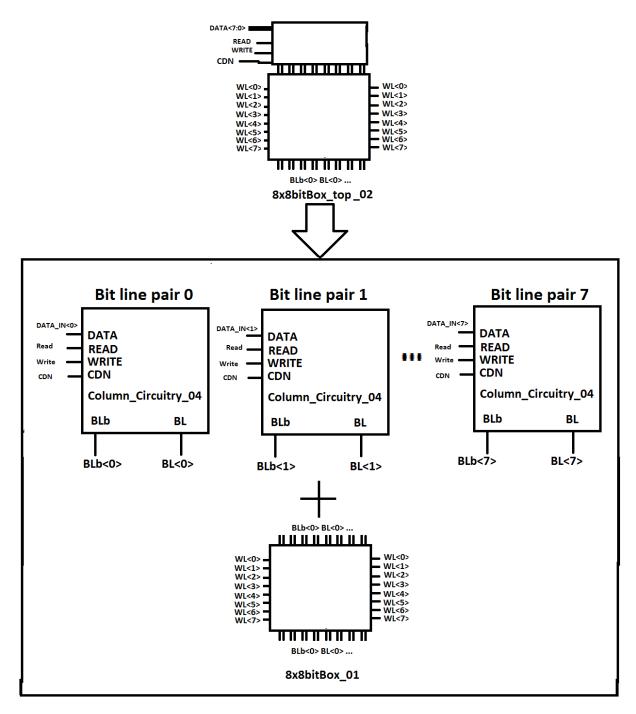

Figure 16: The 8x8bitBox\_top\_02 cell.

Figure 16 shows the 8x8bitBox\_Top\_01 cell which is a standard 8x8bitBox\_Top\_01 cell with added column circuitry for each pair of bit lines. Because a whole row of 8 bits/cells, or a single byte, is always written or read at the same time, no multiplexing is required in this cell.

Figure 17: The 8x8bitBox\_topleft\_02 cell.

Figure 17 shows the 8x8bitBox\_TopLeft\_01 cell which is a standard 8x8bitBox\_Top\_01 cell with both column circuitry and row circuitry. The necessity of this block comes from the fact that the upper left corner cell needs both column and row circuitry.

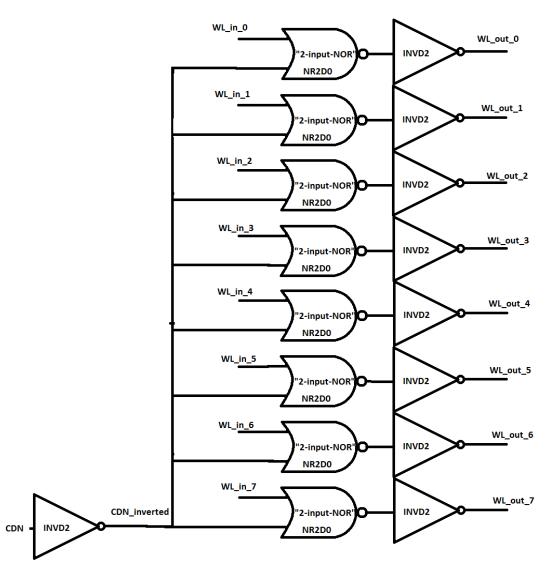

## 5.3.3 Row driver circuit

The row driver's function is to drive the write lines when activated by the row decoder. The write lines are connected to the gates of the pass transistors that connect the 6T-SRAM cells to the bit lines. As there may be a lot of pass transistors on every row, a line driver is required to adequately charge the accumulated gate and wire capacitance. In this implementation, a driver strength level of 2 (see section 4.5) is considered more than sufficient, and may be sufficient for much larger memory arrays.

Figure 18: The Row\_WLDriver\_01 cell used in the 6T-SRAM system

Figure 18 shows the Row driver cell. The row driver cell drives eight rows/write lines.

| CDN | WL_in_x | WL_out_x |

|-----|---------|----------|

| 0   | x       | 1        |

| 1   | 0       | 0        |

| 1   | 1       | 1        |

Table 3: The truth table for the Row\_WLDriver\_01 cell.

Table 3 shows the truth table for the row driver cell. WL\_in\_x means WL\_in\_0, WL\_in\_1, WL\_in\_2, and so on. The logic value 'X' means 'don't care'.

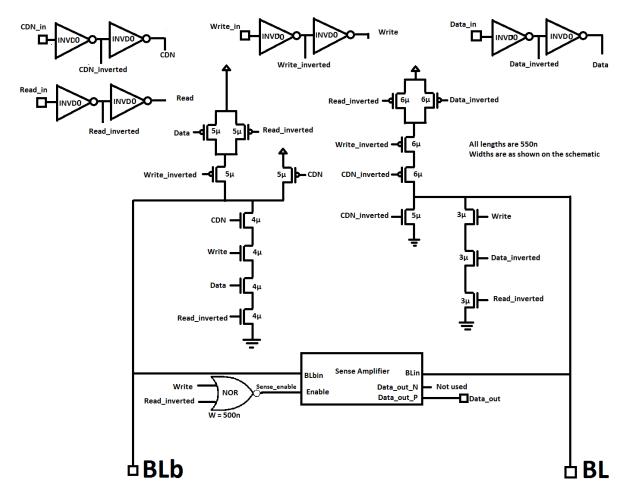

## 5.3.4 Bit line driver circuitry

A custom transistor-level logic circuit was created for the purpose of driving the bit lines. There were three reasons for choosing a custom design over using standard logic gates. The first reason for choosing a custom design is that the high capacitance bit lines need to charge or discharge quickly, requiring transistors with a high driver strength. A custom design would allow the designer to accurately control the driver strength of the circuit. Another problem with the standard gate solution was that uneven timing in the logic connected to the bit-line driving transistors lead to considerable power consumption as a result of glitches. The custom circuit was designed with the purpose of minimizing glitches during standard read or write operations. The third problem was that the input to the bit lines require tri-state logic, as the bit lines are cut off from the circuit when the column is not being read from or written to. When tri-state logic is needed, the standard logic gate solution has to be supplemented by pass transistors, and the added design time means the designer might as well do a custom design to suit his/her needs. Because the driver transistors have a large gate width, which leads to higher gate capacitance of the circuit.

*Figure 19: The Column\_Circuitry\_04 cell, or bit line pair driver.*

Figure 19 shows the bit line pair driver circuit used in the 6T-SRAM system. The bit line pair driver drives a single pair of bit lines. The signals CDN, CDN\_inverted, Write, Write\_inverted, Data, Data\_inverted, Read and Read\_inverted are all internal signals used to ensure the functionality of the circuit. Sense\_enable is an internal signal derived from the Write signal and the Read\_inverted

signal, and is used to enable the sense amplifier. The Read\_in, Write\_in and Data\_in signals are all demultiplexed onto the appropriate column, and all bit line pair drivers in one column share the same signals. Refer to table 4 for the functionality of the circuit.

| CDN | Read_in | Write_in | Data_in | BLb | BL | Sense_enable |

|-----|---------|----------|---------|-----|----|--------------|

| 0   | Х       | Х        | Х       | 1   | 0  | Х            |

| 1   | 0       | 0        | Х       | Z   | Z  | 0            |

| 1   | 0       | 1        | 0       | 1   | 0  | 0            |

| 1   | 0       | 1        | 1       | 0   | 1  | 0            |

| 1   | 1       | 0        | Х       | Z   | Z  | 1            |

| 1   | 1       | 1        | Х       | 1   | 1  | 0            |

Table 4:The truth table for the Column\_Circuitry\_04 cell.

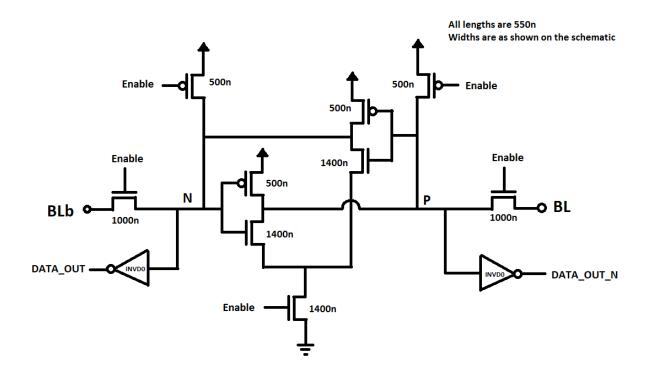

### 5.3.5 Sense amplifier

As the length of the bit lines increases, the capacitance to ground seen from the column circuitry increases. The driver strength of the 6T-SRAM cell is low compared to the driver strength required to rapidly discharge one of the bit lines during a read. A read erases the value in the SRAM cell, and a rewrite is always necessary after a write. Fully discharging one of the bit lines is necessary in order to rewrite to a cell after a read, and discharging quickly is essential to avoid a large short-circuit power consumption on the measuring cells (usually a buffering inverter) caused by degraded logic (see section 4.7). The purpose of a sense amplifier is to detect any slight difference in voltages on two nodes and amplify that difference to non-degraded voltage levels. In this design a variation of the Full Complementary Positive Feedback Sense Amplifier (FCPFSA) is designed. This kind of sense amplifier has the added functionality of automatically performing a rewrite whenever a read is performed.

Figure 20: The sense amplifier used in the SRAM system.

The designed sense amplifier operates as follows: When the sense amplifier is not active, nodes N and P are precharged to the VDD voltage level and the inverters in the inverter loop are disconnected from ground. Immediately after enable goes high, nodes N and P are both disconnected from the power supply and are connected instead to the negative and positive bit lines, respectively. The inverter loop is enabled by connecting the inverters to ground. The charge stored on nodes N and P will initially be equal, but the inherent instability caused by the inverter loop will allow any slight difference in voltage on the nodes (from the bit lines, through the pass transistors), to cause a quick discharge of one of the nodes. The difference in voltage needed on the bit lines is not known, but a reasonable assumption is that a 200mV difference will ensure that noise or the offset in the physical implementation will not cause an error during the read. Wide NMOS transistors are required to quickly discharge the node, and in turn speed up the discharging of the bit line. The cell is designed so that both nodes N and P will have an identical capacitance to ground, requiring a dummy-inverter on the P node. For a 64 Byte memory, which was simulated, a sense amplifier is not necessary as the SRAM cell itself discharges the bit lines rapidly. The sense amplifier was included in order to more accurately predict the power consumption and leakage current of larger cell arrays. The width of the NMOS transistors were arbitrarily chosen to be either 1400n and 1000n, and their widths must be increased when moving to very large memory cell arrays.

#### 5.3.6 6T-SRAM-Cell

Figure 21: The 6T SRAM cell.

#### 5.3.6.1 Transistor sizing

For this section, please see figure 21. The transistor dimensions were chosen as follows: The length of the NMOS transistors were designed to have a minimum leakage current as decided by the simulations in section 5.1.2. A length of L = 550nm is chosen for all transistors. As a typical layout of an SRAM cell is symmetrical, one can reduce the area of each cell by choosing the width and length of the PMOS transistors to be equal to the length and width of the NMOS transistors (see section 5.1.2). A minimum length of 300nm was chosen.

*Read stability:* In the case of a read, both bit lines are precharged up to the VDD voltage and subsequently the pass transistors are opened up to discharge one of the bit lines depending on the value retained in the cell. In the case of a logic '0' retained, the transistor D0 will discharge the bit line BL down to ground. When this happens, it is important that the voltage on node1 does not exceed Vth when current is intermittently flowing through transistors P1 and D0, which could invert the voltage of node0. Intuitively, this means that transistor D0 should be less resistive than transistor P1, and enough so that the node1 voltage never exceeds Vth. This means the width of D0 has to be larger than the width of P1. According to [10], the width of D0 has to be 1.2 times as large as the width of P1. The same goes for transistors D1 and P0.

*Write stability*: In the case of a write, the bit lines are forced to either BLb = 0V and BL = VDD or the opposite, depending on value written. In the case of a logic '0' being stored, BL is pulled low by external column circuitry and the pass transistors are opened. In this case it is important that the voltage on node1 never exceeds Vth when current is intermittently flowing through transistors U0 and P1. Intuitively, this means that P1 should be less resistive than U0, and enough so that the node1 voltage never exceeds Vth. This means that the width of P1 should be larger than the half the width of U0, owing to the mobility of a PMOS transistor being about half of the mobility of an NMOS transistor. According to [10], the width of P1 has to be at least larger than 0.56 than that of U0.

Choosing U0 and U1 to be the same size as D0 and D1 meets the requirements of read and write stability, and simplifies the layout through symmetry (see section 5.1.2).

| Transistor name | U0 and U1 | D0 and D1 | PO and P1 |

|-----------------|-----------|-----------|-----------|

| Width [nm]      | 360       | 360       | 300       |

| Length [nm]     | 550       | 550       | 550       |

Table 5: Transistor sizes for the 6T SRAM cell

#### 5.3.7 Reset circuitry

The reset signal CDN needs only be considered in the peripheral circuitry. To reset the SRAM, WL is set to 1, BL is set to 0, and BLb is set to 1. Because BL, BLb and WL are shared among a lot of SRAM cells, the amount of transistors per cell used for resetting the memory is very low. The column reset circuitry is implemented as a part of the column logic, specifically as part of the bit line pair driver. The row reset circuitry was implemented as a part of the row driver circuit.

## 5.4 Extrapolator

#### 5.4.1 The gate count unit of measurement

As per the TSMC datasheet, one gate is equivalent to 4 transistors with a width of  $0.85\mu$ m and a length of 300nm, for a total area of 0.68 pm<sup>2</sup> per gate count. The gate count of custom transistor

level designs was decided by dividing the area of the design by this value, and rounding to the nearest half integer.

$$Gate \ Count = \frac{Cell \ Area \ [m^2]}{0.68 * 10^{-12} \ [m^2]}$$

Formula 5: The formula for normalizing a cell's area to the gate count unit of measurement

5.4.2 Predicting the gate count and leakage current of the memory systems In order to predict the gate count (area) of the peripheral circuitry, various mathematical methods were used and a few assumptions were made:

- 1) Beyond 64 Bytes any multiplexing or demultiplexing will be done only with 1-2 demultiplexers or 2-1 multiplexers.

- 2) The additional wires that are required on the address bus as the memory expands will not be buffered. This would lead to even more complicated mathematics.

- 3) Because cells are separated horizontally by a large gate-source and gate-drain impedance (almost no current passes through the gate of the transistor), total leakage current in a bigger cell can be modelled as a sum of leakage currents through the smaller cells contained in the bigger cell.

The leakage currents of bottom-level custom-designed cells were determined by simulating their total leak in the 64-Byte system and then dividing by the number of custom-designed cells in the 64-Byte design.

For the C2MOS (KHAN\_DFF) D-Flip-Flop, the leakage contribution from the cells have to be multiplied by 1.54. For details see section 5.6.3 and appendix A.

## 5.4.3 Predicting the read and write energy of the memory systems

In order to predict the read and write energy of the increasingly complex peripheral circuitry, a severe simplification is made. It is assumed that the read and write energy consumed by the peripheral circuitry is proportional to the total gate count of the peripheral circuitry. Then, the results from the 64Byte simulations could simply be multiplied by the ratio of increase in the gate count of the peripheral circuitry. Another assumption is that the read and write energy of the cell array does not increase significantly when the cell array is expanded, as only a single byte of 8 cells is written to or read from at the same time.

$E_{predicted} = \frac{Gate \ count_{predicted, peripheral}}{Gate \ count_{64Byte, peripheral}} * E_{64Byte, peripheral} + E_{64Byte, cells}$

Formula 6: Extrapolated read and write energies, based on the 64 Byte simulations.

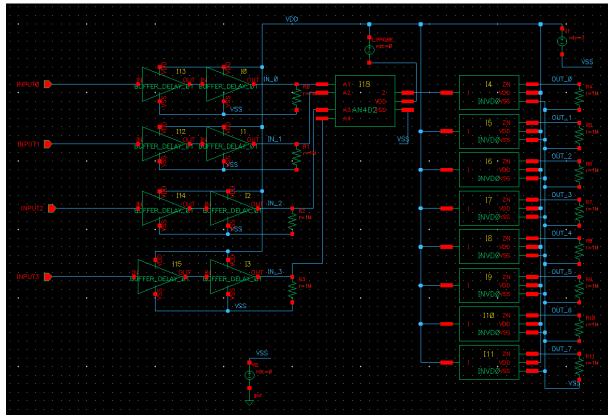

# 5.4.4 Measuring average leakage current of standard cells

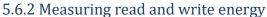

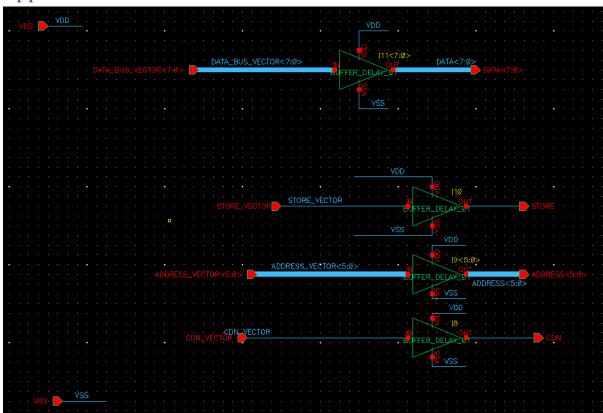

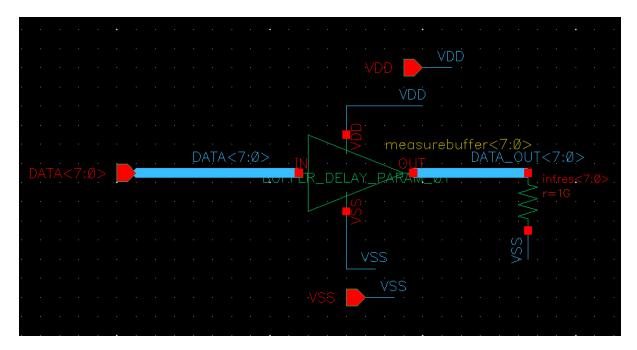

Figure 22: The testbench for measuring the average leakage current of standard cells

In order to measure the average leakage current of several standard cells used in the design of the peripheral circuits, a simple testbench was designed. In figure 22, the testbench is displayed, and the cell being measured is the AN4D2 standard cell.

A test stimulus covering all the different combinations of inputs was applied. After applying a certain combination of inputs, the cell would be left idle for a sufficient amount of time (here: 0.5s) in order to stabilize the internal voltages of the cell. After stabilizing the cell, the supply current going to the cell was measured over a short period of time (200ns) and averaged. After measuring the leakage current of every combination of inputs, the arithmetic mean of all the leakage currents was calculated. This average leakage current was used as a representative value for the leakage of the cell.

Figure 23: The testbench used to measure average leakage currents in the cells which make up the peripheral circuitry.

| Cell name | Gate Count | Leakage current [A] |

|-----------|------------|---------------------|

| INVD0     | 0.5        | 5.0E-14             |

| INVD2     | 1          | 1.9E-13             |

| INVD4     | 2          | 3.9E-13             |

| NR2D0     | 1          | 5.5E-14             |

| NR2D2     | 2          | 2.09E-13            |

| AN2D0     | 1.5        | 1.18E-13            |

| AN2D2     | 2          | 3.68E-13            |

| MUX2D0    | 3          | 1.74E-13            |

| MUX4D0    | 6.5        | 3.61E-13            |

| AN4D0     | 2.5        | 1.13E-13            |

| AN4D2     | 3          | 3.83E-13            |

| BUFFD0    | 1          | 1.0E-13             |

| BUFFD2    | 1.5        | 2.86E-13            |

5.4.5 Table of the cells' leakage current and gate count

Table 6: Simulated leakage currents of various TSMC standard cells and the gate counts as specified in the TSMC standard cell datasheet

Table 6 Shows the simulated leakage current of various TSMC standard cells and the gate counts as specified in the TSMC standard cell datasheet. The simulations of leakage currents were performed by the author of this report on the grounds that the results in the datasheet provided by TSMC were admitted to be wrong. The leakage currents were simulated at with a supply voltage of 3V, in the default process corner and at a temperature of 70 degrees Celsius. 5.0E-14 is the same as 5.0 \* 10<sup>-14</sup>.

| Cell Name                   | Gate Count | Leakage Current |

|-----------------------------|------------|-----------------|

| DEMUX-1-2_02                | 4.5        | 6.27E-13        |

| DEMUX-1-4_01                | 13.5       | 1.88E-12        |

| DEMUX-1-8_02                | 21.5       | 1.05E-12        |

| Column circuitry (including | 65         | 9.9E-13         |

| sense amplifier)            |            |                 |

| Row_WLDriver                | 17         | 2.15E-12        |

| MUX-8-1_02                  | 16         | 8.96E-13        |

| REFDFF (DFCNQD1)            | 7          | 7.62E-13        |

| C2MOS DFF (KHANDFF)         | 12.5       | 1.05E-13        |

| SRAM6T Cell                 | 1.5        | 3.6E-14         |

Table 7: A table of calculated gate counts and leakage currents of non-standard cells

Table 7 shows the calculated and simulated leakage currents of non-standard cells designed for the purpose of this report. See appendix A for details. The cells DEMUX-1-2\_02, DEMUX-1-4\_01, DEMUX-1-8\_02, Row\_WLDriver, MUX-8-1\_02 are cells made up entirely of standard cells, the others are custom transistor-level designs. The leakage currents and gate counts of the cells made up of standard cells are calculated by taking the sum of the leakage currents and gate counts of the standard cells contained within the cell, as per table 6. The gate counts of the custom designs were calculated by dividing the area of the design by the area per gate count (see section 5.4.1). The leakage currents of the custom designs were calculated from the simulation results of the complete 64 Byte systems. Specifically, the memory cell leakage was found by dividing the total cell leakage by the amount of cells (64 \* 8 cells), and the Column circuitry was found by dividing the total column circuitry leakage with the amount of bit line pairs (4 columns \* 8 bit-line pairs per column).

5.4.6 Calculating the amount of multiplexers, demultiplexers and buffers

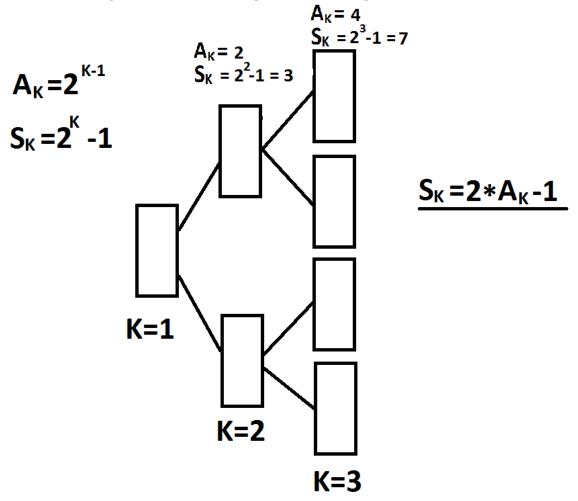

#### Figure 24: A simplified solution of the sum of a geometric row $2^{N-1}$

Figure 24 shows a simple equation for determining the sum of elements in any construct where elements double every iteration.  $A_k$  is the amount of elements in the Kth row.  $S_k$  is the sum of all elements in the row up until the Kth row. See [11] for details on row theory. This applies to constructs such as a demultiplexing or multiplexing circuit consisting only of 1-2 demultiplexers or 2-1 multiplexers. This also applies to the specific buffer fan-outs assumed in this design, where every buffer drives the input of two other buffers. In order to find the sum of elements, one needs only count the amount of elements in the final stage of the fan-out, double that number and subtract one.

In order to simplify the calculations of buffer and multiplexer/demultiplexer fan-outs, the existing 64-Byte memory was assumed to be an atomic cell (indivisible, foundation cell), and all further expansion of the memory system would happen through simple doubling fan-outs as shown in figure 24.

| 1                            |                             |                               |

|------------------------------|-----------------------------|-------------------------------|

| Cell name                    | Amount in the SRAM system   | Amount in the DFF system      |

| SRAM6T                       | Col * Row * 8               | 0                             |

| Row_WLDriver                 | Row / 8                     | 0                             |

| Column circuitry + sense amp | Col * 8                     | 0                             |

| DEMUX-1-2                    | 2*(Col /4 – 1) + Row/8 - 1  | Bytes/64 - 1                  |

| DEMUX-1-4                    | Col / 2                     | 0                             |

| DEMUX-1-8                    | Row / 8                     | (1.125/8) * Bytes             |

| BUFFD0                       | 8*(Col/2) + 8 * (Col/4-1) + | (1/8 + 1/64) * Bytes + 1/64 * |

|                              | Row/8 - 1                   | Bytes + 9 * (Bytes/64 -1)     |

| MUX2D0                       | 8* (Col/4 – 1)              | Bytes/64 - 1                  |

| MUX4D0                       | 8*(Col/4)                   | 0                             |

| MUX-8-1                      | 0                           | 8*(1/8 + 1/64) * Bytes        |

| D-Flip-Flops                 | 0                           | Bytes * 8                     |

| 5.4.7 Table of cell count predic | ction formulas |

|----------------------------------|----------------|

|----------------------------------|----------------|

Table 8: The formulas for calculating the number of cells contained within either a D-flip-flop memory system or a 6T-SRAM memory system.

Table 8 shows the formulas used for calculating the number of cells in the D-Flip-Flop and 6T-SRAM memory systems. The 'Row' variable is the amount of rows in the SRAM system, which is the same as the amount of write lines. The 'Col' variable is the amount of columns in the SRAM system, which is the same as the total amount of pairs of bit lines divided by 8. The 'Bytes' variable is the amount of bytes in the D-Flip-Flop system, which is the same as the amount of D-Flip-Flops divided by 8. The values were calculated by taking advantage of the hierarchical structure of the design, as well as taking advantage of the multiplexers, demultiplexers and buffers forming a geometric row as described in section 5.4.6. When calculating the amount of rows and columns per byte of memory, a ratio of 4 rows per column was assumed, and the resulting formulas are applied:

$$Columns = \sqrt{\frac{Bytes}{4}}, \quad Rows = \sqrt{\frac{Bytes}{4}} * 4$$

Formula 7: Calculation of the amount of rows and columns as a function of the number of bytes.

## 5.5 Miscellaneous non-standard cell schematics

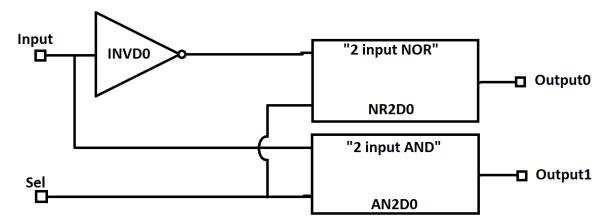

Figure 25: The DEMUX-1-2\_02 cell.

| Input | Sel | Output0 | Output1 |

|-------|-----|---------|---------|

| 0     | Х   | 0       | 0       |

| 1     | 0   | 1       | 0       |

| 1     | 1   | 0       | 1       |

Table 9: The truth table for the DEMUX-1-2\_02 cell

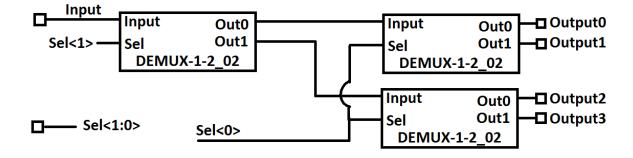

Figure 26: The DEMUX-1-4\_01 cell.

| Input | Sel<1> | Sel<0> | Output3 | Output2 | Output1 | Output0 |

|-------|--------|--------|---------|---------|---------|---------|

| 0     | Х      | Х      | 0       | 0       | 0       | 0       |

| 1     | 0      | 0      | 0       | 0       | 0       | 1       |

| 1     | 0      | 1      | 0       | 0       | 1       | 0       |

| 1     | 1      | 0      | 0       | 1       | 0       | 0       |

| 1     | 1      | 1      | 1       | 0       | 0       | 0       |

Table 10: The corresponding truth table for the DEMUX-1-4\_01 cell.

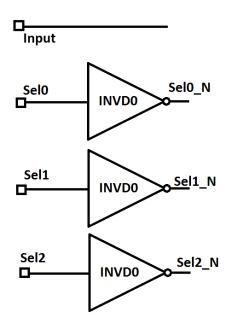

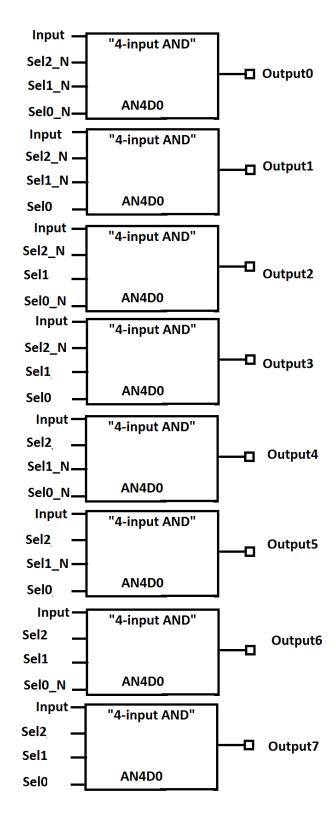

Figure 27: The DEMUX-1-8\_02 Cell.

| Input | Sel2 | Sel1 | Sel0 | Out7 | Out6 | Out5 | Out4 | Out3 | Out2 | Out1 | Out0 |

|-------|------|------|------|------|------|------|------|------|------|------|------|

| 0     | Х    | Х    | Х    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 1     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    |

| 1     | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    |

| 1     | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    |

| 1     | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0    |

| 1     | 1    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0    |

| 1     | 1    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    |

| 1     | 1    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0    |

| 1     | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

Table 11: The truth table corresponding to the DEMUX\_1-8\_02 cell.

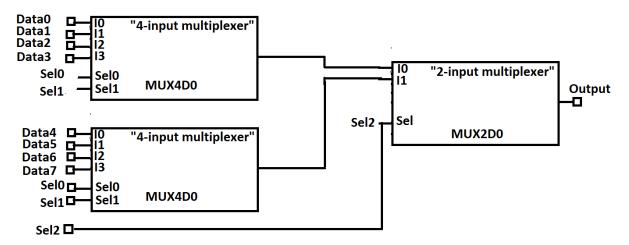

#### Figure 28: The MUX\_8-1\_02 cell

| Sel2 | Sel1 | Sel0 | Output |

|------|------|------|--------|

| 0    | 0    | 0    | Data0  |

| 0    | 0    | 1    | Data1  |

| 0    | 1    | 0    | Data2  |

| 0    | 1    | 1    | Data3  |

| 1    | 0    | 0    | Data4  |

| 1    | 0    | 1    | Data5  |

| 1    | 1    | 0    | Data6  |

| 1    | 1    | 1    | Data7  |

Table 12: The truth table corresponding to the MUX\_8-1\_02 cell

# 5.6 Method of simulation

#### 5.6.1 Simulator

Simulator version: Cadence Virtuoso Spectre Simulator 13.1.1.117.isr8 64bit

#### Virtuoso version: IC6.1.6-64b.500.12

#### **Simulation parameters**

| Simulation parameter      | Setting or value  |  |

|---------------------------|-------------------|--|

| Gmin                      | 10 <sup>-17</sup> |  |

| Gear2only                 | Turned on         |  |

| Error preset (err preset) | Moderate          |  |

Table 13: The non-default simulator settings used in all simulations.

Table 13 shows a selection of simulation parameters that were modified for the purpose of measuring leakage current. All other simulation parameters were set to the default values.

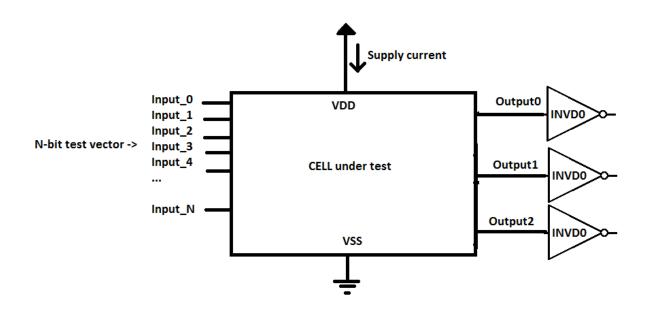

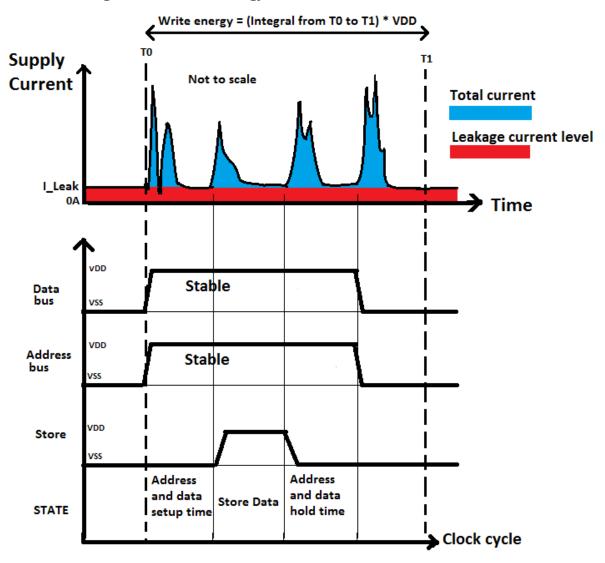

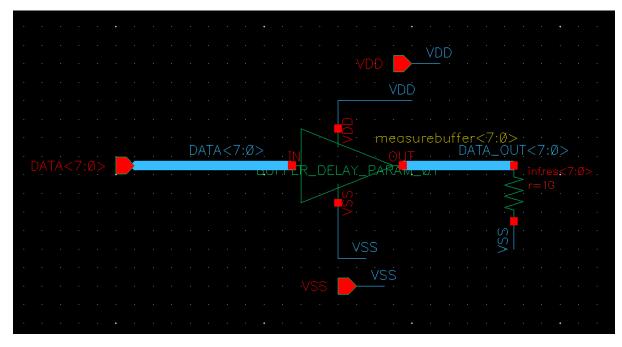

Figure 29: An example showing the calculation of the energy spent during a D-Flip-Flop system write operation.

Figure 29 shows a write operation for the D-Flip-Flop system (bottom graph) along with an example graph (top graph) of the combined supply current for the entire system. The supply current in the simulations is much lower than what the graph implies. The energy is calculated by using the following formula:

$$E = VDD * \int_{T0}^{T1} i(t) dt$$

Formula 8: Energy (E) as a function of supply current (i(t))

Formula 8 shows the calculation of the energy of an operation. The operation could be either read or write, performed on any of the memory systems presented in this report. T0 would always be the time of the first signal change (usually the address and data bus signals) during an operation. T1

would always be exactly one clock cycle after the last signal change during an operation, and the system would be Idle during that last clock cycle. A static supply voltage is assumed.

Earlier calculations subtracted the integral of the supply current level, but the contribution of leakage currents during a read or write was discovered to be negligible when measuring read and write energies. In the simulations, the leakage current was in the order of magnitude less than 10<sup>-3</sup> of the active read and write induced currents. Another problem with subtracting the contribution of leakage currents is that leakage current is only defined in a static system, and therefore its contribution is unknown during a read or write.

## 5.6.3 Determining the worst case initial memory state

## 5.6.3.1 D-flip-flops

To determine the worst case state of the memory array when examining leakage currents, three cases were simulated on an 8-byte memory circuit using the reference D-flip-flop (REFDFF).

When using the REFDFF flip-flop, having all zeros stored in the memory maximized the leakage current.

When using the C2MOS (KHAN\_DFF) flip-flop, having all ones stored in the memory meant the leakage current from the cells was 1.54 times higher than the leakage current from the cells when having all zeros stored in the memory. Due to the extremely long simulation time required to fill the memory with ones, this result will not influence the simulations run and the higher leakage current has to be considered in the prediction calculations instead.

The read and write energies were the highest when writing all ones to a byte containing all zeros, for both flip flops.

See appendix A for details on the memory state simulations.

#### 5.6.3.2 SRAM

As the SRAM cells are symmetrical, the effect of the memory state on leakage characteristics and read and write energy is assumed to be negligible. A '11111111' is chosen to be written to a byte containing '00000000', and the same byte is read.

#### 5.6.4 64 Byte D-Flip-Flop simulation setup