### NUTS Backplane Revision

Improving Reliability and Modularity of the NTNU Test Satellite

### Stian Haug

Master of Science in ElectronicsSubmission date:July 2016Supervisor:Bjørn B. Larsen, IETCo-supervisor:Roger Birkeland, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

### Abstract

This paper details the process of reviewing and updating the backplane circuit board of the test satellite designed at NTNU. It covers introductory theory on the subject, a complete review of the current design, proposed updates and a schematic implementation of proposed updates to the backplane system. A brief discussion and a conclusion on how the system has been successfully improved and simplified is presented.

## Contents

| A        | bstra | nct          |                                                     | 1  |

|----------|-------|--------------|-----------------------------------------------------|----|

| Li       | st of | Figur        | es                                                  | 7  |

| Li       | st of | <b>Table</b> | S                                                   | 9  |

| A        | bbre  | viation      | IS                                                  | 11 |

| 1        | Intr  | oducti       | ion                                                 | 13 |

|          | 1.1   | Summ         | ary                                                 | 13 |

|          | 1.2   | Summ         | ary - Norwegian                                     | 14 |

|          | 1.3   | Proble       | em description                                      | 15 |

|          | 1.4   | NUTS         | •                                                   | 16 |

| <b>2</b> | Pre   | vious o      | development and relevant theory                     | 19 |

|          | 2.1   | NUTS         | satellite overview                                  | 19 |

|          |       | 2.1.1        | Backplane                                           | 20 |

|          |       | 2.1.2        | OBC - On Board Controller                           | 20 |

|          |       | 2.1.3        | ADCS - Attitude Determination and Control System .  | 21 |

|          |       | 2.1.4        | EPS - Electronic Power System                       | 21 |

|          |       | 2.1.5        | Antenna module                                      | 21 |

|          |       | 2.1.6        | Payload                                             | 21 |

|          | 2.2   | Backp        | lane design considerations                          | 22 |

|          |       | 2.2.1        | Electronics in space: Radiation, vacuum and temper- |    |

|          |       |              | <i>atures</i>                                       | 22 |

|          |       | 2.2.2        | Fault isolation, detection and recovery             | 25 |

|          | 2.3   | BUS e        | evaluation                                          | 26 |

|          |       | 2.3.1        | $I^2C$ bus                                          | 26 |

|          |       | 2.3.2        | CAN bus                                             | 27 |

| 3 | Des | ign pr  | oposition                                       | 33     |

|---|-----|---------|-------------------------------------------------|--------|

|   | 3.1 | Propo   | sed backplane design                            | 33     |

|   |     | 3.1.1   | Data carrier                                    | 33     |

|   |     | 3.1.2   | Sensor network                                  | 36     |

|   |     | 3.1.3   | Power distribution                              | 38     |

|   |     | 3.1.4   | Lab access and programming                      | 41     |

|   |     | 3.1.5   | Backplane Control                               | 42     |

|   |     | 3.1.6   | Module slot requirements                        | 45     |

|   |     | 3.1.7   | Fault isolation                                 | 47     |

|   |     | 3.1.8   | Proposed design summary                         | 49     |

| 4 | Des | ign im  | plementation                                    | 51     |

|   | 4.1 | 0       | lane implementation overview                    | 51     |

|   | 4.2 | _       | carrier (implementation) $\ldots$               | 51     |

|   | 4.3 |         | distribution (implementation)                   | 52     |

|   | 4.4 |         | r network (implementation)                      | 54     |

|   | 4.5 |         | ccess and programming (implementation)          | 57     |

|   | 4.6 |         | blane Control (implementation)                  | 59     |

|   |     | 4.6.1   | CAN IO expanders                                | 59     |

|   |     | 4.6.2   | Slot state holder                               | 60     |

|   |     | 4.6.3   | Control-logic power and power cycling           | 64     |

|   |     | 4.6.4   | Module programming and inter-module programming | 65     |

|   |     | 4.6.5   | Control intervals and fault avoidance           | 68     |

|   | 4.7 |         | le slot (implementation)                        | 69     |

|   | 4.8 |         | isolation (implementation)                      | 70     |

|   |     | 4.8.1   | Fault isolation control                         | 72     |

|   | 4.9 | Propo   | sed testing methodology                         | 74     |

|   |     | 4.9.1   | What to test (functionality)                    | 74     |

|   |     | 4.9.2   | How to test (physical access)                   | 74     |

|   |     | 4.9.3   | Test bench                                      | 74     |

| 5 | Res | ults    |                                                 | 77     |

| 0 | 5.1 |         | cation of power control signals.                | 77     |

|   | 0.1 | 5.1.1   | Test A                                          | 77     |

|   |     | 5.1.2   | Test B                                          | <br>79 |

|   |     | 5.1.3   | Test C                                          | 80     |

| 6 | Dis | cussior | a                                               | 83     |

| 7 | Cor | nclusio | n                                               | 85     |

| 8 | Bib | liography                  | 87 |

|---|-----|----------------------------|----|

| 9 |     | pendix                     | 89 |

|   | 9.1 | Slot state update interval | 89 |

|   | 9.2 | Design Schematics          | 91 |

\_\_\_\_\_

## List of Figures

| 1.1  | 3D model of NUTS backplane based design                                                                        | 16 |

|------|----------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Stacked PCB versus Backplane based PCBs                                                                        | 17 |

| 2.1  | Block schematic overview of the NUTS system $\hfill \ldots \ldots \ldots$ .                                    | 19 |

| 2.2  | Overview of the backplane and modules                                                                          | 20 |

| 2.3  | TID effect on an NMOS transistor                                                                               | 23 |

| 2.4  | DD effect on a bipolar junction transistor                                                                     | 24 |

| 2.5  | SEE on an NMOS transistor caused by cosmic rays                                                                | 25 |

| 2.6  | Typical I <sup>2</sup> C bus structure $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 27 |

| 2.7  | Data transfer on the $I^2C$ bus $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                             | 28 |

| 2.8  | The layered ISO11898 standard architecture                                                                     | 28 |

| 2.9  | Typical CAN bus structure                                                                                      | 29 |

| 2.10 | Standard CAN message structure                                                                                 | 30 |

| 3.1  | Data bus using I <sup>2</sup> C structure from current design                                                  | 35 |

| 3.2  | Sensor bus using I <sup>2</sup> C from current design. $\ldots$                                                | 37 |

| 3.3  | New sensor bus design using $I^2C$                                                                             | 39 |

| 3.4  | Current power distribution in the backplane design                                                             | 40 |

| 3.5  | Current backplane houskeeping system                                                                           | 44 |

| 3.6  | Proposed new backplane houskeeping system                                                                      | 46 |

| 3.7  | Current isolation towards module slots preventing fault prop-                                                  |    |

|      | agation.                                                                                                       | 48 |

| 3.8  | Proposed new isolation towards module slots to prevent fault                                                   |    |

|      | propagation                                                                                                    | 50 |

| 4.1  | New backplane implementation overview                                                                          | 52 |

| 4.2  | New implementation of the data carrier using CAN bus                                                           | 53 |

| 4.3  | Powerdistribution implementation using E-fuses                                                                 | 55 |

| 4.4  | Sensornetwork power measurement implementation                                                                 | 56 |

| 4.5  | $I^2C$ multiplexer design $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$       | 57 |

| 4.6  | Sensornetwork module slot $I^2C$ repeater implementation | 58 |

|------|----------------------------------------------------------|----|

| 4.7  | High density connector for lab programming               | 58 |

| 4.8  | Slot controller block schematic                          | 61 |

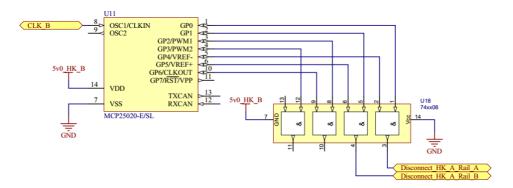

| 4.9  | Implementation of the slot controller CAN IO expanders   | 62 |

| 4.10 | Implementation of the slot controller state holders      | 63 |

| 4.11 | Housekeeping module power implementation.                | 66 |

| 4.12 | Housekeeping power control signal implementation         | 66 |

| 4.13 | Module programming block schematic                       | 67 |

| 4.14 | Inter module re-programming block schematic              | 68 |

| 4.15 | Layout of the backplane slot headers                     | 71 |

| 4.16 | $I^2C$ bus repeater for module isolation                 | 71 |

| 4.17 | JTAG bus isolation switches for module isolation         | 72 |

| 4.18 | Utility/reset signal fault isoaltion                     | 73 |

| 5.1  | Breadboard test scircuit                                 | 78 |

## List of Tables

| 4.1 | Controllable parameters of the                       | he backpl | ane. |   |       |   | • |   | • |   | • | • | 59 |

|-----|------------------------------------------------------|-----------|------|---|-------|---|---|---|---|---|---|---|----|

| 4.2 | Power states of the backplane                        | e logic . |      |   |       |   |   |   |   |   |   |   | 65 |

| 4.3 | Slot control signal fault conse                      | equences  |      | • | <br>• | • | • | • | • | • | • |   | 69 |

|     |                                                      |           |      |   |       |   |   |   |   |   |   |   |    |

| 5.1 | Measurements form Test A                             |           |      |   |       |   |   |   |   |   |   |   | 79 |

|     | Measurements form Test A<br>Measurements form Test B |           |      |   |       |   |   |   |   |   |   |   |    |

## Abbreviations

| $\mathbf{ADCS}$ Attitude Determination and Control System |

|-----------------------------------------------------------|

| <b>CAN</b> Controller Area Network                        |

| <b>DD</b> Displacement Damage                             |

| <b>EPS</b> Electronic Power System                        |

| <b>FET</b> Field-Effect Transistor                        |

| <b>FPGA</b> Field-Programmable Gate Array                 |

| $\mathbf{I^2C}$ Inter-Integrated Circuit                  |

| IC Integrated Circuit                                     |

| I/O Input/Output                                          |

| <b>IRQ</b> Interrupt Request                              |

| <b>ISO</b> International Standardization Organization     |

| JTAG Joint Test Action Group                              |

| <b>LED</b> Light-Emitting Diode                           |

| $\mathbf{MCU}$ Micro Controller Unit                      |

| MUX Multiplexer                                           |

| <b>OBC</b> OnBoard Controller                             |

| <b>PCB</b> Printed Circuit Board                          |

| <b>SDA</b> Serial Data Line                               |

${\bf SEE}$  Single Event Effects

${\bf TID}\,$  Total Ionizing Dose

${\bf UHF}~$ Ultra High Frequency

${\bf VHDCI}$  Very-High-Density Cable Interconnect

**VHF** Very High Frequency

### Chapter 1

### Introduction

#### 1.1 Summary

The NTNU Test Satellite is double CubeSat being built at NTNU. The main payload of the satellite is a camera for earth observations. The satellite is based on a modular design with a "motherboard" style backplane where modules are placed in slots. In the current revisions of the backplane, lack of documentation and partially incomplete schematics combined with an increase in complexity over several iterations has made the task of realizing the backplane within an acceptable time-frame difficult. For data transfer the current backplane makes use of two parallel I<sup>2</sup>C buses for redundancy and a custom made arbitration bus for arbitration between the two OBCs (On-board Controllers) in the satellite. This results in a complex arbitration scheme having to be implemented in software with the potential of fault propagation over the arbitration bus between modules. A new design is proposed using CAN bus with built in arbitration with priority based on message address. Due to the robust nature of the CAN bus a single bus is considered able to replace the two I<sup>2</sup>C buses. In the current design control signals for the backplane are sent using a single wire custom serial bus implementation based on shift-registers. The proposed new design connects the control of utility functions and housekeeping on the backplane, such as module power management, to the CAN bus. A new schematic design for the backplane is presented and test methodology suggested. The design is partially assembled on breadboard and tested. Lastly a partial hardware test and verification is presented before a conclusion is reached on the reduced complexity and future ease of implementation when it comes to board layout and production.

#### 1.2 Summary - Norwegian

Ved NTNU bygges det en test saltetitten basert på en dobbel CubeSat. Hovedlasten til satellitten er et kamera for atmosfæriske observasjoner. Satellitten bruker et modulært design basert på et sentralt hovedkort hvor andre moduler kan plasseres. Også kalt et bakplan. I den gjeldende versjonen av bakplanet har mangel på dokumentasjon og delvis uferdige skjemategninger kombinert med en økning i komplexitet over flere iterasjoner resultert i et design som er vanskelig å implementere på en akseptabel måte. For overføring av data brukes to parallelle I<sup>2</sup>C buser for redundans og en spesiallaget arbitreringsbus mellom de to OBCene i satellitten. På grunn av dette må en relativt kompleks arbitrerings metodikk implementeres fysisk og i programvare til OBCene. Det er også potensiale for at en eventuell feil kan spre seg via arbitreringslogikken. Et nytt design er foreslått som tar i bruk CAN bus med innebygget arbitrering og meldingsbasert prioritet. CAN busen er en robust bus, noe som tillater oss å erstatte begge de redundante  $I^2C$  busene med en enkel CAN bus. Videre er kontrollsignalene til bakplan logikken i det nåværende designet basert på en spesiallaget seriell bus laget med skiftregistre. I det nye designet foreslås det å koble bakplanets kontrollsignaler til CAN bussen. Videre presenteres et nytt skjemautlegg for bakplanet og test metodikk for et ferdig kort er foreslått. Deler av kontroll logikken og strømforsyningen på bakplanet er testet og verifisert ved delvis sammensetting og målinger på lab. Til slutt konkludered det med et design som reduserer kompleksiteten og gjør utlegg og produksjon av PCB betydelig lettere.

#### 1.3 Problem description

The current focus of the NUTS project is to finish the design and build hardware for an integrated engineering model. Through this project, the student should focus on the top-level system design in general, with particular focus on the backplane and how it interconnects all other subsystems of the satellite.

The backplane is one of the principal components of the satellite. It distributes power and provides access to the databases to the rest of the subsystems.

The backplane must be designed to be reliable, as maintenance is impossible after launch. Challenges due to the space environment, such as temperature cycles, radiation environment, failing electronic components and vacuum must be identified and discussed. In areas where mitigation of such problems is possible, solutions should be presented. Whether the solutions be implemented should be based on a cost/benefit analysis.

Key tasks for the student:

- Study and evaluate different interconnecting designs possible for NUTS, with a view on the previous proposed designs and prototypes.

- Evaluate and study different bus architectures, such as I<sup>2</sup>C vs. CANbus in addition to the needed backplane control logic.

- Propose a design, and produce this by designing it in Altium Designer.

- Propose test regimes to identify if the backplane fulfills its desired tasks.

In addition to the given tasks, the student is expected to participate in relevant group work. The NUTS project is a multi disciplinary project, which requires more involvement from the student than just the completion of the individual task and report.

#### 1.4 NUTS

The NTNU Test Satellite is double CubeSat [1] being built at NTNU. According to the original Mission statement [2] the aim is to "design, develop, test, launch and operate a double CubeSat". This is a multidisciplinary project where student learning is in focus and through "hands-on" experience that aims to teach students skills needed in jobs post graduation. The main payload of the satellite is a camera for atmospheric observations. The original Mission statement [2] lists the following goals for the project:

- Deliver a tested satellite according to mission specifications

- Transmit a beacon signal that can be received by radio amateurs

- Confirm successful de-tumbling

- Establish two-way communication and receive full telemetry

- Test camera

- Initiate camera pinpointing

- Initiate camera sequence

- Receive a valid series of images

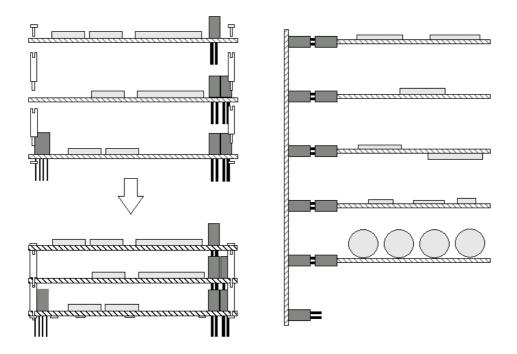

Figure 1.1: The figure shows a 3D model of the proposed backplane design used in NUTS.

Figure 1.2: The figure shows the standard PC104 stacked card design used in most CubeSats to the left and the proposed backplane design used in NUTS to the right.

The main deviation form "standard" CubeSat designs is the choice not to use PC-104 form factor for the electronics design. Instead a backplane design is used as shown in Figure 1.1 and Figure 1.2. One of the main reasons for this decision is enhanced reliability. Using two backplane masters for redundancy both can remove other subsystems form the data bus and backplane power. The backplane essentially allows any module to talk to any other module and power management on individual module basis. The mission statement has been subject to change over the last few years.

### Chapter 2

## Previous development and relevant theory

This section will introduce the satellite and each module will be briefly described. The last part of this section will cover design considerations of particular importance to the backplane and the design decisions to be made regarding the backplane.

#### 2.1 NUTS satellite overview

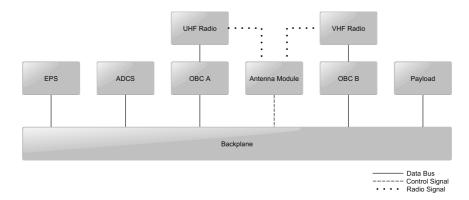

The NUTS satellite is a modular system with functions spread out over multiple modules as shown in figure 2.1. With a clearly defined interface between the modules this approach allows the system to be spread out over several student groups for development.

Figure 2.1: Block schematic overview of the NUTS system showing how each module relates to each other and the backplane.

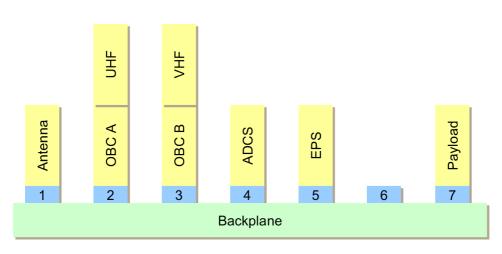

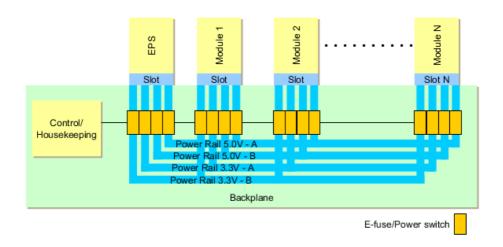

Figure 2.2: Overview of the backplane and modules of the NUTS system showing how modules are set in to slots on the backplane.

#### 2.1.1 Backplane

The backplane is the "motherboard style" circuit board that other modules in the sattelite slot in to as shown in figure 2.2. It is mostly transparent to the other modules and ensures a parallel configuration of the satellite modules. The principle is that any module can access any other module regardless of its placement in the backplane slot. The backplane distributes power form the EPS module to the other modules. It also ensures isolation between a module and the backplane to such an extent that faulty modules should not propagate their fault to the rest of the system. Each module has access to databuses and sensorbuses on the backplane. A selection of "housekeeping" logic states can be set on the backplane to disconnect parts of a module or a whole module from the backplane, as well as disconnecting modules from faulty power-rails in the case of a partial power failure in the backplane or on the EPS. The backplane also provides utility buses and signals allowing one module to reset another and in special cases reprogram an other module via a dedicated JTAG bus between modules. When assembling the satellite in a laboratory environment the backplane provides headers for lab access allowing for programming and test of all modules while the satellite is partly or fully assembled.

#### 2.1.2 OBC - On Board Controller

The NTNU Test Satellite will have two on board computers also called onboard controllers (OBC) working redundantly. The main task of the OBC is to monitor the health of the system and execute necessary actions when particular situations demand it. The OBC periodically requests health data from software instances in other parts of the satellite and poll's sensors in the different areas of the satellite for monitoring power usage and temperatures. It also sets the system states according to battery levels. Each of the two OBC's will act as a gateway for the UHF and the VHF radios with each of the radios connected to one of the on board controllers. This will enable the satellite to communicate with the ground station in full duplex mode allowing communication in both directions simultaneously. With each of the two controllers doing either sending or receiving.

#### 2.1.3 ADCS - Attitude Determination and Control System

As the satellite is detached from the launch vehicle the orientation may defer form the desired orientation. It may also have rotation along multiple axis called tumbling. In order to make use of the satellite and its payload a measure of control over the satellite is needed. The ADCS detects and affects the satellites physical orientation in space. De-tumbling is the most critical part of the ADCS system. Charging the satellite using solar panels and communication between satellite and ground station is to a degree dependent the tumbling speed of the satellite.

#### 2.1.4 EPS - Electronic Power System

The Electronic Power System includes the solar panels and battery as well as the electronics required to regulate charging from the solar panels and power the satellite. It also has mechanical switches disconnecting all power from the rest of the satellite to ensure it is powered completely down during launch before it reaches orbit. Ensuring the battery can receive charge from the solar panels is the most critical part of the EPS.

#### 2.1.5 Antenna module

The antenna module contain the antennas and the deployment electronics. The antennas will be released based on a timer activated on power up. Redundancy is also present allowing the OBC to control the deployment if the timer fail ensuring they are deployed once the spacecraft is in orbit.

#### 2.1.6 Payload

The payload is a camera with an FPGA module able to take pictures. The pictures are then compressed to a JPEG2 format in the FPGA module

making the file size suitable for download via the radiolink to the ground station. This payload can allow for reprogramming of the FPGA in orbit potentially allowing the satellite features to be updated over time.

#### 2.2 Backplane design considerations

#### 2.2.1 Electronics in space: Radiation, vacuum and temperatures

The space environment is a harsh environment especially for electronics. Thinner atmosphere and weaker magnetic field leaves the spacecraft and its electronics more exposed to radiation in the form solar wind, solar energetic particles form flares and coronal mass ejections as well as galactic cosmic rays. In orbits ranging form 700 kilometers to 6000 kilometers the trapped particles in the Van Allen belts also become relevant.

A detailed explanation of the effects of space radiation can be found in the article "What could go wrong? The effects of ionizing radiation on space electronics." by J. Scarpulla and A. Yarbrough [3, p15-19]. In this article the effects of radiation in space on electronics is divided in to three categories:

- Total ionizing dose (TID) effects The accumulation of ionizing dose depositions over a long time.

- Displacement damage (DD) The accumulation of defects in the crystal lattice of semiconductor materials caused by high energy radiation.

- Single event effects (SEE) A single high energy particle creating a highly ionizing dose deposition in a sensitive region of a device.

#### Total ionizing dose effects (TID)

TID is a measure of the integrated radiation dose the spacecraft acquires over a given time period. Energetic ions can break down or rearrange atomic bonds altering the material properties. After the electronics has been exposed to sufficient total-dose radiation insulation materials can become more electrically "leaky" reducing the insulating capasity. TID also affects conductive materials such as metal film in resistors changing their characteristics over time.

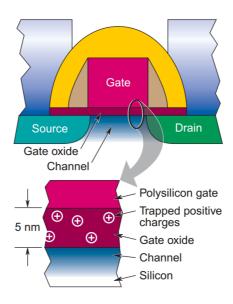

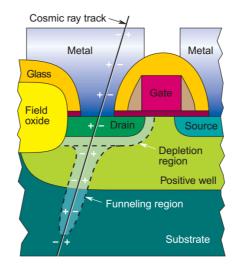

However, the biggest challenge when it comes to TID is the effect it has on NMOS and PMOS transistors. NMOS and PMOS transistors are used in most electronic circuits as switching elements to propagate logic states throughout the circuit. When the gate oxide is exposed to radiation it becomes ionized by the dose it absorbs and even though the electrons are fairly mobile the so called "holes" (electron voids or positive charge carriers are often referred to as "holes") are not. Over time these "holes" become trapped and accumulate in the gate oxide as shown in figure 2.3. After enough of these positive charges are trapped in the gate oxide the positive charge builds up and eventually has the same effect as if a positive voltage was applied on the gate of the transistor. This results in NMOS transistors that are permanently in the "on" or conducting state and PMOS transistors in a permanent "off" or insulating state.

As the technology continues to scale down the sizes of transistors a result is that the gate oxide is also becoming thinner. As this happens the gate oxide is able to trap less positive charge over all and are naturally becoming more radiation resistant.

Figure 2.3: Illustration from J. Scarpulla and A. Yarbrough [3] showing the effect of TID on the gate oxide of an NMOS transistor.

#### Displacement damage (DD)

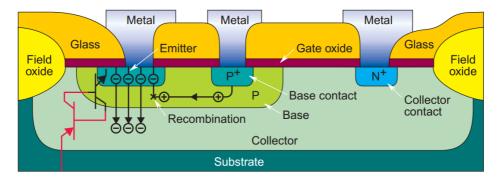

Also referred to as neutron and proton damage displacement damage happens when neutron or proton that are higly energetic penetrate in to the semiconductor crystal lattice such as the silicon. The intrusive proton or neutron transfers some of its energy to the silicon nucleus potentially knocking the nucleus out of position. Also referred to as elastic scattering the affected and now "free" silicon atom has to disperse with the energy gained through its displacement. This can happen through ionization or by in turn displacing other atoms. An alternative is that the incident particle is absorbed in to the struck nucleus. This is called inelastic scattering and the exited nucleus needs to emit some of the absorbed energy through reemitting the particle at a lower energy along with a gamma ray. Either way the result causes displacements in the crystal lattice. The outcome is essentially microscopic crystal imperfections called voids and clusters in the crystal lattice that can cause interference in the orderly flow of charges in the semiconductor as is shown in figure 2.4

Figure 2.4: Illustration from J. Scarpulla and A. Yarbrough [3] showing the effect of DD in the crystal lattice of a bipolar junction transistor. Electrons are lost to recombination in "holes" before reaching the collector.

#### Single event effects (SEE)

In space it is possible to have so called single event effects from a single particle causing trouble. Single particles from cosmic rays can pass through a space craft and its internal components and exit on the other side in a straight line. Shielding a space craft from these types of particles is highly impractical. When a energetic ion passes through a semiconductor it leaves behind a wake or column of ionized material. The column is electrically neutral and consists of an equal number of electrons and holes effectively creating a temporary "conducting wire" as shown if Figure 2.5. This disturbs the "normal" current paths and electric fields. The result can be significant current flow or temporary "shorts" as the ion "track" dissipates by recombination. This can result in single event upsets, burnouts, latchup or other undesirable events. Single event upsets can include so called "bit flips" in memory devices. As mentioned when talking about TID CMOS scaling affects a components radiation resistance characteristics. However when it comes to SEE the scaling down of CMOS devices has a negative outcome as less energy is required to compel single event effects or the "wake" affects bigger parts of the circuit making it more likely to experience SEE's.

Figure 2.5: Illustration from J. Scarpulla and A. Yarbrough [3] showing the effect of SEE in NMOS transistor. The energetic particle passes through the device leaving a wake of liberated charges. This can momentarily create a short between the drain terminal and the substrate.

#### 2.2.2 Fault isolation, detection and recovery

Any spacecraft orbiting earth needs some degree of autonomous operation in order for the spacecraft to be able to perform its tasks when not in direct contact with the ground station. This requires a design is dependable and can handle faults. As described in [4] chapter 15.2.1 we can achieve a dependable system by:

- Fault-avoidance to prevent, by design, the occurrence of a fault.

- Fault-tolerance to provide, by redundancy, the specified service in spite of faults occurring.

- Fault-removal to remove the presence of design faults.

- Fault-forecasting to estimate, by evaluation, the presence, creation and consequences of errors.

Faults result in errors. Errors can in turn result in failures.

#### 2.3 BUS evaluation

This section will briefly look at different alternatives when it comes to choice of main data carrier bus and provide a foundation for evaluating the current bus choice against alternatives in later chapters. Especially the different recommended methods for error checking and fault tolerance are reviewed.

#### 2.3.1 I<sup>2</sup>C bus

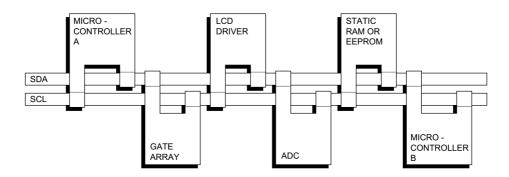

The I<sup>2</sup>C bus was originally developed by Philips Semiconductors (now NXP Semiconductors) as a simple bidirectional 2-wire bus for efficient inter-IC control as stated in the I<sup>2</sup>C-bus specification and user manual [5]. The I<sup>2</sup>C bus is a 2-wire bus requiring only a serial data line and a serial clock line. Each device connected to the bus must have a unique address often set in hardware. Figure 2.6 shows a typical application using the I<sup>2</sup>C bus. The bus speed ranges from the 100 kbit/s standard mode transfer rate all the way up to 3.4 Mbit/s in High-speed mode when supported.

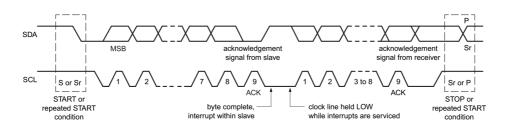

#### Byte format

Bytes on the SDA line are always 8 bit long and are followed by ACK (acknowledge) bit. Any number of bytes can be transmitted in a transfer operation, however each byte must be followed by an ACK bit as shown in figure 2.7. A slave can force the master to wait for it to finish an internal operation or interrupt service by holding the SCL line LOW releasing it when it is ready.

#### Arbitration

Arbitration is only required when the  $I^2C$  bus is set up as a multi-master system. A master can only start a transfer when the bus is free. However, In the event of two masters initiating a transfer at the same time each master checks that the value it puts SDA (Serial Data Line) on the bus actually is present on the bus. Bit by bit the masters check if the bus is high. If a master tries to send a HIGH, but detects that the SDA level is LOW, the master knows that it has lost the arbitration and turns off its SDA output driver. The master winning the arbitration continues to send its message and the master loosing the arbitration must restart its transmission once the bus is free. Control of the bus is only dependent on the address and data sent by competing masters this means there is no central master or order of priority on the bus.

Figure 2.6: Illustration from data-sheet [5] showing a typical  $I^2C$  bus implementation.

#### Error Checking and Fault Confinement

- Software reset Software reset is an optional feature implemented in some I<sup>2</sup>C devices. A message can be sent to force the device to reset. (Only devices that does not pull SDA or SCL line after applying the supply voltage must use this function as it otherwise could block the bus.)

- **Bus clear** In the case of SCL being stuck LOW the recommended procedure is HW reset signal for devices with HW reset inputs. Alternatives for devices without HW reset signals are power cycling to activate the mandatory internal Power-On Reset circuit. In the case of the SDA line stuck LOW the master should send nine clock pulses. This should make the device holding the signal LOW release the bus. If not, HW reset or power cycle should be used.

- Software defined error check Checksums or error detection methods can be baked in to the higher level functionality of the messaging structure in the case of MCU to MCU communication.

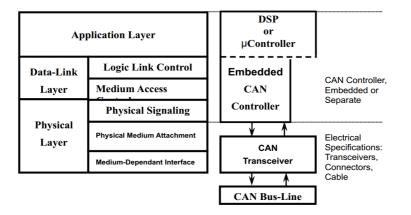

#### 2.3.2 CAN bus

The CAN bus (Controller Area Network bus) was originally designed by Bosch and is an International Standardization Organization (ISO) defined serial communications bus [6]. One of the key points of the CAN standard is the high immunity to electrical interference and the ability to self-diagnose and repair data errors. The CAN communications protocol is described in

Figure 2.7: Illustration from data-sheet [5] showing data being transferred on the  $I^2C$  bus.

Figure 2.8: Illustration from data-sheet [6] showing the layered ISO11898 standard architecture of the CAN bus.

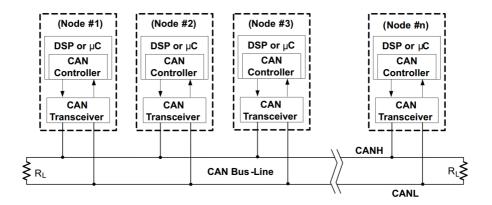

ISO-11898: 2003 [7] which shows that it follows the Open Systems Interconnect model which is defined in terms of layers as shown in figure 2.8. The Controller Area Network (CAN) consists of nodes connected to a bus. The bus is a two wire differential type bus and the nodes consists of a controller and an transceiver. The controller is often embedded inside a microcontroller with the transceiver being a stand alone chip. The typical layout is shown in figure 2.9. The transceiver handles the level translation and generation of the differential signal towards the bus and reads the bus differential signal providing appropriate feedback to the CAN controller.

When using the standard CAN we can send and receive messages with a structure as shown in figure 2.10 and contains the following fields:

- **SOF** Start of frame bit marking the start of a message. Also and used for synchronizing nodes on the bus.

- Identifier 11bit CAN message identifier containing the message pri-

Figure 2.9: Illustration from data-sheet [6] showing the typical CAN bus structure.

ority. (Lower binary value has higher priority.)

- **RTR** Single remote transmission request. Dominant if information is required from a node specified by the identifier in the message.

- **IDE** Single dominant identifier extension specifying that no extension to the identifier is present. (CAN messages can be used in either extended or standard mode where the extended mode has an "extended" 29 bit identifier.)

- **r0** Reserved bit (Not currently in use)

- **DLC** 4bit containing the length of data transmitted.

- Data The actual data transmitted. (Up to 64 bits)

- CRC Cyclic redundancy check (checksum) for the data transmitted.

- ACK ACK bit received by every node in the network. If one node fails to set the dominant ACK bit the message is discarded and the sender repeats the message.

- **EOF** End of frame.

- **IFS** Inter-frame space making time for the controller to move a correctly received frame to a message buffer area.

| S<br>O<br>F | 11-bit<br>Identifier | R<br>T<br>R | I<br>D<br>E | r0 | DLC | 08 Bytes Data | CRC | ACK | E<br>O<br>F | I<br>F<br>S |

|-------------|----------------------|-------------|-------------|----|-----|---------------|-----|-----|-------------|-------------|

|-------------|----------------------|-------------|-------------|----|-----|---------------|-----|-----|-------------|-------------|

Figure 2.10: Illustration from data-sheet [6] showing message structure in a standard CAN message.

#### Arbitration

In the CAN bus a Arbitration is handled in a nondestructive, bit-wise arbitration manner. Meaning that the node winning arbitration continues with the message, without the message being affected by another node. As a zero is the dominant bit in CAN messages the message that has the most consecutive zeros in the identifier wins the arbitration. The result is the lowest identifiers have the highest priority.

#### Message types

The four different types of messages on a CAN bus are as follows:

- **The Data Frame** Containing data from 0 to 8 bytes the data frame is the most common message type.

- The Remote Frame Used to request data from a node. This message type contains no data.

- The Error Frame A message that violates the formatting rules of a CAN message. Transmitted when a node detects an error and causes all the other nodes to send an error frame making the original transmitter repeat its message. A node can however not tie up a bus by repeatedly sending error frames.

- **The Overload Frame** Can be used to create extra delay between messages. Transmitted by a node that becomes too busy.

A valid frame is achieved when a message is error free. An error free message has the last bit of the ending EOF field in the error-free recessive state. If a dominant bit in the EOF field is read the transmitter repeats the message.

#### Error Checking and Fault Confinement

The CAN-protocol uses five different methods for error checking. Two of these methods are on the bit level and three at the message level. When an

error is detected through any of these methods an error frame is generated from the receiving node. If a faulty node hangs up a bus by continuously repeating an error, its transmitting capability is removed by its controller when an error limit is reached. Error checking is as follows:

- 1. **CRC** 16bit Cyclic redundancy check containing a 15bit checksum and a 1bit delimiter.

- 2. ACK A single acknowledge bit and an acknowledge delimiter bit.

- 3. Form Check Checks the SOF, EOF, ACK delimiter, and the CRC delimiter bits. These must always be recessive bits. When a dominant bit is detected, an error is generated.

- 4. **Transmit monitoring** As the transmitter is transmitting a message it also monitors the bus. If a data bit is written and the opposite read an error is generated. This does not happen for arbitration bits.

- 5. **Bit Stuffing** Bit stuffing rule where after five consecutive bits of the same value a complement is expected. If a sixth bit is received with the same value an error is generated. Stuffed bits are removed by a receiving node's controller.

The differential structure of the bus lines and the abundant error checking is what contributes to the CAN bus being a relatively robust bus.

# Chapter 3 Design proposition

Several iterations of the backplane has been devised previously. Each iteration has solved issues discovered in the previous designs and implemented solutions to the specific challenges encountered. This approach over several iterations has resulted in a complex design that solves a great deal of the problems. However, it has also resulted in a design where the complexity itself has become a problem with respect to lack of documentation of design decisions made previously as well as knowledge transfer for new students. In this section we will review the choice's made and challenges faced in the current design (NUTS Backplane v4.0) [8] and make decisions on what to keep, what to simplify and what to change. The chapter will outline a new design proposal.

#### 3.1 Proposed backplane design

When updating the backplane design and reducing its complexity we need to do a review of the current state of the backplane. The functions of the backplane will be examined in the following sections and are divided in to the categories: data carrier, sensor network, power distribution, lab access and programming, backplane control, module slot requirements and fault isolation. The current state of the NUTS backplane is revison 4 and was designed by Ingulf Helland [8].

#### 3.1.1 Data carrier

The data carrier is the main bus where data is transported between the different modules. This bus needs to be robust as a failure in this bus will isolate each module form other modules. The bus must also allow for an

arbitration scheme that prevents any faulty modules form blocking other modules form using the bus.

#### Current state

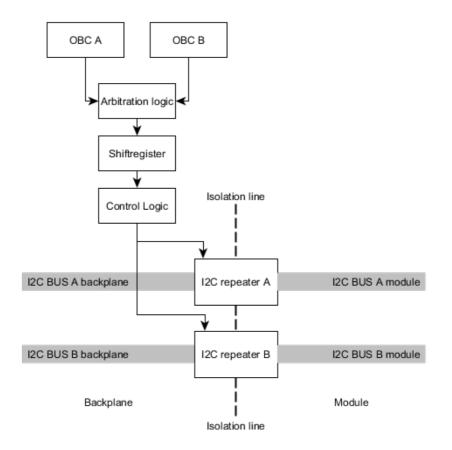

In the current design the data carrier is designed as an  $I^2C$  bus with a second  $I^2C$  bus as redundancy as shown in figure 3.1. The two  $I^2C$  buses are routed throughout the backplane connecting to all the modules. However there is no support for two I<sup>2</sup>C buses on a lot of the modules. This is resolved by connecting both the I<sup>2</sup>C buses to the same I<sup>2</sup>C port on the module card. To ensure a module is connected to only one of the I<sup>2</sup>C buses at any given time the buses are isolated from the module side using I<sup>2</sup>C repeaters with "hotswap support" that fulfills isolation standards. To avoid conflict between the two I<sup>2</sup>C buses only one I<sup>2</sup>C repeater IC is active at a time. Each module slot in the backplane has a set of control logic able to turn each of the repeaters on or of. The state of the control logic is set in a shift register. The shift register receives its states from one of the OBC modules through a separate custom serial bus able to clock data in to a specific module slot shift register based on its address. A custom arbitration bus and logic between the two OBC's are also present to allow for control from both OBC's based on an software defined arbitration scheme. This ensures control is maintained if one of the OBC's fail.

Then main drawback of this design is its complexity. It requires every single type of module slot to have its own logic control. It requires a custom arbitration bus as well as a custom serial bus to clock states in to the shift register of each module slot. It also requires each of the module slots to be custom designed for the module used in the slot. Especially the OBC's slots requires extra pins for the arbitration logic connections and the serial communication towards the slot shift registers. The consequence has been a design with a complexity that have been difficult in terms of knowledge transfer for new students. It also requires extra work with respect to PCB board layout as less of the component layout in each slot is identical and as a result is not repeatable across the board.

#### Proposed changes

When we compare the fault and error handling capabilities of the CAN bus and the  $I^2C$  bus discussed in 2.3 it is clear that the CAN bus has a more robust design. The  $I^2C$  bus relies heavily on the ability to perform a hardware reset if a fault presents it self on the bus. This is not always possible without physical access to the satellite. Implementing direct control

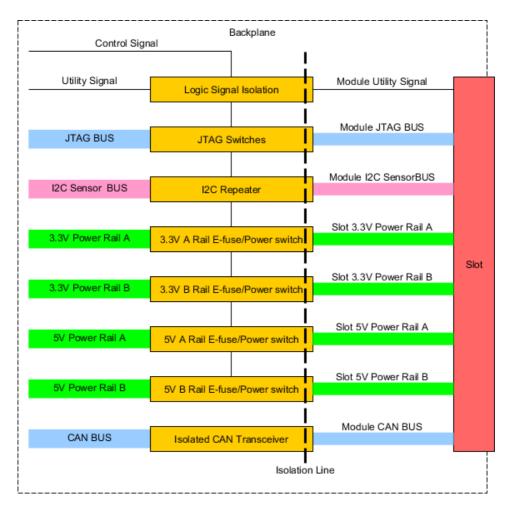

Figure 3.1: Figure showing the the redundancy functionality implemented in the current data bus based on two  $I^2C$  buses.

from the OBCs to reset the  $I^2C$  bus provides a new point of failure and further need for software check and control from the OBC. By choosing a CAN bus as the main data carrier with a single CAN bus replacing the two  $I^2C$  buses in the current iteration of the back plane we can significantly reduce the complexity of the design. The CAN bus has built in arbitration ensuring each of the modules has priority based on it's address in the CAN network allowing us to completely remove the custom arbitration bus in the current design. By making use of a CAN protocol the overhead is reduces as error-checking is handled within the CAN controller and custom error checking does not need to be implemented on the software side of the MCUs connected to the bus. The result is an implementation that is simpler and more robust. Complexity can further be reduced when it comes to slot control signals. This is discussed in section 3.1.5.

## 3.1.2 Sensor network

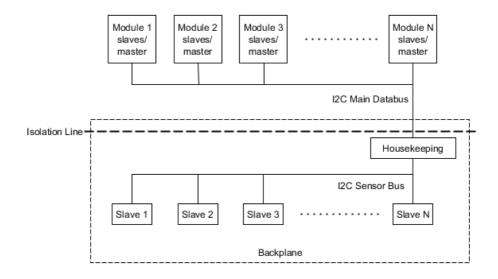

The satellite needs a subsystem that enables its on-board control modules to monitor the status of the hardware in the satellite. Such a sensor systems needs to be independent of the status messages the modules might send themselves to the OBC via the main databus. This separation is important in order to allow the OBC to detect failures which the modules may not able to report them selves. Being battery powered the satellite has a limited power reserve to draw from in order to perform its main operational functions. It is critical that the power usage of the whole system does not exceed the battery's capacity to deliver power at any given time, as well as the solar panels ability to sufficiently charge the battery. Taking this in to account the most important sensors on the backplane are sensors to determine power consumption of connected modules as well as the power consumption of the backplane itself. A common structure of sensor systems are so called sensor networks where a bus is shared between all the sensors and the sensors are accessed by a master using it's address in the network. By allowing all sensors in the sattelite to connect to the same sensor network whether it is located on the backplane or on a module, they can all be accessed by any master connected to the bus.

#### Current state

The sensor network in the current design is based on a single  $I^2C$  bus with sensors in the form of slaves distributed on the back plane circuit board as shown in figure 3.2. The sensor  $I^2C$  bus is connected to a housekeeping module that connects the  $I^2C$  sensor bus to the main  $I^2C$  databus. The

Figure 3.2: Sensor bus as implemented in the current design  $I^2C$  bus.

backplane itself holds only current sensors used to measure each modules power consumption as well as the backplane power consumption. This is done using the INA219 IC which is a current/power monitor with an integrated I<sup>2</sup>C interface. The the power consumption is measured at each module slot both for the 3.3V and the 5.0V rails. This part of the current design is incomplete with no connections to a master reading the sensor bus data.

The main drawback of this design is that it does not allow for sensors to be placed on modules without connecting them to the main  $I^2C$  data buses. This results in a design where sensors are spread across different buses. The housekeeping module has not been realized in this design and the exact details of how the sensor bus is connected to the main data bus is not documented. An issue also encountered in current designs was the need for more sensors of a single type than allowed by that sensor types configurable address space.

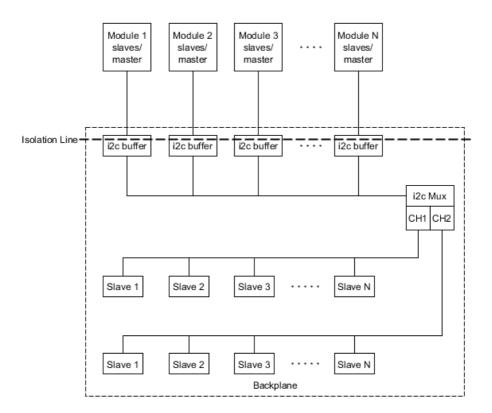

#### Proposed changes

In section 3.1.1 a new CAN bus based data carrier is proposed to replace the original dual  $I^2C$  bus system. However, when it comes to sensor peripherals the  $I^2C$  bus is a well suited bus. The  $I^2C$  bus is typically used for attaching peripheral ICs to processors. The  $I^2C$  bus used only as a sensor bus also

provides a better domain separation between sensor data and the main data bus. This can allow the OBCs to gather sensor data while the main data bus is in use or down and vice versa. The new proposed  $I^2C$  bus design also allow sensors on the module cards to be connected to the same bus as well. This design will also allow micro controllers placed on module cards to access the sensor bus and reading the satellite sensor data as well should the module card design require it. The new sensor bus design is outlined in figure 3.3. The figure shows a single  $I^2C$  bus used as a sensor bus in the satelite. It allows both sensors located on the backplane and sensors located on modules to be connected to the same bus. Further more the figure 3.3 shows the use of  $I^2C$  buffers to ensure electrical isolation between the modules and the backplane to avoid fault propagation in the event of module failures. The buffers also allow the modules to be hot-swapped while the system is powered up in a lab environment. The I<sup>2</sup>C buffer chip can also be used to disconnect a module from the  $I^2C$  bus by powering down the module side of the buffer chip. This is discussed in more detail in section 3.1.7. Figure 3.3 also shows an  $I^2C$  MUX used before the slave sensor ICs on the backplane. This allows for the same type of I<sup>2</sup>C sensors to be used on the module cards without worrying about them having the same address as the sensors placed on the I<sup>2</sup>C bus on the backplane. As in the current design each module slot will have INA219 sensors to monitor both the power consumption of the 3.3V and the 5.0V. It is estimated that 16 of these sensors will be needed in the backplane design as well as at least 4 on the EPS module card. As this particular sensor only have 16 different configurable addresses a MUX is needed.

## 3.1.3 Power distribution

The EPS provides power to the satellite in the form of two redundant 5.0V rails and two redundant 3.3V rails. The backplane must be able to distribute this power to the connected modules in a reliable manner. Modules must be allocated a maximum power draw over time as well as peak current limits. The backplane must manage power in a way that ensures module functionality but does not allow modules to, through a fault or otherwise, consume excessive amounts of the satellites power. The backplane must also be able to disconnect faulty modules form the power rails as well as disconnecting faulty power rails from the modules.

Figure 3.3: New sensor bus design using  $I^2C$  and a bus multiplexer.

Figure 3.4: The current backplane power distribution.

#### Current state

The EPS provides four power rails to the backplane as shown in figure 3.4. On the backplane the four power rails is distributed to the modules through E-fuses. The e-fuses can be set to disconnect when the current draw passes a limit set by the resistor network connected to the E-fuse. This allows us to define different current limits for the different slots based on each modules need. The e-fuse can be reset by a control signal from the backplane control/housekeeping module if tripped. This signal can also be used to manually trigger the e-fuse should it be needed. This setup allows the power rails to be controlled in two ways for each of the rails. Either disconnecting a module from a power rail or disconnecting the EPS from a power rail effectively powering down that power rail.

The main drawback of this design is that it requires the EPS module slot to be specially designed for the EPS effectively reducing the re-usability of the slot design in a PCB layout process. It also makes use of the custom designed control bus and control logic discussed in section 3.1.1.

## Proposed changes

Very little needs to be changed in the design of the power distribution system of the satellite. The current design is well thought through and robust. However, the slots for the modules should be modified with a unified design to allow any module to be connected in to any slot. This will facilitate reusability in the layout process of the PCB. Proposed changes to the control signal for the e-fuses is discussed in section 3.1.5.

#### 3.1.4 Lab access and programming

Access to the satellite circuit boards for testing purposes are important in a lab environment. It is important that the system allows us to ensure system functionality by physically accessing test point in the satellite and doing measurements. Important elements that needs to be accessed are buses, power rails at different locations and control signals for direct control of satellite functions. Relevant test points must be accessible both when the satellite is open and circuit boards are directly accessible, but also when the satellite is fully assembled and undergoing full scale tests. The backplane must provide a programming bus to all the connected modules allowing for the modules to be reprogrammed after the satellite is fully assembled.

#### Current state

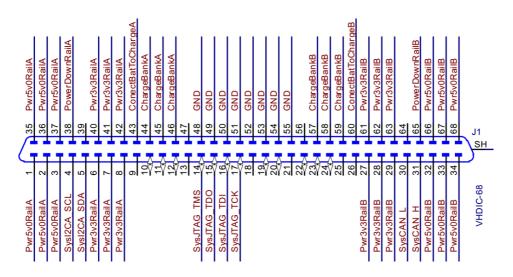

Currently the satellite is designed with a separate test socket for ever module slot. Custom PCBs are then designed to connect to these sockets and provide test data results in the form of LED lights indicating value of logic levels. After assembly access to measurement points are given through a very-high-density cable interconnect (VHDCI) header with 68-pins. A JTAG-bus is connected to every module slot on the backplane and can be accessed through a connector on the OBC. Jumpers on the OBC sets the module address allowing us to choose what module is being programmed by the JTAG programmer connected to the OBC JTAG header.

The drawback of this design is the use of extra custom PCB cards to detect and flag the system status. This requires extra PCBs to be designed. As well as the area need for extra headers on the backplane itself taking up important PCB real-estate. Also, the programming of modules connected to the JTAG bus is done via the OBC. This makes reprogramming the satellite while fully assembled difficult or impossible as access to the OBC is required.

#### Proposed changes

In the new design we remove the custom PCBs and test headers. As many as possible of the test points currently routed to these custom PCBs will be routed to the 68-pin VHDCI header. Measurement points not needed when the satellite is fully assembled will be broken out on the backplane PCB itself and assessable using a logic analyzer. A second 68-pin VHDCI header will be added should the amount of needed measurement points exceed the available pins in a single 68-pin VHDCI header. The JTAG bus must be accessible through the VHDCI header. Setting the address of what slot is being programmed by the JTAG bus should also be done through the VHDCI header. This will allow the satellite to be fully accessible and reprogrammable after assembly or any at state before fully assembled.

## 3.1.5 Backplane Control

The backplane must provide functions that allows each module slot to be controlled and its states to be set. The system must be able to set states for power-rails connected to the slots as well as connecting or disconnecting the buses or signals going to and from the module via the module slot. This is important in order to limit fault exposure and to contain and isolate failures to a single module preventing propagation of said failure to other modules. Control of these states is exercised by the OBC modules and the backplane must provide a way for the OBC to control these states and functions.

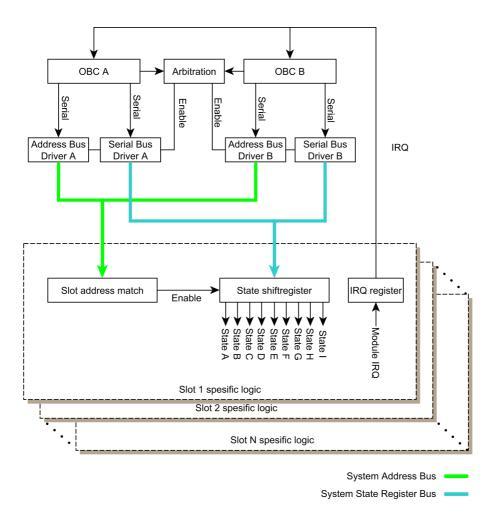

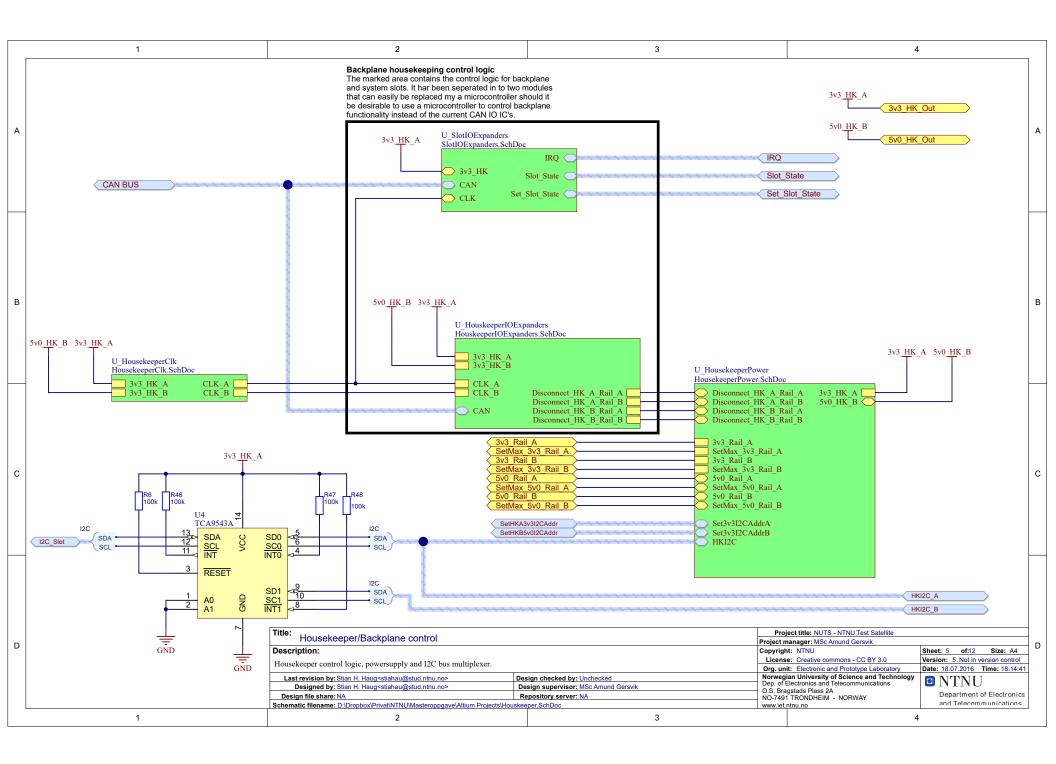

#### Current state

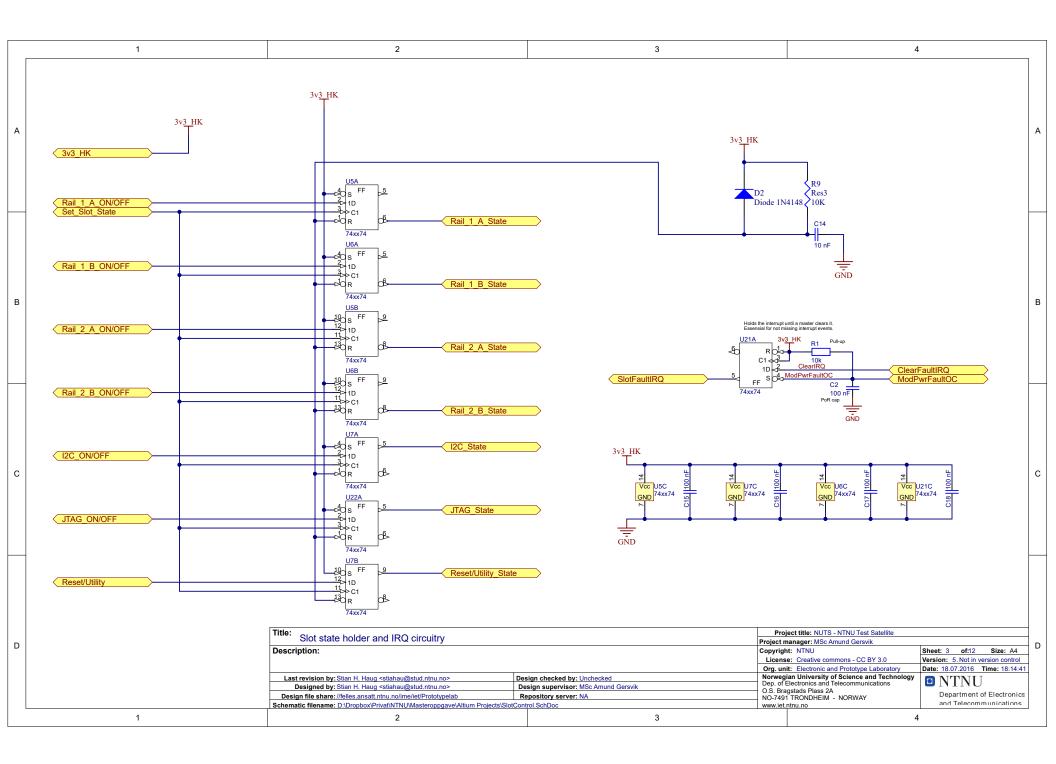

In the current design the backplane control signals and state holders are referred to as housekeeping. Figure 3.5 shows an overview of how backplane functionality is currently controlled. An arbitration scheme based on a custom arbitration bus between the two OBCs decides who can write to the module slot logic. When one of the OBSs win the arbitration it is given access to bus driver chips located on the backplane. These ICs are used to drive the respective address bus and state register bus. Using the address bus driver the active OBC can place an address on the address bus. The address bus is three wires allowing for 3bit addressees used to match against 3bit address predetermined in the hardware of a module slot. When the module slot recognize its address the slot state shiftregister is enabled allowing new data to be clocked in to it in a serial manner via the system state register bus. The system state register bus consists of wires connected the state shiftregister allowing data, clock and set signals to be controlled. Given that the address on the address bus is a match, the OBC can then clock the desired states in to the shiftregister using the serial bus driver ending with a set signal moving the data in the shift register from the serial input to the parallel output effectively setting the slot states. Should states change as the result of automated responses generated in the slot is self, such as a e-fuse being triggerd. The changed state will set and store an IRQ in the IRQ register. The IRQ register is effectively a D flip-flop used to store the interrupt until such a time that the OBC can read it.

The biggest issue with this design is the complexity, it requires a lot of hardware to work. A custo marbitration bus. Four bus drivers effectively creating six buses. Two serial buses for each OBC on the module side to control the bus driver ICs. As well as two custom buses on the backplane to control the state register. Each module slot also requires address matching hardware, a state shift register and IRQ logic. This is effectively the main bulk of all the electronics on the backplane.

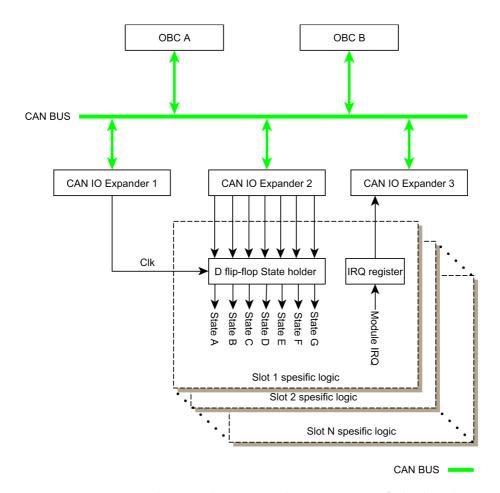

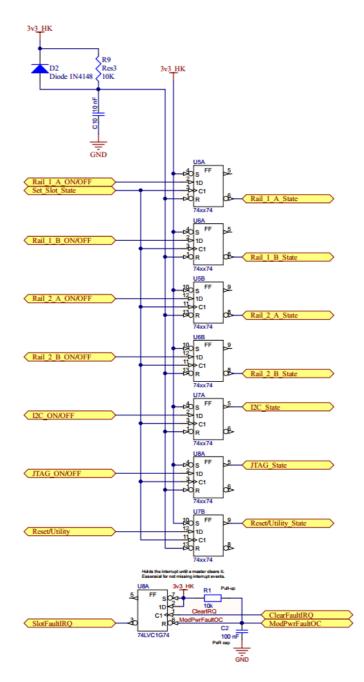

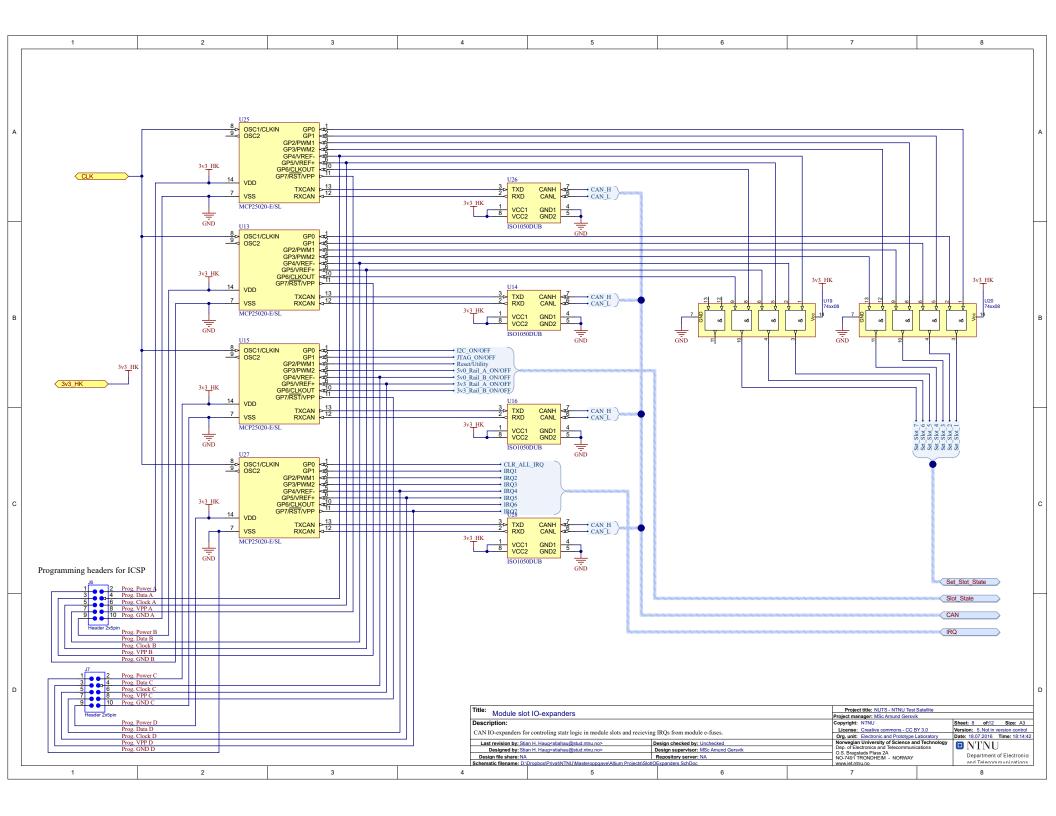

#### Proposed changes

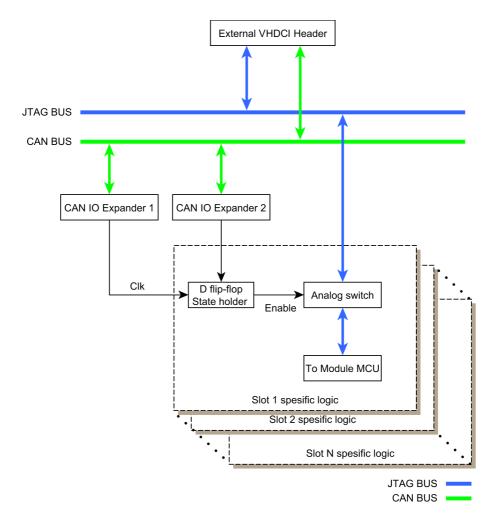

As discussed in section 3.1.1 changing the data bus to a CAN bus based data bus would remove the need for arbitration between the two OBCs as the arbitration would be inherent in the CAN bus standard based on the OBCs defined CAN bus address. However this would only work for setting the states of the backplane slots if these the setting of said states where subject to this arbitration. It would not be desirable that an OBC could have access to the system state register bus even though it had lost arbitration inherent in the CAN protocol. However, using the CAN bus to access and set the logic states of the backplane would make setting the backplane states subject to the arbitration in the CAN bus. In figure 3.6 CAN IO expanders are connected directly to the CAN bus on the backplane and controllable from the OBCs via the CAN bus. The CAN IO expanders are quite simple ICs with a CAN bus port on the one side and eight I/O pins on the other side. The I/O pins can then be set high or low by sending a message via the CAN bus to the CAN IO expander. In figure 3.6 D flipflop are used as state holder. Each slot has a single D flip-flop for each state effectively storing the state. CAN IO expander number 1 has it's first output pin connected to the clock input of all D flip-flop's specific to the first slot. The second pin connected to all D flip-flop's specific to the second slot and similarly for all consecutive slots. This allows a message to be sent from an OBC over the CAN bus setting the CAN IO expander pin high effectively clocking any states that may be on the input of the D flip-flop to the outputs storing those states in the D flip-flop's. What states are stored are given by CAN IO expander number 2 which has its outputs connected in parallel to all slots. CAN IO expander number 3 is configured to receive inputs. If an IRQ is raised a message is generated and put on the CAN bus detailing what input was sensitized and allowing both OBCs to read it.

This backplane houskeeping system allows the six serial buses shown in figure 3.5 to be replaced by a single CAN bus connection. It also does away

Figure 3.5: Figure showing the current version of the houskeeping electronics used to set module slot states for controlling backplane slot functionality.

the need for a custom arbitration bus and the bus driver logic. Further more it makes use of the standard CAN protocol and removes the need for implementing custom serial communication protocols in the OBC. It also allows the slot header it self to be reduced in pin count and makes it possible to remove connections between the OBC and the backplane that was only used by the OBC making a more universal connection between modules and the backplane possible as proposed in section 3.1.6. These changes would also make it possible to add a third OBC should it be desirable to make a system based on three ore more OBCs voting for fault tolerance in a later iteration of the satellite.

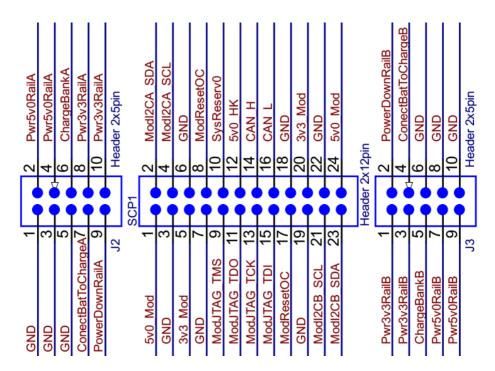

#### **3.1.6** Module slot requirements

As briefly discussed in section 2.1.1 a module is a unit that slots in to the backplane in one of several slots. A module normally consists of a circuit board that performs a specific function or fulfills a certain role in the satellite system as a whole. A module slot on the backplane itself is basically a header that provides the module with the necessary physical connections to perform its task in the satellite system.

#### Current state

In the current system there are three distinct slot types. Slave slots, master slots and a single EPS slot. The slave slot is the most basic slot. The system has four identical slots of this type and the header in this slot provides a slave module with the necessary connections when it comes to power, data buses and the programming bus. As well as some utility connections for use in a lab environment. The second slot type is the Master slot. It provides the same connectivity as the slave slot but has an extended header in order to facilitate the use of the arbitration, address and register buses described in section 3.1.5. The EPS slot is the only slot that needs extra pins to provide power from the module as all other modules receives power through the slot header. The extra power pins providing power to the backplane and the other modules via the backplane also comes in the form of an extended header. All three slots have different sized headers to prevent a module of the wrong type to be inserted in to a slot. An important note is that the headers are designed with diagonal split with equal pins on each side. This makes it possible to rotate a module  $180^{\circ}$  in a slot.

The main drawback of this design is the predefined headers limiting the number of choices when it comes to module placement and also requires

Figure 3.6: Figure showing the proposed new version of the houskeeping electronics used to set module slot states for controlling backplane slot functionality.

three different headers with with different schematics and different layout requirements.

#### **Proposed changes**

In the new design a single uniform slot and header layout for all module types is proposed. In section 3.1.5 the proposed changes to the backplane control system involve replacing the current serial buses used for backplane control functions and arbitration with a control scheme based on messages over the CAN bus. This effectively removes the need for any additional pins in the header of the master slots making them identical to the slave slots. By including the extra pins used by the EPS to deliver power to the backplane in all the slots a uniform slot design can be achieved. This will greatly reduce the complexity in the schematic design and allow for reuse-ability in the PCB layout process simplifying the layout process.

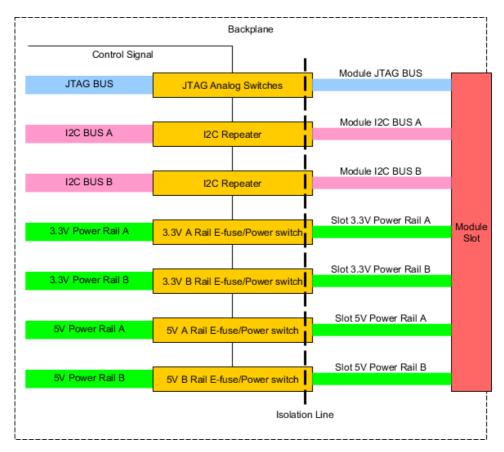

## 3.1.7 Fault isolation

As discussed in section 2.2 faults due to radiation in space may be unavoidable when using "of-the-shelf" electronics that are not radiation hardened in a satellite. It will ultimately lead to faults in the semiconductors in those components. This means that our options are limited when it comes to Fault-avoidance. Efforts are better spent on Fault-tolerance. This means that by design we can tolerate faults in our system and still perform the mission critical tasks of the satellite. The satellite design already provides fault-tolerance in key areas. The EPS provides redundant power rails. and using a set of two OBCs, each with its own radio, also provides redundancy. The backplane must facilitate these redundancies and provide fault isolation. Fault isolation is a type of fault-tolerance. By isolating a fault to a single module and preventing it or a potential resulting error or failure in the module from spreading to other modules the system becomes more fault-tolerant.

#### Current state

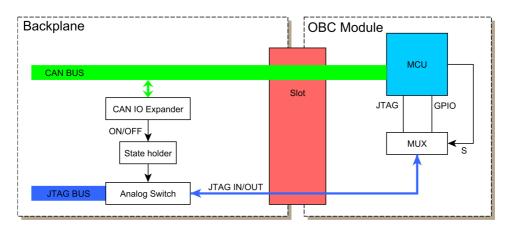

As discussed in section 3.1.3 the backplane provides redundant power of both 5.0V and 3.3V to each module. As discussed in section 3.1.1 the current  $I^2C$  data bus is also designed with redundancy in mind consisting of two parallel buses. It also features I2C repeaters that features electrical isolation and can be shut down in order to disconnect the  $I^2C$  bus from the module should a failure be present on the module side. Figure 3.7 shows isolation towards

Figure 3.7: The current isolation towards module slots to prevent fault propagation.

the module slot. It also shows analog switches disconnecting the JTAG bus from the module providing further isolation.

## Proposed changes

The approach to fault isolation and module fault tolerance achieves acceptable fault confinement in modules and requires little change to be implemented in the new design. As shown in figure 3.8 the proposed change to a CAN bus as data carrier mentioned in section 3.1.1 is isolated through the use of a CAN transceiver. The can transceiver operates without any input from the backplane control signals. Should a fault present itself that inhibits a module from using the CAN bus the module is effectively dead and can be disconnected by powering down the power rails to that module. In figure 3.8 a utility signal has been added. This is a signal that can be used for utility functions towards the module. It should be controllable from the an OBC via the CAN bus as described in section 3.1.5. Typically this signal can be used to hard reset a module or it can be used to deploy the antennas on the antenna module should they fail to deploy. The  $I^2C$  bus has been reduced to a single bus dedicated to collecting sensor data and is electrically isolated from the module through an  $I^2C$  repeater as in the current design.

## 3.1.8 Proposed design summary

A new design is proposed where the dual  $I^2C$  bus is removed as main data bus and replaced with a single CAN bus. A separate sensor-bus using  $I^2C$ provides domain separation between the data bus and sensor bus. The introduction of CAN bus enable us to remove all custom arbitration logic on the backplane as arbitration with priority in inherent in the CAN bus protocol. Each module slot will receive its own state holders controlled by simple CAN IO-expanders connected to the CAN bus. This allow us to remove the custom designed shift-register based serial data bus currently used for slot control. It also allows any module connected to the CAN bus to control the backplane. Each module slot on the backplane will be redesigned with a uniform slot header design enabling reusability in the PCB layout process and making the design more flexible while reducing complexity.

Figure 3.8: The proposed new isolation towards module slots to prevent fault propagation.

# Chapter 4 Design implementation

This chapter will cover the actual implementation of the changes to the backplane design proposed in chapter 3. The different ways to implement the proposed changes will be evaluated and criteria such as fault tolerance will be reviewed for the new implementations. The chapter will make some references to schematics and relevant parts of the schematics will be included in figures in this chapter. The complete schematics can be found in the appendix in chapter 9. Lastly this chapter will suggest a test approach and methodology to verify the design.

# 4.1 Backplane implementation overview

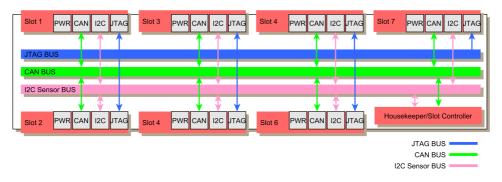

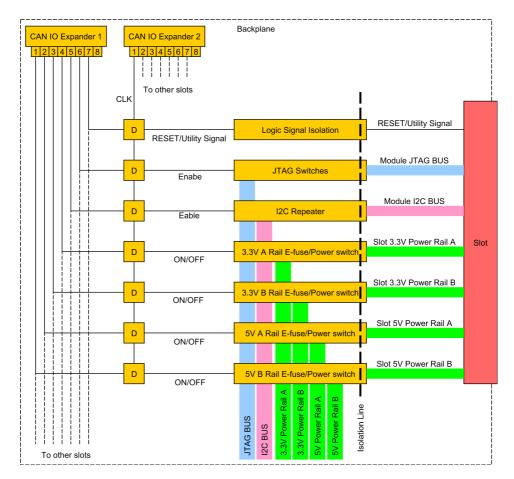

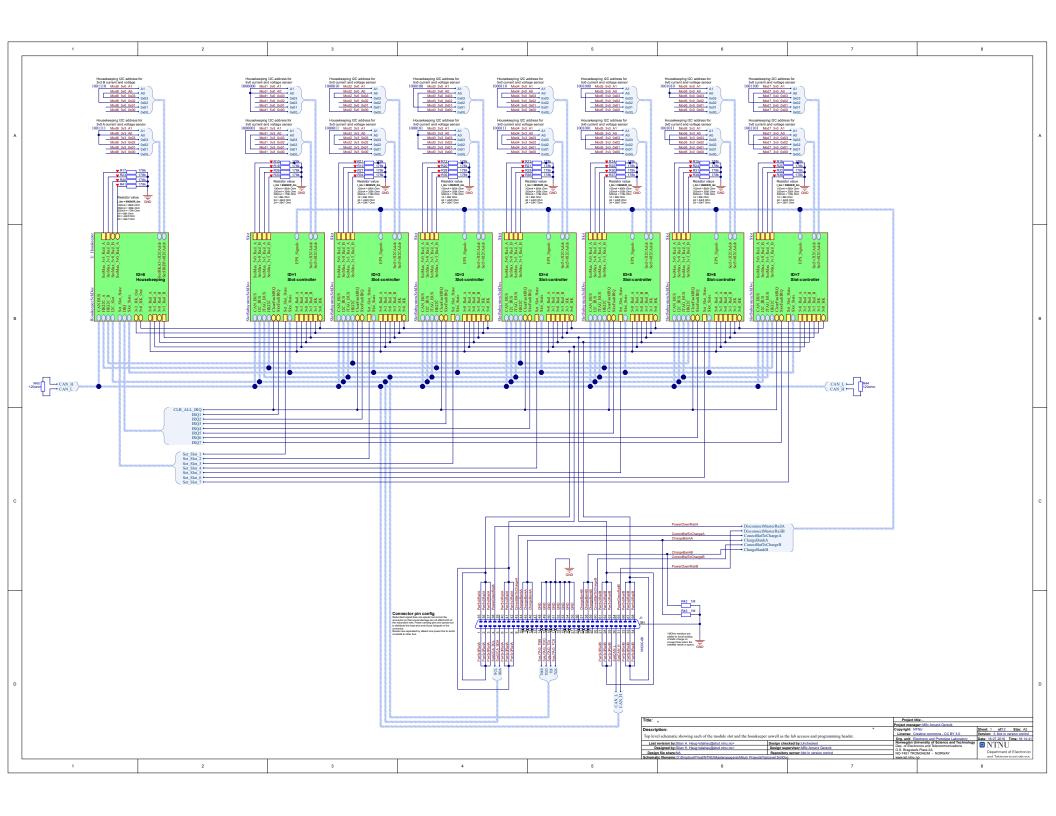

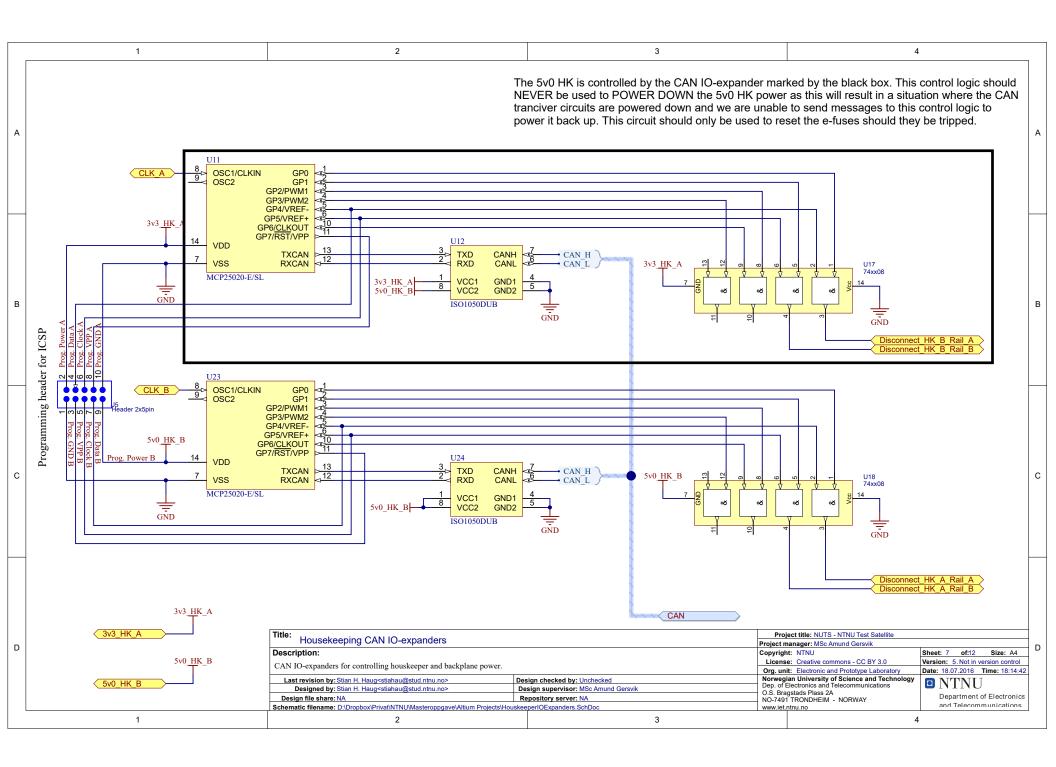

An overview showing the new revision of the backplane design is presented in Figure 4.1. A total of seven module slots are marked in red with an eighth virtual module slot containing the housekeeping logic. The housekeeper can be addressed from any module slot allowing any slot to control parameters of any other slot. In practice only the OBS modules connected will be controlling slot functions.

# 4.2 Data carrier (implementation)

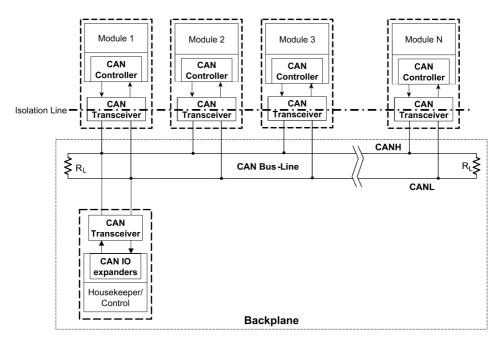

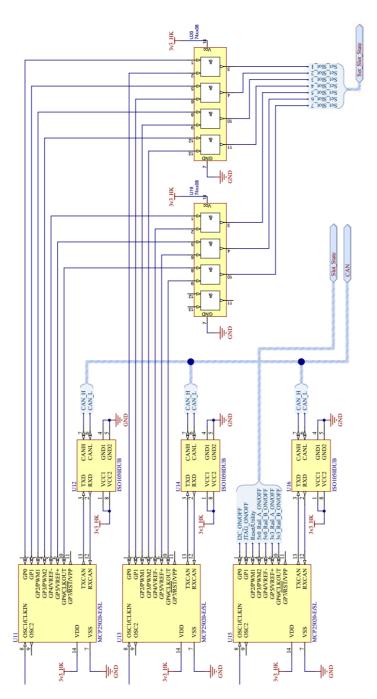

As proposed in the previous chapter section 3.1.1 the new data carrier is implemented as a CAN bus. Figure 4.2 shows each module having a CAN controller and a CAN transceiver. The CAN controller implements the CAN protocol and CAN functionality towards the user of the CAN bus. In the satellite modules talking to the CAN bus the Atmel AVR UC3C 32-bit Flash Microcontrollers [9] are used. These microcontrollers have the CAN

Figure 4.1: Overview of the new backplane design implementation.

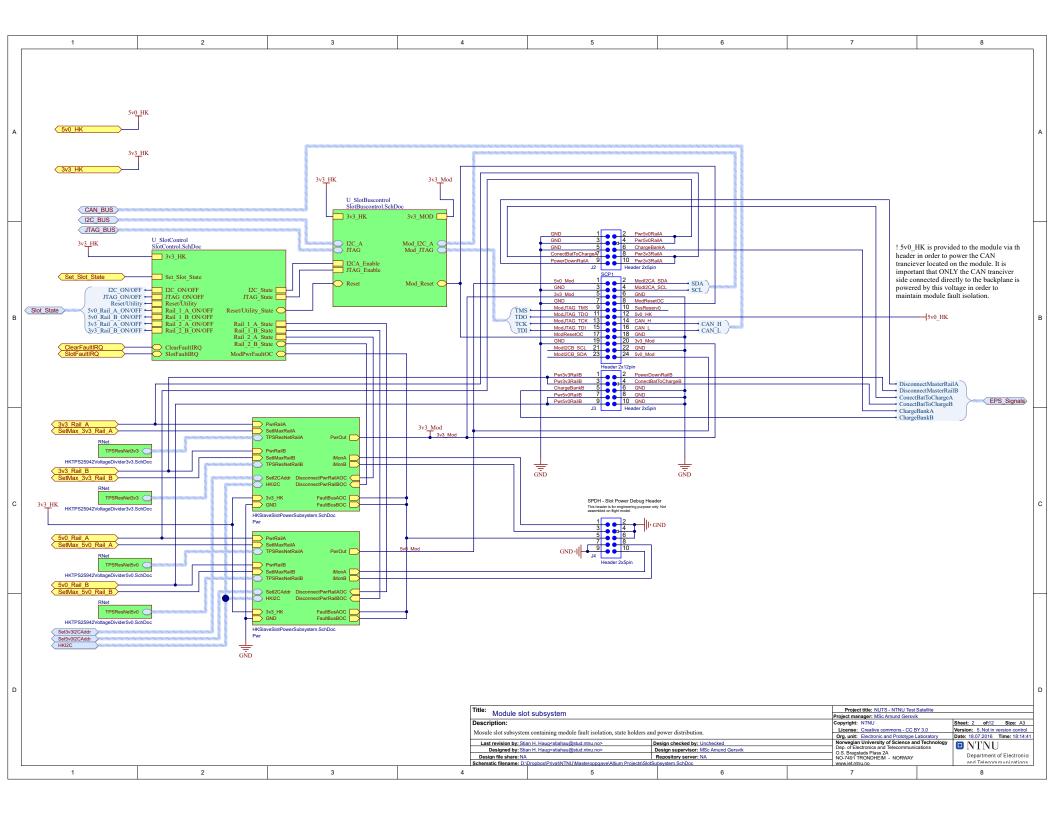

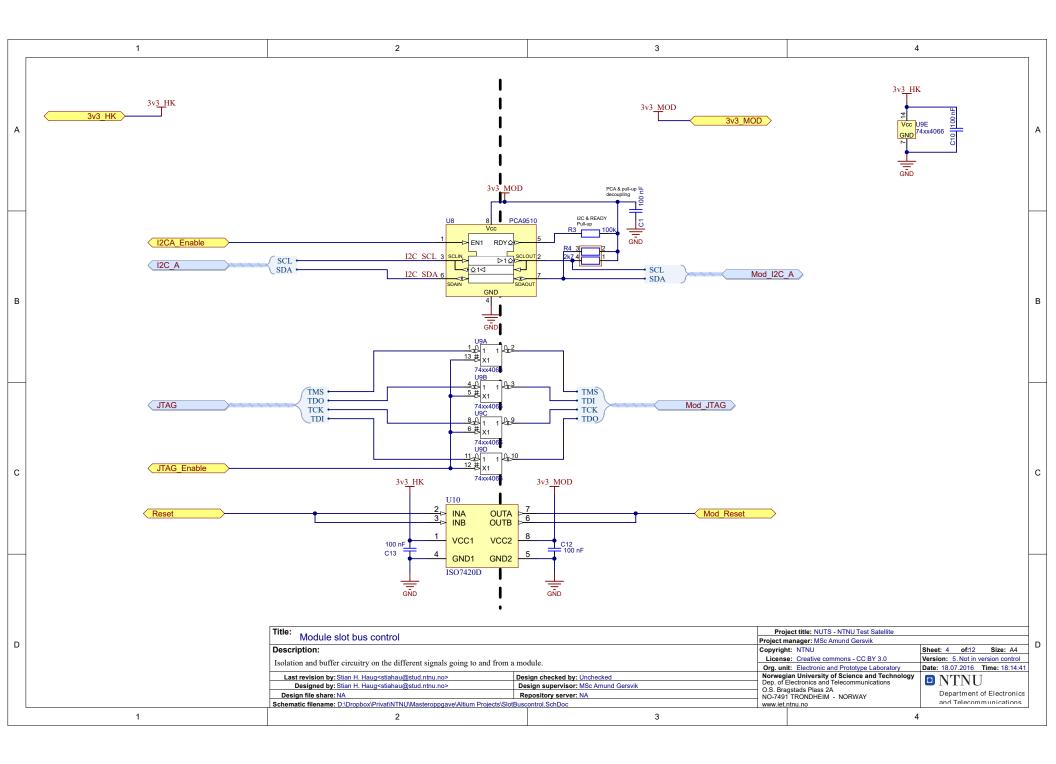

controller built in to the microcontroller taking care of the CAN data link layer as per the ISO 11898-1 standard [7]. When it comes to the CAN transceivers the ISO1050 Isolated CAN Transceiver [10] based on the ISO 11898-2/3 Medium Access Unit [11] standards is used. It provides electrical isolation between the module and the backplane and performs the level translations between the CAN controller providing serial data through RXD and TXD serial data pins and the CAN bus data lines on the backplane who uses CAN H and CAN L signals. The CAN bus simply consists of two datalines on the backplane with end termination resistors. Further more in figure 4.2 the housekeeping is shown as a virtual module. The housekeeping logic itself is designed as a module but is not physically placed on a different PCB. However, the structure and isolation is designed as a module. This will be further discussed in section 4.6.

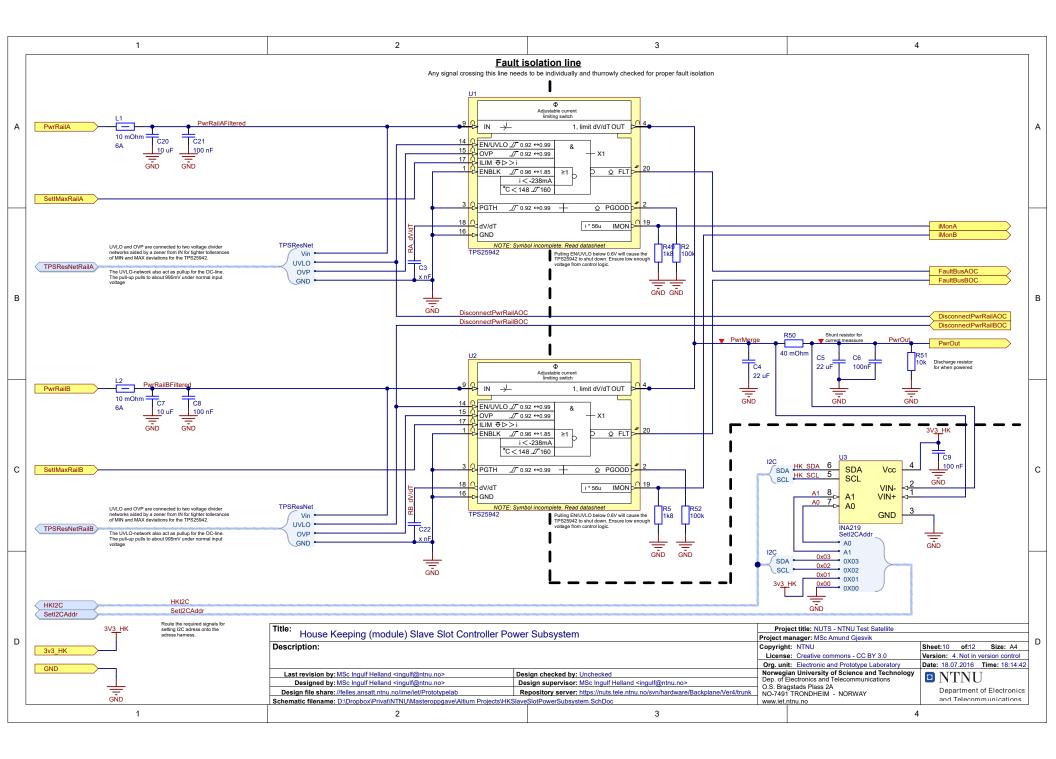

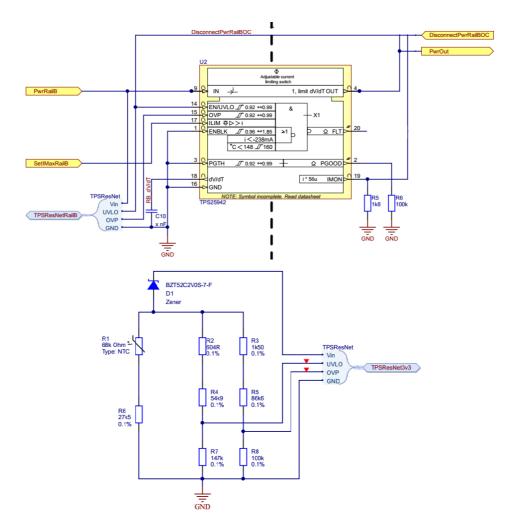

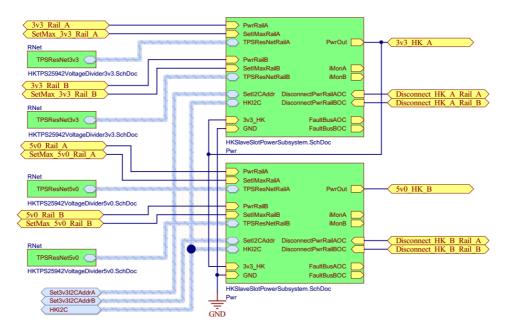

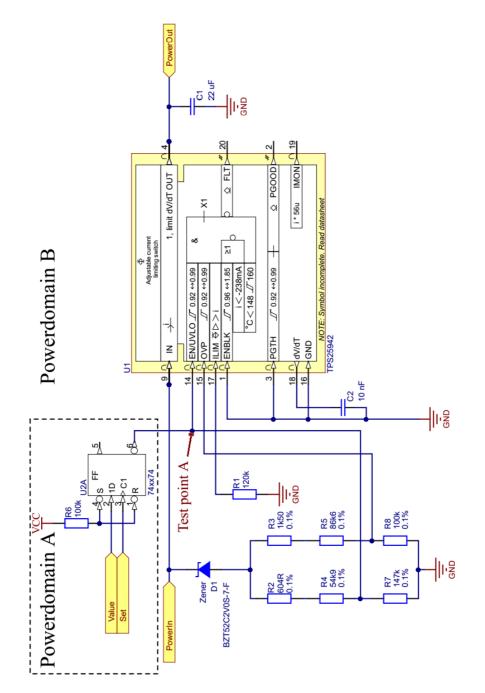

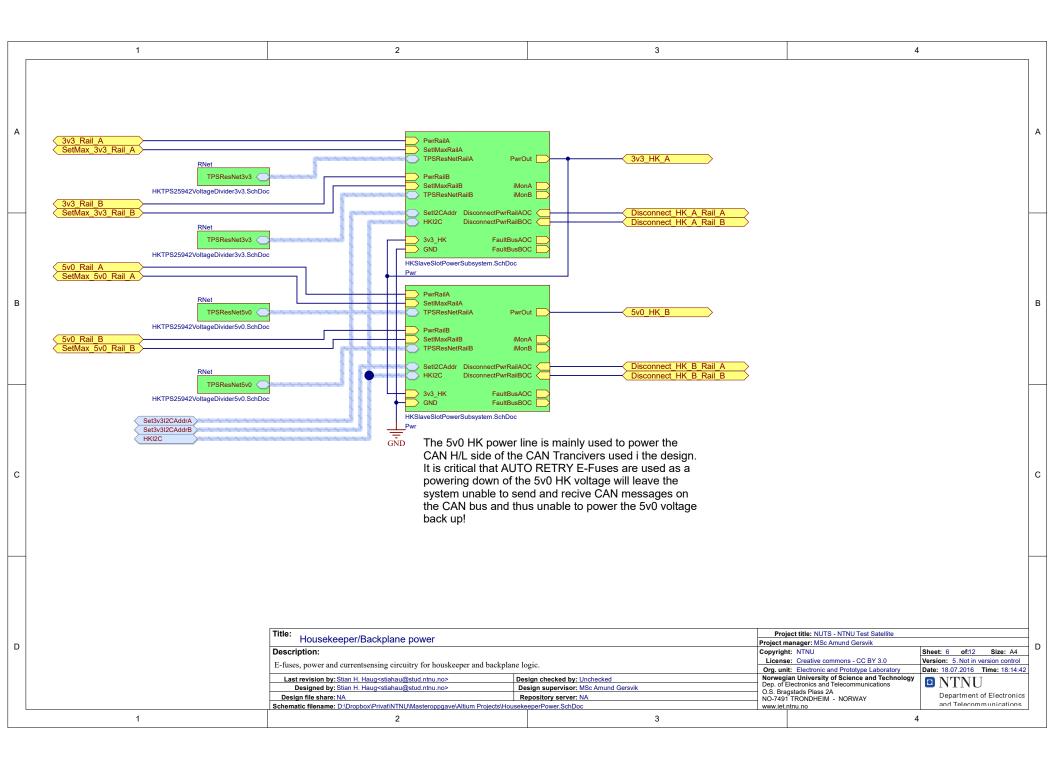

# 4.3 Power distribution (implementation)

When it comes to power distribution as mentioned in section 3.1.3 the design needs very few changes. Most of the changes done are with respect to the control signals that will be covered in section 4.6. The implementation of the e-fuse used on the backplane is shown in figure 4.3. The circuit based on the TPS25942A eFuse IC from Texas Instruments [12]. The integrated back-toback FETs provide bidirectional current control well suited for systems with multiple power sources. The power rail delivers power on the input pin (9) and delivers power through the output pin (4). The overpower protection is set through a resistor network connected to the EN/UVLO pin (14) and OVP (15) pin respectively. The resistors connected to EN/UVLO are used for setting programmable undervoltage lockout threshold. An undervoltage event on the input will open the internal FET disconnecting the rail from

Figure 4.2: New implementation of the data carrier making use of CAN bus. The figure shows how the modules are connected to the backplane bus while placed off board. And the "viritual" module for housekeeping implemented on the backplane.

the output. Similarly the resistors connected to the OVP pin is used to set the programmable overvoltage protection threshold. An overvoltage event will also open the FET disconnecting the output from the supply rail. The ILIM pin (17) is used to set the overload and short-circuit current limit. This is done by connecting a resistor of a size determined by equation 4.1 to ground.

$$I_{(LIM)} = \frac{89000}{R_{(ILIM)}}$$

(4.1)

When the internal FET has been opened either by over-voltage, undervoltage or over-current the e-fuse can be reset by pulling EN/UVLO low and then back high. If the voltage on EN/UVLO is held below 0.6V the e-fuse will be held in an off state keeping the rail disconnected from the output. Driving EN/UVLO to ground will be discussed in section 4.6 as this is considered part of the houskeeping/backplane control logic. Component C10 is a capacitor used to regulate the ramp up time of the output and will be determined by each modules requirement.

The implementation shown in figure 4.3 represents the power delivery implementation for a single power line in a single module slot. Each module slot has four of these circuits. One for each of the two 3.3V power lines and one for each of the two 5.0V power lines. With a total of 7 module slots in the design the implementation outlined in figure 4.3 is repeated 28 times trough out the design with varying resistor network values. As well as four additional times for the viritual backplane houskeeping module for a total of 32 times.

The actual power lines consist of four lines traced in parallel from one side of the board to the other side of the board connecting to each of the module slots on the away. Every power line is connected both to outbound and inbound pins on the header in each slot as discussed in section 4.7. This allows the EPS module to be connected to any of the slots. It also allows more then one EPS to be installed in the backplane provided the EPS modules used can be connected in parallel.

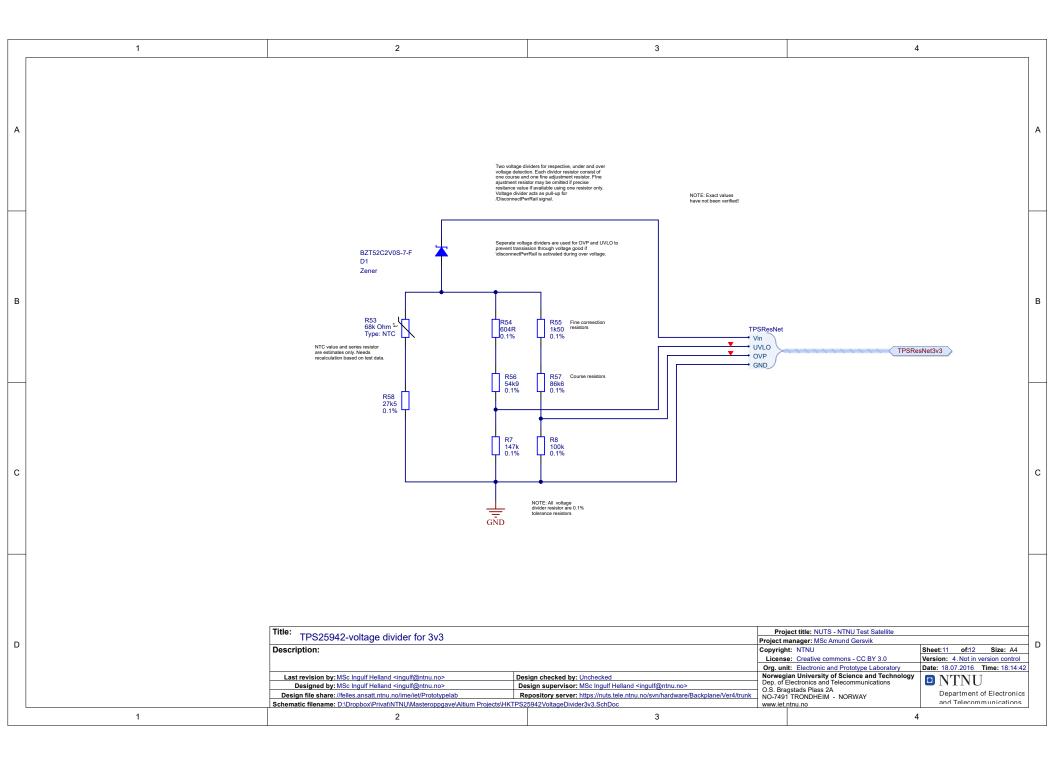

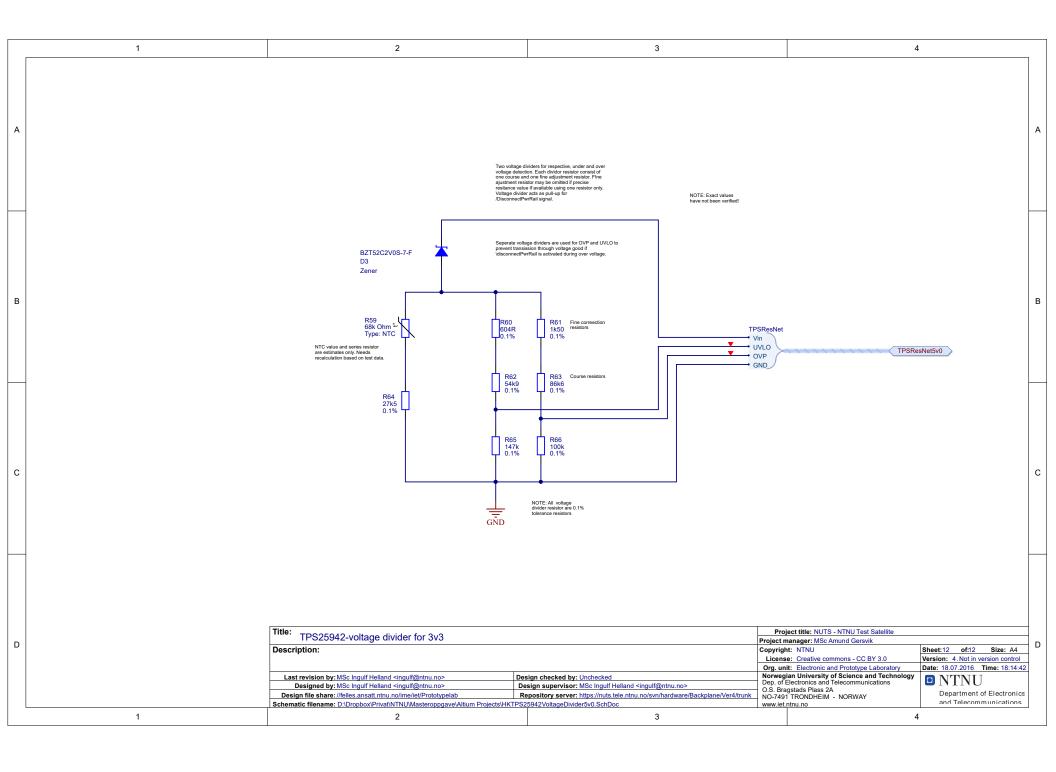

# 4.4 Sensor network (implementation)

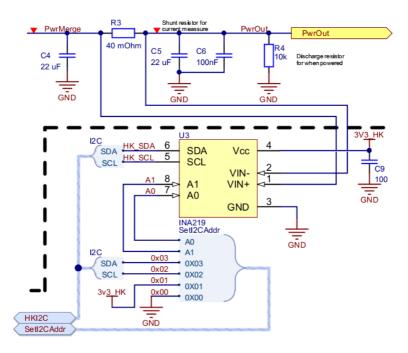

As described in section 4.3 four power lines are provided to each module slot. After the e-fuse the two lines of same voltage are joined and provides a single point where the current flow can easily measured on its way to the module slot header. Figure 4.4 shows the schematics where the current sensor is used. The INA219 is a quite simple component with a set of serial

Figure 4.3: Shows the E-fuse implementation in the power distribution on the backplane. Simplified schematics showing only e-fuse related components. Complete schematic can be found in the appendix.

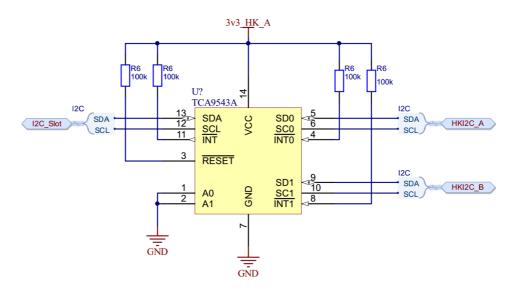

data pins (SCL on pin 5 and SDA on pin 6) in the form of an  $I^2C$  bus connection. The I<sup>2</sup>C bus can be used by any master to request a current measurement. The INA219 gets a current readout by measuring the voltage difference between pin 1 and 2 connected over a 40mOhm shunt resistor placed in the power line. The  $I^2C$  address can easily be set to one of 16 different addresses based by connecting the A0 (7) and A1 (8) pins to either SCL, SDA, VCC or GND. This is done in the top level schematics in order to easily being able to change the values if needed. One of the problems addressed in section 3.1.2 was the limited number of addresses the INA219 has at its disposal. We must be able to measure the current consumption at two different points in each of the module slots as well as two places in supply for the virtual housekeeping module. The his results in the number of required implementations of the schematics in figure 4.4 reaching 16 in total. We know that the INA219 is used in the EPS design as well putting the total number of sensors over the limit of 16 address spaces. To overcome this an  $I^2C$  MUX is used as shown in figure 4.5. This moves the INA219 sensors on the backplane to a higher address space avoiding conflict with any components using a similar address space on the modules.

Figure 4.4: Simplified schematics showing how the INA219 sensor is used to measure power consumption. Complete schematics can be found in the appendix.

Figure 4.5:  $I^2C$  multiplexer used to increase and separate the address space of the sensors on the backplane and the modules.

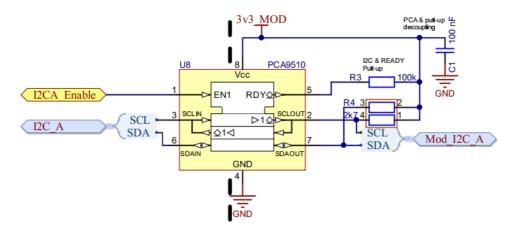

The current sensors on the backplane are all connected to the  $I^2C$  bus. This bus is made available to all the modules through the module slot header as shown in section 4.7. This allows both masters and slaves to connect to the same bus and either provide information or request it. This structure allows any master located on any module to request any sensor data individually from any of the sensors connected to the sensor bus. In the current design the only masters in the system are the two OBCs. However, it is possible to allow the microcontrollers located on other modules such as theADCS to be connected to the  $I^2C$  bus allowing functions such as tracking and orientation controls of the satellite to be accessed over the  $I^2C$  bus in the event of a main data bus failure.

# 4.5 Lab access and programming (implementation)

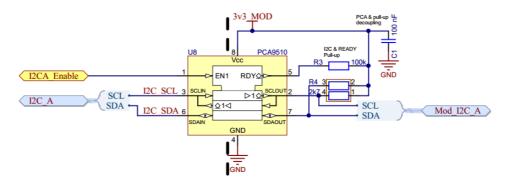

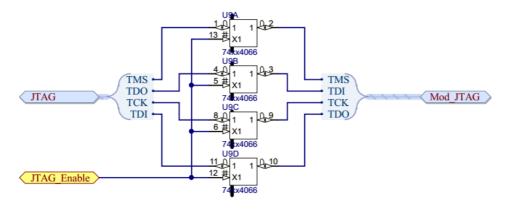

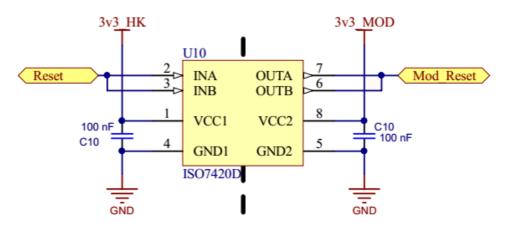

Lab access is provided through a single VHDCI (very-high-density cable interconnect) header as shown in figure 4.7. Providing 68 pins it allows the satellite to be accessed in all states of assembly. Especially once the satellite is fully assembled the VHDCI header provides access to the sensor bus, CAN bus, power rails, battery charging points and battery control signals. It also has available pins if it is later decided that more test points need to be connected to the header making them available in a fully assembled state.