# Development Tools for the Xilinx Zynq-7000 SoC

Design of a Development Framework and System Interaction Method for Embedded Systems on the Zynq-7000 SoC

### Roland Peterer Christian Schmid

Master of Energy and Environmental Engineering

Submission date: July 2016

Supervisor: Lars Einar Norum, ELKRAFT

Norwegian University of Science and Technology Department of Electric Power Engineering

#### MASTER THESIS

# Development Tools for the Xilinx Zynq-7000 SoC

Design of a Development Framework and System Interaction Method for Embedded Systems on the Zynq-7000 SoC

Authors: Christian SCHMID and Roland PETERER

Supervisor: Prof. Dr. Lars NORUM

Department of Electric Power Engineering

July 1, 2016

# Declaration of Authorship

We, Christian Schmid and Roland Peterer, declare that this thesis titled "Development Tools for the Xilinx Zynq-7000 SoC" and the work presented in it are our own. We confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where we have consulted the published work of others, this is always clearly attributed.

- Where we have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely our own work.

- We have acknowledged all main sources of help.

- Where the thesis is based on work done by ourself jointly with others, we have made clear exactly what was done by others and what we have contributed ourself.

Trondheim, July 1, 2016

$"Any \ sufficiently \ advanced \ technology \ is \ indistinguishable \ from \ magic."$

Clarke's Third Law

#### Abstract

#### Development Tools for the Xilinx Zynq-7000 SoC

Design of a Development Framework and System Interaction Method for Embedded Systems on the Zynq-7000 SoC

by Christian Schmid and Roland Peterer

The evolution of processing system hardware provides powerful and versatile implementation platforms for system engineers such as the Xilinx Zynq-7000 SoC. Due to this new capable hardware, advanced and more demanding control systems become feasible. However, the complexity of such targets has risen enormously. They rely on special features and enhancements to enable the necessary power for complex tasks. In order to use those, a profound knowledge of the target platform is needed.

In order to ease the usage of a hardware platform, a comprehensive development framework was set up. It allows the usage of the commonly known approach to design and outline control algorithms with Matlab/Simulink. The developed control method can then be tested in combination with the desired hardware. The framework guides the system engineer in generating the necessary code, the setup of the target hardware and the deployment of the realized control design. Methods to test and interact with the running system on the target in realtime are introduced.

A simple way of interacting with the completed system was realised. It allows the change of parameters and the monitoring of signals in the system during run time. Furthermore, recording transient step responses is possible. By utilizing standard Ethernet protocols as a base, the interaction can take part on a remote system in a GUI. Other means of interaction can be implemented due to the open data interface. This enables the supervision and manipulation of the running target from afar.

# Acknowledgements

We would like to thank our Thesis Advisor Prof. Dr. Lars Norum for his support and time. Also, our gratitude goes to our Master's Study Advisor Prof. Dr. Benno Bucher who supported us throughout our studies.

Further we thank Anirudh Budnar Acharya and Eirik Haustveit for the collaboration and exchange of ideas.

Additionally we thank Tomas Richter for the interesting discussions and support during the MathWorks course "Programming Xilinx Zynq SoCs with Matlab and Simulink"

Roland would like to express his sincere gratitude to the *Hirschmann Stiftung* for the financial support. It would not have been possible to enter this exchange adventure without its support.

# Contents

| D            | eclar | ation o | of Authorship                                                    | iii       |

|--------------|-------|---------|------------------------------------------------------------------|-----------|

| A            | bstra | ct      |                                                                  | vii       |

| $\mathbf{A}$ | ckno  | wledge  | ments                                                            | ix        |

| $\mathbf{G}$ | lossa | ry and  | Abbreviations                                                    | xv        |

| 1            | Intr  | oducti  | ion                                                              | 1         |

|              | 1.1   | Overv   | iew over the Document                                            | 1         |

|              | 1.2   | Projec  | et Environment                                                   | 1         |

|              | 1.3   | Purpo   | se of the Project                                                | 2         |

|              | 1.4   | Introd  | uction to Embedded Systems                                       | 2         |

|              | 1.5   | Short   | Overview over the Xilinx Zynq-7000 SOC and the Digilent ZedBoard | 3         |

| 2            | Pro   | blem I  | Definition and Functional Specification                          | 5         |

|              | 2.1   | Develo  | ppment Framework                                                 | 5         |

|              |       | 2.1.1   | Functional Requirements for the Development Framework            | 6         |

|              | 2.2   | Remot   | te System Interaction                                            | 6         |

|              |       | 2.2.1   | Functional Requirements for the Remote System Interaction        | 7         |

|              | 2.3   | Accom   | panying Documentation                                            | 7         |

|              | 2.4   | Guide   | lines and other Specifications                                   | 7         |

| 3            | App   | oroach  | and Elaborated Solution                                          | 9         |

|              | 3.1   | Prosec  | cuted Approach                                                   | 9         |

|              | 3.2   | Develo  | opment Framework                                                 | 9         |

|              |       | 3.2.1   | Custom Reference Design                                          | 9         |

|              |       | 3.2.2   | Main Simulink Project                                            | 10        |

|              |       | 3.2.3   | Simulink Library                                                 | 13        |

|              | 3.3   | Remot   | te System Interaction                                            | 13        |

|              |       | 3.3.1   | Getting and Setting of Parameters                                | 14        |

|              |       | 3.3.2   | Logging of Slow Time Series                                      | 17        |

|              |       | 3.3.3   | Step Response Analysis of Fast Signals                           | 18        |

|              |       | 3.3.4   | System Control                                                   | 20        |

|              |       | 3.3.5   | User Interface                                                   | 21        |

| 4            |       | _       | with the Development Framework and Remote System In-             |           |

|              | tera  | action  |                                                                  | <b>23</b> |

|              | 4.1   |         | quisites                                                         | 23        |

|              | 4.2   | Develo  | opment Framework                                                 | 24        |

|              |       | 4.2.1   | A Note on Signals and the PL Clock Frequency                     | 24        |

|              |       | 4.2.2   | Prepared Peripherals                                             | 25        |

**7**9

|   |     | 4.2.3         | User Function Canvases                                                 | 26         |

|---|-----|---------------|------------------------------------------------------------------------|------------|

|   |     | 4.2.4         | Usage of the FiFo Buffer                                               | 28         |

|   |     | 4.2.5         | Usage of the Watchdog                                                  | 29         |

|   |     | 4.2.6         | Implementation of the User Functions                                   | 29         |

|   |     | 4.2.7         | Simulation of the whole Model                                          | 29         |

|   |     | 4.2.8         | Synthesis, Code Generation and Deployment                              | 30         |

|   |     | 4.2.9         | Realtime On-Target Testing                                             | 31         |

|   |     | 4.2.10        | Performance of the User PS Functions                                   | 31         |

|   |     | 4.2.11        | Notes on Modification outside the User Canvases                        | 32         |

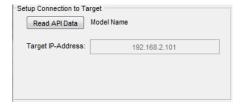

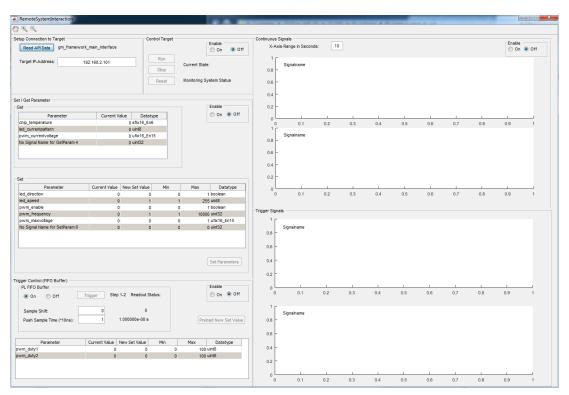

|   | 4.3 | Remot         | e System Interaction                                                   | 33         |

|   |     | 4.3.1         | Usage of the Lianx Simulink Blocks                                     | 33         |

|   |     | 4.3.2         | Generation of the PS Executable and Readout of API Parameters          | 36         |

|   |     | 4.3.3         | Deployment of the Generated Code                                       | 36         |

|   |     | 4.3.4         | Persistent User Function Deployment                                    | 36         |

|   |     | 4.3.5         | Usage of the GUI                                                       | 37         |

| 5 | Eum | thon D        | adranound Information                                                  | 41         |

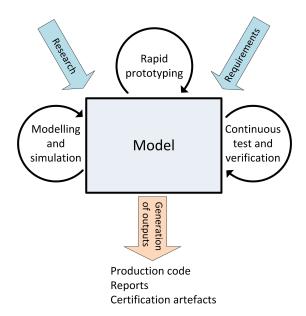

| Э | 5.1 |               | ackground Information  o/Simulink Workflow                             | 41         |

|   | 5.1 | 5.1.1         | Model Based Design                                                     | 41         |

|   |     | 5.1.1 $5.1.2$ | Matlab/Simulink as a Code Development Environment                      | 42         |

|   |     | 5.1.3         | Creation of a Reusable IP Core for Vivado                              | 43         |

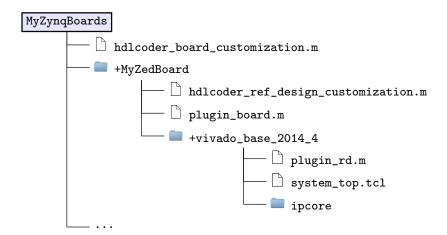

|   |     | 5.1.4         | Creation of a Custom Reference Design                                  | 43         |

|   |     | 5.1.4 $5.1.5$ | Writing a Custom Device Driver using Matlab/Simulink                   | 46         |

|   | 5.2 |               | lded System Software                                                   | 47         |

|   | 5.2 | 5.2.1         | Embedded Operating Systems                                             | 47         |

|   |     | 5.2.1 $5.2.2$ | Performance and Feature Considerations                                 | 49         |

|   | 5.3 | -             | as an Embedded Operating System                                        | 52         |

|   | 0.0 | 5.3.1         | Linux Variants for the ZedBoard                                        | 52         |

|   |     | 5.3.2         | Custom Linux Lianx                                                     | 53         |

|   |     | 5.3.2         | Customizing the Linux System Image                                     | 54         |

|   |     | 5.3.4         | Linux Device Tree and Drivers                                          | 55         |

|   |     | 5.3.5         | Performance Tweaking with Linux                                        | 56         |

|   |     | 3.3.3         | 1 oriormance 1 reasons man 2 man 1 v v v v v v v v v v v v v v v v v v |            |

| 6 |     |               | ation and Tutorials                                                    | <b>5</b> 9 |

|   | 6.1 | _             | of the ZedBoard and connecting with a Remote Console                   | 59         |

|   |     | 6.1.1         | Setup SD Card                                                          | 59         |

|   |     | 6.1.2         | Hardware Setup                                                         | 59         |

|   |     | 6.1.3         | Setup the Connection                                                   | 60         |

|   |     | 6.1.4         | Usage of the Remote Console                                            | 63         |

|   | 6.2 |               | g up the Demo Project                                                  | 64         |

|   |     | 6.2.1         | Overview over the Demo Project                                         | 64         |

|   |     | 6.2.2         | Setting up the Development Framework                                   | 64         |

|   |     | 6.2.3         | Implementing the Remote System Interaction                             | 65         |

|   | 0.0 | 6.2.4         | Running the Demo Model                                                 | 69         |

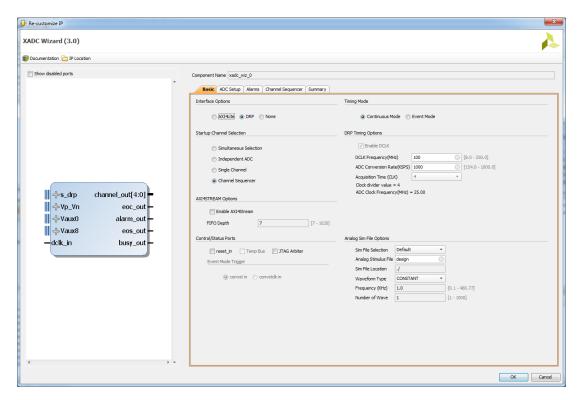

|   | 6.3 | _             | Zynq XADC in Custom Reference Design using Matlab/Simulink             | 71         |

|   |     | 6.3.1         | Create Vivado Reference Project                                        | 71         |

|   |     | 6.3.2         | Interface Definition                                                   | 74         |

|   |     | 6.3.3         | Register Reference Design                                              | 75         |

|   |     | 6.3.4         | Implement a Simulink Example Model                                     | 76         |

|   |     |               |                                                                        |            |

7 Conclusion and Expandability

|              | 7.1            | Summ     | ary                                          | 79 |

|--------------|----------------|----------|----------------------------------------------|----|

|              |                | 7.1.1    | The Development Framework                    | 79 |

|              |                | 7.1.2    | The Remote System Interaction                | 79 |

|              | 7.2            | Shortc   | omings, Improvements and Possible Extensions | 80 |

|              |                | 7.2.1    | The Development Framework                    | 80 |

|              |                | 7.2.2    | The Remote System Interaction                | 81 |

|              | 7.3            | Verdic   | t                                            | 82 |

| A            | $\mathbf{Add}$ | litional | Reading                                      | 83 |

| $\mathbf{B}$ | Che            | atshee   | ts                                           | 85 |

|              | B.1            | Linux    | Cheatsheet                                   | 86 |

|              | B.2            | Matlal   | Cheatsheet                                   | 87 |

| $\mathbf{C}$ | Digi           | ital Ap  | pendix                                       | 89 |

| Bi           | bliog          | raphy    |                                              | 91 |

# List of Figures

| 2.1  | Development Framework in which the User Function Resides in the PS and PL Frames |

|------|----------------------------------------------------------------------------------|

| 2.2  | Interaction GUI on a Remote Machine                                              |

| 3.1  | Model of the PS Part in the Framework                                            |

| 3.2  | Canvas of the User Run State                                                     |

| 3.3  | Remote System Interaction Simulink Communication Blocks 14                       |

| 3.4  | Get Parameters Block                                                             |

| 3.5  | Set Parameters Block                                                             |

| 3.6  | Continuous Signal Block                                                          |

| 3.7  | Step Response, FiFo Control Block                                                |

| 3.8  | Control Target Block                                                             |

| 4.1  | Connection setup for PMODs as Inputs                                             |

| 4.2  | Connection setup for PMODs as Outputs                                            |

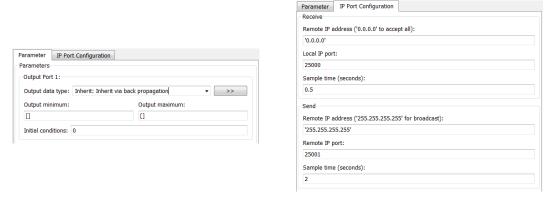

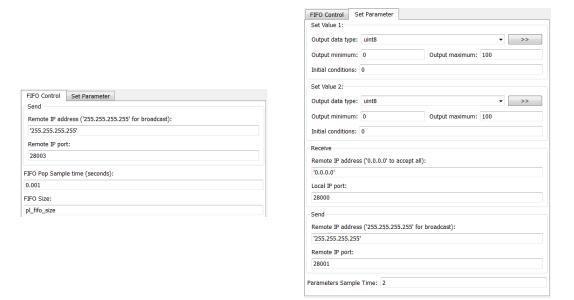

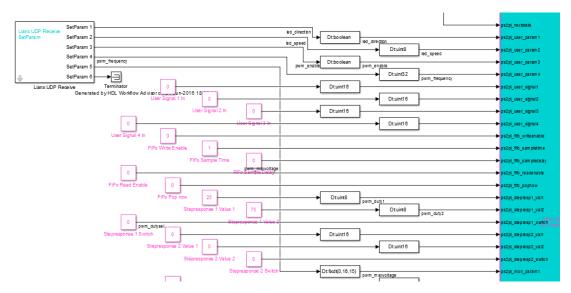

| 4.3  | Mask of Lianx UDP Receive SetParam Block                                         |

| 4.4  | Mask of Lianx UDP Send GetParam Block                                            |

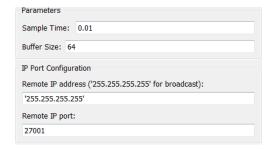

| 4.5  | Mask of Lianx Continuous Signal Block                                            |

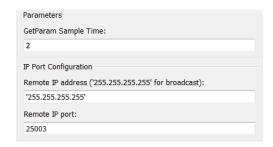

| 4.6  | Mask of Lianx Control Target StateControl Block                                  |

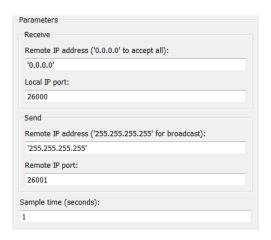

| 4.7  | Mask of Lianx PL FIFO Buffer PS Control Block                                    |

| 4.8  | GUI Start Screen                                                                 |

| 4.9  | GUI with loaded Modules                                                          |

| 4.10 | Additional Plot Control                                                          |

| 5.1  | Model Based Design Workflow                                                      |

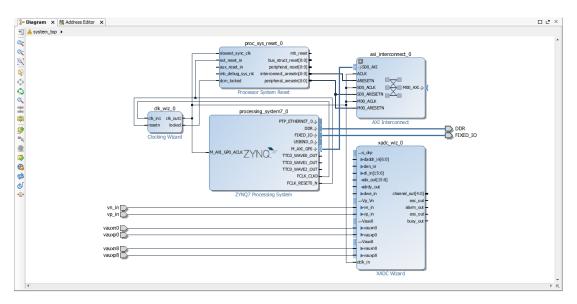

| 5.2  | Vivado Hardware Design with Simulink PL Canvas                                   |

| 5.3  | Claimed Folder Structure for Custom Reference Design 45                          |

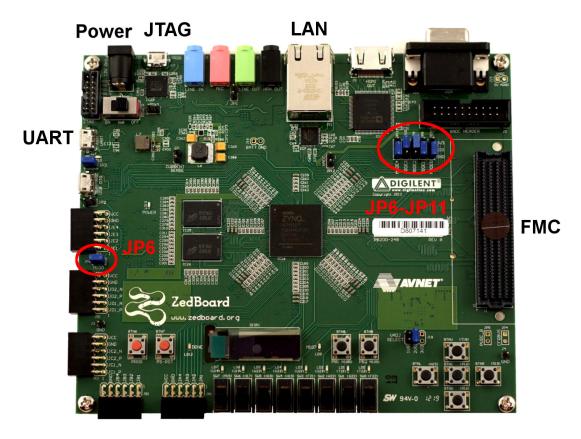

| 6.1  | ZedBoard with Connectors and Jumpers                                             |

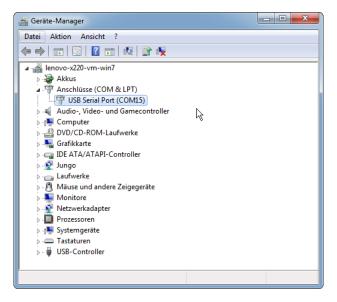

| 6.2  | Windows Device Manager with the COM-port of the ZedBoard USB-to-                 |

|      | UART Adapter                                                                     |

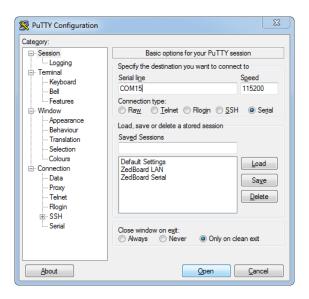

| 6.3  | PuTTY Settings for Serial Connection                                             |

| 6.4  | Remote Bash on the ZedBoard via a Serial Connection 62                           |

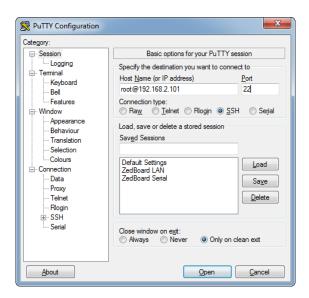

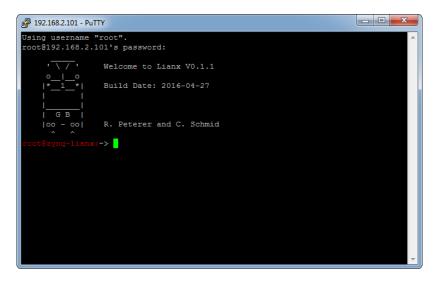

| 6.5  | PuTTY Settings for SSH Connection                                                |

| 6.6  | Remote Bash on the ZedBoard via a Ethernet Connection using SSH $$ . $$ 65       |

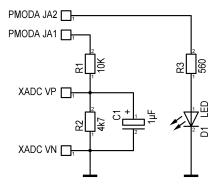

| 6.7  | Schematic of the Demo Project Hardware                                           |

| 6.8  | Connecting the Lianx Control Target State Control Block 65                       |

| 6.9  | Connecting the Lianx UDP Receive SetParam Block 66                               |

| 6.10 | Mask Parameters of the Lianx UDP Receive SetParam Block 67                       |

| 6.11 | Connecting the Lianx Continuous Signal and Lianx UDP Send GetParam               |

|      | Block                                                                            |

|      | Connecting the Lianx PL FIFO Buffer PS Control Block Outputs 68                  |

| 6.13 | Connecting the Lianx PL FIFO Buffer PS Control Block Inputs 68                   |

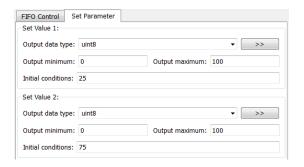

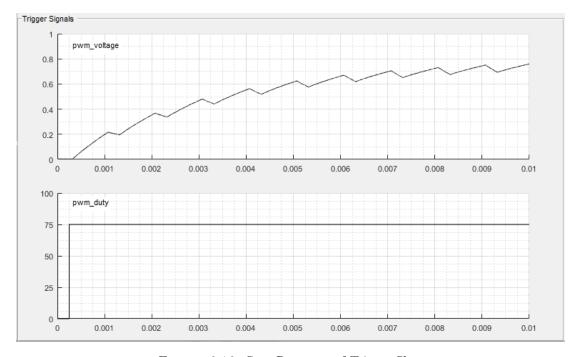

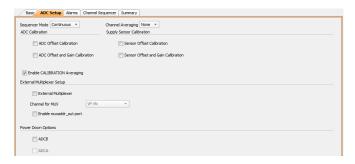

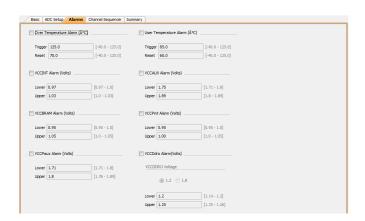

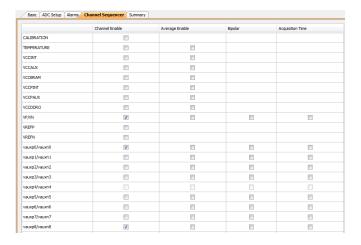

| 6.14 Mask Parameters of the Lianx PL FIFO Buffer PS Control 6.15 GUI Start Screen 6.16 Step Response of Trigger Shot 6.17 XADC Wizard Tab settings: Basic 6.18 XADC Wizard Tab settings: ADC Setup 6.19 XADC Wizard Tab settings: Alarms | 68<br>69<br>70<br>72<br>72<br>72 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 6.20 XADC Wizard Tab settings: Channel Sequencer                                                                                                                                                                                         | 73<br>73                         |

| List of Tables                                                                                                                                                                                                                           |                                  |

| 3.1 Blinking Patterns of State LED                                                                                                                                                                                                       | 11<br>13                         |

# Glossary and Abbreviations

#### Asymmetric Multi Processing (AMP)

On the cores of a processor, different software systems (bare-metal and/or operating systems) are running. See also: SMP.

#### Analog to Digital Converter (ADC)

Unit which measures an analog signal and passes the discretised value in digital form.

#### Advanced eXtensible Interface (AXI)

High performance data connection both in terms of frequency and transmitting capabilities. In the Zynq mainly used for communication between the PS and PL.

#### Bare-metal system

An embedded system software which implements the functionality directly without any operating system or similar setup.

#### Bitfile

Binary file containing a FPGA hardware description, similar to an executable software for processing systems.

#### Bourne-again Shell (Bash)

Standard shell for Linux.

#### Constraint File

Is used to set IO standards and chip pin mapping for Vivado projects.

#### **Cross-Compiler**

In contrast to normal compiling, cross-compiling prepares executable code for a different system architecture as the one it is compiled on.

#### Direct Memory Access (DMA)

Method of allowing the direct access of memory by peripherals without causing additional processor load.

#### Digital Signal Processing (DSP)

Special FPGA structures for complex digital signal operations.

#### Dynamic Reconfiguration Port (DRP)

IP core interface to interact with the hardwired XADC.

#### Field Programmable Gate Array (FPGA)

Digital integrated circuit with programmable gate arrays. The functionality is programmed and can be modified in the field in a hardware description language (HDL). Features vary heavily between FPGAs and are distinctly different from software-based, sequential processing systems.

#### First Stage Boot Loader (FSBL)

Program which runs directly on the underlying hardware, without an intermediate system software layer.

#### Framework

Set of tools and libraries as an environment. Used to ease and guide development of a given system and functionality.

#### General Purpose Input/Output (GPIO)

Pin which can be used as a simple input or output by the user. Usually, also combining several GPIOs and connecting them to special peripheral modules to implement communication buses is possible.

#### Graphical User Interface (GUI)

Program, website or other mean of a graphical manipulation interface to oversee and manipulate another program or system.

#### Graphical User Interface Design Environment (GUIDE)

Graphical user interface development environment of Matlab.

#### Hardware Description Language (HDL)

Language to describe the hardware to be implemented in an FPGA.

#### High Level Synthesis (HLS)

Process of generating a hardware description from an abstract algorithm design or model.

#### Integrated Development Environment (IDE)

Software which combines all needed tools and further simplifying mechanisms to allow the development and testing of code for a certain system.

#### Inter Integrated Cirquit (I<sup>2</sup>C)

Serial peripheral bus system for low-speed communication between several master and slave participants.

#### Joint Test Action Group (JTAG)

Industry Colaboration which defined a standard for in-cirquit programming and debugging. The interface allows low-overhead serial communication with a stopped or running system.

#### MicroBlaze

Separate processor realised within a programmable logic structure (Softcore).

#### Multicore Communication API (MCAPI)

Standard of communication methods between systems in an AMP scheme.

#### Multiplexed Input/Output (MIO)

Interface which connects multiple peripheral pins to processor signals. Configured via the PS [58, page 54]

#### **NEON**

The NEON engine (as an addition to the standard ARM functionality) provides Single Instruction Multiple Data (SIMD) facilities.

#### Open Asymmetric Multi Processing (OpenAMP)

Framework for using standardised AMP interaction methods between the involved software systems.

#### Operating System (OS)

System software which offers basic functionality like hardware drivers, file system support or network capabilities. Most often provides multitasking support and the use of standardised library functions for simpler development, as well as standard tools for working on a system.

#### Operator

Person who runs, oversees and manipulates a given system.

#### **PMOD**

Standard pin array interface using GPIOs.

#### Processing System (PS)

System which runs software code, including the processor and associated elements.

#### Programmable Logic (PL)

System which consists of programmable logic blocks and its connections. Hardware structures described in HDL run on this part of a device.

#### Register Transfer Level (RTL)

Description of data flow and operations in an abstract design.

#### Remote System

Computer or other device connected to the target. Used for interaction and control of the target by means of a GUI or a superordinated control system.

#### Second Stage Boot Loader (SSBL)

A more sophisticated, but still minimal system software. It is started by the FSBL and is responsible for initialising further hardware and start the bare-metal software or operating system.

#### Serial Peripheral Interface (SPI)

Serial bus system for communication between processor parts or peripherals. Less flexible than  $I^2C$ , it is mainly used for more local usage.

#### Simulink PL Canvas

Canvas to implement functionality of HDL part.

#### Symmetric Multi Processing (SMP)

On all cores of a processor the same system software is run.

#### System Engineer

Person who develops and modifies a system, e.g. a control system for a given appliance.

#### Target System

Platform on which an intended function is realised.

#### Tool Command Language (TCL)

Language to describe and script the initialisation of a Vivado project.

#### User Datagram Protocol (UDP)

UDP is a simple connectionless transmission protocol for computer networks.

#### Universal Asynchronous Reciever Transmitter (UART)

A very common serial communication protocol. Physical interfaces include RS-232 or EIA-485.

#### Universal Serial Bus (USB)

Standard serial connection for computer peripherals.

#### Watchdog

Monitoring system to determine if a system is still sane. If it isn't assured of propper functionality by a keep alive signal periodically, the system is put into a safe state by the watchdog.

#### XADC

Analog to digital converter integrated in the Xilinx Zynq-7000 SoC.

Additionally, a good list of common terms and abbreviations can be found in [9].

## Chapter 1

## Introduction

This chapter gives an overview over this document. It introduces the project context and its purpose. There is also a brief introduction into embedded systems in general and the used platform in particular to get the reader started.

#### 1.1 Overview over the Document

The introductory chapter gives the reader an overview over the whole document, as well as some general information about the project and the context it stands in. Next, the underlying problem and the resulting functional specification of the project are outlined. The Approach and Elaborated Solution chapter explains the approaches which were used to implement the desired functionality, while the Working with the Development Framework and Remote System Interaction chapter focuses on the usage of the resulting framework and tools. Chapter Further Background Information gives a deeper insight into surrounding or underlying topics, while Demonstration and Tutorials shows the implemented functionality. Also it helps to get readers started in setting up and using the provided tools. Finally, a conclusion over the reached topics rounds up the project.

In the Glossary, to be found on page xv, some less commonly known expressions and abbreviations are explained. Appendix A lists some additional resources for interested readers, while Appendix B gives some hints about convenient commands and tools for both Linux and Matlab. In Appendix C the structure and contents of the Digital Appendix are described for easier navigation and comprehension.

#### 1.2 Project Environment

The Department of Electric Power Engineeringof the Norwegian University of Science and Technology in Trondheim strives to introduce a new, universal hardware platform for control applications. It is bound to make use of the Xilinx Zynq-7000 SoC, which offers great flexibility and versatility as a hardware base. While the control algorithms and other software-based parts of future projects should reside in a Zynq, the effective purpose of a system and therefore its surrounding hardware vary significantly. Some projects already made use of this platform. However, there is no consistent way of designing such systems and most of the gained insights into the common base is lost after each project. Therefore a framework which defines a handy workflow would be helpful to ease the getting started with the Zynq SoC.

#### 1.3 Purpose of the Project

The evolution of processing system hardware provides powerful and versatile implementation platforms to system engineers such as the Xilinx Zynq-7000 SoC. Due to this new capable hardware, advanced and more demanding control systems become feasible. However, the complexity of such targets has risen enormously. They rely on special features and enhancements to enable the necessary power for complex tasks. In order to use those, a profound knowledge of the target platform is needed.

While traditional commercial projects can make use of experienced specialists for all aspects of such an implementation, especially applications in education and/or research can't always rely on such expertise. Time and knowledge are limited. Moreover, also modern design approaches suggest the development of algorithms and functions on a higher abstraction level. Therefore, it would be beneficial to allow a system engineer to concentrate on the design of the control aspects for a certain application, without the need of experience in special hardware interaction or even low-level programming skills.

As outlined in chapter 2, the aim of this project is to help system engineers to get started with their work on a complicated and versatile hardware platform. Also it should diminish the need for extensive research about the underlying hardware base by summarising several aspects of the Xilinx Zynq-7000 SoC environment and use.

#### 1.4 Introduction to Embedded Systems

Modern power electronic designs heavily rely on advanced control algorithms. Be it multilevel converters, motor drive systems, energy storage or power station systems. For an efficient, safe and reliable operation, they all depend on highly sophisticated and demanding control schemes. Usually such control schemes are implemented in an embedded system. These embedded systems are electronic structures which serve a distinct purpose. They are highly optimised for performance and reliability. Some applications even demand real-time and fully deterministic behaviour, which can only be achieved on a system with delimited purposes.

When designing algorithms for an embedded system, the main concern must be reliability and performance. Unnecessary operations should not interfere with the immediate purpose of the system. Therefore the special limitations and demands should already be taken into account in the design process. For further information about code optimisation also see [25, 31]. While working on an embedded system, the design principle should be:

#### **KISS**

Keep it simple, stupid. [45]

This means that the complexity and size of a system should be kept as small as possible. This helps to keep it comprehensible and reduces the risk of unwanted interferences. It also rises the manageability and eases maintenance significantly.

# 1.5 Short Overview over the Xilinx Zynq-7000 SOC and the Digilent ZedBoard

The Xilinx Zynq-7000 SoC is a modern, high performance system on chip. It is equipped with both a software processing system and a programmable logic part (FPGA). It features a dual-core ARM Cortex-A9 MPCore with a maximum frequency of 1 GHz, supports several external memory types, features a NEON engine, provides UART, USB2.0, Gigabit Ethernet and SD/SDIO support as well as many more. The FPGA, originating from the Artix-7 or Kintex-7 family, consists of and features a specialized DSP, an XADC and Block RAMs. The PS and PL part are interfaced with a high performance AXI interface. [59]

The combination of both a processing system and a programmable logic offers a huge advantage in control applications. Highly critical and demanding tasks can be outsourced to the FPGA. There they can meet hard realtime requirements, run in parallel and in a deterministic environment. More complex tasks like interfacing to other components or the user can be implemented in the processing system, where a lot of peripherals can be used. MicroBlaze softcores or other complex and customised structures can be implemented and undertake special tasks, due to the vast size of the FPGA. All this adds up to a high performing foundation for all kinds of control systems.

The Digilent ZedBoard is a development kit based on the Xilinx Zynq Z-7020 SoC, which features the most powerful Artix-7 FPGA of the Zynq family. 512 MB of DDR3 memory offer both fast and vast storage. The ZedBoard allows the user to concentrate on the software and FPGA design on a proven hardware base. A broad range of interfaces offers flexibility for more complex projects, such as an USB host, audio inputs and outputs (connected via I<sup>2</sup>S), Gigabit Ethernet, HDMI and VGA output, an 128x32 OLED display, a total of 7 push buttons, 8 switches, 9 LEDs, several PMODs and a FMC port for more complex interfacing. An SD card slot offers easy and flexible boot and data storage possibilities. To make the developer's life easier, there is also an USB to UART bridge and the possibility of daisy-chained JTAG programming. Booting from JTAG is also possible, as well as from the internal 256 MB Quad-SPI flash. [5]

For further reference on the Xilinx Zynq-7000 SoC, its applications and the ZedBoard, also see [9].

## Chapter 2

# Problem Definition and Functional Specification

The aim of this project is to provide future system engineers for power electronics with the necessary environment to easily conceive, implement and test their control design on a target hardware. In addition it should enable an operator to remote interact with the developed system. This shall be done by providing two sets of tools; on one hand a framework for the development phase, on the other hand a GUI for remote system interaction.

#### 2.1 Development Framework

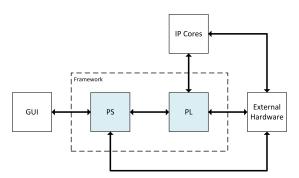

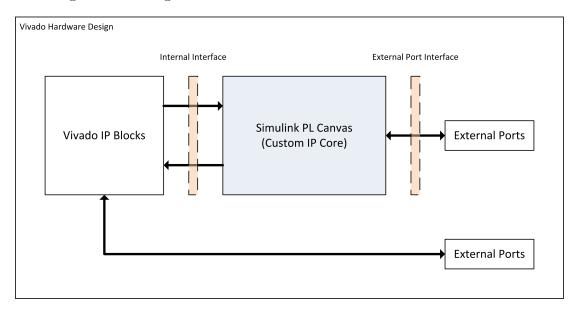

In order to ease the usage of a hardware platform, a comprehensive development framework shall be set up. It allows to benefit from a commonly known approach to design and outline control algorithms in combination with the desired hardware. It also guides the system engineer in generating the necessary code, the setup of the target hardware and the deployment of the realized control design. Methods to test and interact with the running system are introduced. Figure 2.1 shows the framework, which offers the containers of the custom user functions for the PS and PL parts. It also provides the connections to the surrounding components.

FIGURE 2.1: Development Framework in which the User Function Resides in the PS and PL Frames

#### 2.1.1 Functional Requirements for the Development Framework

In descending priority, the functional requirements are as follows:

- Must have criteria:

- Canvas for implementing the user function into the framework

- Methods for code generation and synthesis of the user function, as well as the deployment onto the target

- Methods to deploy user functions to the target persistently and run them standalone

- Interface hooks for the user functions to communicate with hardware and a GUI (see section 2.2)

- Nice to have criteria:

- Analysation of performance boosting measures, the need of them and their implementation (priority and affinity, threading, parallelism, AMP etc.)

#### 2.2 Remote System Interaction

A simple way of interacting with the system shall be realised. It targets mainly for the usage of the finished system by an operator without the need of all development tools and skills. But such an interaction can also come in handy during testing and setting up a system. It allows the change of parameters and the monitoring of signals in the system during run time. By utilizing standard Ethernet protocols as a base, the interaction can take part on a remote system in a GUI, as depicted in Figure 2.2. This enables the supervision and manipulation of the running target from afar. In this part, the ease of use and setup in the operating phase is emphasized.

FIGURE 2.2: Interaction GUI on a Remote Machine

#### 2.2.1 Functional Requirements for the Remote System Interaction

In descending priority, the functional requirements are as follows:

- Must have criteria:

- Enable the user to get and set parameters

- Logging of time series data (slower, continuously monitored signals)

- Analysis of a step response with parameter step setup, triggering of the step and the response measurement

- Methods for starting and stopping of the system

- Enable the user to export acquired data

- Nice to have criteria:

- Dynamic creation of the GUI, depending on the needs of the user function

#### 2.3 Accompanying Documentation

The documentation of the framework should guide the user to ease the first steps upon usage. Where the provided tools fall short, a comprehensive description of all parts should allow the adaption to new needs. Furthermore, for the remote system interaction part the usage and setup is described in detail. The method of communication with the running system is disclosed in detail. This enables the development of other tools using the same interface for further enhancements and use scenarios.

#### 2.4 Guidelines and other Specifications

Besides the overall goal of the project, resulting in the functional specification above, some additional guidelines are to be followed.

- As a target hardware platform, the Digilent ZedBoard with a Xilinx Zynq-7000 SoC is to be used.

- For a reference implementation, the motor drive system developed by Eirik Haustveit is to be used as a first use case.

- Only free or already licensed software available at the NTNU are to be used.

## Chapter 3

# Approach and Elaborated Solution

This chapter describes the functionality of the developed Framework and the Remote System Interaction. Those parts should accomplish the specified functional requirements. The chapter outlines the methods used to implement the needed features and gives a general overview over the possibilities. Detailed information about the usage and modification is described in chapter 4. The source code of all developed parts can be found in Appendix C.

#### 3.1 Prosecuted Approach

To ease the development of embedded systems, several tools exist in the market. For almost all platforms, at least one Integrated Development Environment (IDE) exists. For the Zynq in particular, one of the most powerful tools is Vivado, which is released by the manufacturer of the Zynq, Xilinx. But this targets mostly the development by using traditional coding style, with program code for the PS and hardware descriptive language for the PL part. This requires the system engineer to have considerable knowledge in writing program and HDL code. The use of Matlab/Simulink offers a much easier entry into the world of embedded systems for students. Since most students are familiar with it and the graphic way of defining algorithms with Simulink offers a flat learning curve. Even in more advanced development teams it is an often used tool. More information on the workflow with Matlab/Simulink can be found in section 5.1. Due to its advantages and support for the Zynq, it was decided to use Matlab/Simulink as a base to realise both the Development Framework and the Remote System Interaction. This allowed the use of tools, scripts and predefined function provided by MathWorks to setup the solution presented in this document.

#### 3.2 Development Framework

The Framework consists of various parts which are explained in the following subsection. It is organised in a folder structure, which can be found in Appendix C.

#### 3.2.1 Custom Reference Design

To be able to deploy a system onto a target, the hardware layout and other information must be defined. This is done by implementing a Reference Design, which itself is announced to Matlab for use. The process of customizing such a Custom Reference Design is described in section 6.3 and in [33]. The design used for the Development Framework is described in subsection 4.2.2

#### 3.2.2 Main Simulink Project

The main part of the Development Framework is set up by using a Simulink project. This allows for a comprehensive automation of tasks and management of files (see [34] for further information).

The Simulink project contains a startup script (scripts/project\_startup.m) which sets up the needed paths for the Reference Design, adds the Simulink Library and changes the current Matlab path to a work folder. The main Simulink model (models/frame-work\_main.slx) contains the functionality of the Framework and the User Canvases. It is described in the following sections.

#### Overview over the Model

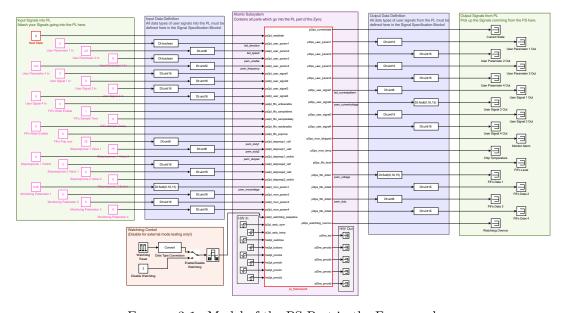

The Development Framework model is built highly hierarchical. On the topmost level, the main software part is realised. It contains all necessary sections for the framework functionality, especially for the interfacing between the PS and PL part as can be seen in Figure 3.1.

FIGURE 3.1: Model of the PS Part in the Framework

Within the main PS part, the first user canvas for the user software is placed. Also, the atomic subsystem  $pl\_framework$  which contains all PL parts is placed here. This contains the main control state machine, the different states and all other PL functions such as monitoring, the FiFo buffer and the Watchdog. Within the states and the monitoring block, the respective user canvases can be found while the other parts need not to be changed for using the provided functionality.

#### Control State Machine

To be able to control the system, a basic control state machine is realised within the PL. It consists of four states: Init state, Stop state, Run state and Failsafe state. The goal is to allow the system engineer to prepare different structures for each state he wants to run his system in. Basically, all states are provided with a set of identical inputs and outputs to interact with the surrounding system. Between those, the engineer can realise the desired functionality without having to care for the transition from one state to another.

Figure 3.2: Canvas of the User Run State, here with the Contents of the Demo Project

The state machine is realised entirely within the PL. This allows for a secure operation even when an error occurs in the PS (time constrains not met, software or system misbehaviour etc.). The next state to be executed is defined by a next state signal from the PS. However, if either the watchdog or the measurement system detect a faulty behaviour, the state machine switches into the Failsafe state, which is locking within the PL. It stays in Failsafe until all alarms from both the watchdog and the monitoring are revoked and the PS initiates a switch to the Init state.

An LED indicator shows which state is active. It is realised in the PL and drives the pin PMODA JA1.

| State          | LED Pattern          |

|----------------|----------------------|

| Init State     | off                  |

| Stop State     | on                   |

| Run State      | blinking slow (1 Hz) |

| Failsave State | blinking fast (5 Hz) |

Table 3.1: Blinking Patterns of State LED

#### Communication with GUI and Hardware

The Framework provides several prepared signals between the various system parts such as the GUI, the PS and PL parts as well as hardware interfaces (be it hardware pins or IP cores). As long as the system uses only parts which are integrated in the underlying reference design, all communication is already implemented in the framework. Communication with the GUI is done in the topmost model level, while the interface to the hardware and IP cores lies on the edge of the atomic subsystem and is accessed from the main PL part.

#### **User Function Canvases**

The main part for the system engineer to work in are the User Function Canvases. One canvas is provided within the topmost model level and contains all user software functions. For each of the four states, a canvas for the respective functionality in the PL is provided, as well as one canvas for the Monitoring System. Within these canvases, the system engineer places all his functions. All of them are connected by a set of prepared signals and parameters, which can be used as needed. While the PS and the monitoring canvases are executed all the time, the User State Canvases are only active during the associated state. While all input signals to these four canvases are parallel, the outputs are multiplexed in accordance to the state machine.

#### Monitoring

The Monitoring System, which resides in the PL, is always active and is to be used to detect unwanted conditions within the system. Several inputs provide data to the user to check the operation parameters and an alarm output allows to set the state machine to the Failsafe mode, in which appropriate measures against the fault can be taken.

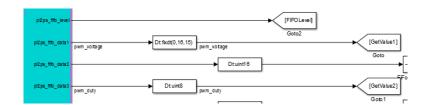

#### FiFo Buffer for Fast Signal Analysis

To enable the analysis of fast signals and step responses on parameter changes, a FiFo buffer is implemented into the PL. It records the data provided by the user into block ram structures and can be read out at a slower pace afterwards. Within the Framework, the triggering and pacing mechanisms for recording data are provided. The FiFo capture is activated by enabling it and changing one of the parameter switches. The FiFo will now run until it is full, even if a state transition occurs. This allows for debugging transitions into Failsafe as well. The signals to be recorded into the FiFo must be provided by the user states.

The pace at which the FiFo buffer records data can be set by the system engineer from the PS side, as well as the delay for the parameter switch. Since this requires a complex logical structure, a certain delay always occurs when the FiFo is triggered. Table 3.2 gives an overview over the timeouts and delays.

The readout of the FiFo is handled by the PS, in conjunction with the Remote GUI. For the readout, the PS supplies the FiFo with a base clock, to which on each edge a new set of data is transmitted.

| Sample Time       | 1 | 1 | 1  | 2 | 2 | 2  |

|-------------------|---|---|----|---|---|----|

| Sample Delay      | 0 | 1 | 10 | 0 | 1 | 10 |

| 1st FiFo Push     | 2 | 2 | 2  | 2 | 2 | 2  |

| Switch Transition | 2 | 3 | 12 | 2 | 4 | 22 |

Table 3.2: Sample Delays on the FiFo Trigger (1 sample corresponds to 10 ns for a PL clock frequency of 100 MHz)

#### Watchdog

The PL state machine is equipped with a watchdog. It makes sure that the independent running PL part of the Zynq notices when the collaborating software in the PS doesn't work as expected anymore.

The PL software needs to send a keep alive signal periodically. If this doesn't happen for a defined time, the watchdog sets the PL state machine into Failsafe mode, which in itself is locking (see section 3.2.2). Therefore, a simple return of the keep alive signal isn't sufficient for recovery, but a transition from any state to the Init state must occur to free the system again. This ensures that the transition into the Init state can not happen if the PL system receives the order to change to it next by mistake, e.g. from a corrupt parameter storage.

The overrun condition of the watchdog is announced to the PS software in order for proper detection and to initiate the releasing procedures if necessary.

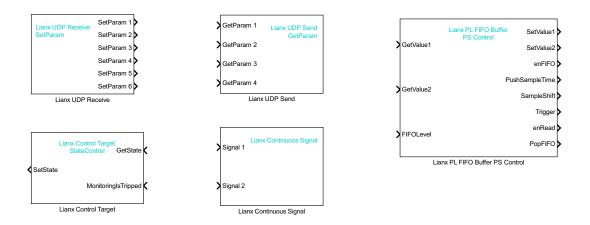

#### 3.2.3 Simulink Library

In the provided Simulink Library in Appendix C, some practical Simulink Blocks are available. Most of them offer functionality for the Remote System Interaction described in section 3.3, but some ease the development of synthesisable Simulink code for the PL part. For example, some Flipflops or Edge Detectors are implemented.

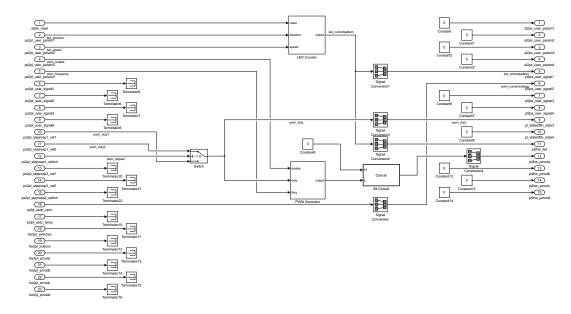

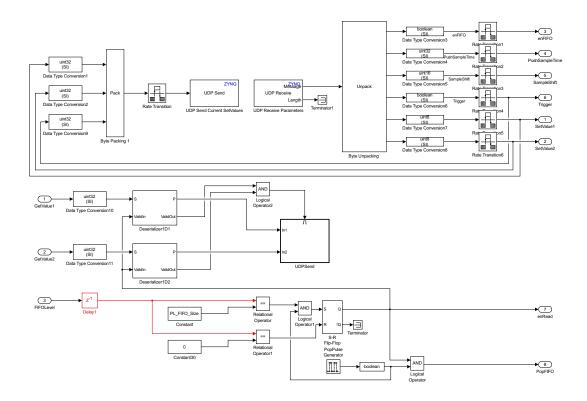

#### 3.3 Remote System Interaction

During the development and implementation phase of the control algorithm, direct testing methods can be applied such as external mode or PIL simulation. To enable an operator to interact with the developed system, some enhancement is needed. For remote interaction with the system, a communication between the target (Zynq) and a remote system (PC) has to be established. This communication is realised as a UDP interface which is already provided by MathWorks. Advantages of a UDP interface are that it is simple, fast and has a small overhead. However, it is a connectionless protocol which means there is per se no guarantee that the sent data reach their target. Since all safety relevant functions are implemented within the PS and PL standalone, a connectionless UDP communication interface is a good starting point for remote system interaction.

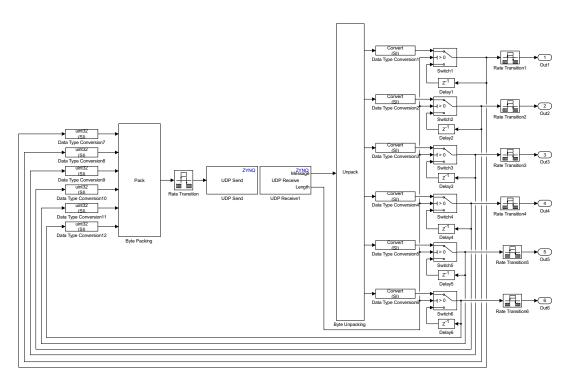

The Remote System Interaction part provides various Simulink blocks for different tasks. They are described in detail in the following subsections. This tasks go from simple "Get and Set parameters" to complex tasks like "FiFo control". All described blocks can

be found in the PS part of the provided Simulink library in Appendix C. An overview of the available block is depicted in Figure 3.3.

Figure 3.3: Remote System Interaction Simulink Communication Blocks

For enhancement of such remote system interaction blocks there are the following three main design tasks.

- Creation and assembly of Simulink Library blocks and their masking.

- Writing of a script to read out fundamental parameters of created library block which are needed for correct GUI interaction afterwards.

- Creation of a GUI module which enables remote system interaction with the designed block.

This is also the order how the blocks developed in this work are presented in the next subsection.

#### 3.3.1 Getting and Setting of Parameters

#### Lianx UDP Send GetParam

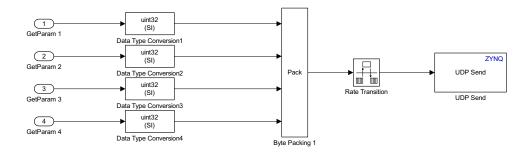

Simulink Block: The aim of the Block Lianx UDP Send GetParam is to send parameters from the target to the GUI. The designed block is illustrated in Figure 3.4. To fulfil its task the block needs at least a UDP Socket to send data. This socket block is already realised by MathWorks as an s-function and can easily be deployed to the target. It makes sense to pack some signal together to bring down the network load. This is done by a byte packing block. Since this library should be generic and does not know in advance which data type the signal has, a data type conversion is necessary because only integer data can be transmitted. The width of the signal is limited to 32bit. Since this block is used to get parameters, a sample time of 2 seconds<sup>1</sup> should be sufficient even though the input data can have a smaller sample time. To slow down the transmission, a rate transmission block is implemented.

There is a timing issue with the used table object in Matlab, which has grave implications on the performance of data updates. Therefore its wise to use a sample time > 1 second [3, p. 571].

FIGURE 3.4: Get Parameters Block

Simulink blocks can be masked for multiple reasons. One reason is to implement a small documentation of such a designed block that other users know how to use it. Another reason is to hide complexity and present only important parameters to the user which he can set on his own. One can define default values for chosen mask parameters such that the user does not need to set a value by himself. As long as the dependencies are not known the mask should not be changed. Some scripts are relying on these mask parameters which would not work anymore.

**API:** To interact with the target later on some important information is needed to setup the GUI. Since the library block stays constant except the set parameters of it, all important parameters which need to be known can be read out via a script. All Simulink block information and parameters can be gathered with the following instructions:

```

find_system(<sys>, '<Constraint1>', <Constraintvalue1>);

get_param(<Object>, <Parameters>);

```

For further information about the capability of these functions, the MathWorks documentation is a good reference.

Some parameters like the data type can only be determined when the model is in compile mode. Therefore the model has to be set in it. Then the parameters can be read out and the compile mode terminated afterwards. Interaction with the model is impossible during compile mode.

```

eval([<sys>, '([],[],[],''compile'')']);

get_param(...

eval([<sys>, '([],[],[],''term'')']);

```

All values of the determined parameters are stored in a Matlab variable of class type struct. The structure of the variable is as follows:

```

API (struct)

GetParam (struct)

BlockName (char)

RemoteURL (char), default: '255.255.255', (broadcast)

RemotePort (double), default: 25003

SampleTime (double)

DataType (4x1 cell)

ParamName (4x1 cell)

```

The DataType cell array can only be determined during compilation of the model. It is important to know the datatype for correct reinterpretation of the value in the GUI after it was changed to uint32 and transferred over UDP. The ParamName contains the signal name which defines an appropriate label for the parameter. The definition of a signal name is explained in subsection 4.3.1.

GUI: In the GUI there is a panel for each interaction library block. Each panel is only filled when the corresponding block is used. An init function determines if such a block is available in the API list and if so loads and prepares the specific module. For the UDP transmission from the GUI to the target, the instrument control toolbox of MathWorks is used. To initialise such an UDP object the IP address of the target and the local port of the GUI need to be known. The local port of the UDP object corresponds to the remote port to which the target sends its data. The UDP object listens on the allocated port and creates an interrupt when a specified amount of data is received. This interrupt is known as a callback function in Matlab. This particular callback function reads the received data from the input buffer as uint32 values. For correct display of the received values, the data type needs to be known and a conversion has to be made. When the values are transformed to their correct type, they are written into the prepared table and the user can see them.

#### Lianx UDP Receive SetParam

FIGURE 3.5: Set Parameters Block

**Simulink Block:** The aim of the Block Lianx UDP Receive SetParam is to receive parameters from the GUI and send back the current value for control purposes. The designed block is illustrated in Figure 3.5. The read back part of the current values is very similar to the get parameter block. On the other hand there is a UDP Receive block which implements an UDP socket to listen on a specified port. Each time a UDP datagram is received it is unpacked and distributed to the specific outport. Since it is possible that for some signal an initial value is wanted, there is a delayed feedback

of the current value. This is updated by the new set value each time a datagram is received. To fulfil the requirements of the receiving block regarding the sample time a rate transition block transforms this via back propagation.

Hint: There is a parameter called blocking time inside the UDP Receive block, which should be handled with care. It should be kept as short as possible (default: 10 µs) because it blocks the process before it returns control to the scheduler.

**API:** For the API the same procedure as for the get parameter block is valid. There just are some additional parameters which need to be determined because the set parameter block has a read back capability and can show the current values. Therefore it needs a send and receive block with properties.

```

API (struct)

SetParam (struct)

ReceiveRemoteURL (char), default: '0.0.0.0', (all)

localPort (double), default: 25000

SendRemoteURL (char), default: '255.255.255', (broadcast)

remotePort (double), default: 25001

ReceiveSampleTime (double), default: 0.5

SendSampleTime (double), default: 2

DataType (6x1 cell)

ParamName (6x1 cell)

Min (6x1 cell)

Max (6x1 cell)

...

```

**GUI:** For the GUI part of the set parameter block its almost the same as before. There is some additional functionality which validates if the new set value fits the requirements. These are set by the user via min and max values. Additionally it is checked if the new set values fulfil the data type requirements. If they do not, they are either set back to the value before or rounded to an appropriate fixpoint value if the data type requires so.

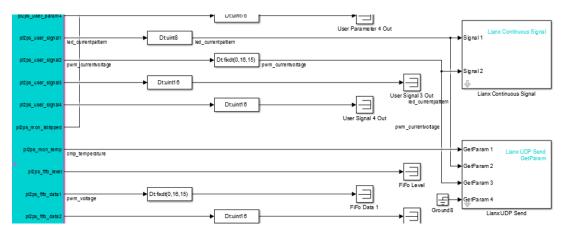

#### 3.3.2 Logging of Slow Time Series

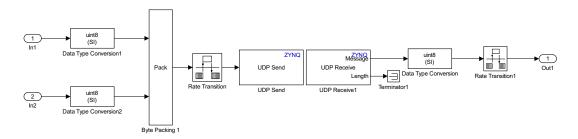

**Simulink Block:** The aim of the block *Lianx Continuous Signal* is to continuously send slower signal to the GUI. The block is depicted in Figure 3.6. A rate transition block, which can be set to a specific value, assures a periodic data flow. A buffer captures a certain amount of data which are packed later on with a byte packing block. The reason for the buffering and packing is to reduce the UDP overhead and send bigger datagrams. Another benefit is on the GUI side; processing a few bigger data packets is faster then a lot of small ones.

**API:** For the API there is a SigBufferSize parameter which sets the size of the signal buffer. For a good signal buffer size there are some things to consider. Since the transferred data are of datatype uint32 there are 4 bytes for each sent value. Due to the two signal lines there are 8 bytes for each sample. It is good practice that a UDP package should not exceed 512 bytes. Therefore each buffer has 64 values to capture before sending a datagram. The Signal buffer slows down the update rate in the GUI. If the sample time is 0.01 s then each 0.64 s a datagram package is sent.

Figure 3.6: Continuous Signal Block

```

API (struct)

ContSig (struct)

BlockName (char)

RemoteURL (char), default: '255.255.255.255', (broadcast)

RemotePort (double), default: 27001

SampleTime (double), default: 0.01

SigBufferSize (double), default: 64

DataType (2x1 cell)

ParamName (2x1 cell)

```

GUI: The GUI part of the continuous signal is designed such that the x-axis is set to a range of 10 seconds per default. From 0 to 10 seconds its static and starts rolling when the time exceeds 10 seconds. The callback function of the UDP block considers the signal buffer size to split the received data correctly into signal 1 and signal 2. Each time the callback function of the UDP class object is called, the axes in the GUI are updated. All received data is stored in a ring buffer. Before the ring buffer overflows all so far captured data points are stored as a mat-file with date and time as file name. When the continuous signal module is turned off, all remaining values in the ring buffer are also stored. That way the user has access to all data which was acquired while the module was on.

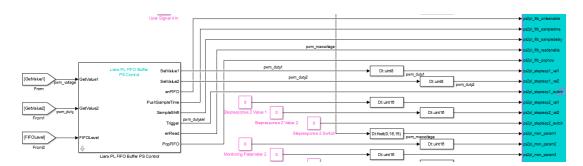

#### 3.3.3 Step Response Analysis of Fast Signals

Simulink Block: The aim of the block Lianx PL FIFO Buffer PS Control is to control the FiFo buffer which resides in the PL from the GUI. Additionally it also controls the read back of the captured values into the GUI. The FiFo buffer has some parameters which can be set. The upper part of the block depicted in Figure 3.7 is responsible to set those parameters. The trigger value and the two set values are fed back in order to display them correctly in the GUI. The trigger signal is responsible to switch from set value 1 to set value 2 and vice versa. For the latter there is also the possibility to set an initial value if needed. The lower part of the block is responsible for controlling the read out of the FiFo buffer. When the FiFo is triggered, it starts to capture data and the FiFo level will rise to its maximum (the FiFO buffer size). When it reaches this value, the read out process starts. A pulse generator is needed to pop the FiFo buffer. All popped values are packed to a appropriate size and sent over UDP to the GUI. The packed size is calculated using the following algorithm:

```

maxUDPSize = 512; % byte

nrSignal = 2; % 2 Channel

SignalWidth = 4; % uint32

% determine max SignalBufferSize as factor of FIF0Buffer Size

```

```

% constraint by maxUDPSize

if round(PL_FIF0_Size) == PL_FIF0_Size

maxFrameSize = maxUDPSize/nrSignal/SignalWidth;

fact = factor(PL_FIF0_Size);

BufferSize = 1;

for n = 0:numel(fact)-1

if BufferSize <= maxFrameSize</pre>

NewValue = BufferSize*fact(end—n);

if NewValue <= maxFrameSize</pre>

BufferSize = NewValue;

else

BufferSize = BufferSize;

end

else

end

end

else

error('Input datatype not valid, must be an integer.');

end

```

A UDP send block is enabled during the readout process. This sends data packages with the pre defined size. When the FiFo level reaches its end (at level 0), it is disabled.

FIGURE 3.7: Step Response, FiFo Control Block

**API:** The API structure of this block contains some important information about the signal buffer size which the GUI part needs to know. The default pop rate of the FiFO

buffer is 1 kHz which means a FiFo of size 10000 needs 10 seconds to read out. The FiFo buffer channels are read out in parallel.

```

API (struct)

PLFIFOBuf (struct)

BlockName (char)

FIFORemoteURL (char), default: '255.255.255.255', (broadcast)

FIFORemotePort (double), default:

28003

SigBufferSize (double)

RemoteURL (char), default: '0.0.0.0', (all)

LocalPort (double), default:

28000

SendRemoteURL (char), default:

'255.255.255', (broadcast)

RemotePort (double), default:

28001

SampleTime (double), default:

FIFOPopSampleTime (double), default:

PLFIFOSize (double)

InportDataType (2x1 cell)

OutportDataType (6x1 cell)

GetParamName (2x1 cell)

SetParamName (2x1 cell)

Min (2x1 cell)

Max (2x1 cell)

```

**GUI:** On the GUI side, the FiFo buffer control block needs two UDP objects, one for the set and read back signal and the other to receive the readout values stored in the FiFo. For the readout process the UDP object has an input buffer size of

```

(input buffer size) = (FiFo buffer size) \cdot (number of signals) \cdot (size of datatype)

```

When all values are received, the UDP object initiates a callback function which updates the trigger data axes and stores the values as a mat-file.

#### 3.3.4 System Control

**Simulink Block:** The aim of the block *Lianx Control Target* is to remotely control the target. The block is depicted in Figure 3.8. This block is responsible to send next state signals to the target and receives current state and state of the monitoring system. Its very handy to have the state information of the guarded system available. This helps to see if there is a monitoring problem present in the PL part which can't be reset from the PS.

FIGURE 3.8: Control Target Block

**API:** The most important parameter for the API list in this case is the port informations.

```

API (struct)

CtrlTarget (struct)

BlockName (char)

ReceiveRemoteURL (char), default: '0.0.0.0', (all)

LocalPort (double), default: 26000

SendRemoteURL (char), default: '255.255.255', (broadcast)

RemotePort (double), default: 26001

SampleTime (double), default: 1

```

**GUI:** The GUI part of this block consists of three buttons. One to set the system into the Run state, one to set the system into the Stop state and one to reset / initialise the system. The current state is depicted as text and the monitoring state is shown as a coloured field, red for tripped and green for no alarm in condition.

#### 3.3.5 User Interface

The base structure of the user interface is designed using GUIDE. This is a development environment to create GUI's, provided by MathWorks. The GUI could also have been designed using another programming language such as C, C++, Java, ... The reason why it was realised using Matlab is because it was best known to the authors and provides some handy typecast and UDP libraries. A disadvantage of using Matlab is, that it is an interpreter programming language and is therefore not as fast as C or C++ which are compiled languages. The bottleneck of the developed application lies on the GUI side. Some callback function of UDP objects to update incoming data are too time consuming. It seems that the problem is less the amount of data to process, but rather the rate of callbacks. All callback functions can be interrupted by another which then are queued until there is enough CPU time available. There are some hints on the internet to fasten Matlab application using their profiling tools [36] to find the time consuming functions. When these functions are determined one can look for faster solutions and improve performance. The approach during the GUI development phase was:

make it work make it right make it fast [17]

Unfortunately there was not enough time to focus on the optimisation of performance.

When the GUI development is finished, there is a possibility of creating a standalone application. Such an application can run without a Matlab license. The only thing which is needed is the Matlab Runtime in the version as the application was created with. In the Matlab version R2015b there is a bug regarding the Matlab application compiler toolbox. The compiled GUI has a different look than during the design phase. To correct this bug there are some lines of code to add in a startup script [21].

#### Overview of UDP Ports and Signals

The following list gives an overview of the default UDP port specification with its transfer datatype and the data structure itself.

#### • Lianx UDP Receive SetParam

destination port: 25000 transfer datatype: uint32

data: [SetParam1|SetParam2|SetParam3|SetParam4|SetParam5|SetParam6]

local port: 25001

transfer datatype: uint32

data: [CurrentParam1|CurrentParam2|CurrentParam3|CurrentParam4|

CurrentParam5|CurrentParam6|

#### • Lianx UDP Send GetParam

local port: 25003

transfer datatype: uint32

data: [GetParam1|GetParam2|GetParam3|GetParam4]

#### • Lianx Continuous Signal

local port: 27001

transfer datatype: uint32 data: [Signal1|Signal2]

#### • Lianx PL FIFO Buffer PS Control

destination port: 28000 transfer datatype: uint32

data: [SetValue1|SetValue2|enFIFO|PushSampleTime|SampleShift|Trigger]

local port: 28001

transfer datatype: uint32

data: [Current Value1|CurrentValue2|CurrentTrigger]

local port: 28003

transfer datatype: uint32 data: [GetValue1, GetValue2]

#### • Lianx Control Target StateControl

destination port: 26000 transfer datatype: uint8

data: SetState local port: 26001

transfer datatype: uint8

data: [GetState|MonitoringIsTripped]

### **Dynamic Creation**

The task of a dynamic creation of the GUI could not be fulfilled due to a shortage of time. But the developed GUI modules are only setup if in the generated API list such a block is referenced, otherwise the module will not be loaded. The imperfection about this solution is that the area stays empty.

# Chapter 4

# Working with the Development Framework and Remote System Interaction

This chapter describes how to work with the Development Framework and the Remote System Interaction. In section 6.2 a sample implementation using the here presented methods can be found.

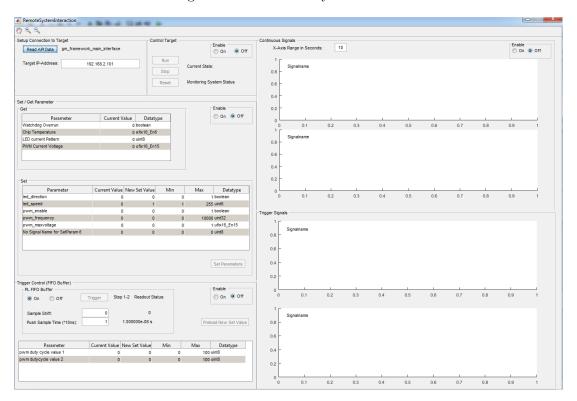

# 4.1 Prerequisites

To be able to use the Development Framework and Remote System Interaction designed in this project, some prerequisites must be met. Since some of the tools change rapidly due to their ongoing development, backwards compatibility might be unreliable. Due to the highly interlinked usage of tools, functionality is only provided if using the given release versions.

#### • Matlab/Simulink R2015b

HDL Coder Support Package for Xilinx Zynq-7000 Platform 15.2.0

Embedded Coder Support Package for Xilinx Zyng-7000 Platform 15.2.2

Embedded Coder Support Package for ARM Cortex-A Processors 15.2.0

Embedded Coder 6.9

HDL Coder 3.7

Simulink Coder 8.9

Instrument Control Toolbox 3.8

Fixed-Point Designer 5.1

Matlab Coder 3.0

DSP System Toolbox 9.1

- Xilinx Vivado 2014.4 with SDK (WebPack Edition is sufficient<sup>1</sup>)

- Lianx System Software running on the ZedBoard (see section 6.1 for setup instructions)

<sup>&</sup>lt;sup>1</sup> for device limitations see [54].

#### • Development Framework

#### • Lianx Libraries

Also, it is crucial that the system engineer has a basic understanding of embedded systems and the challenges of their development. Although the Development Framework tries to ease the development process, not all obligations can be taken over. For example, the engineer needs to know about the advantages and disadvantages of implementing certain functions in software or programmable logic. Failure to understand the basic principles and executing an intensive examination of the framework will have serious impacts on the resulting system. Not all these steps can be covered in this Thesis, but the reader is highly encouraged to dive into the explanatory chapter 5 and the additional literature in Appendix A, as well as other sources of information about embedded system engineering.

## 4.2 Development Framework

This section outlines the usage of the Development Framework and its adaption to the system engineer's needs. To help the understanding of the framework and to demonstrate the basic functionality, a sample implementation was developed. It is described in section 6.2, as well as the steps needed to set it up.

The framework as is provides some basic functionality and tools. A fully generic framework which covers all needs is not feasible. But in its basic setup, it should be able to handle most scenarios with only minor modifications. Hints on modifying the framework are given in subsection 4.2.11.

The basic workflow is as follows:

- The system engineer designs his system and informs himself about the provided functions and canvases of the framework (subsection 4.2.1 to subsection 4.2.5).

- Then the User functions are implemented into the framework. This process is described in subsection 4.2.6.

- Subsection 4.2.7 describes the simulation of the whole system.

- After the functionality of the system was tested in simulation, the PL bitfile is created and programmed onto the Zynq FPGA (subsection 4.2.8).

- Now the system can be tested on the target in realtime as described in subsection 4.2.9.

- Some hints on the performance analysis of the PS part are given in subsection 4.2.10.

#### 4.2.1 A Note on Signals and the PL Clock Frequency

Simulink is a data flow based modelling technique. Therefore, to transport data between the different blocks of the framework, signals are used. All signals the user has to deal with are described in the section about their respective functionality. For a better overview, the signal names are strictly hierarchical, beginning with the notation of their origin and target, followed by its functionality and finally a distinctive name.  $ps2pl\_user\_param3$  for example denotes a signal which transports the third parameter

from the PS to the PL user state which the system engineer can use for whatever he desires.  $pl\_mon2fifo\_data2$  is the second data source for the FiFo block, comming from the Monitoring system within the PL.

While the PS can execute its code at a predefined rate, the PL clock is set in the Reference Design. Also, the transfer rates of the signals transmitted between the PS and PL over the AXI interface need to be defined. Both those rates are set with Simulink workspace variables:

- pl\_axi\_freq (default: 1000 \hookin 1000 Hz)

Defines the transfer rate of the signals between the PS and PL part.

- pl\_clock\_freq (default: 100'000'000 \hookenset 100 MHz)

Indicates the PL clock frequency set in the Reference Design. Used to calculate time steps within PL blocks and control the rate transitions for simulation.

Since the Zynq uses 32bit ARM processors for the PS, operations with a higher word width are strongly discouraged. While such are possible, they have a severe impact on performance. Also note that Simulink supports 32bit wide data over the AXI-Interface only, so staying within the 32bit limit is recommended. The use of floating point signals is not possible on the PL and AXI interface, so only integer and fixed point data can be used. For more information about fixed point design see also [26].

#### 4.2.2 Prepared Peripherals

To interact with the hardware, the following peripherals are prepared for use:

#### • ZedBoard LEDs, Switches and Buttons

The eight LED on the ZedBoard are available as an output signal, as well as the eight switches and fife buttons are as inputs.

#### • Zynq XADC

The Zynq XADC, as well as the needed data readout algorithms, are implemented into IP cores in the reference design. The differential voltage measurement between the pins Vp and Vn of the XADC header are provided, corresponding directly to measurements between 0 V and 1 V. Also, the temperature of the chip is available as a value in  $^{\circ}$ C.

#### • ZedBoard PMODs

*PMODA* to *PMODD* are available as both input and output signals. See subsection 4.2.8 for the mode selection.

The signals to and from the hardware and IP cores are as follows:

- ip2pl\_xadc\_vpvn (ufix16\_en15: 0 = 0 V, 1 = 1 V) Supplies the measured Voltage between Vp and Vn on the XADC header.

- ip2pl\_xadc\_temp (sfix16\_en6: value in °C) Supplies the measured chip temperature.

- hw2pl\_switches (uint8)

Supplies the value of the switches on the ZedBoard.

- hw2pl\_buttons (ufix5) Supplies the value of the buttons on the ZedBoard.

- hw2pl\_pmod<a-d> (uint8, except for PMODA which is ufix7²)

Depending on the configuration, these signals provide or accept signals to or from the PMOD headers PMODA to PMODD. If used as an output, the signal direction reverses to pl2hw pmod<a-d>.

- pl2hw\_led (uint8)

Output to the ZedBoard LEDs.

Note that the use and connection of the PMODs is done while setting up the synthesis of the PL hardware description. See subsection 4.2.8 for further information about that step. The addition of further IP cores and other peripherals can be achieved by modifying the underlying Reference Design of the framework. This process is described in section 6.3. Some hints on the adaption of the framework are given in subsection 4.2.11.

#### 4.2.3 User Function Canvases

First of all, the system engineer needs to outline which parts of his system shall reside in which part of the framework. For slower processes (e.g. 1 kHz), the PS canvas is the right choice, while critical and fast functions (e.g. 100 MHz) should reside in the PL whenever possible. Then, on the PL side, he has to consider what functions need to be implemented where. What is needed to reach a secure state of the system and how can this be implemented in the Failsafe state? What signals are needed? Which parameters should be analysed and recorded for a closer inspection with the FiFo buffer? Only when all these design steps are dealt with, the implementation can begin.

#### User PS Canvas

In the User PS canvas, the system engineer can place the processes which should reside in the PS. The canvas is provided with several signals to and from the PL. Most importantly, the signal  $ps2pl\_nextstate$  controls the systems state machine. Note that once the state machine is in Failsafe mode, only a transition to the Init state can release it again.