# Ultra-low voltage embedded processor system for Internet-of-Things microcontrollers

**Danton Canut Benemann**

Embedded Computing Systems Submission date: July 2014 Supervisor: Snorre Aunet, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

| Title:   | Ultra-Low Voltage Embedded Processor              |  |

|----------|---------------------------------------------------|--|

|          | System for the Internet of Things Microcontrolers |  |

| Student: | Danton Canut Benemann                             |  |

#### **Problem description:**

It is predicted that billions of embedded devices will soon be connected to the internet. End nodes will typically contain a microcontroller to collect, process, and interpret sensory input data. Many of these will run from small batteries and may need to harvest energy from the environment to achieve an acceptable battery lifetime. The microcontroller typically includes a CPU, memories, buses, and peripherals. The student should design the embedded processor system within the microcontroller.

The system should be able to run from a wide supply voltage range. The system should be implemented in an low- voltage standard cell library using state-of-the-art design techniques.

The system should support voltage scaling from the nominal voltage down to the subthreshold voltage domain, allowing a wide tradeoff between performance and power consumption. The student should analyze the system properties and compare them to an identical system implemented using traditional libraries and design techniques.

| Responsible professor: | Snorre Aunet, NTNU-IET |

|------------------------|------------------------|

| Supervisor:            | Frode Pedersen, ATMEL  |

## Abstract

As devices get an ever increasing foothold on the internet and the Internet of Things becomes the usual landscape in the mass consumer electronic products is necessary to bring embedded processors capable of bringing performance to the micro controllers of such devices. compares Is the intention of this project to compare under different scenarios suitable for the applications two embedded processors form Atmel's one AVR 8-bit and an AVR32 UC3 to identify which is the one that has the lowest power consumption, lowest energy consumption. It has been shown that the AVR has the less power consumption (about half) but in terms of energy the AVR32 is less taxing. A test bench was implemented including SPI communication modules and memories, This is due to the long execution times of the AVR which are for 1.5 to 10 longer than the AVR32. These conclusions scale when implementing on lower feature size (this project uses UMC's 130nm typical process library and UMC's 65 typical process library). Also the conclusion stand when restricting the standard library such that an "Ultra low voltage" friendly net list is produced and tested vielding similar results.

# Preface

This Master Thesis was carried out as a part of the study program European Masters in Embedded Computing Systems at Department of Electronics and Telecommunications of the Norwegian University of Science and Technology under the supervision of Prof. Snorre Aunet. The work was done at the Atmel office in Trondheim under the supervision of Frode Pedersen during period between January and July 2014.

# Contents

| Li            | st of                      | Figure                 | es                                                           | vii      |

|---------------|----------------------------|------------------------|--------------------------------------------------------------|----------|

| $\mathbf{Li}$ | st of                      | Tables                 | 3                                                            | ix       |

| $\mathbf{Li}$ | st of                      | Acron                  | lyms                                                         | xi       |

| 1             | Intr                       | oducti                 | on                                                           | 1        |

|               | 1.1                        | Histor                 | ical Perspective                                             | 2        |

|               |                            | 1.1.1                  | Internet of Things                                           | 2        |

|               |                            | 1.1.2                  | Related Work                                                 | 2        |

|               | 1.2                        | Asigm                  | ent Interpretation                                           | 3        |

|               | 1.3                        | Contri                 | butions                                                      | 3        |

|               | 1.4                        | Repor                  | t Organization                                               | 4        |

| <b>2</b>      | Bac                        | kgrour                 | nd                                                           | <b>5</b> |

|               | 2.1                        | Power                  |                                                              | 5        |

|               |                            | 2.1.1                  | Dynamic Power                                                | 5        |

|               |                            | 2.1.2                  | Static Power                                                 | 6        |

|               |                            | 2.1.3                  | Dynamic Voltage Frequency Scaling (DVFS) and Voltage Islands | 7        |

|               |                            | 2.1.4                  | Near- Threshold Voltage (NTC) and Sub-Threshold Voltage      |          |

|               |                            |                        | (STC)                                                        | 7        |

|               | 2.2 Heterogenous Computing |                        | ogenous Computing                                            | 8        |

|               |                            | 2.2.1                  | 8/16bit cores vs 32-bit cores                                | 9        |

| 3             | Imp                        | lemen                  | tation                                                       | 11       |

|               | 3.1                        | $\operatorname{Setup}$ | and Work Flow                                                | 11       |

|               |                            | 3.1.1                  | Hardware                                                     | 12       |

|               |                            | 3.1.2                  | Software                                                     | 15       |

|               | 3.2                        | Synthe                 | esis                                                         | 17       |

|               |                            | 3.2.1                  | Synthesis script                                             | 17       |

|               |                            | 3.2.2                  | Libraries                                                    | 18       |

|               | 3.3                        | Power                  | and Energy Analysis                                          | 19       |

|               |                            | 3.3.1                  | Power                                                        | 19       |

|          |       | 3.3.2     | Energy                                                     | 19        |

|----------|-------|-----------|------------------------------------------------------------|-----------|

| 4        | Res   | ults      |                                                            | <b>21</b> |

| -        | 4.1   |           | esis AVR and AVR32                                         | 21        |

|          |       | 4.1.1     | Library variation                                          | 21        |

|          |       | 4.1.2     | Area Comparison                                            | 22        |

|          |       | 4.1.3     | Timing Achieved                                            | 22        |

|          | 4.2   | Power     | and Energy comparison between the AVR and AVR32            | 23        |

|          |       | 4.2.1     | 8-bit Math Test                                            | 24        |

|          |       | 4.2.2     | 8-bit Switch Test                                          | 27        |

|          |       | 4.2.3     | 16-bit Math Test                                           | 30        |

|          |       | 4.2.4     | 16-bit Switch Test                                         | 33        |

|          |       | 4.2.5     | 32-bit Math Test                                           | 36        |

|          |       | 4.2.6     | RAM Write Test                                             | 39        |

|          |       | 4.2.7     | Serial Peripherial Interface (SPI) Read and Wirte Test     | 42        |

|          |       | 4.2.8     | Tranfer Control Protocol / Internet Protocol Checksum Com- |           |

|          |       |           | putation (TCP/IP Checksum Computation) Test                | 45        |

|          |       | 4.2.9     | Summary                                                    | 48        |

| <b>5</b> | Dis   | iscussion |                                                            |           |

|          | 5.1   | Synthesis |                                                            | 49        |

|          |       | 5.1.1     | Area                                                       | 49        |

|          |       | 5.1.2     | Timing                                                     | 49        |

|          | 5.2   | Power     | and Energy                                                 | 50        |

|          |       | 5.2.1     | AVR vs AVR32                                               | 50        |

|          |       | 5.2.2     | Core vs System                                             | 51        |

|          |       | 5.2.3     | NTV and STV                                                | 51        |

|          | 5.3   | Future    | e Work                                                     | 51        |

|          |       | 5.3.1     | Test Cases and Peripherals                                 | 51        |

|          |       | 5.3.2     | Real STV, NTV and More Libraries                           | 52        |

|          |       | 5.3.3     | Tools and Testing Cores at the Same Time                   | 52        |

|          |       | 5.3.4     | Cores                                                      | 52        |

|          | 5.4   | Concl     | usions                                                     | 52        |

| R        | efere | nces      |                                                            | 53        |

# List of Figures

| 2.1  | NMOS.[24]                                                                | 6  |

|------|--------------------------------------------------------------------------|----|

| 2.2  | Energy per Operation and Delay vs Voltage.[11]                           | 8  |

| 2.3  | big.LITTLE system.[13]                                                   | 9  |

| 2.4  | 8-bit Central Processing Unit (CPU) Comparison[16]                       | 9  |

| 2.5  | Atmel's Product Range [6]                                                | 10 |

| 3.1  | AVR core (AVR) setup                                                     | 13 |

| 3.2  | AVR32 UC core (AVR32) setup                                              | 14 |

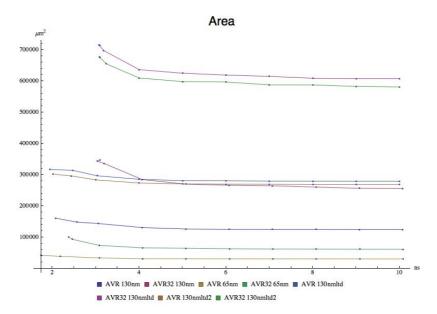

| 4.1  | Area footprint                                                           | 23 |

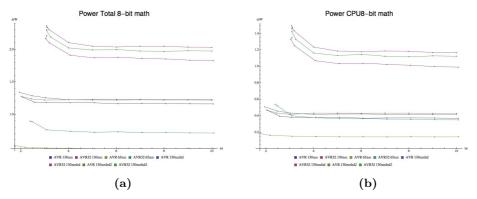

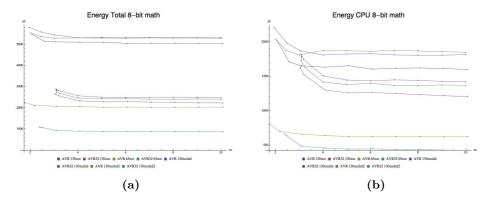

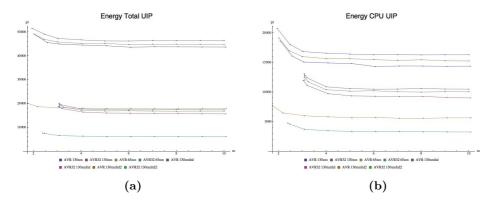

| 4.2  | Power Graphs for the 8-bit Math Test                                     | 24 |

| 4.3  | Energy Graphs for the 8-bit Math Test                                    | 24 |

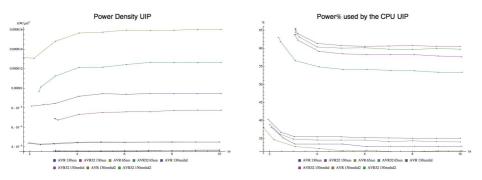

| 4.4  | Power Density Graphs for the 8-bit Math Test                             | 24 |

| 4.5  | CPU % Power Graphs for the 8-bit Math Test $\ldots \ldots \ldots \ldots$ | 24 |

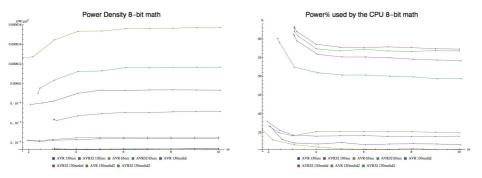

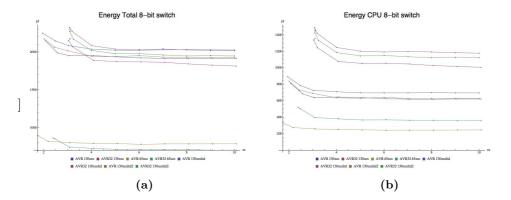

| 4.6  | Power Graphs for the 8-bit Switch Test                                   | 27 |

| 4.7  | Energy Graphs for the 8-bit Switch Test                                  | 27 |

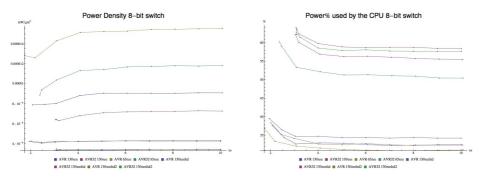

| 4.8  | Power Density Graphs for the 8-bit Switch Test                           | 27 |

| 4.9  | CPU % Power Graphs for the 8-bit Switch Test                             | 27 |

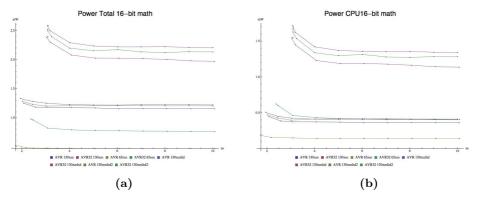

| 4.10 | Power Graphs for the 16-bit Math Test                                    | 30 |

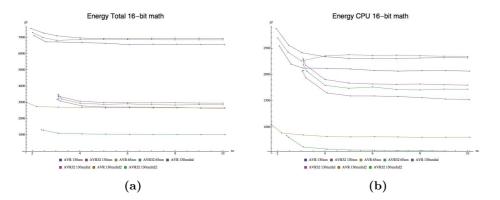

| 4.11 | Energy Graphs for the 16-bit Math Test                                   | 30 |

| 4.12 | Power Density Graphs for the 16-bit Math Test                            | 30 |

| 4.13 | CPU % Power Graphs for the 16-bit Math Test                              | 30 |

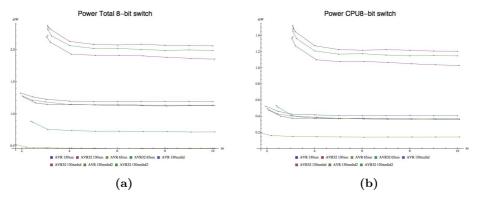

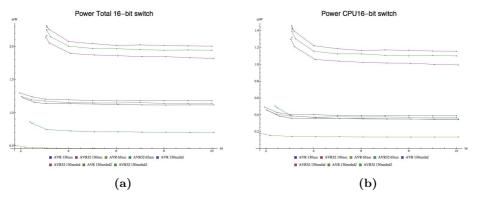

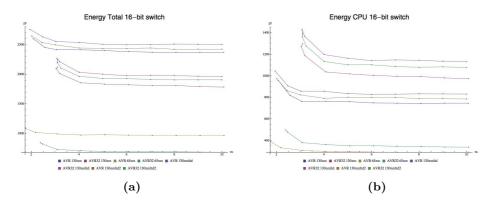

| 4.14 | Power Graphs for the 16-bit Switch Test                                  | 33 |

| 4.15 | Energy Graphs for the 16-bit Switch Test                                 | 33 |

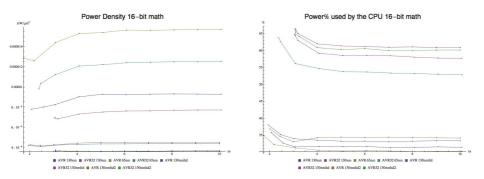

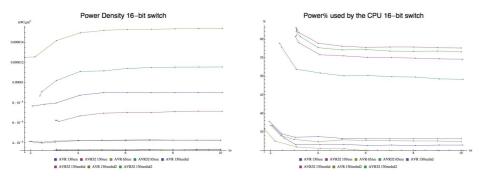

| 4.16 | Power Density Graphs for the 16-bit Switch Test                          | 33 |

| 4.17 | CPU % Power Graphs for the 16-bit Switch Test $\ldots$                   | 33 |

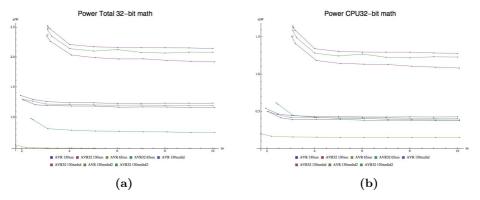

| 4.18 | Power Graphs for the 32-bit Math Test                                    | 36 |

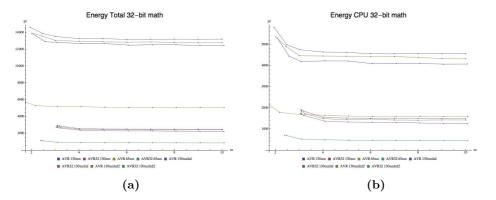

|      | Energy Graphs for the 32-bit Math Test                                   | 36 |

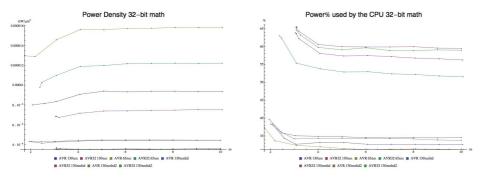

|      | Power Density Graphs for the 32-bit Math Test                            | 36 |

| 4.21 | CPU % Power Graphs for the 32-bit Math Test                              | 36 |

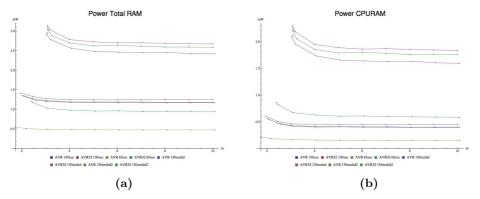

|      | Power Graphs for the RAM Test                                            | 39 |

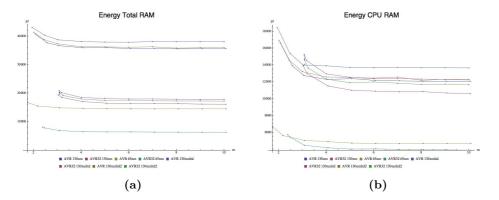

|      | Energy Graphs for the RAM Test                                           | 39 |

| 4.24 | Power Density Graphs for the RAM Test             | 39 |

|------|---------------------------------------------------|----|

| 4.25 | CPU % Power Graphs for the RAM Test               | 39 |

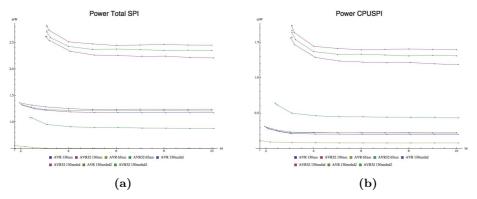

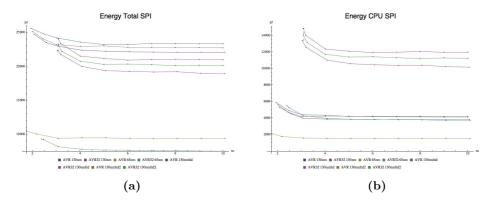

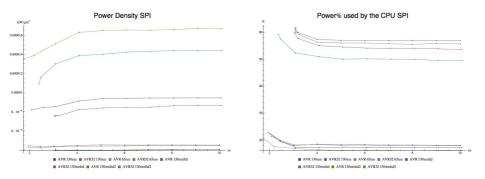

| 4.26 | Power Graphs for the SPI Test                     | 42 |

| 4.27 | Energy Graphs for the SPI Test                    | 42 |

| 4.28 | Power Density Graphs for the SPI Test             | 42 |

| 4.29 | CPU % Power Graphs for the SPI Test               | 42 |

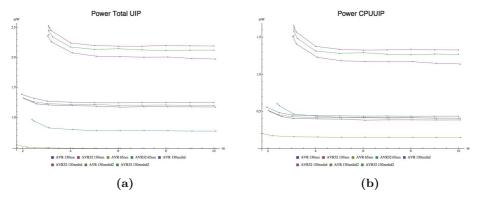

| 4.30 | Power Graphs for the TCP/IP Checksum Test         | 45 |

| 4.31 | Energy Graphs for the TCP/IP Checksum Test        | 45 |

| 4.32 | Power Density Graphs for the TCP/IP Checksum Test | 45 |

| 4.33 | CPU % Power Graphs for the TCP/IP Checksum Test   | 45 |

# List of Tables

| 3.1  | Address Map                                       | 15 |

|------|---------------------------------------------------|----|

| 4.1  | Area vs targeted time                             | 22 |

| 4.2  | Timing Achieved for each net-list                 | 23 |

| 4.3  | Power Comparisons 8-bit Math Test                 | 25 |

| 4.4  | Energy Comparisons 8-bit Math Test                | 25 |

| 4.5  |                                                   |    |

|      | Sub-Threshold Voltage (STV)                       | 26 |

| 4.6  | Power Comparisons 8-bit Switch Test               | 28 |

| 4.7  | Energy Comparisons 8-bit Switch Test              | 28 |

| 4.8  | 8-bit Switch Energy Estimation for NTV and STV    | 29 |

| 4.9  | Power Comparisons 16-bit Math Test                | 31 |

| 4.10 | Energy Comparisons 16-bit Math Test               | 31 |

| 4.11 | 16-bit Math Energy Estimation for NTV and STV     | 32 |

| 4.12 | Power Comparisons 16-bit Switch Test              | 34 |

| 4.13 | Energy Comparisons 16-bit Switch Test             | 34 |

|      | 16-bit Switch Energy Estimation for NTV and STV   | 35 |

|      | Power Comparisons 32-bit Math Test                | 37 |

| 4.16 | Energy Comparisons 32-bit Math Test               | 37 |

| 4.17 | 32-bit Math Energy Estimation for NTV and STV     | 38 |

| 4.18 | Power Comparisons RAM Test                        | 40 |

| 4.19 | Energy Comparisons RAM Test                       | 40 |

| 4.20 | RAM Energy Estimation for NTV and STV             | 41 |

| 4.21 | Power Comparisons SPI Test                        | 43 |

| 4.22 | Energy Comparisons SPI Test                       | 43 |

|      | SPI Energy Estimation for NTV and STV             | 44 |

| 4.24 | Power Comparisons TCP/IP Checksum Test            | 46 |

|      | Energy Comparisons TCP/IP Checksum Test           | 46 |

|      | TCP/IP Checksum Energy Estimation for NTV and STV | 47 |

# List of Acronyms

$V_{dd}$  supply voltage.

$V_{th}$  threshold voltage.

**AHB** Advance High Performance Bus.

**AMBA** Advance Microcontroller Bus Architecture.

**APB** Advance Peripherial Bus.

${\bf ARM}\,$  Advance Risc Machine.

$\mathbf{AVR}\ \mathrm{AVR}\ \mathrm{core}.$

AVR bus AVR Bus System.

$\mathbf{AVR32}\ \mathrm{AVR32}\ \mathrm{UC}\ \mathrm{core.}$

**CMOS** Complematry Metal Oxide Semiconductor.

**CPU** Central Processing Unit.

**DSP** Digital Signal Processor.

**DVE** Discovery Visualization Environment.

**DVFS** Dynamic Voltage Frequency Scaling.

GPIO General Purpose Input Output.

HDL Hardware Description Language.

I/O Input/ Output.

**IoT** Internet of Things.

${\bf nMOS}\,$ n-channel Metal Oxide Semiconductor.

**NTNU** Norwegian University of Science and Technology.

${\bf NTV}\,$  Near-Threshold Voltage.

**pMOS** p-channel Metal Oxide Semiconductor.

**RISC** Reduced Instruction Set Computer.

**RTL** Register Transfer Level.

SAIF file Switching Activity Interchange File.

SoC System on Chip.

- **SPI** Serial Peripherial Interface.

- ${\bf STV}$  Sub-Threshold Voltage.

- ${\bf TCP}\,$  Transfer Control Protocol.

- **TCP/IP Checksum Computation** Tranfer Control Protocol / Internet Protocol Checksum Computation.

- VCD file IEEE standard waveform database dumpfile.

- VCS Verilog Compiler Simulator.

- **VPD file** Synopsys waveform database dumpfile.

# Chapter – Introduction

In today's world the number of devices featuring features enabled by embedded systems is increasing. At the core of these devices there is a System on Chip (SoC) consisting of at least a CPU a General Purpose Input Output (GPIO), a memory and a bus connecting all. From the user /environment perspective the goal of these SoC is to react to stimulus on the GPIO. In a well implemented system the reaction to the stimuli is a appropriate according to a program stored in the memory ran by the CPU. The human machine interfaces for the majority of this systems are very limited or non existent. But these machines are the cornerstone of modern consumer products which features have become standard of living in modern industrialized societies.

At the same time there is a huge pressure towards have higher integration between devices by means of sharing data, collaborating to solve tasks, accessing remote peripherals, producing data, etc. All of that will enable the implementation of interesting and useful features such as load balancing in an electric grid by timing when and where electric consumers can get online and how much power it can be drawn form there. For this to happen SoC besides the CPU, memory GPIO and bus it must contain at least one communication module that enables it to communicate with other devices. And the vast majority of this embedded systems will have limited access to electrical power.

Since the set of tasks that is expected to be performed by the embedded systems varies a lot depending on the application one might be tempted to think that different CPUs will perform better than others performing certain tasks. Parallel to that it is known that the amount of power used by any electronic device is proportional to the squared of the voltage. The juxtaposition of the previous two statements mean that in order to implement an efficient device whose energy consumption is as low as possible -so it can be operated with a constrained power budget like a small battery or by harvesting energy- It is necessary to study different CPUs performing the same tasks. It is also necessary to watch the effect that the use of different

#### 2 1. INTRODUCTION

implementations of different on the energy consumption. The goal of this thesis to observe the energy consumption in an 8-bit implementation of Atmel's popular AVR core and in a 32-bit AVR32 and to quantify the impact different process technology and reduced library more suitable to a ultra low voltage library.

## **1.1** Historical Perspective

#### 1.1.1 Internet of Things

In 1999 Kevin Ashton was the first person to use the term Internet of Things (IoT) [2] during a presentation for Procter & Gamble identifying the potential of integrating the RFID technology in the supply chain to gather data and the internet. He points out that most of the information available on the internet has been either been input by a human or triggered by a human action. The accuracy, consistency and flow of this data then is dependent of human accuracy, consistency and latency. Thanks to RFID technology and similar technologies data can be automatically be uploaded to the internet with the accuracy, consistency and latency of machines. Is also Ashton's view that this automatic data gathering capabilities and easy access thru the internet will empower machines to reduce waste, increase efficiency and alert when maintenance task should be performed.

Meanwhile in 2004 an article published on Scientific American [21] made the analogy of the segmentation of different communication protocols for devices to comunicate such as ZigBee, Bluetooth, etc. to the Arpanet and other Internet predecessors in the 1960's and makes a very good case why devices should use the same internet standards to exchange information. Among the main advantages identified by the article are packet switched networks, unique addressing for each nodes

#### 1.1.2 Related Work

This work builds on the idea to use the AVR as a coprocessor for the AVR32 exposed in the master thesis of M Sc. Yahsir Mahmood[20]. It is also used a modified version of his test bench for benchmarking the AVR32. On his thesis M. Sc Mahmood goes thru the process of designing an energy efficient AVR Bus System (AVR bus) to Advance Peripherial Bus (APB) needed to access the peripherals with the AVR and the AVR32[20]. In this work however instead of using the AVR bus to APB bridge an AVR bus to Advance High Performance Bus (AHB) bridge is used as it enables the AVR to access the same high performance RAM as the AVR32 and puts the AVR on the same heretical level as AVR32.

#### **1.2** Asigment Interpretation

The following tasks were proposed and executed to address the problem:

- **Task 1:** Set up a test bench that connects RAM, SPI communication modules and other periferials via an AMBA AHB lite bus with a CPU.

- **Task 2:** Test access to memory and peripherals connected in task 1 using an AVR and an AVR32 and confirm it function correctly.

- **Task 3:** Choose a set of test programs to benchmark that perform tasks of a simple but representative IoT application.

- **Task 4:** Synthesize the set-ups used for task 2 in different feature sizes and with different constraints.

- **Task 5:** Perform power analysis on the results of task 4 running the test programs established on task 3.

- Task 6: Compute the energy used to perform each test program under each net-lists.

Upon completion of these tasks data the following objectives are achieved:

- **Objective 1:** Identify the effect on power and energy consumption that constraining the standard cells that the synthesis tool can use under different scenarios.

- **Objective 2:** Identify which scenarios favor the architecture of the AVR32 and which favor the aAVR.

- **Objective 3:** Test if the conclusions from objective 2 stands if feature size is changed.

- **Objective 4:** Extrapolate the energy and power figures if implemented on an ultra low voltage library.

# **1.3** Contributions

A test bench that accepts any core that interfaces thru AHB bus. Eight different test relevant to the IoT scenario to better understand the power, energy consumption of the AVR and AVR32. A comparison consisting of 640 experiments where libraries and timing contains and feature size core and application were varied to monitor the power and energy consumption and an estimate of what to expect when moving to the STV and NTV domains.

#### 4 1. INTRODUCTION

# 1.4 Report Organization

This report is organized as:

- **Chapter 1: Introduction** Introduces the master thesis, provides some historical perspective, states how the problem was interpreted, how it was approached, summarizes the contributions of the thesis and shows how the report is organized.

- **Chapter 2: Background** Provides the theoretical background on the components of power on a Complematry Metal Oxide Semiconductor (CMOS) circuit, examines some techniques to save power while paying performance penalty such as Dynamic Voltage Frequency Scaling (DVFS) and voltage islands and explains the potentials saving that can be achived by reducing the voltage near and below the threshold region. Also comments on the advantage of heterogenous computing and shows two commercial examples.

- **Chapter 3: Implementation** Describe the work flow that was followed, the components that were used, how were used, the tests that were performed and how they were performed the tools that were used for testing.

- **Chapter 4: Results** Shows the result obtained by the methodology proposed. Address each test and extracts and directs attention to interesting facts derived from the results .

- Chapter 5: Discussion Analyzes the results and provides some explanations .

## 2.1 Power

There are two sources of power dissipation by a CMOS circuit [22]

$$P_{total} = P_{dynamic} + P_{static} \tag{2.1}$$

#### 2.1.1 Dynamic Power

Dynamic power is consumed when changing the logic level the inputs of a gate, this causes the n-channel Metal Oxide Semiconductor (nMOS) and p-channel Metal Oxide Semiconductor (pMOS) transistors to switch. From figure it is appreciated that any switching activity will cause that the pMOS and the nMOS transistors are in the *conducting* state at the same time causing a *short circuit current* to flow between supply voltage  $(V_{dd})$  and *GND*. At the same time the effective load capacitance is discharged or charged causing further power consumption. [22]

$$P_{dynamic} = P_{switching} + P_{short\ circuit} \tag{2.2}$$

It is possible to express:

$$P_{short\ circuit} = I_{short\ circuit} V_{DD} \tag{2.3}$$

Where  $P_{short\ circuit}$  is the average short-circuit power,  $I_{short\ circuit}$  is the average short-circuit current.

For quantifying the power dissipated by the switching activity we need to know two quantities the effective capacitance driven by the gate and how often this capacity (switching frequency) is charge/discharge. The effective capacitance is dependent of the gate, interconnect and the load. The switching frequency is dependent of the logic and clock frequency. After some mathematics and analysis of the circuit is possible to express the average switching power as: [22]

$$P_{swtiching} = \alpha C V_{DD}^2 f \tag{2.4}$$

#### 6 2. BACKGROUND

Where  $P_{swtiching}$  is the average swtiching power,  $\alpha$  is the *activity factor* that expresses in terms of the clock frequency the charging/ discharging, C is the *effective capacitance* and f is the clock frequency.

#### 2.1.2 Static Power

Figure 2.1: NMOS.[24]

Static power for CMOS has three main contributors. Subthreshold leakage, gate leakage drain and source diffusion leakage.<sup>[22]</sup>

$$P_{static} = (I_{sub} + I_{gate} + I_{junct})V_{DD}$$

$$(2.5)$$

Figure 2.1 shows the junction of semiconductor materials that form an pMOS transistor. Thru these junctions and thanks to minority carriers there is a leakage current. The gate leakage can be reduced by substituting the silicon dioxide with high dielectric materials between the gate and the semiconductor substrate.[12] Leakage of the junctions can be reduced by doping [1]and voltage on the body[8].

When operating on the subthreshold region the MOS transistor then can be modeled as bipolar transistor as shown by Figure bla the and equation 2.6 describes the behavior of the current flowing from drain to source.<sup>[22]</sup>

$$I_{sub} = I_{ds0} e^{\frac{V_{gs} - V_{t0} + \eta V_{ds} - \kappa_{\gamma} V_{sb}}{nv_T}} \left(1 - e^{-\frac{V_{ds}}{v_T}}\right)$$

(2.6)

Where  $I_{ds0}$  is the current at threshold it is dependent of process and geometry,  $V_{gs}$  is the voltage between the gate and source,  $V_{t0}$  threshold voltage when  $V_{source} = V_{body}$ ,  $\eta$  DIBL coefficient,  $V_{ds}$  voltage between drain and source,  $\kappa_{\gamma}$  body effect (geometry, dielectric, surface potential, etc),  $V_{sb}$  Voltage between source and body,  $v_T$  Termal voltage. [22] From equations 2.5 and 2.3 have a linear dependency to  $V_{DD}$ , but is worth noticing that  $I_{sub}$  is exponentially dependent of  $V_{ds}$  at the same time equation 2.4 shows a quadratic dependency to  $V_{DD}$ . Then it is shown that lowering the operating voltage is a way to save power. Nevertheless reducing the voltage can degrade the performance as it reduces de current that goes from drain to source and with that the time that is required to drive the loads increasing delays.

# 2.1.3 Dynamic Voltage Frequency Scaling (DVFS) and Voltage Islands

DVFS scaling is a technique used to save power. It reduces de voltage and frequency when the work load is low (meaning the timing constrains are more relaxed) and increases the voltage and frequency when the work load is high (meaning the timing contains are tighter). For achieving an energy efficient implementation it is required that voltage/ frequency regulator is an efficient one, the granularity of the voltage and frequency to choose from allow to adapt at any processor workload. The main goal is to consume less energy, this means that the power savings for a task must be greater than the time increase for the same task.[7]

It is possible to have different voltages on a SoC this technique is known as voltage islands. Each island operates on a different voltage level .This technique allows blocks to be grouped together on an island where the voltage presents the right compromise between the power savings and performance degradation. It does not require the regulation overhead that DVFS and it is not aware of the workload situation. [14]

# 2.1.4 Near- Threshold Voltage (NTC) and Sub-Threshold Voltage (STC)

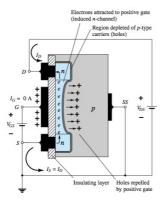

As stated in the previously, reducing the voltage dramatically reduce the power consumed. Figure 2.2 shows the relationship between the energy spent for operation, the delay and the supply voltage. More energy is saved from the transition from super-thresholdvoltage to NTV than form NTV to STV this is due to the increase in leakage that is observed when  $V_{dd}$  < threshold voltage ( $V_{th}$ ). The same figure also shows an exponential growth on the delay in the STV region. It is of particular interest the existence of a minimum on the energy per operation curve that indicates there is a voltage in the sub-threshold region that is optimum form the energy perspective but comes at the cost of increased delay. [11]

#### 8 2. BACKGROUND

Figure 2.2: Energy per Operation and Delay vs Voltage.[11]

## 2.2 Heterogenous Computing

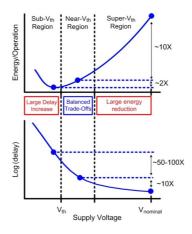

Kummar et al. have shown that higher energy efficiency can be achieved on a SoC by using heterogenous cores.[17] By definition an heterogenous core system is a multi-core system made up by different cores. There are difference in terms of energy efficiency, performance, power consumption and capabilities between different cores. There are energy efficient cores that are suitable for simple operations and high performance cores capable of performing complex task but the power consumption is high. Having both on the same SoC allow to have the best of both worlds.

Industry have taken notice of this and there are examples of heterogenous mulicores that feature an energy efficient core and a high performance core being deployed such as:

Advance Risc Machine (ARM) exploits the energy efficiency of the Cortex- A7 core (LITTLE) and the high performance of the Cortex- A15 (big) in its *big.LITTLE* architecture shown on Figure 2.3. ARM is quick to notice that despite labeling the Cortex-A7 as *LITTLE* it features micro-architecture advances that culminates on performance than implementations of the Cortex-A8 at a fraction of the power.[13]

NVIDIA uses a power optimized Cortex A9 core(companion core) and four performance optimized Cortex A9 cores (main cores) in its *Tegra 3* formerly known as *Kal-El*. The companion core is limited to 500MHz [23]

Figure 2.3: big.LITTLE system.[13]

# 2.2.1 8/16bit cores vs 32-bit cores

Since the smbedded systems environment is diverse, system performance is difficult to define. Some applications require realtime guarantees, others require high precision and/or fast measurement peripherals, others have very limited energy/power contains and finally there are the ones that require lots of computing power.[16] Figure 2.4a shows the benchmark obtained after running the code on Figure 4.2b. It is shown that the AVR is a good candidate to be considered for be a *LITTLE* like co- processor. For an heterogenous system. 8/16 bit processors have the problem that they not support

| CPU Architectures | Code size<br>(bytes) | Execution time<br>(cycles) |

|-------------------|----------------------|----------------------------|

| 8051              | 112                  | 9384                       |

| PIC16             | 87                   | 2492                       |

| AVR               | 46                   | 335                        |

(a) Code Size and Execution

| int max(int *array)<br>{ |

|--------------------------|

| char a;                  |

| int maximum=-32768;      |

| for (a=0;a<16;a++)       |

| if (array[a]>maximum)    |

| maximum=array[a];        |

| return (maximum);        |

| }                        |

|                          |

(b) Sample Code

Figure 2.4: 8-bit CPU Comparison[16]

large memory space since the mayority of them feature only 16.bit address bus. This an other limitations have open the door for 32-bit cores that might be not the right solution due its increase complexity, Nevertheless there are application areas that require some of the extra performance offered by the 32-bit alternative for a small part

#### 10 2. BACKGROUND

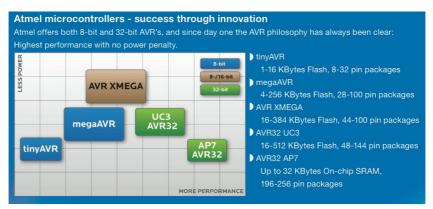

of the application providing further motivation for an heterogenous architecture.[16] Figure 2.5 Shows Atmel's portfolio for 8-bit and 32-bit micro controllers.

Figure 2.5: Atmel's Product Range [6]

# Chapter Implementation

This chapter is divided in three sections. Setup and Work Flow covers the hardware and test cases used for this project. Synthesis explains how the synthesis was performed and declares the libraries used to produce the net-lists on which the power analysis was performed. And the power analysis section go thru the generation of the reports and data gathering and manipulation. Data that is presented in Chapter 4

# 3.1 Setup and Work Flow

This section is divided into two main parts. The first part describes the hardware used and the second describes the software used. It is very important to note that there is no silicon used for this project.

The basic work flow is as follows:

- Step 1: The hardware is defined at the RTL label and a test program is prepared.

- **Step 2:** Synopsys' Verilog Compiler Simulator (VCS) to produce a Synopsys waveform database dumpfile (VPD file).

- **Step 3:** Verify the correct functionality using Discovery Visualization Environment (DVE).

- **Step 4:** Test case is prepared on C or asm and compile them with AVR-toolchain or AVR32-toolchain (depending on the targeted processor) to produce the executable.

- Step 5: Use executable, VCS, and DVE to check function, start and end times of the program or interesting subroutine.

- **Step 6:** Use Synopsys' design complier and synthesis script to produce the appropriate net-list and save the it for future usage.

- **Step 7:** Transform the VPD file into a IEEE standard waveform database dumpfile (VCD file) and this into a Switching Activity Interchange File (SAIF file) for this last transformation the tool requires the start and end time of interest.

- **Step 8:** Use Synopsys' design compiler and power analysis script with the net-list generated on step 6 and the SAIF file on the step 7

- **Step 9:** Extract and analyze the data outputted on the power report generated on step 8.

#### 3.1.1 Hardware

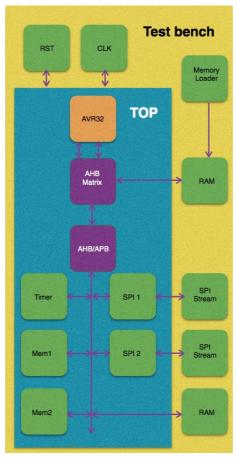

In order to be able to compare the energy consumption of the AVR32 and the AVR they must be tested under the same circumstances. Figure 3.2 and 3.1 show the test environments for both processors. As it is shown the test environments are as similar as it can be. The only mayor difference is that the AVR setup includes a bridge AVR bus to AHB. This bridge is not necessary for the AVR32 since it has native interface for AHB.

#### 3.1.1.1 AVR32 UC core

The AVR32 is a Super Harvard architecture 32-bit processor that features a compact Reduced Instruction Set Computer (RISC) instruction set including Digital Signal Processor (DSP) instructions fully orthogonal. This processor has two AHB interfaces one for the program memory and other for data and peripheral communication, RAM interface, 15 32-bit wide general purpose registers 32-bit wide stack pointer, program counter and link register. It is a 3- stage pipeline processor allowing one instruction per clock cycle for most instructions.[5]

#### 3.1.1.2 AVR core

The AVR is a Harvard architecture 8-bit RISC processor. It has 32 registers 8-bits wide, The last six is are concatenated in pairs to form a 16-bit wide pointers to address the data space. Since it is a Harvard architecture the program memory and the data memory are not only physically separated but they have separate address spaces, separate data and address lines and the data memory is accessed by using the same instructions as the Input/ Output (I/O). [4]

The AVR data bus is synchronous based on master/ slave scene and has 16-bit for addresses, 8-bit for data form the master, 8-bits for data from the slave, write, read, wait, single bus cycle and burst signals. This bus allow single access operation, this means that on the same clock cycle the master puts the address on the address lines and either send data or receives it and is ready for another operation on the next clock cycle if there is no wait signal form the slave.[3]

Figure 3.1: AVR setup

#### 3.1.1.3 Advance High Performance Bus

AHB is a multi master bus protocol part of the Advance Microcontroller Bus Architecture (AMBA) family of open protocols for on-chip communications created by ARM. AHB is the high performance bus that supports high clock frequency. It is a pipelined bus that uses the master/ slave scheme which means the master on the first clock cycle put the address and the appropriate control signals and the next clock cycle it expects a reply form the slave (transfer complete, error, wait state or split transaction) and puts the next address on the bus. [18]

For the scope of this project it is used the single master AHB lite standard which is a simpler implementation [19] and the bridge implemented is constrained to simple

#### 14 3. IMPLEMENTATION

Figure 3.2: AVR32 setup

write <sup>1</sup> and simple read that allow the slaves to add wait states.

#### 3.1.1.4 Top and Test bench

Figure 3.2 and Figure 3.1 shows what is instantiated at the top level and how it interfaces with the test bench. The top-level include the processor core (AVR or AVR32) AHB, APB busses -in the case of the AVR the AHB to AVR bus- two SPI modules a timer, two memory modules. The test bench has the clock generator, RAMs, program memory and the program memory loader that takes the .hex file and loads the memory with it.

$<sup>^1 \</sup>rm Due$  the mismatch between the 32-bit wide data bus from the AHB and the 8-bit wide data bus from the AVR bus all write operations are a read/ modify operations

| Peripherial    | Base Address            |

|----------------|-------------------------|

| AHB RAM        | 0x00000000              |

| APB RAM        | $0 \mathrm{xFFFF} 0000$ |

| Timer          | $0 \mathrm{xFFFF} 2000$ |

| SPI 1          | $0 \mathrm{xFFFF} 3000$ |

| SPI 2          | 0xFFFF4000              |

| ${\rm Mem}\ 1$ | 0xFFFF0000              |

| ${\rm Mem}\ 2$ | $0 \mathrm{xFFFF} 0000$ |

| Table 3.1:     | Address Map             |

Table 3.1 shows the peripherals with it is corresponding Base Address.

#### 3.1.2 Software

This section explains what the each test do. All this were written in C (except for the case of the SPI for the AVR which was written in assembly) and complied by the AVR toolchain and AVR32 toolchain to produce the executable code needed by the processors.

All the test were proposed thinking on an IoT scenario were a micro controller gets data from a sensor via a communication peripheral (SPI was chosen due its simplicity and huge popularity), the communication is bidirectional -the data streams are simulated by the test bench- performs some arithmetic manipulation (addition correcting systematic error and multiplication for sensitivity error correction), testing this value against a parameter and use Transfer Control Protocol (TCP) to connect to the internet. Due to board range of applications for the arithmetic manipulation three tests were proposed -8, 16, and 32 bit- and due to the unknown amount of cases to be handled two tests were proposed -8 and 16 bit-. The TCP is a complex protocol and with the support given by media access hardware undefined it is difficult to specify what to test. The computing the check sum of a TCP packet was chosen due to its importance when determining data integrity and assuming simple hardware that implements complete functionality for layers 1 to 3 of the OSI model.

#### 3.1.2.1 8-bit Math Test

This test in its main defines two 8-bit operands and calls a function that adds and a function that multiplies. It takes 4340ns for the AVR and 1220ns for the AVR32 to finish.

#### 3.1.2.2 8-bit Switch Test

This test in its main defines a 8-bit operand and calls a function that selects the case and returns a 8-bit value to the main. It takes 1700ns for the AVR and 980ns for the AVR32 to finish.

### 3.1.2.3 16-bit Math Test

This test in its main defines two 16-bit operands and calls a function that adds and a function that multiplies. It takes 5680ns for the AVR and 1340ns for the AVR32 to finish.

#### 3.1.2.4 16-bit Switch Test

This test in its main defines a 16-bit operand and calls a function that selects the case and returns a 16-bit value to the main. It takes 2120ns for the AVR and 980ns for the AVR32 to finish.

#### 3.1.2.5 32-bit Math Test

This test in its main defines two 32-bit operands and calls a function that adds and a function that multiplies. It takes 10720ns for the AVR and 1160ns for the AVR32 to finish.

#### 3.1.2.6 RAM Write Test

This test in its main performs 100 RAM writes. It takes 30340ns for the AVR and 6640ns for the AVR32 to finish.

### 3.1.2.7 SPI Read and Wirte Test

This test its main sets up SPI 1, SPI 2, then performs 10 times a SPI read on SPI 1, a multiplication, 8-bit shift and a write on SPI 2. The program for the AVR first configures the bridge to access the I/O space and then proceeds to do the same as the program for the AVR32 and after that it configures back the bridge to address the memory space. It takes 18820ns for the AVR and 8560ns for the AVR32 to finish.

## 3.1.2.8 TCP/IP Checksum Computation Test

This test in its main computes the check sum field of a 120 byte TCP frame. which is a set of 16-bit sum, shift and byte swap operations. It takes 37220ns for the AVR and 7900ns for the AVR32 to finish.

#### 3.2 Synthesis

The goal of the synthesis is to translate the Register Transfer Level (RTL) code to a net-list of interconnected logic gates chosen from a library.

The synthesis is done by the Synopsys' design compiler following the instructions and contains stated by the synthesis scripts.

Performing the synthesis is paramount for this project. Changes done on the constrains and library selection produced the variation in results that will be presented on Chapter 4 and discussed on Chapter 5. To produce a net-list a library is chosen, a clock period is targeted and a maximum area is defined. For all cases the maximum area set to zero knowing it will be impossible to the tool to achieve this but will force the tool to get the smallest possible, the tool is also instructed to do its best effort. Per each library used ten clock periods were targeted, form 1ns to 10ns with a step of one nano second. Additionally the tool is intructed to keep the hierarchy -this is don e so the power analisys is heriarchial as well-

#### 3.2.1 Synthesis script

The script commands the tool to do:

Step 1: Analyze.

Step 2: Elaborate.

Step 3: Link.

Step 4: Load the library with the standard cells.

Step 5: Load the constraints (area, timing, wire model).

Step 6: Compile the design (clock gating is performed at this stage).

Step 7: Write net-lists.

The set of steps defined before will produce a net list that would be used on power and energy analysis described later this chapter. Ideally for this project a STV or NTV library should be used for this project but no such library was available so a super threshold voltage library was restricted to simulate the restriction in terms of gates that are present in a subthreshold voltage libraries.

The synthesis tool produces the following reports:

#### 18 3. IMPLEMENTATION

- **Area:** Reports the area taken bay the combinational logic, non combinational and sequential and the hierarchical distribution.

- **Clock Gating:** Shows the elements that are clock gated with its inputs, outputs and related registers. Presents the elements that were not able to be clock gated and the violation that will ocur if gated. It also displays a summary with the number of clock gating elements, the number of registers gated, the number of registers ungated.

- **Resources:** Reports on the resources shared by the modules, the implementations and the multiplexors added.

- Power: Presents a power consumption estimate.

- **Timing:** Shows critical paths, different points on the path and the time it takes from point to point. Gives a summary on the required data time and the arrival of that data and computes the slack.

- **References:** Reports the cells that were used, library of origin, area per cell number of cells used and the total area that type of cell takes on the design

- All Violators: Reports on the modules that violate the timing and the area constrictions and by how much it is missed.

#### 3.2.2 Libraries

Two base libraries were used to produce the net-list used in this thesis. UMC's 130nm FSC0H\_D generic core and UMC's 65nm FSE0K\_D generic core. To see the effect of feature size on energy consumption. For the understanding the effects of a 130nm low voltage library two the cells available for the synthesis tool in two different stages. Both of this libraries are super-threshold voltage. There was no sub-threshold voltage nor near-treshold voltage available.

#### 3.2.2.1 UMC's FSC0H\_D Generic Core

#### No restrictions

This is a high performance 130nm library that provide support arithmetic cells for data-path design. The corner used was typical process 1.2 V at 25°C with a gate density of 250000 gates per mm<sup>2</sup> featuring a drawn gate length of  $0.12\mu$ m with a power consumption of 6nW/MHz/gate[9].

#### Restricted (ltd)

For these synthesis the tool was not allowed to use any gate with more inputs than two and the maximum outputs is two as well. This is the most restricted the library can get.

#### Restricted (ltd2)

For these synthesis the tool was allowed to use the same gates as the (ltd) case plus gates with a fan-in and fan-out of three.

#### 3.2.2.2 UMC's FSE0K\_D Generic Core

This is a low leakage 65nm library that provide support arithmetic cells for data-path design. The corner used was typical process 1.2 V at  $25^{\circ}$ C with a gate density of 900000 gates per mm<sup>2</sup> featuring a drawn gate length of  $0.06\mu$ m with a power consumption of 1.9nW/MHz/gate[10].

## **3.3** Power and Energy Analysis

#### 3.3.1 Power

Before doing the power analysis two things have to be ready. A net list produced by the synthesis tool and a SAIF file that contains the switching activity caused by a test program. For the power analysis again Synopsys' design complier is used with a report power script. The power script first it loads the library data base, it is very important to use the same library used during the synthesis. Then it reads the SAIF file and reports the power used by each component of the top level and the total power.

#### 3.3.2 Energy

The energy is obtained by multiplying the power (average power) results obtained by the report of the power analysis and multiply it by the time spent on the task (the time difference between the end time and start time used for generating the SAIF file) both the energy and power results are only valid for the test case being studied on the net list tested, since at its core it was generated with the switching activity the program caused. For purposes of this thesis the effects described on Section 2.1.4will be estimated a black box and the results described shown by Figure 2.2 apply directly system wide. By using the (3.1) the total energy consumption is estimated where  $\Delta$  energy consumption factor expressed as the ratio of the energy consumed when changing form the super-threshold voltage to the NTV or STV this wil yield to  $E_{total}$ being the energy consumed by the system under the NTV or STV conditions.

$$E_{total} = \Delta E_{total \ Super} \tag{3.1}$$

#### 20 3. IMPLEMENTATION

Based on Johnsen preliminary results[15] for the design of the *Full-Custom* SubNear-Threshold Cell Library in 130nm CMOS the values used for the STV case (350mV)  $\Delta = 0.072$  and for the NTV case (400mV)  $\Delta = 0.094$ . Only the result produced by netlist wiht a target clock period of 10ns will be used for the estimation. The net-list 130nmltd will be used for NTV and STV and the 130ltd2 ones for NTV.

# Chapter Results

In this section the results of the synthesis process with the different restrictions and the power analysis data will be presented in graph.

#### 4.1 Synthesis AVR and AVR32

Ten different clock periods were targeted to produce ten net lists for each core set-up (AVR or AVR32) and library (UMC's FSC0H\_D Generic Core -130nm-, UMC's FSC0H\_D Generic Core Restricted -130nmltd-, UMC's FSC0H\_D Generic Core Restricted -130nmltd2- or UMC's FSE0K\_D Generic Core) a total of 80 net lists-65nm-.

#### 4.1.1 Library variation

#### 4.1.1.1 UMC's FSC0H\_D Generic Core Unrestricted (130nm)

This is the base case. Against the results obtained by this set of net lists comparisons will be made since all the available cells are used and power optimization technique clock gating was done successfully.

#### 4.1.1.2 UMC's FSC0H\_D Generic Core Restricted (130nmltd)

This case is the best substitute candidate for a subthreshold voltage since all the gates with fan-ins and fan-outs larger than two were restricted. The clock gating cells were restricted so no clock gating was not performed. This case also takes the largest surface on the wafer.

#### 4.1.1.3 UMC's FSC0H\_D Generic Core Restricted (130nmltd2)

This case is the best substitute candidate for a STV since all the gates with fan-ins and fan-outs larger than three were restricted. The clock gating cells were restricted so no clock gating was not performed. This case also takes the largest surface on the wafer.

#### 4.1.1.4 UMC's FSE0K\_D Generic Core (65nm)

This case give us information on how power, area and timing scales for the superthreshold operation it is important as a reference point to observe the effect that feature size has on power and energy. This case also takes the smallest surface on the wafer.

#### 4.1.2 Area Comparison

Figure 4.1 shows that for every case and every core restricting the clock period below certain point causes the area to increase -around 4 ns for the AVR32 and around 3 ns AVR. Table 4.1 show some interesting comparisons that help us to watch the effects of the library constriction and core selection.

| Target         | 130     | nm      | 130n    | mltd    | 130m    | mltd2   | 651     | nm      |

|----------------|---------|---------|---------|---------|---------|---------|---------|---------|

| $(ns/\mu m^2)$ | AVR     | AVR32   | AVR     | AVR32   | AVR     | AVR32   | AVR     | AVR32   |

| 1              | 160634. | 347241. | 316990. | 714925. | 301690. | 675180. | 41094.4 | 99675.8 |

| 2              | 147715. | 343153. | 313741. | 716474. | 295957. | 677208. | 38298.6 | 92870.7 |

| 3              | 143369. | 336020. | 296455. | 697892. | 283271. | 655172. | 33063.  | 73243.8 |

| 4              | 130395. | 284294. | 285102. | 636489. | 273185. | 609820. | 30820.8 | 65494.4 |

| 5              | 125878. | 269527. | 280718. | 625014. | 270459. | 598123. | 30456.6 | 63887.7 |

| 6              | 124987. | 266066. | 280163. | 619191. | 269422. | 596939. | 30056   | 62560.3 |

| 7              | 124535. | 264314. | 279270. | 614902. | 269146. | 587792. | 29964.8 | 61721.6 |

| 8              | 124333. | 260168. | 279156. | 608965. | 268594. | 587566. | 29899.8 | 61392.3 |

| 9              | 124255. | 256329. | 279073. | 607360. | 268558. | 582834  | 29817.9 | 61009.3 |

| 10             | 124250. | 255328  | 279068. | 607254. | 268501. | 581165. | 29815.4 | 60802.2 |

Table 4.1: Area vs targeted time

#### 4.1.3 Timing Achieved

Table 4.2 shows that for every case and every core restricting the clock period below certain point causes the synthesis tool to fail to achieve the timing goal -around 4 ns for the AVR32 and around 3 ns AVR and there is minimum clock period achieved -around 3.1 ns for the AVR32 and 2 ns for the AVR using 130nm feature size-. For the 65nm library the minimum clock period is smaller -around 1.7 ns AVR and 2.4 ns for the AVR32-.

Figure 4.1: Area footprint

| Target | 13    | 0nm   | 130  | nmltd | 130r | nmltd2 | 65    | ónm   |

|--------|-------|-------|------|-------|------|--------|-------|-------|

| (ns)   | AVR   | AVR32 | AVR  | AVR32 | AVR  | AVR32  | AVR   | AVR32 |

| 1      | 2.07  | 3.09  | 1.94 | 3.1   | 2.01 | 3.09   | 1.74  | 2.38  |

| 2      | 2.57  | 3.04  | 2.47 | 3.07  | 2.44 | 3.08   | 2.18  | 2.46  |

| 3      | 3.06  | 3.19  | 3.03 | 3.18  | 3    | 3.24   | 3.08  | 3.08  |

| 4      | 4.07  | 4.07  | 4    | 4     | 4    | 4      | 4.08  | 4.08  |

| 5      | 5.07  | 5.07  | 5    | 5     | 5    | 5      | 5.08  | 5.08  |

| 6      | 6.07  | 6.07  | 6    | 6     | 6    | 6      | 6.08  | 6.08  |

| 7      | 7.07  | 7.07  | 7    | 7     | 7    | 7      | 7.08  | 7.08  |

| 8      | 8.07  | 8.07  | 8    | 8     | 8    | 8      | 8.08  | 8.08  |

| 9      | 9.07  | 9.07  | 9    | 9     | 9    | 9      | 9.08  | 9.08  |

| 10     | 10.07 | 10.07 | 10   | 10    | 10   | 10     | 10.08 | 10.08 |

Table 4.2:

Timing Achieved for each net-list

## 4.2 Power and Energy comparison between the AVR and AVR32

#### 4.2.1 8-bit Math Test

#### 4.2.1.1 Super Threshold Voltage

Figure 4.2: Power Graphs for the 8-bit Math Test

Figure 4.3: Energy Graphs for the 8-bit Math Test

Figure 4.4: Power Density Graphs for Figure 4.5: CPU % Power Graphs for<br/>the 8-bit Math Testthe 8-bit Math Test

|                                                            | Total Power |      | CPU Power |      | wer  |      |

|------------------------------------------------------------|-------------|------|-----------|------|------|------|

|                                                            | Max         | Min  | Mean      | Max  | Min  | Mean |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nm       | 1.83        | 1.58 | 1.65      | 3.38 | 2.68 | 2.87 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd    | 1.84        | 1.66 | 1.71      | 3.32 | 2.79 | 2.93 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd2   | 1.85        | 1.61 | 1.69      | 3.28 | 2.59 | 2.8  |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)65\text{nm}$  | 1.81        | 1.51 | 1.59      | 3.23 | 2.44 | 2.63 |

| $\left(\frac{\text{AVR32ltd}}{\text{AVR32}}\right)$ 130nm  | 1.11        | 1.05 | 1.1       | 1.18 | 1.09 | 1.15 |

| $\left(\frac{\text{AVR32ltd2}}{\text{AVR32}}\right)$ 130nm | 1.08        | 1.04 | 1.06      | 1.13 | 1.07 | 1.1  |

| $\left(\frac{\text{AVR3265}}{\text{AVR32130}}\right)$ nm   | 0.41        | 0.36 | 0.39      | 0.4  | 0.32 | 0.36 |

| $\left(\frac{\text{AVRltd}}{\text{AVR}}\right)$ 130nm      | 1.08        | 1.04 | 1.06      | 1.16 | 1.1  | 1.12 |

| $\left(\frac{\text{AVRltd2}}{\text{AVR}}\right)$ 130nm     | 1.05        | 1.01 | 1.04      | 1.16 | 1.01 | 1.13 |

| $\left(\frac{\text{AVR65}}{\text{AVR130}}\right)$ nm       | 0.41        | 0.4  | 0.4       | 0.41 | 0.38 | 0.39 |

Table 4.3: Power Comparisons 8-bit Math Test

|                                                            | Total Energy |      | CPU Energy |      | ergy |      |

|------------------------------------------------------------|--------------|------|------------|------|------|------|

|                                                            | Max          | Min  | Mean       | Max  | Min  | Mean |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nm       | 0.51         | 0.44 | 0.46       | 0.95 | 0.75 | 0.81 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd    | 0.52         | 0.47 | 0.48       | 0.93 | 0.78 | 0.82 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd2   | 0.52         | 0.45 | 0.47       | 0.92 | 0.73 | 0.79 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)65\text{nm}$  | 0.51         | 0.43 | 0.45       | 0.91 | 0.69 | 0.74 |

| $\left(\frac{\text{AVR32ltd}}{\text{AVR32}}\right)$ 130nm  | 1.11         | 1.05 | 1.1        | 1.18 | 1.09 | 1.15 |

| $\left(\frac{\text{AVR32ltd2}}{\text{AVR32}}\right)$ 130nm | 1.08         | 1.04 | 1.06       | 1.13 | 1.07 | 1.1  |

| $\left(\frac{\text{AVR3265}}{\text{AVR32130}}\right)$ nm   | 0.41         | 0.36 | 0.39       | 0.4  | 0.32 | 0.36 |

| $\left(\frac{\text{AVRltd}}{\text{AVR}}\right)$ 130nm      | 1.08         | 1.04 | 1.06       | 1.16 | 1.1  | 1.12 |

| $\left(\frac{\text{AVRltd2}}{\text{AVR}}\right)$ 130nm     | 1.05         | 1.01 | 1.04       | 1.16 | 1.01 | 1.13 |

| $\left(\frac{\text{AVR65}}{\text{AVR132}}\right)$ nm       | 0.41         | 0.4  | 0.4        | 0.41 | 0.38 | 0.39 |

Table 4.4:

Energy Comparisons 8-bit Math Test

In Figure 4.2a it is observed that the power consumption for the systems using the AVR is very similar for the 130nmltd2 and 130nmltd cases when targeting clock periods larger than 4ns, when targeting periods smaller there is a transition around 3ns and in the vicinity of 2ns the 130ltd2 behaves similar to the 130nm case mainly because the power consumption of the later grows faster than the 130nmltd. Figure 4.2b shows that the AVR 130nmltd2 core consumes more power than its counterparts the but the effect described earlier it is present here as well and around the 3ns it is surpassed by the 130nmltd. The power consumption of the AVR32 65nm is comparable with the power consumption with the implementations of the AVR cores using the 130nm library. Figure 4.3a shows that systems with AVR32 cores consume half the energy than the ones based on the AVR core, however Figure 4.3b shows that if we compare just cores AVR32 cores energy expenditure is only 80% (on average) the energy used by the AVR cores. Figure 4.5Timing restriction around 3ns produces AVR core that the smallest power fraction under the 130nmltd2 case.

| 4.2.1.2 | $\mathbf{NTV}$ | and | $\mathbf{STV}$ |

|---------|----------------|-----|----------------|

|         |                |     |                |

| (pJ)                 | $65 \mathrm{nm}$ | $130 \mathrm{nm}$ | 130  ltd2 | 130 ltd |

|----------------------|------------------|-------------------|-----------|---------|

| AVR                  |                  |                   |           |         |

| Super $TV$           | 2035.46          | 5034.4            | 5281.78   | 5320.84 |

| NTV                  |                  |                   | 496.487   | 500.159 |

| STV                  |                  |                   |           | 383.1   |

| AVR32                |                  |                   |           |         |

| Super $TV$           | 866.2            | 2228.94           | 2411.94   | 2481.48 |

| NTV                  |                  |                   | 226.722   | 233.259 |

| $\operatorname{STV}$ |                  |                   |           | 178.667 |

Table 4.5:

8-bit Math Energy Estimation for NTV and STV

#### 4.2.2 8-bit Switch Test

#### 4.2.2.1 Super Threshold Voltage

Figure 4.6: Power Graphs for the 8-bit Switch Test

Figure 4.7: Energy Graphs for the 8-bit Switch Test

Figure 4.8: Power Density Graphs for Figure 4.9: CPU % Power Graphs forthe 8-bit Switch Testthe 8-bit Switch Test

|                                                            | Total Power |      | CPU Power |      |      |      |

|------------------------------------------------------------|-------------|------|-----------|------|------|------|

|                                                            | Max         | Min  | Mean      | Max  | Min  | Mean |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nm       | 1.88        | 1.64 | 1.72      | 3.39 | 2.81 | 2.98 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd    | 1.89        | 1.73 | 1.77      | 3.39 | 2.84 | 3.04 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd2   | 1.91        | 1.75 | 1.79      | 3.39 | 3.01 | 3.17 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)65\text{nm}$  | 1.81        | 1.55 | 1.61      | 3.19 | 2.52 | 2.67 |

| $\left(\frac{\text{AVR32ltd}}{\text{AVR32}}\right)$ 130nm  | 1.11        | 1.05 | 1.09      | 1.17 | 1.08 | 1.14 |

| $\left(\frac{\text{AVR32ltd2}}{\text{AVR32}}\right)$ 130nm | 1.07        | 1.04 | 1.06      | 1.12 | 1.06 | 1.09 |

| $\left(\frac{\text{AVR3265}}{\text{AVR32130}}\right)$ nm   | 0.4         | 0.36 | 0.38      | 0.38 | 0.32 | 0.35 |

| $\left(\frac{\text{AVRltd}}{\text{AVR}}\right)$ 130nm      | 1.08        | 1.04 | 1.06      | 1.15 | 1.09 | 1.12 |

| $\left(\frac{\text{AVRltd2}}{\text{AVR}}\right)$ 130nm     | 1.04        | 1.   | 1.01      | 1.08 | 0.99 | 1.02 |

| $\left(\frac{\text{AVR65}}{\text{AVR130}}\right)$ nm       | 0.42        | 0.41 | 0.41      | 0.41 | 0.39 | 0.39 |

Table 4.6:

Power Comparisons 8-bit Switch Test

|                                                            | Total Energy |      |      | CPU Energy |      |      |

|------------------------------------------------------------|--------------|------|------|------------|------|------|

|                                                            | Max          | Min  | Mean | Max        | Min  | Mean |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nm       | 1.08         | 0.95 | 0.99 | 1.96       | 1.62 | 1.72 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd    | 1.09         | 1.   | 1.02 | 1.95       | 1.64 | 1.75 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd2   | 1.1          | 1.01 | 1.03 | 1.95       | 1.73 | 1.83 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)65\text{nm}$  | 1.04         | 0.89 | 0.93 | 1.84       | 1.45 | 1.54 |

| $\left(\frac{\text{AVR32ltd}}{\text{AVR32}}\right)$ 130nm  | 1.11         | 1.05 | 1.09 | 1.17       | 1.08 | 1.14 |

| $\left(\frac{\text{AVR32ltd2}}{\text{AVR32}}\right)$ 130nm | 1.07         | 1.04 | 1.06 | 1.12       | 1.06 | 1.09 |

| $\left(\frac{\text{AVR3265}}{\text{AVR32130}}\right)$ nm   | 0.4          | 0.36 | 0.38 | 0.38       | 0.32 | 0.35 |

| $\left(\frac{\text{AVRltd}}{\text{AVR}}\right)$ 130nm      | 1.08         | 1.04 | 1.06 | 1.15       | 1.09 | 1.12 |

| $\left(\frac{\text{AVRltd2}}{\text{AVR}}\right)$ 130nm     | 1.04         | 1.   | 1.01 | 1.08       | 0.99 | 1.02 |

| $\left(\frac{\text{AVR65}}{\text{AVR132}}\right)$ nm       | 0.42         | 0.41 | 0.41 | 0.41       | 0.39 | 0.39 |

Table 4.7: Energy Comparisons 8-bit Switch Test

Figure 4.6a it is observed that the power consumption for the systems using the AVR for the 130nmltd2 and 130nm cases. Figure 4.6b shows that the all the AVR based on the 130nm library consumes more or less the power than the AVR32 65nm. Figure 4.7a shows that all systems based on the 130nm library the differences on energy consumption are small or null around the 4ns target, the same effect is observed around the 3ns mark for the systems using the 65nm library. Figure 4.3b shows the same behavior described for the power consumed by the cpus expenditure is only 80% (on average) the energy used by the AVR cores. Figure 4.9 shows two groups the ones based on the AVR32 architecture and the ones based on the AVR architecture. It is interesting to note that for the AVR 130nm core fraction being near 3ns smaller than the one near the 4ns and the AVR32 65nm is significant less.

| (pJ)                 | $65 \mathrm{nm}$ | $130 \mathrm{nm}$ | 130  ltd2 | $130 \ \mathrm{ltd}$ |

|----------------------|------------------|-------------------|-----------|----------------------|

| AVR                  |                  |                   |           |                      |

| Super $TV$           | 788.8            | 1917.6            | 1931.2    | 2028.1               |

| NTV                  |                  |                   | 181.533   | 190.641              |

| $\operatorname{STV}$ |                  |                   |           | 146.023              |

| AVR32                |                  |                   |           |                      |

| Super $TV$           | 705.6            | 1815.94           | 1949.22   | 2019.78              |

| NTV                  |                  |                   | 183.227   | 189.859              |

| $\operatorname{STV}$ |                  |                   |           | 145.424              |

4.2.2.2 NTV and STV

Table 4.8: 8-bit Switch Energy Estimation for NTV and STV

#### 4.2.3 16-bit Math Test

#### 4.2.3.1 Super Threshold Voltage

Figure 4.10: Power Graphs for the 16-bit Math Test

Figure 4.11: Energy Graphs for the 16-bit Math Test

Figure 4.12: Power Density Graphs for Figure 4.13: CPU % Power Graphs forthe 16-bit Math Testthe 16-bit Math Test

|                                                            | Total Power |      | CPU Power |      | wer  |      |

|------------------------------------------------------------|-------------|------|-----------|------|------|------|

|                                                            | Max         | Min  | Mean      | Max  | Min  | Mean |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nm       | 2.01        | 1.71 | 1.8       | 3.99 | 3.13 | 3.38 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd    | 2.02        | 1.81 | 1.87      | 3.82 | 3.29 | 3.44 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd2   | 2.03        | 1.76 | 1.84      | 3.87 | 3.07 | 3.31 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)65\text{nm}$  | 1.99        | 1.63 | 1.71      | 3.86 | 2.84 | 3.06 |

| $\left(\frac{\text{AVR32ltd}}{\text{AVR32}}\right)$ 130nm  | 1.12        | 1.08 | 1.1       | 1.18 | 1.1  | 1.15 |

| $\left(\frac{\text{AVR32ltd2}}{\text{AVR32}}\right)$ 130nm | 1.08        | 1.04 | 1.06      | 1.13 | 1.05 | 1.09 |

| $\left(\frac{\text{AVR3265}}{\text{AVR32130}}\right)$ nm   | 0.41        | 0.36 | 0.39      | 0.4  | 0.32 | 0.36 |

| $\left(\frac{\text{AVRltd}}{\text{AVR}}\right)$ 130nm      | 1.08        | 1.04 | 1.06      | 1.16 | 1.1  | 1.12 |

| $\left(\frac{\text{AVRltd2}}{\text{AVR}}\right)$ 130nm     | 1.05        | 1.02 | 1.04      | 1.15 | 1.06 | 1.12 |

| $\left(\frac{\text{AVR65}}{\text{AVR130}}\right)$ nm       | 0.42        | 0.4  | 0.41      | 0.41 | 0.39 | 0.39 |

Table 4.9:

Power Comparisons 16-bit Math Test

|                                                            | Total Energy |      | CPU Energy |      | ergy |      |

|------------------------------------------------------------|--------------|------|------------|------|------|------|

|                                                            | Max          | Min  | Mean       | Max  | Min  | Mean |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nm       | 0.48         | 0.4  | 0.43       | 0.94 | 0.74 | 0.8  |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd    | 0.48         | 0.43 | 0.44       | 0.9  | 0.78 | 0.81 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd2   | 0.48         | 0.41 | 0.44       | 0.91 | 0.72 | 0.78 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)65\text{nm}$  | 0.47         | 0.38 | 0.4        | 0.91 | 0.67 | 0.72 |

| $\left(\frac{\text{AVR32ltd}}{\text{AVR32}}\right)$ 130nm  | 1.12         | 1.08 | 1.1        | 1.18 | 1.1  | 1.15 |

| $\left(\frac{\text{AVR32ltd2}}{\text{AVR32}}\right)$ 130nm | 1.08         | 1.04 | 1.06       | 1.13 | 1.05 | 1.09 |

| $\left(\frac{\text{AVR3265}}{\text{AVR32130}}\right)$ nm   | 0.41         | 0.36 | 0.39       | 0.4  | 0.32 | 0.36 |

| $\left(\frac{\text{AVRltd}}{\text{AVR}}\right)$ 130nm      | 1.08         | 1.04 | 1.06       | 1.16 | 1.1  | 1.12 |

| $\left(\frac{\text{AVRltd2}}{\text{AVR}}\right)$ 130nm     | 1.05         | 1.02 | 1.04       | 1.15 | 1.06 | 1.12 |

| $\left(\frac{\text{AVR65}}{\text{AVR132}}\right)$ nm       | 0.42         | 0.4  | 0.41       | 0.41 | 0.39 | 0.39 |

Table 4.10:

Energy Comparisons 16-bit Math Test

In Figure 4.10a shows a group for the AVR cores and another for the AVR32 under the 130nm library. The same effect is noted on Figure 4.10b with the AVR3265nm on the same group as the AVR cores based on 130nm library Figure 4.11a exhibits the same grouping behavior described for the power case with the note that the AVR 65nm system is clustered with the systems with AVR32 130nm.Figure 4.3b displays that if we compare just cores AVR32 cores energy expenditure is only 80% (on average) the energy used by the AVR cores. Figure 4.5Timing restriction around 3ns produces AVR core that the smallest power fraction under the 130nmltd2 case.

| (pJ)                 | $65 \mathrm{nm}$ | 130nm   | 130  ltd2 | 130 ltd |

|----------------------|------------------|---------|-----------|---------|

| AVR                  |                  |         |           |         |

| Super $TV$           | 2663.92          | 6554.72 | 6844.4    | 6935.28 |

| NTV                  |                  |         | 643.374   | 651.916 |

| $\operatorname{STV}$ |                  |         | —         | 499.34  |

| AVR32                |                  |         |           |         |

| Super $TV$           | 1022.42          | 2641.14 | 2856.88   | 2953.36 |

| NTV                  |                  |         | 268.547   | 277.616 |

| $\operatorname{STV}$ |                  |         |           | 212.642 |

4.2.3.2 NTV and STV

Table 4.11: 16-bit Math Energy Estimation for NTV and STV

#### 4.2.4 16-bit Switch Test

#### 4.2.4.1 Super Threshold Voltage

Figure 4.14: Power Graphs for the 16-bit Switch Test

Figure 4.15: Energy Graphs for the 16-bit Switch Test

Figure 4.16: Power Density Graphs for Figure 4.17: CPU % Power Graphs forthe 16-bit Switch Testthe 16-bit Switch Test

|                                                            | To   | otal Po | wer  | CPU Power |      | wer  |

|------------------------------------------------------------|------|---------|------|-----------|------|------|

|                                                            | Max  | Min     | Mean | Max       | Min  | Mean |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nm       | 1.85 | 1.63    | 1.7  | 3.36      | 2.82 | 2.98 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd    | 1.88 | 1.7     | 1.75 | 3.45      | 2.89 | 3.06 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd2   | 1.88 | 1.69    | 1.75 | 3.42      | 2.94 | 3.08 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)65\text{nm}$  | 1.75 | 1.53    | 1.58 | 3.11      | 2.51 | 2.64 |

| $\left(\frac{\text{AVR32ltd}}{\text{AVR32}}\right)$ 130nm  | 1.1  | 1.06    | 1.09 | 1.16      | 1.08 | 1.14 |

| $\left(\frac{\text{AVR32ltd2}}{\text{AVR32}}\right)$ 130nm | 1.07 | 1.04    | 1.05 | 1.11      | 1.07 | 1.09 |

| $\left(\frac{\text{AVR3265}}{\text{AVR32130}}\right)$ nm   | 0.4  | 0.36    | 0.38 | 0.38      | 0.32 | 0.35 |

| $\left(\frac{\text{AVRltd}}{\text{AVR}}\right)$ 130nm      | 1.07 | 1.05    | 1.06 | 1.12      | 1.09 | 1.11 |

| $\left(\frac{\text{AVRltd2}}{\text{AVR}}\right)$ 130nm     | 1.03 | 1.01    | 1.02 | 1.08      | 1.02 | 1.05 |

| $\left(\frac{\text{AVR65}}{\text{AVR130}}\right)$ nm       | 0.42 | 0.4     | 0.41 | 0.41      | 0.39 | 0.4  |

Table 4.12:

Power Comparisons 16-bit Switch Test

|                                                            | Total Energy |      |      | CPU Energy |      |      |

|------------------------------------------------------------|--------------|------|------|------------|------|------|

|                                                            | Max          | Min  | Mean | Max        | Min  | Mean |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nm       | 0.86         | 0.75 | 0.78 | 1.56       | 1.3  | 1.38 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd    | 0.87         | 0.78 | 0.81 | 1.59       | 1.34 | 1.42 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)$ 130nmltd2   | 0.87         | 0.78 | 0.81 | 1.58       | 1.36 | 1.42 |

| $\left(\frac{\text{AVR32}}{\text{AVR}}\right)65\text{nm}$  | 0.81         | 0.71 | 0.73 | 1.44       | 1.16 | 1.22 |

| $\left(\frac{\text{AVR32ltd}}{\text{AVR32}}\right)$ 130nm  | 1.1          | 1.06 | 1.09 | 1.16       | 1.08 | 1.14 |

| $\left(\frac{\text{AVR32ltd2}}{\text{AVR32}}\right)$ 130nm | 1.07         | 1.04 | 1.05 | 1.11       | 1.07 | 1.09 |

| $\left(\frac{\text{AVR3265}}{\text{AVR32130}}\right)$ nm   | 0.4          | 0.36 | 0.38 | 0.38       | 0.32 | 0.35 |

| $\left(\frac{\text{AVRltd}}{\text{AVR}}\right)$ 130nm      | 1.07         | 1.05 | 1.06 | 1.12       | 1.09 | 1.11 |

| $\left(\frac{\text{AVRltd2}}{\text{AVR}}\right)$ 130nm     | 1.03         | 1.01 | 1.02 | 1.08       | 1.02 | 1.05 |

| $\left(\frac{\text{AVR65}}{\text{AVR132}}\right)$ nm       | 0.42         | 0.4  | 0.41 | 0.41       | 0.39 | 0.4  |

Table 4.13:

Energy Comparisons 16-bit Switch Test

The case for 16-bit math and 16-bit switch have very similar results. The only thing that strikes out is that the energy consumption for both the system and the CPU is smaller when using an AVR

#### 4.2.4.2 NTV and STV

| (pJ)                 | $65 \mathrm{nm}$ | $130 \mathrm{nm}$ | 130  ltd2 | $130 \ \mathrm{ltd}$ |

|----------------------|------------------|-------------------|-----------|----------------------|

| AVR                  |                  |                   |           |                      |

| Super $TV$           | 973.08           | 2372.28           | 2423.16   | 2505.84              |

| NTV                  |                  |                   | 227.777   | 235.549              |

| $\operatorname{STV}$ |                  |                   |           | 180.42               |

| AVR32                |                  |                   |           |                      |

| Super $TV$           | 687.96           | 1785.56           | 1906.1    | 1965.88              |

| NTV                  |                  |                   | 179.173   | 184.793              |

| $\operatorname{STV}$ |                  |                   |           | 141.543              |

Table 4.14: 16-bit Switch Energy Estimation for NTV and STV

#### 4.2.5 32-bit Math Test

#### 4.2.5.1 Super Threshold Voltage

Figure 4.18: Power Graphs for the 32-bit Math Test

Figure 4.19: Energy Graphs for the 32-bit Math Test