# Programmable Microcontroller Peripherals

#### **Anders Ruden**

Master of Science in Electronics Submission date: June 2013

Supervisor: Bjørn B. Larsen, IET

Co-supervisor: Tor Erik Leistad, Atmel Norway AS

Norwegian University of Science and Technology Department of Electronics and Telecommunications

### **Problem Statement**

Microcontroller hardware peripherals implement fixed, specific functions or protocols which cannot be changed once silicon is made. A typical microcontroller will have several peripherals multiplexed on the same pins, leaving some of the microcontroller hardware unused in the end application.

A study is proposed to investigate if peripherals can be substituted by embedded programmable CPUs, which emulate features normally supported by a hardware module, such as SPI, UART, TWI, or USB. The study should propose a specific solution and implement this in HDL. One or more of the protocols should be implemented to demonstrate the selected solution. The resulting area, power consumption, and performance should be compared to a traditional hardware solution.

### Acknowledgements

I would like to acknowledge the people that have helped me to complete this master thesis.

First, I would like to thank my supervisor at Atmel, Tor Erik Leistad. He have been extremely helpful by explaining all my questions in the smallest detail, in a manner that is easily understandable. He have also given me good feedback on my work and guided me when i have been stuck. Without him it would have been impossible for me to finish this thesis.

In addition, I would like to thank my supervisor at NTNU, Professor Bjørn B Larsen for the help and feedback he have given me throughout this school year on both the preliminary work and the master thesis.

Last, I will thank my family and friends who have been supporting me throughout the years of my master's studies.

### Abstract

This thesis is a continuation of work done in a specialization project. The result from the preliminary work have been used to implement a programmable peripheral processor in HDL that can replace non-programmable hardware modules. The implemented solution have then been tested to find out if it is capable of doing the most basic operations that a UART protocol require to do parallel-to-serial and serial-to-parallel conversions. The results of the implementation and testing have been analysed and the performance, area and power consumption have been presented. The resulting performance and area have also been compared to traditional hardware solutions.

The results from the tests demonstrates that the presented peripheral processor is capable of doing the basic operations that is required to do parallel-to-serial and serial-to-parallel conversions. However, the area of the peripheral processor is significantly larger than the total area of multiple non-programmable hardware modules. The result of this is that the cost of utilizing a peripheral processor will be greater than with existing solutions.

### Sammendrag

Denne oppgaven er en fortsettelse på arbeidet gjort i et fordypningsprosjekt. Resultatet fra forarbeidet har blitt brukt til å implementere en proggrammerbar perifer prosessor i HDL som kan erstatte ikke-programmerbar maskinvare. Den implementerte løsningen har blitt testet for å finne ut om den er i stand til å gjøre de mest elementære operasjonene som behøves for å gjøre seriell-til-parallell og parallell-til-seriell datakonvertering på samme måte som en UART protokoll. Resultatet av implementasjonen og testingen har deretter blitt analysert og ytelsen, størrelsen og strømforbruket til prosessoren har blitt presentert. Ytelsen og strømforbruket har også blitt sammenlignet med tradisjonelle ikke-programmerbare løsninger.

Resultatene fra testene viser at den gjeldene prosessoren er i stand til å gjøre de mest elementære operasjonene som kreves for seriell-til-parallell of parallell-til-seriell convertering. Imidlertid, viser resultatene også at prosessoren er betydelig større enn størrelsen til flere ikke-programmerbare maskinvare moduler sammenlagt. Dette fører til at også kostnaden til den perifere prosessoren vil bli betydelig større en eksisterende løsninger.

### Contents

| P            | roble | m Statement                | i    |

|--------------|-------|----------------------------|------|

| $\mathbf{A}$ | ckno  | wledgements                | ii   |

| $\mathbf{A}$ | bstra | act                        | iii  |

| Sa           | amme  | endrag                     | iv   |

| Li           | st of | Figures                    | ix   |

| Li           | st of | Tables                     | xi   |

| $\mathbf{A}$ | bbre  | viations                   | xiii |

| 1            | Intr  | roduction                  | 1    |

|              | 1.1   | Motivation                 | 1    |

|              | 1.2   | Approach                   | 2    |

|              | 1.3   | Outline                    | 2    |

| <b>2</b>     | The   | eory                       | 5    |

|              | 2.1   | Hardware Versus Processor  | 5    |

|              | 2.2   | Processor Architecture     | 6    |

|              | 2.3   | First Peripheral Processor | 8    |

|              | 2.4   | USART                      | 9    |

|              |       | Clock Generation           | 9    |

|              |       | Registers                  | 11   |

|              |       | Frame Format               | 14   |

|              |       | Transmitter                | 14   |

|              |       | Receiver                   | 15   |

|              | 2.5   | AMBA Bus                   | 17   |

|              |       | AMBA APB                   | 18   |

| 3            | Sun   | nmary of Preliminary Work  | 21   |

|              | 3.1   | Emulation                  | 21   |

|              | 3.2   | Instruction Set            | 22   |

|              | 3.3   | Architecture               | 24   |

|              | 2 4   | Donformanno                | വര   |

*Contents* vi

|   | 3.5            | Cost Analysis                               |

|---|----------------|---------------------------------------------|

| 4 | Pro            | cedure 2                                    |

|   | 4.1            | Verilog Implementation                      |

|   | 4.2            | Test Programs                               |

|   | 4.3            | Synthesis                                   |

| _ | D              | lu                                          |

| 5 | <b>Res</b> 5.1 | ults         3           CPU Core         3 |

|   | 5.1            | Register File                               |

|   |                | ALU                                         |

|   |                | Instruction Decoder                         |

|   |                |                                             |

|   |                | Branch Control and Program Counter          |

|   | <b>F</b> 0     | Program Memory                              |

|   | 5.2            | External Modules                            |

|   |                | Internal Data Bus                           |

|   |                | APB Bus                                     |

|   |                | Data Stack                                  |

|   |                | Control and Status Registers                |

|   |                | Data In/Out Registers                       |

|   |                | IRQ Line                                    |

|   |                | Timer/Counter                               |

|   |                | Input/Output Port                           |

|   | 5.3            | Instructions Implemented                    |

|   | 5.4            | Simulation                                  |

|   | 5.5            | Synthesis Reports                           |

|   | 5.6            | Net List Reports                            |

| 6 | Dia            | cussion 5                                   |

| U |                | Instruction Set                             |

|   | -              |                                             |

|   | 6.2            |                                             |

|   |                | Pipelining                                  |

|   |                | Negative Numbers                            |

|   |                | Shared Program Memory and Data Stack        |

|   |                | PUSH and POP Instructions                   |

|   |                | JUMP Instruction                            |

|   | 6.3            | Exteral Modules                             |

|   |                | Internal Data Bus                           |

|   |                | Data Stack                                  |

|   |                | Control and Status Registers                |

|   |                | Data In/Out Registers                       |

|   |                | Timer/Counter                               |

|   |                | IRQ Line                                    |

|   |                | Input/Output Port                           |

|   | 6.4            | Simulation                                  |

|            | ••   |

|------------|------|

| Contents   | V1:  |

| 0016601663 | V 1. |

|            |      |

|              | 6.5   | Test of Instructions           | 60<br>60<br>62<br>63<br>63 |

|--------------|-------|--------------------------------|----------------------------|

|              |       | Speed of Operations            | 65<br>66<br>67             |

|              |       | Design For Test Coverage       | 68                         |

| 7            | Con   | clusions                       | 69                         |

| A            | Sim   | ulation results                | 71                         |

| 11           | A 1   | Simulation of instructions     | 71                         |

|              | A.2   | UART simulation                | 75                         |

| В            | Sim   | ulation programs               | 79                         |

|              | B.1   | Test of instructions           | 79                         |

|              | B.2   | UART program                   | 80                         |

| $\mathbf{C}$ | Veri  | ilog Code                      | 85                         |

|              | C.1   | Register File                  | 85                         |

|              | C.2   | ALU                            | 86                         |

|              | C.3   | Instruction Decoder            | 88                         |

|              | C.4   | Branch control                 | 96                         |

|              | C.5   | Program Memory                 | 98                         |

|              | C.6   | Internal Data Bus              | 99                         |

|              | C.7   | Data Stack                     | 102                        |

|              | C.8   | Control and Status Registers   | 104                        |

|              | C.9   | Data In/Out Registers          | 105                        |

|              |       | IRQ Line                       | 106                        |

|              |       | Timer/Counter                  | 107<br>109                 |

|              |       | Input/Output Port              | 109                        |

|              |       | Topmodule Peripheral Processor | 111                        |

|              |       | Parameters                     | 116                        |

|              |       |                                |                            |

| Bi           | bliog | graphy                         | 117                        |

## List of Figures

| 2.1 | A Simple Processor                                        |

|-----|-----------------------------------------------------------|

| 2.2 | Peripheral Processors in the CDC 6600 supercomputer [1] 8 |

| 2.3 | Block diagram of a USART module                           |

| 2.4 | Frame Formats [2]                                         |

| 2.5 | Start Bit Sampling [2]                                    |

| 2.6 | Data and Parity Bit Sampling [2]                          |

| 2.7 | Stop Bit Sampling and Next Bit Sampling [2]               |

| 2.8 | A typical AMBA system [3]                                 |

| 2.9 | Write and read transfer for APB bus [3]                   |

| 3.1 | PPU Block Diagram [4]                                     |

| 3.2 | Excerpt from the UART C-code                              |

| 5.1 | PPU Core Block Diagram                                    |

| 5.2 | PPU Block Diagram                                         |

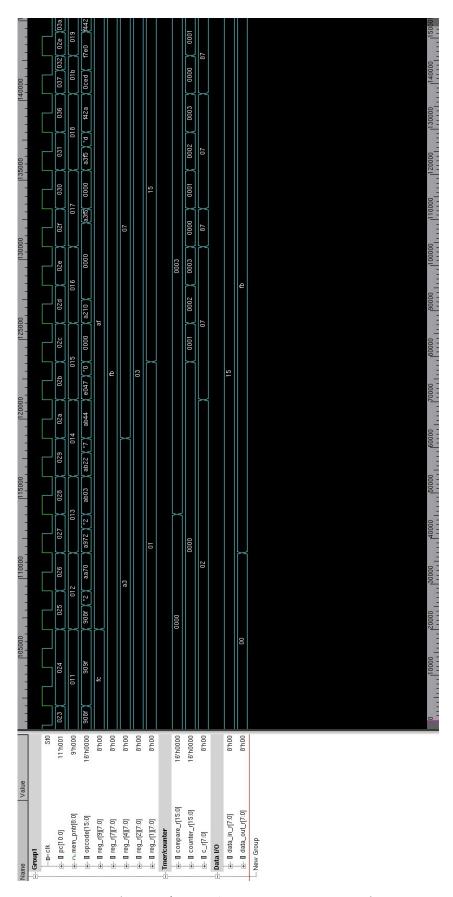

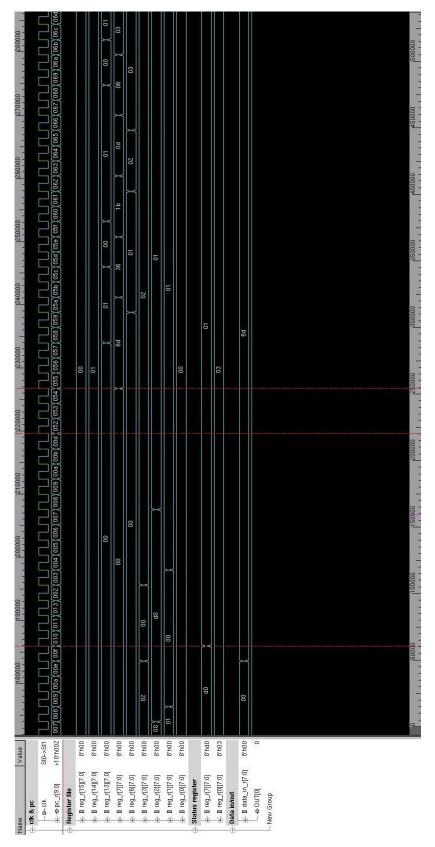

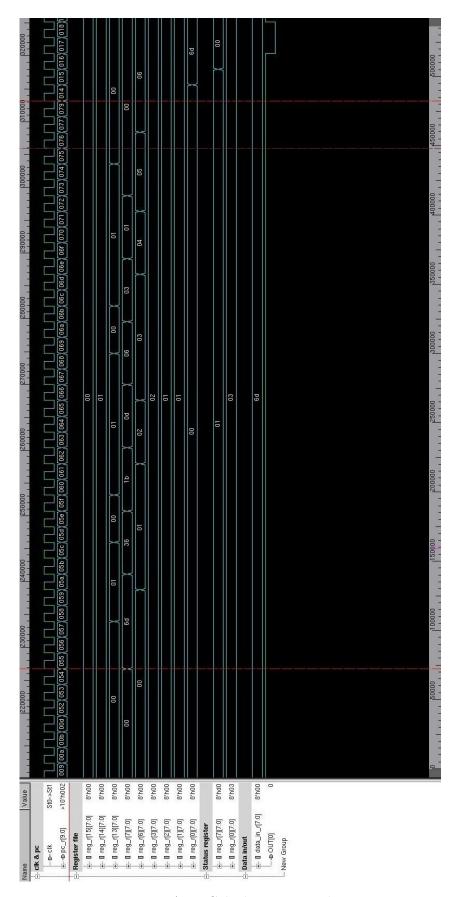

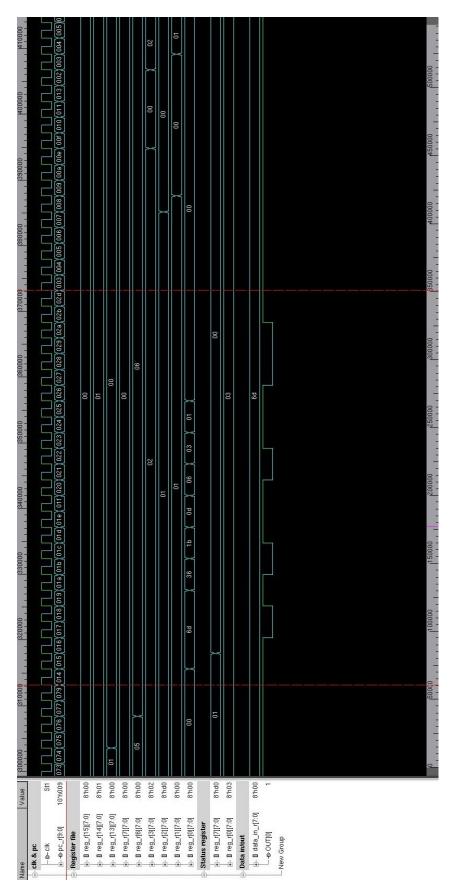

| A.1 | Branch and jump waveform                                  |

| A.2 | Register operations waveform                              |

| A.3 | Stack operations waveform                                 |

| A.4 | In/out and timer operations waveform                      |

| A.5 | Checking for status bit                                   |

| A.6 | Calculating parity bit                                    |

| A.7 | Shifting data out                                         |

| A.8 | Shifting data in                                          |

### List of Tables

| 2.1  | Line Control Register                                     |

|------|-----------------------------------------------------------|

| 2.2  | Line Status Register                                      |

| 2.3  | Interrupt Register                                        |

| 2.4  | Divisor Register                                          |

| 2.5  | AMBA APB signals                                          |

| 3.1  | 16 bit opcode                                             |

| 3.2  | 8 bit opcode                                              |

| 3.3  | Sum of logic                                              |

| 5.1  | Signal description                                        |

| 5.2  | Signal description                                        |

| 5.3  | Signal description                                        |

| 5.4  | Signal description                                        |

| 5.5  | Signal description                                        |

| 5.6  | Description of registers in the timer                     |

| 5.7  | Description of Control Register                           |

| 5.8  | Gives the address used for different modes and outputs 45 |

| 5.9  | Signal description                                        |

| 5.10 | Included instructions                                     |

| 5.11 | Area report                                               |

| 5.12 | Setup timing report                                       |

| 5.13 | Clock Gating report                                       |

| 5.14 | Design For Test Coverage                                  |

| 5.15 | Setup Timing report                                       |

| 5.16 | Hold Timing report                                        |

| 5.17 | Time Based Power                                          |

### Abbreviations

**AHB** Advanced High-performance Bus

ALU Arithmetic Logic Unit

AMBA Advanced Microcontroller Bus Architecture

APB Advanced Peripheral Bus ASB Advanced System Bus

ATPG Automatic Test Pattern Generator

CPU Central Processing UnitDMA Direct Memory AccessFIFO First In First Out

**HDL** Hardware Description Language

IRQ Interrupt ReQuest

LCR Line Control Register

LIFO Last In First Out

LSB Least Significant Bit

LSR Line Status Register

MSB Most Significant Bit

NAND2 Not AND gate with 2 inputs

PPU Peripheral Processing Unit

RTL Register Transfer Level

SPI Serial Peripheral Interface

SRAM Static Random Access Memory

**TWI** Two Wire Interface

**UART** Universal Asynchronous Receiver and Transmitter

**USART** Universal Synchronous and Asynchronous Receiver and Transmitter

**USB** Universal Serial Bus

### Chapter 1

### Introduction

This thesis is a continuation of the preliminary work done in a specialization project the autumn 2012. Some parts of this thesis will therefore include the same content as given in the report for the preliminary work. It will be informed when the content is from the preliminary work. The motivation is the same for this thesis and the preliminary work [4].

#### 1.1 Motivation

Data is often needed to be transferred between a microcontroller and other devices. A common way to do this is by using a data transfer protocol that do a parallel to serial conversion and then sends the data serially between the external device and the microcontroller. There are several different protocols that support this type of parallel to serial conversion. USART, SPI, TWI and USB are four common protocols. Each protocol have separate advantages and limitations and is therefore not suitable in the same situations.

A microcontroller have to support several different transfer protocols. Today this is done on Atmel microcontrollers by having different hardware modules to control the various data transfer protocols [2]. The disadvantage of this is that the microcontroller is locked to only support the predefined data transfer protocols because these modules

are not programmable. If a user want to do data transfer with a protocol that is not supported, the user have to program the CPU to control the data transfer. This is complicated and uses a lot of CPU resources which could have been used for other tasks, and is therefore not desirable. An alternative solution can therefore be to implement a programmable peripheral processor to control the data transfer instead of non-programmable hardware.

### 1.2 Approach

Based on the problem description and the result of the preliminary work, the following bullet points summarizes the work that is done in this thesis:

- A peripheral processor is implemented in HDL. The results from the preliminary work are used as a specification to implement a peripheral processor in HDL.

- Simulations are run on the Implemented Solution. A test program that can simulate the behaviour of a peripheral protocol is created.

- The Implemented Solution is analysed. The results are analysed to present the performance, area and power consumption of the peripheral processor.

- The implemented Solution is compared to Existing Modules. The performance, area and power consumption of the implemented solution are compared to existing hardware modules.

#### 1.3 Outline

The report presents first the theory required to understand the content of the thesis. Next a summary of the preliminary work is presented in chapter 3. The summary includes the most important results needed to give a specification of the peripheral processor. Furthermore, chapter 4 gives a detailed description of the different steps in

the work towards the presented solution. The results of the implemented peripheral processor is presented in chapter 5. Chapter 6 describes the functionality and explains the reasons for the choices made. Last, the conclusions is given in chapter 7.

### Chapter 2

### Theory

The theory in chapter 2.1, 2.2, 2.3 and 2.4 is the same as in the preliminary work. Chapter 2.5 summarizes the AMBA APB bus specification.

#### 2.1 Hardware Versus Processor

There are two different methods to do data processing. One is by using a processor and the other is by using non programmable hardware modules. Non programmable hardware modules consists of logic gates such as AND, OR, XOR and NOT gates. These logic gates are set up in order to do one specific task or several tasks simultaneously. The advantage of a non programmable hardware module is that it is significantly faster than a processor and can do several tasks simultaneously. It is also considerable cheaper to produce non programmable hardware modules if the task to be solved are simple. However, when a non programmable hardware module is produced, it can not be changed. If it is a requirement for another or a different function, a new module have to be produced. This is where a processor have it biggest advantage.

A processor has the same building blocks as non programmable hardware, that is logic gates. The difference is that the processor can perform different tasks decided by the program on the processor. The advantage of this is that a processor can do lot of

different tasks on the same circuit by loading a different program to it. Nevertheless, a processor is huge and costs a lot compared to simple hardware modules. In addition, the processor can only do one task at a time and will often need long time to complete a task.

Because of the drawbacks of a processor, many microcontroller producers have concluded that using non programmable hardware is the best solution for serial communication with external devices. This Includes, among others, Atmel [2], Texas Instruments [5] and Energy Micro [6].

#### 2.2 Processor Architecture

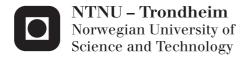

There are many different types of processors, but they all have some mutual components that are essential for the processor to be able to operate. Figure 2.1 gives an example of a simple processor.

The Arithmetic Logic Unit (ALU) is the component that does calculations and operations on the data. The two inputs A and B are the data inputs and FS is the function select input. The FS input selects what function to be done with the data on input A and B. This function can for example be to add data A with data B. The result is given on the output F. The V, C, N and Z signals are status bits that give information about the data on the output F.

V: Overfow Indicator

C: Carry Flag

N: Negative Flag

Z: Zero Flag

The register file is the temporary memory where the data currently being processed is stored. AA and BA gives the data address of the data to be placed on the data bus A and B. DA gives the address of where in the register to write the data from the ALU. WE is the write enable signal and is set high only if the data on the D Data bus is to be stored. The A Data, B Data and D Data bus all have the same width that is given by the width of the registers.

Figure 2.1: A Simple Processor

The instruction register receives an instruction by the program memory. This instruction is then decoded by the instruction decoder and then the instruction decoder sets all the pins to the value corresponding to the instruction to be executed. For example, an instruction could be to add register 1 with register 2 and store the added value in register 3. This would result in the following events:

- 1: The instruction register will be loaded with the instruction.

- 2: The instruction decoder will decode the signal in the instruction register and set its outputs.

- 3: The outputs are: DA=3, BA=2, AA=1, WE=1, MS=0, FS=ADD PL=0, JB=0, and BC=0.

- 4: The instruction will be executed.

The program memory is where the program to be executed is stored. The program is as a list with all the instructions stored in the order they are to be executed in. The program counter is a pointer that points to the instruction that is to be executed. For each instruction executed, the program counter is incremented with one and the

next instruction will be executed.

The branch control is controlling the program counter. If PL is set to 1, a branch or jump is called. JB determines if it is a branch or jump. If JB is set to 0, the program counter is loaded with the data on the A Data bus. If JB is set to 1, a conditional branch is called. BC will then select the branch condition from the status bits.

### 2.3 First Peripheral Processor

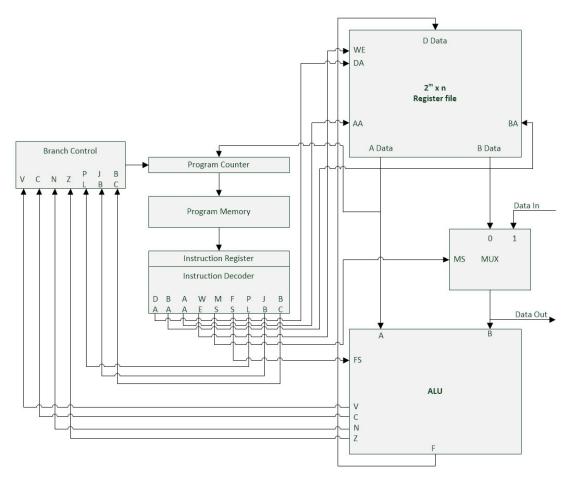

The first computer that used a peripheral processor to control Input/Output signals was the CDC 6600 [7] [1]. The CDC 6600 was a supercomputer developed by Seymour Cray for the firm Control Data Corporation in 1967. This supercomputer had one CPU and ten identical peripheral processors. The Peripheral processors was much smaller than the CPU. Each peripheral processor had a register that could store 4096 12-bit words and a repertoire of 62 instructions. Each peripheral processor also had access to the central storage and access to all the 12 peripheral channels. Figure 2.2 gives an illustration of how the Peripheral Processors are included in the CDC 6600 computer.

FIGURE 2.2: Peripheral Processors in the CDC 6600 supercomputer [1]

Having ten independently constructed processors would use a lot of area and cost a lot. Therefore did each peripheral processor actually share one ALU. This could be done because of the time needed to read and write to the registers. For example each peripheral processor would use 1000 nano seconds to add the value register in register A to the value in register B and store it in register C. But the ALU would actually

only use 100 nano seconds to perform the add operation. For that reason, one ALU could be shared between 10 processors to maximize its efficiency. Each peripheral processor was given a time slot where it had access to the ALU.

#### 2.4 USART

The functionality of the USART is extracted from [2] and [8]. Universal Synchronous and Asynchronous Receiver and Transmitter (USART) is a popular method for transmitting serial data. Its main features, among others, is that it can switch between synchronous and asynchronous communication and it can have different length on the data frames. Synchronous operation uses a clock and data line while there is no separate clock accompanying the data for asynchronous transmission. Both transmission and reception can occur at the same time. This is known as full duplex operation.

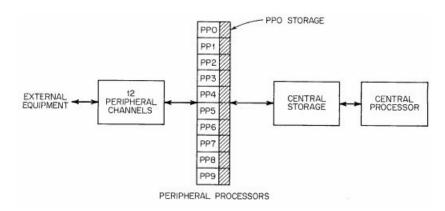

The USART consists of three main modules that is a transmitter, a receiver and a baud generator. Additional the USART also have registers for storing status flags and data. A overview of a USART is given in figure 2.3

#### **Clock Generation**

The USART can operate on several different clock frequencies and baud rates. The clock frequency decides the baud rate of the USART. When the USART operates as a master, the user have to set the baud rate of the USART before it can be activated. This is done by writing a value to the Divisor Register. The Baud Generator will then use this value to calculate the baud rate. The baud rate is a function of both the value in the Divisor Register and the CPU clock speed. Equation 2.1 gives the formula for calculating the Divisor value if the preferred baud rate is known. The baud rate can commonly range from 2400 bit/s to 1 Mbit/s depending on the clock frequency the master is operating on.

$$DivisorValue = \frac{Clk_{CPU}}{16*(BaudRate)} - 1$$

(2.1)

FIGURE 2.3: Block diagram of a USART module

### Registers

There are several registers in the USART for storing the different control signals and status signals. The different registers are listed in table 2.1, to table 2.4.

| LCR        |                                                          |  |  |  |  |  |

|------------|----------------------------------------------------------|--|--|--|--|--|

| Bit number | Function                                                 |  |  |  |  |  |

| 7          | Transmit Data Bit 8                                      |  |  |  |  |  |

|            | When bit 5 in LCR is set this bit is the 9th data bit of |  |  |  |  |  |

|            | the transmitted character.                               |  |  |  |  |  |

| 6          | Receive Data Bit 8                                       |  |  |  |  |  |

|            | When bit 5 in LCR is set this bit is the 9th data bit of |  |  |  |  |  |

|            | the received character.                                  |  |  |  |  |  |

| 5          | 9 Bit Characters                                         |  |  |  |  |  |

|            | 0 = 5 to 8 bits character length.                        |  |  |  |  |  |

|            | 1 = 9 bits character length.                             |  |  |  |  |  |

| 4          | Even Parity                                              |  |  |  |  |  |

|            | 0 = enable odd parity                                    |  |  |  |  |  |

|            | 1 = enable even parity                                   |  |  |  |  |  |

| 3          | Parity enable                                            |  |  |  |  |  |

|            | 0 = send no parity bit after data bits                   |  |  |  |  |  |

|            | 1 = generate or check a parity bit after data bits.      |  |  |  |  |  |

| 2          | Stop bits                                                |  |  |  |  |  |

|            | 0 = transmit  1  stop bit after data bits are sent       |  |  |  |  |  |

|            | 1 = transfer  2  stop bits.                              |  |  |  |  |  |

| [1:0]      | Character length                                         |  |  |  |  |  |

|            | 00 = transmit  5  bits of data per frame                 |  |  |  |  |  |

|            | 01 = transmit 6 bits of data per frame                   |  |  |  |  |  |

|            | 10 = transmit 7 bits of data per frame                   |  |  |  |  |  |

|            | 11 = transmit 8 bits of data per frame                   |  |  |  |  |  |

Table 2.1: Line Control Register

| LSR        |                                                               |  |  |  |  |  |

|------------|---------------------------------------------------------------|--|--|--|--|--|

| Bit number | Function                                                      |  |  |  |  |  |

| 7          | Error flag                                                    |  |  |  |  |  |

|            | 0 = The receive FIFO has no errors.                           |  |  |  |  |  |

|            | 1 = the receive FIFO has parity, farming, or break con-       |  |  |  |  |  |

|            | dition errors.                                                |  |  |  |  |  |

| 6          | Transmitter empty flag                                        |  |  |  |  |  |

|            | 0 = transmitter is shifting data out to the serial line.      |  |  |  |  |  |

|            | 1= the transmit FIFO and transmit shift register are          |  |  |  |  |  |

|            | both empty.                                                   |  |  |  |  |  |

| 5          | Transmit FIFO empty flag                                      |  |  |  |  |  |

|            | 0 = the transmit FIFO has at least 1 peace of data            |  |  |  |  |  |

|            | remaining.                                                    |  |  |  |  |  |

|            | 1 = the transmit FIFO is empty                                |  |  |  |  |  |

| 4          | Break indication                                              |  |  |  |  |  |

|            | This is set to 1 if the receiver detects a string of 0 for    |  |  |  |  |  |

|            | longer than a full word transmission time. Under this         |  |  |  |  |  |

|            | condition the FIFO is loaded with a 0x00 character and        |  |  |  |  |  |

|            | the receiver remains idle until it detects a valid start bit. |  |  |  |  |  |

| 3          | Farming error                                                 |  |  |  |  |  |

|            | This is set to 1 when the receiver detects an invalid stop    |  |  |  |  |  |

|            | bit.                                                          |  |  |  |  |  |

| 2          | Parity error                                                  |  |  |  |  |  |

|            | This is set to one when the receives character has an         |  |  |  |  |  |

|            | incorrect parity bit.                                         |  |  |  |  |  |

| 1          | Overrun error                                                 |  |  |  |  |  |

|            | This is set to 1 when the receiver FIFO is full and a         |  |  |  |  |  |

|            | completed character in the receive shift register is de-      |  |  |  |  |  |

|            | stroyed.                                                      |  |  |  |  |  |

| 0          | Receiver data ready                                           |  |  |  |  |  |

|            | 0 = the receive FIFO is empty                                 |  |  |  |  |  |

|            | 1 = data is ready to be read from the receive FIFO.           |  |  |  |  |  |

TABLE 2.2: Line Status Register

| Interrupt Register |                                                         |  |  |  |  |  |

|--------------------|---------------------------------------------------------|--|--|--|--|--|

| Bit number         | Function                                                |  |  |  |  |  |

| 7                  | USART Mode Select                                       |  |  |  |  |  |

|                    | 0 = Asynchronous operation                              |  |  |  |  |  |

|                    | 1 = Synchronous operation                               |  |  |  |  |  |

| 6                  | Enable Receiver Line status Interrupt                   |  |  |  |  |  |

|                    | Set this bit to 1 to enable this interrupt.             |  |  |  |  |  |

| 5                  | Enable Transmit FIFO Empty Interrupt                    |  |  |  |  |  |

|                    | Set this bit to 1 to enable this interrupt.             |  |  |  |  |  |

| 4                  | Enable Receive Data Available Interrupt and             |  |  |  |  |  |

|                    | Timeout Interrupt                                       |  |  |  |  |  |

|                    | Set this bit to 1 to enable this interrupt.             |  |  |  |  |  |

| [3:1]              | Interrupt ID                                            |  |  |  |  |  |

|                    | These bits are used to identify the highest priority of |  |  |  |  |  |

|                    | the interrupts                                          |  |  |  |  |  |

| 1                  | Interrupt pending                                       |  |  |  |  |  |

|                    | 0 = an interrupt is pending                             |  |  |  |  |  |

|                    | 1 = there are no interrupts                             |  |  |  |  |  |

Table 2.3: Interrupt Register

| Divisor Register |           |  |  |  |

|------------------|-----------|--|--|--|

| Bit number       | Function  |  |  |  |

| [15:0]           | Baud Rate |  |  |  |

Table 2.4: Divisor Register

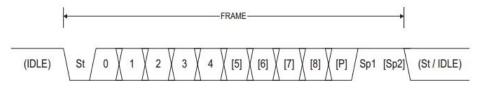

#### Frame Format

When there is no data to be sent, the serial line is high. The first bit of a frame is the start bit. This bit is always low and one clock cycle long. The next bits are the data bits and these bits can vary from 5 to 9 bits. The least significant bit is sent first and the most significant bit is sent last. The bit following after the data bits is a parity bit only if parity is enabled in the Line Status Register. Last there is a stop bit and can be defined as one or two clock cycles long. The stop bit is always high. The stop bit can immediately be followed by a new start bit if there is more data to be transferred. If there is no more data to be transferred the line will stay high.

FIGURE 2.4: Frame Formats [2]

- St Start bit, always low.

- (n) Data bits (0 to 8).

- P Parity bit, always high.

- Sp Stop bit, always high.

- IDLE The line is high when there is no transfer.

#### Transmitter

For transmitting signals with the USART the processor first have to set the flags in the LCR and IR registers so that the USART operates whit the correct mode. The baud rate also have to be set before a transmission can be started. When the baud rate and the control flags has been set, the processor can transmit data by writing to the transmitter address as it was a memory space.

When the USART receives data it places the data into a FIFO buffer. The transmitter pops data from the FIFO to a shift register and the shift register performs a parallel to serial conversion by shifting data out on the serial line for transmission.

The transmitter also generates the start bit, parity bit, and stop bit. When the transmission is complete, the transmitter sets the Transmitter Empty flag to 1 to indicate that the transmission is complete.

#### Receiver

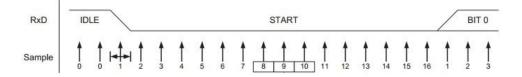

The receiver is more complex than the transmitter. The receiver constantly monitors the receive serial line. When the receiver notices that the line goes low, it starts a sampling process to verify that it is a valid start bit. This sampling is done with a frequency that is 16 times faster than the baud rate. When the start bit goes from high to low the receiver will do 3 samples of the start bit. These samples will be done on sample 8, 9 and 10. the receiver will then compare the 3 samples and if two or more of the samples are logical low, the start bit is considered as a valid start bit. If only one of the samples are logical low, the start bit is considered as a noise spike and the receiver starts looking for a the next high to low transition. An illustration of the sampling process is given in figure 2.5.

FIGURE 2.5: Start Bit Sampling [2]

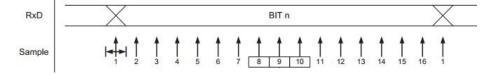

If the start bit is considered as a valid start bit, the data recovery can begin. For each data bit received, the same sampling that was done with the start bit is done with all the bits received. The sampling of data bit and parity bit is the same and is illustrated in figure 2.6

FIGURE 2.6: Data and Parity Bit Sampling [2]

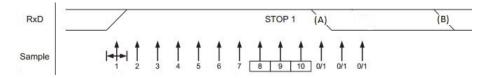

The same sampling is done for the stop bit. But there is a difference after the last sample. After the 10th sample is done, the receiver is immediately ready for a new

high to low transition that indicating a new start bit. Figure 2.7 illustrates the sampling of the stop bit and the earliest possible beginning of a new start bit. The first point where a new start bit can occur is on the point marked (A), and (B) marks a stop bit of full length.

FIGURE 2.7: Stop Bit Sampling and Next Bit Sampling [2]

The reason for the variable length for the stop bit is because of the possibility for asynchronous transmission. The transmitter and receiver does not necessary operate at the exact same clock frequency. If the transmitter is sending frames at too fast bit rate, the variable stop bit length will minimize the difference. If the transmitter is sending frames too fast or too slow compared to the internally generated baud rate, the receiver will not be able to synchronize the frames. This will only be noticed if the receiver expects a stop bit, but the received bit is logical low. When that happens the Farming Error flag will be set in the Line Status Register. If the USART is using synchronized transmission, the transmitter will send a clock to the receiver. The data reception will have the same protocol for sampling data, but there will not be any mismatch between the transmitter and receiver baud rate.

After one frame is shifted in to the receive Shift Register, the received frame is pushed in to the receive FIFO and the Receiver Data Ready flag is set to one. This tells the processor that at least one data frame is ready to be read. The receiving operation can continue and new frames can be pushed into the FIFO. If the FIFO gets full and a frame is written over a frame that yet is to be read by the processor, the Overrun Error flag is set. If the parity bit does not match the received data the Parity Error flag will be set.

#### 2.5 AMBA Bus

The Advanced Microcontroller Bus Architecture (AMBA) is a standard designed for on-chip communication on high performance embedded microcontrollers [3]. The AMBA specification is divided into three different buses:

- Advanced High-performance Bus (AHB)

- Advanced System Bus (ASB)

- Advanced Peripheral Bus (APB)

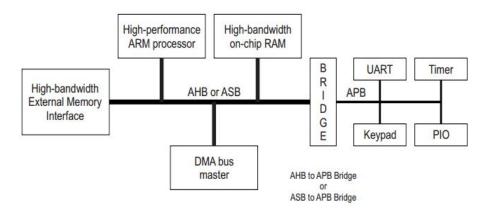

The AMBA AHB and ASB are in general used for the main bus system in a micro-controller. The AHB is for high-performance, high clock frequency system modules and is the most advanced bus of the three different AMBA buses. The ASB is an alternative for the AHB where the high performance of the AHB is not required. The AMBA APB is for peripheral modules and is optimized for minimal power consumption. Figure 2.8 gives an overview of how a typical AMBA system is connected.

FIGURE 2.8: A typical AMBA system [3]

#### AMBA APB

The AMBA APB is a bus optimized to be used with peripheral modules and is the most relevant AMBA bus for this thesis. The APB is connected to the main bus via a bridge that handles the communication between the main bus and the APB. All the signals on the APB is controlled by a master connected to the main bus and all the peripheral modules are connected as slaves to the APB. A big advantage with the APB is that it is static when not in use and will therefore use minimal power in this situation.

The signals used in the APB bus is named with the single letter P prefix. Table 2.5 shows the list of signals in the bus and a description.

| Name    | Description                                           |  |  |  |  |

|---------|-------------------------------------------------------|--|--|--|--|

| PCLK    | Bus clock                                             |  |  |  |  |

| PRESETn | Reset signal for bus, active low.                     |  |  |  |  |

| PADDR   | Address bus, 32 bit wide                              |  |  |  |  |

| PSELx   | A signal to each bus slave to indicate that the slave |  |  |  |  |

|         | is selected. There is a different PSELx signal for    |  |  |  |  |

|         | each bus slave.                                       |  |  |  |  |

| PENABLE | Used to indicate the second cycle of a data trans-    |  |  |  |  |

|         | fer.                                                  |  |  |  |  |

| PWRITE  | When set high, the signal indicates a write access,   |  |  |  |  |

|         | when low a read access.                               |  |  |  |  |

| PRDATA  | Read data. Driven by the selected slave, 32 bit       |  |  |  |  |

|         | wide.                                                 |  |  |  |  |

| PWDATA  | Write data, 32 bit wide.                              |  |  |  |  |

Table 2.5: AMBA APB signals

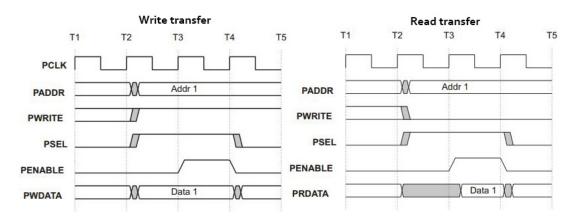

The operation of the APB can be represented with three states: IDLE, SETUP and ENABLE. The idle state is the default state of the bus. When a transfer is required the bus moves to the SETUP state, stays in this state for one clock cycle and then moves to the ENABLE state. The ENABLE state lasts for one clock cycle and if a new transfer is required, the bus will move directly to the SETUP state after the ENABLE state. If no new transfer is required, the bus will move back to the IDLE state. Figure 2.9 shows both a write transfer and a read transfer. The first clock cycle, T1->T2, shows the IDLE state of the bus, T2->T3 shows the SETUP state and T3->T4 shows the transfer state.

FIGURE 2.9: Write and read transfer for APB bus [3]

The write transfer starts with the SETUP state. In this state PADDR, PWRITE, PSEL and PWDATA will be set. The next clock cycle the ENABLE state will be asserted. The signals set in the SETUP state will remain the same and the PENABLE signal will now be set high.

The timing of PADDR, PWRITE, PSEL and PENABLE is the same for the read transfer, but PRDATA will not be set until the ENABLE state is reached.

# Chapter 3

# Summary of Preliminary Work

Some of the content in this chapter is the same as in the preliminary work.

### 3.1 Emulation

The preliminary work was a joint effort between the author and Joacim Dybedal. This was the specialization project and was done the autumn 2012. The main goal of the work was to find a possible solution for how a peripheral processor could be implemented and compare this solution to existing hardware modules. This was done by first emulating an SPI and UART module by writing software with the programming language C, and then run this software on an Atmel AVR. The software was then used to extract the instruction set used by the AVR to explore what operations an implementation of a peripheral processor should be able to perform. The instruction set extracted was then used to create a new and optimized instruction set for a peripheral processor. Also, a solution of how the peripheral processor could be implemented was suggested. This solution was then compared with existing hardware modules with respect to area, performance and power consumption.

When running the software to emulate a UART module on the AVR, a significant issue with having a processor controlling the data transfer was found. The AVR was running with a clock frequency of 11.05925 MHz. This resulted that the maximum

baud rate of the UART could be 2400 bits/s. A non-programmable hardware module can support a baud rate up to 250 KHz with the same clock frequency. In addition to the problem with the baud rate, it was also a problem that full duplex mode not was possible. The problem could be solved by simulating full duplex mode by switching between transmitting and receiving, but this would result in a lower baud rate.

## 3.2 Instruction Set

The instruction set extracted from the UART and SPI software may not include all the instructions needed. This is because the UART program did have less functionality than a fully functional UASRT. Furthermore, the peripheral processor is also supposed to run other serial communication protocols, such as TWI and USB. However, the time limit made it impossible to investigate all the protocols and UART and SPI where therefore prioritized. The UART was the most resource-demanding program and used a total of 26 registers in the AVR. However, the compiler does not care about reusing registers if it is not necessary. An estimation that 16 registers are enough should therefore be valid.

Two suggestions of an optimized opcode was given based on the instruction set extracted from the UART and SPI software. The first suggestion was a reduction of the opcode to 16 to 14 bits. A reduction of the opcode length from 16 to 14 bit will reduce the amount of logic needed to decode the opcode. However, it will not reduce the space needed to store the instructions. This is because the registers have a size of 8 bit and the instructions will therefore be stored in two registers anyway. Therefore, a second suggestion was made. This suggestion was to divide the instruction set into two parts. One part with 8 bit instructions and one part with 16 bit instructions. With this solution, no bits will be wasted when the instructions are stored and the instructions with 8 bits will be transferred to the instruction register faster. Table 3.2 and 3.1 gives the instructions included in the second solution.

| Instruction | Opcode              | Instruction | Opcode              |

|-------------|---------------------|-------------|---------------------|

| MOVW        | 0000 0000 0ddd 0rrr | STS         | 0011 0kkk dddd kkkk |

| CPC         | 0000 0001 dddd rrrr | RJMP        | 0100 kkkk kkkk kkkk |

| SBC         | 0000 0010 dddd rrrr | RCALL       | 0101 kkkk kkkk kkkk |

| ADD         | 0000 0011 dddd rrrr | LDI         | 0110 KKKK dddd KKKK |

| CPSE        | 0000 0100 dddd rrrr | BRCS        | 0111 00kk kkkk k000 |

| СР          | 0000 0101 dddd rrrr | BRLO        | 0111 00kk kkkk k000 |

| SUB         | 0000 0110 dddd rrrr | BREQ        | 0111 00kk kkkk k001 |

| ADC         | 0000 0111 dddd rrrr | BRMI        | 0111 00kk kkkk k010 |

| TST         | 0000 1000 dddd dddd | BRVS        | 0111 00kk kkkk k011 |

| AND         | 0000 1000 dddd rrrr | BRLT        | 0111 00kk kkkk k100 |

| CLR         | 0000 1001 dddd dddd | BRHS        | 0111 00kk kkkk k101 |

| EOR         | 0000 1001 dddd rrrr | BRTS        | 0111 00kk kkkk k110 |

| OR          | 0000 1010 dddd rrrr | BRIE        | 0111 00kk kkkk k111 |

| MOV         | 0000 1011 dddd rrrr | BRBS        | 0111 00kk kkkk ksss |

| IN          | 0000 1100 dddd aaaa | BRCC        | 0111 01kk kkkk k000 |

| OUT         | 0000 1101 rrrr aaaa | BRSH        | 0111 01kk kkkk k000 |

| SBR         | 0001 KKKK dddd KKKK | BRNE        | 0111 01kk kkkk k001 |

| COM         | 0010 0001 dddd 0010 | BRPL        | 0111 01kk kkkk k010 |

| NEG         | 0010 0001 dddd 0011 | BRVC        | 0111 01kk kkkk k011 |

| SWAP        | 0010 0001 dddd 0100 | BRGE        | 0111 01kk kkkk k100 |

| INC         | 0010 0001 dddd 0101 | BRHC        | 0111 01kk kkkk k101 |

| ASR         | 0010 0001 dddd 0110 | BRTC        | 0111 01kk kkkk k110 |

| ROR         | 0010 0001 dddd 0111 | BRID        | 0111 01kk kkkk k111 |

| DEC         | 0010 0001 dddd 1000 | BRBC        | 0111 01kk kkkk ksss |

| JMP         | 0010 0001 kkkk 110k | BLD         | 0111 1000 dddd 0bbb |

|             | kkkk kkkk kkkk      | BST         | 0111 1001 dddd 0bbb |

| CALL        | 0010 0001 kkkk 111k | SBRC        | 0111 1010 rrrr 0bbb |

|             | kkkk kkkk kkkk      | SBRS        | 0111 1011 rrrr 0bbb |

| ADIW        | 0011 1kkk kddd kkkk | SUBI        | 0010 01KK dddd KKKK |

| MUL         | 0010 0010 dddd rrrr | SBCI        | 0010 10KK dddd KKKK |

| SER         | 0010 0001 dddd 1001 | CPI         | 0010 11KK dddd KKKK |

| LDS         | 0011 0kkk dddd kkkk | ORI         | 0111 11KK dddd KKKK |

Table 3.1: 16 bit opcode

| Instruction | Opcode    | Instruction | Opcode    |

|-------------|-----------|-------------|-----------|

| NOP         | 1000 0000 | SEC         | 1001 1sss |

| ICALL       | 1000 0001 | SEH         | 1001 1sss |

| IJMP        | 1000 0010 | SEI         | 1001 1sss |

| RET         | 1000 0011 | SEN         | 1001 1sss |

| RETI        | 1000 0100 | SES         | 1001 1sss |

| SLEEP       | 1000 0101 | SET         | 1001 1sss |

| CLC         | 1001 0sss | SEV         | 1001 1sss |

| CLH         | 1001 0sss | SEZ         | 1001 1sss |

| CLI         | 1001 0sss | POP         | 1010 dddd |

| CLN         | 1001 0sss | PUSH        | 1011 rrrr |

| CLS         | 1001 0sss | LSL         | 1100 dddd |

| CLT         | 1001 0sss | ROL         | 1101 dddd |

| CLV         | 1001 0sss | TST         | 1110 dddd |

| CLZ         | 1001 0sss | LSR         | 1111 dddd |

Table 3.2: 8 bit opcode

### 3.3 Architecture

When studying the possibilities of how the architecture of the peripheral processor could be, one question arisen. This was what parts of the processor that could be shared between the CPU and the peripheral processor. It would be a benefit to the cost of the peripheral processor to share the program memory with the main CPU. However, if the program memory was to be shared between the CPU and the peripheral processor, all the instructions to the peripheral processor had to be transferred between the memory and the peripheral processor with the main bus in the system. The problem with this is that the CPU will be unable to do anything if the main data bus is occupied by the peripheral processor.

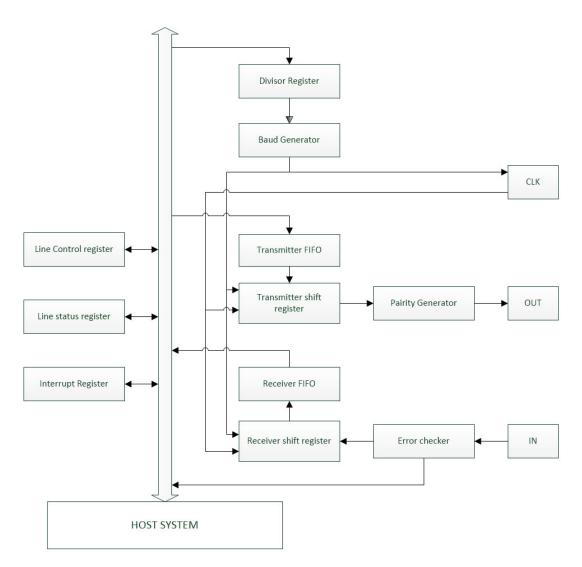

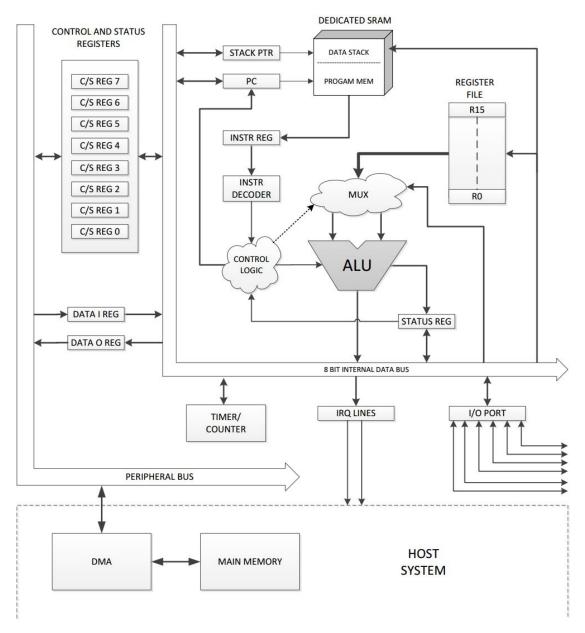

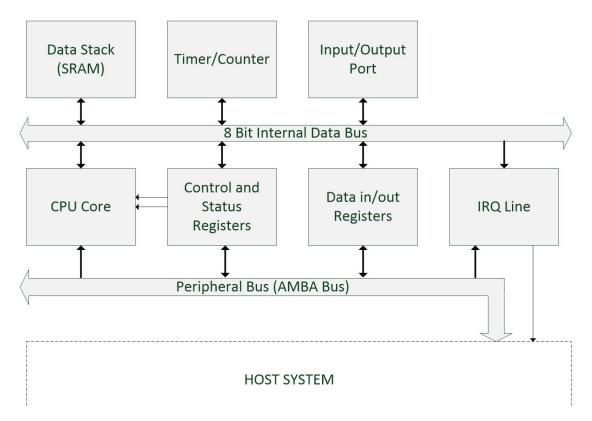

It was also looked into the sizes of the different memories and what extra logic that was needed to control the peripheral processor. A suggestion of how the peripheral processor could be is given in figure 3.1.

The core of the peripheral processor will primarily consist of a register file, ALU, instruction decoder, SRAM and other control logic. The core is then connected to external modules with an internal bus that is specifically designed for this peripheral

FIGURE 3.1: PPU Block Diagram [4]

processor. C/S REG 0 to 7 are the control and status registers. These registers are to set the settings and to read the status of the transfer protocol running on the processor. DATA I REG and DATA O REG are the registers that the CPU writes the data to be transmitted to and reads the data that is received. The IRQ LINES are the interrupt and request signals from the peripheral processor to the CPU. The DATA STACK and PROGRAM MEMORY have a size of 4096 bytes. Furthermore, the peripheral processor will have direct connection to the input and output ports. Additionally, the peripheral processor will need a 16 bit timer to control the transfer

baud rate. The host system will be connected to the peripheral processor with an AMBA APB bus, shown as the peripheral bus.

## 3.4 Performance

During the programming of the UART two issues about running a UART on a processor was found. The first one is that full duplex mode is not possible. This is because a processor cannot do multiple tasks simultaneously. The other issue is that the baud rate have to be significantly lower than it can be on non programmable hardware. As mentioned in chapter 2.4 the receiver have to have a sampling frequency that is 16 times higher than the baud rate. In addition to this the processor will have to use several clock cycles between each sample.

FIGURE 3.2: Excerpt from the UART C-code

Figure 3.2 gives an illustration of how many clock cycles needed from the second sampling to the third. In this example the divisor value (clkCount) is set to 287 and therefore the third sample will be done when TCNT1 is between 2583 (clkCount\*9) and 2870 (clkCount\*10). When the program reaches line number 196 the first time TCNT1 will be less than 2583 and the while-loop will have to do one more loop. The next time the program reaches line 196 TCNT1 is 2731. Now the criteria for the third sample is fulfilled, but the loop needed a total of 217 clock cycles to circle one time. In this example divisor value was chosen to be 287. This value is taken from [2] and results in a commonly used baud rate at 2400 bits/s.

## 3.5 Cost Analysis

The suggestion given in chapter 3.3 was then used to estimate the cost of the peripheral processor. The total cost was given in NAND2 equivalents and was calculated separate for the registers in each module. The formula used for calculating the number of NAND2 gates per register is given in equation 3.1. This is a formula Atmel has provided. A list of the different registers with each corresponding number of bits and NAND2 equivalents is given in table 3.3.

$$TotalNAND2 = NumberOfBits * 10 * 2$$

(3.1)

| Register             | Number of bits | Number of NAND2 gates | Percent |

|----------------------|----------------|-----------------------|---------|

| Register file        | 128            | 2560                  | 2.4%    |

| C/S Registers        | 64             | 1280                  | 1.2%    |

| Data I/O             | 16             | 320                   | 0.3%    |

| Stack Ptr            | 8              | 160                   | 0.2%    |

| Program Counter      | 12             | 240                   | 0.2%    |

| Instruction Register | 16             | 320                   | 0.3%    |

| I/O Ports            | 8              | 160                   | 0.2%    |

| Status Register      | 8              | 160                   | 0.2%    |

| Timer/Counter        | 104            | 2080                  | 2.0%    |

| Sum without SRAM     | 364            | 7280                  | 6.9%    |

| SRAM                 | 32768          | 98304                 | 93.1%   |

| Total                | 33132          | 105584                | 100%    |

Table 3.3: Sum of logic

For comparison, the USART module in the ATmega128 microcontroller have a total of 11 8-bit registers. This results in a total of about 11\*8\*10\*2=1760 NAND2 gates. Furthermore, the SPI module have a total of 4 8-bit registers. This results in a total of about 4\*8\*10\*2=640 NAND2 gates. Last, the TWI module have a total of 5 8-bit registers that results in a total of about 5\*8\*10\*2=800 NAND2 gates. These three modules will therefore require a total of about 1760+640+800=3200 NAND2 gates.

# Chapter 4

# Procedure

The block diagram of the peripheral processor given in figure 3.1 was used as a specification together with the block diagram given in figure 2.1 to implement the peripheral processor in HDL. It is important to notice that figure 2.1 and 3.1 was only used as a guideline to how the peripheral processor was to be implemented and was not used as a complete specification.

The main HDL language in Amel is Verilog. It was therefore natural to use Verilog to implement the processor in HDL. The main advantage of using this language was that Atmel then could give the author access to all the necessary tools that Atmel utilizes.

## 4.1 Verilog Implementation

All the modules discussed have a reset signal. This signal will reset all modules when set to logical 0, but it will not be mentioned when discussing the different modules. Also, some names of the input and output signals have been changed from their original names in figure 2.1 and 3.1. Therefore, all names mentioned in this chapter will have the same name as the final result given in chapter 5.

When starting on the code for the processor, the theory in chapter 2.2 was the starting point. First the register file and the ALU was implemented. The register file was given the same inputs and outputs as given in figure 2.1 but with a small name change. When implementing the ALU, it was decided that functions important for the processor to work would be implemented first, and that more functions would be added later if time allowed it.

After the first draft of the register file and the ALU was implemented, the implementation of the instruction decoder was started. Before implementing the instruction decoder, a decision of what size and layout of the opcode to be used had to be made. It was chosen to use the same opcode layout as Atmel have on their 8-bit AVR. The reason for the choice will be discussed in chapter 6. Similarly as the ALU, only a few instructions where included in the instruction decoder at first.

The branch control and the program counter was implemented after the instruction decoder was tested and working. The program counter was not implemented as a separate module, but was included in the branch control. Also, two extra signals, best and offset, was added between the instruction decoder and the branch control.

As concluded in the preliminary work, an SRAM would be used as program memory and stack to save area. The SRAM module was provided by Amel, but needed a wrapper to be able to communicate with the rest of the system. First it was planned to have a shared SRAM between the program memory and the stack, but this was changed during the implementation to two separate SRAM modules for the program memory and the stack.

The stack was moved out of the CPU core and the read and write procedure to the stack was set to be done via the data bus. A timing issue occurred when reading and writing to the stack. To correct this, two signals where added to the branch control and instruction decoder: hold\_pc and done\_hold. hold\_pc was also added to the program memory.

After reading and writing to the stack was working properly, all the other external modules where implemented. And the internal data bus was extended each time a new external module was added.

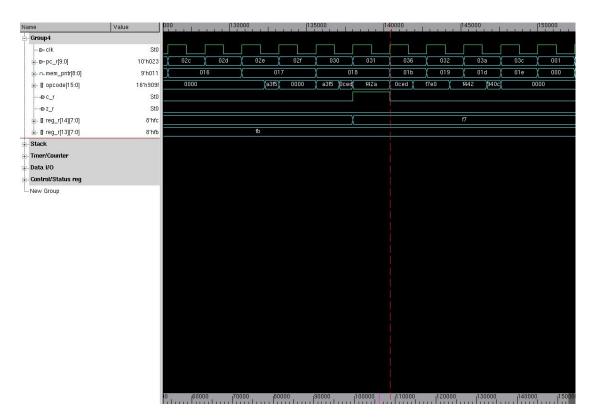

## 4.2 Test Programs

When all the modules were working and connected to the system, two test programs were made. The first test program was made to check that all the instructions of the peripheral processor was function properly. This was done with a test bench that inserted the opcode for all the different instructions into the program memory at the beginning of the simulation and then let the processor run trough all the instructions.

The second test program was made to be more realistic. This test program was loaded into the peripheral processor by simulating the same method the host system would use to program it. To do this, the test bench was made to load the instructions into the memory one by one each clock cycle by using the input signals from the APB bus into the peripheral processor.

The task of the test program was to behave as a simple UART module to verify that the processor was able to do the most basic operations needed by a UART module. For the transmitter part, this included checking the status register for new data on the input register, loading 8 bit from the input register, calculating parity bit and transmitting one data frame including start bit and stop bit.

The receiver part of the test program was to recognise a start bit on the input port, shift 8 bits into a register, transfer this data to the output register and then sending an interrupt to the host system.

## 4.3 Synthesis

When the peripheral processor was working on the RTL level, Spyglass was used to check for problems with the design that is not possible to synthesize. The errors

and warnings where corrected and a synthesize was done. Synthesis was done with Design Compiler by using a script that Atmel provided. This script did also analyse the peripheral processor and printed several reports of the specifications of the circuit. The most important reports where area, timing and fault coverage.

After the synthesis was done, Formality was run to check that all the modules did behave the same way before and after the synthesis. When this test was succeeded, a clock tree synthesis was done. This synthesis did a layout of the circuit so that more specific reports could be presented.

Last, a power simulation was done. This was done by simulating the UART program running on the peripheral processor with the same clock tree and layout made in the previous step.

# Chapter 5

# Results

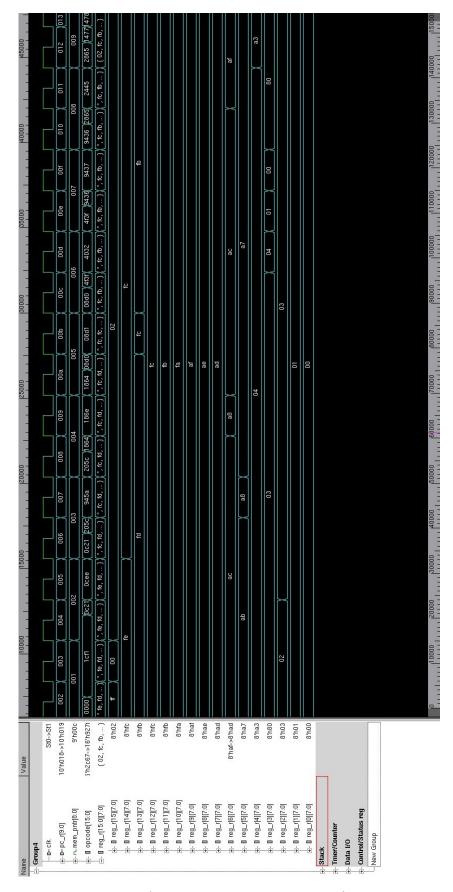

## 5.1 CPU Core

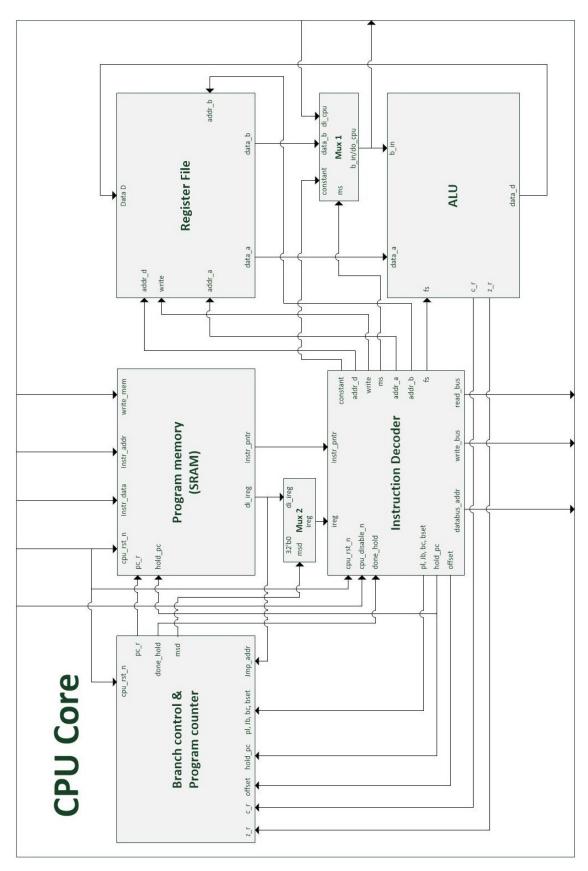

Figure 5.1 gives an illustration of the core of the peripheral processor. It has several common features as the example processor given in chapter 2.2, but there are also some major differences. Table 5.1 and 5.2 gives a short description of all the in/out signals connected to each module including the bit size of the signals.

FIGURE 5.1: PPU Core Block Diagram

| Signals from the register file: |           |                                                            |  |

|---------------------------------|-----------|------------------------------------------------------------|--|

| Signal                          | Bit Size  | Description                                                |  |

| data_a                          | 8         | Data to be transmitted from the register pointed           |  |

|                                 |           | to by addr_a to ALU.                                       |  |

| data_b                          | 8         | data to be transmitted from the register pointed           |  |

|                                 |           | to by addr_b to Mux.                                       |  |

| Signals from                    | the mux   | :                                                          |  |

| b_in                            | 8         | Data to be transmitted from the mux to the ALU.            |  |

| do_cpu                          | 8         | Data to be transmitted to external modules.                |  |

| Signals from                    | the ALU   | J:                                                         |  |

| data_d                          | 8         | data to be written to the register pointed to by addr_d.   |  |

| c_r                             | 1         | Carry flag                                                 |  |

| $Z_{-}Z$                        | 1         | Zero flag                                                  |  |

| Signals from                    | the instr | ruction decoder:                                           |  |

| addr_a                          | 4         | Points to the register that is the output on data_a.       |  |

| addr_b                          | 4         | Points to the register that is the output on data_b.       |  |

| addr_d                          | 4         | Points to the register that the content on data_d          |  |

|                                 |           | is to be written to.                                       |  |

| write                           | 1         | Is set high when the content on data_d is written          |  |

|                                 |           | to a register.                                             |  |

| constant                        | 8         | Contains a constant given in an instruction.               |  |

| ms                              | 2         | Signal to select input on the mux.                         |  |

| fs                              | 5         | Selects ALU function.                                      |  |

| read_bus                        | 1         | Is set high when the internal data bus is to be read.      |  |

| write_bus                       | 1         | Is set high when data is written to the internal data bus. |  |

| databus_addr                    | 7         | Gives the address of the location that data is to be       |  |

|                                 |           | written to or read from via the internal data bus.         |  |

| offset                          | 7         | Used when branching. Gives the number of steps             |  |

|                                 |           | the program counter will jump. Is given in two's           |  |

|                                 |           | complement and can be both positive and nega-              |  |

|                                 |           | tive.                                                      |  |

| hold_pc                         | 1         | When held high, the program counter will not in-           |  |

|                                 |           | crement. Used for instructions that need more              |  |

|                                 |           | than one clock cycle to complete.                          |  |

| pl                              | 1         | When set high, a branch or jump is called.                 |  |

| jb                              | 1         | Determines if a branch or jump is called.                  |  |

| bc                              | 2         | Determines what status flag that triggers a branch.        |  |

| bset                            | 1         | Determines if the branching is triggered on high or        |  |

|                                 |           | low status flag.                                           |  |

Table 5.1: Signal description

| Signals from  | Signals from the branch control: |                                                      |  |  |

|---------------|----------------------------------|------------------------------------------------------|--|--|

| pc_r          | 11                               | Program counter                                      |  |  |

| done_hold     | 1                                | This signal is set high one clock period after       |  |  |

|               |                                  | hold_pc is set high. Used when writing to and        |  |  |

|               |                                  | reading from the stack.                              |  |  |

| msd           | 1                                | Used when jumping. This signal decides if the sig-   |  |  |

|               |                                  | nal to the instruction decoder comes from the pro-   |  |  |

|               |                                  | gram memory or if it is set to zero.                 |  |  |

| Signals from  | the prog                         | ram memory:                                          |  |  |

| di₋ireg       | 32                               | The instructions to be decoded. Is 32 bit wide and   |  |  |

|               |                                  | contains two instructions.                           |  |  |

| $instr\_pntr$ | 1                                | A pointer that points to the part of the instruction |  |  |

|               |                                  | register that is to be decoded.                      |  |  |

| Signals from  | the exte                         | rior:                                                |  |  |

| Signal        | Bit Size                         | Description                                          |  |  |

| $instr\_data$ | 32                               | Used when programming the memory. Contains           |  |  |

|               |                                  | the data to be written to the program memory.        |  |  |

| $inst\_addr$  | 9                                | Used when programming the memory. Points to          |  |  |

|               |                                  | the memory location where the instruction data is    |  |  |

|               |                                  | to be written.                                       |  |  |

| $write\_mem$  | 1                                | Is set high if the program memory is to be pro-      |  |  |

|               |                                  | grammed.                                             |  |  |

| cpu_disable_n | 1                                | When held low, the CPU will be paused.               |  |  |

| cpu_reset_n   | 1                                | When set low, the CPU will jump to the start of      |  |  |

|               |                                  | the program memory. No registers will be reset.      |  |  |

Table 5.2: Signal description

## Register File

The register file have sixteen registers each with the size of eight bit. Writing to the register will occur at the rising edge of the clock and when write is set to logical one. The input on data\_d will then be written to the address given by addr\_d. The output on data\_a and data\_b is not driven by the clock, but will always give the data where addr\_a and adddr\_b is pointing to.

#### ALU

The ALU is primarily combinatorial and not driven by the clock. The only elements of the ALU that is sequential is the status flags c\_r and z\_r. These two signals will at the rising clock edge be given the value that was generated by the operation done at that clock edge.

#### Instruction Decoder

The instruction decoder have been changed a lot compared to chapter 2.2. The instruction register and instruction decoder are now in the same module. Also, the data into the instruction register, di\_ireg, is 32 bit, but each instruction is only 16 bit. Therefore an extra signal, instr\_pntr, is added to indicate what part of the 32 bit data that is to be decoded. The instruction decoder has no clock and is therefore 100% combinatoric. The signal hold\_pc is used when instructions that need two clock periods is executed. Because the instruction decoder do not have a clock, a signal from the branch control is needed to indicate the start of the second clock period. This is the done\_hold signal. The two signals cpu\_rst\_n and cpu\_disable\_n have the same functionality in the instruction decoder. Both signals will set the instruction decoder to do NOP-operations.

The instruction decoder is using the same opcode layout and addressing mode used in the AVR Instruction Set[9].

## Branch Control and Program Counter

The branch control and program counter have been included in one module. The offset signal is used when branching and is given in two's complement. This is because the program counter have to be able to branch in both directions. The msd signal is used when a jump is called. This signal is necessary to prevent the instruction decoder to decode the jump address as an instruction. When a jump is called, the 32 bit in the next program memory location is used as the address for the jump.

This address can accidentally have the same binary number as a valid instruction for the instruction decoder and will cause the processor to execute a random instruction while the branch control is jumping to an address. Therefore the msd signal will set the ireg signal from Mux 2 to be zero when a jump is called.

### **Program Memory**

The Program memory is based on an SRAM module provided by Atmel and have a size of 512 x 32 bits. This size will give room for a program with 1024 16-bit instructions. The program memory consists of a wrapper and the SRAM module. The wrapper is controlling the signals to and from the program memory so that the SRAM module is compatible with the rest of the system. Among others, the wrapper is inverting the clock signal to the SRAM. This is to prevent reading from it to require two clock cycles.

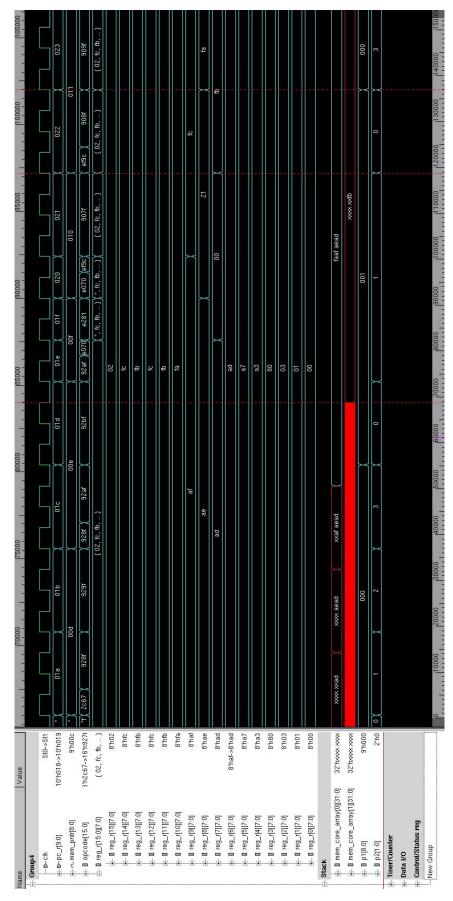

### 5.2 External Modules

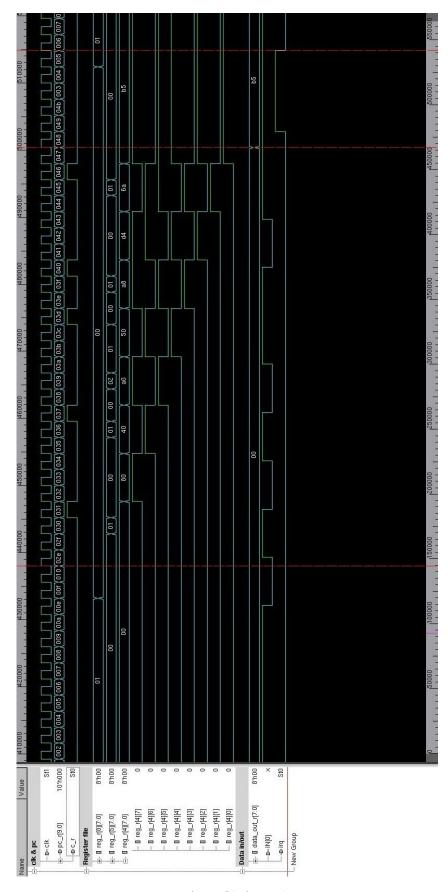

Figure 5.2 gives an illustration of the whole peripheral processor with the bus system and all the modules connected to it.

#### **Internal Data Bus**

The 8-bit internal data bus is the bus that connects the CPU core together with all the external modules. The CPU core is the master of the bus and no reading or writing operations are done without the CPU core controlling it. When writing is to be done, the CPU core will send three signals to the data bus: databus\_addr, do\_cpu and write\_bus. The signal databus\_addr is a 7-bit signal that is divided into two parts. The first three bits gives the address of the external module where the data is to be sent and the last four bits gives what register in the external module

FIGURE 5.2: PPU Block Diagram

that is to be written to. The signal do\_cpu is the data signal from the CPU core to the external modules.

For example, if data is to be written to the first register of the control and status register. The CPU core will set the 7 bits in the databus\_addr signal to 0010001. The first three bits (001) is the address of the control and status register and the last four bits (0001) is the address of the first register in the control and status register. Also the CPU core will set write\_bus high. Because databus\_addr points to the control and status register and write\_bus is set high, the data bus will set the signal w\_cs\_reg high, forward the last four bits of databus\_addr to cs\_reg\_addr and forward the data on do\_cpu to di\_cs\_reg. The control and status register will notice that w\_cs\_reg is set high and therefore write the data on di\_cs\_reg to the address on ca\_reg\_addr.

Reading from an external module works with the same principle, however the CPU core does only need to set the address to the register it will read from. The signal read\_bus is only needed when reading from the data stack and the timer.

Table 5.3 gives a short description of the signals from the CPU core and the data bus.

| Signals from        | the | e CPU core:                                           |

|---------------------|-----|-------------------------------------------------------|

| do_cpu              | 8   | Data out from the CPU core to the internal data       |

|                     |     | bus.                                                  |

| databus_addr        | 7   | Gives the address where the data on the data bus      |

|                     |     | is sent to or read from.                              |

| write_bus           | 1   | Is set high when the data on the data bus is to be    |

|                     |     | written to an external module.                        |

| read_bus            | 1   | Is set high when the CPU core is to read data from    |

|                     |     | the data bus.                                         |

| Signals from        | the | e internal data bus:                                  |

| di_cpu              | 8   | The data to the CPU core.                             |

| write_stack         | 1   | Is set high when data is to be written to the stack.  |

| read_stack          | 1   | Is set high when data is to be read from the stack.   |

| $di\_stack$         | 8   | The data to the stack.                                |

| w_cs_reg            | 1   | Is set high when data is to be written to the control |

|                     |     | and status register.                                  |

| $cs\_reg\_addr$     | 4   | Gives the address of what register in the control     |

|                     |     | and status register to read from or written to.       |

| di_cs_reg           | 8   | The data to the control and status register.          |

| w_io_reg            | 1   | Is set high when data is to be written to the in-     |

|                     |     | put/output register.                                  |

| di_io_reg           | 8   | The data to the input/output register.                |

| w_timer             | 1   | Is set high when data is to be written to the timer.  |

| $r_{	ext{-}}$ timer | 1   | Is set high when data is to be read from the timer.   |

| timer_addr          | 4   | Gives the address of what register in the timer that  |

|                     |     | is to be read from or written to.                     |

| di_timer            | 8   | The data to the timer.                                |

| w_irq               | 1   | Is set high when data is to be written to the IRQ     |