# High-Level Synthesis for Application-Specific Integrated Circuit Implementation using LegUp

Jørgen F Holmefjord

Master of Science in Electronics Submission date: June 2016 Supervisor: Kjetil Svarstad, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

| Title:   | High-Level Synthesis for                |

|----------|-----------------------------------------|

|          | Application-Specific Integrated Circuit |

|          | Implementation using LegUp              |

| Student: | Jørgen Frydenlund Holmefjord            |

# Problem description:

Architectural exploration is a long and complex process where a number of hardware architectures are built and evaluated based on minimum performance requirements and worst-case operational scenarios. With this method, satisfactory results can be achieved if a diverse number of candidates are produced. However, the number of architectures to be evaluated is limited by time and engineering resources. In this context, High Level Synthesis (HLS) is a compelling alternative to shorten the development time, and consequently, increasing the number of architectures that can be evaluated during the exploration. Furthermore, by automating the entire architecture exploration process, the optimization engine can take advantage of the higher level of abstraction and generate far more and diverse architectures than it would be possible by parametrized RTL.

During the autumn of 2015, a project was conducted to evaluate the open-source HLS tool LegUp [13], and whether it can be used in a framework for architectural exploration of digital hardware. During the work with the project some fundamental issues were exposed, limiting the tool's usefulness for our initial intentions. The main issues are related to input and output of the generated modules, structure of memory management, and size of signals.

The goal of this master thesis is to resolve the encountered issues, and if time allows it, start building an initial framework for architectural exploration.

# Possible sub-tasks and goals of this thesis are:

- Explore the two approaches proposed in the project for resolving the encountered issues.

- Determine if LegUp's C-like memory-bound architecture can be eliminated by de-referencing pointers or turn memory elements into generic signals.

- Re-evaluate if LegUp is capable of generating synthesizable Verilog HDL for ASIC implementation and if it can be used in a framework for automatic architectural exploration.

- Set an initial HLS framework for architectural exploration of digital hardware.

- Create scripts to automate simulation, synthesis, and power dissipation extraction.

- Integrate Nordic Semiconductor's coding style and practices into LegUp Verilog libraries, i.e. interfaces, parameters, naming conventions, power/clock domains, etc.

| Responsible professor: | Kjetil Svarstad, IET             |  |  |  |  |  |  |  |

|------------------------|----------------------------------|--|--|--|--|--|--|--|

| Supervisor:            | Isael Diaz, Nordic Semiconductor |  |  |  |  |  |  |  |

# Abstract

Low power and small area are becoming increasingly important and highly demanded in large System-on-Chip (SoC) designs, incorporating billions of transistors. This entails that the typical design methodology is no longer sufficient, if hardware manufacturers want to supply the best product on the market. Architectural exploration is an important part of the design process, where multiple designs are built and evaluated in terms of area, performance, and power consumption. High-level synthesis (HLS) is a compelling alternative to reduce the effort put into architectural exploration. By using HLS in a framework for architectural exploration of digital hardware, the number and diversity of architectural variations that can be generated and evaluated is far greater than what could have been done manually.

During a previous project, the HLS-tool LegUp was explored. The goal was to see if the tool could be used the described framework. The conclusions from the project was that LegUp had some issues, limiting its ability to generate Register-Transfer Level (RTL)-code suitable for Application-Specific Integrated Circuit (ASIC) implementation.

This thesis presents a solution for an architectural exploration framework built on an adapted version of LegUp. The framework can generate a large amount of architectural variations of a design written in C, and run simulation, synthesis, layout and power analysis on each design. Randomized constraints are used in the framework to vary the output from the HLS-tool. The framework generate reports of area usage, maximum performance, and estimated power consumption for each of the generated designs, for the designer to be able to choose the best design based on trade-offs from the design specifications.

A proof of concept was conducted, running a FIR-filter design through the created framework. The result showed that a decrease in area of 13.28% and a decrease in power consumption of 9.52% could be achieved by selecting the best-case design over the worst-case design. These results indicate that the concept works. The overhead of the generated designs vary between 30-200%, making it impractical for hardware design. However, it looks like the fidelity of the results are high, making it possible to use the framework-results for selecting the best architecture. During the process of adapting LegUp to work with a tool-flow for ASIC implementations, some of the functionality of the tool have been lost. Some bugs has also been introduced and discovered. Before using the created framework for any commercial purpose, these problems must be eliminated.

# Sammendrag

Lavt effektforbruk og lite areal er stadig mer etterspurt i store design av enbrikkesystemer, bestående av milliarder av transistorer. Dette fører til at den typiske design-metoden ikke lenger er brukende, dersom maskinvareprodusentene ønsker å tilby det beste produktet på markedet.

Arkitektur-utforsking er en viktig del av designprosessen, hvor flere design skapes og blir evaluert i form av areal, ytelse, og effektforbruk. Høynivå syntese (HLS) er et attraktivt konsept for å redusere den samlede innsatsen designeren må legge ned i arkitektur-utforskingen. Ved å benytte HLS i et rammeverk for arkitektur-utforsking av digital maskinvare kan langt flere og mer varierte arkitekturelle variasjoner genereres og evalueres, sammenlignet med å utføre arbeidet manuelt.

I et tidligere prosjekt ble HLS-verktøyet *LegUp* utforsket. Målet var å undersøke om verktøyet kunne brukes i det beskrevne rammeverket. Konklusjonen fra prosjektet var at noen problemer med LegUp begrenser muligheten til å generere Register-Transfer Level (RTL)-kode egnet til implementering på applikasjonsspesifikk integrert krets (ASIC) arkitekturer.

Denne avhandlingen presenterer en løsning for et rammeverk for arkitek-tur-utforskring bygget på en tilpasset versjon av LegUp. Rammeverket kan generere et stort antall arkitekturelle variasjoner av et design skrevet i C, og kjøre simulering, syntese, layout, og effekt-analyse på hvert design. Randomiserte føringer benyttes i rammeverket for å generere varierte design fra HLS-verktøyet. Rammeverket genererer rapporter som beskriver arealbruk, maksimal ytelse, og beregnet effektforbruk for hvert design, slik at designeren kan velge det designet som passer best, basert på avveininger mellom viktige parametre fra designspesifikasjonen.

Et konseptbevis ble utført ved å kjøre et FIR-filter design gjennom rammeverket. Resultatet viste at en besparelse i areal på 13.28% og en besparelse i effektforbruk på 9.52% kan oppnås ved å velge det designet med best resultater over designet med dårligst resultater. Disse resultatene viser at konseptet fungerer. HLS-verktøyet genererer en økning i areal og effektforbruk sammenlignet med et tilsvarende design skrevet direkte i RTL-kode på mellom 30-200%, noe som gjør det lite økonomisk å benytte verktøyet til design av maskinvare. Forholdet mellom de genererte resultatene ser likevel ut til å stemme (høy *fidelity*), noe som gjør at rammeverk-resultatene kan benyttes til å velge arkitektur for designet. Gjennom prosessen med å tilpasse LegUp til å generer kode som støttes av verktøyene i rammeverket har noe av den originale funksjonaliteten gått tapt. Noen feil har også oppstått og blitt oppdaget. Før rammeverket brukes til noen form for kommersielle formål må alle problemer som er beskrevet i denne rapporten elimineres.

# Preface

This report is the result of the Master's thesis conducted during the spring of 2016, concluding a Master of Science degree in Electronics, Design of Digital Systems. The report is submitted to the Department of Electronics and Telecommunications at the Norwegian University of Science and Technology.

This work is a continuation of a specialization project conducted during the autumn of 2015. The project was proposed by Nordic Semiconductor in August 2015, and the continuation into a Master's thesis was a natural choice in January 2016. During the work with this thesis, I have learned a lot about the concept of high-level synthesis and how to implement integrated circuits, all the way from the planning stage until final layout.

I would like to thank my supervisors Isael Diaz at Nordic Semiconductor and professor Kjetil Svarstad from NTNU, for their guidance, support and feedback through this project. Finally, I want to thank my family and friends for their support, encouragement and inspirational discussions during this work and through the whole degree.

Trondheim, 2016-06-10

Jørgen Frydenlund Holmefjord

# Contents

| $\mathbf{Li}$ | List of Figures |                                     |      |  |  |  |

|---------------|-----------------|-------------------------------------|------|--|--|--|

| $\mathbf{Li}$ | List of Tables  |                                     |      |  |  |  |

| $\mathbf{Li}$ | st of           | Algorithms                          | xv   |  |  |  |

| A             | crony           | /ms                                 | xvii |  |  |  |

| 1             | Intr            | oduction                            | 1    |  |  |  |

|               | 1.1             | Motivation                          | 1    |  |  |  |

|               | 1.2             | Previous work                       | 2    |  |  |  |

|               | 1.3             | Project objectives                  | 2    |  |  |  |

|               | 1.4             | Contributions                       | 5    |  |  |  |

|               | 1.5             | Method                              | 5    |  |  |  |

|               | 1.6             | Overview of the thesis              | 6    |  |  |  |

| <b>2</b>      | The             | eory and background                 | 7    |  |  |  |

|               | 2.1             | High-Level Synthesis                | 7    |  |  |  |

|               | 2.2             | LegUp                               | 10   |  |  |  |

|               |                 | 2.2.1 Producing Verilog Output      | 11   |  |  |  |

|               |                 | 2.2.2 Classes                       | 12   |  |  |  |

|               |                 | 2.2.3 Constraints                   | 15   |  |  |  |

|               | 2.3             | LLVM                                | 15   |  |  |  |

|               |                 | 2.3.1 Intermediate Representation   | 15   |  |  |  |

|               | 2.4             | Alternative hardware design methods | 17   |  |  |  |

|               |                 | 2.4.1 Chisel                        | 17   |  |  |  |

|               |                 | 2.4.2 Functional programming        | 17   |  |  |  |

|               | 2.5             | Power dissipation in CMOS circuits  | 18   |  |  |  |

|               |                 | 2.5.1 Switching power               | 18   |  |  |  |

|               |                 | 2.5.2 Internal power                | 19   |  |  |  |

|               |                 | 2.5.3 Leakage power                 | 19   |  |  |  |

|               | 2.6             | Tool-flow                           | 19   |  |  |  |

|               |                 | 2.6.1 Simulation                    | 19   |  |  |  |

|   |      | $2.6.2  \text{Synthesis}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                     |

|---|------|------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | 2.6.3 Layout                                                                                                                                   |

|   |      | $2.6.4  \text{Power analysis}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                |

|   | 2.7  | Reference design                                                                                                                               |

|   |      | 2.7.1 FIR-filter                                                                                                                               |

| 3 | Ada  | ting LegUp 23                                                                                                                                  |

|   | 3.1  | Approach                                                                                                                                       |

|   |      | 8.1.1 Post-processing                                                                                                                          |

|   |      | $3.1.2  \text{Pre-processing}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                |

|   |      | 3.1.3 The used approach $\ldots \ldots 24$                               |

|   | 3.2  | $\Gamma CL \text{ commands} \dots \dots$ |

|   | 3.3  | Removing top-level and FPGA-specific modules                                                                                                   |

|   | 3.4  | Removing memory controller                                                                                                                     |

|   | 3.5  | Declaring inputs and outputs                                                                                                                   |

|   |      | 8.5.1 Name prefix                                                                                                                              |

|   |      | 8.5.2 TCL-command                                                                                                                              |

|   | 3.6  | Assigning values to outputs                                                                                                                    |

|   |      | 8.6.1 LLVM IR assignment parser program                                                                                                        |

|   |      | 3.6.2 Assigning output signals                                                                                                                 |

|   |      | 3.6.3 Removing local RAMs                                                                                                                      |

|   | 3.7  | Streaming inputs/outputs                                                                                                                       |

|   | 3.8  | $\beta$ ignal sizes $\ldots \ldots 38$                            |

|   | 3.9  | Testbench generation                                                                                                                           |

|   | 3.10 | Coding constraints                                                                                                                             |

|   |      | $3.10.1 \text{ Structs} \qquad \qquad 40$                                                                                                      |

|   |      | $8.10.2 \text{ Pointers} \dots \dots$    |

|   |      | 8.10.3 Arrays                                                                                                                                  |

|   |      | 3.10.4 Inputs and outputs                                                                                                                      |

| 4 | Too  | flow example 43                                                                                                                                |

|   | 4.1  | ILS with LegUp                                                                                                                                 |

|   |      | 4.1.1 Constraint files                                                                                                                         |

|   |      | 4.1.2 Makefile                                                                                                                                 |

|   |      | 1.3 Compilation                                                                                                                                |

|   |      | 1.4 Link-time optimizations                                                                                                                    |

|   |      | $4.1.5$ Verilog generation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 46$                                          |

|   | 4.2  | Simulation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 50                                                          |

|   |      | .2.1 Simulation libraries                                                                                                                      |

|   |      | A.2.2 Running simulation                                                                                                                       |

|   | 4.3  | Synthesis $\ldots \ldots 52$                 |

|   | 4.4  | Jayout                                                                                                                                         |

|   |      |                                                                                                                                                |

|              | 4.5            | Power analysis                                                                             | 54  |

|--------------|----------------|--------------------------------------------------------------------------------------------|-----|

| <b>5</b>     | Cre            | ating the framework                                                                        | 57  |

|              | 5.1            | Create new project                                                                         | 57  |

|              | 5.2            | Framework-script                                                                           | 57  |

|              |                | 5.2.1 Constraint generating                                                                | 60  |

|              |                | 5.2.2 Report generating                                                                    | 62  |

|              | 5.3            | Running the framework                                                                      | 62  |

| 6            | Frai           | nework results                                                                             | 65  |

|              | 6.1            | First test-run                                                                             | 65  |

|              |                | 6.1.1 Handling unexpected results                                                          | 68  |

|              | 6.2            | Full tool-flow framework run                                                               | 70  |

|              | 6.3            | Bugs in the generated design                                                               | 74  |

|              | 6.4            | Path and hold violations                                                                   | 75  |

|              | 6.5            | LegUp specific code optimization $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 76  |

| 7            | Dise           | cussion                                                                                    | 79  |

| 8            | Con            | clusion                                                                                    | 83  |

|              | 8.1            | Future work                                                                                | 84  |

|              |                | 8.1.1 Abstraction level                                                                    | 84  |

|              |                | 8.1.2 Resolving bugs                                                                       | 84  |

|              |                | 8.1.3 Eliminating RAM states                                                               | 84  |

|              |                | 8.1.4 Advances in LegUp since last release                                                 | 85  |

|              |                | 8.1.5 Automatic code-optimization                                                          | 85  |

|              |                | 8.1.6 Incorporating Nordic Semiconductors DDVC                                             | 85  |

| Re           | efere          | nces                                                                                       | 87  |

| A            | ppen           | dices                                                                                      |     |

| $\mathbf{A}$ | $\mathbf{Sou}$ | rce code listings                                                                          | 91  |

|              | A.1            | FIR-filter reference design                                                                | 91  |

|              |                | A.1.1 C source code                                                                        | 91  |

|              |                | A.1.2 Optimized C source code                                                              | 92  |

|              |                | A.1.3 Verilog source code                                                                  | 93  |

|              |                | A.1.4 Testbench for FIR-filter                                                             | 94  |

|              | A.2            | LLVM IR Parser program                                                                     | 96  |

|              | A.3            | Generating valid signals                                                                   | 99  |

|              | A.4            |                                                                                            | 100 |

|              | A.5            |                                                                                            | 100 |

|              | A.6            |                                                                                            | 101 |

|              | A.7            | Script for running framework                                                               | 102 |

| A.8 | Constraint-generator program |  |  |  |  |  |  |  | • |  |  |  |  |  |  |  |  |  |  |  | 10 | 6 |

|-----|------------------------------|--|--|--|--|--|--|--|---|--|--|--|--|--|--|--|--|--|--|--|----|---|

|-----|------------------------------|--|--|--|--|--|--|--|---|--|--|--|--|--|--|--|--|--|--|--|----|---|

# List of Figures

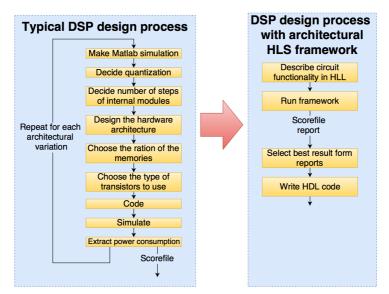

| 1.1 | Typical DSP design process compared to HLS-framework.                      | 2  |

|-----|----------------------------------------------------------------------------|----|

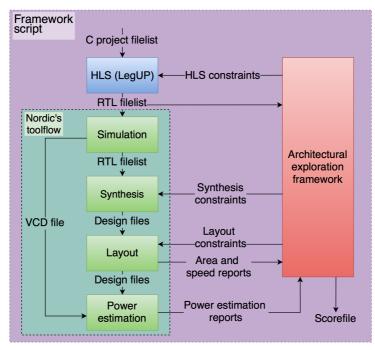

| 1.2 | Proposed framework-solution [13].                                          | 3  |

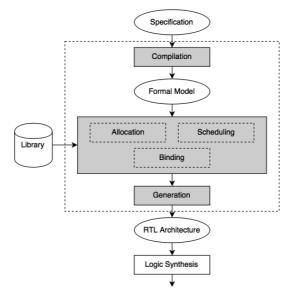

| 2.1 | Information flow in a typical HLS-tool [8]                                 | 8  |

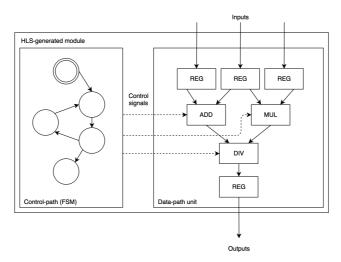

| 2.2 | Typical division of control and data-path in the generated RTL from HLS.   | 9  |

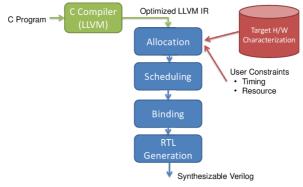

| 2.3 | Information flow in LegUp [19]                                             | 11 |

| 2.4 | LLVM's three-phase compiler structure [15]                                 | 17 |

| 2.5 | Power dissipation components distribution [26]                             | 18 |

| 2.6 | Direct form representation of a N-order FIR-filter.                        | 22 |

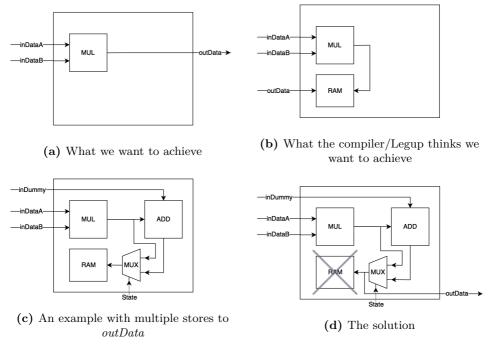

| 3.1 | Problem with assigning values to output                                    | 34 |

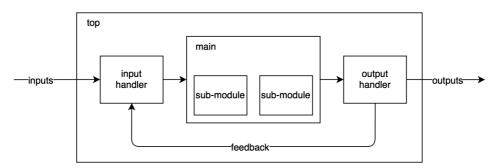

| 3.2 | Top-level concept for streaming inputs and outputs                         | 36 |

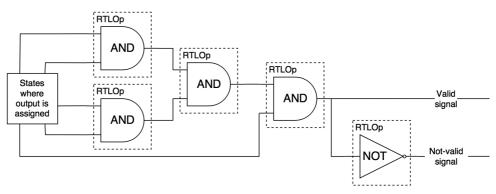

| 3.3 | Generating not-valid signal.                                               | 37 |

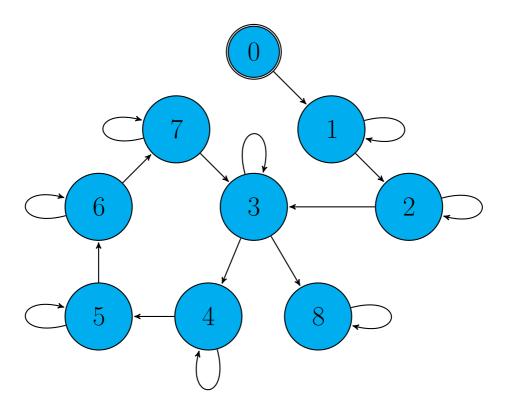

| 4.1 | State diagram of generated FSM                                             | 49 |

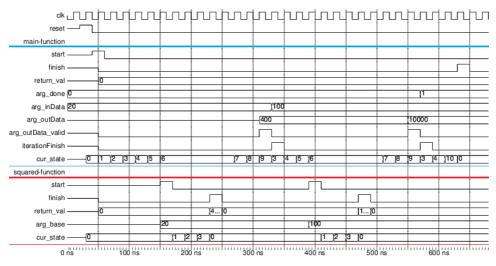

| 4.2 | Simulation waveform of example design                                      | 52 |

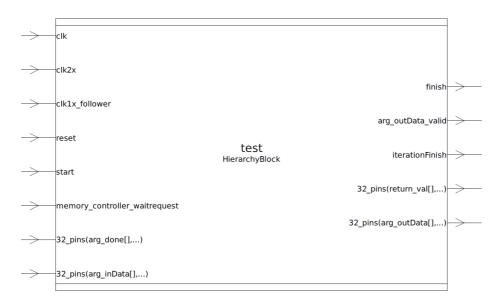

| 4.3 | Top-level module generated by synthesis                                    | 53 |

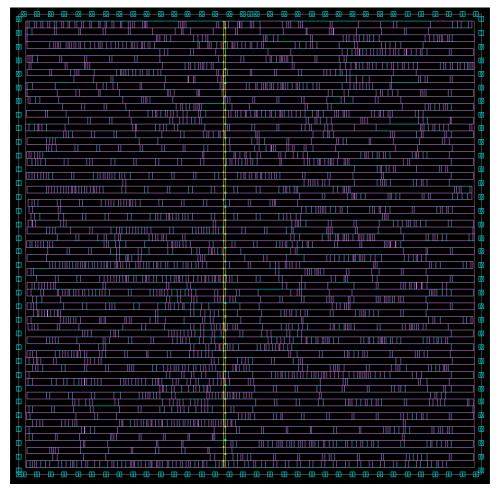

| 4.4 | Chip-layout of example design                                              | 54 |

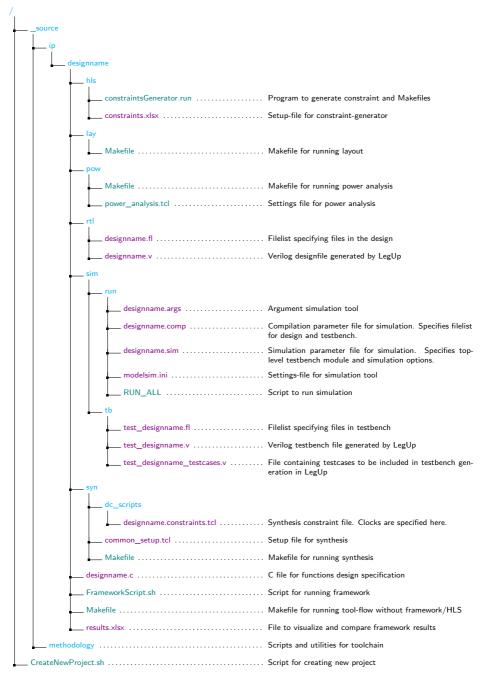

| 5.1 | Directory and file-tree of the framework                                   | 58 |

| 5.2 | Setup of constraint file generation in Excel spreadsheet                   | 61 |

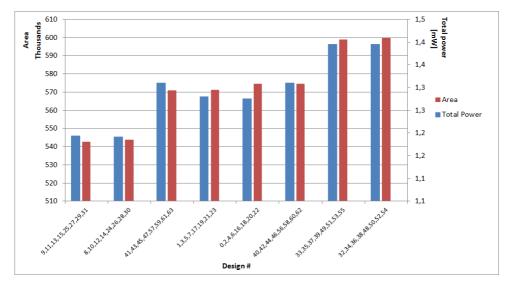

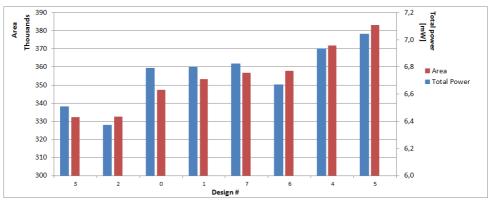

| 6.1 | Results from 1. framework-run                                              | 67 |

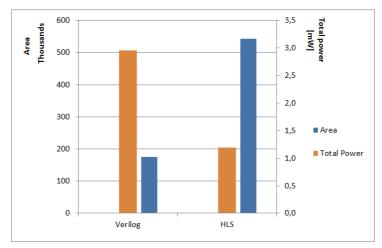

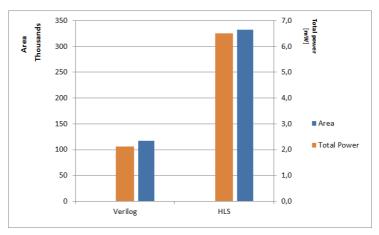

| 6.2 | Comparison of Verilog-design towards best HLS-design from 1. framework-    |    |

|     | run                                                                        | 68 |

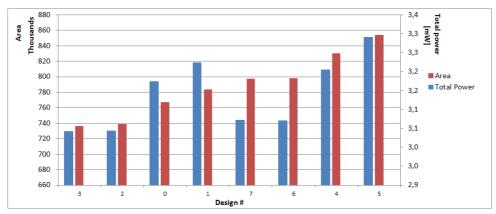

| 6.3 | Results from 2. framework-run                                              | 69 |

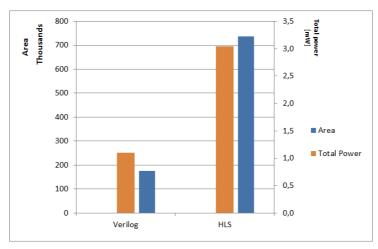

| 6.4 | Comparison of Verilog-design towards best HLS-design from 2. framework-    |    |

|     | run                                                                        | 70 |

| 6.5 | Results from framework with full tool-flow                                 | 72 |

| 6.6 | Comparison of Verilog-design towards best HLS-design from full tool-flow   |    |

|     | framework-run                                                              | 72 |

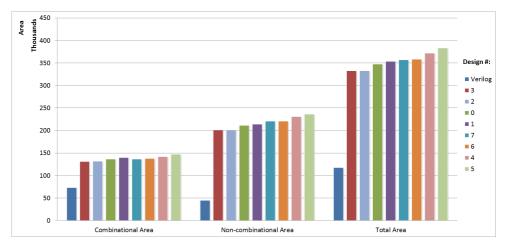

| 6.7 | Area distribution of results from framework with full tool-flow $\ldots$ . | 73 |

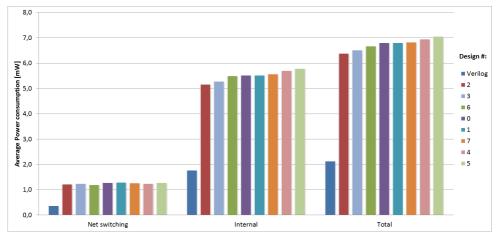

| 6.8 | Power distribution of results from framework with full tool-flow           | 73 |

# List of Tables

| 2.1  | HLS-flows supported by LegUp and partitioning between SW and HW .      | 11 |

|------|------------------------------------------------------------------------|----|

| 2.2  | Description of constraints used in this project                        | 16 |

| 3.1  | Vector values after parser run                                         | 32 |

| 4.1  | Tool-flow example synthesis results                                    | 52 |

| 4.2  | Tool-flow example layout results                                       | 55 |

| 4.3  | Tool-flow example power analysis results                               | 55 |

| 6.1  | Constraints and values for first run                                   | 65 |

| 6.2  | Results from 1. framework-run                                          | 66 |

| 6.3  | Decimal to binary conversion of design numbers                         | 67 |

| 6.4  | Results from 2. framework-run                                          | 69 |

| 6.5  | Area results from full tool-flow framework-run                         | 71 |

| 6.6  | Power estimation results from full tool-flow framework-run             | 71 |

| 6.7  | Number of used registers from full framework run                       | 74 |

| 6.8  | Critical path length and maximum frequency results from full framework |    |

|      | run                                                                    | 75 |

| 6.9  | Results of best design from framework run with optimized C-code        | 77 |

| 6.10 | Overhead from results of optimized C-code                              | 77 |

|      |                                                                        |    |

# List of Algorithms

| 3.1 | Adding parameters to a module                  | 28 |

|-----|------------------------------------------------|----|

| 3.2 | Input file handling in LLVM IR parser program  | 32 |

| 3.3 | Output file handling in LLVM IR parser program | 33 |

| 3.4 | Assigning values to outputs                    | 35 |

|     |                                                |    |

# Acronyms

- **ANSI** American National Standards Institute.

- **ASIC** Application-Specific Integrated Circuit.

- **CPU** Central Processing Unit.

- **CSV** Comma-Separated Values.

- **DDVC** Digital Design and Verification Conventions.

- DFG Data-Flow Graph.

- **DSL** Domain Specific Language.

- **DSP** Digital Signal Processing.

- **FIR** Finite Impulse Response.

- FPGA Field-Programmable Gate Array.

- ${\bf FSM}\,$  Finite State Machine.

- GCC GNU Compiler Collection.

- HCL Hardware Construction Language.

- HDL Hardware Description Language.

- HLL High-Level Language.

- HLS High-Level Synthesis.

- ${\bf HW}\,$  Hardware.

- **IDE** Integrated Development Environment.

- **IIR** Infinite Impulse Response.

- ${\bf IR}\,$  Intermediate Representation.

- ${\bf LTO}$  Link-Time-Optimization.

- ${\bf RAM}\,$  Random Access Memory.

- ${\bf RTL}$  Register-Transfer Level.

- ${\bf SoC}$  System-on-Chip.

- ${\bf SW}$  Software.

- $\mathbf{VCD}\,$  Value Change Dump.

# Chapter Introduction

# 1.1 Motivation

With the increasing focus on power consumption and small design-size, hardware manufacturer are forced to develop their products with these parameters in mind. Architectural exploration of hardware plays a vital role in the process of creating integrated circuits with the best trade-offs between speed, area, and power consumption for a given specification. The process of architectural exploration is a tedious and time-consuming process, involving many steps. During the exploration, a number of hardware architectures are built and evaluated based on minimum performance requirements and worst-case operational scenarios. By generating a large number of designs with great diversity, a satisfactory result can be achieved. The number of architectures that can be evaluated is limited by available time and resources. High-Level Synthesis (HLS) is a compelling alternative to shorten this process. By reducing the time for creating each design, the number of evaluated designs can be increased, with the potential of generating far more diversity between the architectures than what would ever have been possible by parametrized Register-Transfer Level (RTL).

On the left side of figure 1.1 a typical design process for a Digital Signal Processing (DSP) application is shown. On the right side, the same design process is shown, using a HLS-based framework. It can easily be seen that the effort the designer has to put into the process is reduced with the second alternative.

The thesis will look at the implementation of a framework for architectural exploration of digital hardware, targeted for Application-Specific Integrated Circuit (ASIC) implementation. The ultimate goal is to create a framework that automatically explores a wide variety of architectural variations and presents the best alternatives with regards to a given design goal or constraints.

## 2 1. INTRODUCTION

Figure 1.1: Typical DSP design process compared to HLS-framework.

# 1.2 Previous work

In my specialization project [13], conducted during the autumn of 2015, I explored the academic open source HLS-tool *LegUp*. This tool has a maturity not before seen in an academic HLS-tool, and that it is open-source makes it appealing for the concept of a framework for architectural exploration of hardware. LegUp provides ANSI-C to Verilog high-level synthesis, but their focus is targeted towards implementation on Field-Programmable Gate Array (FPGA) architectures. The official target support of the output is limited to a few boards from the FPGA manufacturer Altera, and beta-support for a single board from Xilinx. This thesis will target ASIC implementations. The findings from [13] was that there are some issues with the original version of LegUp, limiting its usability for the desired framework. The issues are mainly related to input and output of the generated modules, structure of memory management, and size of signals. A framework for architectural exploration of hardware, using HLS, was proposed in [13]. An illustration showing the tool- and information-flow of the framework is shown in figure 1.2.

# 1.3 Project objectives

The initial goals of the specialization project were found to be a bit exaggerated. For this Master's thesis it was decided to focus on a smaller part of the ultimate goal, to get the necessary basics of the HLS-tool working well, before proceeding with the framework. The main goal of this thesis is therefore to resolve the issues encountered

Figure 1.2: Proposed framework-solution [13].

during the specialization project. It is not know if all issues can be resolved, or how time consuming it will be. Other objectives are therefore added in a prioritized order:

## 1. Explore approaches

Two possible approaches towards resolving the issued, were described in [13]. The first step of this thesis will be to explore both these alternatives and look at positive and negative sides of each method. The outcome of this objective will affect the rest of the work with this thesis, making it an important decision. All aspects of the two approaches must therefore be taken into consideration before making a choice.

#### 2. Resolve issues

For LegUp to be usable in a framework for architectural exploration, it is vital that the tool is adapted to generated Verilog suitable for ASIC implementation. This objective is thought to be the most time-consuming, and its outcome is very uncertain. However, if completed successfully, the use-space of LegUp can be extended to other concepts. LegUp's architecture is, like the input language C, quite memory-bound. Random Access Memory (RAM) modules, memory controllers, and pointers are used for many things where a simple

## 4 1. INTRODUCTION

signal could have given the same result. It should be looked into if this memoryarchitecture can be changed by de-referencing pointers or turn memory elements into generic signals. A proper way of handling inputs and outputs should also be implemented, to avoid being limited to a certain amount of ports on the generated designs.

# 3. Create framework

When the issues have been resolved, the work with creating a framework for architectural exploration can be started. The framework will be based on the flow shown in figure 1.2, using various scripts and programs to run the tool-flow, generating constraints, and creating scorefiles. The framework should be easy to use and ideally be able to run without any interactions with the user.

# 4. Proof of concept

To verify and illustrate the concept in action, a proof of concept will be created. By creating one or more reference designs which will be run through the framework, it is expected to get a wide variety of generated designs with varying results in terms of area, power consumption, and performance. The reference design will also be implemented directly in Verilog Hardware Description Language (HDL), to compare and calculate the overhead of the HLS-generated designs.

# 5. Evaluation

Based on the results from the conducted proof of concept, a re-evaluate of LegUp's usefulness in a framework for architectural exploration of digital hardware, will be conducted. This evaluation will be based on the deviation of the results among the generated designs, as well as the overhead compared to the design written in Verilog. Other aspects can also be considered, like how well the adaption of LegUp is performed and how well the generated Verilog HDL synthesize for ASIC architectures.

# 6. Techniques for reducing overhead

The typical overhead of HLS-tools are in the range of 30-40%. One of the initial objectives of this concept included the integration of Nordic Semiconductor's coding style and practices, the Digital Design and Verification Conventions (DDVC) [29], into LegUp's Verilog libraries. This include things like interfaces, parameters, naming conventions, power/clock domains, etc. It is assumed that this can give a large reduction of the overhead generated by the HLS-tool, when integrated into Nordic Semiconductor's existing modules.

# 1.4 Contributions

The intentions of this work have been to create an adapted version of the open source HLS-tool LegUp, to make it more suited for generating Verilog targeted towards ASIC architectures. It was also time to create a framework for architectural exploration of digital hardware, and to conduct a proof of concept study.

# The following list summarize the contributions made through this thesis:

- An adapted version of LegUp has been created. The adapted version support features that is important for implementation towards ASIC architectures. This include the possibility of having multiple inputs and outputs in the generated modules, the inputs and outputs can be streaming, eliminating the need for stopping and starting the module for each run, and an improved method of generating testbenches that include all signals and desired testcases.

- A framework for architectural exploration of digital hardware has been developed. This framework can generate a large number of architectural variations with great diversity. Area, power and performance information will automatically be extracted from each design, allowing the designer to choose the best architecture for further implementation.

- Using a FIR-filter reference design, a proof of concept study has been conducted, showing that the framework can be used for architectural exploration of digital hardware.

- LegUp's usability in a framework for architectural exploration of digital hardware has been evaluated, based on results from the proof of concept study and the performance of the adapted version of LegUp.

# 1.5 Method

The work performed in this thesis is based on multiple research methods. Before the problem could be solved, a study of the architecture and structure of LegUp had to be conducted, to understand the connections and information-flow in the tool. This study was primarily carried out during the previous project [13], but also continued into the work with this thesis. A plan for how to resolve each of the issues at hand was devised and discussed before being carried out, to ensure a good solution. The problems at hand requires in-depth knowledge of the libraries in LegUp, but when the source of the issue had been located, fixing the issue was based on trial and error. By replacing a piece of code with some other solution, a new output can be generated and evaluated. This process is repeated until the issue is resolved. The creation of the framework is based on the idea proposed by Isael Diaz. A study of architectural

exploration and HLS-concepts had to be conducted before building the framework, to make sure the output would have the desired diversity. An experimental study of the usefulness of the created framework was conducted as a proof of concept, to check if the initial hypothesis holds. By running a reference design through the framework, a large amount of data was reported. The data was analyzed to draw the conclusion about the hypothesis.

# 1.6 Overview of the thesis

In general, this thesis is divided into 8 chapters, each presenting one or more of the project objectives described above, in addition to appendix. In chapter 2, the background and theory required to understand the rest of the thesis is described. Point one and two from the list above is described in chapter 3. Chapter 4 uses a design example to present a thorough description of the information-flow in LegUp and the other tools used in the framework. In chapter 5 the third objective, the process of creating a framework, is described. The fourth objective, to create a proof of concept, is presented in chapter 6. The evaluation of the proof of concept results, corresponding to the fifth objective, as well as a discussion of LegUp in general, with focus on its usefulness in the created framework, has been presented in chapter 7. Finally the work is summarized and concluded in chapter 8. Chapter 8 also include a section of future works, describing aspects that will be interesting to look into more detail at in an eventual continuation of this project. Appendix include code-listings of designs and implementations, that are described and discussed in the main chapters.

# Chapter Theory and background

Some theory and background is needed to get a thorough understanding of the material in the following chapters. Some parts of this background chapter were written as part of the specialization project [13], but it is included here to allow the report to be a freestanding document. Some sections have been extended to add a deeper level of understanding to some of the described concepts, compared to what was presented in the previous report. Some information from section 3.3 of the *Methodology*-chapter has also been included in section 2.6 of this report, as it describes part of the same tool-flow used here.

In the early days of digital hardware design, gate design and layout were performed by hand. With the rapid growth in the numbers of transistors per digital chip-design, this method quickly became too time-consuming and the need for new and more automated design methods rose. RTL-design using HDL has long been the standard in digital hardware design. With the increasing demand for low power and small area in large System-on-Chip (SoC) designs with multiple billion transistors, this methodology is no longer sufficient if hardware manufacturers want to hit the window of opportunity with their state-of-the-art product.

# 2.1 High-Level Synthesis

HLS is not a new concept as it was introduced in research papers in the late 1970s and further researched and developed in the 1980s and early 1990s [23]. The available commercial HLS tools have not been providing the necessary performance and benefits over HDL development for major hardware development companies to adapt this methodology until recently. The concept of HLS starts with a functional specification of the circuit described using a higher abstraction level, often a High-Level Language (HLL). A tool uses target architectural model libraries and design constraints to transform this specification into hardware, represented as a RTL or HDL-model. The typical HLS-flow is shown in figure 2.1 and each of the transition-steps is described in

#### 8 2. THEORY AND BACKGROUND

the below subsections. The input libraries contain information on available hardware resources with power, area, and delay models for the target architecture.

Figure 2.1: Information flow in a typical HLS-tool [8].

# Compilation

The first step of HLS is to compile the functional specification into a formal model. This model can vary between different tools, and can be either a specific representation language or a graphic representation of the flow. The formal model is decided by the developers of the HLS tool.

# Allocation

Necessary hardware resources, such as functional units, storage-, and connectivitycomponents needs to be selected from a given RTL component library in order to satisfy the specification and design constraints. Some HLS tools can also add more resources in the scheduling and binding tasks, if this is needed to meet given constraints.

# Scheduling

Scheduling arranges all operations in an optimized sequence so that variables are read from sources and brought to the input of the correct functional unit for execution and to the destination afterwards. The scheduler takes all dependencies into account when scheduling the operations, in order to get the most efficient result, as some operations can be executed in parallel if no dependencies exist and there is available resources. Operations can be scheduled to finish in one, or take multiple clock-cycles, and operations can also be chained to eliminate the need for storing the result between operations, and to reduce the total number of cycles needed.

# Binding

In the binding task, all clock-cycle-crossing variables, operations, and transfers are bound to a free resource, in the time-frame when it is scheduled. Non-overlapping or mutually exclusive variables can be bound to the the same storage unit, and operations can be bound to the best optimized functional unit if multiple alternatives are available. Each transfer from component to component, either storage or functional unit, needs to be bound to a connection unit, such as a bus or a multiplexer.

## **RTL** Generation

The generated RTL usually consists of two parts, a control-unit and a data-path-unit. The control-unit is often implemented as a Finite State Machine (FSM), which set control-signals to the data-path, and controls the current and next-state of the system. The data-path contains storage-, functional-, and connection-units. An example of this division is shown in figure 2.2. Depending on the intensiveness of the binding

Figure 2.2: Typical division of control and data-path in the generated RTL from HLS.

step, the output RTL can be tightly or loosely bound to the available resources. If an operation is not bound to a specific unit, it is up to the following logic synthesis of the RTL to bind the operations to available resources. The different types of RTL output are illustrated by the following example. a = b \* c executing in state n:

## Without any binding:

state (n): a = b \* c; go to state (n + 1);

# With storage binding:

state (n): S(1) = S(2) \* S(3); go to state (n + 1);

## With functional-unit binding:

state (n): a = MUL1 (b, c); go to state (n + 1);

## With storage and functional-unit binding:

state (n): S(1)=MUL1 (S(2), S(3));

go to state (n + 1);

## With storage, functional-unit, and connectivity binding:

```

state (n): BUS1 = S(2); BUS2 = S(3);

BUS3 = MUL1 (BUS1, BUS2);

S(1) = BUS3;

go to state (n + 1);

```

A loosely bound RTL gives the synthesis-tool the flexibility to optimize the unit binding to updated timing estimates, delays, and loads given by the layout and floor-planning tools.

# 2.2 LegUp

The HLS tool used in this project is called LegUp [6]. LegUp is an open-source academic tool developed at the University of Toronto, Canada. LegUp's goal is to "allow researchers to experiment with new HLS algorithms without building a new infrastructure from scratch" and their long-term vision is to "make FPGA programming easier for software developers" [4]. LegUp takes American National Standards Institute (ANSI)-C as input and generates synthesizable Verilog HDL as output. The developers of LegUp have primarily focused on support for a variety of FPGA boards from manufacturer Altera, but in the latest version (4.0), beta support for Xilinx devices [20] and possibility to configure the tool to generate generic Verilog to target other FPGA vendors or even ASIC through use of generic dividers [18], has been introduced. The big advantage of LegUp compared to similar, commercial tools, is that it is open-source and therefore can be configured to target different

architectures. The RTL and HDL generating part of the tool can be modified or replaced to fit the programmers needs. Since LegUp, in its unmodified form, target FPGA devices, it supports three different synthesis flows; pure-Software (SW), hybrid, and pure-Hardware (HW). The two first synthesis flows will implement a TigerMIPS [24] soft processor, which will run part of the C code. The partitioning of SW and HW in the individual modules are described in table 2.1. It is the pure-HW flow that will be the focus of this project.

| Flow    | Functions run in hardware                | Functions run in software |

|---------|------------------------------------------|---------------------------|

| Pure-SW | None                                     | All                       |

| Hybrid  | Specified hardware-accelerated functions | All other functions       |

| Pure-HW | All                                      | None                      |

Table 2.1: HLS-flows supported by LegUp and partitioning between SW and HW

# 2.2.1 Producing Verilog Output

LegUp is made up of two components; a frontend pass and a target backend pass to the LLVM compiler infrastructure. The information flow in LegUp, shown in figure 2.3, follows the same principle as the information flow described in section 2.1. The LegUp LLVM frontend takes LLVM Intermediate Representation (IR) compiled

Figure 2.3: Information flow in LegUp [19].

by clang, a C frontend for LLVM, as input and links in custom written functions like memcpy, memset and memmove, which do not exist in hardware, but that LLVM assumes exist in the C library. The LegUp backend pass performs allocation, scheduling and binding as described in section 2.1. In the next step, RTL-module objects that represents the final hardware circuit are generated from each LLVM

#### 12 2. THEORY AND BACKGROUND

instruction. Ultimately, Verilog code corresponding to each of the RTL-modules is output to a file.

The allocation, scheduling, and binding in LegUp is performed based on information about available resources and timing information about the specified target FPGAboard, in addition to user-defined constraints and setting. The available information about the FPGA-boards allows for precise scheduling and binding to the available resources. Since the implementation of ASIC designs are quite different from the architecture and implementation of designs on FPGAs, the resource and timing information will not be as easily obtained for the target architecture.

# 2.2.2 Classes

In LegUp there are some predefined classes that is important for the understanding of the description of adapting LegUp, presented in chapter 3. The following subsections will describe some important information about these classes in more detail. The full class descriptions can be found in the LegUp Namespace Reference [9].

# RTLModule

The RTLModule class models a hardware RTL module. The class stores information about all ports (inputs and outputs), signals, parameters and sub-modules. Each function declared in the C-code transforms into a RTLModule object. Each function that is called from the function will be added as a sub-module to the RTLModule object, meaning a module instantiation will be added to the module. Important member-functions of the RTLModule class are:

## getName()

Returns a string containing the name of the RTLModule, i.e. "main" for the module generated by the *main*-function in the C-program.

# find(std::string signal)

Takes a string containing a signal name as parameter and returns a pointer to the RTLSignal in the RTLModule with that name.

# addParam(std::string name, std::string value)

Adds a parameter to the module. The function returns a pointer to the generated RTLSignal object.

# addIn(std::string name, RTLWidth width)

Adds an input-port to the module. The function returns a pointer to the generated RTLSignal object.

# addOut(std::string name, RTLWidth width)

Adds an output-port to the module. The function returns a pointer to the generated RTLSignal object.

## addRegOut(std::string name, RTLWidth width)

Adds a registered output-port to the module. The function returns a pointer to the generated RTLSignal object.

# addReg(std::string name, RTLWidth width)

Adds a register signal to the module. The function returns a pointer to the generated RTLSignal object.

# addWire(std::string name, RTLWidth width)

Adds a wire signal to the module. The function returns a pointer to the generated RTLSignal object.

## addModule(std::string name, std::string instName)

Adds an instantiation of another module to the module. The function returns a pointer to the generated RTLModule object.

# RTLSignal

The RTLSignal class represents the signals within an RTLModule. Both internal signals, port signals and condition signals are all modelled using the RTLSignal class. Important member-functions of the class are:

# getName()

Returns a string containing the name of the RTLSignal, i.e. "clk" for the clock signal.

# getType()

Returns a string describing the signal type. The type can be *reg*, *wire*, *input*, *output*, or *output reg*.

## getNumDrivers()

Return the number of driving RTLSignals.

# getDriver(unsigned i)

Returns a pointer to the i-th driving RTLSignal.

## getCondition(unsigned i)

Returns a pointer to the condition signal of the i-th driving RTLSignal.

## addCondition(RTLSignal \*cond, RTLSignal \*driver)

Adds a conditional driver. If the RTLSignal *cond* is true, the RTLSignal *driver* drives the signal.

# connect(RTLSignal \*s)

Connect this signal unconditionally to another RTLSignal.

## getWidth()

Returns a pointer to a RTLWidth object, describing the width of the RTLSignal. isOp()

Returns true if the RTLSignal is an RTLOp object.

#### 14 2. THEORY AND BACKGROUND

# RTLOp

The RTLOp class is a subclass of the RTLSignal class, representing an operation with one, two or three operands. Each operand is a RTLSignal. The operation can be an arithmetic operation like addition, subtraction, multiplication, or division, and it can also be logical operations like AND, OR, and XOR, or even comparison operations like equal, not equal, less than, less than or equal, greater than, and greater than or equal. The whole list can be seen in the class reference [10]. A RTLOp object modelling an AND operation of two operands, operand1 and operand2, will in Verilog correspond to the operation "operand1 & operand2". Some important member-functions are:

# getOperand(int i)

Returns a pointer to i-th operand of the RTLOp object.

# getNumOperands()

Returns the number of operands of the RTLOp object.

# setOperand(int i, RTLSignal \*s)

Sets the i-th operand to the RTLS ignal  $\boldsymbol{s}.$

# RTLWidth

The RTLWidth class represents the bitwidth of a RTLSignal. An RTLWidth is defined by high and low bits, for instance 31,0 for a 32 bit signal. This will transform into "[31:0]" in Verilog.

# RAM

The RAM class models RAM modules in LegUp. Whenever a variable is loaded or stored, a RAM module is generated to handle the loads and stores. The RAM objects can be divided into two scopes; LOCAL and GLOBAL. A local RAM object is local to a given function and cannot be accessed by other functions. A global RAM object will be implemented in a global memory controller. All modules that use the variable can connect to the RAM via the memory controller. Some important member-functions are:

# getName()

Returns a string containing the name of the RAM module, i.e. "main\_0\_1" for the RAM module generated for the first parameter to the main function declared as volatile (output parameters) in the C-code.

## isROM()

Returns true if the RAM is read-only.

# getScope()

Returns if the RAM is in the local or global scope.

#### 2.2.3 Constraints

Constraints is an important part of LegUp, and it is also used extensively in this project. The constraints are used for setting design goals and limitations on design, and to specify how the HLS-flow will be executed. Constraints play an important role in this concept, as the idea is to generate multiple designs that can be compared in terms of area, performance, and power consumption. For the designs to be different, varying constraints are used for generating the designs. All available constraints are described in the constraint manual [17], but the ones used in this project are described in table 2.2. Some constraints are considered *required*. These constraints must be set for the generated design to be compatible with the tool-flow. *HLS constraints* are used for getting different Verilog-outputs from LegUp. Other constraints from the constraint manual can also be used, but these were selected for this project as their description indicate that they can affect the architecture of the output.

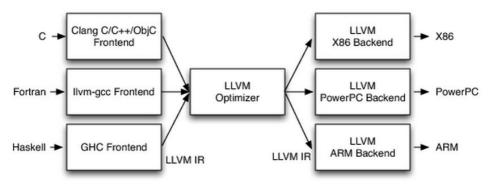

## 2.3 LLVM

LLVM [16], formerly Low-Level Virtual Machine, is a compiler framework that was originally developed as a research infrastructure to investigate dynamic compilation techniques for static and dynamic programming languages, at the University of Illinois in 2000. It is now a open-source project with many contributors from both industry, research groups and individuals, and it is used by companies like Apple in their Xcode Integrated Development Environment (IDE) [21] and Sony for their PS4 developer toolchain [28]. LLVM support a large number of frontends for programming languages, including Clang [7] which support C, C++, Objective-C, and Objective-C++, and is compatible with GNU Compiler Collection (GCC). It also supports a large number of backend target architectures. Figure 2.4 shows how different source languages can be input to the frontend compilers of LLVM, which translate the source into an IR. The IR is then optimized using LLVM's optimizer. At this stage, different source languages can be linked together, and even object files compiled using standard GCC can be linked at this stage. The optimized IR is then translated into the target architecture by the backend.

#### 2.3.1 Intermediate Representation

LLVM use a human readable, assembly-like, strongly typed RISC instruction set as the IR, with support for an infinite number of temporary registers of the form %0, %1, etc. LLVM can also output a dense bitcode format of the IR for serialization. Conversion between the bitcode-format and the human-readable format, and vice versa, can be done with the commands "llvm-dis" and "llvm-as", for dis-assembly and assembly.

DUAL\_PORT\_ BINDING

| Required constraints       |                                                                                                                                  |                |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|

| Parameter name             | Description                                                                                                                      | Required value |  |  |

| DIVIDER_MODULE             | Use generic divider module rather than <i>generi</i><br>Altera primitive                                                         |                |  |  |

| EXPLICIT_<br>LPM_MULTS     | Use Altera primitive multiplier rather than $0$ Verilog multiply operator (*)                                                    |                |  |  |

| INFERRED_RAMS              | Use Verilog inferred RAMs rather than 1<br>Altera altsyncram modules                                                             |                |  |  |

| INFERRED_<br>RAM_FORMAT    | Select format of inferred RAMs. Altera:<br>multiple always blocks, Xilinx: same al-<br>ways block                                | xilinx         |  |  |

| LOCAL_RAMS                 | Infer all RAMs as local RAMs rather than<br>global RAMs. RAMs being accessed by<br>multiple functions will override this setting | 1              |  |  |

| VSIM_NO_ASSERT             | Disable triple-equality assertions. This causes simulation to fail                                                               | 1              |  |  |

|                            | HLS constraints                                                                                                                  |                |  |  |

| Parameter name             | Description                                                                                                                      |                |  |  |

| SDC_NO_CHAINING            | Schedule each operations into a separate cl                                                                                      | ock cycle      |  |  |

| MB_MINIMIZE_HW             | Run LegUp-pass that tries to minimize signal sizes                                                                               |                |  |  |

| CASE_FSM                   | Use case-statements in FSM rather than If-Else                                                                                   |                |  |  |

| PIPELINE_ALL               | Enable pipelining for all loops, regardless of loop-label                                                                        |                |  |  |

| ENABLE_<br>PATTERN_SHARING | Turn on resource sharing for patterns in Data-Flow<br>Graph (DFG)                                                                |                |  |  |

#### **Required constraints**

Table 2.2: Description of constraints used in this project

Use dual-ported on-chip memories

Figure 2.4: LLVM's three-phase compiler structure [15].

Some parts of the LLVM IR will be described in chapter 4. The whole language is too large to be fully explained here, but interested readers can read more about the syntax in the *LLVM Language Reference Manual* [14].

## 2.4 Alternative hardware design methods

HLS is not the only alternative to HDL-languages, if you want to design digital hardware at a higher level of abstraction. The following subsections will shortly describe two alternative approaches to digital hardware design.

#### 2.4.1 Chisel

One interesting approach to designing hardware with a higher level of abstraction, is the Chisel Hardware Construction Language (HCL) [2], developed at UC Berkeley. HDL languages like VHDL and Verilog, were originally designed as simulation languages and later adopted as a basic for synthesis. Chisel, on the other hand, was created as a HCL and is thus *synthesizable by construction*. This entails that no conversion from C, or other HLL, into gates is performed, only generation of generic low-level Verilog with no overhead. Chisel is a Domain Specific Language (DSL) built on Scala [25] with its own syntax, but Scala syntax can also be used to get even greater abstraction in your design. A big advantage using Chisel is its high simulation speed, using C++-based cycle-accurate software simulators.

#### 2.4.2 Functional programming

Functional programming is a relatively different method of hardware design, as it consists only of mathematical functions and immutable data. Two examples of hardware design using functional programming is  $C\lambda$ aSH [1] and Lava [3]. Both Lava and  $C\lambda$ ash are compilers for the functional programming language Haskell [12], but while Lava is an embedded DSL like Chisel, with its own syntax,  $C\lambda$ ash use Haskell syntax and semantics, and use a static analysis approach towards synthesis.

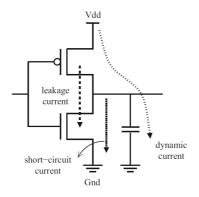

## 2.5 Power dissipation in CMOS circuits

The power dissipation in CMOS circuits can be divided into three categories [26], *dynamic power, short-circuit power* and *leakage power*. This gives a total power dissipation of:

$$P_{total} = P_{dynamic} + P_{short-circuit} + P_{leakage} \tag{2.1}$$

Figure figure 2.5 shows the distribution of the power components of the CMOS circuit. Each component is described in more detail in the following subsections, where *switching power* corresponds to  $P_{dynamic}$ , *internal power* corresponds to  $P_{short-curcuit}$ , and *leakage power* to  $P_{leakage}$ .

Figure 2.5: Power dissipation components distribution [26].

#### 2.5.1 Switching power

Whenever a signal changes the logic state from 0 to 1, the load capacitance is charged by the power supply. The power dissipated during this process is called *switching power*. Half the energy drawn from the power supply needed to charge the capacitance, is dissipated as heat in the process. The *switching power* depends on the frequency of the switching, the switching factor of gates, and the load capacitance, in addition to the supply voltage.

#### 2.5.2 Internal power

The *internal power* is the power used to charge and discharge the internal capacitance of the circuits, whenever a pin changes its logic state. A large part of the *internal power* is the short-circuit power. In the short time when both the pMOS and nMOS transistor of the CMOS circuit is *on*, a current will be drawn from the source  $V_{dd}$  to *Gnd*, through the short-circuit that will occur.

## 2.5.3 Leakage power

Whenever the circuits are turned *on*, a small leakage current will be drawn from the gates. The leakage power is mostly caused by sub-threshold currents and reverse biased diodes in the circuits. The leakage current increase when the technology shrinks, making leakage a bigger problem today than before.

## 2.6 Tool-flow

This section will describe all the tools that are used throughout this thesis, as well as the connection and data-flow between the different tools. This flow is based on the standard tool-flow used at Nordic Semiconductor, and it include some parts adapted from the "*automated area and power estimation tool-flow*" created by Joar Talstad for his Master thesis [35]. Most of the tool-flow is based on scripts and Makefiles that can be run from a Linux shell, but there are also some GUI-tools available that will be mentioned briefly in chapter 4. The following subsections will describe the different sections of the tool-flow in detail. The flow in LegUp will not be described here, as this is covered above and will be presented in more detail in chapter 4.

## 2.6.1 Simulation

Simulation is run to verify the correctness of a design and to help detect and eliminate potential bugs. In this project, the simulation tool also generates a Value Change Dump (VCD)-file, designname.vcd, showing switching activity during simulation. This file is used in the power analysis tool later in the flow, to get a realistic input of the amount of switching in the design. Simulation is performed using the tool ModelSim for Questa-64, version 10.2b 2013.05 [11]. Simulation is executed by calling the script  $RUN\_ALL$ . The RTL-design filelist and a file containing a testbench module must be specified in the filelist found in the sim/tb/-directory. This is used as input to the simulation tool.

## 2.6.2 Synthesis

Synthesis translates a RTL-design written in a HDL-language, like Verilog or VHDL, into a netlist for a specified target library. The tool used for synthesis in this thesis is

#### 20 2. THEORY AND BACKGROUND

Synopsys Design Compiler, version I-2013.12-SP2 [32]. A cell library describing 180nm technology is used as the target architecture. A Makefile is used to start synthesis, and the command make compile runs the full synthesis. The netlist generated by synthesis is found in the file *designName.mapped.v* in the *result*-directory. This netlist is used as input for the layout-tool. Synthesis generate reports showing area-estimates, register count, critical path and static power estimates for the design. As the design will be processed further through the tool-flow, these reports are not that accurate and hence not that useful.

## 2.6.3 Layout

Layout translates the netlist generated during synthesis into a chip layout. The tool used for layout in this project is Synopsys IC Compiler, version L-2016.03-SP1 [33]. A Makefile is used to start layout, and the command make outputs\_cts runs the correct layout-script. Layout produces a new netlist-file, stored in the file designName.output.v in the result-directory. This netlist is used in the power analysis tool for estimating power consumption. Layout generate reports about area and critical paths, stored in the reports-directory. These results are more accurate, as they were gathered from the actual chip layout.

## 2.6.4 Power analysis

Power analysis is performed to get an early indication on how much power the final chip will be consuming. The tool used for power analysis in this thesis is Synopsys Primetime, version K-2015.12-SP3. To get accurate power estimates, the switching activity file generated during simulating is used together with the netlist output from layout. The conclusion from [35] was that this method provides accurate results and is well suited for making RTL-design trade-offs based on power consumption in multi-voltage designs. Power analysis is run on five different power scenarios, each giving a separate result for each of the three power dissipation categories described in section 2.5. The reports are stored in the *reports*-directory.

## 2.7 Reference design

This thesis will look into whether or not LegUp can be used as the HLS-tool in a framework for architectural exploration of hardware. In order to get some output from LegUp that can be compared towards each other, a reference design must be created. The design will be used in the proof of concept, described in chapter 6, and should be something that can be implemented both in C and Verilog. The design should also be simple to implement and verify. In [13], two reference designs were implemented; a FIR-filter and a SAP-1 architecture. The FIR-filter will be used as the reference design in this project, as this is a regular structure that easily can be

implemented and verified. The SAP-1 architecture would have been a interesting second reference design, as it consists of a FSM, just like the output from LegUp. Unfortunately, this architecture has too many design-parts that will be incompatible with the framework. It has therefore been decided to leave this design out of this thesis.

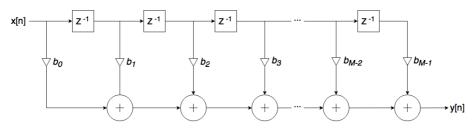

#### 2.7.1 FIR-filter

Finite Impulse Response (FIR)-filters are together with Infinite Impulse Response (IIR)-filters, the two categories of linear time-invariant systems, used in digital signal processing application. The impulse response of a FIR-filter is zero outside some finite time interval. A general FIR-filter can be described by the differential equation [27]:

$$y(n) = \sum_{k=0}^{M-1} b_k x(n-k)$$

(2.2)

or by the system function:

$$H(z) = \sum_{n=0}^{M-1} b_n z^{-n}$$

(2.3)

The impulse response for a FIR-filter is given by:

$$h(n) \triangleq \begin{cases} 0, & n < 0 \\ b_n, & 0 \le n \le M - 1 \\ 0, & n > M \end{cases}$$

(2.4)

From eq. (2.2) and eq. (2.4) we get the discrete convolution equation:

$$y(n) = \sum_{k=-\infty}^{\infty} h(k)x(n-k) \triangleq h(n) * x(n)$$

(2.5)

Figure 2.6 shows the direct form representation of a N-order FIR-filter with N + 1 taps. The figure shows that a FIR-filter requires N memory elements, N adders and N + 1 multipliers.

Even though the process of designing a FIR-filter might not be a trivial task, the implementation of an already designed filter is simple. As seen from eq. (2.5), the filter can be described by the convolution formula, which implies that the filter can be implemented as convolution of the input function x(n) with the impulse response function h(n).

## 22 2. THEORY AND BACKGROUND

Figure 2.6: Direct form representation of a N-order FIR-filter.

# Chapter Adapting LegUp

The main focuses of this thesis has been to resolve the issues encountered in [13], to make LegUp able to generate Verilog more suited for ASIC implementation and synthesis. This chapter will describe the process of resolving these issues and other alterations that have been added to simplify the creation of a framework for architectural exploration of hardware.

## 3.1 Approach

In the future works section of [13], two different approaches to resolving the issues were proposed; post-processing and pre-processing. Both approaches have been explored, but the majority of solutions are based on the pre-processing alternative. The two following subsection will present the two approaches and give some reasoning to why one is preferred over the other.

#### 3.1.1 Post-processing

With the post-processing approach, the idea is to alter the Verilog-code after it is generated, to make it more suitable for ASIC implementations. This approach is easy to work with, as we can concentrate on a single file, the output Verilog file. The drawback of this approach is that you only have the information available in the Verilog file at hand, making it hard to add functionality to the tool.

There exist multiple parser tools for Verilog, for instance Verilog-Perl from VeriPool, a Verilog parser library for Perl [30], and pyverilog, a Hardware Design Processing Toolkit for Python [34]. These tools can be used to parse the Verilog file, to build module, signal, and port hierarchy, and easily add, alter, or remove objects.

## 3.1.2 Pre-processing

The pre-processing approach involves changing the libraries in LegUp that perform HLS operations like allocation, scheduling, RTL-generation and Verilog printing. This requires deep knowledge of the libraries and its connections, to find a good way to change the output. The large libraries is the main drawback of this approach. As LegUp is open-source, the possibilities of this approach are endless, but getting the necessary knowledge of the libraries takes time.

## 3.1.3 The used approach

As it looked like the easiest solution, the post-processing alternative was explored first. However, it was soon realised that the things that could be done easily with this approach, also could be done quite easily with the pre-processing approach. Some larger issues, for instance assigning values to outputs, were not easily solvable using the post-processing method. The focus was therefore directed towards the pre-processing alternative. One advantage of this approach is that the original functionality of LegUp can be kept, while adding new functionality. The switching between original and altered versions are done using TCL-parameters. The postprocessing method was used at a later stage, but then on the LLVM IR-code rather than the generated Verilog.

## 3.2 TCL commands

LegUp uses TCL commands for setting constraints and configuring the HLS-flow. In order to keep the original implementation of LegUp, and to provide additional functionality, some new commands were added. New TCL-parameters can easily be added to LegUp by adding the parameter name to the array *validParameters* and increasing the parameter *NUM\_PARAMETERS* in the file *LegupConfig.cpp*. The value of the parameter can then be read using the function call:

#### LEGUP\_CONFIG->getParameter("parameterName")

to get a string, or

#### LEGUP\_CONFIG->getParameterInt("parameterName")

to get an integer. *LegupConfig.h* must be included to get access to LEGUP\_CONFIG. The most common use of TCL-parameters is to check whether a parameter is set, and perform some action based on this. Parameters can also be used to set values of variables. An example could be a parameter that decides if a designated top-module will be generated or not.

The parameter is defined by adding the following code to the constraint file:

set\_parameter PRINT\_TOP\_MODULE 1

The parameter can then be used to decide if the top-module should be printed:

```

if(LEGUP_CONFIG->getParameterInt("PRINT_TOP_MODULE") {

printTop();

} else {

printVerilogWithoutTop();

}

```

Another example is to use a parameter to set the name of the top-module. This can be used for naming the top-module, or to select top-module in the simulation-settings.

set\_parameter TOP\_MODULE\_NAME "moduleName"

```

1 std::string topModuleName = "top"; // Default name

2 if(LEGUP_CONFIG->getParameter("TOP_MODULE_NAME") {

3 topModuleName = LEGUP_CONFIG->getParameter("TOP_MODULE_NAME");

4 }

```

In the second example, the *getParameter()* function will return false if the parameter is not set.

Other TCL-commands can also be defined by adding the following line to the file *LequpTcl.cpp*:

```

1 Tcl_CreateCommand(interp,

2 "set_custom_main_function",

3 set_custom_main_function,

4 legupConfig,

5 0);

```

Here the second parameter is the TCL-command and the third parameter is the handler function that will be called when the TCL-command is encountered. In the handler function, arguments from the constraint file can be used to configure LegUp. As multiple arguments are supported, more advanced configurations can be performed with this alternative. The parameters that has been added to LegUp is described below.

#### ASIC\_IMPLEMENTATION

This parameter is used to distinguish between the original version of LegUp and the altered version developed in this thesis. If this parameter is set, all

#### 26 3. ADAPTING LEGUP

extra features described in the following subsections will be applied to the generated design. If the parameter is not set, the unaltered edition of LegUp will be used to generate the output.

#### $set\_custom\_main\_function$

This parameter can be used to define inputs and outputs in the *main*-module, as described in section 3.5.2. As this is not a simple TCL-parameter, it takes multiple arguments. The format of the input should be:

portDirection portSize portName

An example of declaring two inputs and two outputs in the *main*-module could be:

```