# Improving the energy efficiency of a microcontroller instruction fetch using tight loop cache

Maja Popovic

Embedded Computing Systems Innlevert: juli 2015 Hovedveileder: Donn Morrison, IET Medveileder: Marius Granaes, Silicon Labs

Norges teknisk-naturvitenskapelige universitet Institutt for elektronikk og telekommunikasjon

# Improving the energy efficiency of a microcontroller instruction fetch using tight loop cache

Maja Popovic

Electronics System Design and Innovation Date of submission: July 2015 Supervisors: Donn Morrison Marius Grannaes

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# **Problem Description**

Recently there has been a lot of effort in making the Internet of Things (IoT) a reality. A central component of this vision is to make low power edge sensor nodes (i.e., nodes with few connections that are not used to route data) in a mesh network. Such systems are often composed of a low power microcontroller coupled with a low power radio operating at low speeds with long duty cycles. A lot of research has been conducted with regards to reducing the power consumption of these systems.

A significant portion of the energy is used for fetching instructions from flash. In some low-power microcontrollers a small cache is used to exploit temporal locality in the instruction stream. Energy is saved, because SRAM used in caches require less energy than flash.

Cache is a very old and well known technique to exploit such differentials in speed/energy. This master thesis will build on the tight loop cache approach, use software simulations to evaluate if it can be used in an application to save energy, proceed to its hardware design and implementation and compare results.

Master thesis was done in collaboration between the CARD group and Silicon Labs, where Marius Grannæs was a co-supervisor.

### Abstract

Energy efficiency in microcontrollers has played an important role in modern digital systems for years. With the increased need for longer battery life and increased complexity of functionalities offered, it becomes crucial to lower energy consumption as much as possible. Studies show that largest amount of energy in embedded systems gets consumed by the memory hierarchy system. Therefore there has been a lot of research pressure in the area of caching techniques with the attempt to reduce energy requirements and thus make battery life longer. Some of these techniques were studied and analyzed in author's Semester Project whereas one of them, called Tight Loop Cache, was chosen to be implemented and evaluated as the most promising when power optimization is concerned. TLC is different from conventional caching techniques because it does not include tagging of cache lines nor valid bits which makes it more attractive and easy to incorporate into a working system.

The technique was implemented both in software (Python) and hardware (Verilog) and later evaluated by counting parameters close to meanings of cache hits and misses. These parameters were then used to calculate power consumption of the system without making use of the technique and with incorporating the technique.

Software simulations showed that using TLC of size only 64B brings benefits of power savings from 10% up to 80% for some benchmarks (taking into account only the memory system consumption). Relying on these encouraging results, the technique was implemented in hardware, synthesized on Xilinx Zynq-7000 and evaluated using power reports generated by VIVADO Design Suite. Hardware implementation was built around ARM Cortex-M0 and included the design of main instruction memory, TLC Controller and tight loop cache itself.

Post implementation power reports showed that the use of TLC of 64B can bring around 25% of power savings into a system working on 10 MHz and synthesized with FPGA fiber. It is believed that, if implemented as an ASIC with completely configurable and controllable synthesis and place and route tools, the design would bring even more power savings than in the case of using a Zynq-7000.

# Preface

This thesis was submitted to the Norwegian University of Science and Technology for fulfilling final requirements for a master's degree. The work has been conducted at the Department of Computer and Information Science, NTNU, Trondheim with Donn Morrison as a supervisor in a collaboration with company Silicon Labs from Oslo with Marius Grannaes as a co-supervisor.

#### Acknowledgements

I would like to thank both my supervisors, Donn Morrison and Marius Grannaes, for guiding me, giving support and new ideas even while being on holidays! Weekly meetings with Donn helped me a lot to get organized and get the feeling of time management importance, whereas Marius's vast knowledge of software compilation and EFM32 in general, discarded any doubt that crossed my mind.

Special thanks to Donn and hardware supply management at NTNU for ordering all the hardware support needed for this thesis to be successfully fulfilled.

# Contents

| Problem Descriptioniii                                      |

|-------------------------------------------------------------|

| Abstractiv                                                  |

| Preface                                                     |

| Contentsvi                                                  |

| List of Figuresviii                                         |

| List of Tablesx                                             |

| List of Abbreviationsxi                                     |

| 1 Introduction                                              |

| 1.1 Energy Efficiency and Microcontrollers 1                |

| 1.2 Thesis Overview and Main Contributions                  |

| 2 Background and Related Work                               |

| 2.1 Related Work                                            |

| 2.1.1 Filter cache                                          |

| 2.1.2 Predictive Filter Cache                               |

| 2.1.3 Loop Cache                                            |

| 2.1.4 Tagless Hit Instruction Cache5                        |

| 2.1.5 History Based Tag Comparison Cache                    |

| 2.1.6 Horizontal Cache Partitioning with Gray encoding5     |

| 2.2 Tight Loop Cache                                        |

| 2.3 Software System Background9                             |

| 2.4 Hardware System Background11                            |

| 2.4.1 Cortex-M0                                             |

| 2.4.2 AHB bus                                               |

| 2.4.3 Simulating the Cortex-M0 core                         |

| 2.4.4 Running the core with Instruction Memory on FPGA [18] |

| 2.4.5 System Design Flow and Power Optimization             |

| 3 Tight Loop Cache Implementation                           |

| 3.1 TLC in software            |

|--------------------------------|

| 3.2 TLC in hardware            |

| 3.2.1 Adding Loop Cache45      |

| 4 Testing and Measurements     |

| 4.1 Software Implementation    |

| 4.1.1 Methodology              |

| 4.1.2 Results                  |

| 4.2 Hardware Implementation    |

| 4.2.1 VIVADO measurements      |

| 4.2.2 Real time measurements   |

| 5 Conclusion and Future Work75 |

| 5.1 Conclusion75               |

| 5.2 Future Work76              |

| References                     |

| Appendix A                     |

| Appendix B                     |

# List of Figures

| Figure 2.1 - sbb instruction format                                                 | 5 |

|-------------------------------------------------------------------------------------|---|

| Figure 2.2 – Loop cache organization and access [10]                                | 1 |

| Figure 2.3 - Loop cache controller state machine                                    | 3 |

| Figure 2.4 - Design of loop counter [10]9                                           | ) |

| Figure 2.5 – Address bus content in time                                            | - |

| Figure 2.6 - ARM Cortex-M0 block diagram [12]14                                     | ŀ |

| Figure 2.7- Cortex-M0 memory map [13]15                                             | , |

| Figure 2.8- Program Memory content [13]16                                           | 5 |

| Figure 2.9- Instruction byte order in memory [14]17                                 | 7 |

| Figure 2.10- Simulation of the loop execution                                       | 3 |

| Figure 2.11- Cortex-M0 pipeline stages[15]                                          |   |

| Figure 2.12- Cortex-M0 schematics[16]                                               |   |

| Figure 2.13 - Cortex-M0 access types[16]                                            | ; |

| Figure 2.14 - AHB-Lite block diagram [17]24                                         | ŀ |

| Figure 2.15- AHB Master interface                                                   | ŀ |

| Figure 2.16- AHB Slave interface                                                    | 5 |

| Figure 2.17 - AHB basic transfer: read and write [17]27                             | 1 |

| Figure 2.18 – ARM Design Start testbench deliverables: block diagram                | ; |

| Figure 2.19 – Core simulation results                                               | ) |

| Figure 2.20 – Block diagram of the system built for implementation on FPGA board 30 | ) |

| Figure 2.21 - Clock generation on zc702 Evaluation Kit                              | ) |

| Figure 2.22 – 7Series primitive elements: buffer and D flipflop                     |   |

| Figure 2.23 – SynqReset module block diagram                                        | 2 |

| Figure 2.24 – Constant2Pulse module block diagram                                   | ) |

| Figure 2.25 - Counter2Constant module block diagram                                 | ; |

| Figure 2.26 – Reset pulse generation: simulation                                    | ; |

| Figure 2.27 – Block RAM principle of operation                                      | ŀ |

| Figure 2.28 – Detector module interface                                             | 5 |

| Figure 2.29 – Generation of Detector signal: simulation                             | š |

| Figure 2.30 – Source code used in [18]                                              | 7 |

| Figure 2.31 – Translation from .c file to .coe file                                 | 3 |

| Figure 2.32 – IC Design general flow                                                    |

|-----------------------------------------------------------------------------------------|

| Figure 2.33 – Digital Design Flow                                                       |

| Figure 3.1 – Difference between data transaction and program jump with instruction      |

| addresses as inputs                                                                     |

| Figure 3.2 – Insertion of a pseudo state for data transaction detection                 |

| Figure 3.3 – Interface between the system and the user                                  |

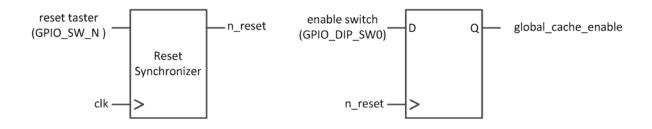

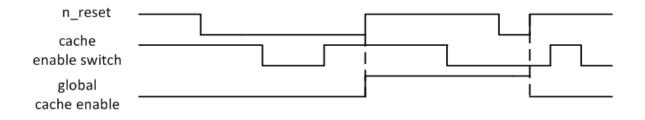

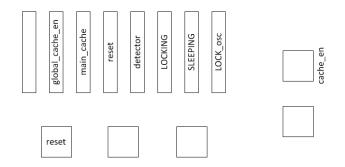

| Figure 3.4 – Generation of global_cache_enable signal                                   |

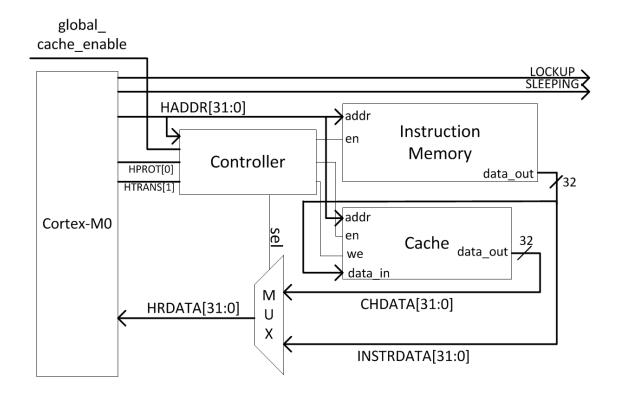

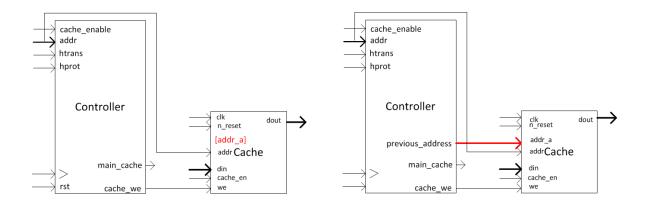

| Figure 3.5 – Introducing Loop cache into the core system                                |

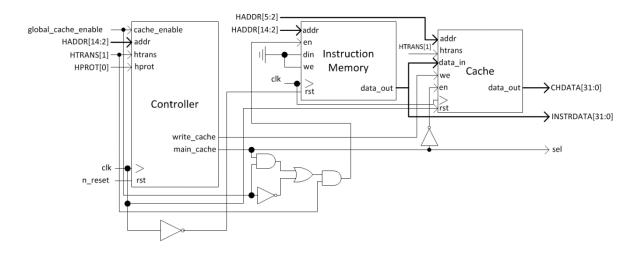

| Figure 3.6 – Interface between Controller, Instruction memory and Loop cache 48         |

| Figure 3.7 – Two different Loop Cache Controller implementations and their interfaces   |

|                                                                                         |

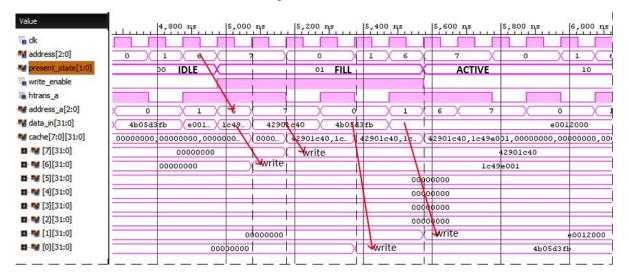

| Figure 3.8 – Timing comparison between two different controller implementations 50      |

| Figure 3.9 – Controller implementation, its state switching and control signal toggling |

|                                                                                         |

| Figure 3.10 – Controller State Machine with output control signals                      |

| Figure 3.11 – Filling of the Loop Cache55                                               |

| Figure 3.12 – Two different Controller-Cache implementations and interfaces             |

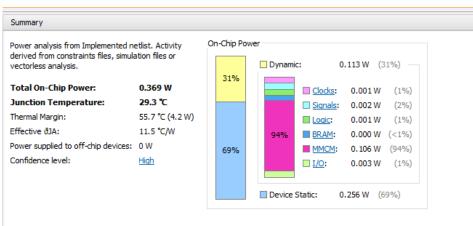

| Figure 4.1- Complete power report, VIVADO layout63                                      |

| Figure 4.2- Power report of the system with no memory hierarchy                         |

| Figure 4.3 – Design timing repor64                                                      |

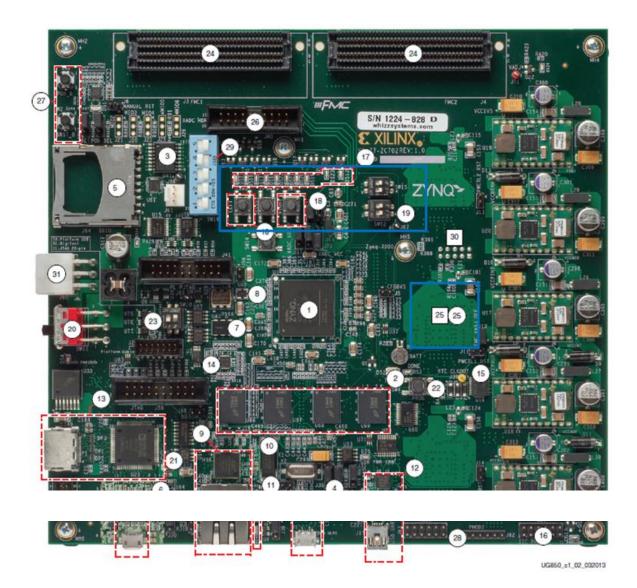

| Figure 4.4 - zc702 Evaluation Kit board layout [20]68                                   |

| Figure 4.5 - System user interface and output status (LEDs, switch and push buttons)    |

|                                                                                         |

| Figure 4.6 - Power domains on the ZC702[26]70                                           |

| Figure 4.7 – Format of a .csv file with real time measurements saved by TI FDPD 70      |

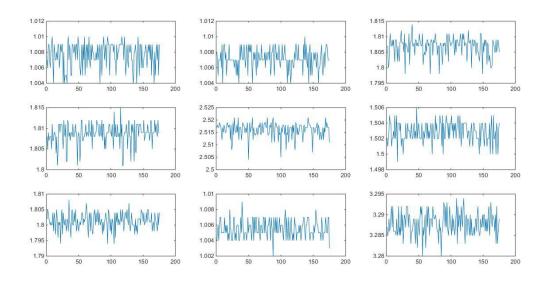

| Figure 4.8 - Real time voltage measurements for LEDs periodically ON and OFF            |

| (Matlab)72                                                                              |

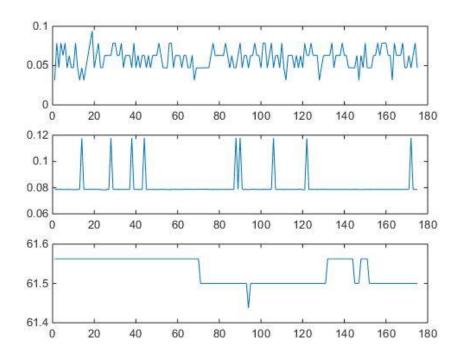

| Figure 4.9 – Real time power consumption for LEDs periodically ON and OFF72             |

| Figure 4.10 – Real time current measurements for LEDs periodicallt ON and OFF 73        |

# List of Tables

| Table 2.1- Cortex-M0 and Cortex-M3 specification comparison [12]                     |

|--------------------------------------------------------------------------------------|

| Table 2.2 – Branching instructions supported by ARMv6-M [14]                         |

| Table 2.3- Loop Instructions    19                                                   |

| Table 2.4- AHB Master output signals of interest                                     |

| Table 2.5 – C code variables and corresponding core registers                        |

| Table 3.1 - State switching mechanism with logical switching conditions and their    |

| implementations                                                                      |

| Table 3.2 – Controller output signals    54                                          |

| Table 3.3 – Instruction Memory Enable signal generation    54                        |

| Table 3.4 – Controller output signals (first version)    56                          |

| Table 3.5 – Utility reports of three different implementations of the Controller 57  |

| Table 4.1 – Simulation results for cache size 64B                                    |

| Table 4.2- Source code modification impact on program loop size    62                |

| Table 4.3 – Dynamic power reports after synthesis and after implementation using     |

| different toggling information (32KB Instruction Memory, 64B cache, loop size 8)62   |

| Table 4.4 – Power report generation details for different measurement configurations |

|                                                                                      |

| Table 4.5 – Different testing configurations                                         |

| Table 4.6 – Power and statistic reports for different system configurations          |

| Table 4.7 – Total and Vcc3V3 power consumption for 4 LEDs ON and OFF71               |

| Table 4.8 – Total power consumption (loop size: 8 instructions)                      |

# List of Abbreviations

| AHB         | Advanced High Performance Bus                   |  |  |  |  |

|-------------|-------------------------------------------------|--|--|--|--|

| ALU         | Arithmetic Logic Unit                           |  |  |  |  |

| AMBA        | Advanced Microcontroller Bus Architecture       |  |  |  |  |

| AP SoC      | All Programmable System-on-Chip                 |  |  |  |  |

| APB         | Advanced Peripheral Bus                         |  |  |  |  |

| <b>APSR</b> | Application Process Status Register             |  |  |  |  |

| CLB         | Complex Logic Block                             |  |  |  |  |

| COF         | Change of Flow                                  |  |  |  |  |

| CPU         | Central processing Unit                         |  |  |  |  |

| DCM         | Digital Clock Manager                           |  |  |  |  |

| EDA         | Electronic Design Automation                    |  |  |  |  |

| EFM32       | Energy Friendly Microcontroller 32b             |  |  |  |  |

| FPGA        | Field Programmable Gate Array                   |  |  |  |  |

| HADDR       | AHB address signal                              |  |  |  |  |

| HDL         | Hardware Description Language                   |  |  |  |  |

| HKMG        | High K Metal Gate                               |  |  |  |  |

| ISA         | Instruction Set Architecture                    |  |  |  |  |

| LUT         | Look Up Table                                   |  |  |  |  |

| LVDS        | Low Voltage Differential Signalling             |  |  |  |  |

| ММСМ        | Mixed Mode Clock Management                     |  |  |  |  |

| MSP         | Main Stack Pointer                              |  |  |  |  |

| NMI         | Non - Maskable Interrupt                        |  |  |  |  |

| NVIC        | Nested Vectored Interrupt Controller            |  |  |  |  |

| PLL         | Phase Locked Loop                               |  |  |  |  |

| РМВ         | Power Management Bus                            |  |  |  |  |

| PSP         | Process Stack Pointer                           |  |  |  |  |

| RISC        | Reduced Instruction Set Computer                |  |  |  |  |

| SAIF        | Switching Activity Interchange Format           |  |  |  |  |

| SBB         | Short Backward Branch                           |  |  |  |  |

| TH-IC       | Tagless Hit - Instruction Cache                 |  |  |  |  |

| TI FDPD     | Texas Instruments Fusion Digital Power Designer |  |  |  |  |

|             |                                                 |  |  |  |  |

TLC Tight Loop Cache

TNS Total Negative Slack

**WNS** Worse Negative Slack

**XDC** Xilinx Design Constraints

# 1 Introduction

#### 1.1 Energy Efficiency and Microcontrollers

There has always been conflict between low cost, high performance and low power consumption specifications in modern digital systems. MCUs are by far the best candidates to build systems targeting these applications mainly because they are self-contained: CPU, on chip SRAM, non-volatile flash memory and other peripherals are all integrated in one chip which consumes far less power than if all these components were used separately. Basic principle behind energy consumption minimization is to put MCU to sleep for as much time as possible, wake it up to perform a certain task as fast as possible and then put it back to sleep. There is no gain if a system consumes less power if it takes it much more time to complete the task (energy consumption is what actually matters at the end). Low power consumption not only brings energy savings, but it also improves system reliability as a whole by reducing heat dissipation. This way components have longer life expectancy because their temperature does not change rapidly, they operate on a stable temperature and therefore there is no need for large cooling systems.

In most digital systems, memory system consumes great part of the overall power consumption and this is why recently a lot of effort has been given to memory hierarchy design in a sense it consumes as little power as possible. Instruction memory access is one of the crucial points where these design modifications can be considered. The reason lays down in the fact that in a typical RISC ISA there are usually four times more instruction than data memory accesses [1]. Moreover, data is most commonly stored in SRAM whereas programs are stored in flash memory whose access infers much more energy consumption. These are all the reasons why it is believed that reducing instruction fetch energy consumption in systems like this would bring a great deal of overall energy consumption reduction.

Embedded application programs usually consist of small number of loops executed many times. It comes natural the thought it would be very efficient to read those instructions from a small buffer (small cache) and thus reduce energy consumption. Most common approaches that involve caching hierarchies put this buffer between CPU and main memory which usually infers time penalties whenever there is a cache miss. Other schemes involve accessing main memory in the same cycle if there is a miss but with the penalty of longer cycle time.

This project explores and implements, both in hardware and software, a caching technique that is believed to overcome both problems (longer cycle time and multiple cycle access) and offer great power savings. It involves using a tight loop cache and a loop cache controller as it will be explained in Chapter 2.2. This technique differs a lot from the original caching techniques (no tagging, no valid bits) and this is the reason why in this report not too much attention was given to basics of caching mechanism. The second reason lays down in the fact that basics of cache as well as other conventional and non-conventional techniques were covered in depth in the author's Winter Semester project and more details can be found there [2].

Since the thesis was a collaboration between NTNU and Silicon Labs, EFM32, MCU from Silicon Labs, was used as a starting point to choose the main processing core for the system to be built around. Nevertheless, TLC is processor independent and can be integrated into almost any modern system. Another reason why EFM32 was chosen was its energy friendliness and popularity amongst designers:

"In a market crowded with MCUs from larger vendors, Silicon Labs' EFM32 Gecko family merits a close look"[3].

#### 1.2 Thesis Overview and Main Contributions

Chapter 2First part of the Chapter describes some of the caching techniques explored<br/>in [2], both conventional and non-conventional ones. The purpose is to<br/>show how TLC compares with other techniques putting emphasis on both<br/>its simplicity and efficiency.

Second part explains the TLC technique the way it was originally proposed in [10].

Next section of the Chapter explains briefly what was done in the Semester Project and what the results and problems were.

The last section goes into detailed description of the ARM Cortex-M0 architecture, instruction set and its communication interface with other system components through AHB interface. It also gives overview of the design modules obtained from ARM as well as other hardware and

software sources found on the internet that were used to build a complete environment that could be tested and evaluated.

- *Chapter 3* Presents details of TLC implementation in software and hardware.

Software implementation includes modifications made to the simulator used in Semester Project with a new state machine employed.

Hardware implementation describes interfaces of building modules as well as details of their operation either in principle or by original simulation figures.

- Chapter 4 Presents experimental setup and results gained from performing different tests of both SW and HW implementations. Evaluation of HW implementation contains power reports obtained both form simulation (VIVADO) and real time measurements.

- *Chapter 5* Thesis ends with the summary of the delivered work and discussion about possible improvements that could be made to the system.

Through the work on the thesis, author made several achievements that can be regarded as a significant effort:

- 1. Detection of data transactions in the input benchmarks used in the software simulation

- 2. Software simulator [2] upgrade with the addition of pseudo states which enabled Controller ignore data transactions and thus bring more power savings

- Hardware implementation of TLC in Verilog and its integration into a system that uses ARM Cortex-M0 Design Start operating on 10 MHz with 32KB Instruction Memory

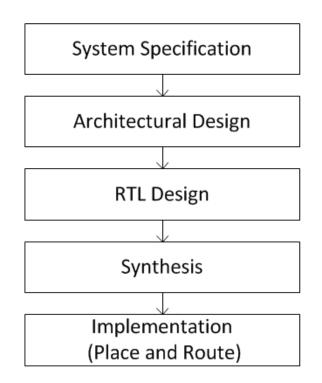

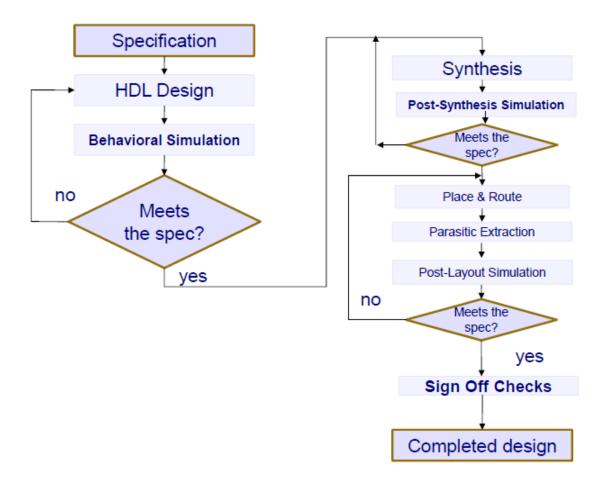

- 4. Exploration, description and application of synthesis and implementation power optimization design flow offered by VIVADO tools

# 2 Background and Related Work

First part of this chapter briefly mentions some of the caching techniques that were explored in author's semester project [2] before tight loop cache was chosen to be implemented and tested. Chapter content then continues to explain in details the tight loop cache technique and the environment that it was implemented on. It is supposed that the reader has knowledge of basics of cache but if that is not the case, more information before reading this Chapter could be obtained from [1] and [2].

#### 2.1 Related Work

#### 2.1.1 Filter cache

One of the first techniques that was proposed in [4] in order to bring power savings was involving insertion of a small, so called Filter Cache, which was communicating directly with the CPU. Although this brought great amount of power savings, it led to a slight performance degradation.

#### 2.1.2 Predictive Filter Cache

Tang, Gupta and Nicolau went further in [5] and tried to reduce this timing degradation introduced when there was a miss in the filter cache. Their strategy involved analysis of subsequent fetch addresses at runtime to predict whether next instruction was in the loop cache or not. If it was predicted to be a cache miss, the instruction was fetched from next cache level, bypassing filter cache (consuming more energy though in case the prediction was wrong but eliminating timing penalty in case it was true). The mechanism used to make the prediction was comparison of the tag of the current fetch and the tag of the predicted next fetch address: if they were the same it was predicted that the next fetch resided in the cache and vice versa.

#### 2.1.3 Loop Cache

Technique proposed in [4] was improved in [6] by Bellas, Hajj, Polychronopoulis and Stamoulis by enhancing both compiler and hardware properties of the system. The compiler not only selected which parts of the code to put into the cache but also did the code structuring to avoid instruction conflicts. Additional hardware included extra control to choose whether to access Loop Cache or Instruction Memory.

#### 2.1.4 Tagless Hit Instruction Cache

Another quite recently proposed technique that also tried to improve timing penalty of the basic caching idea from [4] was presented by Hines, Whalley and Tyson in [7]. They introduced the so called Tagless Hit Instruction Cache (TH-IC) which was placed as L0 (Level 0) cache between the CPU and L1 cache with a difference it was accessed at the same time as L1 cache but the instruction was read from L1 cache only when it was not guaranteed that it resided in the cache. By accessing both memories at the same time it was guaranteed that there was no timing penalty in case of a cache miss. Another big advantage over other techniques is the lack of need for storing tags for each cache entry since the technique itself already excluded tag comparison (that is where the name Tagless Hit came from).

#### 2.1.5 History Based Tag Comparison Cache

Authors in [8] aimed at lowering tag access energy by using the fact that cache hit rates are usually very high which means that data in the cache rarely gets changed and thus tag checks do not need to be performed if data in the cache had not been replaced. Only after there was a miss (data in the cache had been updated), tags needed to be compared in order to determine if the data still resided in the cache or not. The results showed that number of tag comparisons can be reduced by even 90% and this way bring great power savings.

#### 2.1.6 Horizontal Cache Partitioning with Gray encoding

A study about comparison of different cache techniques that was conducted by Su and Despain with results presented in [9], showed that, in general, whenever cache size increased missed rate decreased and that direct mapped caches saved more power but had larger access time than fully associative ones which was expected as well. It was also shown that when using sub-banking, larger blocks (containing entire loops in best case) bring more power savings, whereas Gray coding of memory addresses reduces bit switching up to 33% and thus brought even more energy savings.

There were more techniques explored in [2] apart from the ones mentioned in this chapter and one of them is the one that was chosen to be implemented and tested:

"After thorough analysis, taking into account the information that can be obtained from BRCHSTAT signal as well as the notion of the instructions that can be executed by the core,

some of the techniques from Chapter 2 were completely discarded and some were purposed for implementation. Technique that was regarded as the simplest, the most straight forward and with the least hardware control overhead was the one about Tight Loop Cache..." [2]

Next sub chapter explains the technique in details, the way it was originally purposed in [10], although when implemented in this project, both in hardware and software, slight modifications were introduced as it was already explained in [2].

#### 2.2 Tight Loop Cache

Tight Loop Cache, a technique proposed in [10] and chosen to be implemented in this project, consisted of a small direct map memory array and a loop cache controller. The advantage of using loop cache was double: it did not contain tag nor valid bit for each data instance. On the other hand, there was no timing penalty if there was a cache miss since the Controller had the early notion whether next fetch was going to be a hit or a miss. Based on this information, the core accessed either the loop cache or the main instruction memory.

General principle was based on the detection of the so called sbb (short backward branch) which, when encountered, indicated that a loop was executed for the second time, i.e. the moment when loop cache started to be filled. Next detection of the same sbb indicated the data was already in the loop cache and could be read from there.

Short backward branch instruction was any kind of branching instruction, both conditional and unconditional, that had the format as shown in Figure 2.1:

|        | upper        | lower        |

|--------|--------------|--------------|

|        | displacement | displacement |

| opcode | 11 11        | XX XX        |

|        |              | w bit wide   |

branch displacement Figure 2.1 - sbb instruction format

Upper displacement containing all ones suggested that the branching was performed backwards (end of the loop is encountered) whereas the lower displacement field determined how long the backward jump was (how many instructions the loop consisted of). Lower part of the displacement field was w-bit wide which was directly connected to the size of loop cache, i. e. cache could not contain more than  $2^{w}$  instructions (in case of architecture where each memory location contained only one instruction and program counter was incremented by 1 to access next instruction).

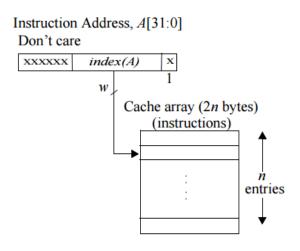

This made sure the loop size could not be larger than the cache size. As mentioned earlier, tight loop cache was direct mapped (contained no address tags), only accessed by index field which was w bits wide. When a loop was smaller than 2<sup>w</sup> instructions, only part of the loop cache was used and loop start did not have to be aligned to any particular address as in the case of many other techniques.

Figure 2.2 shows how loop cache was organized and accessed in a case of  $n=2^{w}$  entries, each entry containing 2 bytes (the last bit of the instruction address was neglected).

Figure 2.2 – Loop cache organization and access [10]

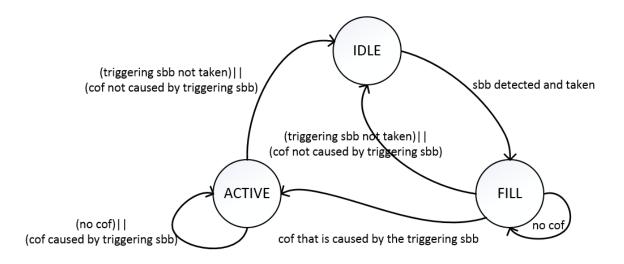

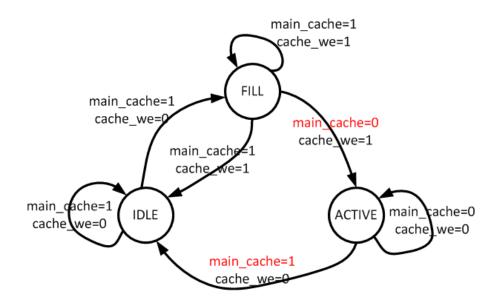

Loop Cache Controller was designed as a state machine with three states: IDLE, FILL and ACTIVE. Initially, the Controller was set to be in the IDLE mode all the time until it had been detected that there was an sbb in the instruction stream. If the controller determined that there was an sbb (information is received from the decoder) and that the branch was taken (information received from a branch status signal from the core), this meant there was a loop encountered and that it was going to be executed for the second time which made Controller move to FILL state. The sbb that forced the Controller enter FILL state was called triggering sbb. In the FILL state, instructions were still read from the main instruction memory, but at the same time cache was filled with the loop instruction stream. This state continued until there was no other change of flow (cof), i.e. no other branch or jump instruction (the program execution was sequential within the loop itself).

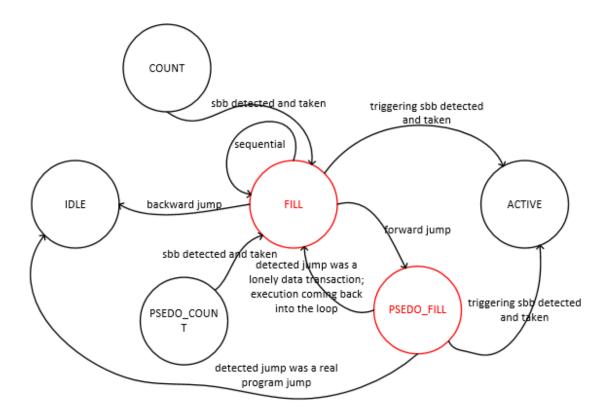

Figure 2.3 - Loop cache controller state machine

Controller went back to IDLE state in case it encountered a non-sequential stream in the loop sequence which was not caused by the triggering sbb (some other branching/jumping instruction inside the loop itself) or if it determined that triggering sbb was not taken. Finally, if the triggering sbb was taken again, the Controller entered ACTIVE state and started reading instructions from the cache. It stayed in the ACTIVE state as long as the loop within itself remained sequential and as long as the triggering sbb, when encountered, was taken (the loop was going to be executed again). In any other case, the Controller went back to IDLE state. There was no way the Controller could migrate from ACTIVE state back to FILL state which was logical considering possible scenarios.

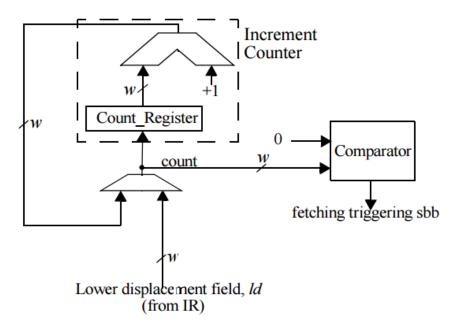

The most important piece of information for the Controller to determine whether next instruction was a hit or a miss was to know when the triggering sbb was fetched, executed and whether the cof was caused by the triggering sbb or some other instruction. The mechanism that made this possible was implemented as the Loop Counter mechanism shown in Figure 2.4.

Figure 2.4 - Design of loop counter [10]

The Controller was initially in IDLE state and stayed there until sbb was detected in the decode pipeline stage when its lower displacement field got loaded into the Count Register of the Increment Counter. This displacement gave the information of how many sequential instructions needed to be executed before sbb was fetched again. After the ld field was saved and later on determined that sbb was taken as well, the Controller entered FILL state. While in this state, on each sequential instruction execution, Increment Counter was incremented by one. By the time Counter reached zero, the Controller knew that the triggering sbb was being fetched. If the sbb was taken, the Controller entered ACTIVE state and the Increment Register was again loaded with the ld field of triggering sbb. This meant that the execution of the loop started from the beginning again. Whenever the counter reached zero again, the same process was repeated. Using this mechanism, the Controller knew when a cof was caused by the triggering sbb only by examining the value in the Increment Register.

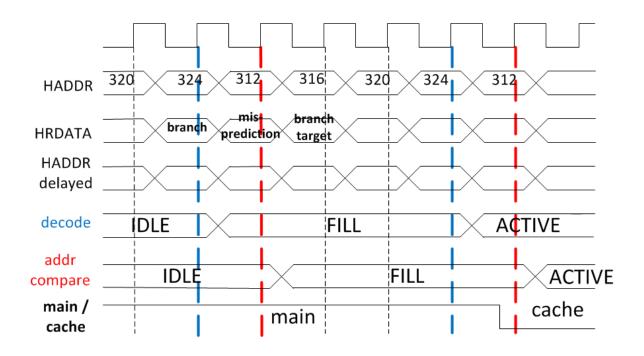

The original technique of using tight loop cache and loop controller, proposed in [10] and briefly explained here, was implemented both in software and hardware with slight modifications as it will be described thoroughly in the next chapter. Figure 3.11 shows cache being filled and read from with an example of loop execution on the core.

#### 2.3 Software System Background

This project was a continuation of work that was conducted during Autumn student semester project during which the author explored different caching techniques and chose to implement one of them, the so called Tight Loop Cache (simple and easily adaptable to any core environment). The principle of operation of the Loop Cache Controller was based on the principle explained in [10] and in the Chapter 2.2 but its implementation in Python was slightly different since the input data was different. The input data, as explained in [2] were benchmarks that were comprising of .csv files that contained memory addresses of consequently fetched instructions. Each next row contained next address to be fetched. A loop was detected by comparing two subsequent fetch addresses and determining that the previous address was larger than the current one. This meant that an sbb occurred and, if within the size of the loop the cache can hold, the Controller left IDLE state and entered FILL state. More details about implementation and actual Python code created as part of the Semester project can be found in [2].

The results from [2] showed that in some benchmarks the technique could bring a great deal of power savings (even up to 70%, taking into account only memory power consumption) whereas in some other benchmarks there was even loss if the cache was used. At the end of project report [2], it was noticed that there were some irregular jumps within loops themselves that caused Loop Cache Controller suddenly leave fill or active state and spend most of its time in idle state which didn't bring great deal of savings of course.

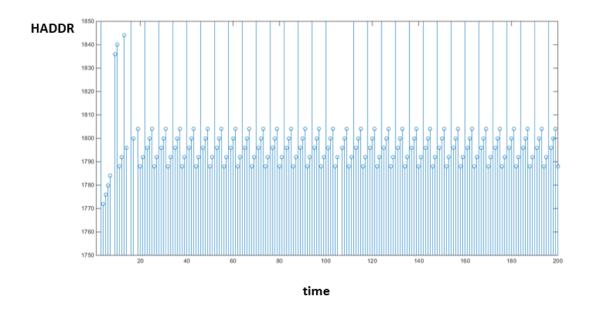

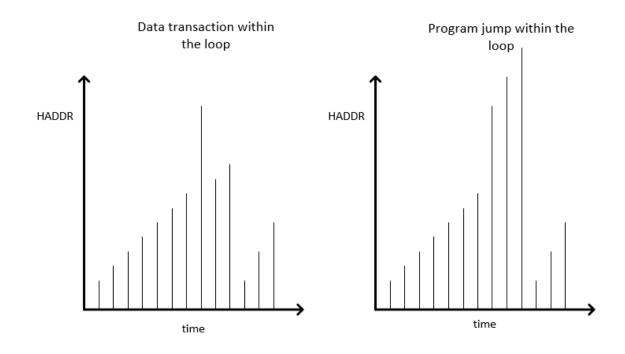

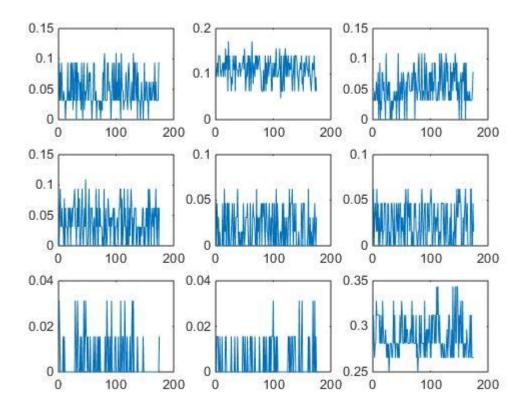

Analysing input data (program traces) more thoroughly this time and plotting them in Matlab made it possible to realize a crucial environment setup mistake that led to semester project results seem non-understandable. Figure 2.5 shows sequence of instruction fetch addresses in one of the benchmarks. As it can be seen, there was a loop consisting of 5 instructions that was over and over again (instruction addresses were gradually growing instruction by instruction and then suddenly dropping to the initial value). The Controller would never go to ACTIVE state while executing this loop and the reason is of course the nonsequential execution within the loop (large jump in address value after two loop instructions).

*Figure 2.5 – Example of Instruction fetch addresses sequence*

The only possible explanation behind these "jumps" inside loop execution lays down in the existence of data reads and writes which are addressed using the same address bus as the instruction fetches. Those data reads/writes cause the Controller toggle between IDLE and FILL states without ever entering ACTIVE which brought only more power dissipation.

Software implementation of the tight loop cache system in this project represents an upgrade of the system implemented in [2] taking into account these data fetches (sudden jumps in address values on the bus) and allowing the controller stay in the same state it was in (not going automatically to idle) even though there is a non-sequential fetch. More details about the implementation will follow in Chapter 3.1.

#### 2.4 Hardware System Background

Work on this project was monitored and supported by the company Silicon Labs, the branch located in Oslo, Norway. The company developed two families of microcontrollers that support low energy consumption concept:

EFM8: 8-bit microcontrollers developed around 8051 and

EFM32: 32-bit microcontrollers developed around ARM Cortex.

This project was dealing with EFM32 MCUs which are based either on ARM Cortex-M0+, ARM Cortex-M3 or ARM Cortex-M4 and are used together with low power peripherals to address any low power application (communications, alarm and security systems, control systems, industrial sensors, medical solutions, car and traffic control systems ...) According to Silicon Labs, EFM32 are the world's most friendly microcontrollers and their advantages over other similar products are certainly the use of 5 different energy modes, very fast wake up time, reduced processing time, energy efficient peripherals etc.

EFM32 are classified into 6 categories (Zero Gecko, Tiny Gecko, Gecko, Leopard Gecko, Giant Gecko and Wonder Gecko) depending on the CPU they use, amount of program memory they have and how much power they consume in different power modes. This variety of choice makes EFM32 quite attractive amongst designers:

"The EFM32 family's wide variety of MCUs, peripherals, I/O interfaces, packages, and other features gives system designers a wealth of choices. In summary, Gecko MCUs are a good choice for small embedded systems that spend most of their time sleeping and then awaken for brief bursts of activity."[3]

Next section will explain why Cortex-M0 Design Start was used as a final core in the implementation, describe its architecture organization and illustrate briefly how the program executed.

#### 2.4.1 Cortex-M0

Initially, Cortex-M3 was chosen as the core to implement the cache system around since it was used in 4 out of 6 different categories of the EFM32 family. The biggest advantage of using Cortex M3 would be its possession of the signal called BRCHSTAT [3:0] which offers branch status information of the instruction in decode and next execute pipeline stage. As described in [11] this signal could give information if the branching instruction is conditional or unconditional, taken or not taken and in decode or execute stage of the pipeline which would be extremely useful as input information for the Loop Cache Controller to early determine whether next fetch was going to be a hit or a miss in the loop cache.

Unfortunately, it was not possible to obtain licenses, use the Cortex-M3 core itself and simulate the system behaviour in the real EFM32 environment. Instead, a Cortex-M0 core was used since its licensing with ARM was not a problem and the Verilog implementation was obtained in a fairly easy way. Main architectural differences and similarities between these cores are shown in Table 2.1. Furthermore, the obtained core was part of a so called, Design Start Package which introduced certain limitations to the usage of the core itself.

|                        | Cortex-M3           | Cortex-M3          |

|------------------------|---------------------|--------------------|

| Architecture           | ARMv7-M             | ARMv6-M            |

| Pipeline               | 3 stage with branch |                    |

| Τιρειπε                | prediction          | 3 stage            |

| Insruction set         | -Thumb (entire)     | -Thumb (most)      |

|                        | -Thumb2 (entire)    | -Thumb2 (some)     |

| Interrupts             | 240, plus NMI       | 32, plus NMI       |

| Performance Efficiency | 3.34 CoreMarks/MHz  | 2.33 CoreMarks/MHz |

| Performance            | 1.25 / 1.50 / 1.89  | 0.87 / 1.02 / 1.27 |

| Efficiency             | DMIPS/MHz           | DMIPS/MHz          |

Table 2.1- Cortex-M0 and Cortex-M3 specification comparison [12]

As it can be seen from Table 2.1 both cores have 3 stage pipeline and they use the same instruction set which is the necessary condition for the cache system to migrate from one core to another although with different power consumption reports of course because they have different performance efficiencies which can also be seen from Table 2.1.

#### 2.4.1.1 Core block diagram

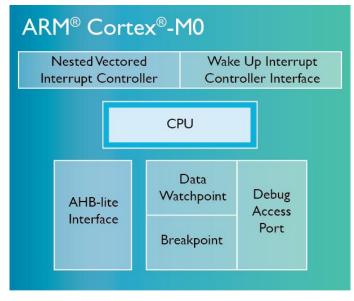

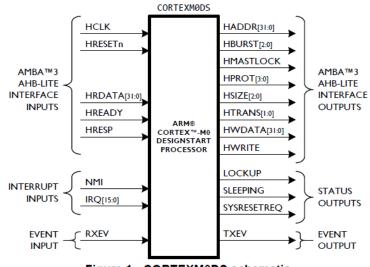

Cortex M0 processor is a 32b RISC processor with von Neumann architecture (program and data memory not separated, share the same bus) which uses Thumb instruction set and supports some functions from Thumb-2 (an upgrade of Thumb in a sense that it is possible for all the instructions to be executed in one CPU state). Thumb-2 instruction set includes both 16b and 32b instructions although latter is only used when none of the former cannot be used to complete the operation.

Cortex-M0 block diagram is shown in Figure 2.6. Main processing core consists of register bank (sixteen 32b registers), ALU and control logic with a three stage pipeline: fetch, decode and execute. Nested Vectored Interrupt Controller has the ability to accept NMI and up to 32 interrupt requests and decide which one to serve comparing their priority levels.

Wake Up Interrupt Controller is an optional module and is used to urge the power management unit to wake up the CPU and NVIC if they are in standby mode and there was an interrupt request.

Figure 2.6 - ARM Cortex-M0 block diagram [12]

Debug Access Port is used to make system development and testing easier and faster: deals with program breakpoints, data watchpoints and debug control in general.

AHB-lite bus interface is a 32b wide on chip bus protocol which is part of the Advanced Microcontroller Bus Architecture (AMBA) specification that was developed by ARM.

#### 2.4.1.2 Core Memory System

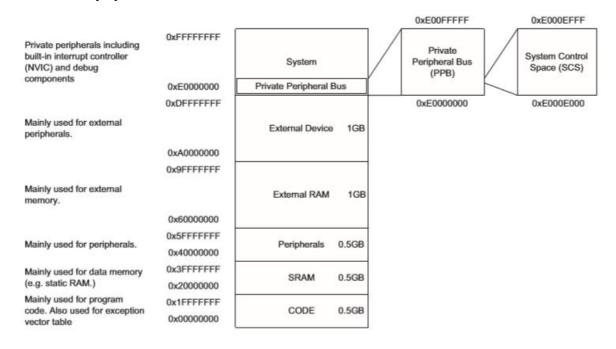

The Cortex-M0 has 4GB of memory address space (2<sup>32</sup>) divided in regions with each region having recommended usage that enables easier software migration between devices based on this core (programming model for interrupt control and debug are the same). Figure 2.7 shows different memory regions in 4GB memory space of the Cortex-M0. The core supports memory transfers of different sizes, such as byte, half-word and word wide either little or big endian memory system.

Figure 2.7- Cortex-M0 memory map [13]

Taking into account the tittle of the thesis it is natural to assume why more attention will be paid to the memory section that starts at 0x00000000 and is dedicated to the code. MCUs have on-chip flash memory that contains the binary code and some of them also have separate boot ROM that contains boot loader program which is executed before the user program (the content of this ROM usually cannot be changed).

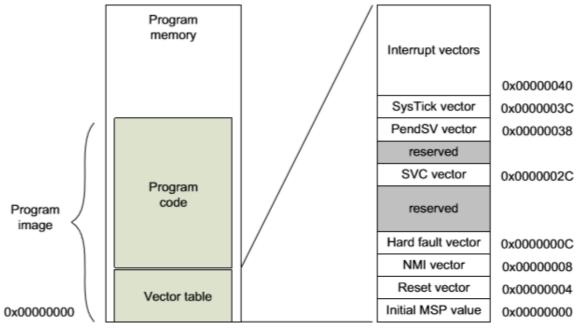

In the case of EFM32, program image starts with a vector table (starting addresses of interrupt handlers) whose size depends on number of interrupts that are implemented (starting address of the vector table depends on the implementer of Cortex-M). Figure 2.8 shows the content of vector table with some basic interrupt vectors that have to exist in every system whereas all the vectors from address 0x00000040 (address of the vector for IRQ #0) are arbitrary and exist only if implemented in the program. As it can be seen in the Figure 2.8, first word of the vector table contains initial main stack pointer value (MSP, contains the address of

the top of the stack) and right after it comes the reset vector which contains the address of the first instruction fetch.

Figure 2.8- Program Memory content [13]

After the reset, processor first reads the first word from the memory and initializes MSP with that value. Next step is to read the second word that determines where the program starts and start fetching instructions from that address and so on in the next clock cycle. Vector table can usually be completely defined using C. This information (first two words from the vector table) are often contained in the so called startup code. The reset handler from startup code can initialize some general system features, variables and memory that are going to be used although this is usually done later in the *main()*. Startup code is usually found in development suites or in software packages from MCU vendors. After the startup code, application code is being executed and it usually contains, as stated in [13]: initialization of hardware (clock, PLL, peripherals), application processing part and interrupt service routines.

#### 2.4.1.3 ARMv6-M instruction set

First ARM processors were using ARM 32b so called ARM Instruction Set which offered very high efficiency but occupied much more program memory space than other 8b or 16b processors. That is why with the announcement of ARM7TDMI processor, ARM announced new 16b instruction set, called Thumb, but not completely denied use of ARM instruction set because it was not possible to implement some functionalities using only Thumb. This processor supported both ARM (32b) and Thumb (16b) instructions and used a state switching mechanism to choose which decoding scheme should be used (based on the so called T bit which was set to 1 in case it was a Thumb and to 0 in case it was an ARM instruction). Thumb instruction set creates a 30% smaller code when compared to the code with the same functionality but written using ARM instruction set. On the other hand, performance is deteriorated by 20%. This is why Thumb-2 instruction set was created: it contains some 32b instructions to perform the functionalities that could be done only by ARM set initially and all the 16b instructions from Thumb. The same functionality coded with Thumb-2 takes around 74% of the size of the code coded with ARM IS maintaining the same performance.

ARM and Thumb instructions are designed to interwork freely but ARMv6-M only supports Thumb instructions and this is why interworking instructions in ARMv6-M must only reference Thumb state execution. All instructions that were used to test hardware implementation in this thesis were 16b Thumb instructions which meant that no interworking was needed but if the reader wants to know more about it, it is described in detail in [14]. ARMv6-M, the architecture used in Cortex-M0, is mostly using 16b Thumb instructions and a minimum subset of essential 32b Thumb instructions: BL, DSB, DMB, ISB, MRS and MSR. The instruction fetches are always half-world aligned. ARMv6-M can be configured to use either little endian or big endian data interpretation, but in the case of Cortex-M0 DS, used in this project, only little endian was supported.

| 15 14 13 12 <b>1</b> 1 <b>1</b> 0 9 8 | 7 6 5 4 3 2 1 0   | 15 14 13 12 11 10 9 8 | 7 6 5 4 3 2 1 0     |

|---------------------------------------|-------------------|-----------------------|---------------------|

| 32-bit Thumb in                       | nstruction, hw1   | 32-bit Thumb i        | nstruction, hw2     |

| Byte at Address A+1                   | Byte at Address A | Byte at Address A+3   | Byte at Address A+2 |

#### Figure A3-5 Instruction byte order in memory

Figure 2.9- Instruction byte order in memory [14]

ARMv6-M has 13 general purpose 32b registers (r0 - r12) and three special purpose 32b registers: SP (Stack Pointer, r13), LR (Link Register, r14) and PC (Program Counter, r15, loaded with reset handler when core resets) whose usage can be guessed from their names. There is also a register called APSR (Application Program Status Register) with least significant four bits used as flags: negative, zero, carry and overflow whose values are checked when conditional branching instructions are executed. In this section more attention will be

given to these instructions since they are the key instructions when a loop needs to be detected which was of crucial importance for this project.

Branching instructions supported by ARMv6-M are listed in Table 2.2. Since this project was focused on loop execution and not function or subroutine calls, only B and BX should be considered in details when implementing the algorithm described in Chapter 2.2. Chapter 3.2 explains two possible implementations of the same principle where in the first one encodings of these specific instructions would have to be used whereas in the second and actual implementation from this project, another approach was chosen where instructions encodings are not that relevant and that is why they are not mentioned in details in this section. More about instruction encodings can be found in [14].

| Branch Instruction | Description                | Range   |  |

|--------------------|----------------------------|---------|--|

| В                  | Branch to target address   | +/-2KB  |  |

| BL                 | Call a subroutine          | +/-16MB |  |

| BLX                | Call a subroutine          | Any     |  |

| BX                 | Branch to a target address | Any     |  |

Table 2.2 – Branching instructions supported by ARMv6-M [14]

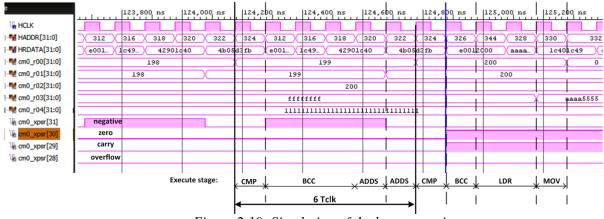

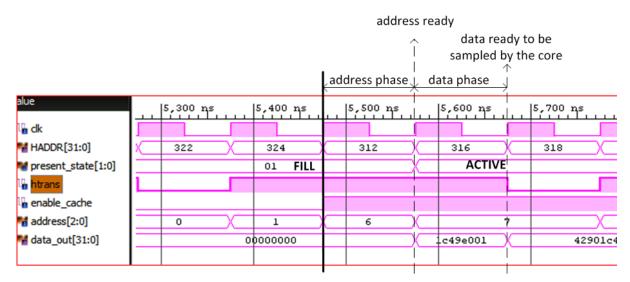

To demonstrate the execution of a loop, execution of a simple test program was simulated in VIVADO Design Suite - the signal waveforms are shown in Figure 2.10.

Figure 2.10- Simulation of the loop execution

Most of the time, the simulation shows execution of a loop as it can easily be noticed only by observing the values on HADDR bus: 312 - 316 - 318 - 320 - 322 - 324 and then going back to 312 and starting all over again. But the last part of the simulation shown in the Figure 2.10 shows the part where the loop breaks and the program continues to execute the rest of the code (that moment is marked by the blue line). Table 2.3 shows all the instructions that

are part of this particular loop: their address, hexadecimal encoding, corresponding assembly code, short description and the duration as reported in [12].

| Address | Instruction<br>(hex) | Assembly                 | Description                                             | Execution<br>Duration<br>[CLK cycles] |

|---------|----------------------|--------------------------|---------------------------------------------------------|---------------------------------------|

| 312 (6) | E001                 | <i>B</i> < <i>PC</i> +2> | Unconditional<br>branch 2 addresses<br>forward          | 1                                     |

|         | 1C49                 | ADDS<br>R1,R1,#1         | Increment the value<br>of R1                            | 1                                     |

| 316 (7) | 1C40                 | ADDS<br>R0,R0, #1        | Increment the value<br>of R0                            | 1                                     |

| 318     | 4290                 | CMP R2,R0                | <i>Compare values in</i><br><i>R2 and R0, set flags</i> | 1                                     |

Table 2.3- Loop Instructions

| 320 (0) | D3FB | BCC <pc-12></pc-12>        | Branch 10 (12)<br>addresses backward<br>if carry cleared | 3 |

|---------|------|----------------------------|----------------------------------------------------------|---|

| 322     | 4B05 | LDR R3,<br><pc+20></pc+20> | Load value from the<br>address pc+20 into<br>register R3 | 2 |

| 324     | 2000 | MOV R0,#0                  | Load zero<br>into R0                                     | 1 |

|         | E001 | <i>B</i> < <i>pc</i> +2>   | Unconditional<br>branch 2 addresses<br>forward           | 1 |

At this point it is important to mention again that ARMv6-M architecture has a 3 stage pipeline: fetch, decode and execute and that the instruction duration depends on how many cycles it takes for it to execute (fetch and decode have fixed duration). The duration column in the Table 2.3 shows how many clock cycles the execution stage takes. As it can be seen from Figure 2.11, up to two 16b instructions are fetched in one transfer. In the next clock cycle first one of them is being decoded and in the third cycle this instruction enters the execution stage whereas the second fetched instruction is being decoded. At the same time, next two instructions can be fetched since last two left the fetch stage.

It can be seen from Figure 2.10 : in the case of a taken branch it takes 3 clock cycles to execute the branch instruction whereas only 1 in case of a non-taken branch, as stated in [12]. In the case of a taken branch some of the instructions are still fetched (those that are not in bold) but they are not executed since the architecture cleans the pipeline from them. In case of a non-

taken branch all of the instructions are executed as it can be seen in Figure 2.10 (e.g. register r3 is indeed loaded with a value read form the memory, register r0 loaded with zero etc.)

Instruction 1 fetch 🖡 decode Inst 1 Instruction 2 fetch 🛉 decode Inst 2 execution Instruction 3 fetch decode Inst 3 Instruction 4 fetch decode Inst 4 Up to two instructions can be fetched in one transfer. (16-bit instructions)

Figure 3. Pipeline stages in the Cortex-M0 processor

*Figure 2.11- Cortex-M0 pipeline stages*[15]

#### 2.4.1.4 ARM Cortex-M0 Design Start

Design Start Implementation was delivered by ARM with two Verilog modules: top module called CORTEXMODS and an obfuscated sub-module called cortexm0ds\_logic. Top module implements ports for the AMBA 3 Lite Interface with possibility of 17 interrupt inputs (16 + NMI), three output status signals and one output event signal. The top module interface is shown in Figure 2.12 and it contains AHB interface signals, interrupt inputs, event input and event and status outputs.

Figure 1 - CORTEXM0DS schematic

Figure 2.12- Cortex-M0 schematics[16]

All interrupt input signals are synchronous and active high, NMI has the highest priority whereas priorities of other 16 interrupt signals can be configured.

There are three output status signals and their meanings will be briefly mentioned here whereas more details can be found in [16]:

- SLEEPING: an active high signal that indicates the processor is IDLE (usually after Wait for Event - WFE or Wait for Instruction - WFI instructions) and will not execute any AHB transactions

- LOCKUP: indicates that the processor is in a non-desirable, LOCKUP state and

- SYSRESETREQ: HIGH value of this signal indicates that the software wants to perform system reset.

Event output signal TXEV is used to indicate that the processor is performing SEV instruction whereas the input RXEV signal is indicating that it should wake up from WFE instruction.

Cortex M0 Design Start implements AHB 3 Lite System Bus Interface using bus clock and reset signals as its global clock and reset signals: HCLK and HRESET. It is important to note that the Design Start implementation of the core does not offer all the possibilities offered by the full core. Here are some of the restrictions introduced that could not be influenced:

- 3b HBURST output signal value was always 000 which indicated that the processor supported only SINGLE type transfer (no BURST transfer),

- HMASTLOCK output signal is driven low all the time which indicates that the processor is not generating locked sequences.

- HPROT[1] signal is always driven low indicating that the transaction is always PRIVILEGED (program execution can access all memory resources)

| Transaction                           | Access | Description                                                                                                         |

|---------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------|

| HTRANS[1:0] = 2'b00                   | IDLE   | The processor does not wish to perform any transaction.                                                             |

| HTRANS[1:0] = 2'b10                   | FETCH  | The processor wishes to perform an instruction fetch.<br>Instructions are fetched 32-bits at a time from memory. If |

| HPROT[0] = 1'b0<br>HSIZE[1:0] = 2'b10 |        | required, the processor internally buffers and manages the extraction of two 16-bit instructions.                   |

| HWRITE = 1'b0                         |        |                                                                                                                     |

| HTRANS[1:0] = 2'b10                   | BYTE   | The processor wishes to perform an 8-bit data access                                                                |

| HPROT[0] = 1'b1                       |        | resulting from an LDRB, LDRSB or STRB instruction.<br>Load instructions will drive the HWRITE signal LOW; store     |

| HSIZE[1:0] = 2'b00                    |        | instructions will drive the HWRITE signal HIGH.                                                                     |

| HTRANS[1:0] = 2'b10                   | HALF-  | The processor wishes to perform a 16-bit data access                                                                |

| HPROT[0] = 1'b1                       | WORD   | resulting from an LDRH, LDRSH or STRH instruction.<br>Load instructions will drive the HWRITE signal LOW; store     |

| HSIZE[1:0] = 2'b01                    |        | instructions will drive the HWRITE signal HIGH.                                                                     |

| HTRANS[1:0] = 2'b10                   | WORD   | The processor wishes to perform a 32-bit data access                                                                |

| HPROT[0] = 1'b1                       |        | resulting from an LDR, LDM, POP, STR, STM or PUSH<br>instruction, or as part of exception entry or return. Loads    |

| HSIZE[1:0] = 2'b10                    |        | will drive the HWRITE signal LOW; stores will drive the HWRITE signal HIGH.                                         |

Figure 2.13 - Cortex-M0 access types[16]

Cortex-M0 core can generate four types of transfer depending on the signals HSIZE[1:0], HTRANS[1:0], HPROT[0] and HWRITE as shown in Figure 2.13.

The most interesting transfer type at this point is the one involving instruction fetch. As described earlier, the fetch involves fetching 32b at a time from the instruction memory with a possibility of extracting two 16b instructions from this sequence.

Although the design start does not offer possibility of hardware debug, there are some registers that are routed from internal logic so that their values could be observed while simulating. Those are 13 general purpose registers, MSP (main stack pointer), PSP (process stack pointer), link register, PC (address of instruction currently in execute), status register (XPSR), control and primask register (more about each one of them can be found in [14]).

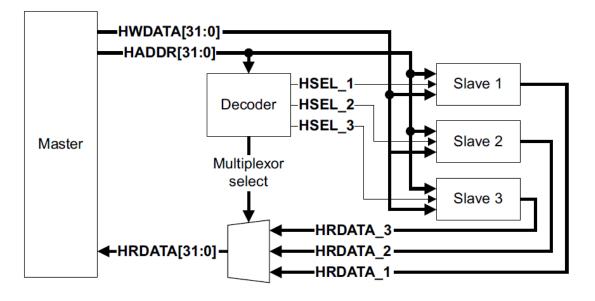

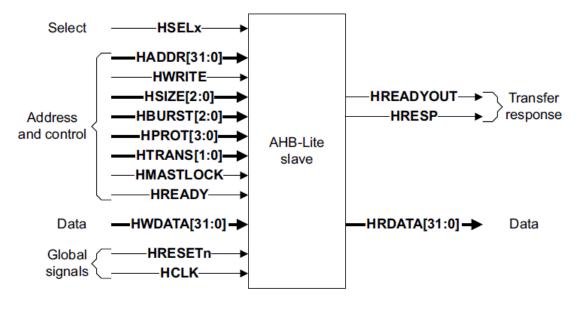

# 2.4.2 AHB bus

AMBA AHB-Lite (Advanced Microcontroller Bus Architecture, Advanced High Performance Bus) is a standard on-chip intercommunication specification developed by ARM but widely used in high performance electronic designs with many different applications. It is based on a master – slave role division concept with one master (Lite suffix), although it can

be extended to include more masters, Multi-layer AHB. If there are slaves that are slower (using lower bandwidth), they are located on the APB (Advanced Peripheral Bus) part of the system

Figure 1-1 AHB-Lite block diagram

## Figure 2.14 - AHB-Lite block diagram [17]

and connected to the AHB by a bus bridge.

Figure 2.14 shows AHB master with three slaves and two inevitable elements which determine which slave is going to communicate with the master: decoder and a multiplexer. Master starts both read and write processes by driving corresponding control signals and setting the address of the slave it wishes to communicate with, decoder decodes the address and generates both slave enable signals and a multiplexor selective input to pass corresponding output data from the slave into the master.

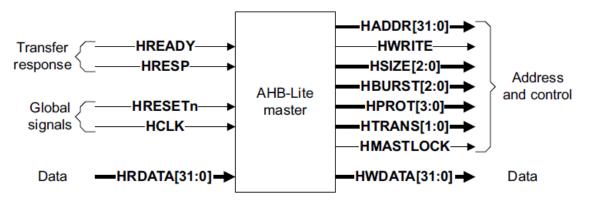

# Master interface

Figure 2.15- AHB Master interface

Figure 2.15 shows AHB master with its interface to the rest of the AHB system. Many of these signals already appeared and were described so in this part emphasis will be put on the situations that can happen in the case of using Cortex-M0 Design Start as a master: the transfer type can only be single, there can be no locked transfers, the transfer is always privileged and the transactions are always non sequential. Each of the output signals sets a type of control over the transfer - their role is shown in Table 2.4. Some of the transfer properties are shown in bold and those represent properties that were hard wired into the Design Start so the non-bolded transfers are not even possible to implement. More information and details about all possible transactions on the AHB bus can be found in [17].

| Signal             | Description                                                                                                            |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| HADDR              | Address phase interface address                                                                                        |  |  |

| HWRITE             | Address phase read/write information                                                                                   |  |  |

| HSIZE              | Data phase transaction data size:<br>- byte<br>- half-word<br>- word                                                   |  |  |

| HBURST             | Address phase burst information<br>-single<br>- incr<br>- wrap [8 16 32]<br>- incr [8 16 32]                           |  |  |

| HPROT              | Protection information<br>-cacheable,<br>- bufferable,<br>- privileged (has access to all resources)<br>- data/ opcode |  |  |

| HTRANS<br>00 or 10 | Address phase transfer type:<br>- idle<br>- busy<br>- non-sequential<br>- sequential                                   |  |  |

Table 2.4- AHB Master output signals of interest

#### **HMASTLOCK**

Address phase locked information - locked - **unlocked**

AHB slave provides information about the status of the transaction by setting values of the two signals: HREADYOUT (when HIGH indicates a transfer has finished, but it can be driven LOW to extend the transfer) and HRESP (success or failure in the communication). Systems that were used in this project, consisted only of instruction memory and a small cache which were designed in a way they could provide new data on each new clock cycle if requested (the signal HREADY which normally would have been provided to the master by the slave, was driven HIGH all the time). Moreover, there was no possibility for slaves to generate errors so the signal HRESP was driven HIGH all the time as well.

#### Slave interface

Figure 2.16- AHB Slave interface

Since Cortex-M0 DS could not perform any other but SINGLE transfer, slaves were not generating any errors and were ready to give new data on each clock cycles, the transfer that is going to be considered here is the basic unlocked single transfer with no wait states and no protection control.

AHB basic transfer consists of two phases: address and data phase and it takes three rising clock edges (two clock periods) for a transfer to complete. After the first rising edge, master sets up the right address and control signals (important signal that is not shown in these

figure is the HTRANS[1] signal which needs to be set HIGH at this point to indicate AHB transfer is about to happen). Signal HWRITE controls the direction of the transfer: if set HIGH the master broadcast data on the HWDATA bus and this data is about to be written into the slave, whereas in the case of this signal LOW the master wishes to read data from the slave and this data is going to appear on the HRDATA bus. On the next clock edge (second), the slave samples control and address signals. Finally on the third clock the processor is able to sample the correct data on the HRDATA bus or the slave is ready to sample HWDATA bus. Figure 2.17 also shows how address phase of a transfer overlaps with data phase of the previous transfer and this is the fundamental principle that makes AHB a high performance bus used by wide spectrum of applications.

Figure 3-2 Write transfer

Figure 2.17 - AHB basic transfer: read and write [17]

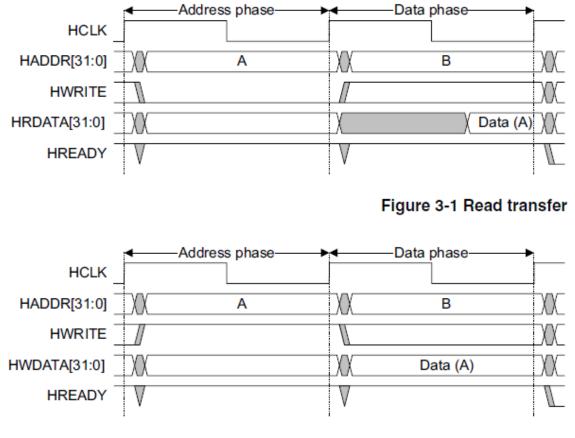

# 2.4.3 Simulating the Cortex-M0 core

As it was mentioned earlier, Cortex-M0 Design Start soft core was obtained from ARM as two modules written in Verilog:

- CORTEXMODS.v ( a top designer module which shows processor interface ) and

- cortexm0ds\_logic.v (an obfuscated module with processor logic implemented).

Apart from the hardware implementation contained in these two files there was also a testbench provided with a top testing Verilog module which had an AHB system containing a master (the core itself) and two slaves:

- a memory model to load a binary of a program to be executed and

- an output console to show the status and results of the running program.

Figure 2.18 – ARM Design Start testbench deliverables: block diagram

Memory model implemented as a part of testbench was word addressable with an 18b wide address bus so the HADDR values that were selecting it were between zero and 2^18 (0x40000) whereas the address that was accessing output console was set to 0x40000000. The binary that was delivered with the testbench (ram.bin) was a binary obtained by compilation of the helloworld.c (also delivered) using ARM's Real View Complier using commands from the Makefile from the package as well. To make the processor execute this program, it was enough only to create a project in any Verilog simulator and make sure that the binary is accessible by

the core (it should be within the simulation folder of the project, otherwise there would be a mistake reported). In this thesis, verifying simulation was performed using Xilinx VIVADO. The output of the simulation were merely messages on the screen showing the status of the program execution, Figure 2.19. This simulation was performed only to prove that the core was behaving the way expected and that it was possible to load different binaries into it. In the next sub chapter it will be explained how the core was synthesized and how the code was being run on an actual FPGA board.

Figure 2.19 – Core simulation results

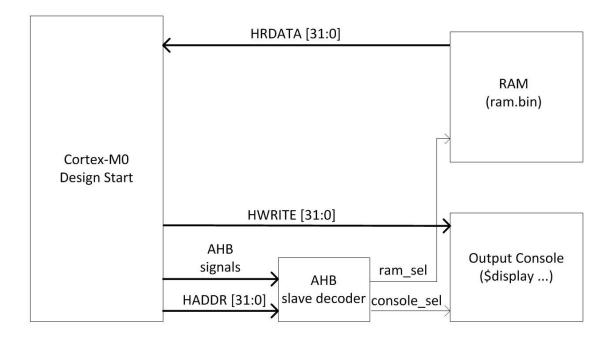

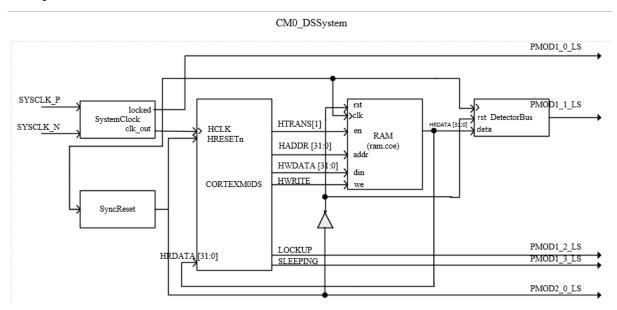

# 2.4.4 Running the core with Instruction Memory on FPGA [18]

Following ideas from [18] with slight modifications, a system for synthesis on ZC702 Evaluation Kit was developed. To develop the whole system which would be able to execute different programs, simulate processor behavior showing signal waveforms and finally verify the correctness by running the core loaded with a program on actual hardware, few system integration steps needed to be performed.

#### 2.4.4.1 Building hardware

The system block diagram is shown in Figure 2.20and the deliverables that came within this tutorial contained these modules. All the blocks were used in the same way as in the manual form Louisianan Tech College of Engineering and Science [18] with some slight differences since in the tutorial the implementation was adapted to NEXYS2 FPGA board.

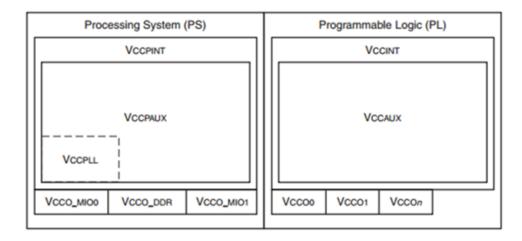

As it was stated earlier, ZC702 Evaluation Kit contains a Zynq-7000 SoC with a Xilinx Artix 7 FPGA Programmable Logic Equivalent System (part number XC7Z020-1CLG484C) that needed to be selected as a target device when creating a project in VIVADO Design Suite. Next step was to add sources to the project which will represent hardware modules. Figure 2.20 shows the overall system (top module, CM0\_DSSystem.v file) with hardware modules that were part of it.

Figure 2.20 – Block diagram of the system built for implementation on FPGA board

## 2.4.4.1.1 Clock generation

The most important part of a synchronous system is the clock: its generation has to be stable and accurate in order for the system to behave as planned. Although the Cortex-M0 processor is said to operate up to 50MHz frequency, in the tutorial [18] system clock was set to 10 MHz and it was decided to maintain the value in this project as well.

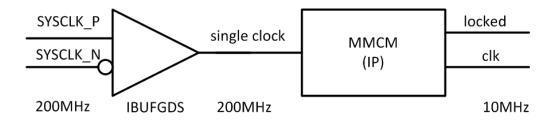

Figure 2.21 - Clock generation on zc702 Evaluation Kit

Clock module was created using Clock Wizard IP generator in VIVADO with the implementation using MMCM (Mixed Mode Clock Manager) and not DCM (Digital Clock Manager) as in [18] since Xilinx 7 Series do not offer DCM any more, only MMCM and PLLs. The EK had a 200 MHz Low Voltage Differential Signalling (LVDS) oscillator with a

differential output: a positive SYSCLK\_P and a negative SYSCLK\_N. Clock generator that was used to synthesize 10MHz frequency contained a single clock source as input and therefore these two signals had to be adapted to be used as a single clock signal. For these purposes, a primitive design element from 7Series FPGA, differential signal input buffer IBUFGDS was used as a connection to MMCM.

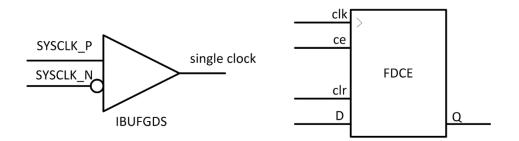

Figure 2.22 – 7Series primitive elements: buffer and D flipflop

Two input signals (SYSCLK\_P and SYSCLK\_N, the board oscillator differential outputs) have to have the same frequency but opposite phase. In this case output of the clock buffer was equal to the master input which is SYSCLK\_P in this case. Single output of the buffer (200 MHz) is then loaded into the frequency synthesizer that gave the desired processing frequency of 10 MHz. As in the case of any frequency synthesizer, there was a locked signal at the output that was indicating if the synthesizer was locked and the output frequency was stable. This signal was also used as an output of the system to drive board LEDs and indicate if the system had a stable clock which is always the first thing to check when performing system debug. Buffer was also used to recover the signal, make rise and fall time smaller.

#### 2.4.4.1.2 Reset generation

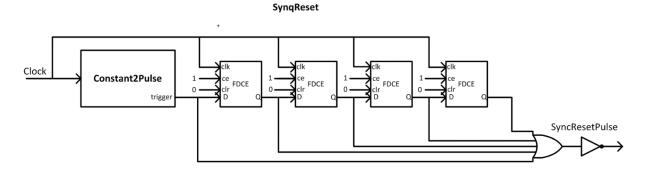

Second most important step was to design reset circuitry for the system, in this case provide a 4 period long low signal for each reset session since that is the reset specification for the Cortex-M0 core. There were three modules from the tutorial [18] that were used to create the clock: DelayCounter.v , Constant2Pulse.v and SyncReset.v (for the sake of simplicity, Figure 2.23shows only the top module). As it was mentioned earlier, reset pulse needed to be at least four cycles long in order to reset the core and in this implementation from [18] it was generated only once at the beginning of the system setup and completely internally, i.e. with no user controlled reset. The idea was to generate a pulse that would surely stay high for four clock cycles and then invert it as shown in Figure 2.23. In order to make the signal four cycles long a short pulse (called trigger in figures) was propagated through four D flip flops and then outputs from all of them together with the original signal were used as inputs of a 5 input OR gate. FDCE elements in the figures are primitive design elements supported by Xilinx 7Series [19] which are nothing but D flip flops with clock enable and asynchronous active high reset.

Figure 2.23 – SynqReset module block diagram

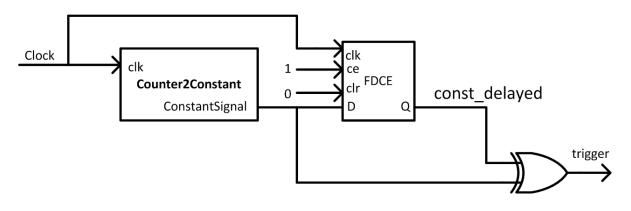

In order to generate trigger signal, a module Constant2Pulse was used. Its implementation was based on the idea that performing an XOR operation on a constant of a signal and its delayed version would produce a pulse at the output. This is shown in Figure 2.24.

## Constant2Pulse

## Figure 2.24 – Constant2Pulse module block diagram

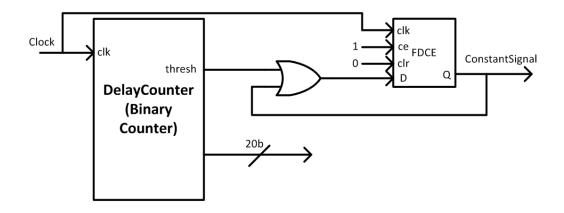

Generation of the constant signal was done within the module called Counter2Constant which is shown in Figure 2.25. The basic idea was to generate a pulse using a binary counter, and once it was generated, use a positive feedback to maintain at least one of the inputs of the OR gate high which created a constant output signal. These signals are shown in Figure 2.25.

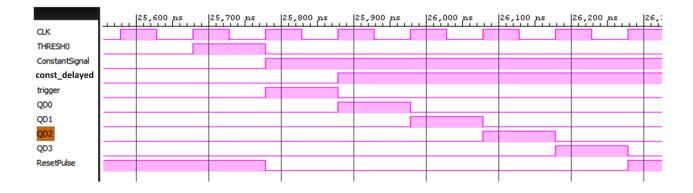

Although having a 20b output, binary counter was configured to count only up to the value F9 and then generate a high signal called *thresh* which was used as input to the OR gate, whereas the 20b output was not used later at all. Simulation of the reset signal generation is shown in Figure 2.26.

## Counter2Constant

Figure 2.25 - Counter2Constant module block diagram

Figure 2.26 – Reset pulse generation: simulation

# 2.4.4.1.3 RAM memory

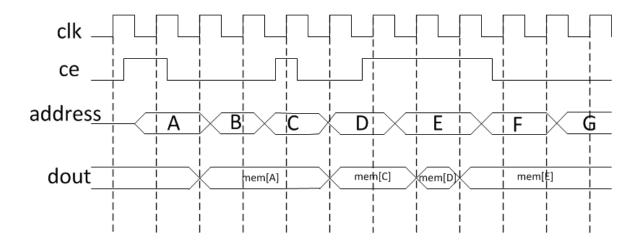

RAM memory was created using IP Block Generator from VIVADO that created 2KB memory which was word addressable, having 9b wide address bus ( $2^9 \times 4B = 2KB$ ) and an active high reset. The memory was designed to work in compliance with AHB interface, i.e. if enabled, on the next rising clock edge output data from the address that was sampled with the current clock edge, was present on the bus as shown in Figure 2.27. Enable signal of the memory

block was connected to HTRANS signal of the AHB bus which was completely understandable since this signal driven high indicated that a new transaction should be performed. This was explained in details in Chapter 2.4.2.

Memory IP block offers the possibility to load memory with initial content saved in a file with an extension .coe. Generation of this file will be explained in Chapter 2.4.4.

Figure 2.27 – Block RAM principle of operation

# 2.4.4.1.4 Detector

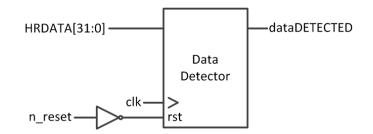

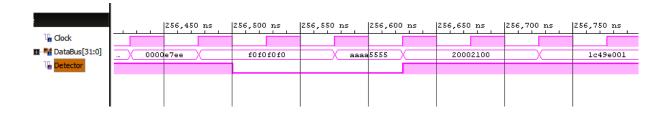

The last part of the system in [18] was the module called Detector that was used to indicate that the processor was executing the loaded program the way planned. It is not that easy to verify proper functioning of a processor core when it does not have peripherals built around it because there are many signals and wide buses that need to be checked. A very simple approach was used in [18]: module Detector was toggling an LED at the output when a certain value would appear on the data input bus, HRDATA. At the beginning, on a system reset, the LED was driven low. Later on, when the value 0xAAAA5555 showed up on the bus, the Detector signal would go high and remain high until value 0xF0F0F0F0 showed up. To sum up, HRDATA value of 0xAAAA5555 was triggering Detector value to go high whereas the value of 0xF0F0F0F0 was driving Detector low. This is shown in Figure 2.29.

Figure 2.28 – Detector module interface

Figure 2.29 – Generation of Detector signal: simulation

The last step to configure the hardware part of the system was to add the Xilinx Design Constraint file (.xdc) to the project constraints. This file was taken over from [20] containing net names that corresponded to net names of the latest ZC702 schematics (although only some of them were used in the project).

# 2.4.4.2 Software

Previous section explained how hardware modules were designed, what was the purpose of each one of them and how they communicated between themselves. Another important aspect of enabling system to work is making it behave in the desired way so that processes could be performed. This is done, as in any other system, by loading a desired program, which was a .coe file in this case into its instruction memory.

$\mu$ Vision IDE from Keil was used to develop software project, make source file editing and program debugging with Cortex-M0 as a target core. Other project properties that needed to be set as in [21] were:

- 1. Target tab

- Working frequency: 10MHz

- Set ROM memory space (size 1KB, starting at zero address)

- Set RAM memory space (size 1KB, starting at address 0x400)

- 2. Output tab:

- Select folder which will contain object files

- Enable the option of creating .hex file when compiling

- 3. ASM tab: