# Synthesis of low-energy near-threshold SHMAC processor core

**Miguel Zapatero**

Embedded Computing Systems Submission date: June 2015 Supervisor: Snorre Aunet, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# Synthesis of low-energy near-threshold SHMAC processor core

Miguel Zapatero Rodríguez

June 2015

Supervisor: Professor Snorre Aunet Department of Electronics and Telecommunications Norwegian University of Science and Technology

# **Project assignment**

Student's name: Miguel Zapatero Rodriguez

Course: TFE4915 - Circuits- and Systems Design, Master's Thesis.

Project title: Synthesis of low-energy near-threshold SHMAC processor core.

Project description:

- Improve a basic cell library that includes: inverter gate, NAND gate, NOR gate and a D Flip-flop creating the layout and optimizing it to work with nearthreshold voltage supplies.

- Use this library to synthesize a core.

- Simulate this core studying the possible improvements in power consumption and how the performance is affected.

# Abstract

In this project an AMBER processor's ALU is synthesized to operate in the near/subthreshold region. The main motivation for this work is to study the possibility of implementing near/subthreshold modules in the SHMAC processor. These modules may be used for low requirement operations and are supposed to decrease the power consumption of the system.

Near/subthreshold operation is a developing method to reduce power consumption in static MOS technology. It consists on using near/subthreshold voltages to reduce the dynamic power of the system. The dynamic power consumption is proportional to the square of the operational voltage so, in theory, reducing the supply voltage can significantly reduce the power usage of the system.

A cell library consisting in NAND,NOR, XOR, inverter and D Flip-flop gates is created aimed to work with a near/subthreshold voltage supply. This was done using CADENCE and standard 65nm CMOS technology.

AMBER processor's ALU is synthesized using the custom library created, and simulated for 400mV.

## **Preface**

This report is written as a master thesis for the Master degree program at the University of Science and Technology (NTNU) of Trondheim. It is written during the spring 2015. The thesis is a continuation of the specialization project of the same name.

The supervisor, Professor Snorre Aunet, proposed this topic but the objectives and approach were chosen by me.

This master thesis has proven a challenge due to the difficulties of using new complex programs such as Cadence but it has given me knowledge about cmos layout and synthesis process.

I would like to thank my supervisor, professor Snorre Aunet, from the support given during the project.

I would also like to thank PHD student Benjamin Bjørnseth and Master student Henrik Fegran for the help provided during in the synthesis process.

# Contents

| Ρı | oject a | assig | Inment                              | ii  |

|----|---------|-------|-------------------------------------|-----|

| Al | ostract |       |                                     | iii |

| Ρı | eface   |       |                                     | iv  |

| C  | ontents | s     |                                     | v   |

| 1  | Intro   | oduct | tion                                | 1   |

|    | 1.1     | Bac   | kground and motivation              | 1   |

|    | 1.2     | Арр   | proach                              | 2   |

| 2  | The     | oreti | ical Background                     |     |

|    | 2.1     | Dar   | k Silicon                           | 3   |

|    | 2.2     | CM    | OS Logic                            | 5   |

|    | 2.3     | Pow   | ver consumption in CMOS circuits    | 5   |

|    | 2.3.3   | 1     | Dynamic or Switching power          | 6   |

|    | 2.3.2   | 2     | Short circuit power                 | 6   |

|    | 2.3.3   | 3     | Static or leakage power consumption | 6   |

|    | 2.4     | Nea   | ar/subthreshold region              | 7   |

|    | 2.5     | Cell  | l library                           | 10  |

|    | 2.6     | Lay   | out                                 | 12  |

|    | 2.6.3   | 1     | DRC                                 | 12  |

|    | 2.6.2   | 2     | LVS                                 | 12  |

|    | 2.6.3   | 3     | PEX                                 | 12  |

|    | 2.6.4   | 4     | Library extraction                  |     |

|    | 2.7     | Syn   | thesis theory                       | 15  |

|    | 2.7.2   | 1     | Verilog and VHDL                    | 16  |

|    | 2.7.2   | 2     | Encounter RTL compiler              | 16  |

|    | 2.7.3   | 3     | Synthesis, place and route          | 16  |

| 3  | Cus     | tom   | design library                      | 17  |

|    | 3.1     | Inve  | erter                               | 17  |

|    | 3.2     | NAM   | ND Gate                             | 21  |

|    | 3.3     | NO    | R Gate                              | 24  |

|    | 3.4     | D-F   | lipflop                             | 27  |

|    | 3.5     | XOF   | R                                   | 29  |

|    | 3.6     | Extr  | raction                             | 30  |

| 4 | Synthe | esis process |  |

|---|--------|--------------|--|

| 5 | Discus | ssion        |  |

| 5 | .1 Li  | ibrary       |  |

|   | 5.1.1  | Inverter     |  |

|   | 5.1.2  | NAND         |  |

|   | 5.1.3  | NOR          |  |

|   | 5.1.4  | D-Flipflop   |  |

|   | 5.1.5  | XOR          |  |

| 5 | .2 S   | ynthesis     |  |

| 6 | Conclu | usions       |  |

| 6 | 5.1 Fu | urther work  |  |

| 7 | Refere | nces         |  |

| 8 | Append | dix          |  |

# **LIST OF FIGURES**

| Figure 1. Moore's law                                                    | 4  |

|--------------------------------------------------------------------------|----|

| Figure 2, power density                                                  | 4  |

| Figure 3, energy per operation and frequency                             | 7  |

| Figure 4, energy/V <sub>dd</sub>                                         | 8  |

| Figure 5, variation in performance                                       | 9  |

| Figure 6, failure rate                                                   |    |

| Figure 7, PEX parameters 1                                               | 13 |

| Figure 8, PEX parameters 2                                               | 13 |

| Figure 9, parasitics extraction                                          | 14 |

| Figure 10, extracted view                                                | 14 |

| Figure 11, synthesis process                                             | 15 |

| Figure 12, inverter schematics                                           | 18 |

| Figure 13, inverter curve                                                | 18 |

| Figure 14, delay and energy/operation inverter without parasitics        | 19 |

| Figure 15, inverter layout                                               | 20 |

| Figure 16, delay and energy/operation inverter with parasitics           | 21 |

| Figure 17, delay and energy/operation inverter without parasitics        | 22 |

| Figure 18, NAND layout                                                   | 23 |

| Figure 19, delay and energy/operation NAND with parasitics               | 24 |

| Figure 24, D-Flipfop delay and energy/operation inverter with parasitics | 29 |

| Figure 25, delay and energy/operation XOR with parasitics                | 30 |

|                                                                          |    |

# LIST OF TABLES

| Table 1, NAND truth table                    |    |

|----------------------------------------------|----|

| Table 2, NOR truth table                     |    |

| Table 3,NOT truth table                      |    |

| Table 4, D-Latch truth table                 | 11 |

| Table 5, XOR truth table                     | 11 |

| Table 6, inverter without parasitics data    | 19 |

| Table 7, inverter without parasitics data    |    |

| Table 8, NAND without parasitics data        | 21 |

| Table 9, NAND with parasitics data           | 23 |

| Table 10, NOR with parasitics data           |    |

| Table 11, D-Flipflop without parasitics data | 27 |

| Table 12, D-Flipflop with parasitics data    |    |

| Table 13, XOR with parasitics data           |    |

| Table 14, ALU results                        |    |

|                                              |    |

# **1** Introduction

The introduction consists of a brief description of the background and motivation for this project, and a brief explanation of the approach followed.

## **1.1 Background and motivation**

Nowadays the dark silicon effect is a main concern in the development of computing systems. The escalation in the transistor sizes has not been followed by a similar reduction in power consumption and this has led to electronic systems in which only a subset of the resources can be power at the same time.

Heterogeneous computer systems are systems that use more than one type of processor to handle different task. The use of specialized processor design for a particular task can increase the performance of the system or reduce its power consumption. Using different modules with different performances and power consumptions is thought to be one of the best approaches in order to overcome this dark silicon limitation.

The EECS department of the NTNU is currently developing a heterogeneous processor (the Single-ISA Heterogeneous many-core Computer or SHMAC) to research the challenges of heterogeneous computer systems. The aim is to exploit the heterogeneous processor in an attempt to mitigate the dark silicon effect.

On the other hand, reducing the power consumption is a main research topic in the electronic field and near/subthreshold supply is one of the main trends in this research.

The power consumption in static CMOS technology is caused by three contributions; these are short circuit, leakage and switching power consumption. The switching power is proportional to the square of the voltage supply and the leakage and short circuit power are also proportional to the voltage supply so reducing it can lead to an important reduction in power consumption. The problem is that the performance of the circuit also reduces with the reduction in voltage supply so it is important to study the effect of this reduction and try to achieve the best trade-off between power consumption and performance.

Using a near/subthreshold module in the SHMAC platform will allow the ECCS to investigate the possibility of using a very low power consumption unit for computations with low speed requirement.

# 1.2 Approach

This project is a continuation of the specialization project of the same name. In this specialization project due to the impossibility of synthesising in near/subthreshold voltages with the provided library, a small cell library was made (based on schematic design).

For this master thesis the first step is to do an extensive research on near/subthreshold MOS technology. It is important to acquire this knowledge to be able to understand the possibilities and limitations of this technology and, later on, to study the characteristics of the near/subthreshold implementation.

The second step consists in improving the previous library by creating the layout of the cells and extracting its parasitics. This implies familiarizing with the tool Virtuoso of Cadence.

The third step will be compare the behaviour of the cells and see how the parasitics affect the functionality.

The fourth step will be to synthesize the ALU of the AMBER processor which is given in a hardware description language (Verilog). This requires familiarizing with the use of different programs: encounter RTL compiler, Synopsis and Virtuoso.

The fifth step is simulating the synthesized ALU to study how the reduction in the power supply influence in the power consumption and performance which respect to the normal voltage supply.

# 2 Theoretical Background

# 2.1 Dark Silicon

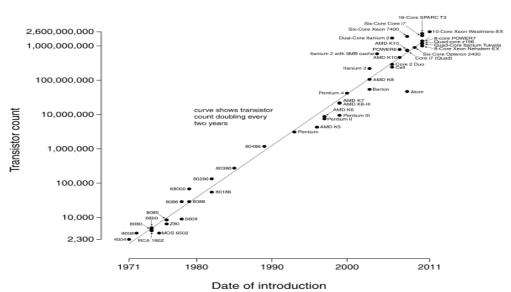

In accordance with Moore's law, the number of transistors that can be implemented per unit of area doubles every two years (see Figure1). Unfortunate, the power consumption has not decreased in the same proportion. This has led to electronic systems consuming more and more energy and increasing their power density (see Figure2).

This increase in the energy consumption has three main adverse effects:

- Economic impact: For large systems (such as data centres) the cost of the energy (in the form of electricity) is one of the main concerns.

- Battery life: Portable electronic devices are more and more powerful but the batteries technology is not able to follow the increase in power consumption. This leads to lower battery live.

- Thermal issues: Electronic devices with a high grade of integration are nowadays not able to work at full performance due to the impossibility of dissipating all the heat that the power dissipation creates. This make impossible to power all the devices in a system at maximum frequency.

The third point leads to the so call "Dark Silicon effect" that consist in the impossibility of power all the transistors in a chip at the same time.

To deal with this Dark Silicon effect, several approaches are been researched; been heterogeneous systems one of the most promising.

#### Microprocessor Transistor Counts 1971-2011 & Moore's Law

Introduction of CMOS over bipolar bought the industry 10 years (example: IBM mainframe processors)

[Ref: R. Chu, JEP'04]

Figure 2, power density

# 2.2 CMOS Logic

CMOS technology, or complementary metal oxide semiconductor, is a widely used technology due to the low static consumption. Since one transistor of the pair is always off, the series combination draws significant power only momentarily during switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other forms of logic.

CMOS technology also has the advantage of been extremely easy to use to create logic circuits given its logic function.

CMOS digital gates are made from analog nMOS and pMOS transistors. This means that the behaviour of the gates will have an undesired analog component despite the design. Some of this effects are raise time, fall time and leakage current.

During the creation of the gates, several parameters can be modified to try to minimize these effects being the most important the width and the length in the nMOS and pMOS transistors.

# 2.3 Power consumption in CMOS circuits

The increase of power consumption and the appearance of the dark silicon effect have led to an increase in the research of low power consumption electronic devices.

The power consumption in CMOS circuit has three causes: dynamic, static and short circuit power consumption. The total power consumption can be express as the addition of these three powers.

## Ptotal=Pdynamic+Pstatic+Pshort circuit

Technology improvements led to decreased  $C_L$ ,  $I_{sc}$  and  $I_{leakage}$  that help decreasing the power consumption and architecture design can decrease the activity reducing the power consumption even further. The problem is that the increase in the number of transistors may cause these improvements to be insufficient.

The next approach is reducing  $V_{DD}$  but it does not come without a setback. Reducing  $V_{DD}$  also reduces the speed at which the circuit can operate. This is because with lower  $V_{DD}$  the currents are smaller and it takes longer to charge the capacitances (both internal and in the load). When the voltage supply is lowered to a point where it is close or even lower than the threshold voltage we said that is operating in the near/subthreshold region.

In traditional CMOS circuits the main cause of power dissipation was the dynamic power consumption or switching power, but the appearance of newer technologies in which the leakage current increases and the dynamic power decreases has made the static power consumption an important factor to take into account. This is especially true for circuits working in the near or subthreshold region due to the increase in the delay.

## 2.3.1 Dynamic or Switching power

The dynamic power consumption or switching power is causes by the activity of charging and discharging the load capacitances when the circuits state changes.

Switching power =  $\alpha \times f_{clk} \times C_L \times V_{DD}^2$

Where:

- $\alpha$  is the activity rate of the circuit.

- $f_{clk}$  is the frequency at which the circuit is working.

- $C_L$  is the load capacitance.

- $V_{DD}$  is the voltage supply.

This source of power consumption can be easily decrease by decreasing  $V_{DD}$  and that is the objective of this thesis.

## 2.3.2 Short circuit power

The short circuit power is due to the brief period in which the NMOS and PMOS transistors in the CMOS circuits are conducting at the same time when a logic changes occur. During this time there is an open path between power supply and ground.

Short circuit power =

$$I_{sc} \times V_{DD}$$

Where:

- $I_{sc}$  is the short circuit current.

- $V_{DD}$  is the voltage supply.

This source of power consumption is the least important one and will not have a big impact in the circuit power consumption.

## 2.3.3 Static or leakage power consumption

The static or leakage power consumption is due to the leakage current that exist in the transistors. In complementary MOS technology, half of the transistors will have leakage between drain and source leading to some power consumption.

$Leakage \ power = I_{leakage} \times V_{DD}$

Where:

- $V_{DD}$  is the voltage supply.

- *I*<sub>leakage</sub> is the leakage current.

As the dynamic power decreases the leakage power takes more and more importance, been significant when working in the near/subthreshold region.

## 2.4 Near/subthreshold region

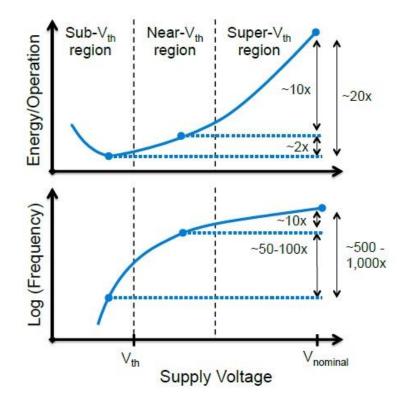

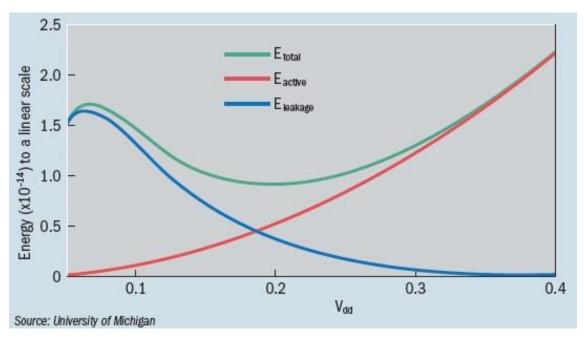

As the voltage supply is lowered the circuit power consumption decreases and so does the performance of the circuit. Due the increase in the delay of the operations the leakage power increase its importance (the operations takes longer so the transistors are leaking for more time) and, in some points in the subthreshold region, it may even be bigger than the switching power (see Figure 4).

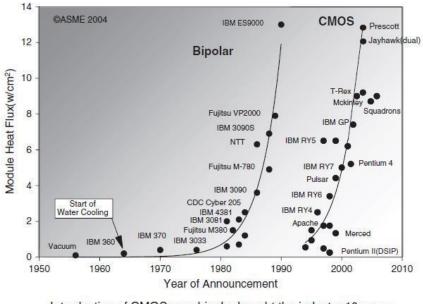

To measure the performance of a circuit we make use of two variables: the energy consumption per operation (related to the power consumption and the time it takes to realize an operation) and the frequency (the maximum speed the circuit can achieve).

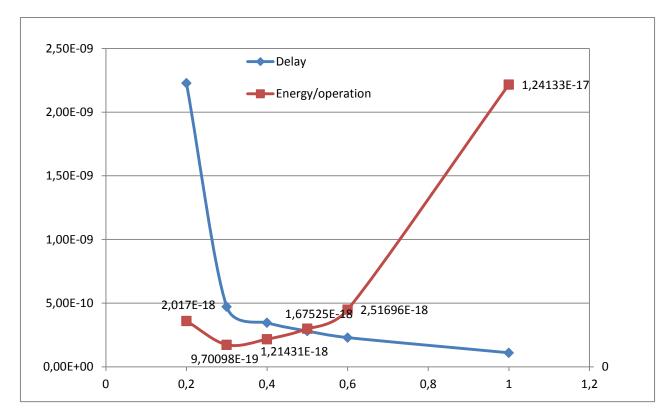

In the nearthreshold region, reducing the supply voltage led to a reduction in the energy per operation and frequency that are of the same order (see figure 3).

In the subthreshold region, reducing the supply voltage decrease the energy per operation but the frequency may decrease in a much bigger amount. If the supply voltage decrease too much, the gain obtain by the lowered switching power is counteracted by the increase in the leakage power(see figure 3).

Figure 3, energy per operation and frequency

When using near/subthreshold technology, it is important to study the speed and power consumption requirements of the system to be able to achieve the maximum energy savings with the lowest speed diminish possible.

Figure 4, energy/V<sub>dd</sub>

Near/Subthreshold technology presents other problems. The most important of this are:

- Increased performance variation.

- Increased functional failure.

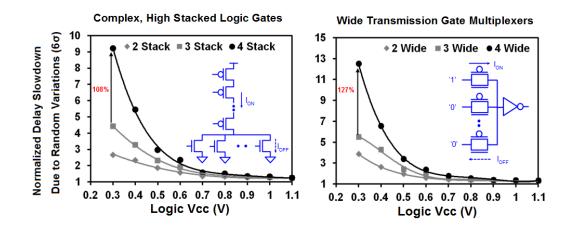

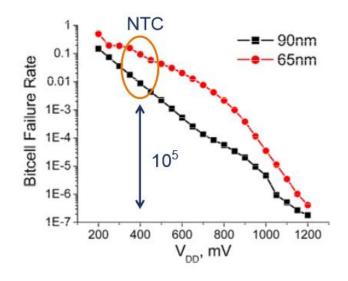

When working in near/subthreshold region small changes in the transistors can cause an important variation in the performance of the system and the possibility of a critical functional failure also increase. These problems become more and more important as the voltage supply is reduced (see figures 5 and 6).

Figure 5, variation in performance

To reduce the impact of the random variations it is important to reduce the number of transistors stacked in a gate (see Figure 5). This can be easily achieved by using only 2 or 3 input gates. The downside of this is a reduction in the optimization in the synthesis process. There are other techniques like body biasing (adjusting the threshold value for the transistors) but they are usually too expensive to be used in most systems.

Reducing the probability of failure in a circuit working in near/subthreshold voltage is difficult and expensive. The only method to ensure that there will not be many failures is used a reduced number of transistors, due to this, subthreshold voltage supply is mainly used in not very complex systems like watches or pacemakers.

# 2.5 Cell library

A cell library is a set of low level cells that can be used to synthesize larger designs.

The cells are created using standard 65nm PMOS and NMOS transistors. To create the D flip-flop the NAND and inverter gates are used.

The cells have to be able to work in near/subthreshold operation point and need to be adjusted to perform as well as possible. For this, the sizes of the transistors were modified, increasing the width of the transistors when needed. This process used feedback from the simulations

In a library is important:

-To be able to have high density. This can be achieve with a high variety of cells that allow the synthesis tool to optimize the design and with cells as regular as possible.

-To have as few parasitics as possible. This can be achieve during the layout design.

The cell library done during the specialization project consists in:

• NAND gate. The truth table is shown in Table 1.

Table 1, NAND truth table

| 2 Input NAND gate |   |     |  |  |

|-------------------|---|-----|--|--|

| Α                 | В | A.B |  |  |

| 0                 | 0 | 1   |  |  |

| 0                 | 1 | 1   |  |  |

| 1                 | 0 | 1   |  |  |

| 1                 | 1 | Ó   |  |  |

• NOR gate. The truth table is shown in Table 2.

#### Table 2, NOR truth table

| 2 Inpu | ut NOF | R gate |  |  |

|--------|--------|--------|--|--|

| A      | В      | A+B    |  |  |

| 0      | 0      | 1      |  |  |

| 0      | 1      | 0      |  |  |

| 1      | 0      | 0      |  |  |

| 1      | 1      | Ó      |  |  |

• NOT gate or inverter. The truth table is shown in Table 3.

| Table | 3,NOT | truth | table |  |

|-------|-------|-------|-------|--|

|       |       |       |       |  |

| NOT g | gate |

|-------|------|

| A     | Ā    |

| 0     | 1    |

| 1     | 0    |

• D-Latch. The truth table is shown in Table 4.

| D-l | _atcl | า               |       |

|-----|-------|-----------------|-------|

| Е   | D     | Q <sub>t+</sub> | MODE  |

| 0   | 0     | Qt              | HOLD  |

| 0   | 1     | Qt              | HOLD  |

| 1   | 0     | 0               | RESET |

| 1   | 1     | 1               | SET   |

Table 4, D-Latch truth table

These cells only consist on schematics and they need to be improve creating the layout and extracting their parasitics. During the layout creation they will also be optimize within possible with the objective of having a low power consumption and a high frequency of operation.

These cells are enough to synthesize any logic circuit but for optimization purposes another cell was created.

• XOR gate. The truth table is shown in Table 5.

| 2 Inp | ut XOR gate |     |  |

|-------|-------------|-----|--|

| A     | В           | A⊕B |  |

| 0     | 0           | 0   |  |

| 0     | 1           | 1   |  |

| 1     | 0           | 1   |  |

| 1     | 1           | 0   |  |

#### Table 5, XOR truth table

# 2.6 Layout

The logical gates do not show the true behaviour of a cell, they are only good for the logical simulation of the cell. To get the real behaviour of a cell the physical representation of the cell has to be taken into account. This is the layout level and is the lowest level of representation of a cell.

The layout is a representation of the silicon with the different layers of metal polysilicon and dopants. It also includes the contacts and vias where the cell will be connected.

To create the layout of a cell there are several rules that have to be follow. This rules included:

- Distance between layers. The minimum distance at which different layersc an be placed.

- Width areas. Minimum width that lines or areas can have.

- Contacts . The contacts have to be along the edge of the chip.

- Wells. Wells that have different potential have to be separated a minimum distance between themselves.

## 2.6.1 DRC

DRC or design rule check. Once the layout of the cell has been created we need to run the DRC. It checks that the layout follows all the design rules and shows you all the infringements that have occurred allowing easier corrections.

This is one of the most tedious steps, until you are familiarized with the rules you will commit many infringements and modifying the layout to correct them is pretty time consuming.

## 2.6.2 LVS

LVS or layout versus schematics. Once the DRC test is passed is time to place the vias. The LVS checks that the schematic model corresponds with the layout and that all the components are rightly connected. It also checks that no via or path is missing in the layout with respect the schematic.

### 2.6.3 PEX

PEX or parasitics extraction. At this point the layout is already created. The PEX extracts the parasitics of the design and integrate them into the cell. There are several parameters that can be adjusted to be more or less precise in the extraction, see Figures 7 and 8. Once that all the parameters are chosen the parasitics are extracted, see Figure 9; and the extracted view is shown, see Figure 10.

## After the PEX is done a PEX file is created. This file will be used for the simulation.

| For Help on ST SWITCHES type unix                                                | command : calibreSTSwitch  | esHelp -lvs              |

|----------------------------------------------------------------------------------|----------------------------|--------------------------|

| SWITCH FOR PEX EXTRACTION                                                        |                            |                          |

| Select Process Option                                                            | STANDARD -                 |                          |

| Select Process Corner for parasitics                                             | RCTYP -                    | 1                        |

| Select modess corner for parasities                                              |                            | 1                        |

| Enable Jivaro reduction                                                          | OFF -                      |                          |

| Spice accuracy pa                                                                | rameters management        |                          |

| Extract from layout AS AD PS PD parameters of                                    | f MOS for simulation       |                          |

| Extract from layout STI stress parameter for                                     | simulation                 |                          |

| Extract from layout NGCON parameter of MOS f                                     | or simulation              |                          |

| □ Extract from layout WPE (SCA,SCB,SCC) parame                                   | ters of MOS for simulation | n (license ADP required) |

| □ Extract from layout NRD NRS parameters of MO                                   | S for simulation           |                          |

| □ Skip ERC1 to ERC12 rules check (Wells biasin                                   | g) (sign-off)              |                          |

| □ Check ERC13 and ERC14 rules check (Connectio                                   | ns through OD/PO)          |                          |

| □ Skip ERC13 and ERC14 rule checks only ouside                                   | this marker:               | ALL_CHIP -               |

| □ Check ERC15 rules check (Floating OD-PO inte                                   | montion)                   |                          |

| Check if Nwell is connected to POWER pins                                        | Section)                   |                          |

| Check if Pwell is connected to GND pins                                          |                            |                          |

| Abort on critical ERC errors: Wells multi-co                                     |                            |                          |

| HDOrt on critical ERC errors: wells multi-co     Sense extraction and comparison | nnected                    |                          |

|                                                                                  |                            |                          |

| Analog mode (no parallel/series reduction pe                                     |                            |                          |

| Do not compare ESU and EDU of non salicided                                      |                            |                          |

| Compare area and perimeter of isolated PW to                                     | UNW diode                  |                          |

#### Figure 7, PEX parameters 1

| Tolerance for stripped stacked metal capa carea (%) 1                       |       |

|-----------------------------------------------------------------------------|-------|

| Tolerance for stripped stacked metal capa operi (%) 1                       |       |

| Tolerance for elementary fringe metal capa length (%) 1                     |       |

| Tolerance for elementary fringe metal capa finger spc (%)                   |       |

| Tolerance for stack fringe wetal capa length (%) 1                          |       |

| Tolerance for dram capacitor carea comparison (%)                           |       |

| Tolerance for dram capacitor operimeter comparison (%)                      |       |

| □ Do not filter unused devices (D AB RC RG)                                 |       |

| □ Extract and compare ebeamprobe & microprobe                               |       |

| ■ Do not extract PO/OD resistors,mim and metal capacitors on undefined bulk |       |

| $\Box$ Extract from the layout all non supported gates                      |       |

| □ Allow pins swappability for mim (not recommanded)                         |       |

| □ No extract ddnwpw under ddnwpw;nodevice (default = sign-off)              |       |

| Capacitor area comparison tolerance (%) (default = sign-off) 1              |       |

| Capacitor perim comparison tolerance (%) (default = sign-off) 1             |       |

| □ Enable electrical comparison (default = sign-off)                         |       |

| Capacitance (C) comparison tolerance (%) (default = sign-off) 1             |       |

| Resistance (R) comparison tolerance (%) (default = sign-off)                |       |

| Metal Resistance (R) comparison tolerance (%) (default = sign=off) 6        |       |

| Inductors d & w comparison tolerance (%) (default = sign-off) 0.3           |       |

| Inductors 1 comparison tolerance (%) (default = sign-off) 4                 |       |

| Inductance 1s comparison tolerance (%) (default = sign-off) 5               |       |

| Tolerance for mosRF W comparison (%) (default val = sign-off) 1             |       |

| Tolerance for mosRF L comparison (%) (default val = sign-off) 0             |       |

| Varactors w & 1 tolerance (%) (default val = sign-off) 0.1                  |       |

| Varactors capacitance tolerance (%) (default val = sign-off) 5              |       |

|                                                                             |       |

| OK                                                                          | Reset |

|                                                                             |       |

Figure 8, PEX parameters 2

| +Navigator 3**                                                                                                                                                        | 参 IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | /_gate ×   |            |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Results                                                                                                                                                               | and the second se | Layout Net | Source Net | R Count | and the second se | The second se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C+CC Total (F              |

| ↔<br>Extraction Results                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GND<br>Vdd | GND        | 8       | 6,42873E-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | and the second se | 1.14362E-16<br>1.15954E-16 |

| Comparison Results                                                                                                                                                    | 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | OUT        | OUT        | 4       | 6.53101E-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1,12513E-16<br>1,60623E-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.25933E-16                |

| * Parasitics                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IN         | IN         | 2       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1,89810E-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2,21801E-16                |

| Extraction Report     LVS Report     Separate Properties User Files     LAYOUT_PIDSP Rules     Rules File View     Info     M Finder     Schematics Setup     Options |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |            |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |

| Launch Eile E            | dit ⊻iew <u>C</u> | reate Ver <u>i</u> fy Co <u>n</u> r | ectivity Option | : <u>T</u> ools <u>W</u> indow 0 | )pti <u>m</u> ize *Design Kit Ca | libre <u>H</u> elp |            |          |                  |  | cādence |

|--------------------------|-------------------|-------------------------------------|-----------------|----------------------------------|----------------------------------|--------------------|------------|----------|------------------|--|---------|

|                          |                   | • 🛈 🔯 🗙                             | e 0 1           | ™                                | Classic                          |                    | F          |          |                  |  |         |

| F. 🤫 👙                   | +                 | <b>्</b> 🖉 🗖                        | » (F)Selec      | ::0 Sel(N):0 Sel(                | I):0 Sel(0):0 X 25.505           | Y -8,060           | dX -25,940 | dY 1.615 | Dist:25,990 Cmd: |  |         |

| Palette                  | ? ð ×             |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| Layers                   | ē ×               |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| Valid 🗌 Used             |                   |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| Filter                   | - 2               |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| M1 drawing<br>AV NV      | AS NS             |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| Nane                     | Vis Sel           |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

|                          | +-+-              |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| Layer P                  | . V S 🛆           |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| PP net                   |                   |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| PP bnd                   | ¥ ¥               |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| 0D_25 drv<br>0D25_18 drv |                   |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| 0D25_18 drv<br>RPO drv   |                   |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| HRI dru                  |                   |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| CO dru                   | <b>× ×</b>        |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| CO net<br>CO pin         |                   |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| CO pin<br>CO cte         | ele 🗹 🗹           |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| CO lil                   |                   |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| CO sra                   | nc 🗹 🗹            |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| M1. drv                  | <b>× ×</b> -      |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| bjects                   | ē×                |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| Objects                  | VSA               |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| - Instances              | × × D             |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| Pins<br>Vias             | žž,               |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

| 100                      |                   |                                     |                 |                                  |                                  |                    |            |          |                  |  |         |

## 2.6.4 Library extraction

After all the cells have pass all the test and their parasitics have been extracted, three different files are needed.

- Abstract view. Obtained by the abstract generator.

- .LEF files. These are library exchange format files . Also obtained by the abstract generator.

- .lib files contain information about the timing and functionality of the cells. They are obtained using Liberate.

# 2.7 Synthesis theory

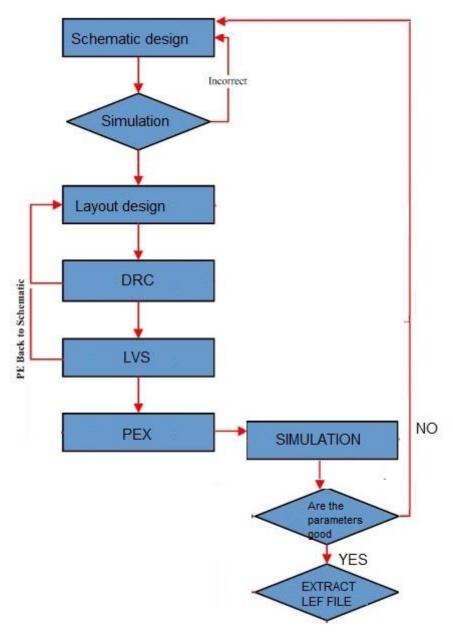

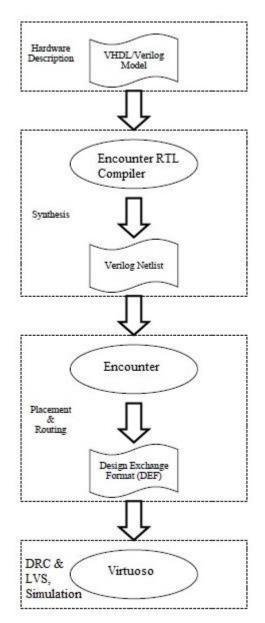

The objective of the synthesis process is to get a circuit design (in which we can do power and timing simulation) from an abstract high level model (the given Verilog code for Aurora's ALU). The synthesis process consists in different phases, see Figure 11.

Figure 11, synthesis process

## 2.7.1 Verilog and VHDL

The design to be synthesized is a 32 bits ALU. This ALU is part of the Amber open source project. This ALU supports the functions: 32-bit add and subtract, AND, OR, XOR, NOT, Zero extent 8-bit numbers.

The ALU is given in Verilog language. Verilog is a hardware description language used to model and simulate hardware designs at different level of abstraction. The ALU is given in a behavioural level of abstraction. See Appendix 2.a.

## 2.7.2 Encounter RTL compiler.

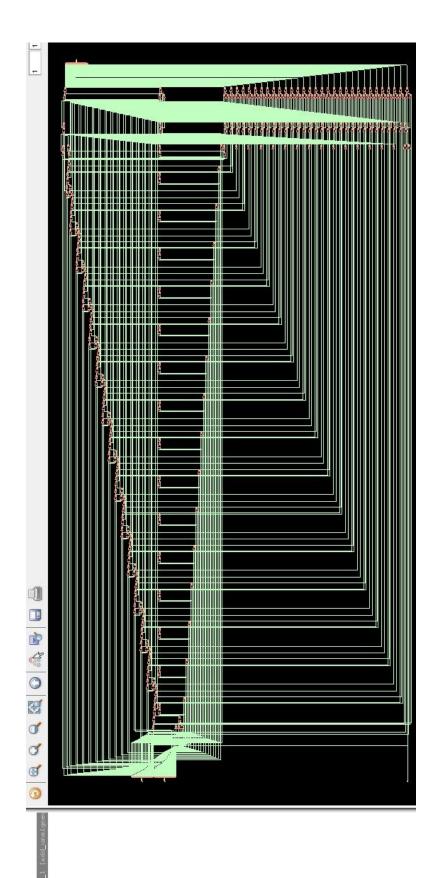

Given a Verilog behavioural description and a cell library, Encounter RTL compiler transform it into an RTL description of the circuit (written in Verilog), part of the code is shown in Apendix 2.b. This is a list of the pins, wires, components and the way they are connected between them. It is already possible to import this file to Virtuoso for verification purposes, see Apendix 2.c.

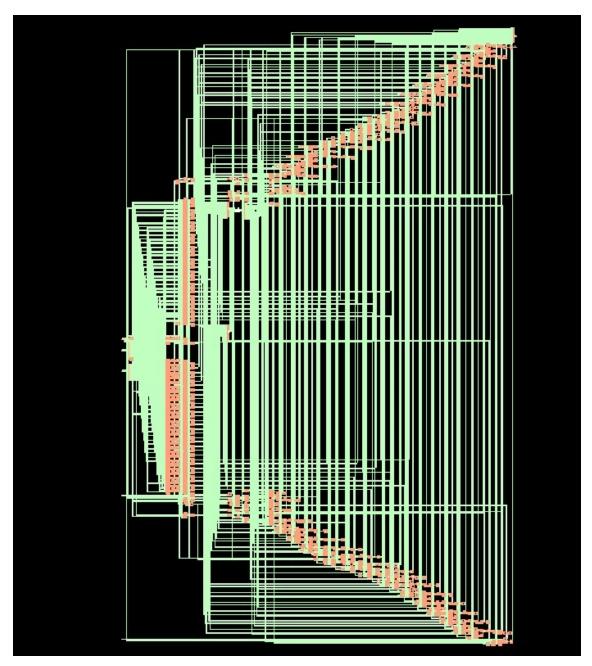

## 2.7.3 Synthesis, place and route

Once the RTL code is ready it is possible to synthesize it with the LEF file from the library. The physical properties contained in the LEF file are used in the synthesiser for the routing. The synthesis can be adjusted for different levels of optimization for a better or worse level of integration (more or less chip surface unused). This is a heavy process that takes a long time. Due to the limitation of using a common server for the synthesis instead of a dedicated computer, this process took a really long time and a good optimization was not possible.

This process results in a .DEF file (Design exchange format) which can be imported into Virtuoso.

Now The DRC and LVS test has to been pass again to make sure that the synthesized circuit follows all the design rules and the layout and schematics correspond. Now it is possible to run a simulation using ERC.

# 3 Custom design library

The library is based in the cell library done during the specialization project. It contained the inverter, NAND, NOR and D-flipflop gates and later on the XOR gate was included. The behaviour of the gates can be seen in Appendix 1.

The main data to be obtained is:

- Rise time. Time that the signal needs to get from 10% to 90% of its final value.

- Fall time. Time that the signal needs to get from 90% to 10% of its final value.

- Average power consumption. Calculated assuming that the all the values of the inputs have the same probability.

With this data other parameters have been calculated:

- Delay. Taking into account the worst case of the rise and fall time.

- Energy per operation. Using the average power consumption and the delay.

The cells have been optimized within possible by changing the width of the transistors. The main reason to do this is increase the current that is used to charge the capacitances in the cases with worst delay. See Appendix 4.a for the optimization flow.

## 3.1 Inverter

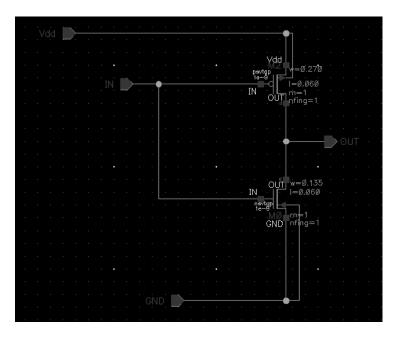

The inverter is the simplest gate that can be done (see figure 12) but it is important to adjust the sizes of the transistors to get a good characteristic curve (see figure 13).

To get a good curve the width of the PMOS was increased.

Figure 12, inverter schematics

Figure 13, inverter curve

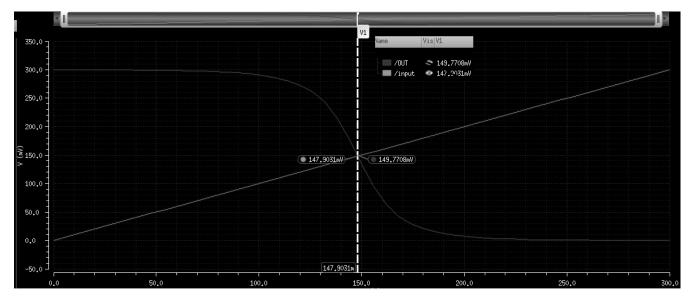

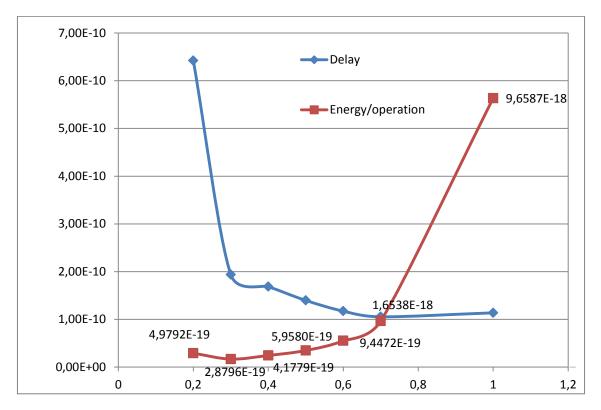

The data obtain in the inverter simulation is shown in table 1. The delay and energy per operation for the different voltages is shown in figure 12.

The worst delay in the inverter happened when the signal had to change from 0 to 1. In this case the delay was conditioned by the rise time.

| Voltage | Rise time | Fall time | Delay    | ∆delay | Average power | ∆power   | Energy/operation | ΔEnergy/operation |

|---------|-----------|-----------|----------|--------|---------------|----------|------------------|-------------------|

| 0,2     | 4,28E-10  | 3,25E-10  | 6,42E-10 | 564,9% | 7,75E-10      | 0,9127%  | 4,9792E-19       | 5,1552%           |

| 0,3     | 1,29E-10  | 1,09E-10  | 1,94E-10 | 170,3% | 1,49E-09      | 1,7502%  | 2,8796E-19       | 2,9813%           |

| 0,4     | 1,12E-10  | 9,87E-11  | 1,69E-10 | 148,3% | 2,48E-09      | 2,9167%  | 4,1779E-19       | 4,3255%           |

| 0,5     | 9,31E-11  | 8,24E-11  | 1,40E-10 | 122,9% | 4,27E-09      | 5,0200%  | 5,9580E-19       | 6,1685%           |

| 0,6     | 7,82E-11  | 7,00E-11  | 1,17E-10 | 103,1% | 8,06E-09      | 9,4856%  | 9,4472E-19       | 9,7810%           |

| 0,7     | 7,03E-11  | 6,53E-11  | 1,05E-10 | 92,7%  | 1,57E-08      | 18,4675% | 1,6538E-18       | 17,1225%          |

| 1       | 7,58E-11  | 7,33E-11  | 1,14E-10 |        | 8,50E-08      |          | 9,6587E-18       |                   |

#### Table 6, inverter without parasitics data

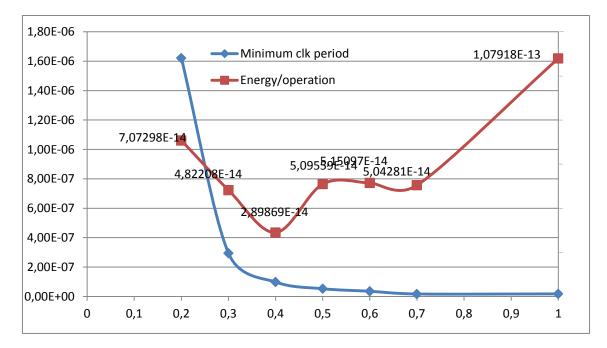

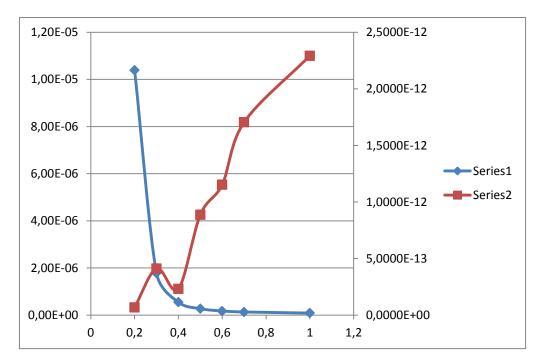

Figure 14, delay and energy/operation inverter without parasitics

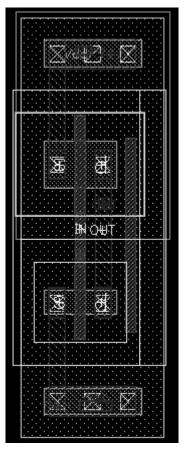

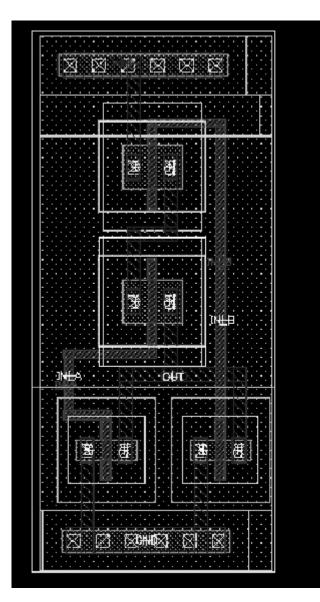

The layout is created, see Figure 15.

Figure 15, inverter layout

After the RTS and LVS test are passed, the parasitics are extracted and the data is calculated again, see table 6 and figure 16.

| Voltage | Rise time | Fall time | Delay    | ∆delay  | Average power | Δpower   | Energy/operation | ∆Energy/operation |

|---------|-----------|-----------|----------|---------|---------------|----------|------------------|-------------------|

| 0,2     | 1,08E-06  | 8,50E-07  | 1,62E-06 | 9200,0% | 4,36E-08      | 0,7124%  | 7,0730E-14       | 65,5404%          |

| 0,3     | 1,96E-07  | 1,48E-07  | 2,94E-07 | 1667,2% | 1,64E-07      | 2,6801%  | 4,8221E-14       | 44,6829%          |

| 0,4     | 6,57E-08  | 4,91E-08  | 9,86E-08 | 559,4%  | 2,94E-07      | 4,8016%  | 2,8987E-14       | 26,8602%          |

| 0,5     | 3,51E-08  | 2,51E-08  | 5,26E-08 | 298,6%  | 9,68E-07      | 15,8109% | 5,0956E-14       | 47,2173%          |

| 0,6     | 2,37E-08  | 1,71E-08  | 3,55E-08 | 201,3%  | 1,45E-06      | 23,7139% | 5,1510E-14       | 47,7305%          |

| 0,7     | 9,67E-09  | 1,14E-08  | 1,70E-08 | 96,6%   | 2,96E-06      | 48,3750% | 5,0428E-14       | 46,7282%          |

| 1       | 1,18E-08  | 9,32E-09  | 1,76E-08 |         | 6,12E-06      |          | 1,0792E-13       |                   |

Table 7, inverter without parasitics data

Figure 16, delay and energy/operation inverter with parasitics

## 3.2 NAND Gate

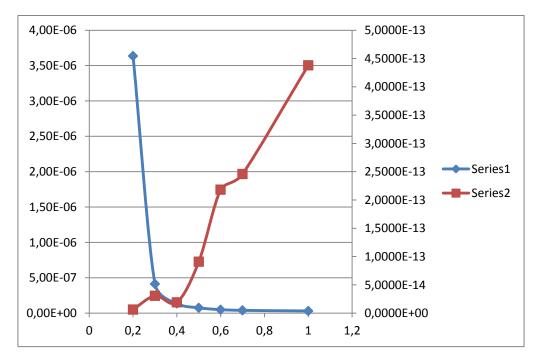

The data obtain in the NAND gate simulation is shown in table 8. The delay and energy per operation for the different voltages is shown in figure 13.

The worst delay in this gate happened when the signal had to change from 1 to 0. In this case the delay was conditioned by the fall time.

| Voltage | Rise time | Fall time | Delay    | ∆delay  | Average power | Δpower   | Energy/operation | ΔEnergy/operation |

|---------|-----------|-----------|----------|---------|---------------|----------|------------------|-------------------|

| 0,2     | 3,99E-10  | 9,04E-10  | 1,36E-09 | 1088,7% | 6,58E-10      | 1,6303%  | 8,9195E-19       | 17,7488%          |

| 0,3     | 1,46E-10  | 1,78E-10  | 2,67E-10 | 214,1%  | 1,26E-09      | 3,1219%  | 3,3585E-19       | 6,6831%           |

| 0,4     | 1,23E-10  | 1,21E-10  | 1,84E-10 | 147,9%  | 2,06E-09      | 5,1041%  | 3,7945E-19       | 7,5506%           |

| 0,5     | 1,04E-10  | 9,84E-11  | 1,56E-10 | 125,2%  | 3,14E-09      | 7,7800%  | 4,8937E-19       | 9,7379%           |

| 0,6     | 9,07E-11  | 8,28E-11  | 1,36E-10 | 109,3%  | 5,59E-09      | 13,8528% | 7,6057E-19       | 15,1345%          |

| 0,7     | 8,03E-11  | 8,28E-11  | 1,24E-10 | 99,7%   | 8,28E-09      | 20,5154% | 1,0283E-18       | 20,4610%          |

| 1       | 8,20E-11  | 8,30E-11  | 1,25E-10 |         | 4,04E-08      |          | 5,0254E-18       |                   |

#### Table 8, NAND without parasitics data

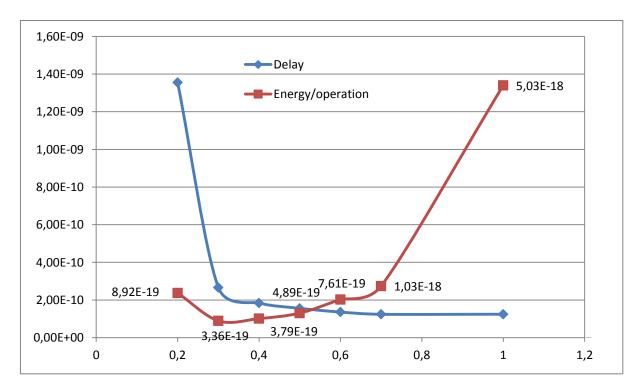

Figure 17, delay and energy/operation inverter without parasitics

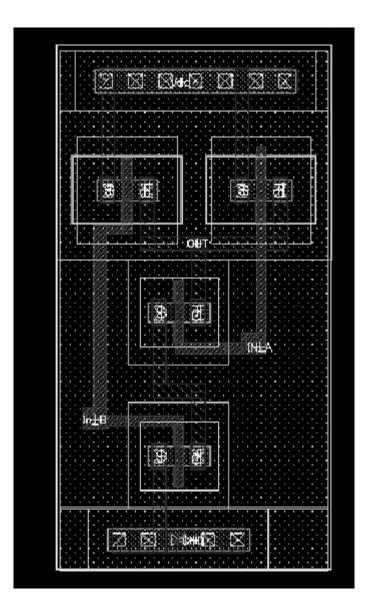

The layout is created, see Figure 18.

After the RTS and LVS test are passed, the parasitics are extracted and the data is calculated again, see table 9 and figure 19.

Figure 18, NAND layout

### Table 9, NAND with parasitics data

| Voltage | Rise time | Fall time | Delay    | ∆delay   | Average power | ∆power   | Energy/operation | ∆Energy/operation |

|---------|-----------|-----------|----------|----------|---------------|----------|------------------|-------------------|

| 0,2     | 6,52E-07  | 1,92E-06  | 2,87E-06 | 11785,2% | 1,29E-09      | 0,0254%  | 3,7172E-15       | 2,9984%           |

| 0,3     | 1,28E-07  | 3,28E-07  | 4,92E-07 | 2017,2%  | 4,53E-08      | 0,8903%  | 2,2264E-14       | 17,9591%          |

| 0,4     | 4,86E-08  | 1,02E-07  | 1,53E-07 | 628,3%   | 8,21E-08      | 1,6144%  | 1,2575E-14       | 10,1436%          |

| 0,5     | 2,79E-08  | 5,05E-08  | 7,58E-08 | 311,0%   | 6,33E-07      | 12,4499% | 4,7993E-14       | 38,7133%          |

| 0,6     | 1,95E-08  | 3,23E-08  | 4,84E-08 | 198,6%   | 2,26E-06      | 44,4554% | 1,0944E-13       | 88,2815%          |

| 0,7     | 1,53E-08  | 2,48E-08  | 3,71E-08 | 152,4%   | 2,48E-06      | 48,8006% | 9,2181E-14       | 74,3571%          |

| 1       | 1,09E-08  | 1,63E-08  | 2,44E-08 |          | 5,09E-06      |          | 1,2397E-13       |                   |

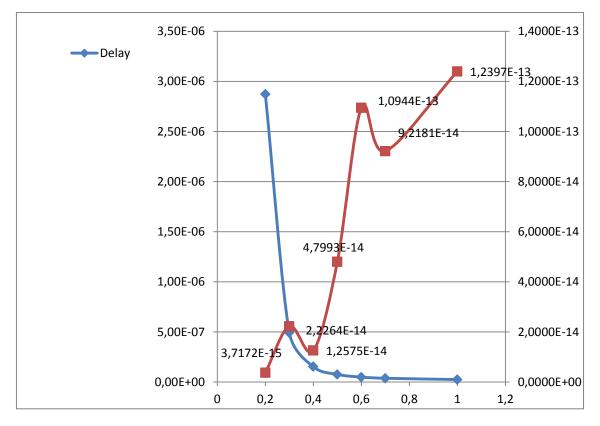

Figure 19, delay and energy/operation NAND with parasitics

# 3.3 NOR Gate

The data obtain in the NOR gate simulation is shown in table 10. The delay and energy per operation for the different voltages is shown in figure 20.

The worst delay in this gate happened when the signal had to change from 0 to 1. In this case the delay was conditioned by the fall time.

| Voltage | Rise time | Fall time | Delay    | ∆delay  | Average power | ∆power   | Energy/operation | ΔEnergy/operation |

|---------|-----------|-----------|----------|---------|---------------|----------|------------------|-------------------|

| 0,2     | 1,49E-09  | 4,74E-10  | 2,23E-09 | 2018,8% | 9,06E-10      | 0,8049%  | 2,0170E-18       | 16,2488%          |

| 0,3     | 3,14E-10  | 1,21E-10  | 4,71E-10 | 427,0%  | 2,06E-09      | 1,8302%  | 9,7010E-19       | 7,8150%           |

| 0,4     | 2,31E-10  | 1,03E-10  | 3,47E-10 | 314,2%  | 3,50E-09      | 3,1138%  | 1,2143E-18       | 9,7824%           |

| 0,5     | 1,87E-10  | 9,08E-11  | 2,81E-10 | 254,5%  | 5,97E-09      | 5,3031%  | 1,6753E-18       | 13,4957%          |

| 0,6     | 1,53E-10  | 7,81E-11  | 2,30E-10 | 208,1%  | 1,10E-08      | 9,7422%  | 2,5170E-18       | 20,2764%          |

| 0,7     | 1,37E-10  | 7,09E-11  | 2,06E-10 | 186,7%  | 2,09E-08      | 18,5689% | 4,3023E-18       | 34,6589%          |

| 1       | 147,22-12 | 7,36E-11  | 1,10E-10 |         | 1,13E-07      |          | 1,2413E-17       |                   |

Table 10, NOR without parasitics data

Figure 20, NOR delay and energy/operation inverter without parasitics

The layout is created, see Figure 22.

After the RTS and LVS test are passed, the parasitics are extracted and the data is calculated again, see table 10 and figure 23.

Figure 22, NOR layout

| Voltage | <b>Rise time</b> | Fall time | Delay    | ∆delay   | Average p | ∆power   | Energy/operat | ∆Energy/operation |

|---------|------------------|-----------|----------|----------|-----------|----------|---------------|-------------------|

| 0,2     | 2,42E-06         | 1,00E-06  | 3,64E-06 | 11767,2% | 1,78E-09  | 0,0126%  | 6,4748E-15    | 1,4781%           |

| 0,3     | 2,75E-07         | 2,22E-07  | 4,13E-07 | 1337,3%  | 7,40E-08  | 0,5219%  | 3,0576E-14    | 6,9797%           |

| 0,4     | 9,14E-08         | 8,69E-08  | 1,37E-07 | 443,8%   | 1,40E-07  | 0,9849%  | 1,9148E-14    | 4,3710%           |

| 0,5     | 5,03E-08         | 4,66E-08  | 7,55E-08 | 244,4%   | 1,20E-06  | 8,4863%  | 9,0845E-14    | 20,7380%          |

| 0,6     | 3,28E-08         | 3,04E-08  | 4,93E-08 | 159,4%   | 4,43E-06  | 31,2640% | 2,1830E-13    | 49,8324%          |

| 0,7     | 2,62E-08         | 2,12E-08  | 3,93E-08 | 127,2%   | 6,26E-06  | 44,1705% | 2,4611E-13    | 56,1807%          |

| 1       | 2,06E-08         | 1,44E-08  | 3,09E-08 |          | 1,42E-05  |          | 4,3806E-13    |                   |

Figure 22 NOR delay and energy/operation inverter with parasitics

# 3.4 D-Flipflop

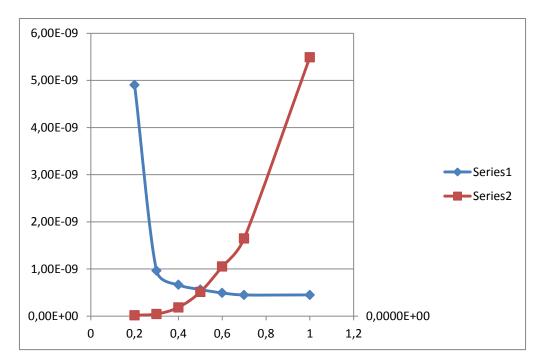

For the purpose of this project the propagation delay has been considered a ten percent of the clock period; the D signal has been set for a five percent of the clock cycle. This allows us to directly simulate the circuit with different frequencies to see when it start failing.

The data obtain in the flip-flop simulation is shown in table 11. The delay and energy per operation for the different voltages is shown in figure 23.

| Voltage | Minimum  | ∆minperiod | Average power | ∆power   | Energy/operation | ∆Energy/opera | ∆maxfrequency |

|---------|----------|------------|---------------|----------|------------------|---------------|---------------|

| 0,2     | 4,90E-09 | 1088,7%    | 3,36E-09      | 0,0337%  | 8,3907E-17       | 0,3667%       | 9,2%          |

| 0,3     | 9,64E-10 | 214,1%     | 6,44E-09      | 0,3810%  | 1,8662E-16       | 0,8157%       | 46,7%         |

| 0,4     | 6,66E-10 | 147,9%     | 1,05E-08      | 2,2854%  | 7,7349E-16       | 3,3808%       | 67,6%         |

| 0,5     | 5,64E-10 | 125,2%     | 1,60E-08      | 7,4652%  | 2,1378E-15       | 9,3439%       | 79,9%         |

| 0,6     | 4,92E-10 | 109,3%     | 2,86E-08      | 17,5511% | 4,3870E-15       | 19,1749%      | 91,5%         |

| 0,7     | 4,49E-10 | 99,7%      | 4,23E-08      | 30,0899% | 6,8660E-15       | 30,0102%      | 100,3%        |

| 1       | 4,51E-10 | 100,0%     | 2,06E-07      |          | 2,2879E-14       |               | 100,0%        |

| Table 11, | <b>D-Flipflop</b> | without | parasitics | data |

|-----------|-------------------|---------|------------|------|

|-----------|-------------------|---------|------------|------|

Figure 23, D-Flipflop delay and energy/operation inverter without parasitics

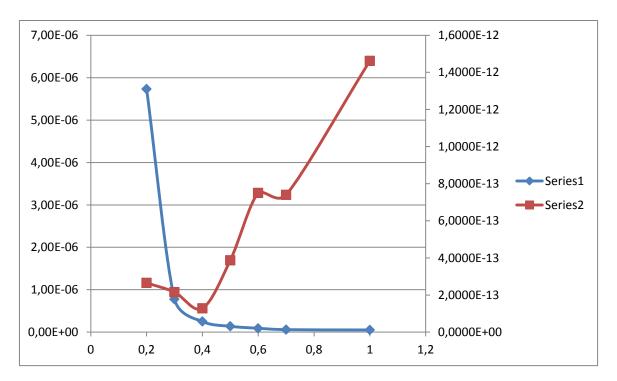

We simulate the D-Flipflop again using the version of the NAND and inverter with parasitics. The data obtain is shown in table 12. The delay and energy per operation for the different voltages is shown in figure 24.

| Voltage | Minimum  | ∆minperiod | Average power | ∆power | Energy/operation | ∆Energy/operation | ∆maxfrequency |

|---------|----------|------------|---------------|--------|------------------|-------------------|---------------|

| 0,2     | 1,04E-05 | 11785,2%   | 6,61E-09      | 0,0%   | 6,8743E-14       | 3,0%              | 0,8%          |

| 0,3     | 1,78E-06 | 2017,2%    | 2,31E-07      | 0,9%   | 4,1173E-13       | 18,0%             | 5,0%          |

| 0,4     | 5,54E-07 | 628,3%     | 4,20E-07      | 1,6%   | 2,3255E-13       | 10,1%             | 15,9%         |

| 0,5     | 2,74E-07 | 311,0%     | 3,24E-06      | 12,4%  | 8,8755E-13       | 38,7%             | 32,2%         |

| 0,6     | 1,75E-07 | 198,6%     | 1,16E-05      | 44,5%  | 1,1538E-12       | 50,3%             | 50,4%         |

| 0,7     | 1,34E-07 | 152,4%     | 1,27E-05      | 48,8%  | 1,7047E-12       | 74,4%             | 65,6%         |

| 1       | 8,82E-08 | 100,0%     | 2,60E-05      | 100,0% | 2,2926E-12       | 100,0%            | 100,0%        |

Figure 20, D-Flipfop delay and energy/operation inverter with parasitics

## 3.5 XOR

This gate did not exist in the previous library; it is an addition to improve the synthesis optimization. The results displayed are directly the ones obtain after extracting the parasitics from the layout, see table 13 and figure 25.

| Voltage | Rise time | Fall time | Delay    | ∆delay                                | Average power | ∆power   | Energy/operation | ∆Energy/operation |

|---------|-----------|-----------|----------|---------------------------------------|---------------|----------|------------------|-------------------|

| 0,2     | 3,82E-06  | 3,01E-06  | 5,73E-06 | 10906,1%                              | 4,63E-08      | 0,1665%  | 2,6558E-13       | 18,1638%          |

| 0,3     | 5,07E-07  | 5,18E-07  | 7,77E-07 | 1478,6%                               | 2,77E-07      | 0,9968%  | 2,1549E-13       | 14,7383%          |

| 0,4     | 1,69E-07  | 1,64E-07  | 2,54E-07 | 482,6%                                | 5,08E-07      | 1,8247%  | 1,2875E-13       | 8,8056%           |

| 0,5     | 9,20E-08  | 8,22E-08  | 1,38E-07 | 262,6%                                | 2,81E-06      | 10,0979% | 3,8768E-13       | 26,5146%          |

| 0,6     | 6,08E-08  | 5,36E-08  | 9,11E-08 | 173,4%                                | 8,24E-06      | 29,6027% | 7,5071E-13       | 51,3436%          |

| 0,7     | 3,93E-08  | 3,93E-08  | 5,90E-08 | 112,3%                                | 1,25E-05      | 45,0956% | 7,4031E-13       | 50,6325%          |

| 1       | 3,50E-08  | 2,77E-08  | 5,25E-08 | · · · · · · · · · · · · · · · · · · · | 2,78E-05      |          | 1,4621E-12       |                   |

#### Table 13, XOR with parasitics data

Figure 21, delay and energy/operation XOR with parasitics

## 3.6 Extraction

Now that all the cells in the library are created and their parasitics are extracted we proceed to extract the LEF file.

# 4 Synthesis process

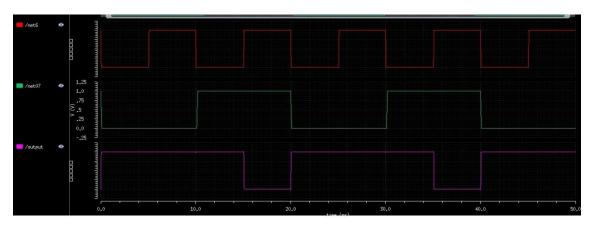

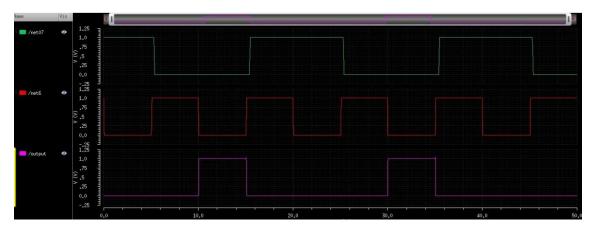

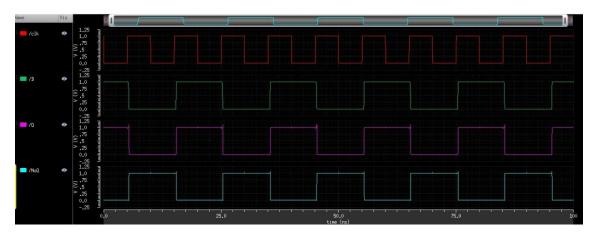

As expected, we obtain 0101 0100 0100 0001 0001 0001 0000  $|_b$  (54411110  $|_h)$  in the output (o\_out).

|  | a a a a a a                                    |         |  |  |

|--|------------------------------------------------|---------|--|--|

|  |                                                | · · · · |  |  |

|  |                                                |         |  |  |

|  | i_status_bits_carry a25_alu<br>i_function<8:0> |         |  |  |

|  |                                                |         |  |  |

Figure 26, ALU symbol

With the LEF files and the RTL code we start the place and route. We export the DEF file. See Appendix 2.d.

The circuit pass both the DRC and the LVS.

We proceed to measure the delay and the energy for this operation. The data is obtained for the ALU working at 1V, 0.5V, 0.4V and 0.3V. All operations have been made considering that the ALU is working at normal temperature (27°C), see table 14.

| Voltage | Delay    | ∆delay | Average<br>power | Energy/operation | ∆Energy/operation |

|---------|----------|--------|------------------|------------------|-------------------|

| 1V      | 8,01E-08 |        | 0,0026           | 2,08E-10         |                   |

| 0.5V    | 4,01E-07 | 5,01   | 0,000434724      | 1,74E-10         | 0,84              |

| 0.4V    | 1,06E-06 | 13,28  | 6,62789E-05      | 7,04E-11         | 0,34              |

| 0.3V    | 5,19E-06 | 64,93  | 6,94424E-05      | 3,61E-10         | 1,73              |

#### Table 14, ALU results

# **5** Discussion

## 5.1 Library

Including the parasitics in the gates has increase the delay of the cells and the power consumption in at least one order of magnitude. This proves that the parasitics effects should not be dismiss and it has proven especially significant for lower voltages.

### 5.1.1 Inverter

The inverter has the minimum energy/operation when working with four hundred milivolts supply (see figure 16 and table 7). A four hundred milivolts supply voltage would be the best operation point.

In this operation point:

- The energy per operations of the inverter is 26,86% of the energy per operation with one volt supply voltage.

- The delay is 559,4% of the delay with one volt supply voltage.

The cell may still be useful for near/subthreshold voltages supplies but the increase in the delay is significant and the reduction in energy per operation is not so significant.

### 5.1.2 NAND

The NAND gate has the minimum energy/operation when working with two hundred milivolts supply (see figure 19 and table 9). But in this point the delay has increased more than a hundred times and, despite the energy per operation been significantly lower, this delay is too big to work with. For this reason the best operation point would be a four hundred milivolts supply voltage.

In this operation point:

- The energy per operations of the NAND is 10,14% of the energy per operation with one volt supply voltage.

- The delay is 628,3% of the delay with one volt supply voltage.

The cell behavior in four hundred milivolts is pretty good being the reduction in energy per operation significantly bigger than the increase in the delay of the cell.

### 5.1.3 NOR

The NOR gate has the minimum energy/operation when working with two hundred milivolts supply (see figure 22 and table 10). But at this point the difference in energy per operation respect when working at three or four hundred milivolts is insignificant when compare with the huge increase in the delay. Four hundred milivolts is the next minimum in the energy per operation and has less delay than with three hundred milivolts, so we select four hundred milivolts as best operational point.

- The energy per operations of the NOR is 4,37 % of the energy per operation with one volt supply voltage.

- The delay is 443,8% of the delay with one volt supply voltage.

The cell behavior in four hundred milivolts is pretty good being the reduction in energy per operation significantly bigger than the increase in the delay of the cell.

### 5.1.4 D-Flipflop

The D-Flipflop has the minimum energy/operation when working with two hundred milivolts supply (see figure 24 and table 12). But in this point the maximum working frequency of the D-Flipflop is only 0,8% of the frequency when working using one volt power supply, despite the energy per operation been significantly lower. For this reason the best operation point would be a four hundred milivolts supply voltage.

In this operation point:

- The energy per operations of the D-Flipflop is 10,1% of the energy per operation with one volt supply voltage.

- The maximum frequency is 15,9% of the maximum frequency with one volt supply voltage.

The cell behavior in four hundred milivolts is acceptable been the decrease in energy per operation worth the decrease in maximum frequency.

### 5.1.5 XOR

The XOR gate has its minimum energy/operation when working with four hundred milivolts supply (see figure 25 and table 13). A four hundred milivolts supply voltage would be the best operation point.

In this operation point:

• The energy per operations of the XOR is 8,08% of the energy per operation with one volt supply voltage.

• The delay is 482,6% of the delay with one volt supply voltage.

The cell behavior in four hundred milivolts is pretty good being the reduction in energy per operation significantly bigger than the increase in the delay of the cell.

## 5.2 Synthesis

The results of simulating the synthesized ALU with parasitics for near threshold voltages are not as good as expected see table 14.

The best reduction in energy per operation occurs for four hundred millivolts, the voltage supply at which the library cells had a better behaviour. For this voltage supply:

- The energy per operation one third of the energy per operation with one volt voltage supply.

- The delay in the operation is 13,28 times the delay of the circuit with one volt power supply.

There may be many causes for these results:

- The use of only two inputs gates in the custom library make the synthesis tool use large areas (more gates) and increase the power consumption, including new cells in the library will improve both delay and power consumption but on the other hand it may cause the reliability of the circuit to decrease when working in the near/subthreshold area.

- The simulation was done for the worst case scenario, that means that the circuit will almost always have better results than showed.