### Channel Filter Cross-Layer Optimization

Joar Nikolai Talstad

Master of Science in ElectronicsSubmission date:June 2015Supervisor:Snorre Aunet, IETCo-supervisor:Isael Diaz, Nordic Semiconductor<br/>Jan Egil Øye, Nordic Semiconductor

Norwegian University of Science and Technology Department of Electronics and Telecommunications

| Title:   | Channel Filter Cross-Layer Optimization |

|----------|-----------------------------------------|

| Student: | Joar Nikolai Talstad                    |

#### Problem description:

The objective of this project is to analyze a channel filter in a number of designdimensions, in order to arrive to an ultimate solution that is re-configurable and can potentially have low energy consumption and good performance at the cost of moderate complexity increase. The goal is the final implementation of a channel filter that compared to state-of-the-art in literature: consumes less energy, presents the same performance, does not occupy more than 30% additional footprint. The configuration time should not be longer than 2 clock cycles.

The methodology to be used consists of running multiple times a short design cycle with initial constraints. A candidate implementation is generated at the end of every cycle and saved for posterior evaluation. A comparison between the various implementation candidates is done by comparing each solution in terms of cost and performance. Finally, a number of candidates that best suit the initial constraints are merged into a single reconfigurable architecture. In this manner the final solution can adapt itself to the computational requirements in real time.

| Responsible professor: | Snorre Aunet, IET                  |

|------------------------|------------------------------------|

| Supervisors:           | Jan Egil Øye, Nordic Semiconductor |

|                        | Isael Diaz, Nordic Semiconductor   |

#### Abstract

The recent raise of Internet of Things has increased the demand of energy-efficient wireless devices. However, the design process of a lowenergy, high-performance device for all operational cases is not trivial. Thus, in this thesis a cross layer optimization technique called algorithmarchitecture co-design is used to optimize one of the most critical DSP blocks in any communication device, namely, the channel filter.

In order to effectively trade between similar RTL designs in terms of area and power dissipation, a fully automated tool-flow is created which performs RTL-simulation, synthesis, layout and power analysis. The tool-flow provides the results of a 500 gate design in less than 5 minutes, running on a computer of the current industry standard, and is considered to be very accurate based on the results of a previous study.

A digital low pass filter is first optimized through a constructed filter sorting algorithm. It generates a large number of theoretical filter solutions and sorts them based on how eligible they are for hardware implementation. The algorithm is made generic, and hence applicable for any filter requirement, and proves to find the most energy-efficient solution.

The hardware architecture of the most effective filter implementation is then thoroughly analyzed in two stages. Firstly, in order to find the filter's most effective quantization levels, and secondly, in order to make the architecture dynamic with regards to filter performance and power dissipation. In the latter, two main approaches are proposed.

The first approach adapts the filter order, and hence the stopband attenuation, according to the quality of the radio link. The best implementation of this approach manages to reduce the power dissipation of 28%, 55% and 88% for the constructed low power modes, with an increase of only 8% in area compared to the non-dynamic implementation.

The second approach adapts the quantization level, and hence the amount of noise introduced by the filter, according to the radio link. Here, the best implementation reduces the power dissipation of 11%, 32% and 81% for the low power modes, while increasing the area of only 18%.

#### Sammendrag

Konseptet Internet of Things har de siste årene økt etterspørselen av energieffektive, trådløse enheter. Å utvikle systemer som tilbyr lavt effektforbruk og høy ytelse for ethvert funksjonsområde er imidlertid ingen triviell oppgave. Denne oppgaven anvender derfor en kryssoptimaliseringsteknikk kalt algorithm-architecture co-design for å optimalisere en av de mest kritiske DSP-blokkene i ethvert kommunikasjons-system, nemlig kanalfilteret.

For å effektivt kunne veie like RTL design opp mot hverandre når det gjelder areal og effekttap, er det laget en automatisk verktøy-flyt som utfører RTL-simulering, syntese, layout og power analyse. Verktøy-flyten gir resultater fra et 500 gate design på mindre enn 5 minutter når den kjører på en datamaskin av dagens industristandard, og anses å være nøyaktig basert på resultater fra en tidligere studie.

Et digitalt lavpass-filter er først optimalisert gjennom en konstruert filtersorterings-algoritme. Den genererer et stort antall teoretiske filterløsninger og sorterer dem basert på hvor egnet de er for hardwareimplementasjon. Algoritmen er generisk, og derfor anvendelig for alle filter-spesifikasjoner, og viser seg å finne den mest energieffektive løsningen.

Hardware-arkitekturen til den mest effektive filter-implementasjonen er deretter nøye analysert i to steg. Først for å finne filterets mest effektive kvantiseringsnivå, og deretter for å gjøre arkitekturen dynamisk med hensyn til filter-ytelse og effekttap. I det sistnevnte er det foreslått to hovedtilnærminger.

Den første tilnærmingen tilpasser filterets orden, og dermed dempningen i stopp-bånd, i henhold til kvaliteten på radioforbindelsen. Den beste implementasjonen av denne tilnærmingen reduserer effekttapet med 28%, 55% og 88% for de konstruerte laveffekt-modusene, med en økning i areal på bare 8% sammenlignet med den ikke-dynamiske implementasjonen.

Den andre tilnærmingen tilpasser kvantiseringsnivået, og dermed mengden støy introdusert av filteret, i henhold til radioforbindelsen. Her gir den beste implementasjonen en reduksjon i effekttap på 11%, 32% og 81% for de forskjellige laveffekt-modusene, med en økning på bare 18% i areal.

#### Preface

This thesis completes a Master of Science degree in Electronics, Design of Digital Systems, submitted to the Department of Electronics and Telecommunications at the Norwegian University of Science and Technology. The assignment was given by Nordic Semiconductor in January 2015, and the work was completed in June the same year.

Working with this thesis has been very interesting, but also challenging and time-consuming, as it required me to familiarize with a lot of different CAD tools, as well as theory regarding digital signal processing. The work has given me insight in modern IC development, and practice in designing and implementing low-power oriented systems, which I think will be useful in the future.

Firstly, I would like to thank my supervisor Professor Snorre Aunet at NTNU for his help and guidance throughout this last semester. I would also like to thank my supervisors at Nordic Semiconductor, Jan Egil Øye and Isael Diaz. Your continuous feedback throughout this process has been invaluable for me, and for that I am very grateful. Finally, I wish to thank my family for their support, and my fiancé Sissel Klakegg for all her love and encouragement over these 5 years.

Trondheim, 2015-6-10

Joar Nikolai Talstad

## Contents

| Li       | st of | Figures                                              | xi   |

|----------|-------|------------------------------------------------------|------|

| Li       | st of | Tables                                               | xv   |

| Li       | st of | Acronyms                                             | xvii |

| 1        | Intr  | oduction                                             | 1    |

|          | 1.1   | Motivation                                           | . 1  |

|          | 1.2   | Algorithm-architecture co-design                     | . 2  |

|          | 1.3   | Previous work                                        |      |

|          | 1.4   | Objectives                                           |      |

|          | 1.5   | Thesis overview                                      | . 3  |

| <b>2</b> | Bac   | ground and Theory                                    | 5    |

|          | 2.1   | The channel filter in wireless communication systems | . 5  |

|          | 2.2   | Digital filters                                      | . 6  |

|          |       | 2.2.1 FIR filters                                    | . 7  |

|          |       | 2.2.2 IIR filters                                    | . 8  |

|          | 2.3   | Quantization noise                                   | . 12 |

|          |       | 2.3.1 Truncation                                     | . 13 |

|          |       | 2.3.2 Rounding                                       | . 13 |

|          | 2.4   | CMOS Power Dissipation                               | . 14 |

|          |       | 2.4.1 Static Power                                   | . 14 |

|          |       | 2.4.2 Dynamic Power                                  | . 15 |

|          | 2.5   | Low power techniques                                 | . 16 |

|          |       | 2.5.1 Clock gating                                   | . 16 |

|          |       | 2.5.2 Datapath gating                                | . 16 |

|   |     | 2.5.3   | Power gating                                                                  | 17            |

|---|-----|---------|-------------------------------------------------------------------------------|---------------|

| 3 | Aut | omate   | ed area and power estimating tool-flow                                        | 19            |

|   | 3.1 | The s   | teps of a complete design cycle                                               | 2             |

|   |     | 3.1.1   | RTL Design                                                                    | 20            |

|   |     | 3.1.2   | Commands in terminal                                                          | 20            |

|   |     | 3.1.3   | Simulation                                                                    | 20            |

|   |     | 3.1.4   | Synthesis                                                                     | 2             |

|   |     | 3.1.5   | Layout                                                                        | 2             |

|   |     | 3.1.6   | Power Analysis                                                                | 2             |

|   |     | 3.1.7   | Visualization in Matlab                                                       | $2^{4}$       |

| 4 | Aut | omate   | ed filter generation and eligibility calculation                              | 2             |

|   | 4.1 |         | nated filter generation                                                       | 2!            |

|   |     | 4.1.1   | Filter requirements                                                           | 20            |

|   |     | 4.1.2   | Filter type                                                                   | 2             |

|   |     | 4.1.3   | Filter structure                                                              | 2             |

|   |     | 4.1.4   | Filter generating algorithm                                                   | $\frac{2}{2}$ |

|   | 4.2 |         | cient quantization algorithm                                                  | 2             |

|   | 4.3 |         | pility calculation                                                            | 3             |

|   | 1.0 | 4.3.1   | Characteristics                                                               | 3             |

|   |     | 4.3.2   | Eligibility function                                                          | 3             |

|   | 4.4 |         | ts of the AFGEC                                                               | 3             |

|   | 4.4 | 4.4.1   | Winner candidates from the AFGEC                                              | 3             |

|   |     | 4.4.1   | Conclusion of the AFGEC                                                       | 3             |

| _ | DT  | r · · · |                                                                               |               |

| 5 |     | -       | lementation of winner candidates                                              | 4             |

|   | 5.1 |         | ework                                                                         | 4             |

|   | 5.2 |         | cients                                                                        | 4             |

|   | 5.3 |         | r scenarios                                                                   | 4             |

|   | 5.4 |         | ts of the RTL implementations                                                 | 4             |

|   |     | 5.4.1   | Conclusion of the RTL implementations                                         | 4             |

| 6 | Qua |         | tion level exploration                                                        | 4             |

|   | 6.1 | Quant   | tization noise analysis                                                       | 4             |

|   | 6.2 | Imple   | mentation                                                                     | 5             |

|   | 6.3 | Result  | ts of the quantization level exploration $\ldots \ldots \ldots \ldots \ldots$ | 5             |

|   |     | 6.3.1   | Conclusion of the quantization level exploration                              | 5             |

| 7 | Dyi | namic   | RTL                                                                           | 5             |

|   | 7.1 |         | mentation                                                                     | 5             |

|   |     | 7.1.1   | Modes of performance                                                          | 5             |

|   |     | 7.1.2   | Dynamic filter order                                                          | 5             |

|   |     |         | v · · · · · · · · · · · · · · · · · · ·                                       |               |

|    |       | 7.1.3   | Dynamic quantization noise                                                           | 60  |

|----|-------|---------|--------------------------------------------------------------------------------------|-----|

|    |       | 7.1.4   | Power gating                                                                         | 62  |

|    | 7.2   | Result  | ts of the dynamic implementations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 63  |

|    |       | 7.2.1   | Dynamic filter order results                                                         | 63  |

|    |       | 7.2.2   | Dynamic quantization noise results                                                   | 67  |

|    |       | 7.2.3   | Power gating results                                                                 | 70  |

|    |       | 7.2.4   | Conclusion of the dynamic implementations                                            | 70  |

| 8  | Dise  | cussior | 1                                                                                    | 73  |

|    | 8.1   | Algori  | thm-architecture co-design and platform level implementation                         | 73  |

|    | 8.2   | Evalua  | ation of dynamic implementations                                                     | 74  |

|    |       | 8.2.1   | Dynamic order                                                                        | 74  |

|    |       | 8.2.2   | Dynamic noise                                                                        | 74  |

|    |       | 8.2.3   | Possible combined solution                                                           | 75  |

|    | 8.3   | Thoug   | ghts around future work                                                              | 76  |

|    |       | 8.3.1   | Fine-tune the AFGEC algorithm                                                        | 76  |

|    |       | 8.3.2   | Include power gating in tool-flow and implement                                      | 76  |

|    |       | 8.3.3   | Extended quantization level exploration                                              | 76  |

|    |       | 8.3.4   | Similar studies                                                                      | 77  |

|    |       | 8.3.5   | Link quality estimator and mode selector                                             | 77  |

| 9  | Con   | clusio  | n                                                                                    | 79  |

|    | 9.1   | Future  | e work                                                                               | 80  |

| Re | efere | nces    |                                                                                      | 81  |

| Aj | open  | dices   |                                                                                      |     |

| Α  | Aut   | omate   | d area and power estimating tool-flow                                                | 83  |

|    | A.1   | Makef   | ile for the automated tool-flow                                                      | 83  |

|    | A.2   | IIRFil  | t testbench in SystemVerilog                                                         | 84  |

|    | A.3   | Makef   | ile for synthesis                                                                    | 88  |

|    | A.4   | Synthe  | esis design constraints                                                              | 88  |

|    | A.5   | Makef   | ile for layout                                                                       | 89  |

|    | A.6   | Makef   | ile for power analysis                                                               | 90  |

|    | A.7   | Power   | analysis script                                                                      | 90  |

|    | A.8   | Matla   | b script for visualizing score results                                               | 97  |

| в  | Aut   | omate   | d filter generation and eligibility calculation                                      | 101 |

|    | B.1   | Matla   | b script for AFGEC                                                                   | 101 |

| С  |       | -       | ementation of winner candidates                                                      | 109 |

|    | C.1   | System  | nVerilog code for IIRFilt46                                                          | 109 |

| D             | Qua | intization level exploration                                | 115 |

|---------------|-----|-------------------------------------------------------------|-----|

|               | D.1 | Matlab script for quantization noise analysis               | 115 |

| E Dynamic RTL |     | namic RTL                                                   | 117 |

|               | E.1 | SystemVerilog code for DynOrderMux                          | 117 |

|               | E.2 | SystemVerilog code for DynNoiseRnd12                        | 123 |

|               | E.3 | Clock and reset distribution of dynamic RTL implementations | 131 |

# List of Figures

| 1.1  | The master thesis workflow                                                 | 4  |

|------|----------------------------------------------------------------------------|----|

| 2.1  | Basic transmit-receive procedures in digital communications                | 5  |

| 2.2  | Building blocks of DSP systems: Adder, multiplier and delay element .      | 6  |

| 2.3  | Direct Form realization of an FIR filter                                   | 8  |

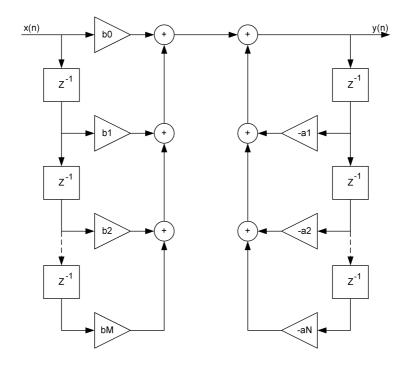

| 2.4  | Direct Form I realization of an IIR filter                                 | 9  |

| 2.5  | Direct Form II realization of an IIR filter                                | 10 |

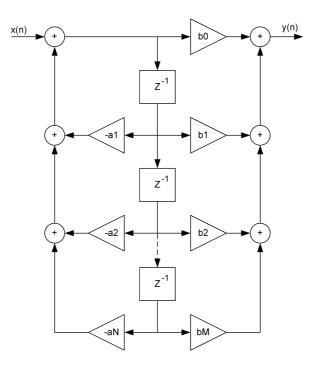

| 2.6  | Cascade-Form realization of an IIR filter, with generic Second-Order       |    |

|      | Section                                                                    | 11 |

| 2.7  | Relationship between original and truncated signal                         | 13 |

| 2.8  | Relationship between original and rounded signal                           | 14 |

| 2.9  | CMOS power dissipation categories                                          | 14 |

| 2.10 | CMOS power dissipation circuit diagram                                     | 15 |

| 2.11 | Enabled register with and without clock gating                             | 16 |

| 2.12 | Datapath gating using guarded evaluation                                   | 17 |

| 2.13 | Ideal and realistic effect of power gating                                 | 18 |

| 3.1  | Automated area and power estimating tool-flow                              | 19 |

| 3.2  | Detailed overview of the automated area and power estimating tool-flow     | 24 |

| 4.1  | Automated filter generation and eligibility calculation flow diagram       | 25 |

| 4.2  | Flow chart of the coefficient quantization algorithm                       | 29 |

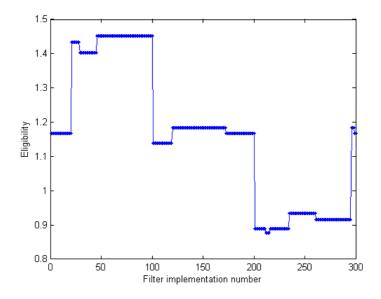

| 4.3  | Calculated eligibility for each of the 300 filter implementations          | 33 |

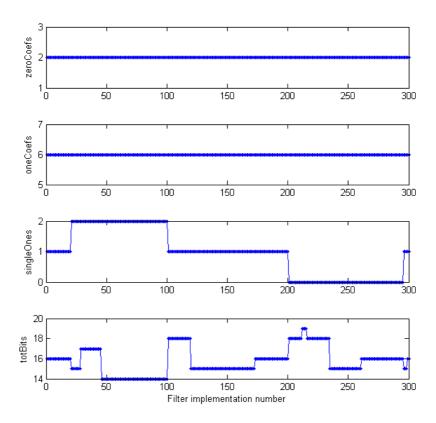

| 4.4  | The parameters which influence the four characteristics, of each filter    |    |

|      | implementation                                                             | 34 |

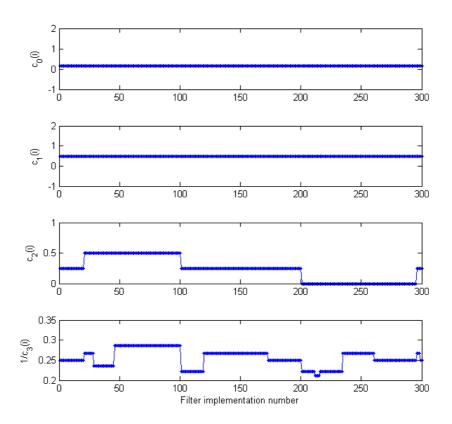

| 4.5  | The four characteristics yielding the Eligibility function, of each filter |    |

|      | implementation                                                             | 35 |

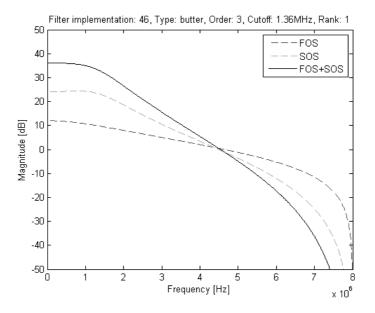

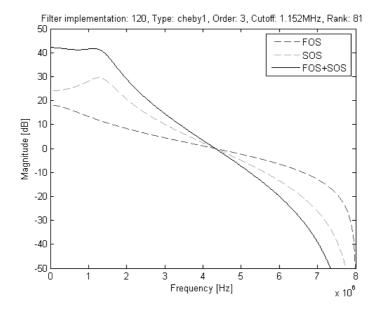

| 4.6  | Frequency response of IIRFilt46                                                                         | 36 |

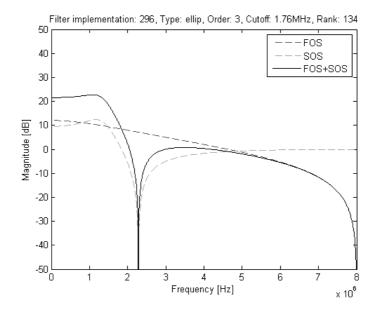

|------|---------------------------------------------------------------------------------------------------------|----|

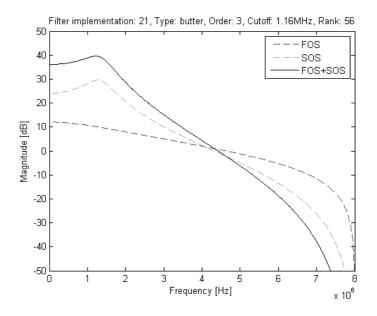

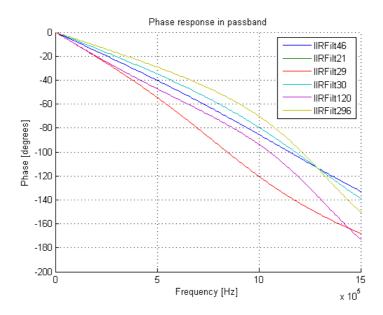

| 4.7  | Frequency response of IIRFilt21                                                                         | 37 |

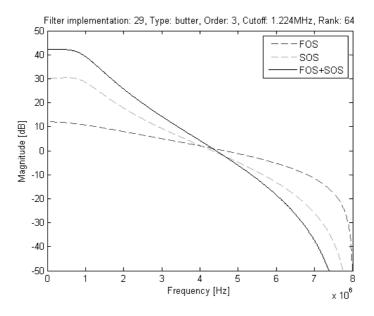

| 4.8  | Frequency response of IIRFilt29                                                                         | 38 |

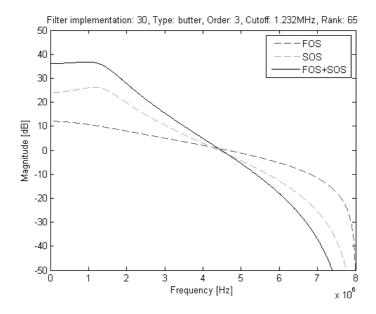

| 4.9  | Frequency response of IIRFilt30                                                                         | 38 |

| 4.10 | Frequency response of IIRFilt120                                                                        | 39 |

| 4.11 | Frequency response of IIRFilt296                                                                        | 39 |

| 4.12 | Phase response in passband of winner candidates                                                         | 40 |

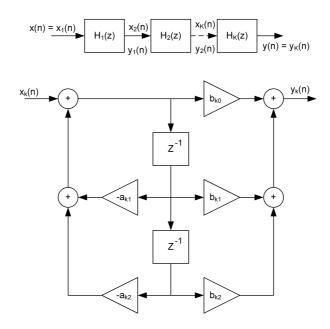

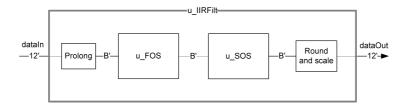

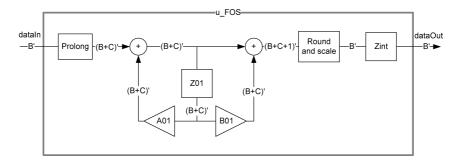

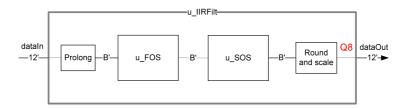

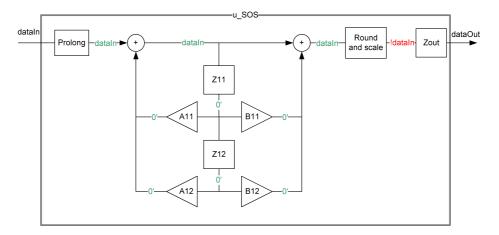

| 5.1  | Top level block diagram of the <i>IIRFilt</i> implementations                                           | 42 |

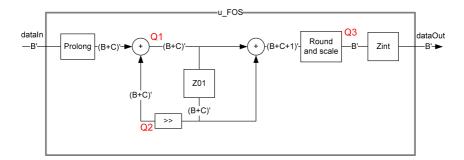

| 5.2  | Block diagram of the first order section in <i>IIRFilt</i>                                              | 43 |

| 5.3  | Block diagram of the second order section in <i>IIRFilt</i>                                             | 43 |

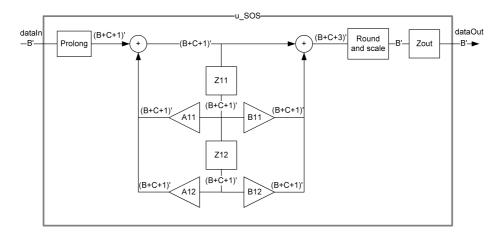

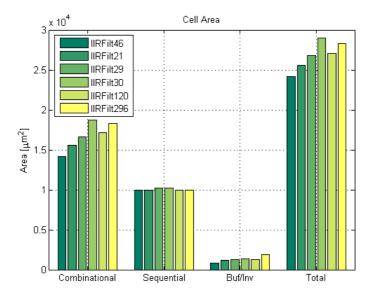

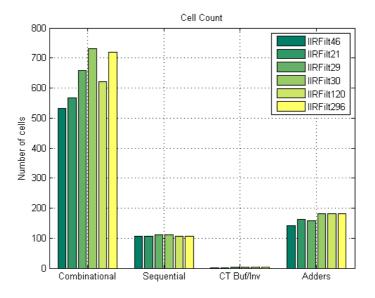

| 5.4  | Cell area of <i>IIRFilt</i> implementations                                                             | 45 |

| 5.5  | Number of logic cells in <i>IIRFilt</i> implementations                                                 | 46 |

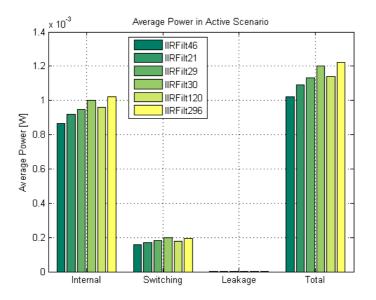

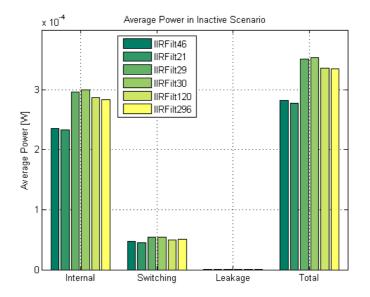

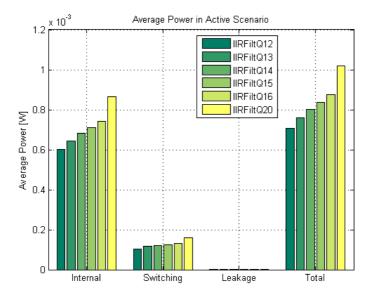

| 5.6  | Average power dissipation in active scenario for <i>IIRFilt</i> implementations                         | 46 |

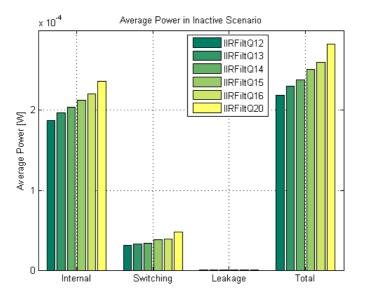

| 5.7  | Average power dissipation in inactive scenario for $IIRFilt$ implementations                            | 47 |

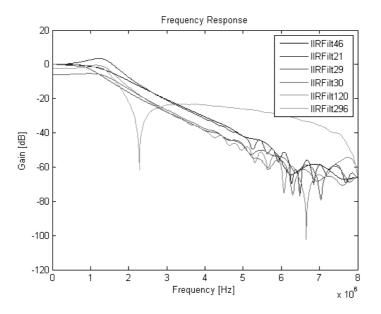

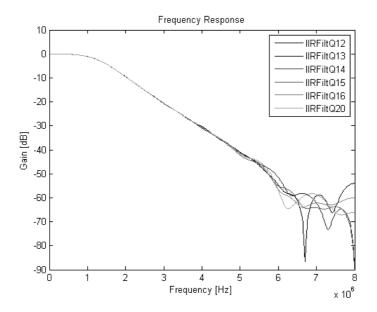

| 5.8  | Frequency response of <i>IIRFilt</i> implementations, computed from impulse response in simulation      | 48 |

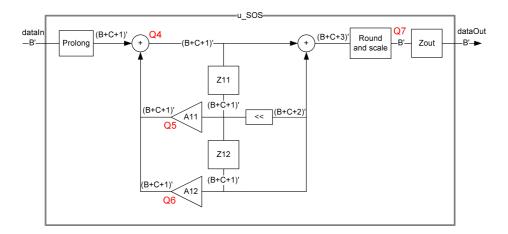

| 6.1  | Quantization noise sources at top level                                                                 | 49 |

| 6.2  | Quantization noise sources in the first order section                                                   | 50 |

| 6.3  | Quantization noise sources in the second order section $\ldots \ldots \ldots \ldots$                    | 50 |

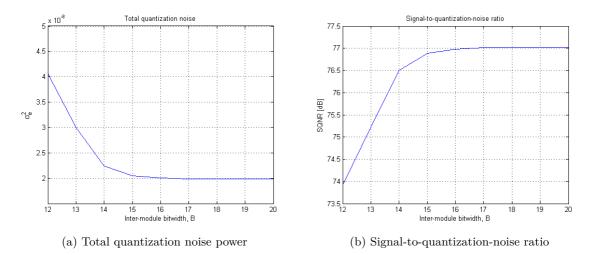

| 6.4  | Total quantization noise power and SQNR for different inter-module bitwidths                            | 51 |

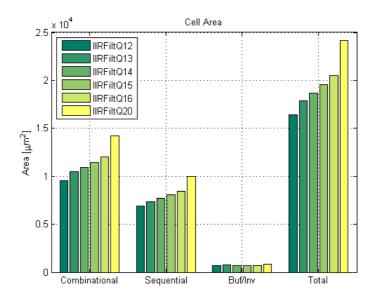

| 6.5  | Cell area of <i>IIRFiltQ</i> implementations                                                            | 53 |

| 6.6  | Average power dissipation in active scenario, for the $I\!I\!RFiltQ$ implement                          |    |

|      | tations                                                                                                 | 53 |

| 6.7  | Average power dissipation in inactive scenario, for the <i>IIRFiltQ</i> implementations                 | 54 |

| 6.8  | Frequency response of <i>IIRFiltQ</i> implementations, computed from impulse response in simulation     | 54 |

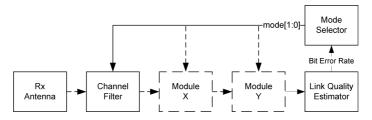

| 7.1  | Link quality estimator and mode selector provides the dynamic modules                                   |    |

|      | with the current mode of operation                                                                      | 57 |

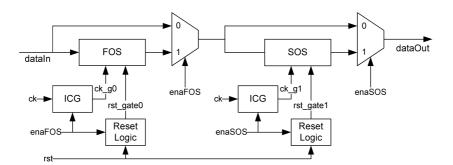

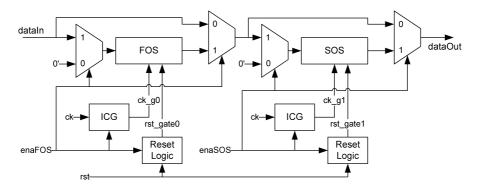

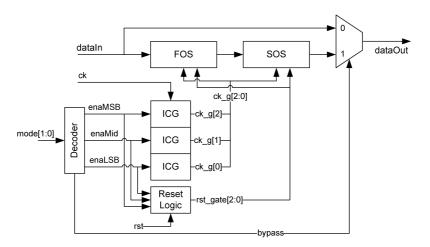

| 7.2  | Implementation with dynamic filter order, <i>DynOrder</i>                                               | 58 |

|      | Analysis of second order section in <i>DynOrder</i> when inactive                                       | 58 |

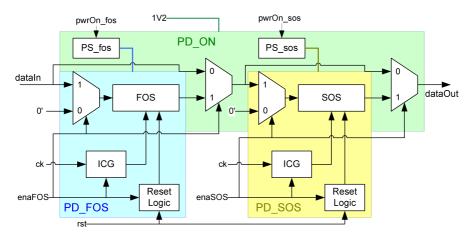

| 7.4  | Implementation with dynamic filter order, including datapath gating using input MUX, <i>DynOrderMux</i> | 59 |

| 7.5  | Implementation with dynamic filter order, including datapath gating                                     |    |

|      | using input registers, <i>DynOrderReg</i>                                                               | 60 |

| 7.6  | Register of wordlength $WL$ is divided into sections of significance                                    | 61 |

| 7.7  | Implementations with dynamic quantization noise, <i>DynNoise</i>                                        | 62 |

| 7.8  | Power gating analysis of the <i>DynOrderMux</i> implementation                                          | 63 |

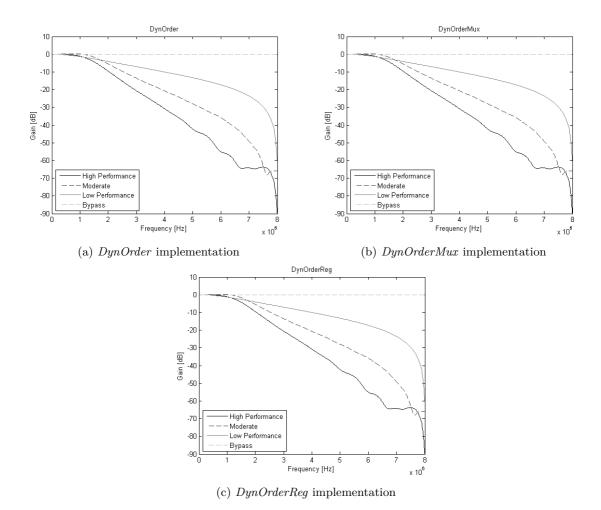

| 7.9  | Frequency responses of the dynamic filter order implementations                  | 65  |

|------|----------------------------------------------------------------------------------|-----|

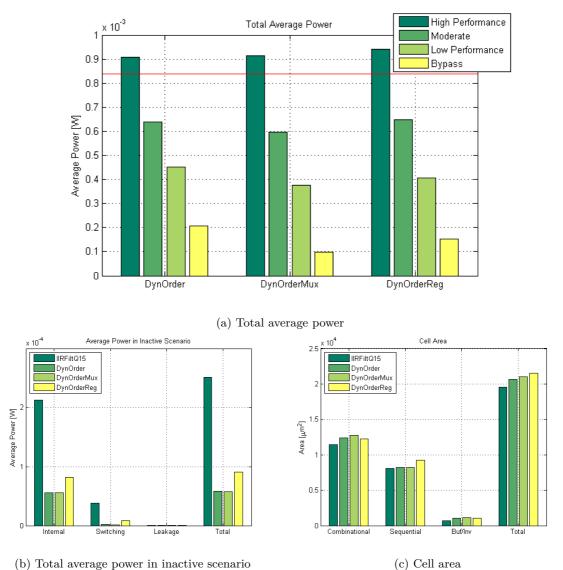

| 7.10 | Power and area results of the dynamic filter order implementations               | 66  |

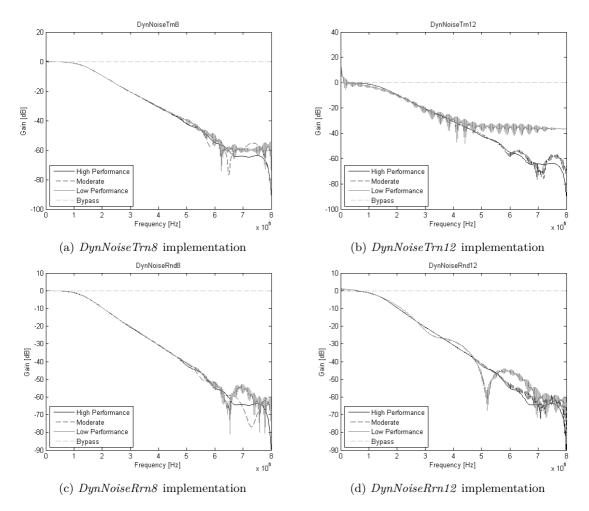

| 7.11 | Frequency responses of the dynamic quantization noise implementations            | 68  |

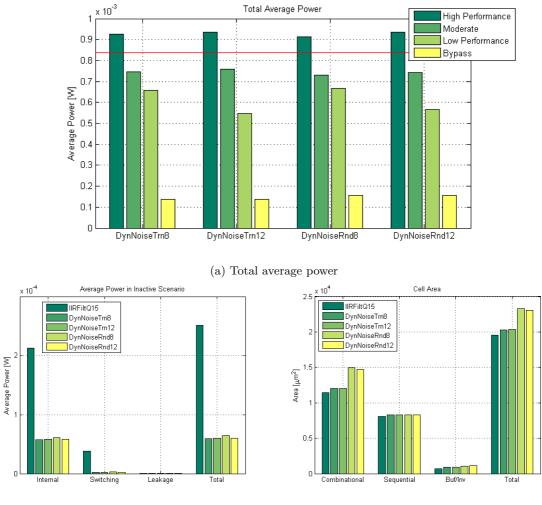

| 7.12 | Power and area results of the dynamic quantization noise implementations         | 69  |

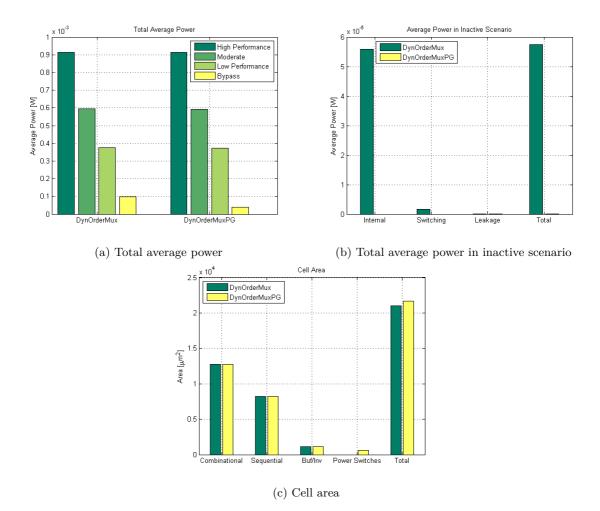

| 7.13 | Estimated power and area results of a power gated implementation                 | 71  |

|      |                                                                                  |     |

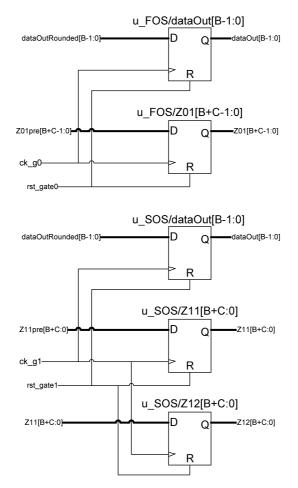

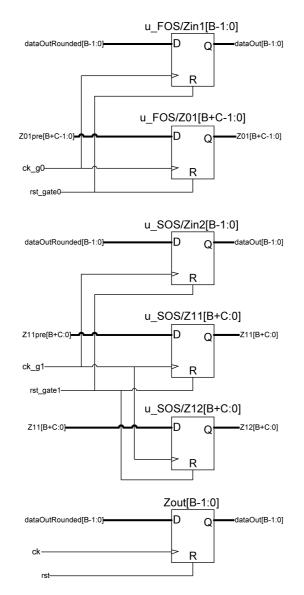

| E.1  | Registers and clock signals in the <i>DynOrder</i> and <i>DynOrderMux</i> imple- |     |

|      | mentations                                                                       | 131 |

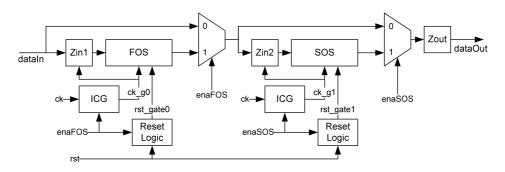

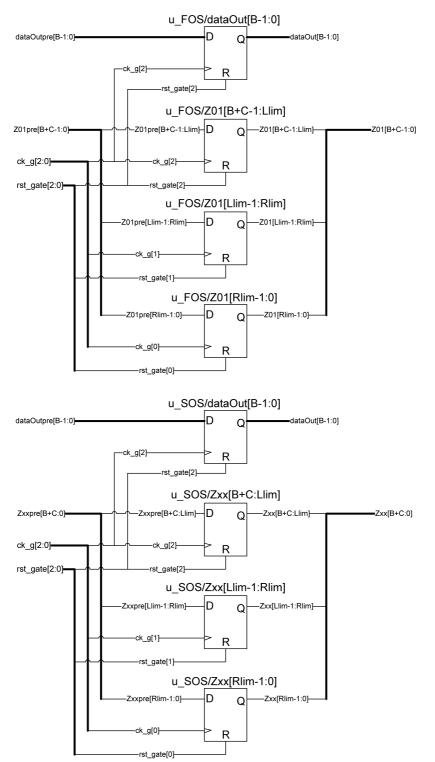

| E.2  | Registers and clock signals in the <i>DynOrderReg</i> implementation             | 132 |

|      |                                                                                  |     |

## List of Tables

| 3.1 | Overview of test cases and power scenarios                                                     | 21 |

|-----|------------------------------------------------------------------------------------------------|----|

| 4.1 | Filter requirements                                                                            | 26 |

| 4.2 | Parameters in the filter generating algorithm                                                  | 27 |

| 5.1 | Quantized filter coefficients in decimal                                                       | 44 |

| 5.2 | Quantized filter coefficients in binary and hardware implementation $\ . \ .$                  | 44 |

| 6.1 | Implementations during quantization level exploration $\ldots \ldots \ldots$                   | 52 |

| 7.1 | Control signals in dynamic filter order implementations                                        | 57 |

| 7.2 | Control signals in dynamic quantization noise implementations                                  | 60 |

| 7.3 | Dynamic quantization noise implementations                                                     | 61 |

| 7.4 | $180 \mathrm{nm}$ technology power switching cell details $\ldots \ldots \ldots \ldots \ldots$ | 63 |

| 8.1 | Possible combined dynamic order and dynamic noise solution                                     | 75 |

### List of Acronyms

AFGEC Automated Filter Generation and Eligibility Calculation.

**CMOS** Complementary Metal-Oxide-Semiconductor.

**CSV** Comma-Separated Values.

**DSP** Digital Signal Processing.

FDA Filter Design and Analysis.

**FIR** Finite Impulse Response.

FOS First Order Section.

**IIR** Infinite Impulse Response.

**IoT** Internet of Things.

**IP** Intellectual Property.

**RTL** Register-Transfer Level.

**SAIF** Switching Activity Interchange Format.

SOS Second Order Section.

SQNR Signal-to-Quantization-Noise Ratio.

VCD Value Change Dump.

### Chapter 1

### Introduction

Energy efficiency has become one of the most important aspect in today's wireless technology, with increasing demands in both performance and battery life time. With the Internet of Things (IoT) at its staring point, which is expected to reach 50 billion connected devices over the next decade [5], it is more relevant than ever to come up with low power design methodologies that prolong the battery life time of wireless communicating devices. Sleep modes are used to shut down parts of the circuit whenever they are unused. But as important as saving power in sleep mode, is to save power when the device is computing.

#### 1.1 Motivation

When designing an Intellectual Property (IP) in the industry, there is usually not time nor resources to compare tens or hundreds of different implementations in order to find the most eligible one. Thus, several sub-optimal solutions will be implemented. This thesis addresses this problem by taking a closer look at one of the IPs that may be implemented in numerous ways, namely the channel filter, in order to find an optimized implementation of the filter. The computational IPs are often implemented as *static*, in the meaning of providing the same performance at all times. The IP then needs to be able to provide the best level of performance for the worst case scenario, which implies that it will be overqualified in most cases. However, by making the IP *dynamic* it may adapt its performance to the computational requirements. This will require a slight increase in the amount of logic, but may potentially reduce the average power dissipation in the typical case.

#### 2 1. INTRODUCTION

#### 1.2 Algorithm-architecture co-design

This thesis will explore a methodology called *algorithm-architecture co-design* which is described in the doctoral dissertation by Isael Diaz [4]. It states that "the best implementation for any application requires a fine tuning between both algorithm and architecture." Diaz explains that since design constraints vary considerably among different applications, a general abstraction model will result in sub-optimal implementations. Thus, he writes, "efficient implementations can only be realized if both algorithm and architecture are prepared towards a common goal."

The common goal in this work is to reduce the power dissipation of the channel filter, without increasing the area more than 30% and while maintaining the performance of the filter at an acceptable level. This thesis will try to achieve the optimal solution by addressing the algorithm and architecture aspects in the following way:

#### Algorithm optimization

Minimal power dissipation can be obtained by finding the simplest digital signal processing algorithm which provides the desired filter performance. Investigating different filter types and structures may then lead to find the implementation which is most eligible for hardware implementation with regards to area and consequently power dissipation. Some filtering algorithms may also be better suited for a dynamic implementation, and should therefore be prioritized.

#### Architecture optimization

Investigating the architecture of the hardware implementation may lead to finding possible simplifications. For instance, parts of the circuit may be bypassed in order to reduce the power dissipation, although this will degrade the performance of the filter and increase the total area due to additional control logic. Such trade-offs will be examined in order to find the optimal solution in terms of power dissipation.

#### 1.3 Previous work

In the author's specialization project [14], the accuracy of two early stage power estimation methods is explored. The first method takes use of the commercial Designfor-Power tool PowerArtist by Ansys Apache, which estimates power dissipation from Register-Transfer Level (RTL). The tool yields promising results and accuracy, but its license is not available for the time being. The second method annotates switching activity from RTL simulation on post-layout netlists in Synopsys' PrimeTime-PX. This method proves to detect the power states of a multi-voltage full-chip design, and estimates its power dissipation within 1% deviation for low activity scenarios and within 13% deviation for high activity scenarios, using a sign-off power analysis as reference. The specialization project report concludes that this method is well suited for making RTL-design tradeoffs based on power dissipation in multi-voltage designs, but that it will require a custom-made automated tool-flow. The automated tool-flow should first perform a simplified synthesis and layout of an RTL-design in order to generate a post-layout netlist, and then perform the power analysis in PrimeTime-PX which applies activity files from RTL.

#### 1.4 Objectives

The work to be done can be split into the following objectives:

- 1. Create an automated tool-flow based on the previous work, which enables an efficient work-flow when making tradeoffs among a set of different RTL implementations. The tool-flow should create a scorefile for each implementation which extract details regarding area and power from the layout reports and power estimation reports.

- 2. Create a script that generates a large number of theoretical filters and sorts them based on hardware implementation friendliness.

- 3. Implement the highest scoring filters in Objective 2 in RTL, run them through the tool-flow in Objective 1, and verify or disprove the prediction. Settle for one implementation that will be used for further investigation.

- 4. Investigate the effect of quantizing at different levels. Make several RTLimplementations and verify using the tool-flow in Objective 1. Find the optimal quantization level in the tradeoff between quantization noise and area/power.

- 5. Investigate different approaches in making the channel filter dynamic. Implement in RTL and analyze the gain versus overhead introduced using the tool-flow in Objective 1.

The order and interrelation of the objectives are visualized in the master thesis workflow, in Figure 1.1.

#### 1.5 Thesis overview

Chapter 2 presents the theory regarding digital filters, power dissipation, quantization noise and commonly used low-power design techniques, which is considered useful material for the reader.

Chapter 3 describes the automated area and power estimating tool-flow. Chapter 4 describes the automated filter generation and eligibility calculation algorithm, along

#### 4 1. INTRODUCTION

Figure 1.1: The master thesis workflow

with the results and conclusion with the most eligible solutions. Chapter 5 describes the RTL implementation of the winner candidates, and presents their resulting area and power dissipation. The results are compared to the predictions in Chapter 4, and a conclusion is made where the most efficient filter is found. Chapter 6 carries out a quantization noise analysis of the filter, and presents the results of different quantization level implementations. Chapter 7 presents two main approaches in making the filter dynamic. Several implementations are made for each approach, which are analyzed with regards to area, power and performance.

Chapter 8 discusses the overall result, and takes a look at the methodology from a more generic point of view. Finally, Chapter 9 presents the overall conclusions and lists the objectives for future work.

### Chapter 2

### **Background and Theory**

This chapter presents the material needed in order to understand how power is dissipated in CMOS circuits, some basic low-power design techniques, and some digital signal processing theory regarding digital filters.

#### 2.1 The channel filter in wireless communication systems

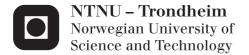

An illustration of a basic wireless communication system is shown in Figure 2.1 [9]. Note that this is an abstracted model, and does not necessarily represent the system mentioned in this thesis.

Figure 2.1: Basic transmit-receive procedures in digital communications

#### 6 2. BACKGROUND AND THEORY

In such systems, a *channel filter* is typically placed in both the transmitter and the receiver, filtering the information in baseband. This is done in transmission to avoid leaking energy into the neighboring bands, and in reception to reject interfering signals outside the operating band, and unwanted products from mixers and amplifiers [10]. This is typically done in the digital domain, which is the case that will be explored in this thesis.

#### 2.2 Digital filters

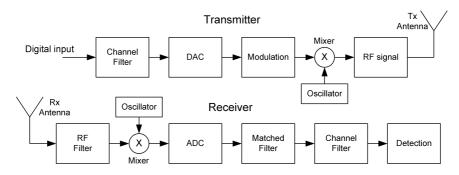

A digital filter is a Digital Signal Processing (DSP) system which alters the spectral content of an input signal in order to remove noise, improve signal quality or extract signal information, to mention a few common objectives [7]. DSP systems are defined as an implemented algorithm which performs a certain operation on digital signals in order to achieve a predefined task. The processing of digital signals, and hence digital filters, can be described by additions, multiplications and time shifts, using the building blocks in Figure 2.2 [7]. A digital filter can be implemented in software or hardware using these building blocks.

Figure 2.2: Building blocks of DSP systems: Adder, multiplier and delay element

#### Filter representations

Digital filters may be represented in several ways, and one of them is the I/O equation, or difference equation. The general constant-coefficient difference equation of discrete-time systems is defined as [11]:

$$y(n) = -\sum_{k=1}^{N} a_k y(n-k) + \sum_{k=0}^{M} b_k x(n-k)$$

(2.1)

where x(n) is the input, y(n) is the output, and  $a_k$  and  $b_k$  are the coefficients of the system. Here, the larger number of M and N is called the *order* of the system,

although N is usually selected to equal or exceed M. Another way of representing digital filters is by its system function [11]:

$$H(z) = \frac{\sum_{k=0}^{M} b_k z^{-k}}{1 + \sum_{k=1}^{N} a_k z^{-k}}$$

(2.2)

which is the ratio of the system input and output after performing the z-transform. The system function is defined by the coefficients  $a_k$  and  $b_k$ , which determines the poles and zeros of the system, and thereby its frequency response [11]. The impulse response of a digital filter can be obtained by applying the unit impulse function,

$$\delta(n) = \begin{cases} 1 & , n = 0 \\ 0 & , n \neq 0 \end{cases}$$

(2.3)

to the input of the system. Hence, by substituting x(n) with  $\delta(n)$  in Equation 2.1, the equation for the impulse response is found. Digital filters can be divided into two categories based on their impulse response. These are, Finite Impulse Response (FIR) and Infinite Impulse Response (IIR) filters.

#### 2.2.1 FIR filters

FIR filters are defined exclusively by the input x(n) and the coefficients  $b_k$ , as the output y(n) do not depend on previous output values. Hence, the I/O equation of FIR filters can be defined by:

$$y(n) = \sum_{k=0}^{M} b_k x(n-k)$$

(2.4)

The impulse response of an FIR filter can, as the name implies, be represented by a finite number of samples. These samples are identical to the coefficients of the filter, as can be verified by inserting  $x(n) = \delta(n)$  into Equation 2.4:

$$y(n) = \sum_{k=0}^{M} b_k$$

(2.5)

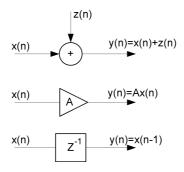

The simplest structure for implementing an FIR filter, is called the direct-form. This realization requires M - 1 memory elements, M multiplications and M - 1 additions, which is illustrated in Figure 2.3 [11].

#### 8 2. BACKGROUND AND THEORY

Figure 2.3: Direct Form realization of an FIR filter

The finite length of the FIR filter impulse response ensures that they are stable [7]. And when the system has linear phase, the coefficients also are symmetrical, which makes it possible to reuse half the coefficients. This may reduce the number of multiplications to M/2 [11]. However, the disadvantage with FIR filters is that they require a relatively high order (number of coefficients) in order to obtain steep curves in the frequency response, which implies a high complexity [7].

#### 2.2.2 IIR filters

If the impulse response of a filter is not of finite length, it is called an IIR filter [7]. An easy way to recognize an IIR filter is that the output of the filter not only depends on previous input values, but also on previous output values, which creates feedback loops in the system. The I/O equation and system function of an IIR filter can be described by Equation 2.1 and 2.2, respectively.

There are several ways of realizing IIR filters. The Direct Form structures can be realized by splitting the system function in Equation 2.2 into an all-zero filter and

Figure 2.4: Direct Form I realization of an IIR filter

an all-pole filter, as follows [11]:

$$H(z) = H_1(z)H_2(z)$$

(2.6)

where

$$H_1(z) = \sum_{k=0}^{M} b_k z^{-k}$$

(2.7)

$\quad \text{and} \quad$

$$H_2(z) = \frac{1}{1 + \sum_{k=1}^N a_k z^{-k}}$$

(2.8)

#### 10 2. BACKGROUND AND THEORY

Figure 2.5: Direct Form II realization of an IIR filter

#### The Direct Form I structure

The Direct Form I structure, illustrated in Figure 2.4, is realized by first implementing the all-pole filter  $H_1(z)$  followed by the all-zeros filter  $H_2(z)$ . Note that if the  $a_k$  coefficients are zero, this becomes an FIR filter. This structure requires M + N + 1 multiplications, M + N additions and M + N memory elements.

#### The Direct Form II structure

The Direct Form II structure, illustrated in Figure 2.5, is obtained by placing the all-pole filter in front of the all-zero filter. This is a more compact structure, as the memory elements may be reused. Consequently, it requires a maximum of M + N + 1 multiplications, M + N additions, and max(M, N) memory elements. Unfortunately, the Direct Form structures are extremely sensitive to quantization and are not recommended in practical applications, as small changes in the filter coefficients results in large changes in the placement of poles and zeros in the system if N is large [11]. To reduce this effect, high-order IIR filters are often factored into first- and second-order sections, or *biquadratic sections*, which are connected in cascade to form the overall filter [7].

#### 2.2. DIGITAL FILTERS 11

Figure 2.6: Cascade-Form realization of an IIR filter, with generic Second-Order Section

#### The Cascade-Form structure

The Cascade-Form structure of H(z) can be expressed as

$$H(z) = \prod_{k=1}^{K} H_k(z)$$

(2.9)

where

$$K = \lceil \frac{N+1}{2} \rceil \tag{2.10}$$

and

$$H_k(z) = \frac{b_{k0} + b_{k1}z^{-1} + b_{k2}z^{-2}}{1 + a_{k1}z^{-1} + a_{k2}z^{-2}}$$

(2.11)

If N > M, some of the second-order sections will have *b*-coefficients that are zero. Also, if N is odd, one of the sections will have  $a_{k2} = 0$  in order to form a first-order

#### 12 2. BACKGROUND AND THEORY

section. Each of the sections defined by Equation 2.11 can be realized as either Direct Form I or II. There are also many ways of pairing the poles and zeros when factoring into second-order sections, and ordering the sections. For infinite-precision arithmetic all implementations are equivalent, but for practical applications the various implementations may differ significantly [11]. The Direct Form II realization of a cascaded second-order section is illustrated in Figure 2.6.

#### **Commonly Used IIR Filters**

When the structure of the filter is selected, the values of the coefficients need to be determined. This implies determining the poles and zeros of the filter, which is a well-developed field in analog filter design. There also exist several computer programs for designing digital filters. One example is the Filter Design and Analysis (FDA) tool in Matlab, which calculates the coefficients based on a set of design constraints and specifications. However, the tool needs to know which filter to generate, and this section presents the characteristics of the three most commonly used IIR filters:

Butterworth filters are all-pole filters where all the poles occur on a circle of a given radius, at equally spaced points. The frequency response of Butterworth filters are monotonic in both passband and stopband [11].

Chebyshev Type I filters are all-pole filters that have equiripple behaviour in passband, and monotonic behaviour in stopband. The poles is placed on an ellipse, and is easiest determined by first finding the points of an equivalent order Butterworth filter. The details of this can be found in [11].

*Elliptic filters* contain both poles and zeros, and have equiripple behaviour in both passband and stopband. The poles are placed according to the Jacobian elliptic function, and the zeros are placed on the imaginary axis. The Elliptic filters manages to spread the approximation error equally over the passband and stopband, and are therefore considered the most efficient from the view of yielding the smallest order filter for a given specification. A disadvantage with the Elliptic filter compared to Butterworth and Chebyshev, is that its phase response is more nonlinear in the passband [11].

#### 2.3 Quantization noise

When performing fixed-point multiplications, you usually need to quantize a number via rounding or truncation in order to keep the same word length, which degrades the precision level of the signal [11]. The consequence of rounding and truncation is that a quantization error, the difference between the number prior and after quantization, is introduced to the signal. The characteristics of this error depends on the number representation of the signal. We will focus on the *two's-complement* representation.

#### 2.3.1 Truncation

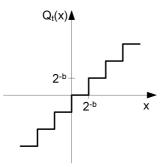

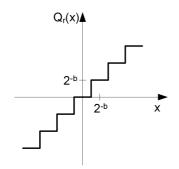

For positive numbers, truncation results in a number that is smaller than the original. Hence, the quantization error  $E_t$  is within the region  $-(2^{-b_t} - 2^{-b}) \leq E_t \leq 0$ , where b and  $b_t$  are the number of bits before and after truncation, respectively. In two's complement, truncating a negative number increases the magnitude of the negative number. Hence, the truncation error is always negative, and falls within the region  $-(2^{-b_t} - 2^{-b}) \leq E_t \leq 0$  [11]. The relationship between the original signal x, and the truncated signal  $Q_t(x)$  is illustrated in Figure 2.7, where the quantization error is defined as  $E_t = x - Q_t(x)$ .

Figure 2.7: Relationship between original and truncated signal

If the quantization error is uniformly distributed in the range  $-\Delta \leq E \leq 0$ , the mean value of the error is  $-\frac{\Delta}{2}$  and the quantization noise power is  $\frac{\Delta^2}{3}$ .

#### 2.3.2 Rounding

In rounding, the maximum error that can be introduced is  $\frac{1}{2}(2^{-b_r}-2^{-b})$ , where  $b_r$  is the number of bits after rounding. The round-off error can be either positive or negative, and falls within the region  $-\frac{1}{2}(2^{-b_r}-2^{-b}) \leq E_r \leq \frac{1}{2}(2^{-b_r}-2^{-b})$ . Thus the quantization error of rounding is symmetrical about zero, as illustrated in Figure 2.8. Here, the quantization error is defined as  $E_r = x - Q_r(x)$ , where x is the original signal and  $Q_r(x)$  is the rounded signal.

If the quantization error is uniformly distributed in the range  $-\frac{\Delta}{2} \leq E \leq \frac{\Delta}{2}$ , the mean value of the error is zero and the quantization noise power is  $\frac{\Delta^2}{12}$  [11].

Figure 2.8: Relationship between original and rounded signal

#### 2.4 CMOS Power Dissipation

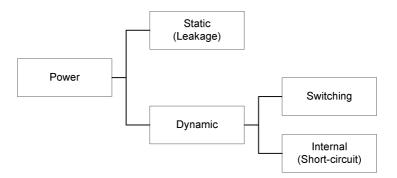

The power dissipation of digital Complementary Metal-Oxide-Semiconductor (CMOS) circuits can be categorized as shown in Figure 2.9. The following sections will explain each component in detail, and present the resulting equation.

Figure 2.9: CMOS power dissipation categories

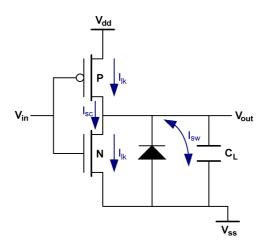

#### 2.4.1 Static Power

The power dissipated by a gate when it is inactive, is called *static power* or *leakage power*. This is due to the fact that all static power components are caused by leakage currents. Most of the static power dissipation is due to the source-to-drain subthreshold leakage  $I_{sb}$ , which is caused by reduced threshold voltages that prevent the gate from turning off completely. The other component results from current leaking between the diffusion layers and substrate [12]. The leakage currents are denoted  $I_{lk}$  in Figure 2.10.

Figure 2.10: CMOS power dissipation circuit diagram

#### 2.4.2 Dynamic Power

The power dissipated by an active gate is called *dynamic power*, and can be split into the following two categories.

#### **Internal Power**

Whenever the voltage on a net changes, a circuit dissipates power due to charging or discharging of internal capacitances. This is one of the components of *internal power*, together with the more dominating component called *short-circuit power*. The latter is caused by the short-circuit current going from  $V_{dd}$  to ground the short period of time the PMOS and NMOS transistors are simultaneously open during switching [12]. In Figure 2.10,  $I_{sc}$  is the short-circuit current rising when both transistor types are partially open.

#### Switching Power

The *switching power* is the power dissipated by charging and discharging the load capacitance  $C_L$ , which is given by the sum of net and gate capacitances at the output. In Figure 2.10,  $I_{sw}$  denotes the switching current charging and discharging the output capacitance. The switching power component is part of the following equation, which shows the total average power in a digital CMOS circuit:

$$P_{avg} = P_{switching} + P_{short-circuit} + P_{leakage}$$

=  $\alpha C_L V_{dd}^2 f_{clk} + I_{sc} V_{dd} + I_{lk} V_{dd}$  (2.12)

#### 16 2. BACKGROUND AND THEORY

The switching component is calculated from the supply voltage  $V_{dd}$ , the load capacitance  $C_L$ , the clock frequency  $f_{clk}$  and the switching activity factor  $\alpha$ . The factor  $\alpha$  is defined as the average number of times in each clock cycle a specific node makes a power consuming transition, going from 0 to 1 [3].

#### 2.5 Low power techniques

This section presents some of the most common low-power techniques for reducing dynamic and static power dissipation, which will be part of the dynamic implementations in Chapter 7.

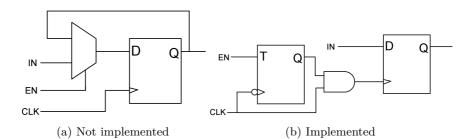

#### 2.5.1 Clock gating

One of the most common low-power techniques is *clock gating*, which means to prevent the clock signal from propagating to parts of the circuit whenever it is not required [1]. This reduces dynamic power in the clock distribution tree, and in the sequential elements connected to that clock.

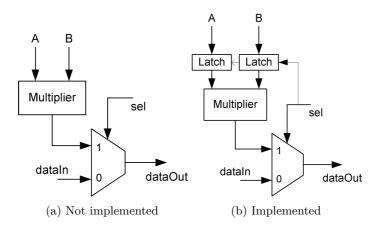

The most simple clock gate is realized with the clock signal and the enable signal connected to the inputs of an AND-gate. However, this structure is sensitive to glitches in the enable signal, that would create glitches in the gated clock signal as well. A better solution is obtained by using a latch in addition to the AND-gate, which filters the glitches in the enable signal [1]. This structure can be seen in Figure 2.11b, where it appears in front of a register, while Figure 2.11a shows the enabled register without clock gating.

Figure 2.11: Enabled register with and without clock gating

#### 2.5.2 Datapath gating

Significant amounts of dynamic power may be wasted in combinational datapaths, due to switching activity that has no contribution to the functionality of the circuit [1].

*Guarded evaluation* is a datapath gating technique which can be applied when the outputs of embedded combinational blocks are not used. Transparent latches are inserted at the inputs of the combinational block, and control logic is added to determine when the output of the block is unused. The control signal is then used to latch the inputs, preventing the combinational block from toggling [1]. An example of guarded evaluation is illustrated in Figure 2.12, where a multiplier represents the combinational block.

Figure 2.12: Datapath gating using guarded evaluation

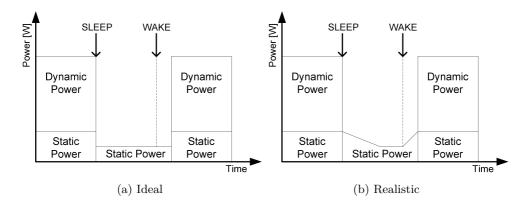

#### 2.5.3 Power gating

While clock- and datapath gating can be used to reduce the dynamic power dissipation of a circuit, *power gating* may be used to reduce static power. The basic strategy of power gating is to provide a low power mode and an active mode, and switch between the modes in order to maximize the power reduction while minimizing the impact on performance. A disadvantage of power gating is that it adds significant time delays to safely power up and down the circuits. Also, controlling a power domain requires one or more power switches, which will increase the area and also contribute with additional leakage power. Figure 2.13 illustrates the ideal versus the realistic effect of power gating [8].

#### 18 2. BACKGROUND AND THEORY

Figure 2.13: Ideal and realistic effect of power gating

## Chapter 3

# Automated area and power estimating tool-flow

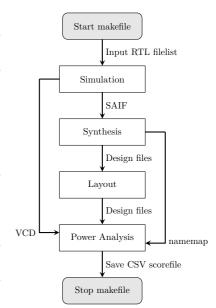

This chapter describes the tool-flow that is created in order to obtain area and power numbers for each RTL implementation, addressing Objective 1 in Section 1.4. The tool-flow is based on the previous work of the author [14], where it was found that fast and accurate power estimations could be obtained by applying switching activity information from RTL simulation on post-layout netlists. The tool-flow is created using a Makefile of the GNU Make Utility<sup>1</sup> to structure a list of commands with certain dependencies. The Makefile can be read in Appendix A.1, and its function is illustrated in Figure 3.1. The toolflow estimates the area and power dissipation of an RTL design automatically by simply providing it with the RTL filelist. The figure shows the dependencies between the steps in the tool-flow, and a simplified overview of how design files are passed on to succeeding tools. The tool-flow is

Figure 3.1: Automated area and power estimating tool-flow

<sup>&</sup>lt;sup>1</sup>https://www.gnu.org/software/make/manual/make.pdf

#### 20 3. AUTOMATED AREA AND POWER ESTIMATING TOOL-FLOW

run on a computer of the current industry standard, holding two 2.8 GHz six-core Intel Xeon E5660 processors and 32 GB RAM, running a 64 bit CentOS 5.10 operating system.

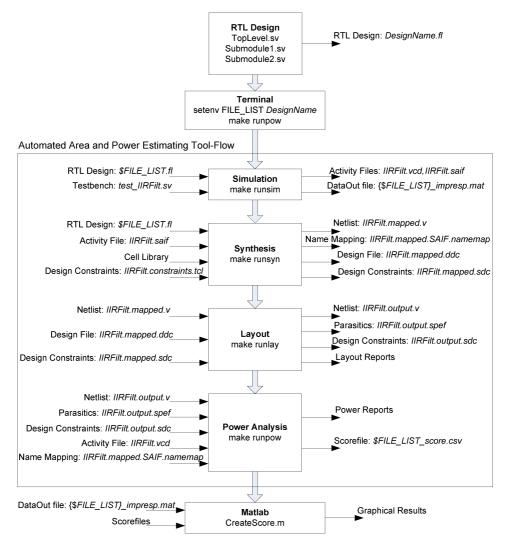

#### 3.1 The steps of a complete design cycle

Figure 3.2 shows a complete design cycle in this work, from RTL design to illustrated results of the designs area and power dissipation, including the automated tool-flow. The steps in this design cycle will now be explained in detail.

#### 3.1.1 RTL Design

A module is designed in SystemVerilog<sup>2</sup>, and a filelist is written which lists all RTL files that makes the complete design. The filelist must have a unique name, representing that particular design, as it will be used throughout the whole tool-flow.

#### 3.1.2 Commands in terminal

Two simple commands needs to be executed in terminal in order to start the automated tool-flow. The first command sets the enviormental variable FILE\_LIST to the unique name of the current RTL design. The second command, make runpow, tells the Makefile to run the power analysis. Due to the dependencies, the Makefile will first complete the simulation, synthesis and layout, before starting on the power analysis.

#### 3.1.3 Simulation

This is the first step of the automated tool-flow. The current RTL design is simulated in Mentor Graphics' Questa<sup>3</sup>, running a testbench which applies several test frequencies to the data input of the module. Since all RTL designs are planned to have the same interface, the testbench will be reused for all cases. The test scenarios are listed in Table 3.1. The testbench SystemVerilog code can be found in Appendix A.2. The testbench also logs the data output, such that the frequency response may be calculated from the impulse response in simulation. Furthermore, the simulation tool generates both Value Change Dump (VCD) and Switching Activity Interchange Format (SAIF) activity files. VCD is a cycle accurate activity file format which will be used to annotate switching activity in power analysis. SAIF is an average activity file format which, in this case, only is used to generate a name-mapping file in synthesis. The name-mapping will ensure name consistency between the activity file and the netlist.

<sup>&</sup>lt;sup>2</sup>http://www.eda.org/sv/SystemVerilog\_3.1a.pdf

$<sup>^{3}</sup>$ http://www.mentor.com/products/fv/questa/

| Test case             | Power Scenario | Description                                                                                                             |

|-----------------------|----------------|-------------------------------------------------------------------------------------------------------------------------|

| Impulse response      | None           | A single pulse is input to the sys-<br>tem. This can be used to calcu-<br>late the frequency response of the<br>filter. |

| Inactive              | Inactive       | The clock is the only signal ac-<br>tive. This can be used to measure<br>power dissipation in idle state.               |

| 1 MHz input           | Active         | The data input is a 1 MHz sinus.<br>Attenuation is measured.                                                            |

| $2\mathrm{MHz}$ input | Active         | The data input is a 2 MHz sinus.<br>Attenuation is measured.                                                            |

| 3 MHz input           | Active         | The data input is a 3 MHz sinus.<br>Attenuation is measured.                                                            |

Table 3.1: Overview of test cases and power scenarios

#### 3.1.4 Synthesis

This is the second step of the automated tool-flow. When the Makefile encounters this step, it enters a new Makefile dedicated to synthesis, which can be found in Appendix A.3. The synthesis is performed in Design Compiler<sup>4</sup> using Synopsys' reference scripts for recommended methodology [13].

The RTL design, given by the filelist variable, is synthesized to a netlist of logic gates from a given cell library in Synopsys Design Compiler. The cell library used is of 180 nm technology. The synthesis is performed under certain design constraints, including input transition times, output capacitance load and clock signal details, which can be found in Appendix A.4. A name-mapping file is generated from the SAIF activity file created in simulation. This will be used in power analysis to map the signals from RTL simulation to the corresponding pins in the post-layout netlist. The synthesis creates a Verilog netlist, a Synopsys design file and an expanded constraint file, which all will be used in layout.

Slight changes are made to the recommended methodology scripts in order to read in the correct RTL design and perform the name-mapping. Important commands for this are listed below.

<sup>&</sup>lt;sup>4</sup>http://www.synopsys.com/Tools/Implementation/RTLSynthesis/DesignCompiler/

```

set FILE_LIST [getenv "FILE_LIST"]

set DESIGN_NAME "IIRFilt"

set RTL_SOURCE_FILES "[N_ReadFileListu[substu"../rtl/${FILE_LIST}.fl"]]

"

analyze -format sverilog -define HINST_TSMC_180_ARM_1V2 ${

RTL_SOURCE_FILES}

saif_map -start

read_saif -auto_map_names -input /pri/jota/workspace/master/ip/IIRFilt/

sim/run/rtl/IIRFilt.saif -instance test_IIRFilt/u_IIRFilt -verbose

saif_map -type ptpx -write_map ${RESULTS_DIR}/${DESIGN_NAME}

.mapped.SAIF.namemap

```

#### 3.1.5 Layout

As the Makefile encounters the layout step, it enters the layout dedicated Makefile, which can be read in Appendix A.5. As for the synthesis step, the layout is also performed using Synopsys' reference scripts for recommended methodology [13].

The synthesized design files are passed on to Synopsys IC Compiler  $^5$  which performs floorplanning, place and route, clock tree synthesis and optimization algorithms. The script is set up to create a quadratic core layout with a core utilization of 40%, with a vertical power supply through the center of the core. Key commands for this customization are listed below.

```

set DESIGN_NAME "IIRFilt"

set ICC_IN_VERILOG_NETLIST_FILE "/pri/jota/workspace/master/ip/IIRFilt/

syn/results/$DESIGN_NAME.mapped.v" ;

"/pri/jota/workspace/master/ip/IIRFilt/

set ICC_IN_SDC_FILE

syn/results/$DESIGN_NAME.mapped.sdc"

set ICC_IN_DDC_FILE

"/pri/jota/workspace/master/ip/IIRFilt/

syn/results/$DESIGN_NAME.mapped.ddc"

create_floorplan \

-control_type aspect_ratio \

-core_aspect_ratio 1 \

-core_utilization 0.4 \

-left_io2core 5 \

-bottom_io2core 5 \

-right_io2core 5 \

-top_io2core 5 \

-start_first_row

create_power_straps -direction vertical -start_at 150.0 -nets {

DVDD_1V2 AVSS} -layer METAL2 -width 1.0

```

$<sup>^{5} \</sup>rm http://www.synopsys.com/Tools/Implementation/PhysicalImplementation/Pages/ICCompiler.aspx$

The output of the layout is a post-layout netlist, a design constraint file, and a parasitic exchange file. It also generates several layout reports, from which details regarding cell count and area can be extracted. These will be included in the Comma-Separated Values (CSV) scorefile generated in the end of power analysis. The details are:

- Number of combinational cells

- Number of sequential cells

- Number of clock tree buffers/inverters

- Number of adders

- Combinational area

- Noncombinational area

- Total area

#### 3.1.6 Power Analysis

When the Makefile reaches the final step, it enters the power analysis dedicated Makefile, given in Appendix A.6. The power analysis script is also based on Synopsys' reference scripts. However, the script can be read in its entirety in Appendix A.7 due to several customizations.

The design files from layout are passed on to Synopsys' PrimeTime-PX<sup>6</sup>, which performs the power analysis. It analyzes the activity in different scenarios, defined by certain time windows of the VCD file. The power scenarios are given in Table 3.1, where *Active* is an average power analysis of three different time windows. PrimeTime uses the VCD activity file generated in RTL simulation to initiate toggling in as many nets as possible. The name-mapping file ensures that the toggling information reaches the correct pin. The nets that are not directly annotated, will get their toggling information from activity propagating throughout the circuit. The power analysis generates a power report for each scenario. The information extracted from these reports into the scorefile is:

- Total internal power

- Total switching power

- Total leakage power

- Total power

<sup>&</sup>lt;sup>6</sup>http://www.synopsys.com/Tools/Implementation/SignOff/Pages/PrimeTime.aspx

#### 24 3. AUTOMATED AREA AND POWER ESTIMATING TOOL-FLOW

Figure 3.2: Detailed overview of the automated area and power estimating tool-flow

#### 3.1.7 Visualization in Matlab

Finally, one or more CSV scorefiles may be input to the Matlab<sup>7</sup> script which is created to visualize the scores and easily compare the different RTL implementations. The script also reads the impulse response dumped from RTL simulation in order to plot the frequency responses of the implementations. The Matlab script can be read in Appendix A.8.

<sup>&</sup>lt;sup>7</sup>http://se.mathworks.com/products/matlab/

## Chapter 4

# Automated filter generation and eligibility calculation

This chapter describes the Automated Filter Generation and Eligibility Calculation (AFGEC) algorithm, which is a Matlab script that generates a set of filters and sorts them based on how eligible they are for hardware implementation. The flow of the AFGEC algorithm is illustrated in Figure 4.1. The script can be read in its entirety in Appendix B.1. Section 4.1 and 4.2 describes the automated filter generation, Section 4.3 describes the calculation of the eligibility factor, while Section 4.4 carry out the results of the AFGEC algorithm.

#### 4.1 Automated filter generation

This section explains the filter generation algorithm, states the filter requirements and elaborates on the filter types and structures that are chosen.

Figure 4.1: Automated filter generation and eligibility calculation flow diagram

#### 4.1.1 Filter requirements

The filter to be generated should be a low-pass filter with cut-off frequency close to 1 MHz and sampling frequency of 16 MHz. The gain/attenuation at 1 MHz should be as close to 0 dB as possible, within 3 dB deviation. The attenuation at 2 MHz and 3 MHz should be more than 6 dB and 12 dB, respectively. There are no strict requirements with regards to phase linearity of the filter, other than the fact that it should be close to linear in passband. The requirements are summarized in Table 4.1.

| Factor                             | Requirement      |

|------------------------------------|------------------|

| Characteristic                     | Low pass         |

| Sampling frequency                 | $16\mathrm{MHz}$ |

| Cut-off frequency                  | $1\mathrm{MHz}$  |

| Max att./gain at $1\mathrm{MHz}$   | $3\mathrm{dB}$   |

| Min attenuation at $2\mathrm{MHz}$ | $6\mathrm{dB}$   |

| Min attenuation at $3\mathrm{MHz}$ | $12\mathrm{dB}$  |

Table 4.1: Filter requirements

#### 4.1.2 Filter type

An advantage of FIR filters is the possibility of having linear phase response. However, there are no strict requirements regarding phase linearity in this work, which makes the IIR filters just as applicable. As described in Section 2.2.1, a disadvantage of FIR filters is that they require a relatively high order in order to obtain steep curves in the frequency response. A high filter order implies a large amount of registers and multipliers, which again will have a significant impact on the area and power dissipation. Therefore, since energy is of the essence in this work, it is decided to focus on IIR filters. All of the commonly used IIR filters presented in Section 2.2.2 will be generated in the AFGEC algorithm. That is the Butterworth, Elliptic and Chebyshev Type I filters. It is interesting to see if either of the IIR filters are more eligible for hardware implementation than the others.

#### 4.1.3 Filter structure

Obviously, implementing the IIR filters in a Direct Form I structure is a suboptimal solution. As described in Section 2.2.2, it requires the double amount of registers as for instance the Direct Form II structure, which clearly would effect the power dissipation. Moreover, we read that both Direct Form structures are extremely sensitive to quantization and was not recommended for practical applications. Hence, all the generated filters will be structured as first- and second-order sections in the Cascade-Form, which exploits the robustness of low order filters. This structure may

also be well suited for a dynamic approach, where subsections can be enabled or disabled based on the current filter requirement. This topic will be addressed in Chapter 7.

#### 4.1.4 Filter generating algorithm

The filter generating algorithm is the first part of the AFGEC script, which can be read in its entirety in Appendix B.1. The script is a Matlab program which takes use of the functions butter, cheby1 and ellip in order to design digital IIR filters.

#### Initial values

The purpose of the filter generating algorithm is to generate a large number of filters, which eventually will be compared against each other. However, the filters are not intended to range from very poor performance to excellent performance. It is rather important that the filters are just slightly different, with almost identical performance. Hence, when generating the filters, it is decided to keep the filter order  $n_{ord}$  fixed at 3 for all solutions, and rather focus on the more fine-grained variations that rise when sweeping the cut-off frequency of the filter over a certain interval. The initial frequency  $f_c$  is set according to the specifications, to 1 MHz, and the frequency step interval is set to 8 kHz. This is the interval which the cut-off frequency increases from one filter solution to the next. Hence, as 100 filters of each type are generated, their cut-off frequencies range from 1 MHz to 1.8 MHz. All filters are converted from transfer function representation to second-order section representation in Matlab, using the tf2sos function, before quantizing the coefficients. The initial values are summarized in Table 4.2.

| Parameter  | Value           | Description                                        |

|------------|-----------------|----------------------------------------------------|

| $T_b$      | 100             | Number of Butterworth filters to be generated      |

| $T_c$      | 100             | Number of Chebyshev Type I filters to be generated |

| $T_e$      | 100             | Number of Elliptic filters to be generated         |

| $n_{ord}$  | 3               | Filter order                                       |

| $f_c$      | $1\mathrm{MHz}$ | The initial filter cut-off frequency               |

| $f_{step}$ | $8\mathrm{kHz}$ | Frequency step interval                            |

Table 4.2: Parameters in the filter generating algorithm

#### Definitions

A total of T filters are generated, grouped into a vector Y, defined as

$$Y = \{y^1, y^2, \cdots, y^{T-1}\}$$

#### 28 4. AUTOMATED FILTER GENERATION AND ELIGIBILITY CALCULATION

where  $y^i$  is the *i*th filter solution, and T is derived from

$$T = T_b + T_c + T_e$$

The cut-off frequencies of the implementations are given by the initial value  $f_c$ , the step value  $f_{step}$  and the filter implementation number i, as

$$f_c^i = \begin{cases} f_c + f_{step}(i-1) & \text{if} & 0 < i \le T_b \\ f_c + f_{step}(i-T_b-1) & \text{if} & T_b & < i \le T_b + T_c \\ f_c + f_{step}(i-T_b-T_c-1) & \text{if} & T_b + T_c & < i \le T \end{cases}$$

Each filter solution can be described by its N coefficients, defined in vector  $A^i$ , as

$$A^{i} = \{a_{0}^{i}, a_{1}^{i}, \cdots, a_{N^{i}-1}^{i}\}$$

The number of coefficients N in a cascaded biquadratic structured filter depends on the filter order  $n_{ord}$ , as

$$N = \left\lceil \frac{n_{ord}}{2} \right\rceil * 6$$

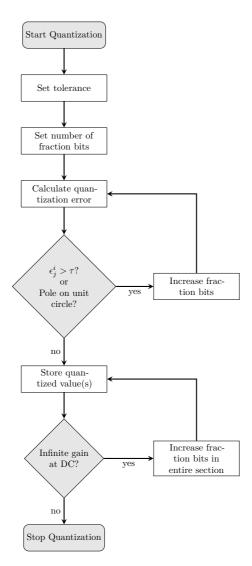

#### 4.2 Coefficient quantization algorithm

The coefficient quantization algorithm is the second step of the AFGEC algorithm. Its purpose is to represent the filter coefficients from the previous section with as few bits as possible, without changing the original values more than a predefined tolerance value. The coefficient quantization algorithm is visualized in Figure 4.2.

The quantization algorithm starts with zero fraction bits, and increases the number of bits after the decimal point as long as the quantization error  $\epsilon_j^i$  is greater than the tolerance  $\tau$ . A smaller tolerance value implies more accurate coefficients and hence a higher number of bits per coefficient. In this work, a tolerance value of  $2^{-3}$  is used. The number of fraction bits will also be increased if the filter after quantization has infinite gain for some frequency. This will occur if a pole is moved to the unit circle, i.e. if one of the feedback coefficients  $a_k$  are -1. Infinite gain can also occur at DC if the sum of  $a_k$ -coefficients are -1, since this implies that the denominator in Equation 2.2 is zero. If this occurs, the property will be tested again, with an increased number of fraction bits for all coefficients.

Figure 4.2: Flow chart of the coefficient quantization algorithm

#### Definitions

$\bar{Y}$  is the set of quantized filters, defined as

$$\bar{Y} = \{\bar{y}^1, \bar{y}^2, \cdots, \bar{y}^{T-1}\}$$

And  $\bar{A}^i$  is the vector of quantized coefficients in the *i*th filter solution, defined as

$$\bar{A}^i = \{\bar{a}^i_0, \bar{a}^i_1, \cdots, \bar{a}^i_{N^i-1}\}$$

The quantization error of the *j*th coefficient in the *i*th filter implementation,  $\epsilon_j^i$ , is defined as

$$\epsilon^i_j = a^i_j - \bar{a}^i_j$$

When each quantization is finished, the number of bits used to represent the coefficients in the *i*th filter is stored in the vector  $\bar{B}^i$ , which is defined as

$$\bar{B}^i = \{\bar{b}^i_0, \bar{b}^i_1, \cdots, \bar{b}^i_{N^i-1}\}$$

#### 4.3 Eligibility calculation

As the set of filters is generated and quantized, it is of interest to sort them based on how eligible they are for hardware implementation. For this, it is first necessary to extract some characteristics that can indicate how expensive it will be to implement each filter solution with regards to area and power dissipation.

#### 4.3.1 Characteristics

As the structure and order of the filters are selected, the coefficients are the only variables left which separate the solutions. The filter coefficients will define the number of multipliers, adders and shift operators used in the filter, and their complexity, which will have a significant impact on the filter's power dissipation. The following explains how these metrics can be extracted from the coefficient numbers.

#### Zero- and one-coefficients

The number of coefficients that are zero or one, are important parameters, as either of them implies that the circuit will require a multiplier less. For instance, if the coefficient  $b_{k2}$  in Figure 2.6 is 1, that multiplier can been removed, and the output from the second delay element can be wired directly to the following adder. And if  $b_{k2}$  is 0, not only the multiplier can be removed, but also the adder in front of  $b_{k1}$ . Hence, a zero-coefficient will also imply one less adder. The characteristics  $c_0^i$  and  $c_1^i$ are the rates of zero-coefficients and one-coefficients, respectively. These are defined as

#### 4.3. ELIGIBILITY CALCULATION 31

$$c_0^i = \frac{1}{N^i} \sum_{j=0}^{N^i-1} \alpha(a_j^i)$$

and

$$c_1^i = \frac{1}{N^i} \sum_{j=0}^{N^i - 1} \beta(a_j^i)$$

with the functions  $\alpha(x)$  and  $\beta(x)$  defined as

$$\alpha(x) = \begin{cases} 1 & \text{if } x = 0\\ 0 & \text{if } x \neq 0 \end{cases}$$

and

$$\beta(x) = \begin{cases} 1 & \text{if } x = 1\\ 0 & \text{if } x \neq 1 \end{cases}$$

As the number of zero- and one-coefficients are found, the remaining coefficients should be investigated, as these are the ones that will be implemented as multipliers and shift operators. When excluding the zero- and one-coefficients in  $A^i$ , we get the set of remaining coefficients  $\hat{A}^i$ , defined as

$$\hat{A}^{i} = \{\hat{a}^{i}_{0}, \hat{a}^{i}_{1}, \cdots, \hat{a}^{i}_{M^{i}-1}\}$$

and the corresponding vector with number of bits after quantization

$$\hat{B}^{i} = \{\hat{b}_{0}^{i}, \hat{b}_{1}^{i}, \cdots, \hat{b}_{M^{i}-1}^{i}\}$$

where  $M^i = N^i (1 - c_0^i - c_1^i)$ .

#### Single-one coefficients

If a coefficient have a binary representation that is all zeros except for a single-one bit, it will be implemented as a shift operation. For instance, the binary representation of the number 2 is 010.00, and the binary representation of the number 0.5 is 000.10. Coefficients that hold this property will have a smaller contribution to the power dissipation compared to a coefficient that is implemented as a multiplier, as a shift operator is less complex. The number of single-one-coefficients out of remaining coefficients is the characteristic  $c_2^i$ , defined as

$$c_2^i = \frac{1}{M^i} \sum_{j=0}^{M^i-1} \gamma(\hat{a}_j^i)$$

with the function  $\gamma(x)$  defined as

$$\gamma(x) = \begin{cases} 1 & \text{if } x \in \{2^i\}; \text{ where } i \in \mathbb{Z} \\ 0 & \text{otherwise} \end{cases}$$

#### Bits per coefficient

The parameter affecting the complexity of the multipliers and the shift operators, is the number of bits per coefficient, as this determines the amount of combinational logic. This describes the last characteristic  $c_3^i$  which is the average number of bits in the remaining coefficients, defined as

$$c_3^i = \frac{1}{M^i} \sum_{j=0}^{M^i - 1} \hat{b}_j^i$$

#### 4.3.2 Eligibility function