# Ultra-Low Power SAR-ADC in 28nm CMOS Technology

**Thomas Hanssen Nornes**

Master of Science in Electronics Submission date: July 2015 Supervisor: Trond Ytterdal, IET Co-supervisor: Snorre Aunet, IET Carsten Wulff, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

## Problem description

The project goal is to design a 10-bit, sub-nanowatt SAR ADC in 28nm FD-SOI technology with a sampling frequency of 1kS/s. Main performance characteristic is power consumption; with secondary characteristics being resolution and energy efficiency (FOM).

The project tasks are as follows:

- Confirm validity of previous work in the new technology

- · Improve on previous work

- Do design and layout of the ADC at transistor level

- Characterize performance through simulation.

Design specifications are as follows:

| Parameter           | Value       |  |

|---------------------|-------------|--|

| CMOS technology     | 28nm FD-SOI |  |

| Supply voltage      | < 1V        |  |

| Maximum input level | $1V_{pp}$   |  |

| Sampling frequency  | 1kHz        |  |

| Resolution          | 10-bit      |  |

The project was given on January 19, 2015. It was supervised by Trond Ytterdal, IET , together with assistant supervisior Carsten Wulf ,IET , and Snorre Aunet, IET .

### Abstract

This thesis presents an improved ultra-low power 10-bit 1 kS/s successive approximation register (SAR) analog to digital converter (ADC) building on the work performed by Simon Josepshen in 2013. The improved ADC has a supply of 450mV and operates at almost half the power consumption of previous work; achieving a consumption of 691.5 pW in post-layout simulation. This is possibly the best power consumption found in available literature. Higher resolution and lower power consumption is achieved with incremental changes to the original design and by exploiting the benefits of new technology. The design differs from the previous in some key ways; having a different comparator topology, different switching procedure and asynchronous operation. The effective resoultion is found to be around 9.4-bit, giving a figure-of-merit of 1.0 fJ/conversion-step.

### Sammendrag

Denne masteroppgaven presenterer en ultra-laveffekt 10-bit 1 kS/s suksessivt-tilnærmingsregister (SAR) analog til digital converter (ADC) som bygger på tidligere utført arbeid av Simon Josephsen i 2013. Den forbedrede ADCen har en spenningsforsyning på 450 mV og opererer med tilnærmet halvparten av effektforbruket til forrige design; med et forbruk på 691.5 pW i simulering etter utlegg. Dette er muligens det beste strømforbruket som finnes i tilgjengelig litteratur. Høyere oppløsning og lavere effektforbruk er oppnåd gjennom inkrementelle forandringer til det originale designet og ved å utnytte fordeller med ny teknologi. Designet skiller seg fra forrige design i noen nøkkelområder; den har en annen komparator topologi, annen tilnærminsprossedyre og asynkron operasjon. Den effektive oppløsningen ble funnet til å være rundt 9.4-bit, noe som gir et godhetstall på 1.0 fJ/konverterings-steg.

## Preface

This thesis is submitted in partial fullfillment of the requirements for the degree of Master of Science (MSc ) at the Department for Electronics and Telecommunication (IET ), Norwegian University of Science and Technology (NTNU ). The work was carried out in the period of January to July 2015, under the supervision of Professor Trond Ytterdal, who is with the IET at NTNU .

#### Acknowledgements

I would like to thank Professor Trond Ytterdal for suggesting the project and for providing his insight and advice. Another thanks to Carsten Wulff for providing insightfull advice and technical support.

Thanks to all the analog-guys in the reading room; Endre Larsen Spydeberg, Harald Garvik and Erlend Strandvik Reindalen, its been nice sharing this last part of the master-degree with you. The previous experience you guys had was a great help. Extra thanks to Harald Garvik for supplying the load capacitors used in this project.

I would also like to thank Professor Snorre Aunet and Aslak L. Holen Lom for pointers and advice regarding the digital portion of the project.

# Table of Contents

| Pro        | oblem       | description i                                  |  |

|------------|-------------|------------------------------------------------|--|

| Ab         | Abstract ii |                                                |  |

| Sammendrag |             |                                                |  |

| Pre        | eface       | vii                                            |  |

| Ta         | ble of (    | Contents ix                                    |  |

| Lis        | st of Ta    | bles xiii                                      |  |

| Lis        | st of Fi    | gures xv                                       |  |

| Ab         | brevia      | tions xvii                                     |  |

| 1          | Intro       | duction                                        |  |

|            | 1.1         | Project specifications                         |  |

|            | 1.2         | Main contributions 2                           |  |

|            | 1.3         | Report outline                                 |  |

| 2          | Low         | power digital design                           |  |

|            | 2.1         | Noise                                          |  |

|            | 2.1.1       | Thermal noise                                  |  |

|            | 2.1.2       | Flicker noise                                  |  |

|            | 2.2         | Process variation and mismatch                 |  |

|            | 2.3         | Power dissipation                              |  |

|            | 2.4         | CMOS thyristor                                 |  |

|            | 2.5         | Voltage scaling in analog CMOS 8               |  |

|            | 2.6         | Fully Depleted Silicon-on-Insulator (FD-SOI)   |  |

|            | 2.7         | Transistor current drive in ultra low power 10 |  |

|            | 2.8         | Gated Clock Routing 11                         |  |

|            | 2.9         | Sampling switch 11                             |  |

|            | 2.10        | Transistor leakage in sub-treshold 13          |  |

|            | 2.11        | Placement using Weinberger image 13            |  |

|   | 2.12                                                                                                                                              | Successive Approximation Register                                                                                                                                                                                                                     | 14                                                                     |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

|   | 2.13                                                                                                                                              | Comparator                                                                                                                                                                                                                                            | 15                                                                     |

|   | 2.13.1                                                                                                                                            | Kickback effect                                                                                                                                                                                                                                       | 17                                                                     |

|   | 2.13.2                                                                                                                                            | Latch offset                                                                                                                                                                                                                                          | 17                                                                     |

|   | 2.13.3                                                                                                                                            | Hysteresis                                                                                                                                                                                                                                            | 17                                                                     |

|   | 2.13.4                                                                                                                                            | Metastability                                                                                                                                                                                                                                         | 17                                                                     |

| 3 | The st                                                                                                                                            | ate of ultra low power                                                                                                                                                                                                                                | 19                                                                     |

|   | 3.1                                                                                                                                               | State-of-the-art                                                                                                                                                                                                                                      | 19                                                                     |

|   | 3.2                                                                                                                                               | General trends in low power design                                                                                                                                                                                                                    | 19                                                                     |

|   | 3.3                                                                                                                                               | Successive approximation algorithms                                                                                                                                                                                                                   | 21                                                                     |

|   | 3.3.1                                                                                                                                             | Monotonic switching procedure                                                                                                                                                                                                                         | 21                                                                     |

|   | 3.3.2                                                                                                                                             | Switchback procedure                                                                                                                                                                                                                                  | 22                                                                     |

|   | 3.3.3                                                                                                                                             | Merged capacitor switching                                                                                                                                                                                                                            | 22                                                                     |

| 4 | Syster                                                                                                                                            | n design and methodology                                                                                                                                                                                                                              | 23                                                                     |

|   | 4.1                                                                                                                                               | System overview                                                                                                                                                                                                                                       | 23                                                                     |

|   | 4.2                                                                                                                                               | Design strategy                                                                                                                                                                                                                                       | 24                                                                     |

|   |                                                                                                                                                   |                                                                                                                                                                                                                                                       |                                                                        |

|   | 4.2.1                                                                                                                                             | Framework                                                                                                                                                                                                                                             | 24                                                                     |

|   | 4.2.1<br>4.2.2                                                                                                                                    | Framework      Ideal system models                                                                                                                                                                                                                    | 24<br>24                                                               |

|   |                                                                                                                                                   |                                                                                                                                                                                                                                                       |                                                                        |

|   | 4.2.2<br>4.2.3                                                                                                                                    | Ideal system models                                                                                                                                                                                                                                   | 24                                                                     |

|   | <ul><li>4.2.2</li><li>4.2.3</li><li>4.3</li></ul>                                                                                                 | Ideal system models                                                                                                                                                                                                                                   | 24<br>25                                                               |

|   | <ul><li>4.2.2</li><li>4.2.3</li><li>4.3</li><li>4.4</li></ul>                                                                                     | Ideal system models          External circuitry          Digital transistor sizing                                                                                                                                                                    | 24<br>25<br>25                                                         |

|   | <ul> <li>4.2.2</li> <li>4.2.3</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>                                                                   | Ideal system models         External circuitry         Digital transistor sizing         Clocking scheme                                                                                                                                              | 24<br>25<br>25<br>26                                                   |

|   | <ul> <li>4.2.2</li> <li>4.2.3</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>                                                      | Ideal system models         External circuitry         Digital transistor sizing         Clocking scheme         Sampling signal generation                                                                                                           | 24<br>25<br>25<br>26<br>28                                             |

|   | <ul> <li>4.2.2</li> <li>4.2.3</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ul>                                         | Ideal system models         External circuitry         Digital transistor sizing         Clocking scheme         Sampling signal generation         Delay element                                                                                     | 24<br>25<br>25<br>26<br>28<br>28                                       |

|   | <ul> <li>4.2.2</li> <li>4.2.3</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> </ul>                            | Ideal system models         External circuitry         Digital transistor sizing         Clocking scheme         Sampling signal generation         Delay element         Bootstrapped sampling switch                                                | <ul> <li>24</li> <li>25</li> <li>26</li> <li>28</li> <li>30</li> </ul> |

|   | <ul> <li>4.2.2</li> <li>4.2.3</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ul>               | Ideal system models         External circuitry         Digital transistor sizing         Clocking scheme         Sampling signal generation         Delay element         Bootstrapped sampling switch         Comparator                             | 24<br>25<br>25<br>26<br>28<br>28<br>30<br>31                           |

|   | <ul> <li>4.2.2</li> <li>4.2.3</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> </ul> | Ideal system models         External circuitry         Digital transistor sizing         Clocking scheme         Sampling signal generation         Delay element         Bootstrapped sampling switch         Comparator         Switching procedure | 24<br>25<br>25<br>26<br>28<br>28<br>30<br>31<br>34                     |

| 5   | Layo            | ut                                   | 39 |

|-----|-----------------|--------------------------------------|----|

|     | 5.1             | Digital routing                      | 39 |

|     | 5.2             | Custom capacitors                    | 40 |

|     | 5.3             | Final layout                         | 40 |

| 6   | Resu            | lts                                  | 43 |

|     | 6.1             | Pre-layout simulations               | 43 |

|     | 6.2             | Post-layout                          | 44 |

| 7   | Discu           | ission                               | 47 |

|     | 7.1             | System power consumption             | 47 |

|     | 7.2             | DAC                                  | 48 |

|     | 7.3             | Changing to the switchback algorithm | 48 |

|     | 7.4             | Comparator                           | 49 |

|     | 7.5             | Digital logic                        | 49 |

|     | 7.6             | Asynchronous operation               | 49 |

|     | 7.7             | Choice of delay element              | 50 |

|     | 7.8             | Future work                          | 50 |

|     | 7.9             | Bootstrapped                         | 51 |

|     | 7.10            | Comparison with previous work        | 51 |

| 8   | Conc            | lusion                               | 53 |

| Bil | Bibliography 55 |                                      |    |

| A   | Veril           | og code                              | 59 |

|     | A.1             | Ideal comparator                     | 59 |

|     | A.2             | Ideal capacitor array                | 60 |

|     | A.3             | Ideal control logic                  | 61 |

| B   | Sche            | matics                               | 64 |

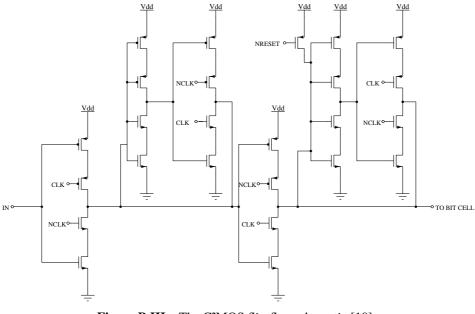

|     | <b>B</b> .1     | Clock feedback control               | 64 |

|     | B.2             | Internal clock generator             | 64 |

|     | B.3             | C <sup>2</sup> MOS flip-flop         | 64 |

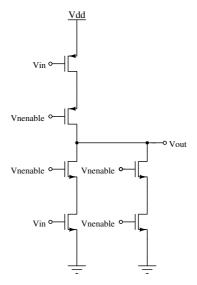

|     | B.4             | Tri-state inverter                   | 65 |

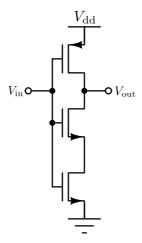

|     | B.5             | Comparator output inverters          | 65 |

|     |                 |                                      |    |

## List of Tables

| 6.1 | Schematic transient noise analysis. ( $C_u = 1 \text{ fF}$ )          | 43 |

|-----|-----------------------------------------------------------------------|----|

| 6.2 | The static power consumption in the ADC ( $C_u = 2 \text{ fF}$ ).     | 44 |

| 6.3 | Results of 60 Monte Carlo runs of 64 sample transients simulating     |    |

|     | mismatch. These simulations where made before layout and used a 1     |    |

|     | fF unit capacitor and 430mV <sub>pp</sub> input.                      | 44 |

| 6.4 | Transient noise analysis post layout used to check the ENOB variation |    |

|     | over corners. Supply voltage was 450 mV for all corners.              | 45 |

| 6.5 | Post-layout performance summary                                       | 46 |

| 6.6 | The power consumption in the ADC before and after layout ( $C_u = 2$  |    |

|     | fF for both).                                                         | 46 |

| 7.1 | Comparison of this work with the previous work                        | 51 |

# List of Figures

| 2.1  | Switching power in a conventional inverter.                          | 7  |

|------|----------------------------------------------------------------------|----|

| 2.2  | The basic concept of a CMOS thyristor [1].                           | 8  |

| 2.3  | Illustration of how voltage scaling affects power consumption        |    |

|      | over four technology generations. The plot shows the minimum         |    |

|      | power consumption for an (arbitrary) analog circuit and the circles  |    |

|      | correspond to the power consumption in a technology at the nominal   |    |

|      | supply voltage for each CMOS process [2].                            | 9  |

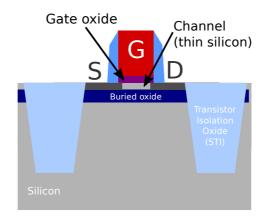

| 2.4  | Planar FD-SOI transistor [3]                                         | 10 |

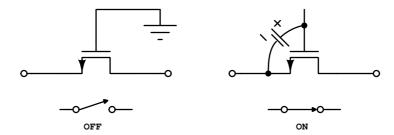

| 2.6  | Basic function of a bootstrapped switch                              | 12 |

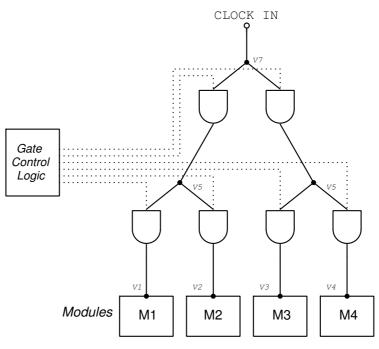

| 2.5  | Gated clock tree [4]                                                 | 12 |

| 2.7  | Different transistor row placement techniques. High freedom          |    |

|      | placement to the left and high density placement on the right [5].   | 14 |

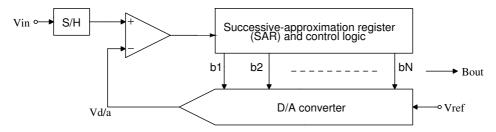

| 2.8  | D/A converter-based successive-approximation converter [6].          | 15 |

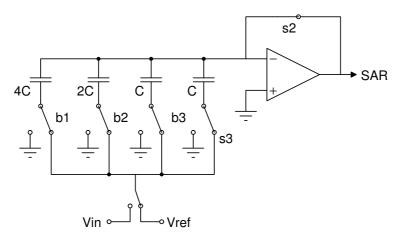

| 2.9  | Charge-Redistribution A/D in a sampling phase [6].                   | 15 |

| 2.10 | The popular StrongARM dynamic track and latch comparator.            | 16 |

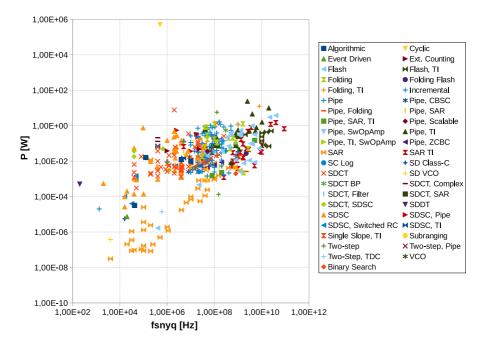

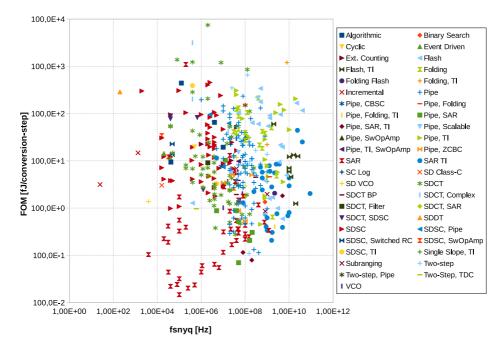

| 3.1  | The power consumption of different types of ADC architectures        |    |

|      | published in [7] compared against the nyquist sampling frequency.    | 20 |

| 3.2  | A plot of FOM against the nyquist frequency for the different SAR    |    |

|      | architectures published in [7].                                      | 21 |

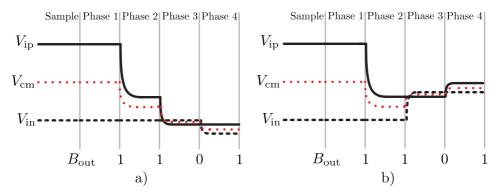

| 3.3  | Illustration of the common mode variation in monotonic (a) and       |    |

|      | switchback (b) [8].                                                  | 22 |

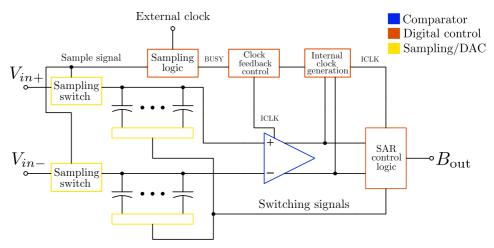

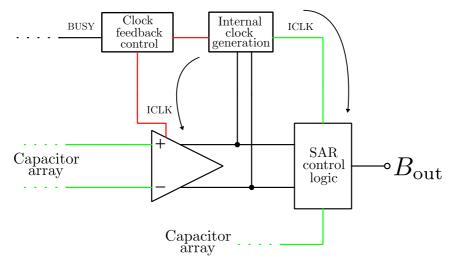

| 4.1  | Abstract overview schematic of the ADC. Component colors             |    |

|      | correspond to the system division used in this thesis.               | 24 |

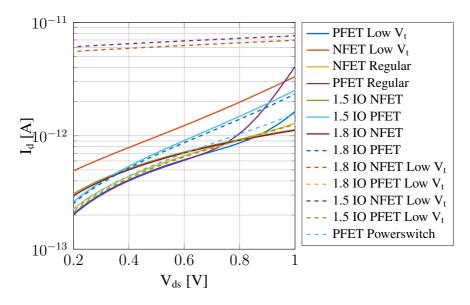

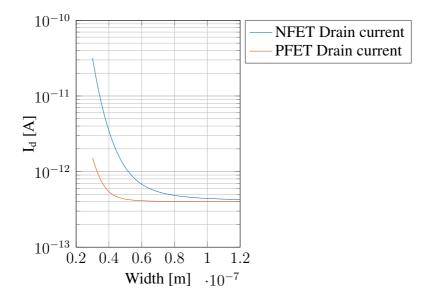

| 4.2  | The leakage currents for all transistors in the current technology.  |    |

|      | Transistors gate voltages are set to the OFF state and current is    |    |

|      | measured through the drain. All transistors have the same dimensions |    |

|      | based on the largest default value.                                  | 26 |

| 4.3  | Adjusting the length of regular $V_t$ pfet and nfet transistors at a |    |

|      | constant supply of 0.4V and a width of 80nm. The graph shows the     |    |

|      | resulting static current.                                            | 27 |

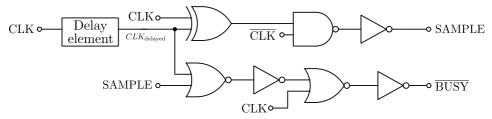

| 4.4  | Paths in the system that could case a race condition. Green must     |    |

|      | propagate before red.                                                | 27 |

| 4.5  | The sample logic block (SL) that is used to generates the SAMPLE     |    |

|      | and BUSY signal in the ADC.                                          | 28 |

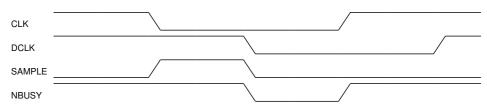

| 4.6  | Timing diagram for the sampling logic block shown in Figure 4.5.     | 29 |

| 4.7  | Statically triggered thyristor based delay element from [1].         | 30 |

|      |                                                                      |    |

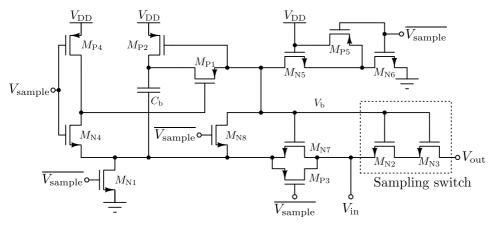

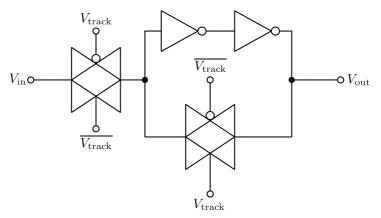

| The boostrapped nfet-type switch used in the ADC design.               | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

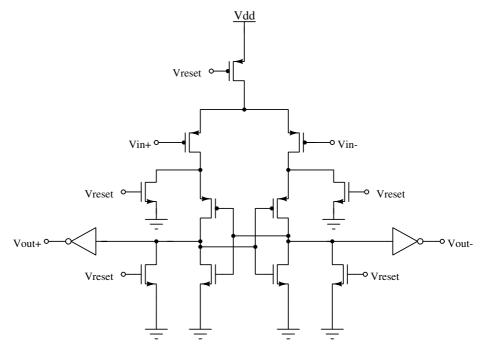

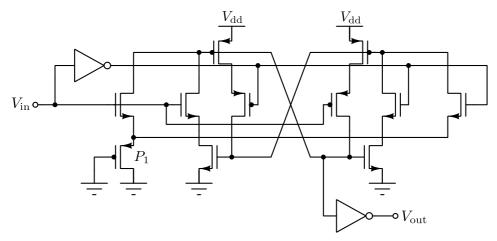

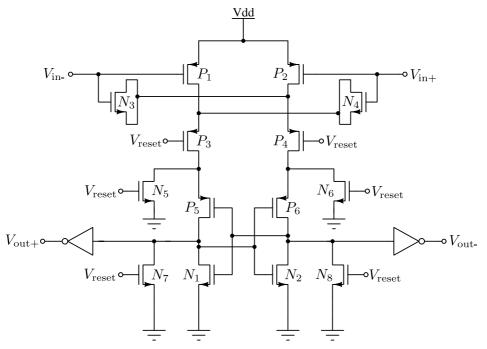

| The dynamic latched comparator used in the ADC.                        | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

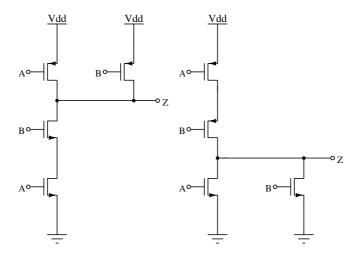

| The conventional 4 transistor NAND (left) and NOR (right) gate         | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

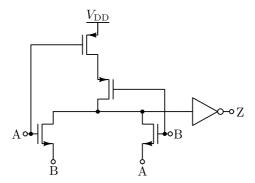

| A XOR gate based on both pass logic and static logic [9].              | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

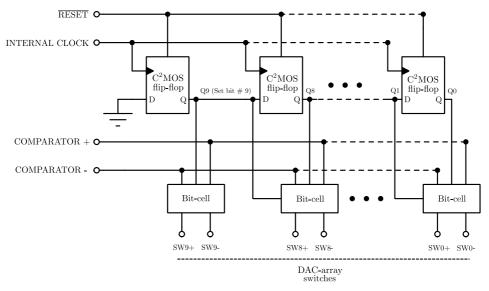

| The flip-flop-based shift register and bit-cells used to implement the |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| successive approximation algorithm.                                    | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

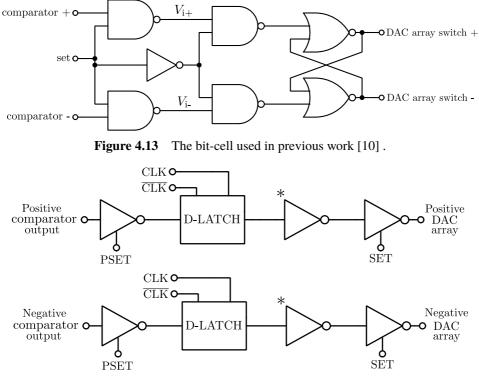

| The bit-cell used in previous work [10].                               | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| The bit cell circuit.                                                  | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| The D-latch used in the ADC bit cells.                                 | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

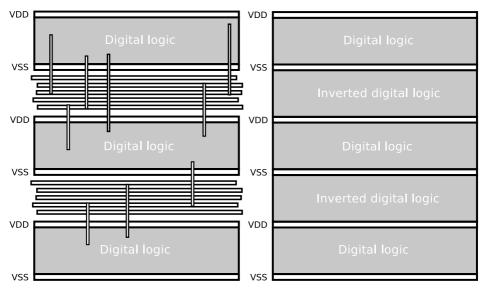

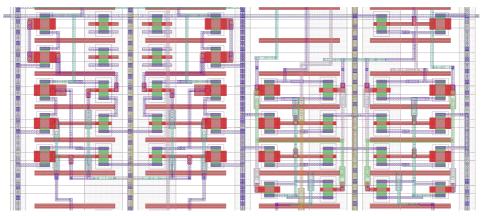

| Digital logic layout in a Weinberger image.                            | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A $4C_{\rm u}$ (8fF) capacitor used in the DAC capacitor array.        | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

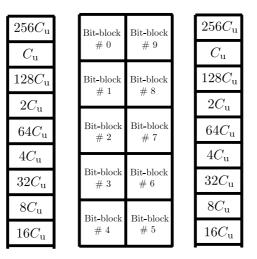

| The organization of the digital "bit-blocks" and the grouping of the   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DAC array capacitors.                                                  | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

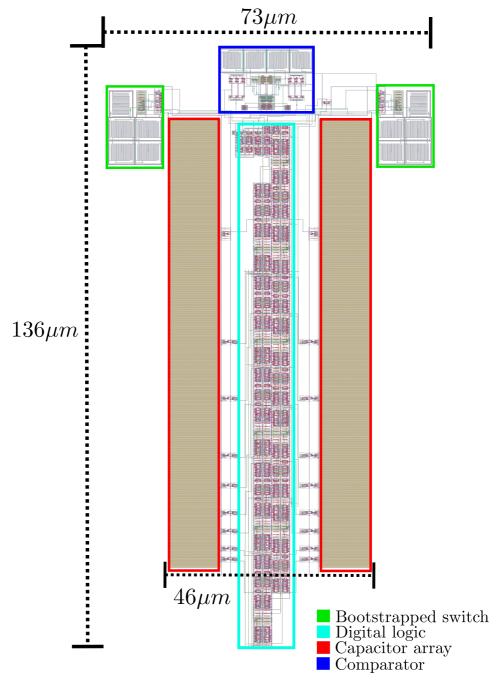

| The complete SAR ADC layout.                                           | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

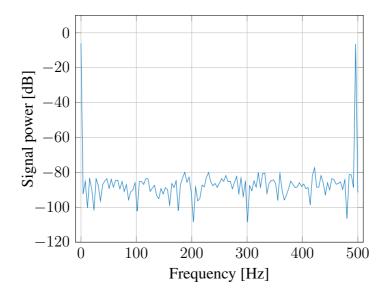

| Spectrum of a 256 sample transient noise analysis after layout.        | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

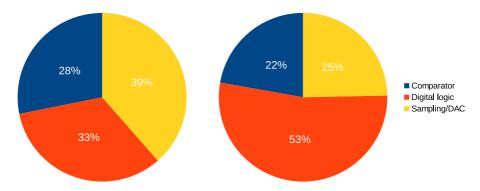

| The power distribution in the ADC pre-layout (left) and                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| post-layout(right) based on the values in Table 6.6.                   | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

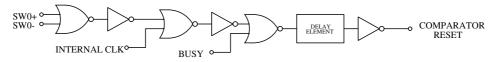

| Asynchronous loop control logic.                                       | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

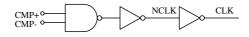

| Internal clock generating logic.                                       | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| The C <sup>2</sup> MOS flip-flop schematic [10].                       | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Inverter with three states. Normal operation and high impedace input   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| and low output.                                                        | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Inverter used in the comparator.                                       | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        | The dynamic latched comparator used in the ADC .<br>The conventional 4 transistor NAND (left) and NOR (right) gate<br>A XOR gate based on both pass logic and static logic [9].<br>The flip-flop-based shift register and bit-cells used to implement the<br>successive approximation algorithm.<br>The bit-cell used in previous work [10] .<br>The bit-cell used in previous work [10] .<br>The bit cell circuit.<br>The D-latch used in the ADC bit cells.<br>Digital logic layout in a Weinberger image.<br>A $4C_u$ (8fF) capacitor used in the DAC capacitor array.<br>The organization of the digital "bit-blocks" and the grouping of the<br>DAC array capacitors.<br>The complete SAR ADC layout.<br>Spectrum of a 256 sample transient noise analysis after layout.<br>The power distribution in the ADC pre-layout (left) and<br>post-layout(right) based on the values in Table 6.6.<br>Asynchronous loop control logic.<br>Internal clock generating logic.<br>The C <sup>2</sup> MOS flip-flop schematic [10] .<br>Inverter with three states. Normal operation and high impedace input<br>and low output. |

## Abbreviations

| ADC    | analog to digital converter                      |

|--------|--------------------------------------------------|

| CMOS   | complementary metal-oxide-semiconductor          |

| DAC    | digital to analog converter                      |

| DIBL   | drain-induced barrier lowering                   |

| ENOB   | effective numbers of bits                        |

| FD-SOI | fully depleted silicon-on-insulator              |

| FOM    | figure-of-merit                                  |

| IET    | Department for Electronics and Telecommunication |

| MSc    | Master of Science                                |

| NTNU   | Norwegian University of Science and Technology   |

| SAR    | successive approximation register                |

| SCE    | short channel effects                            |

| SNR    | signal noise ratio                               |

| SOI    | silicon-on-insulator                             |

| SOTB   | Silicon on Thin BOX                              |

# Chapter 1

## Introduction

The device that bridges the analog and digital world is known as an analog to digital converter (ADC). Digital systems are not able to read an analog signal unless they are converted from an analog quantity into a digital number. This is the jobb of the ADC, and it is used in most applications where digital systems are "sensing" the real world in a non-binary way<sup>1</sup>. Some examples are; radio recievers, cameras, audio recorders, gyroscopes and touchscreens.

As technology scales down, digital circuits see significant performance improvements in speed and power consumption. This is true, to a lesser extent for analog circuits. A rule of thumb is that an analog device consumes more power than a comparable digital device. ADCs are partially analog and partially digital; with the latter becomming more important in the future. Today most of the afforementioned devices and sensors can be found on a cell-phone or tablet, and as a consequence, improvements in ADC power consumption play a key role in extending battery life and functionality of wearable electronics. New medical applications become available as battery life is extended. Wireless sensor nodes are often mentioned as a motivation for reducing ADC power usage. Increased life for sensor nodes enables long term monitoring of patients and can eliviate risks associated with severeal cronic medical conditions. Other emerging fields such as energy harvesters [11] will benefits greatly from any power reduction in analog components.

### **1.1 Project specifications**

This master's thesis aims to implement an ultra-low power ADC in 28nm fully depleted silicon-on-insulator (FD-SOI) technology with a sampling frequency of 1 kS/s, 10-bit resolution, asynchronous operation and sub-nanowatt power consumption. It builds on a previous master's thesis from 2013 by Simon Josephsen [10]; in which, he designed and simulated a 9-bit ultra-low power ADC in 65nm technology. His work resulted in world class ultra-low power performance, obtaining a power consumption of 1.2 nW.

Since comparing different analog designs against each other is not straight forward, designers usually adopt some figure-of-merit (FOM). These equations can be seen as weights that prioritize different strengths of a system. When referring to FOM in this thesis, it will be the in the form shown below:

A keyboard is a binary input device since it only detects two levels.

$$FOM = \frac{P_{\text{total}}}{2^{\text{ENOB}} \cdot f_{\text{s}}} \left[ J/\text{conversion-step} \right]$$

(1.1)

The formula provides a way to measure the effectiveness of a given design based on a few parameters:  $P_{\text{tot}}$  being the total power consumed by the system, ENOB is the effective numbers of bits and  $f_s$  is the Nyquist sampling frequency.

### 1.2 Main contributions

This thesis presents a ADC design which improves on previous work by achieving, to the authors knowledge, the lowest published power consumption, and world class FOM. Improvements to the power consumption and resolution of the design is achieved by:

- changing the clocking scheme from synchronous to asynchronous,

- choosing a more optimal switching scheme,

- changing the topology of logic gates and replacing large clusters of gates with dedicated circuits,

- reducing overall capacitance use,

- change of comparator topology,

- increasing the supply voltage.

#### 1.3 Report outline

The report will be organized as follows:

- 1. **Chapter 2** provides background theory relevant to the later chapters in this report. It covers some general non-idealities and some application specific non-idealities, power consumption, technology properties, digital power saving and a short description of typical SAR ADCs building blocks.

- 2. **Chapter 3** covers the current state-of-the-art in ultra low power design, general trends and typical topologies.

- 3. **Chapter 4** describes the full ADC from a top level perspective and covers each sub-component in detail. It will also elucidate design considerations an justify the changes made to the previous design.

### 3 Chapter 1 - Introduction

- 4. **Chapter 5** presents the ADC layout and briefly comments on design considerations and problems associated with the work.

- 5. Chapter 6 presents the results from circuit simulations; both pre and post-layout.

- 6. Chapter 7 provides a discussion around the results in chapter 6.

- 7. Chapter 8 presents the conclusion.

# Chapter 2 Low power digital design

This chapter will present theory that is relevant to the digital portion of the design process. Important concepts such as dynamic and static power consumption will be explained as well as the different design techniques available for low power design.

#### 2.1 Noise

Noise is always present in electronic circuits. There are two sources of circuit noise. One is the inteference from the outside world; in which case it can be eliminated through carefull design optimization, the other is inherent noise which can never ble eliminated as they are occur due to the structure and function of the components in the circuit. The two main types of inherent noise are: thermal and flicker noise.

#### 2.1.1 Thermal noise

Capacitors do not generate noise, but instead accumulate it. The effect of noise from other devices can be reduced by connecting larger capacitances to their nodes. In a circuit consisting only of passive devices and MOSFETS in their triode region, the squared rms noise on each capacitor is as in [6] :

$$V_{no(rms)}^2 = \frac{kT}{C} \tag{2.1}$$

where k is the Boltzmann's constant, T is the temperature in Kelvin and  $C_s$  is the capacitor where noise is accumulated.

#### 2.1.2 Flicker noise

Regarding flicker noise; [12] says that "This has perhaps been the most widely studied and debated phenomena in the history of noise." while descibing the 50-year history of MOS-FET noise studies. There has been some debate regarding the source of the 1/f fluctuations in transistors. The two main theories have been that they are either caused by carrier trapping and deptrapping at the oxide-semiconductor interface (number fluctuation) or mobil-ity fluctuations due to bulk effects. The former has the most consensus. The flicker noise model for MOSFETs used in most simulators is as follows:

$$i_n^2 = \frac{K}{f} \frac{g_m^2}{WLC_{ox}^2} \Delta f \tag{2.2}$$

K is a konstant dependent on the device type,  $g_m$  is the transconductance, W and L are the gate dimensions,  $C_{ox}$  is the gate capacitance per unit area, f is the frequency, and  $\Delta f$  is the bandwidth of observation [12], [6].

#### 2.2 Process variation and mismatch

Several of the variations of the transistor parameters are a result of the fabrication procedure. For example; dopant consentration and oxide thickness vary considerably and result in significant variations in  $V_t$  and capacitances. In order to design for these variations, factories provide several transistor models that represent different process corners.

The reproduceability of any fabrication process will have limits, making it impossible to produce transistors that are perfectly identical. This mismatch between transistors exists even in the absence of the previously mentioned process variations.

The doping used in several modern technologies is a good example. Transistors are made using a small number of dopants, as few as a hundred, and will vary with the location on the substrate. This changes parameters such as treshold voltage.

$$\sigma^2(\Delta P) = \frac{A_{\rm p}^2}{WL} + S_{\rm p}^2 D^2 \tag{2.3}$$

The above equation describes the expected Gaussian variation in device parameter P between two devices. W and L denote the device dimensions and D is the distance between them.  $S_P$  and  $A_P$  are proporsonal constants derived through experimental measurement. Variations in  $V_t$  and  $K' = \mu_n C_{ox} W/L$  are often the most important when doing analog design.

#### 2.3 Power dissipation

There are three main sources of power dissipation; short circuit power, dynamic power and static power. An expression for the total power consumption in digital CMOS circuits is presented as described in [13] :

$$P_{\text{total}} = p_t (C_L \cdot V \cdot V_{dd} \cdot f_{clk}) + I_{sc} \cdot V_{dd} + I_{\text{leakage}} \cdot V_{dd}$$

(2.4)

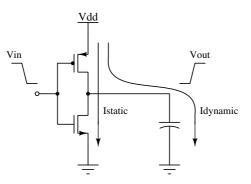

Dynamic power consumption comes from the charging and discharging of internal capacitances in a circuit. Dynamic power increases with the number of transitions during circuit operation and scales with the supply voltage. The first term in Equation(2.4) describes the dynamic power consumption.  $p_t$  is the probability of a transition occuring. The voltage swing is defined by V; usually the supply voltage, but it can be lower.  $C_L$  is the switching capacitance being charged or discharged during a transition; as illustrated in Figure 2.1.  $f_{clk}$  is the switching frequency.

The second term in Equation(2.4) comes from the short circuits that occur in during switching of CMOS circuits. Consider the inverter shown in Figure 2.1. As the input signal transitions from low to high, at one point both transistors are on, creating a temporary short between supply and ground. Shorts can increase power consumption if rise and fall times are uneven or the input signal transition is too slow. Low power circuits will usually have slower transition speeds than a conventional circuit. This is due to the reduced supply voltage and the way transistors are sized for low power. Because of this, short circuits become a larger contributor to the total power consumption in low power circuits [14] . The effect can be largely ignored if correct transistor sizing is employed, meaning that rise and fall times are approximately equal.

The third term is the leakage power, which is consumed when transistors are in their off state. Retaining the same performance while lowering the supply voltages is done by reducing the treshold voltage ( $V_t$ ); ensuring the similar current drive. This comes with a penalty in the form of increased leakage currents; increasing static power consumption.

**Figure 2.1** Switching power in a conventional inverter.

#### 2.4 CMOS thyristor

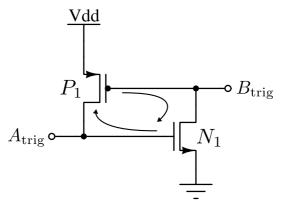

A thyristor is a circuit element quite similar to a transistor. In its simplest form it has three nodes: an anode, cathode and gate. What differentiates the thyristor from a transistor is that once a voltage or current has been applied to its input, causing it to conduct, removing this input will not stop it from conducting. Simply put; it is a latch and once it is conducting, the

Figure 2.2 The basic concept of a CMOS thyristor [1].

only way stop it is to remove the supply [15]. Figure 2.2 shows the concept of implementing a thyristor using regular CMOS transistors. The positive feedback effect is illustrated by the arrows.

#### 2.5 Voltage scaling in analog CMOS

Digital circuits have benefited greatly from the continued downscaling of CMOS technology, achieving increased integration density, greater performance and lower power consumption. A downscaling of supply voltage has followed; compensating for the increased thermal power dissipated in these circuits. At the same time, development has shifted from independent integrated circuits over to system on chip type designs. Meaning that analog and digital components frequently need to be integrated on a single die using the same technology. This presents issues for analog design in modern and future ultra deep submicron CMOS processes [2].

Analog performance is closely linked to the power consumption; an increase in performance will need an increase in power. The required signal integrity (SNR or SINAD) puts limits on the lowest possible power consumption in a circuit. This limit is essensially the energy required to keep the signals above that of the thermal noise. [16]. In [17] this requirement is epxressed as the minimum power per pole:

$$P/f = 8kT \left(\frac{V_S}{V_N}\right)^2 [J]$$

(2.5)

Here, f is the signal frequency bandwidth, k is the Boltzmann constant, T is the temperature in Kevlin and the last part is the signal to noise ration (SNR). This limit is independent

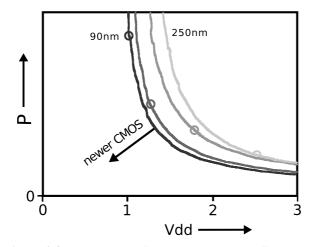

**Figure 2.3** Illustration of how voltage scaling affects power consumption over four technology generations. The plot shows the minimum power consumption for an (arbitrary) analog circuit and the circles correspond to the power consumption in a technology at the nominal supply voltage for each CMOS process [2].

of technology and corresponds to a 10-fold increase in power for each 10dB increase in S/N [16]. The minimum power consumption of digital circuits is given by the number of logic gate transitions m, each using a certain amount of energy  $E_{tr}$ . The m transitions are proporsonal to a power of the number of bits  $N_{bit}$  and is therefore only weakly dependent on the SNR.

$$P = m \cdot f \cdot E_{tr} + P_{stat} \quad (2.6)$$

The general trend is that moving to a new technology causes a drop in performance; given the same power budget [2]. For an analog design, a decrease in supply voltage, leads to and increase in the minimum power consumption. If the supply voltage can be held constant; moving to a new technology reduces power consumption.

#### 2.6 Fully Depleted Silicon-on-Insulator (FD-SOI)

SOI processes are considered more suitable for ultra low power applications compared to the conventional bulk CMOS processes; enabling higher density integration, speed and reduced power consumption. Figure 2.4 shows the general build-up of a FD-SOI type transistor. The use of an insulator below a thin layer of silicon eliminates a large portion of the capacitances found in bulk CMOS [18].

Figure 2.4 Planar FD-SOI transistor [3]

As technology scales down, the variations in  $V_{\rm th}$  become increasingly significant and difficult to negate. The shorter gate lengths also lead to an increase in short channel effects (SCE). Such an effect is the drain-induced barrier lowering (DIBL); resulting in a higher number of charge carriers injected into the channel from the source. This increases the drain off-current ( $I_D$ ) and reduces the gate voltages ability to control drain current[19] [20]. These are challenges facing conventional bulk MOS-FET processes in the sub 100nm era.

The fully depleted silicon-on-insulator (FD-SOI) process has less  $V_{th}$  variation compared to bulk MOS-FET; while also having, reduced soft-error-rates, pn-junction leakage, node capacitance and reduction in SCE. The latter has been linked to some interesting dynamics where SCE unique to SOI interact with effects such as DIBL resulting in some performance improvements [19]. The influence on threshold voltage through the body effect is significantly reduced in SOI; providing higher possible swing and gain [21]. A recent advancement in FD-SOI is the use of Silicon on Thin BOX. A very thin buried oxide (BOX) layer, only 10nm thick, enabling easy voltage adjustment of the back gate; similar to the substrate bias in bulk-MOS device [20] [22] [23].

#### 2.7 Transistor current drive in ultra low power

The typical tuning parameters are the same in sub-threshold as they are in above threshold, but the relationships between them are quite different. As the effective voltage ( $V_{\text{eff}}$ ) becomes negative, the transistor enters the sub-threshold region. Its drain current can then be approximated using the following relationship [6]:

$$I_{\rm D(sub-th)} \cong I_{\rm D0} \left(\frac{W}{L}\right) e^{(qV_{\rm eff}/nkT)}$$

(2.7)

In sub-threshold, the linear relationship W/L has a direct influence on the  $V_{\text{th}}$  of the transistor [24]. This means that W/L sizing does not have the same effect as in above threshold. The sizing of W for example; has a smaller effect on the transistor driving power due to the reverse narrow channel effect (RNCE).

A given technology will usually provide transistors with either low or high threshold voltage  $(V_t)$ . This is a more efficient way to increase current drive than scaling the transistor due to the exponential relationship shown in Equation(2.7). Going from a high  $V_t$  transistor to a low  $V_t$  transistor can increase current drive about 18 times [24]. Body biasing also has a similar this relationship and can further be used to increase current drive of a transistor. The available tuning parameters in the order of effectiveness in sub-threshold:

- using low  $V_t$ /high  $V_t$  transistors,

- bulk voltage tuning,

- tuning the aspect ratio W/L.

#### 2.8 Gated Clock Routing

A digital power reduction method that gained attention at the end of 20th century was the use of clocked gating<sup>2</sup>. The method uses the fact that in a typical digital system; such as a microprocessor; only some parts of the system are active at any given time. An un-gated system might experience redundant switching in some nodes, leading to uneccessary power consumption [4]. As can be seen in Figure 2.5, clocked gating isolates internal module nodes from the a clock line using buffers. These are enabled and disabled based on the system state. Since the combinatorial logic inputs are kepts static in the idle state, less dynamic power is consumed.

#### 2.9 Sampling switch

At higher voltage and oxide thickness, boosting the input voltage to  $2V_{DD}$  provides a way to increase current drive of a transistor. This is done using what is commonly called a charge-pump or clock boosting; combining the sampled voltage of two capacitors and adding them together to make a higher voltage. But as technology scales, this method becomes less attractive; applying large voltages at the gate of a modern transistor is less reliable than before; and can cause permanent gate oxide breakdown [26].

$<sup>^2\,</sup>$  It was extensivly used in the design of the Intel Pentium IV processor [25] .

Figure 2.6 Basic function of a bootstrapped switch

Figure 2.5 Gated clock tree [4]

Bootstrapped circuits approach the problem from another angle and in stead provide a constant voltage at the gate, independent of the input voltage. The basic function is illustrated in Figure 2.6. This improves linearity significantly compared to CMOS gates and clock boosting, in which the gate voltage varies quite a lot.

In order to use the bootstrapped method, each individual switch needs dedicated bootstrapped circuitry. The bootstrapped method generates a voltage  $V_{in} + V_{dd}$ . During the

OFF state, the supply voltage is "sampled" onto a capacitor and the transistor gate is connected to ground. In the ON state, the capacitor is connected between the gate and source of the transistor.

#### 2.10 Transistor leakage in sub-treshold

Gate oxide thickness is reduced in each technology generation in order to mantain current drive and to counter the effect of SCE. This has lead to a significant increase in the gate leakage of modern transistors. The infinite impedance that most designer associate with the gate of a transistor is no longer a valid assumption. Oxide tunneling and injection of hot carrier from substrate to the gate oxide contribute significantly to the power consumption in modern circuits [27]. [28] presents a simplified equation for gate-oxide leakage:

$$I_{ox} = K_2 W \left(\frac{V}{t_{ox}}\right)^2 e^{-\alpha t_{ox}/V}$$

(2.8)

$K_2$  and  $\alpha$  are experimental values and  $t_{ox}$  is the oxide thickness. As can be seen from the formula, increasing oxide thickness reduces the gate leakage. This is generally not an option in short channel transistors as they will se an increase in SCE.

In order to ensure that the SCE does not become a problem, sufficient aspect ratio is required. In a MOSTFET, this ratio can be described using the following relation:

$$AR = \frac{L}{\left[t_{ox}\left(\frac{\epsilon_{si}}{\epsilon_{ox}}\right)\right]^{1/3} W_{dm}^{1/3} X_j^{1/3}}$$

(2.9)

Where  $\epsilon_{si}$  and  $\epsilon_{ox}$  are silicon and oxide permittivities. L is the channel length,  $t_{ox}$  is the oxide thickness,  $W_{dm}$  is the depletion depth, and  $X_i$  is the junction depth [27].

#### 2.11 Placement using Weinberger image

Routing considerations in a complex digital system must be considered early on in a design. It is usually a balance between high freedom in placing transistors or high density. One way; that gives a lot of freedom; is to place transistors rows in parallell and to allocate space between them for the wiring. This of course leads to very low logic density [5].

A method that results in high density, is one where the supply and ground rails are alternated and shared with cells above and below. The transistor cells are also alternated; inverterd based on their placement. The layout results in whats called a Weinberger image. Figure 2.7 illustrates the difference between the two approaches.

**Figure 2.7** Different transistor row placement techniques. High freedom placement to the left and high density placement on the right [5].

### 2.12 Successive Approximation Register