### Energy Efficient True Random Number Generator

**Conrad Georg Foik**

Master of Science in ElectronicsSubmission date:June 2015Supervisor:Per Gunnar Kjeldsberg, IETCo-supervisor:Alf Petter Syvertsen, Silicon Labs Norway AS

Norwegian University of Science and Technology Department of Electronics and Telecommunications

### **Project Description**

Student: Conrad Georg Foik

Project Title: Energy Efficient True Random Number Generator

**Project Definition:** Silicon Labs is a world leader in analog-intensive, mixed signal semiconductors, and the design offices in Oslo are the hub for developing the next generation of energy-efficient microcontrollers. The microcontrollers are based on ARM cores with best-in-class energy friendly peripherals.

In a world of connected hardware, true random numbers are needed for proper cryptography. Getting entropy from on-chip sources with some random variations, such as thermal noise in the ADC, true random numbers can be generated using software algorithms. This software implementation is however costly in terms of energy and CPU-time and too expensive for a node with limited energy budget.

During an autumn project a literature study has been performed with focus on the theoretical background for true random number generators. Based on this different hardware approaches for true random number generation have been studied and the hardware complexity of a selected set of techniques has been evaluated bearing energy efficiency in mind.

This work shall be continued towards a master thesis. The two most promising true random number generator hardware solutions shall be studied in more detail and an energy efficient design shall be implementation for at least one of them. As part of the considerations, entropy sources will be studied in more detail to enable also a trade-off between energy consumption in the source and for post-processing.

Supervisor 1: Professor Per Gunnar Kjeldsberg (NTNU)Supervisor 2: M.Sc. Alf Petter Syvertsen (Silicon Labs)

#### Abstract

For modern cryptography, the availability of true random numbers is indispensable. While recent technology trends require secure communication, they combine this requirement with the need for energy efficient solutions. As a result, true random number generators (TRNG) which satisfy both aspects have to be developed.

Based on this motivation, the here presented project has been focused on the realization of a TRNG for a mixed-signal microcontroller unit (MCU) environment. These kind of MCUs generally contain an analog-to-digital converter (ADC), which is well known to be influenced by random noise processes, as for example thermal noise. To avoid unnecessary design and prototype costs, it is therefore reasonable to try to implement the entropy source of a TRNG based on the existing ADC design. Possible non-random imperfections in the output of the source can be mask by deterministic post-processor algorithms. Two possible post-processors are the von Neumann corrector (VNC) and an extractor based on pairwise independent hash functions (IHF).

To evaluate the proposed concept, during this project the ADC of a typical MCU has been set up to function as an entropy source. The so generated data has been used as a basis for further simulations and analyses of the statistical characteristics of different TRNG designs. To ease these analyses, a novel test has been developed, which can be used to test a bit stream for the existence of special statistical characteristics, required by the VNC.

In addition, both the VNC and IHF have been analyzed with regard to their complexity and implemented in *SystemVerilog*. In order to find an energy efficient implementation of the IHF, two different algorithmic solutions have been considered and the chosen design has been kept generic to be tunable. For the VNC different approaches of clock gating have been explored to reduce unnecessary dynamic power consumption. After the verification of the proposed designs, both post-processors have been synthesized in a standard 65 nm technology, in order to estimate their power performance.

Finally, in connection with the ADC based source, both post-processor designs have been evaluated with regard to both randomness and energy performance. While the output of the approach using the VNC is classified as not random, the IHF based design passes the so called NIST test suite for random numbers, and can therefore be considered to be random. Hence the connection of the ADC based entropy source and the IHF depicts a functional TRNG solution. By tuning the IHF, it has been able to reach an approximated minimum energy consumption of 5.9 nJ for this approach.

#### Preface

The in the following presented master thesis summarizes a project performed in the spring of 2015 and marks the end of a five year master program in electronics at the Norwegian University of Science and Technology (NTNU). During the project, the energy efficient generation of true random numbers in a microcontroller has been explored. The project has been supervised by Professor Per Gunnar Kjeldsberg (NTNU) and M.Sc. Alf Petter Syvertsen from Silicon Laboratories (Silicon Labs).

As the project specification combines two extremely complex subjects, the project has had to cover a wide range of different topics, which has made the project both exciting and challenging. Examples are the mathematical and information theoretical background to understand the concept of randomness and possible post-processing approaches; statistical hypothesis testing to be able to evaluate testing results; a basic understanding of analog circuitry to consider entropy sources; digital design techniques to develop energy efficient solutions; and practical aspects as the setup of simulation and synthesis tools.

Many of this aspects are in this report presented in rather great detail. The motivation behind this is twofold. First, the presented background is considered necessary to understand the during the project developed designs and methodologies. Second, it has been my aim during the writing process to not only enable the reader to understand the here presented implementations but to ease the access to other related projects. As a result, while the theoretical background is kept as general as possible, a number of illustrating examples have been included. Being aware that this might exhaust reader familiar with the topics, it is nevertheless believed to be helpful for others.

To prepare the the performance of this project, a literature study has been performed during the fall of 2014. For convenience, it has been chosen to include some of the findings of this study in the here given report. Readers familiar with the concluding report of the literature study might therefore recognize some of the sections in this thesis. This applies mainly to Chapter 1, which has only been slightly adapted to this project. The in Section 2.1 presented concepts have also been considered during the literature study. However, the section has been revised to give a more intuitive access to the discussed topic. Section 2.3 has with minor variations been introduced during the fall of 2014. It should be noted that, while the two post-processors have been discussed during the literature study, additional aspects - including a new algorithmic solution for the extractor based on pairwise independent hash functions - have been incorporated into Section 2.4. This is also true for the corresponding complexity analysis in Section 4.1.1 and Section 4.1.2. The rest of the report is novel.

Generally, great care has been taken to reference external sources, in order to clearly distinguish the from my own work. However, two cases should be considered in more detail.

The in Section 2.4.2 presented Equation 2.43 and Equation 2.44 are in this form *not* stated in the original article, "True Random Number Generators Secure in a Changing Environment" by Barak, Shaltiel and Tromer. However, due to discrep-

ancies between the notation of the in the article presented corresponding equations and additional inconsistencies between these equations and their related mathematical explanations it is suspected that minor printing errors exists in the equations of the article. As an attempt to contact the authors has been unsuccessful and proving the validity of either one of the equations is out of the scope of this project, this suspicion has had to be accepted, out of a lack of alternatives. Both equation have therefore been modified by me, based on my understanding of the mathematical background presented in the article. Nevertheless, the reader is encouraged to evaluate this decision for him- or herself.

Further, I want to stress at this point, that the basic idea of the in Section 3.2 introduced test, has been proposed by Professor Øyvind Bakke (NTNU).

Finally, on a more personal note, I would like to thank my supervisors Professor Per Gunnar Kjeldsberg (NTNU) and M.Sc. Alf Petter Syvertsen (Silicon Labs) for consistent support and motivation throughout both this project and the preceding literature study; Professor Ingelin Steinsland, Professor Håkon Tjelmeland and the already mentioned Professor Øyvind Bakke (all NTNU) for increasing my understanding of statistical hypothesis testing; and finally, but in no way less important, my friends and family for utterly support, motivation, exhortation and distractions, not only throughout this project but the entire past five years.

Trondheim, June 12, 2015

Conrad G. Foik

## Contents

| Pr            | oject | t Description                                                         | i            |

|---------------|-------|-----------------------------------------------------------------------|--------------|

| Al            | ostra | $\mathbf{ct}$                                                         | iii          |

| Pr            | eface |                                                                       | $\mathbf{v}$ |

| $\mathbf{Li}$ | st of | Figures                                                               | xii          |

| $\mathbf{Li}$ | st of | Tables                                                                | xiv          |

| Li            | st of | Mathematical Symbols                                                  | xv           |

| Li            | st of | Acronyms                                                              | xix          |

| 1             | Intr  | oduction                                                              | 1            |

|               | 1.1   | Random data                                                           | 2            |

|               | 1.2   | Pseudorandom and true random number generators                        | 2            |

|               | 1.3   | This project                                                          | 3            |

|               | 1.4   | Outline                                                               | 5            |

| <b>2</b>      | Bac   | kground                                                               | 7            |

|               | 2.1   | Random Data                                                           | 7            |

|               | 2.2   | Statistical Testing                                                   | 13           |

|               |       | 2.2.1 Testing of a statistical hypothesis                             | 14           |

|               |       | 2.2.2 The NIST test suite for random number generators                | 24           |

|               | 2.3   | Random Noise in an ADC                                                | 29           |

|               | 2.4   | Post-processing algorithms                                            | 34           |

|               |       | 2.4.1 Von Neumann corrector                                           | 36           |

|               |       | 2.4.2 Extractor based on pairwise-independent hash functions $\ldots$ | 38           |

|               | 2.5   | Dynamic Power in Digital Systems                                      | 46           |

| 3             |       | C as an Entropy Source                                                | 51           |

|               | 3.1   | Implementation of an Entropy Source Using an ADC                      | 51           |

|               | 3.2   | A Test for von Neumann Conditions                                     | 53           |

|               | 3.3   | Output Analysis of the Entropy Source                                 | 59           |

| 4            | Pos                                      | t-Processing Algorithms                                            | 65                                                                                                                  |

|--------------|------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|              | 4.1                                      | Complexity of the TRNG Post-Processing Algorithms                  | 65                                                                                                                  |

|              |                                          | 4.1.1 Complexity analysis of TRNG post-processing algorithms       | 66                                                                                                                  |

|              |                                          | 4.1.2 Discussion on the growth of complexity                       | 71                                                                                                                  |

|              |                                          | 4.1.3 Choice of an IHF algorithm suited for implementation         | 78                                                                                                                  |

|              | 4.2                                      | Implementation of Post-Processing Algorithms                       | 80                                                                                                                  |

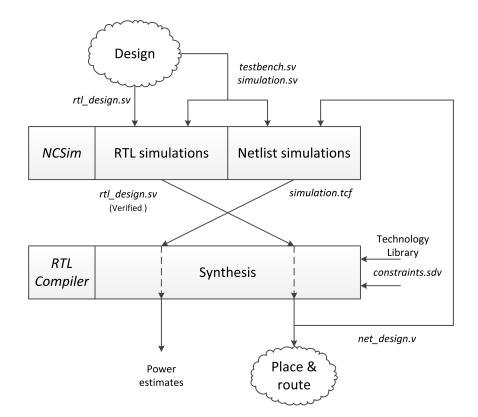

|              |                                          | 4.2.1 General aspects of the design and simulation process         | 82                                                                                                                  |

|              |                                          | 4.2.2 Implementation of the von Neumann corrector                  | 87                                                                                                                  |

|              |                                          | 4.2.3 Implementation of an extractor based on pairwise independent |                                                                                                                     |

|              |                                          | hash functions                                                     | 95                                                                                                                  |

| F            | Erro                                     | luction of Dandomnage                                              | 105                                                                                                                 |

| 5            |                                          | Analysis of the VNC Output                                         | 105                                                                                                                 |

|              | $5.1 \\ 5.2$                             | Analysis of the VNC Output                                         |                                                                                                                     |

|              | 0.2                                      |                                                                    | 110                                                                                                                 |

| 6            | $\mathbf{Esti}$                          | imation of Power and Energy Performance                            | 123                                                                                                                 |

|              | 6.1                                      | Power and Energy Performance of the VNC                            | 124                                                                                                                 |

|              | 6.2                                      | Power and Energy Performance of the IHF                            |                                                                                                                     |

|              |                                          |                                                                    |                                                                                                                     |

| <b>7</b>     | Dise                                     | cussion, Conclusion and Further Work                               | 135                                                                                                                 |

|              | 7.1                                      | Comparison of the VNC and the IHF                                  | 135                                                                                                                 |

|              | 7.2                                      | Conclusion and Further Work                                        | 137                                                                                                                 |

| 8            | Dof                                      | erences                                                            | 141                                                                                                                 |

| 0            | ner                                      | erences                                                            | 141                                                                                                                 |

| $\mathbf{A}$ | $\mathbf{Ext}$                           | ended Background on Information Theory                             | 145                                                                                                                 |

|              |                                          | Entropy and the Uniform Distribution                               | 145                                                                                                                 |

|              |                                          | - •                                                                |                                                                                                                     |

|              | A.2                                      | Entropy and Statistical Dependencies                               | 146                                                                                                                 |

|              | A.2                                      | Entropy and Statistical Dependencies                               |                                                                                                                     |

|              | A.2                                      |                                                                    | 146                                                                                                                 |

| D            |                                          | A.2.1Conditional entropy of a 2-bit vector                         | 146<br>149                                                                                                          |

| В            |                                          | A.2.1 Conditional entropy of a 2-bit vector                        | 146                                                                                                                 |

|              | Set                                      | <ul><li>A.2.1 Conditional entropy of a 2-bit vector</li></ul>      | 146<br>149<br><b>151</b>                                                                                            |

| B<br>C       | Set:<br>Stat                             | <ul> <li>A.2.1 Conditional entropy of a 2-bit vector</li></ul>     | 146<br>149<br>151<br>159                                                                                            |

|              | Setu<br>Stat<br>C.1                      | <ul> <li>A.2.1 Conditional entropy of a 2-bit vector</li></ul>     | 146<br>149<br><b>151</b><br><b>159</b><br>159                                                                       |

|              | Setu<br>Stat<br>C.1                      | <ul> <li>A.2.1 Conditional entropy of a 2-bit vector</li></ul>     | 146<br>149<br><b>151</b><br>159<br>159<br>163                                                                       |

|              | Setu<br>Stat<br>C.1                      | <ul> <li>A.2.1 Conditional entropy of a 2-bit vector</li></ul>     | 146<br>149<br><b>151</b><br><b>159</b><br>159<br>163<br>163                                                         |

|              | Setu<br>Stat<br>C.1                      | <ul> <li>A.2.1 Conditional entropy of a 2-bit vector</li></ul>     | 146<br>149<br>151<br>159<br>159<br>163<br>163<br>163                                                                |

|              | Setu<br>Stat<br>C.1                      | <ul> <li>A.2.1 Conditional entropy of a 2-bit vector</li></ul>     | 146<br>149<br>151<br>159<br>159<br>163<br>163<br>163                                                                |

| С            | Setu<br>Stat<br>C.1<br>C.2               | A.2.1 Conditional entropy of a 2-bit vector                        | 146<br>149<br>151<br>159<br>159<br>163<br>163<br>165<br>170<br>175                                                  |

| С            | Setu<br>Stat<br>C.1<br>C.2               | A.2.1 Conditional entropy of a 2-bit vector                        | 146<br>149<br>151<br>159<br>159<br>163<br>163<br>165<br>170<br>175<br>175                                           |

| С            | Setu<br>Stat<br>C.1<br>C.2               | A.2.1 Conditional entropy of a 2-bit vector                        | 146<br>149<br>151<br>159<br>159<br>163<br>163<br>165<br>170<br><b>175</b><br>175<br>178                             |

| С            | Setu<br>Stat<br>C.1<br>C.2<br>Sys<br>D.1 | A.2.1 Conditional entropy of a 2-bit vector                        | 146<br>149<br>151<br>159<br>163<br>163<br>163<br>165<br>170<br>175<br>178<br>178                                    |

| С            | Setu<br>Stat<br>C.1<br>C.2<br>Sys<br>D.1 | A.2.1 Conditional entropy of a 2-bit vector                        | 146<br>149<br>151<br>159<br>159<br>163<br>163<br>163<br>165<br>170<br>175<br>178<br>178<br>178                      |

| С            | Setu<br>Stat<br>C.1<br>C.2<br>Sys<br>D.1 | A.2.1 Conditional entropy of a 2-bit vector                        | 146<br>149<br>151<br>159<br>159<br>163<br>163<br>163<br>163<br>165<br>170<br>175<br>178<br>178<br>178<br>178<br>178 |

| С            | Setu<br>Stat<br>C.1<br>C.2<br>Sys<br>D.1 | A.2.1 Conditional entropy of a 2-bit vector                        | 146<br>149<br>151<br>159<br>159<br>163<br>163<br>163<br>165<br>170<br>175<br>178<br>178<br>178<br>178<br>178<br>178 |

|   | D.3               | IHF Ir                                                       | nplementation                                                     | . 193                                                            |

|---|-------------------|--------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------|

|   |                   | D.3.1                                                        | Definitions for the IHF                                           | . 193                                                            |

|   |                   | D.3.2                                                        | ihf.sv                                                            | . 193                                                            |

|   |                   | D.3.3                                                        | $ihf_ctrl.sv$                                                     | . 195                                                            |

|   |                   | D.3.4                                                        | $ihf_input_if.sv$                                                 | . 199                                                            |

|   |                   | D.3.5                                                        | $ihf_{-comp.sv}$                                                  | . 200                                                            |

|   |                   | D.3.6                                                        | $ihf_output\_memory.sv$                                           | . 202                                                            |

|   | D.4               | Simula                                                       | tion Setup                                                        | . 203                                                            |

|   |                   | D.4.1                                                        | Definitions                                                       | . 203                                                            |

|   |                   | D.4.2                                                        | Example of a test bench                                           | . 204                                                            |

|   |                   | D.4.3                                                        | Example of a simulation routine                                   | . 209                                                            |

|   |                   | D.1.0                                                        |                                                                   |                                                                  |

| E | Use               |                                                              | -                                                                 |                                                                  |

| E |                   | r Guid                                                       | le for Logical Verification and Synthesis for Power Esti          | <b>-</b>                                                         |

| E | Use<br>mat<br>E.1 | r Guid<br>ions                                               | le for Logical Verification and Synthesis for Power Esti          | -<br>213                                                         |

| E | mat               | r Guid<br>ions<br>Work                                       | le for Logical Verification and Synthesis for Power Esti          | -<br>213<br>. 213                                                |

| E | mat<br>E.1        | r Guid<br>ions<br>Work                                       | le for Logical Verification and Synthesis for Power Esti<br>flow  | <b>213</b><br>213<br>213<br>215                                  |

| E | mat<br>E.1        | r Guid<br>ions<br>Work<br>Setup                              | le for Logical Verification and Synthesis for Power Estiflow      | <b>213</b><br>213<br>213<br>215<br>215                           |

| E | mat<br>E.1        | r Guid<br>ions<br>Work :<br>Setup<br>E.2.1                   | le for Logical Verification and Synthesis for Power Esti<br>flow  | <b>213</b><br>213<br>215<br>215<br>215<br>216                    |

| E | mat<br>E.1        | r Guid<br>ions<br>Work :<br>Setup<br>E.2.1<br>E.2.2<br>E.2.3 | le for Logical Verification and Synthesis for Power Esti-<br>flow | <b>213</b><br>. 213<br>. 215<br>. 215<br>. 215<br>. 216<br>. 217 |

# List of Figures

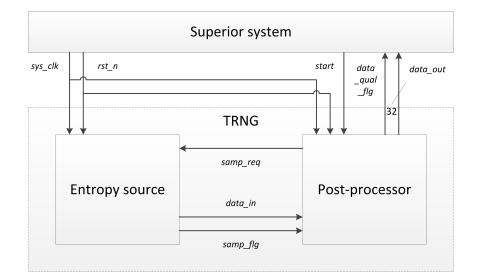

| 1.1                 | Block schematic of a TRNG                                                                                                                        | 3              |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

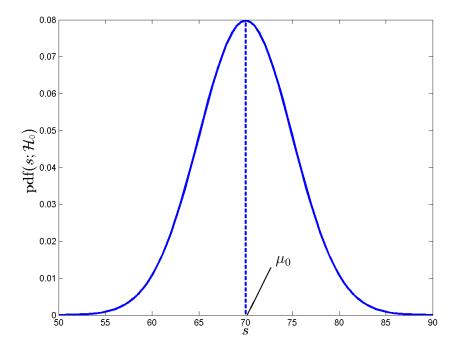

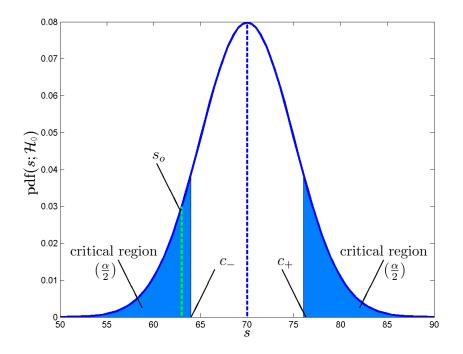

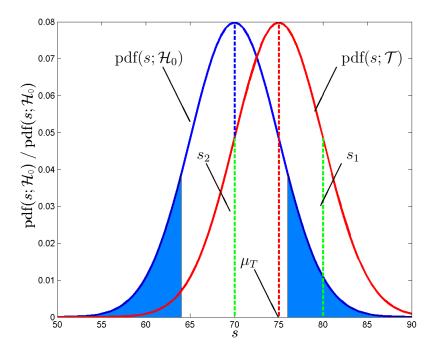

| $2.1 \\ 2.2 \\ 2.3$ | Example of a reference distribution for $\mathcal{H}_0$                                                                                          | 15<br>16<br>17 |

|                     | Relationship of the reference distribution and the true distribution of $s$                                                                      |                |

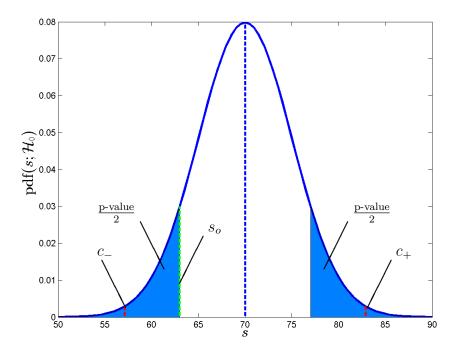

| 2.4                 | P-value for the observed test statistic $s_o$                                                                                                    | 20<br>22       |

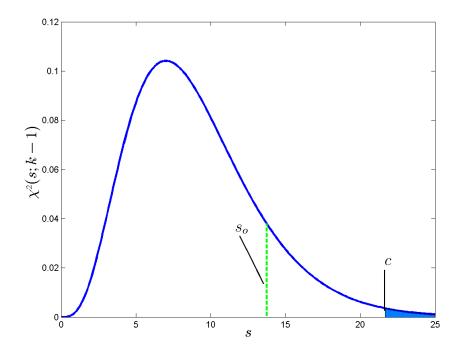

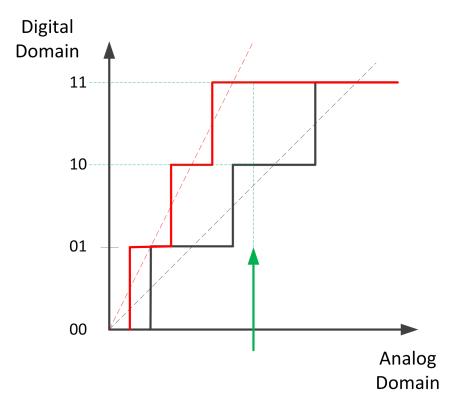

| $2.5 \\ 2.6$        | The chi-squared distribution with nine degrees of freedom                                                                                        | 22<br>32       |

| 2.0<br>2.7          | Example of a quantization imperfection                                                                                                           | 33             |

| 2.1                 | ADC transformation with thermal noise                                                                                                            | 33<br>34       |

| 2.8<br>2.9          | D-flip-flop with enable signal                                                                                                                   | 48             |

| 2.0<br>2.10         | A simple clock gate                                                                                                                              | 49             |

| 2.10                |                                                                                                                                                  | 40             |

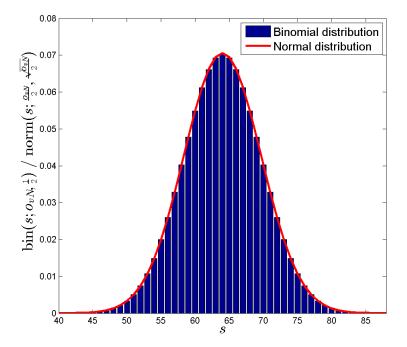

| 3.1                 | Approximation of the binomial distribution by the normal distribu-<br>tion for $o_{\rm vN} = 128$                                                | 58             |

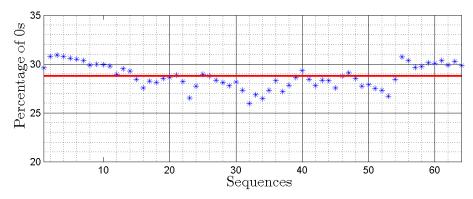

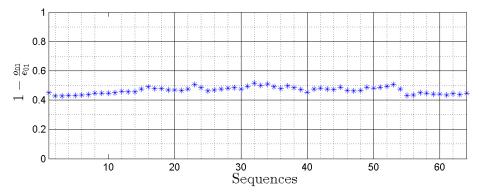

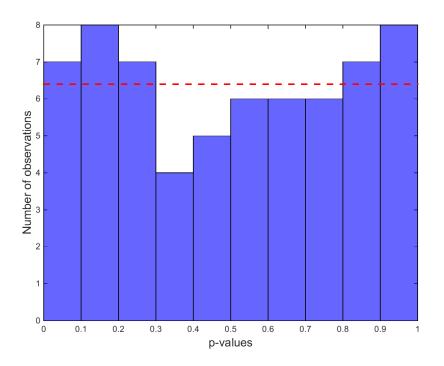

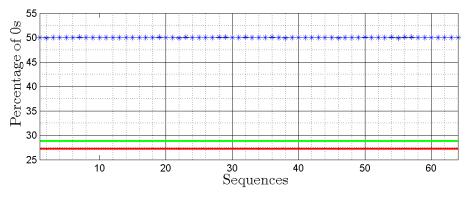

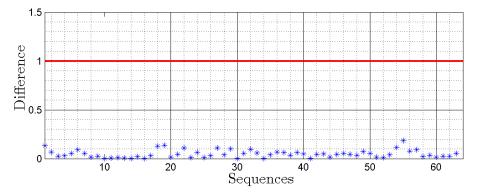

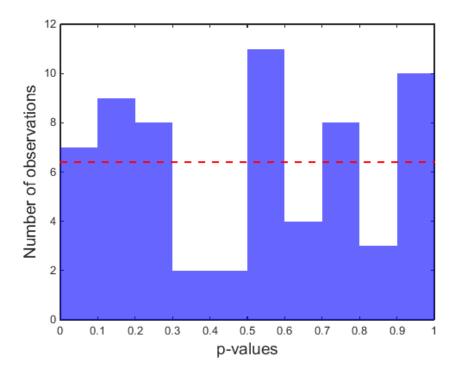

| 3.2                 | Results of the Frequency test for the source data                                                                                                | 62             |

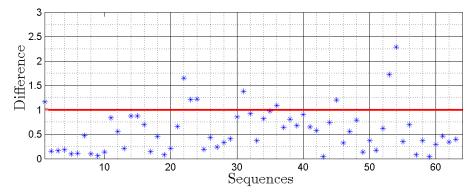

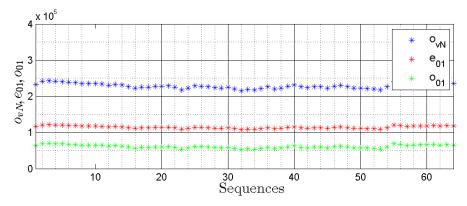

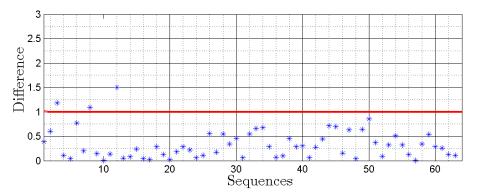

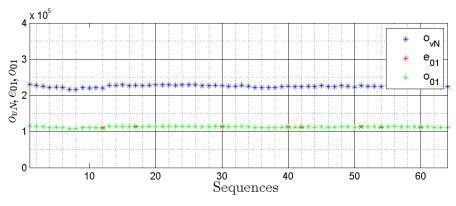

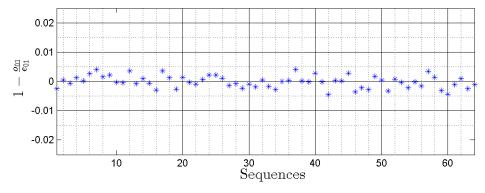

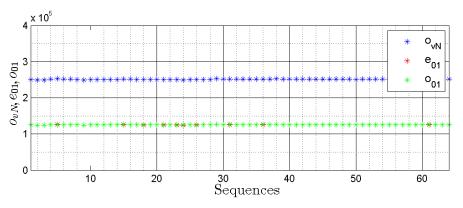

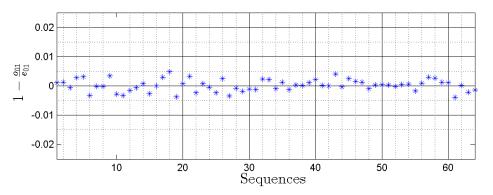

| 3.3                 | Results of the von Neumann condition test for the source data                                                                                    | 64             |

|                     |                                                                                                                                                  |                |

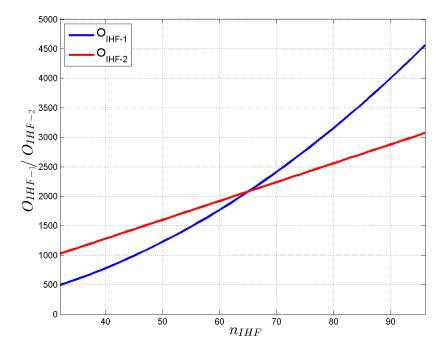

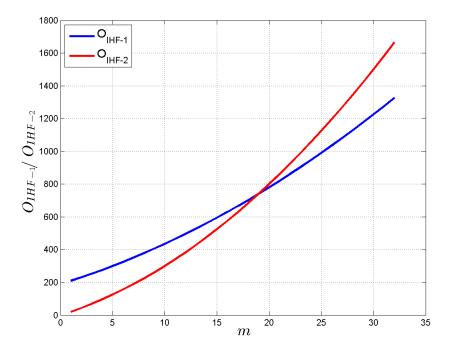

| $4.1 \\ 4.2$        | Number of operations of the IHF-algorithms as functions of $n_{\text{IHF}}$<br>Lower bounds of the number of operations of the IHF-algorithms as | 72             |

|                     | functions $m$                                                                                                                                    | 73             |

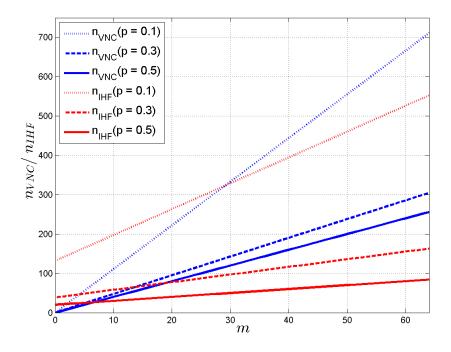

| 4.3                 | Number of input bits required by the VNC and the IHF as functions                                                                                |                |

|                     | of $m$                                                                                                                                           | 74             |

| 4.4                 | Slopes of $n_{\text{VNC}}$ and $n_{\text{IHF}}$ as functions of $p \dots \dots \dots \dots \dots \dots \dots \dots$                              | 74             |

| 4.5                 | Number of operations of the VNC and the IHF-algorithms as func-                                                                                  |                |

|                     | tions of $m$                                                                                                                                     | 76             |

| 4.6                 | Indication of the number of operations for the VNC and the IHF-                                                                                  |                |

|                     | algorithms as functions of $p$                                                                                                                   | 77             |

| 4.7                 | Work flow of the post-processor implementation process                                                                                           | 81             |

| 4.8                 | System environment for post-processor implementations                                                                                            | 83             |

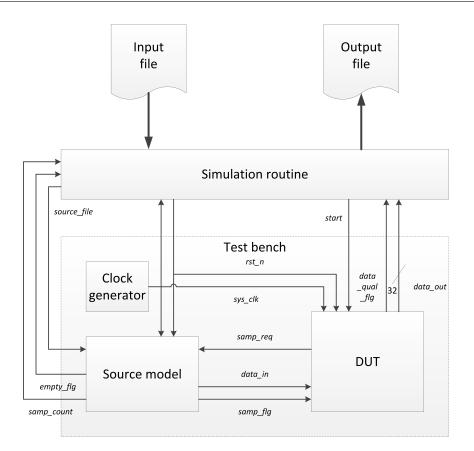

| 4.9                 | Simulation setup for post-processing implementations                                                                                             | 85             |

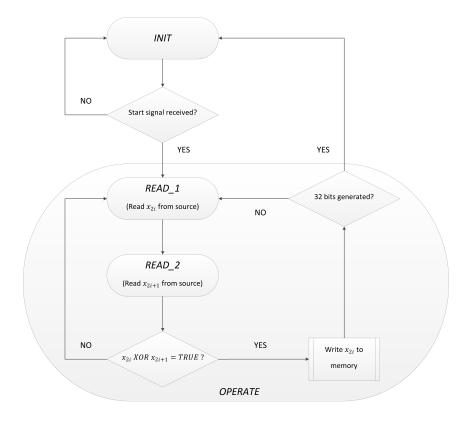

|                     | Flow diagram of a VNC module                                                                                                                     | 88             |

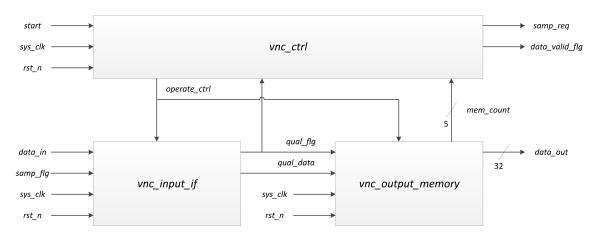

|                     | Block schematic of a VNC module                                                                                                                  | 89             |

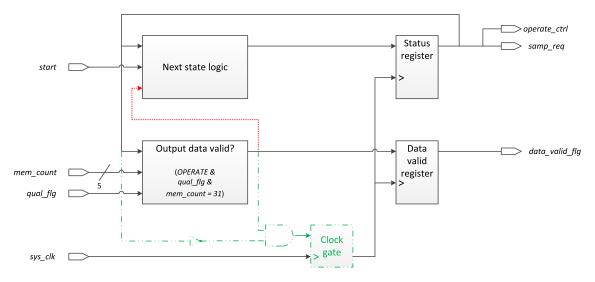

|                     | Block schematic of $vnc_ctrl$                                                                                                                    | 91             |

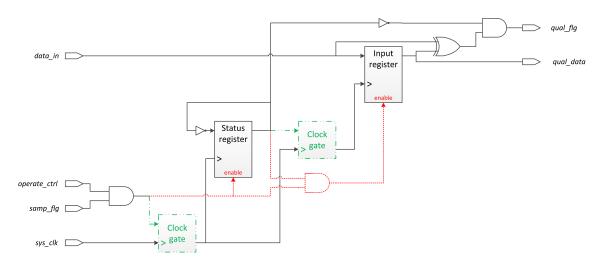

|                     | Block schematic of <i>vnc_input_if</i>                                                                                                           | 92             |

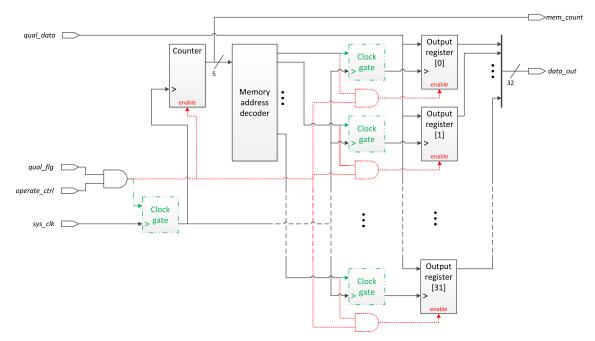

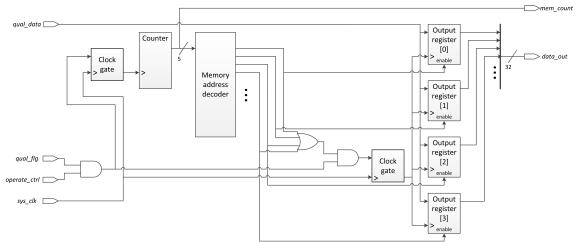

|                     | Block schematics of <i>vnc_output_memory</i>                                                                                                     | 93             |

|                     | Waveform of the first VNC verification simulation                                                                                                | 94             |

| 4.16                | Waveform of the second VNC verification simulation                                                                                               | 96             |

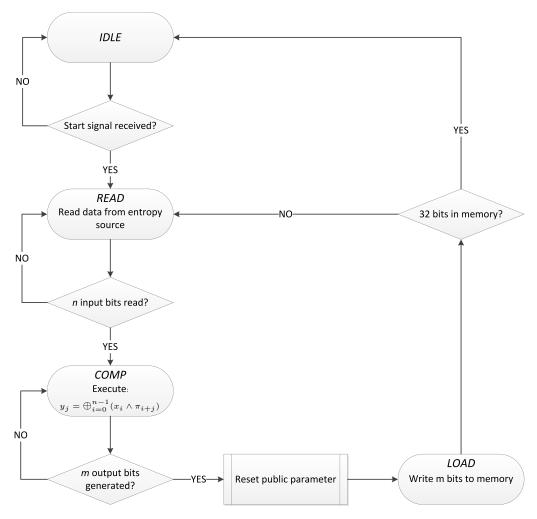

| 4.17 | Flow diagram of a IHF module                                               |

|------|----------------------------------------------------------------------------|

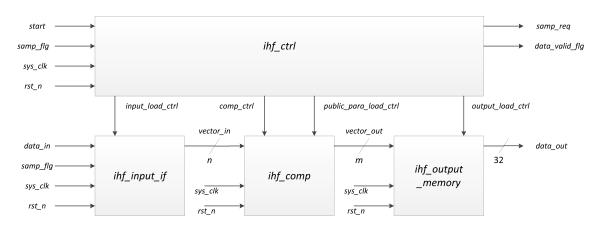

| 4.18 | Block schematic of a IHF module                                            |

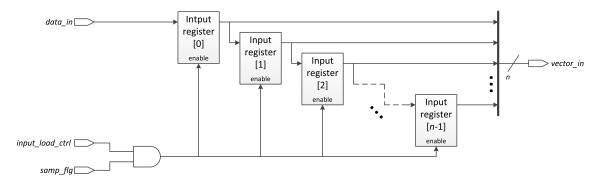

| 4.19 | Block schematic of <i>ihf_input_if</i>                                     |

| 4.20 | Block schematic of <i>ihf_comp</i>                                         |

| 4.21 | Block schematic of <i>ihf_output_memory</i>                                |

| 4.22 | Waveform of the first IHF verification simulation                          |

| 4.23 | Waveform of all four generated output words                                |

| 5.1  | Results of the Frequency test for the VNC                                  |

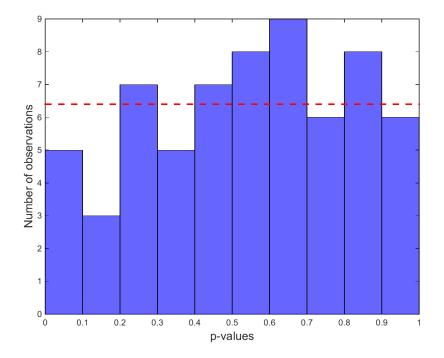

| 5.2  | Results of the von Neumann condition test for the VNC 108                  |

| 5.3  | Observed p-values of the first-level von Neumann condition tests for       |

|      | the VNC                                                                    |

| 5.4  | Illustration of the second VNC iteration approach                          |

| 5.5  | Results of the Frequency test for the second VNC iteration 111             |

| 5.6  | Observed p-values of the first-level Frequency tests for the second        |

|      | VNC iteration                                                              |

| 5.7  | Observed p-values of the first-level von Neumann condition tests for       |

|      | the second VNC iteration                                                   |

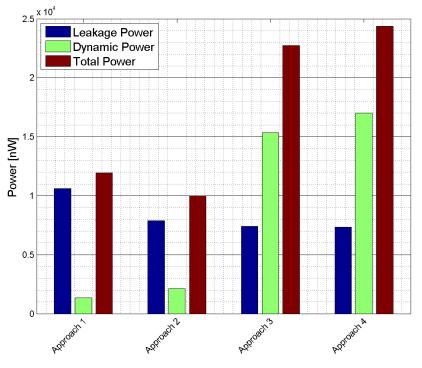

| 6.1  | Power estimates for the VNC                                                |

| 6.2  | Power estimates for <i>vnc_output_memory</i>                               |

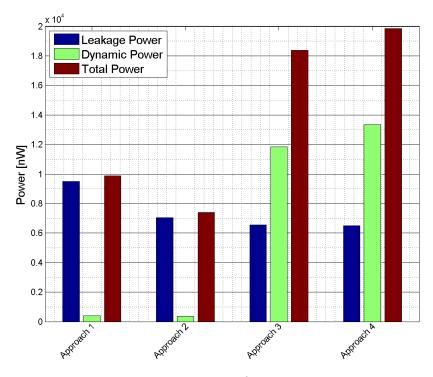

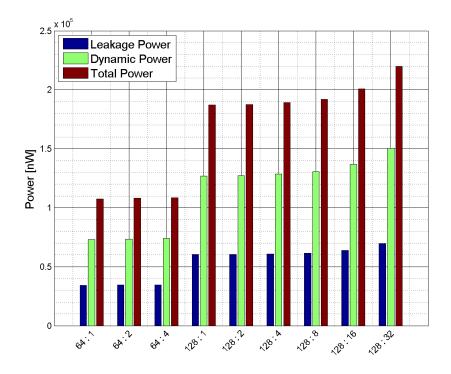

| 6.3  | Power estimates for the IHF                                                |

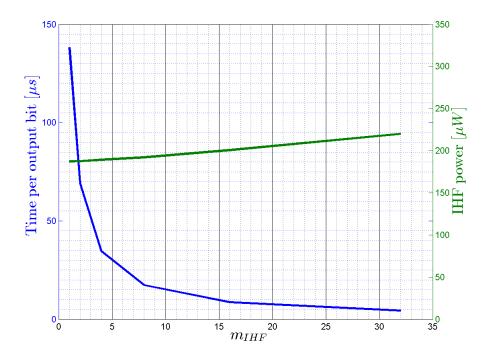

| 6.4  | Power and time per sample for the IHF                                      |

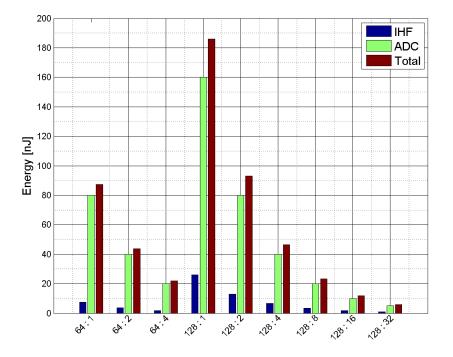

| 6.5  | Energy estimates for an IHF based TRNG solution                            |

| C.1  | Results of the von Neumann condition test for the second VNC iteration 169 |

| E.1  | Work flow of the verification and synthesis process                        |

# List of Tables

| $2.1 \\ 2.2$                                                                | Possible scenarios arising from hypotheses testing                                                                                                                                                        |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.3                                                                         | goodness-of-fit test24The NIST test suite27                                                                                                                                                               |

| $2.4 \\ 2.5 \\ 2.6$                                                         | Extended truth table of the XOR-operation in a VNC $37$ Output probabilities of the mainpluated ensemble $X$ $40$ Example for Equation 2.44 $46$                                                          |

| $3.1 \\ 3.2 \\ 3.3$                                                         | Summary of the used ADC parameters53Contingency table54Used parameters for the NIST test suite61                                                                                                          |

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \end{array}$                     | Number of inner loop iterations for IHF-169List of input and output for the post-processing modules84Summary of simulations for logical verification87Overview over the different VNC design approaches90 |

| <ol> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ol> | Results of the NIST test suite for the output of the second VNC-<br>iteration                                                                                                                             |

| 5.6                                                                         | Summary of the results of the NIST test suite for the IHF with $m_{\rm IHF} =$<br>128                                                                                                                     |

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$                                   | Energy estimates for the VNC                                                                                                                                                                              |

| C.1<br>C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.7<br>C.8                        | Results of the Frequency test for the source data $\dots \dots \dots$                                     |

| C.9  | Results of the NIST test suite for the IHF with $n_{\rm IHF} = 64$ and $m_{\rm IHF} = 4171$                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------|

| C.10 | Results of the NIST test suite for the IHF with $n_{\text{IHF}} = 64$ and $m_{\text{IHF}} = 8172$                                |

| C.11 | Results of the NIST test suite for the IHF with $n_{\rm IHF} = 128$ and                                                          |

|      | $m_{\text{IHF}} = 2 \dots \dots$ |

| C.12 | Results of the NIST test suite for the IHF with $n_{\rm IHF} = 128$ and                                                          |

|      | $m_{\rm IHF} = 4 \dots \dots$    |

| C.13 | Results of the NIST test suite for the IHF with $n_{\rm IHF} = 128$ and                                                          |

|      | $m_{\rm IHF} = 8 \dots \dots$    |

| C.14 | Results of the NIST test suite for the IHF with $n_{\rm IHF} = 128$ and                                                          |

|      | $m_{\rm IHF} = 16$                                                                                                               |

| C.15 | Results of the NIST test suite for the IHF with $n_{\rm IHF} = 128$ and                                                          |

|      | $m_{\rm IHF} = 32$                                                                                                               |

| F.1  | Synthesis results for the VNC modules                                                                                            |

| F.2  | Synthesis results for the <i>vnc_output_memory</i> sub-modules                                                                   |

| F.3  | Synthesis results for the IHF modules with $n_{\rm IHF} = 64$                                                                    |

| F.4  | Synthesis results for the IHF modules with $n_{\rm IHF} = 128$                                                                   |

# List of Mathematical Symbols

| Symbol                     | Explanation                                                        | First reference           |

|----------------------------|--------------------------------------------------------------------|---------------------------|

| $a_i$                      | An arbitrary element of $\mathcal{A}_X$ .                          | Section 2.1               |

| $\mathcal{A}_X$            | $\mathcal{A}_X = \{a_0,, a_{k-1}\}, \text{ the set of } X.$ It     | Section 2.1               |

|                            | contains $k$ different discrete data values,                       |                           |

|                            | which all are possible to be taken by $x$ . In                     |                           |

|                            | the binary case, $\mathcal{A}_X = \{0, 1\}^n$ denotes the          |                           |

|                            | set containing all $2^n$ possible combinations                     |                           |

|                            | of <i>n</i> bits.                                                  | -                         |

| $\alpha$                   | The level of significance for a statistical test                   | Equation 2.19             |

| $\beta$                    | The tuning parameter of the IHF                                    | Equation 4.5              |

| $c_{-/+}$                  | The critical value(s) for a statistical test $(a, b)$              | Equation 2.19             |

| $\gamma$                   | The <i>switching activity</i> of a digital gate                    | Equation 2.47             |

| $\operatorname{dist}(X,Y)$ | The <i>statistical distance</i> between the                        | Equation 2.6              |

|                            | ensembles $X$ and $Y$                                              | $\mathbf{C}_{\mathbf{r}}$ |

| e                          | The expected frequency of occurrence for a                         | Section 2.2.1             |

|                            | given value. In Section 2.3, $e[n]$ is                             |                           |

|                            | incoherently used to illustrate the influence<br>of thermal noise. |                           |

| $\mathrm{E}[x]$            | The expected value for the outcome $x$                             | Section 2.2.1             |

| $\epsilon$                 | A measure of the statistical distance of two                       | Section 2.1,              |

| C                          | ensembles. In this report also often referred                      | Section 2.4.2             |

|                            | to as the <i>quality parameter</i> of the IHF                      | 50001011 2.1.2            |

| g(z)                       | A polynomial in $GF(2^n)$                                          | Equation 2.35             |

| G(z)                       | A <i>irreducible</i> polynomial that defines                       | Section 2.4.2             |

|                            | $GF(2^n)$                                                          |                           |

| $GF((2^n))$                | A Galois field with $2^n$ elements                                 | Section 2.4.2             |

| H                          | A pairwise independent family of hash                              | Section 2.4.2             |

|                            | functions                                                          |                           |

| $h(x = a_i)$               | The Shannon information content                                    | Equation 2.1              |

|                            | associated with the event of $x$ taking on the                     |                           |

|                            | value $a_i$                                                        |                           |

| H(X)                       | The Shannon entropy associated with the                            | Equation 2.2              |

|                            | ensemble $X$                                                       |                           |

| $\mathcal{H}_0$            | The <i>null-hypothesis</i> of a statistical test                   | Section 2.2.1             |

| k                          | Number of elements in $\mathcal{A}_X$                              | Section 2.1               |

|                            |                                                                    |                           |

| Symbol                              | Explanation                                                                                                                                                                                          | First reference |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| $\kappa$                            | The associated amount of min-entropy in bits                                                                                                                                                         | Equation 2.3    |

| l                                   | The level of independence between multiple variables                                                                                                                                                 | Equation 2.14   |

| m                                   | The number of elements in $\overrightarrow{y}$ . Also more loosely used as the number of output bits of a test or an algorithm                                                                       | Section 2.1     |

| $\min$ -Ent $(X)$                   | The <i>min-entropy</i> associated with the ensemble $X$                                                                                                                                              | Equation 2.3    |

| Ν                                   | The number of performed <i>first-level</i> tests                                                                                                                                                     | Section 2.2.2   |

| n                                   | The number of elements in $\overrightarrow{x}$ . Also more loosely used as the number of input bits to a test or an algorithm                                                                        | Section 2.1     |

| $\operatorname{norm}(s;\mu,\sigma)$ | The normal distribution of s with mean $\mu$<br>and standard deviation $\sigma$                                                                                                                      | Section 2.2.2   |

| 0                                   | The observed frequency of occurrence for a given value                                                                                                                                               | Section 2.2.1   |

| 0                                   | An abstract measure of the number of<br>operations required by an algorithm                                                                                                                          | Section 4.1     |

| $\mathcal{P}(i)$                    | $p_i$ is the probability that $x$ takes on the value $a_i$ , $p_i = \Pr(x = a_i)$ . If $\mathcal{A}_X = \{0, 1\}$ , $p$ is used to denote the probability that $x$ is equal to 0, $p = \Pr(x = 0)$ . | Section 2.1     |

| Р                                   | The <i>power dissipation</i> of a digital gate                                                                                                                                                       | Equation 2.45   |

| $\mathcal{P}_X$                     | $\mathcal{P}_X = \{p_0,, p_{k-1}\}, \text{ a set that defines the probabilities of } x \text{ taking a particular value of } \mathcal{A}_X$                                                          | Section 2.1     |

| $\mathrm{pdf}(s;\mathcal{H}_0)$     | The pdf of the <i>reference distribution</i> of s for<br>a given $\mathcal{H}_0$                                                                                                                     | Section 2.2.1   |

| π                                   | The <i>public parameter</i> of the IHF                                                                                                                                                               | Section 2.4.2   |

| Π                                   | A set from which $\pi$ is randomly selected                                                                                                                                                          | Section 2.4.2   |

| 5                                   | The test statistic of a statistical test. $s$ is a<br>unknown variable. The observed test<br>statistic is denoted $s_o$                                                                              | Equation 2.18   |

| t                                   | The security parameter of the IHF                                                                                                                                                                    | Equation 2.34   |

| x                                   | The <i>outcome</i> of X. A discrete variable taking a value out of $\mathcal{A}_X$ with a probability defined in $\mathcal{P}_X$                                                                     | Section 2.1     |

| X                                   | The ensemble X contains the triple $(x, \mathcal{A}_X, \mathcal{P}_X)$ . In this report, X is usually used to model a source of discrete data.                                                       | Section 2.1     |

| Symbol               | Explanation                                                                                                                                                                                                                                                                                                                | First reference             |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| $\overrightarrow{x}$ | $\overrightarrow{x} = \langle x_0,, x_{n-1} \rangle$ , the concatenation of $n$<br>data values. Frequently used vectors are: $\overrightarrow{x}$<br>used to model the output stream of a data<br>source / input to a post-processor or<br>statistical test; $\overrightarrow{y} = \langle y_0,, y_{m-1} \rangle$ denoting | Section 2.1,<br>Section 2.4 |

| $\chi^2(s;k-1)$      | the output of a post-processor.<br>The <i>chi-squared</i> distribution of $s$ with $k-1$ degrees of freedom                                                                                                                                                                                                                | Section 2.2.1               |

# List of Acronyms

| Acronym              | Description                                            |

|----------------------|--------------------------------------------------------|

| ADC                  | Analog-to-Digital Converter                            |

| AES                  | Advanced Encryption Standard                           |

| CMOS                 | Complementary Metal-Oxide Semiconductor                |

| DUT                  | Device under Test                                      |

| FPGA                 | Field-Programmable Gate Array                          |

| $\operatorname{IHF}$ | Extractor based on pairwise Independent Hash Functions |

| IoT                  | Internet of Things                                     |

| LSB                  | Least Significant Bit                                  |

| MCU                  | Microcontroller Unit                                   |

| NIST                 | The National Institute of Standards and Technology     |

| NTNU                 | Norwegian University of Science and Technology         |

| $\operatorname{pdf}$ | Probability Density Function                           |

| PRNG                 | Pseudorandom Number Generator                          |

| RNG                  | Random Number Generator                                |

| RSA                  | Rivest-Shamir-Adleman Public Key Cryptosystem          |

| RTL                  | Register-Transfer Level                                |

| SAR                  | Successive Approximation Register                      |

| TRNG                 | True Random Number Generator                           |

| VNC                  | von Neumann Corrector                                  |

### Chapter 1

### Introduction

Random numbers are a fundamental part of modern cryptography. They are mainly used to determine keys in cryptographic algorithms, as the *Rivest-Shamir-Adleman* Public Key Cryptosystem (RSA), the Diffie-Hellman algorithm or the Advanced Encryption Standard (AES) [1][2]. However, they find also use in the generation of, for example, padding bits, which are used to extend short messages to a fixed number of bits without weakening the used cipher [3]. Due to the importance of random numbers for the security of cryptographic systems, Random Number Generators have to satisfy a number of strict demands. Most importantly, they have to deliver random data that is suitable to be used in cryptographic applications. For instance, if the generated data is not truly random, but rather biased or in other form predictable, an adversary might easily guess the key of a cipher from a reduced number of possibilities. It is also possible that an adversary tries to actively attack the RNG in order to determine or even manipulate the generated data. Hence, RNGs should provide an ability to resist these kinds of attacks. A further requirement that has to be taken into consideration is the speed at which random data can be produced, as some applications are time-critical.

The above mentioned requirements have been known for a long time. However, a rather new demand is introduced by current technology trends: During the last decades more and more devices have been connected to the internet. Whereas, in the past, this mostly affected stationary computer systems and later on also applied to mobile devices (e.g. smartphones, laptops), today an increasing number of gadgets is connected to the internet. This trend is generally referred to as the *Internet of* Things (IoT) [4]. The resulting advanced connectivity is accompanied by the same need for security as more traditional systems. One might, for instance, picture a personal medical device, which measures and transmits sensitive data to an external computer system. This data obviously should be shielded from any possible third party. Another example are home security systems. They need to secure that an adversary neither observes the communication nor actively manipulates the system. While the need for security, and thus reliable RNGs, in these systems is the same as for desktop computers, they generally have stricter requirements with regard to power consumption. Most IoT-devices are wireless embedded systems with limited sources of energy as, for example, batteries. Thus, when designing RNGs that are to be used in IoT related gadgets or other kinds of embedded systems, energy

efficiency has become a more and more important factor that has to be taken into consideration.

An illustrative example of typical components used in IoT gadgets is the *EFM32* Gecko family, which is a series of Microcontroller Units developed by Silicon Laboratories [5]. On one hand, these MCUs are designed for ultra low energy consumption and thus easily integrated in battery driven systems. On the other hand, the EFM32 Geckos support hardware execution of the widely used AES-algorithm, meeting the increasing costumer requirements for security.

An example of an on jitter based RNG that meets the energy requirements of IoT applications is presented in [3]. The proposed design has a throughput of 1.74 Mbits/s and a power consumption of roughly  $240 \,\mu\text{W}$ , using a  $90 \,\text{nm}$  Complementary Metal-Oxide Semiconductor (CMOS) technology. As a result, the RNG requires approximately 138 pJ per single output bit. However, modern cryptography standards require normally a large number of random bits. For example the AES uses a key length of at least 128 bits [6]. Thus, creating for instance an AES key would require a total of roughly 18 nJ.

#### 1.1 Random data

The concept of randomness is the subject of complex discussions in both mathematics and philosophy. However, for a cryptographic approach it is sufficient to think of randomness as uncertainty [7, p. 155]. Using random data to construct a cipher key should leave any adversary as uncertain about the key value as possible. Uncertainty is as such related to the amount of information on the key the adversary is missing, or in other words, the amount of information she would earn, if the key was revealed to her. In information theory, this kind of uncertainty is referred to as *entropy*. At this point it is sufficient to mention that the higher the entropy value associated with a process is, the more uncertain an observer is about the outcome. In Section 2.1, a more detailed definition of entropy is given.

Random data is accompanied by certain statistical characteristics. Most importantly, random data should ideally be independent and uniformly distributed (see Section 2.1). However, even though this characteristics are important, they should not be confused with randomness [3]. For example, deterministic algorithms exist to model uniform outcomes. This does not necessarily mean that an observer is uncertain about the next output value.

# **1.2** Pseudorandom and true random number generators

Modern RNGs are realized as electronic systems, either by means of software, hardware or a hybrid solution. However, electronic devices are in general deterministic systems. By definition, generating any kind of truly random data using a pure deterministic system is impossible [8][9, p. 44]. This simple but important fact describes the key challenge of designing modern RNGs and gives reason to divide them into two main classes: *Pseudorandom Number Generators* and *True Random Number*

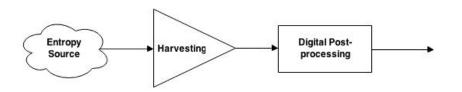

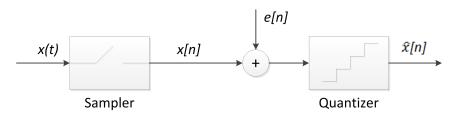

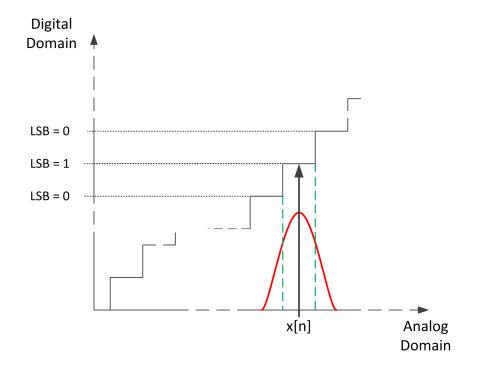

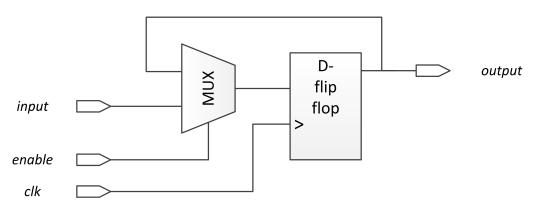

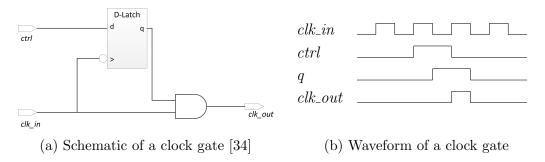

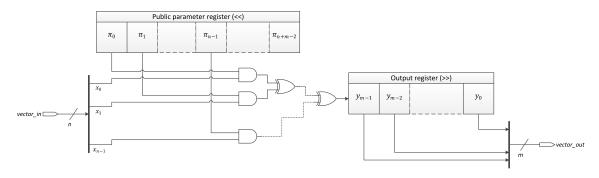

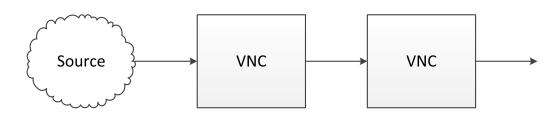

Figure 1.1: Block schematic of a TRNG

#### Generators.

PRNGs are deterministic systems. They use an input, called *seed*, to generate data that for an external observer appears to be random. However, if the seed becomes known, the output data is exactly predictable. Moreover, if the same seed is used for a sufficient long time, patterns start to arise in the output data, which destroys the illusion of randomness. It should nonetheless be noted that PRNGs in general play an important role in cryptography. So called "cryptographically strong" approaches exist, which prevent an adversary from gaining knowledge about the seed. They also provide satisfying long streams of data without patterns. However, they do not solve the original problem of generating random data as they rely on the existence of a random seed.

TRNGs generate random data by observing random processes inside or outside the system. In general, TRNGs consists of three parts [10][11], as depicted in Figure 1.1:

- **Entropy-source:** The entropy-source is the process to be observed. Examples of such processes range from user interactions over thermal noise in electronic resistors to phenomena in quantum physics. It is important to note that the entropy-source is the only true random part of a TRNG. This means that no other part of the system can increase the amount of entropy associated with the data.

- Harvesting: In this step the observed entropy is transformed into a digital data representation. In other words, it can be illustrated as the observation process. A common example is an *Analog-to-Digital Converter* (ADC) which converts an analog noise signal into a digital data stream. As the entropy-source and the harvesting process are closely related, in the literature harvesting is often included in the term entropy-source. This approach is adopted for the purpose of this report.

- **Post-processing:** Most TRNGs use some kind of digital post-processing, even though this is not strictly necessary. The purpose of post-processing varies. Most commonly, it is used to reshape the statistical characteristics of the data, but may also be implemented to increase, for example, the resistance against attacks on the TRNG.

#### 1.3 This project

Motivated by the above discussed, this project focuses on an energy efficient implementation of a TRNG in a mixed-signal MCU environment. Generally, this kind of MCUs are equipped with an ADC. It is therefore reasonable to try to use the existing ADC as an entropy source for the TRNG, due to two reasons. First, additional design cost for the construction of an alternative source can be omitted. Second, with regard to Section 1.2 it is clear that the truly random characteristics of an entropy source cannot be simulated by means of deterministic computer-aided tools, but must be directly observed from prototypes. MCUs are typically realized by means of advanced CMOS technologies which make the production of single prototypes extremely expensive. Thus, by using the existing ADC as a source of entropy, the functionality of the TRNG can be tested and verified before production, without the need of expensive prototyping.

However, ADCs are generally designed to behave as deterministic as possible. Therefore, they must be considered to be rather weak entropy sources. As a result, post-processing is necessary in order to not compromise the quality of the TRNG. During a preceding literature study [12], the most common post-processing algorithms have been considered in a similar context as given for this project. Based on this study, two algorithms appear to be most suited for the given scenario: the *von Neumann Corrector* (VNC) and the *Extractor based on pairwise Independent Hash Functions* (IHF). Both algorithms are based on firm mathematical proofs, and can thus guarantee randomness for the right circumstances. The VNC is a very simple algorithm with a minimum of complexity. However, its functionality is dependent on very specific statistical characteristics of the used source. In contrast, the IHF is a more advanced algorithm, accompanied by more complexity, but, at the same time, it works for a wider range of source characteristics.

With regard to this project specification, the following has been achieved and is discussed in this report:

- A weak entropy source has been implemented using the ADC of an *EFM32* Wonder Gecko

- A test for the source characteristics required by the VNC has been proposed and implemented in MATLAB

- A complexity analysis of both the VNC and the IHF has been performed

- A work flow for logical verification and synthesis for the purpose of power estimation has been composed

- Functional version of both the VNC and the IHF have been implemented in SystemVerilog

- Different combinations of the entropy source and post-processing have been evaluated both with respect to randomness and energy performance

- A functional TRNG has been designed, which passes the NIST test suite and uses approximately 5.9 nJ per output bit

#### 1.4 Outline

The here presented report is structured in the following manner. Chapter 2 covers the background of some of the most fundamental aspects of this report. This includes the introduction of the concept of entropy as a measure of randomness, presenting the procedure of statistical hypothesis testing, a short discussion of the possible use of an ADC as an entropy source, the presentation of the two in the project considered post-processors and a brief background on power dissipation in digital systems. In Chapter 3, the setup of an entropy source based on an ADC is presented. In addition, a test to analyze the output data of the source is proposed and the corresponding analysis is performed. Chapter 4 focuses on the post-processors by first performing an complexity analysis and then presenting the implementation of both post-processors in SystemVerilog. After the implementation, the output of the post-processors in combination with the ADC based entropy source is tested for whether it can be considered to be random. This is presented in Chapter 5. Chapter 6 focuses on the power and energy performance of the different post-processors and their combination with the entropy source. Finally, Chapter 7 presents a comparison of the most important aspects of the VNC and the IHF, a conclusion and a proposal of topics that could be explored in a subsequent project.

### Chapter 2

### Background

This chapter covers the theoretical background of some of the most fundamental aspects of this project. Section 2.1 explores the concept of randomness and Section 2.2 introduces statistical testing, which can be used to test if a data stream can be considered random. The basic concept that enable the use of an ADC as an entropy source are presented in Section 2.3 and Section 2.4 introduces the two in this project considered post-processors. Finally, Section 2.5 focuses on dynamic power dissipation in digital systems.

#### 2.1 Random Data

In Section 1.1, a first informal definition of the concept of randomness has been given. It has been pointed out that randomness depends on the amount of available information about an event, which can be shown to be directly connected to the probability of the event. As such, randomness is closely related to both information theory and probability theory. The following section presents therefore some basic concepts of these fields which are used repeatedly throughout this report. Most importantly, the concept of *entropy* is introduced and established as a measure of randomness.

To be able to discuss the concept of random data in more detail, it is necessary to introduce a mathematical model for a source of data. A first approach is given by the definition of an *ensemble* X as stated in [13, p. 22]: It defines X to be the triple  $(x, \mathcal{A}_X, \mathcal{P}_X)$ , where x is the *outcome* of the data source, which takes on one of the k values included in the set  $\mathcal{A}_X = \{a_0, ..., a_{k-1}\}$ . The probabilities of x taking on any particular value in  $\mathcal{A}_X$  are defined in  $\mathcal{P}_X = \{p_0, ..., p_{k-1}\}$ , where  $p_i$  is the probability that x takes on the value of  $a_i$ ,  $p_i = \Pr(x = a_i)$ . Generally,  $\Pr(x = a_i)$  is referred to as the marginal probability of  $x = a_i$ . Note that  $p_i \leq 0$  for all i in [0, k-1] and  $\sum_{i=0}^{k-1} p_i = 1$ .

Based on this model of a data source, it is possible to discuss the concept of randomness in a more formal manner. As mentioned in Section 1.1, during this project, randomness is considered to be the amount of uncertainty an observer has about some data. Using the ensemble X to model a source of data, randomness is thus the level of uncertainty an observer associates with the outcome x. Uncertainty can be depicted as the lack of information an observer has about x, or, seen from a

different perspective, the amount of information she earns about x when the concrete value of x is revealed to her.

It is common, to measure the amount of information associated with x taking on a particular value  $a_i$  by means of the *Shannon information content*, which is defined as [13, p. 32],

$$\mathbf{h}(x=a_i) \equiv \log_2(\frac{1}{p_i}). \tag{2.1}$$

It is out of the scope of this report to give a detailed discussion about Equation 2.1. However, it is worth noticing the following three properties:

- The value of  $h(x = a_i)$  increases with decreasing  $p_i$ . This means that the more unlikely a particular event is the more information is earned if it actually occurs. This fits the human understanding of information.

- If  $p_i = 1$ ,  $h(x = a_i) = 0$ . In other words, if an event is certain to happen, no information is gained by observing it. Also this fact is intuitively true.

- Any base might be chosen for the logarithmic function in Equation 2.1. Choosing the base to be 2 allows to use *bits* as the unit of measurement, which is convenient for this project.

Using Equation 2.1, it is possible to measure how uncertain an observer is about one particular outcome. However, this is not sufficient to analyze the source characterized by X. Even though one event might occur with low probability, another value might occur frequently (i.e., with high probability). In such a situation an observer would be rather certain about the outcome - at least most of the time.

As an example, one might consider the ensemble X with  $\mathcal{A}_X = \{0, 1\}$  and  $\mathcal{P}_X = \{0.0625, 0.9375\}$ . Using Equation 2.1, the Shannon information content associated with x = 0 is with 4 bits quiet high. However, it is expected that x = 1 most of the time and an observer can be close to certain that also the next outcome of X is 1.

It follows from the example, that, in order to find a meaningful measure for the source, all possible outcomes have to be taken into consideration. This can be achieved by using Shannons definition of entropy<sup>1</sup> [13, p. 32] as the average information content of an ensemble X,

$$H(X) \equiv \sum_{i=0}^{k-1} p_i \cdot \log_2(\frac{1}{p_i}).$$

(2.2)

Analyzing a source by means of Equation 2.2 allows to determine how uncertain an observer is about the outcome on the average. For the purpose of this project, a source with a high entropy value is considered to be closer to a perfectly random outcome than a source with a lower associated entropy.

For the sake of completeness, it is necessary to mention that an alternative to entropy as the measure of randomness exists, which is frequently used in related

<sup>&</sup>lt;sup>1</sup>For readability, Shannons definition of entropy as given in Equation 2.2 is simply referred to as "entropy", throughout the rest of this report.

literature [14]. It is referred to as *min-entropy* and defined for any ensemble X by [14],

$$\min-\operatorname{Ent}(X) \equiv \max(\kappa : \Pr(x = a_i) \le 2^{-\kappa}, \quad \forall i \in [0, k-1]).$$

(2.3)

In other words, the min-entropy of an ensemble X is the maximum value of  $\kappa$  such that the possibility for any possible outcome is at most  $2^{-\kappa}$ . This means that, with regards to Equation 2.1, min-Ent(X) is equal to the smallest information content associated with the ensemble. It is worth noticing that the min-entropy is smaller or equal to the Shannon entropy, and it is therefore a more conservative method to evaluate randomness.

To give a simple example, assuming an ensemble X with  $\mathcal{P}_X = \{\frac{1}{2}, \frac{1}{4}, \frac{1}{8}, \frac{1}{8}\}$ , the maximal probability is  $p_{\text{max}} = \frac{1}{2}$ . Using  $p_{\text{max}}$  and solving Equation 2.3 for  $\kappa$  results in,

$$\kappa = \log_2(\frac{1}{p_{\max}}),\tag{2.4}$$

which yields to  $\kappa = 1$  for  $p_{\text{max}} = \frac{1}{2}$ .

Even though Equation 2.2 and Equation 2.3 are not equivalent, it should be noted that concept of entropy and min-entropy are fairly similar. Through out the reminder of this section and in large parts of this report, the focus is on entropy. However, in some special cases the min-entropy has to be considered. It is therefore essential to note that the in the following derived principles also hold for min-entropy, even though not explicitly stated [14].

Having established the concept entropy as a measure of randomness, it is natural to establish which characteristics of X yield H(X) to reach its maximum value. While this can be achieved by means of mathematical computations, a more intuitive approaches is chosen here, leaving a formal proof to Appendix A.

A first characteristic can be disclosed by considering once more the ensemble X with the set  $\mathcal{A}_X = \{0, 1\}$ . Assuming that an observer would be completely uncertain about the outcome x, she would expect to observe x = 0 with the same probability as x = 1. By the definition of an ensemble as given above, this means that  $\Pr(x = 0) = \Pr(x = 1) = \frac{1}{2}$ . In the same manner, this statement can be formulated for any arbitrary data source with  $\mathcal{A}_X = \{a_0, ..., a_{k-1}\}$ . The outcome x is associated with the maximum amount of uncertainty if the probability of x taking on a particular value is the same for all possible values. In other words, in order to maximize  $\operatorname{H}(X)$ , x must be uniform distributed over  $\mathcal{A}_X$ . This means that  $p_i = \frac{1}{k}$  for all i in the range [0, k - 1]. Combining this statement with Equation 2.2 yields,

$$H(X) \le \log_2(k). \tag{2.5}$$

Appendix A.1 shows that this is the maximum amount of entropy that can be achieved by source which produces a single outcome.

As the main emphasis of this project lies on binary data, it is worth to consider the consequences of using this kind of data. Denoting a source that produces a *n*-bit outcome x as X with  $\mathcal{A}_X = \{0,1\}^n$ , where  $\{0,1\}^n$  is the set that contains all  $2^n$  variants of a *n*-bit word, it follows that  $k = 2^n$ . Thus, by Equation 2.5, the maximum amount of entropy associated with an n-bits binary source is n bits, which matches the intuitive understanding of randomness.

A source that produces uniformly distributed data is frequently described as *un-biased*. In contrast, a source that produces some outcomes with higher probabilities than others is said to be *biased* towards those outcomes. It is obvious that, for the purpose of this project, an unbiased outcome is desirable. However, this is rarely the case. In practice, one must often consider using a slightly biased ensemble in lack of a perfectly unbiased source. Therefore, it is of interest to find a method that can be used to relate the distribution of an ensemble X with the uniform distribution, or, more generally, with the distribution of any arbitrary ensemble Y, where  $\mathcal{A}_X = \mathcal{A}_Y$ . This can be achieved by means of the *statistical distance* between X and Y, defined as [14],

$$dist(X,Y) \equiv \frac{1}{2} \cdot \sum_{i=0}^{k-1} |\Pr(x=a_i) - \Pr(y=a_i)|.$$

(2.6)

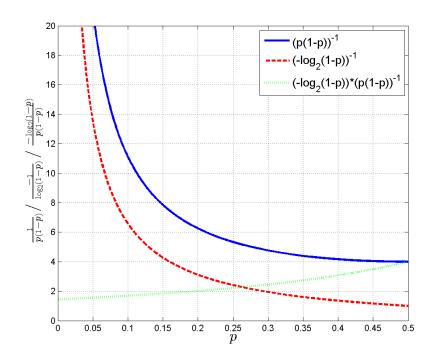

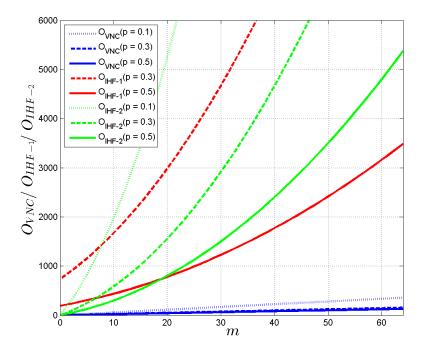

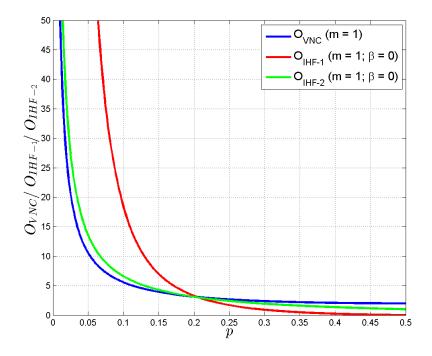

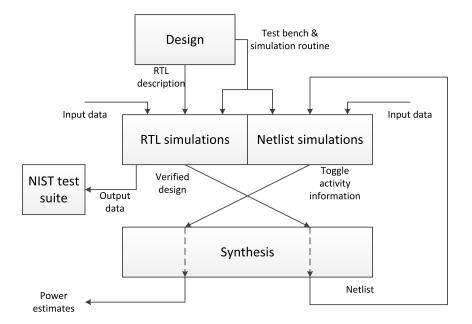

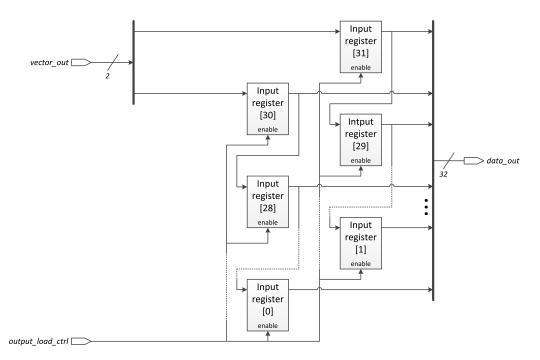

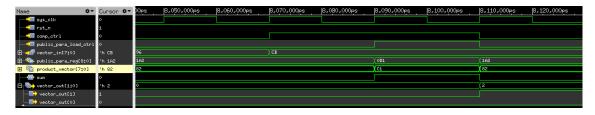

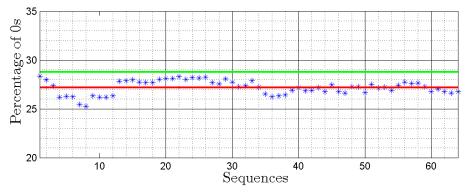

If  $\operatorname{dist}(X, Y) = 0$  the distributions are identical. Otherwise, for  $\operatorname{dist}(X, Y) < \epsilon$ , the distributions  $\mathcal{P}_X$  and  $\mathcal{P}_Y$  are said to be  $\epsilon$ -close. As such,  $\epsilon$  is a measure of the statistical distance.