## Compensation of Threshold Voltage for Process and Temperature Variations in 28nm UTBB FDSOI

Erlend Strandvik

Master of Science in ElectronicsSubmission date:June 2015Supervisor:Trond Ytterdal, IETCo-supervisor:Carsten Wulff, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# **Problem description**

The main goal of this thesis is to design a circuit that compensate threshold voltages for process and temperature variations through the use of adaptive body biasing in a commercially available 28nm FDSOI transistor technology. Its performance should be tested by designing and optimising a 65.5MHz inverter based ring oscillator to be used with this compensation circuit, in order to see its improvement in frequency stability across processing corners and temperature variations compared to an uncompensated ring oscillator.

Subsidiary goals are listed below.

- Identify transistor behaviour suffering from process and temperature variations.

- Design and analysis of compensation circuits, for both NMOS and PMOS, that provides body bias to compensate the threshold voltage for process and temperature variations.

- Identify the limitations of body biasing and apply techniques to push these limits.

- Design and analysis of sub circuits needed to realise the compensation circuit.

- Design and analysis of thirteen stage inverted based *Ring Oscillator*, operating at a frequency of 65.5*MHz*.

- Optimise ring oscillator frequency stability by utilising the compensation circuit, and identify improvements made compared to an uncompensated ring oscillator.

## Abstract

As technology scales down in order to meet demands of more computing power per area, a variety of challenges emerge. Devices with channel lengths of a few nano meters require atomic precision when they are manufactured. Small irregularities in the equipment and manufacturing environment can cause large process variations from die–to–die, but also within–die variations. Along with the increasing density of transistors per die which has led to severe performance issues due to temperature variations, these effects may seriously impact operation and cause large deviations in frequency and power across a the chip.

This thesis will present the analysis and design of a circuit with the goal of compensating the threshold voltage, by means of body biasing, in order to mitigate process and temperature variations. The compensation circuit is designed to provide adaptive body biasing for a large number of equally matched devices within the chip, which may be useful in digital systems with many repetitive instances. Its functionality and effect will be tested by designing it to be used with a 13-stage inverter based ring oscillator operating at 65.5MHz, and observing the improvement in frequency variation across processing corners and a temperature range from  $-40^{\circ}C$  to  $80^{\circ}C$ . All circuits were designed using a commercially available 28nm FDSOI transistor technology because of its excellent susceptibility to body biasing, and its promise as a competitive technology to continue Moore's law.

Results obtained by post–layout simulations on the ring oscillator show that frequency variations across processing corners and temperature has been reduced from 18.69% down to 0.632% by utilising adaptive body biasing provided by the compensation circuit. Ring oscillator frequency temperature sensitivity in a range from  $-40^{\circ}C$  to  $80^{\circ}C$  for the typical corner is shown to be as little as  $29.4\frac{ppm}{cC}$

## Sammendrag

Som et resultat av behovet for økt datakraft skjer det en kontinuerlig nedskalering i størrelse for transistorteknologier, noe som stadig innfører nye utfordringer. Transistorer har nådd et nivå med kanallengder på noen nanometer, noe som stiller ekstremt høye krav til produksjonen. Små uregelmessigheter i produksjonsutstyr og produksjonsmiljø can føre til store prosessvariasjon mellom hver enkelt chip produsert, men også variasjon innad på hver enkelt chip. Sammen med en økt transistortetthet per chip, som fører til store ytelsesproblemer på grunn av temperaturvariasjoner, har disse effektene sammen stor innvirkning i forskjeller på operasjonsfrekvens og effektforbruk.

Denne masteravhandlingen presenterer analyse og design av en krets med målet om å kompensere terskelspenningen, ved hjelp av bulk-biasering, for å minimere effekten av prosess- og temperaturvariasjon. Kompenseringskretsen er laget for å dynamisk tilpasse bulk biasering for et stort antall transistorer av samme type og størrelse på en chip, som kan være nyttig i digitale systemer hvor det er mange repiterte instanser. Funksjonaliteten og effekten av kompenseringskretsen vil bli testet ved å designe den for og brukes med en 13-stegs inverterbasert ringoscillator som opererer på 65.5MHz, for så å observere forbedringer i frekvensvariasjon på tvers av forskjellige prosesshjørner og temperaturer mellom  $-40^{\circ}C$  til  $80^{\circ}C$ . Alle kretser ble designet i en kommersielt tilgjengelig 28nm FDSOI transistor teknologi, på bakgrunn av denne teknologiens utmerkede mottakelighet for bulk biasering og dens lovende utsikter som arvtageren til BULK CMOS for å føre *Moore's law* videre.

Resultater fra simuleringer gjort på nettlister ekstrahert fra utlegg av ringoscillatoren viser at frekvensvariasjon over prosesshjørner og temperatur har blir redusert fra 18.69% ned til 0.632% ved å bruke kompenseringskretsen designet i denne oppgaven. Ringoscillatorens temperatur sensistivitet i temperaturområdet  $-40^{\circ}C$  til  $80^{\circ}C$  for det typiske hjørne viste seg å være bare  $29.4\frac{pm}{cC}$ .

## Preface

The work in this thesis was carried out during spring 2014, at NTNU, Trondheim. I would like to thank my supervisors, Professor Trond Ytterdal and Carsten Wulff, for their guidance throughout this project. During weekly meetings there has been a lot of coffee drinking, good talks and many laughs. Their skill and passion for the art of analog ic-design has been a great motivator, leading me to pursue a career within this field.

Another thanks goes out to my fellow students and office roommates, Endre Larsen, Harald Garvik and Thomas Nornes. Our office has been a joyful place where we have had lots of fun. We have motivated each other, ideas have been exchanged and many topics discussed. Our camaraderie, along with the exhaustible positivity of our supervisors, has turned hardships into good times.

# Table of Contents

|                     |        | Pa                                  | $\mathbf{age}$ |

|---------------------|--------|-------------------------------------|----------------|

| P                   | roble  | em description                      | i              |

| Α                   | bstra  | act                                 | iii            |

| Sammendrag          |        | v                                   |                |

| Preface v           |        | vii                                 |                |

| Table of Contents   |        | xi                                  |                |

| List of Figures xiv |        | xiv                                 |                |

| $\mathbf{Li}$       | ist of | f Tables                            | xv             |

| 1                   | Inti   | roduction                           | 1              |

|                     | 1.1    | Main contributions                  | 3              |

|                     | 1.2    | Thesis outline                      | 3              |

| <b>2</b>            | The    | eory                                | 5              |

|                     | 2.1    | FDSOI                               | 5              |

|                     | 2.2    | Properties of the Mosfet Transistor | 6              |

|                     |        | 2.2.1 Operating Regions             | 8              |

|   |                | 2.2.2 Threshold voltage $\ldots \ldots \ldots$ | 11 |

|---|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 2.3            | OTAs 1                                                                                                                                           | 13 |

|   |                | 2.3.1 Differential input stage                                                                                                                   | 14 |

|   |                | 2.3.2 Current mirrors                                                                                                                            | 15 |

|   | 2.4            | Feedback                                                                                                                                         | 16 |

|   | 2.5            | Sources of variation in integrated circuits                                                                                                      | 18 |

|   |                | 2.5.1 Process variation                                                                                                                          | 19 |

|   |                | 2.5.2 Random process variation                                                                                                                   | 19 |

|   |                | 2.5.3 Temperature variation                                                                                                                      | 21 |

| _ | _              |                                                                                                                                                  |    |

| 3 | $\mathbf{Des}$ | ign 2                                                                                                                                            | 23 |

|   | 3.1            | Compensation of process and temperature variations                                                                                               | 23 |

|   |                | 3.1.1 Variation sensing and compensation                                                                                                         | 24 |

|   | 3.2            | PTAT Current Reference                                                                                                                           | 27 |

|   | 3.3            | Amplifier design                                                                                                                                 | 32 |

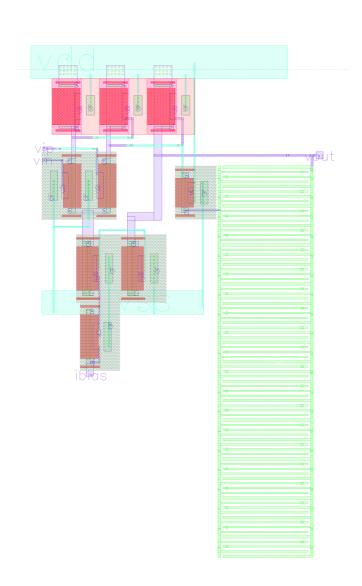

|   |                | 3.3.1 Amplifier layout                                                                                                                           | 34 |

|   | 3.4            | Ring Oscillator                                                                                                                                  | 34 |

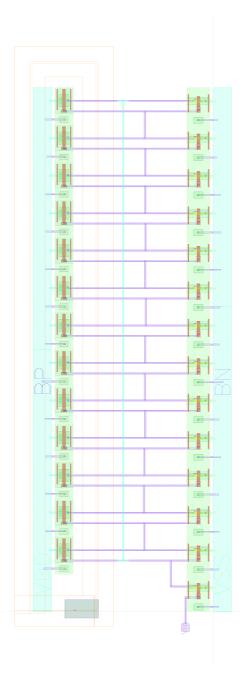

|   |                | 3.4.1 Ring oscillator layout                                                                                                                     | 38 |

|   | 3.5            | Compensation of ring oscillator                                                                                                                  | 38 |

|   | Ð              |                                                                                                                                                  |    |

| 4 | Res            |                                                                                                                                                  | 13 |

|   | 4.1            | PTAT current reference                                                                                                                           | 43 |

|   |                | 4.1.1 Mismatch                                                                                                                                   | 45 |

|   | 4.2            | Two-stage miller amplifier                                                                                                                       | 47 |

|   | 4.3            | Compensation circuit                                                                                                                             | 47 |

|   | 4.4            | Compensation of ring oscillator                                                                                                                  | 51 |

|   |                | 4.4.1 Mismatch in the ring oscillator                                                                                                            | 55 |

| 5  | Con                                             | clusion                     | 59  |

|----|-------------------------------------------------|-----------------------------|-----|

|    | 5.1                                             | Further work                | 60  |

| Aj | Appendix A Design of two-stage miller amplifier |                             |     |

|    | A.1                                             | Implementation of amplifier | III |

# List of Figures

| 2.1  | Illustration of BULK CMOS and UTBB FDSOI CMOS                                                          | 6   |

|------|--------------------------------------------------------------------------------------------------------|-----|

| 2.2  | NMOS intrinsic gain stage.                                                                             | 7   |

| 2.3  | NMOS Low Frequency Small Signal Equivalent Circuit.                                                    | 7   |

| 2.4  | Cross section showing the physical structure of an UTBB FDSOI transistor implemented with triple well. | 13  |

| 2.5  | Differential to singel-ended amplifier                                                                 | 14  |

| 2.6  | Differential input stage                                                                               | 15  |

| 2.7  | A CMOS current mirror                                                                                  | 15  |

| 2.8  | General feedback system                                                                                | 16  |

| 2.9  | Configuraion for calculating open loop gain of a feedback system $\ .$ .                               | 17  |

| 2.10 | Illustration of spread between corners                                                                 | 20  |

| 0.1  |                                                                                                        | 0.4 |

| 3.1  | Diode connected transistor                                                                             | 24  |

| 3.2  | Derivative of logarithmic drain current versus $v_{gs}$                                                | 25  |

| 3.3  | NMOS threshold compensation circuit.[29]                                                               | 27  |

| 3.4  | $V_{eff}$ dependency on temperature variation with constant $I_{ref}$                                  | 28  |

| 3.5  | PMOS threshold compensation circuit.[29]                                                               | 29  |

| 3.6  | PTAT current reference                                                                                 | 30  |

| 3.7  | small signal equivalent circuit of PTAT current reference                                              | 31  |

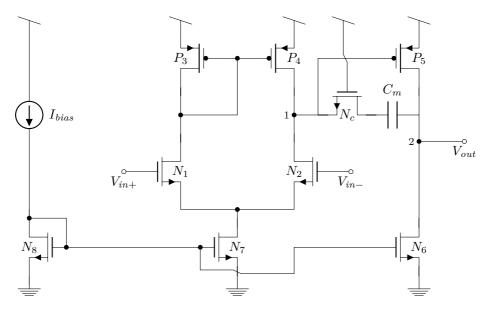

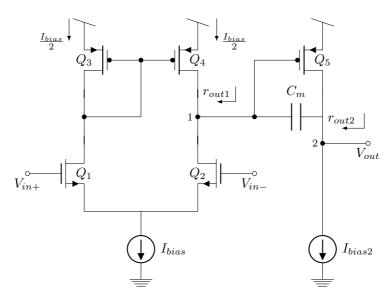

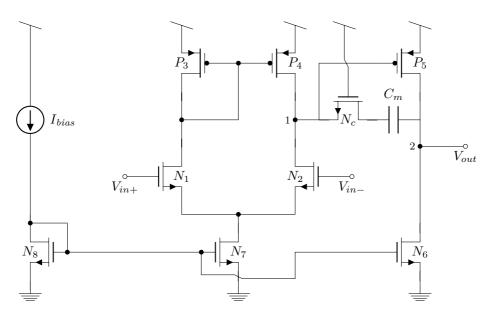

| 3.8  | Implemented two-stage amplifier[29]                                                                    | 33  |

| 3.9  | Layout of two–stage miller amplifier                                                                               | 35 |

|------|--------------------------------------------------------------------------------------------------------------------|----|

| 3.10 | Ring oscillator with 3 inverters                                                                                   | 37 |

| 3.11 | Layout of inverter based ring oscillator with 13 stages                                                            | 39 |

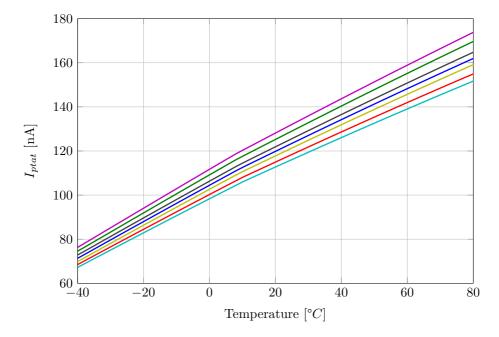

| 4.1  | Corner variation of PTAT current reference for NMOS compensation                                                   | 44 |

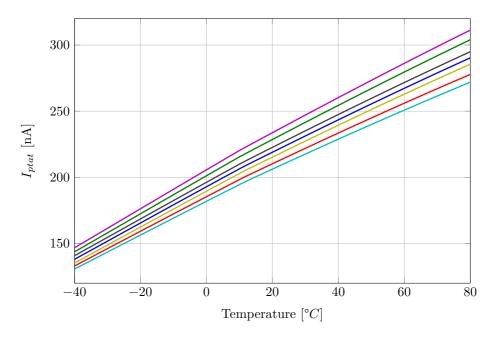

| 4.2  | Corner variation of $\ensuremath{PTAT}$ current reference for $\ensuremath{PMOS}$ compensation                     | 45 |

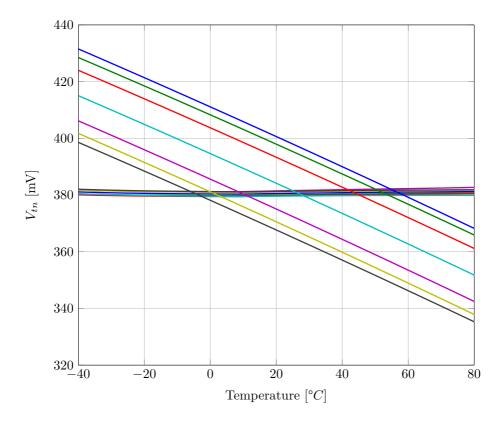

| 4.3  | NMOS threshold voltage versus temperature and process variations, compensated and uncompensated.                   | 49 |

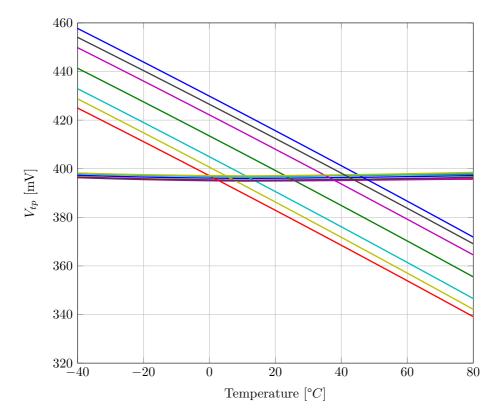

| 4.4  | PMOS threshold voltage versus temperature and process variations, compensated and uncompensated.                   | 50 |

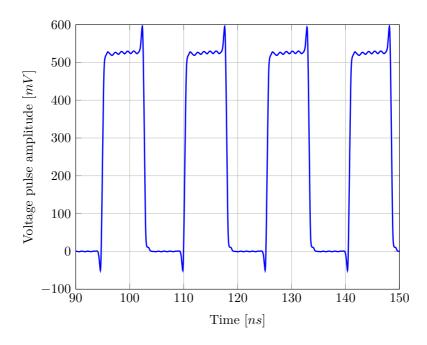

| 4.5  | Ring oscillator voltage pulse.                                                                                     | 52 |

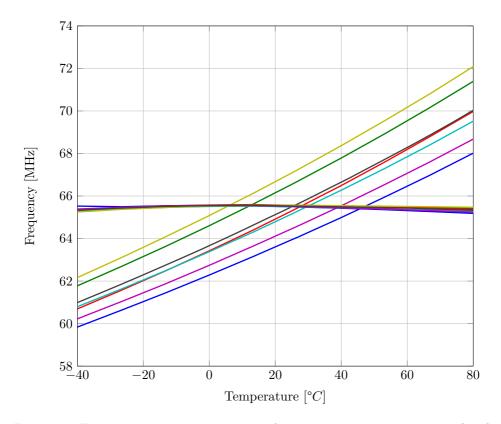

| 4.6  | Frequency versus temperature and process variations, compensated and uncompensated.                                | 54 |

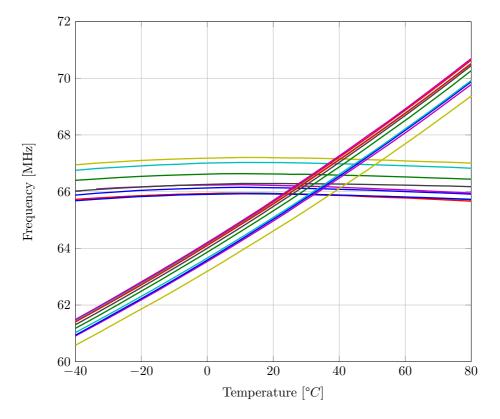

| 4.7  | Frequency versus temperature and process variations, compensated and uncompensated, during monte carlo simulation. | 57 |

| A.1  | Two-stage Miller Amplifier                                                                                         | II |

| A.2  | Implemented two-stage amplifier                                                                                    | IV |

# List of Tables

| 3.1 | Amplifier paramteres                                                                          | 33 |

|-----|-----------------------------------------------------------------------------------------------|----|

| 3.2 | NVTCTRL current reference transistor sizes                                                    | 40 |

| 3.3 | PVTCTRL current reference transistor sizes                                                    | 40 |

| 4.1 | Results of PTAT current reference for NMOS and PMOS compensation circuits.                    | 46 |

| 4.2 | Results of 60 monte carlo runs for the PTAT current reference                                 | 46 |

| 4.3 | Results of amplifier schematic model simulations.<br>[29] $\ldots$                            | 47 |

| 4.4 | Results of amplifier post–layout simulations                                                  | 48 |

| 4.5 | Variations in NMOS and PMOS–threhsold voltage                                                 | 51 |

| 4.6 | Results of NMOS and PMOS compensation circuits.                                               | 51 |

| 4.7 | Resulting properties for the ring oscillator                                                  | 53 |

| 4.8 | Frequency variation in the ring oscillator as a result of process and temperature variations. | 53 |

| 4.9 | Results of 20 ring oscillator monte carlo runs                                                | 56 |

| A.1 | Amplifier paramteres                                                                          | V  |

# 1 Introduction

For the past decades an increasing demand for computational power has emerged as information technology's role in society has expanded dramatically. In year 2003, there were 500-million devices connected to the internet, today we have reached 8.9-billion and an estimate show that as a result of the new trend "Internet of Things" several tens of billions of devices will be connected by year 2030 [1, 2]. This increasing demand has resulted in an approximately doubling of processing power for computers every two years from the seventies and up until now, a development which is known as Moore's law [3]. To maintain this rise in processing power, transistor sizes have been scaled down to fit more devices onto a single chip, so an increased number of operations can be performed in less area and in less time. As transistor process technology has scaled down, a variety of challenges has emerged [4–7]. Transistors are now being produced at an atomic level, which put stringent requirements on presicion in the manufactoring process. Because transistor operation is based on its physical properties, small variations in the manufactoring process can lead to large deviations in transistor operation, which in turn can degrade the performance of an integrated circuit [5]. A high density of transistors on a chip also generate huge amounts of heat, which have a severe impact on transistor performance as it causes variations and increased leakage across the chip and it is considered one of the great challenges for integrated circuits today [7, 8]. All these variations have larger impact when the supply voltage is reduced to meet the low power demands of an increasing number of battery driven devices. Threshold voltage does not scale proportional to supply voltage, and the difference between supply voltage and transistor threshold voltage is reduced [6, 9, 10].

Threshold voltage is a parameter often used to describe transistor operation, and may be defined as the voltage needed to fully invert the transistor channel[11]. It is not a physical property, but a parameter that is derived for analytical purposes to describe transitor operation relative to an approximate level of channel inversion. Transistor variation is also often described in terms of threshold voltage, or rather a deviation relative to an expected threshold voltage, which will be the case in this thesis as well [5]. Variations in threshold voltage cause severe variations in operational frequency and may increase leakage currents, in some cases operational frequency may vary up to 30% whitin the same chip [4, 8, 12]. The threshold voltage can therefore be recognized as a critical parameter to control, in order to minimise the impact of variations due to manufactoring and temperature.

One way to control the threshold voltage is by using bulk biasing, or body biasing. The threshold voltage is a function of the bulk-source potential  $V_{bs}$ , and by applying a postive voltage between bulk and source of a NMOS-transistor, its threshold voltage will be reduced, which will decrease its gate delay, but increase leakage current. By applying a negative voltage between bulk and source of a NMOS-transistor, its threshold voltage will increase which will reduce its gate delay and reduce leakage currents. These two techniques are called forward body biasing and reverse body biasing, and can be exploited to optimise circuit performance in terms of operation frequency and leakge[7, 13].

This thesis will explore body biasing as a technique to compensate the threshold voltage for process and temperature variations in a commercially available 28nmUltra-Thin Buried oxide and Body Fully Depleted Silicon on Insulator, UTBB FDSOI CMOS technology. This technology is engineered to achieve low power operation with less leakage than BULK CMOS, and is viewed as one of the top transistor technologies to continue Moore's law [13, 14]. Systems capable of compensating threshold voltages in both NMOS and PMOS-transistors will be designed and analysed. These compensation systems will then be tested with a thirteen stage ring oscillator. Ring oscillator frequency depend highly on threshold voltage, and will therefore be vulnerable to both process and temperature variations, which makes them very applicable when characterising variations [5]. The compensation circuits effect can then be determined by looking at frequency variations in the ring oscillator across process corners and temperature. The system will adaptively use both forward body bias and reverse body bias, which sometimes is referred to as adaptive body bias, in order to stabilise the ring oscillator frequency. To the authors knowledge, there are currently no other litterature on ring oscillators with body biasing to compensate for process and temperature variations, so in order to compare its effectivity, published results from a few ring oscillators with other means of process and temperature compensation will be looked at. Only published work with on chip measurement will be used.

Of all oscillators looked at in previous work, the most cited [15] utilises a differential ring oscillator with a control voltage compensating for process and temperature variations. With a band gap reference and voltage regulator providing process and temperature insensitive supply voltage, this oscillator has a power consumption of 1.5mW. [15] reports a frequency variation of  $\pm 0.84\%$  around the typical process corner for a temperature range of  $-40^{\circ}C$ – $125^{\circ}C$ . With a variation in frequency of  $\pm 2.12\%$  across three corners TT, FF and SS, [15] yields a worst case variation across both process and temperature of  $\pm 2.64\%$ . A ring oscillator with a much simpler architecture and a total power consumption of  $87\mu W$  is given in [16]. This ring oscillator reports a variation in frequency of 5.8% across corners and  $85\frac{ppm}{c_C}$ over temperature. This means [16] has a lower power consumption and is more insensitive to temperature variations than [15], but has larger variations across process corners.

## 1.1 Main contributions

This thesis has investigated the effiency of body biasing as a tool for reducing process and temperture variations in an inverter based 65.5MHz ring oscillator. This has resulted in the design of a circuit able to compensate the threshold voltages for such variations, which was applied to the ring oscillator reducing its frequency variations across processing corners and temperature dramatically. The main contributions if this thesis are listed below:

- Design and analysis of compensation circuits, for both NMOS and PMOS, that provides body bias to compensate the threshold voltage for process and temperature variations.

- Design of a highly linear low-power low-frequency amplifier with 100.4dB DC-gain, a total power consumption of 188.044pW, and a SNDR= 57.21dB.

- Design and analysis of a PTAT-current reference containing a positive feedback loop.

- Design and analysis of a process and temperature compensated thirteen stage inverted based *Ring Oscillator*, operating at a frequency of 65.5*MHz*.

## 1.2 Thesis outline

In chapter 2, background theory which is relevant to the task at hand will be presented. This includes some basic theory concerning the transistor technology used, and some more theory on its physical structure that is of high importance when using body biasing. There will also be presented some classical theory on transistor operation and amplifier design, in order to support different design choices. Lastly there will be a section explaining sources of variation in integrated circuits. Chapter 3 presents the design and analysis of the compensation system, the ring oscillator and all circuits in the compensation system. In chapter 4, results obtained by simulation will be presented, analysed and discussed, providing the insight needed to obtain a conclusion which is presented in chapter 5.

# 2 Theory

This chapter presents background theory supporting main topics and design choices made throughout this thesis. Much of the basic theory presented in this chapter is based on classical theory that can be found regular text books on analog integrated circuit design, e.g. [11, 17, 18]. However, some less known theory is also presented, and sources for this will be listed were this theory is presented.

First there will be a short presentation of FDSOI-transistors, which will be followed by a section explaining the operation of a MOSFET-transistor, in which an important subsection is dedicated to the threshold voltage and theory concerning body biasing. After a short section about OTAs there will be a section concerning feedback, as feedback is a vital part of the compensation circuit and many of the other circuits designed in this thesis. Lastly, some sources of variation in integrated circuits are present.

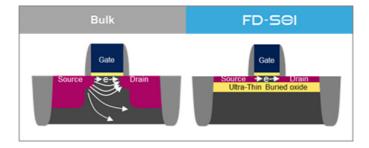

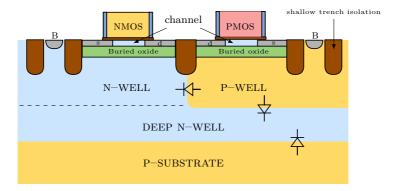

## 2.1 FDSOI

Ultra-Thin Buried oxide and Body Fully Depleted Silicon on Insulator, UTBB FD-SOI, is a planar CMOS transistor technology designed for low power applications and show great potential as a successor to BULK CMOS for continuing Moore's law [13]. UTBB FDSOI transistors are constructed by placing an ultra-thin undoped silicon film channel on top of a buried oxide layer. This oxide layer provides insulation between the substrate and channel, hence the name silicon on insulator. For 28nmFDSOI, the buried oxide is 25nm thick and the channel is 7nm thick. Because of the channel being undoped and so thin, the transistor is fully depleted, which means that it has no intrinsic charge carriers. The threshold voltage is therefore almost independent of the silicon film thickness, but a strong function of the high-k gate metal workfunction and the doped backplane beneath the buried oxide [14]. As a result the FDSOI transistor has improved variability and electrostatics compared to BULK CMOS, and do not need pocket implants or channel doping in order to control the electrostatic and the threshold voltage variation [13]. Back-plane doping is chosen based on what type of transistor is implemented. For regular- $V_{t0}$  (RVT) devices the back-plane doping is identical to gate-type, and for low- $V_{t0}$  (LVT) devices the back-plane doping is opposite to the gate-type. This means that LVT-NMOS lies in an n-doped well, whereas LVT-PMOS lies in a p-well which is isolated from the substrate by a deep n-well, and they are so called flipped well devices. Because of the buried oxide providing insulation between channel and substrate there is less junction capacitance and a more confined electrical path between source and drain, resulting in reduced leakage. The buried oxide along with the thin undoped channel improves short channel effects and reduces the effect of drain induced barrier lowering, making this technology eligible for further downscaling [13]. Figure 2.1 is an illustration of a BULK CMOS transistors structure compared to an UTBB FDSOI transistor.

Figure 2.1: Illustration of BULK CMOS and UTBB FDSOI CMOS

The buried oxide will also have an effect as a second gate, due to the capacitive coupling through the undoped depleted silicon. By applying a voltage to this *back gate*, one gate modulate the front channel threshold voltage. This technique of manipulating the threshold voltage is called body biasing, and can be a useful tool for speed enhancement ,power management and to increase performance of a circuit. Compared to BULK CMOS, FDSOI has an improved body effect from increased capacitive coupling causes the threshold voltage to change approximately  $85m\frac{V}{V_{B}}$  compared to  $25m\frac{V}{V_{B}}$  for advanced BULK CMOS [13].

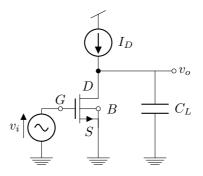

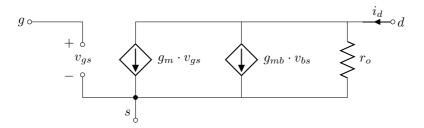

### 2.2 Properties of the Mosfet Transistor

CMOS transistors are central building blocks in today's high density integrated circuits. Transistors in a digital context are operated as switches in which they represent two different states, either 1 or 0. Transistors used in an analog context are used to modulate signals containing information. Using transistors for amplification is one of the most common forms of doing this, as properties needed for amplification are intrinsic to the transistor across technologies. This section will provide the basic theory for understanding mosfet transistors and their operation in an analog context. Figure 2.2 show a NMOS transistor configured as a *intrinsic gain* stage and figure 2.3 depicts the low frequency small signal equivalent model of

a NMOS transistor. With the gate connection (G) serving the input signal, while the bulk (B) is shorted to ground, the intrinsic gain stage can be viewed as a common source configuration loaded by an ideal current source[11].

Figure 2.2: NMOS intrinsic gain stage.

Figure 2.3: NMOS Low Frequency Small Signal Equivalent Circuit.

As we now have defined the intrinsic gain stage we can use figure 2.2 and 2.3 to derive an expression for the transistors intrinsic gain. The intrinsic gain describes the highest possible low frequency small signal voltage gain a transistor can achieve. For low frequencies  $C_L$  acts as an open circuit and the current flowing through  $r_o$  defines the output voltage  $v_o$ , the resulting expression for intrinsic gain is shown in equation (2.1).

$$A_{i,dc} = \frac{v_o}{v_i} = -g_m r_o \tag{2.1}$$

$g_m$  is the transistors transconductance, and  $r_o$  is the transistors output impedance, mostly dominated by the resistance between drain and source. As frequencies rise the impedance at the transistor output gets more and more dominated by  $C_L$ which is comprised by the largest capacitances seen at this node. For the intrinsic configuration this means  $C_L \approx C_{gs} + C_{gd}$ , which is the capacitances between gate to source and gate to drain respectively. These capacitances is not shown in figure 2.3 as this figure represents the transistor for low frequencies. For high frequencies there will be parasitic capacitances between all nodes, where  $C_{gs}$  is largest followed by  $C_{\rm GD}$  [11]. The expression for intrinsic gain at high frequencies is given by equation (2.2).

$$A_{i,ac} = \frac{v_o}{v_i} = -\frac{\frac{g_m}{C_L}}{j\omega}$$

(2.2)

Here  $\omega$  is the angular frequency, defined as  $\omega = 2\pi f$ . By solving the equation for  $|A_{i,ac}| = 1$  we can derive another important intrinsic parameter,  $f_T$ , the unity gain frequency. This parameter is also known as the transition frequency and gives an approximation to the frequency range of which a transistor can operate as an amplifying device. Above this frequency the amplitude of the input small signal current  $|i_{in}|$  exceeds that of the output small signal current  $|i_{out}|$ , and equation (2.3) show this approximated frequency.

$$f_T \approx \frac{g_m}{2\pi C_L} \tag{2.3}$$

#### 2.2.1 Operating Regions

Intrinsic gain and transition frequency are the two most fundamental characteristics of a transistor and make a good starting point when designing analog circuits. However, to do an efficient design one needs to relate these paramters to the operation region of the transistor, so the resulting design is optimised for a given set of specifications. Keep in mind that these definitions and equations are analytic expressions and are merely approximations as there are many other effects that will impact the transistor. However, they are very useful as a starting point when designing analog circuits.

Operation regions of a transistor is defined by the voltage difference between source and drain  $(V_{ds})$  relative to the overdrive voltage  $(V_{eff})$ . The overdrive voltage is defined as  $V_{eff} = V_{GS} - V_{tn}$ , where  $V_{tn}$  is the threshold voltage of an NMOS transistor. If one increases  $V_{ds}$  so that  $V_{ds} \geq V_{eff}$ , the transistor is in active region where the drain current becomes approximately constant due to the drain end of the channel being pinched off and the transistor is saturated. This region of operation is desired when operating the transistor as a amplifier, because of the drain current being nearly independent of  $V_{ds}$  and only changing with  $V_{gs}$ . From the overdrive voltage we can approximate the inversion level of the transistor channel, and the inversion level rises gradually with  $V_{gs}$ . If  $V_{gs} > V_{tn} + 100mV$ the channel is approximately in strong inversion. For a strongly inverted transistor in active region the drain current is dominated by drift current due to an excess of charge carriers, and has an almost quadratic relationship to  $V_{eff}$ . The drain current in strong inversion is given by equation (2.4) where  $\lambda$  is the channel-length modulation and  $\pounds \mu_i$  is the mobility.

$$I_D = \frac{1}{2} \mu_i C_{ox} \left(\frac{W}{L}\right) V_{eff}^2 \left(1 + \lambda V_{ds}\right)$$

(2.4)

When  $V_{gs}$  is decreased and we have  $V_{gs}$  in the region of  $V_{gs} < V_{tn} - 100mV$ , the transistor is in weak inversion. When in weak inversion the drain current is dominated by diffusion and has a exponential relationship to the overdrive voltage and is given by equation (2.5) [11]. Keep in mind that  $V_{ds}$  is still sufficiently large enough to keep the transistor in active region.

$$I_D \cong I_{D0} \left(\frac{W}{L}\right) e^{\left(\frac{qV_{eff}}{nkT}\right)}$$

(2.5)

Where  $I_{D0}$  is given by (2.6) [11],

$$I_{D0} = (n-1)\,\mu_i C_{ox} \left(\frac{kT}{q}\right)^2 \tag{2.6}$$

and n is given by (2.7)

$$n = \frac{C_{ox} + C_{j0}}{C_{ox}} \approx 1.5 \tag{2.7}$$

n is often referred to as the slope factor. When in weak inversion it is possible to obtain useful drain currents in the magnitude of pico amperes [19] due to negative  $V_{eff}$ . This is not possible in strong inversion, as drain currents needs to be large enough to dominate the leakage currents.

By differentiating the drain current with respect to  $V_{gs}$  we obtain the transconductance  $g_m$ . The transconductances in strong and weak inversion is given in equations (2.8a) and (2.8b) respectively.

$$g_m = \frac{\delta I_D}{\delta V_{gs}} = \sqrt{2\mu_i C_{ox} \left(\frac{W}{L}\right) I_D}$$

(2.8a)

$$g_m = \frac{\delta I_D}{\delta V_{gs}} = \left(\frac{q}{nkT}\right) I_{D0} \left(\frac{W}{L}\right) e^{\left(\frac{qV_{eff}}{nkT}\right)} = \frac{qI_D}{nkT}$$

(2.8b)

By remembering equation (2.3) for the transitional frequency we see that the transconductance tells us the transistors ability to drive a load. By relating the transconductance to drain current, we get a design parameter that gives us a measure of how efficient a transistor translates current, or power if you like, into transconductance. This relation is known as the  $\frac{g_m}{I_D}$  ratio and has been recognised as a highly efficient parameter for designing analog circuits [20].

$$\frac{g_{m,strong}}{I_D} = \frac{\sqrt{2\mu_i C_{ox} \left(\frac{W}{L}\right) I_D}}{I_D} = \frac{\sqrt{2\mu_i C_{ox} \left(\frac{W}{L}\right)}}{\sqrt{I_D}}$$

(2.9a)

$$\frac{g_{m,weak}}{I_D} = \frac{\frac{qI_D}{nkT}}{I_D} = \frac{q}{nkT}$$

(2.9b)

From equation (2.9b) it can be seen that in weak inversion the transconductance is constant and maximised for a given constant current. When moving towars strong inversion we see from equation (2.9a) that the  $\frac{g_m}{I_D}$  ratio decreases with the square root of  $I_D$ . The transition frequency can also be expressed as  $f_T \approx \frac{3\mu_i V_{eff}}{4\pi L^2}$  and the overdive voltage  $V_{eff} \approx \frac{2I_D}{g_m}$  [11]. Substituting  $V_{eff}$  into  $f_T$  results in equation (2.10).

$$f_T \approx \frac{6\mu_i I_D}{4\pi L^2 g_m} \tag{2.10}$$

Equation (2.10) tells us that even though  $\frac{g_m}{I_D}$  is maximised in weak inversion it is not very applicable for high frequencies.

Looking at the intrinsic gain in equation (2.1), defining the output resistance  $r_o \approx r_{ds}$  which is given by equation (2.11), the intrinsic gain can be expressed by equation (2.12). These equations show that transistors with long channels operated in weak inversion yields highest achievable dc–gain.

$$r_{ds} = \frac{1}{\lambda I_D} = \frac{L}{(L\lambda) I_D} \tag{2.11}$$

$$A_{i,dc} = -\frac{g_m L}{(L\lambda) I_D} \tag{2.12}$$

For  $V_{DS} < V_{eff}$  we operate the transistor in triode region, and in this region the drain current varies with  $V_{ds}$ . For very low  $V_{ds}$  the triode region is often called *linear region* due to its approximately linear relationship between drain current and  $V_{eff}$ . In the linear region the drain current is given by equation (2.13). This operation region is often used when using a transistor to model a voltage controlled resistor capable of achieving approximately constant high resistance.

$$I_D \cong \mu_i C_{ox} \left(\frac{W}{L}\right) \left(V_{eff} V_{DS} - \frac{V_{ds}^2}{2}\right)$$

(2.13)

An approximation of the resistance when operating the transistor in linear region is given by equation (2.14)

$$R_{ds} = \frac{V_{ds}}{I_D} = \frac{1}{\mu_i C_{ox} \left(\frac{W}{L}\right) V_{eff}}$$

(2.14)

#### 2.2.2 Threshold voltage

From section 2.2 we saw that transistor operation varies with the inversion level of the channel. This inversion level was defined by  $V_{gs}$  and its relation to  $V_{tn}$ , and the borders between weak, moderate and strong inversion are not abrupt, but changing gradually. Therefore, these inversion border definitions are very approximate, and not very well defined. One of the reasons for this is that opposite to  $V_{gs}$ ,  $V_{tn}$ is not a well defined voltage applied to the transistor, but a parameter based on measurements. Often, measurements of threshold voltage is done by looking at drain current versus  $V_{gs}$  relationships, but other techniques exist, and therefore threshold voltage may vary with the techniques applied for measuring it [5]. The threshold voltage is inherent to the transistor, and is decided by physical proporties. Therefore the threshold voltage can be engineered by manipulating the physical properties of the transistor such as gate metal, channel doping, oxide thickness and pocket implants. Based on these physical quantities one can derive analytical expressions for the threshold voltage, whereas the most famous is given in equation (2.15).

$$V_{tn} = V_{t0} + \gamma (\sqrt{V_{SB} + |2\Phi_F|} - \sqrt{|2\Phi_F|})$$

(2.15)

In 2.15,  $\Phi_F$  is the fermi potential of the body given by

$$\Phi_F = -\frac{kT}{q} \ln\left(\frac{N_A}{n_i}\right) \tag{2.16}$$

where  $n_i$  is the carrier consentration of intrinsic silicon,  $N_A$  is the substrate doping and  $\frac{kT}{q}$  is the temperature dependant potential. When the voltage drop from channel to substrate is equal to two times the fermi fotential, the electron concentration in the channel is equal to the hole concentration in the subtrate and is often used as a definition of when a channel is inverted.  $V_{t0}$  is the threshold voltage when  $V_{SB} = 0$ .  $\gamma$  represents the *body-effect factor* and is shown in equation 2.17

$$\gamma = \frac{\sqrt{2qN_AK_s\epsilon_0}}{C_{ox}} \tag{2.17}$$

$K_s$  is the relative permittivity of silicon,  $N_A$  is the substrate doping, q is the charge of an electron and  $\epsilon_0$  is the permittivity of free space. The *body-effect factor* models the capacitive coupling between the substrate and the channel. From equation (2.15) it can be seen that for  $V_{sb} \neq 0$  the threshold voltage will be modulated as a result of the body effect. Higher substrate doping results in higher capacitive coupling and the voltage potential applied to the bulk has greater influence on the threshold voltage. In BULK CMOS the only insulation between channel and substrate is that formed by the depletion region of their pn-junction, and the voltage that can be applied to the bulk is limited by the reverse biased diode formed by the pn-junction. It should be noted that the capacitive coupling between channel and substrate in BULK CMOS is highly nonlinear and changes with the voltage applied to the bulk as the width of the depletion region changes [11]. In FDSOI, this capacitive coupling is stronger and more reliable as the channel is insulated from the substrate, or well, by a layer of insulating oxide [13, 21, 22]. Equations (2.18) (2.19) (2.20) show the analytic expressions describing the theshold voltage of the FDSOI simulation models used in this project and is listed in the documentation of the design kit.

$$V_{t0} = \frac{1}{1 + (1 - n_{eq}) \cdot (C_{ic} - 1)} (n_{eq} \cdot \Phi_T^* \cdot \ln\left(\frac{2n_{eq} \cdot C_{ox} \cdot \Phi_T^*}{q \cdot n_i \cdot T_{si}}\right) + (n_{eq} - 1) \cdot V_{FBB,sub} + V_{FB} + 2n_{eq} \cdot \Phi_T^*) \quad (2.18)$$

$\Phi_T^*$  is a complimentary to absolute temperature dependant potential including the thermal voltage  $\frac{kT}{q}$ .  $T_{si}$  is the silicon channel thickness,  $V_{FB}$  and  $V_{FBB,Sub}$  are the flat-band voltages of the metal gate and silicon substrate respectively.  $V_{FB}$  corresponds to an initial potential difference between the metal gate and the silicon channel due to a difference in work functions.  $V_{FBB,sub}$  corresponds to an initial potential difference between the silicon channel due to their difference between the substrate and the silicon channel due to their different work functions. Engineered work–functions, which decide flat–band voltages, are one of the main components to set the threshold voltage, and is done by a metal gate stack of different materials [13, 22, 23]. There is also a flat-band voltage influencing the bulk threshold (2.15, which is between the metal gate and the silicon channel [11].

$$V_{ts} = V_{t0} + \frac{(1 - n_{eq}) \cdot C_{ic}}{1 + (1 - n_{eq}) \cdot (C_{ic} - 1)} \cdot V_{bs}$$

(2.19)

$$V_{tn} = V_{ts} - \Delta V_g \tag{2.20}$$

$\Delta V_g$  is the drain induced barrier lowering.  $n_{eq}$  is the capacitive divider for the gate, silicon and buried oxide capacitances, also known as the slope factor, and is given in equation (2.21).

$$n_{eq} = 1 + \frac{C_{si}C_{box}}{C_{ox}\left(C_{si} + C_{box}\right)}$$

(2.21)

In (2.19), we see that the second term describes the body–effect of FDSOI–transistors describing the influence of  $V_{bs}$  on the threshold voltage.  $C_{ic}$  is a capacitive coupling factor from substrate to the interface of the channel.  $n_{eq}$  is given in equation (2.21) where  $C_{box}$ ,  $C_{si}$ ,  $C_{ox}$  is the back gate oxide, silicon channel and gate oxide capacitances respectively [22]. Higher back–plane doping will increase  $C_{box}$  and  $C_{si}$ , resulting in a higher body–effect [21, 22]. Back–plane doping is done by creating a doped well in the substrate with distinct doping concentrations. Figure 2.4

show a simplified cross section of the structure in FDSOI low threhold LVT-devices. Using an N-well for the NMOS and P-well for the PMOS-transistor helps lowering the threshold voltage. By applying a voltage to the P or N-well via the bulk terminals marked B, you will modulate the threshold voltage according to equation 2.19, which is a technique called body biasing.

Figure 2.4: Cross section showing the physical structure of an UTBB FDSOI transistor implemented with triple well.

There are two types of body biasing one usually speaks about, forward body biasing FBB and reverse body biasing RBB. FBB is apply a positive voltage to the bulk connection, which lowers the threshold voltage. This will increase the transistors operational frequency, but it will suffer from more leakage. RBB is the opposite, namely applying a negative voltage to the bulk to increase the threshold voltage. RBB reduces leakage at cost of lower operational frequency. The wells in which the devices lies puts restraints on the voltage-range one can apply to the bulk. For example for LVT-devices, if both NMOS and PMOS lies in the same deep n-well, there will be formed a diode in the pn-junction between the PMOS p-well and NMOS nwell. There will also be a diodes formed between the PMOS p-well and its isolating deep n-well, and between deep n-well of both devices to the p-type substrate. These scenarios are depicted in figure 2.4. The body bias voltage-range is therefore limited to voltages that don't cause forward biasing of the diodes in one end of the range, and their breakdown voltage in the other end. Well-diodes becomes forward biased around 200-300mV, whereas the breakdown voltage is approximately 3V[13]. Biasing beyond these limitations may cause significant leakage.

### 2.3 OTAs

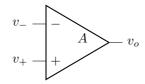

Amplifiers are one of the most common circuit implementations in analog integrated circuits. Amplifiers are key components in signal paths to maintain, or increase, the integrity of signals containing information. Because of the inherent properties of MOSFET-transistors discussed in section 2.2, they are favourable devices when designing small and efficient integrated amplifiers. Section 2.2 explained the intrinsic gain stage, which is also identical to a typical amplifier topology; the common source amplifier. This topology is single-ended, and the ground connection is common to both input signal, supply and output signal. This can be disadvantageous as the output voltage may not only depend on the input signal, but will also follow the supply voltage. This means that ripples and noise in the supply voltage will appear at the output of the amplifier [17]. To circumvent this problem, one can use differential amplifiers. Imagine if you have two identically matched common source stages, then the same ripples and noise will occur at the output of both stages. If you subtract one output from the other, these unwanted effects will be removed from the overall output. A schematic symbol of a differential to single-ended amplifier is shown in figure 2.5.

Figure 2.5: Differential to single-ended amplifier.

The output of this amplifier can be expressed as in equation (2.22), where A is the amplifier gain.

$$v_o = A \left( v_+ - v_- \right) \tag{2.22}$$

As we see in equation (2.22), all signals common between  $v_+$  and  $v_-$  will be removed and only the difference will be amplified. Therefore signals applied to the amplifier needs to be differential, signals on input  $v_-$  needs to be phaseshifted with respect to  $v_+$ . This section will present two common building blocks for realising differential amplifiers which are also central in this project.

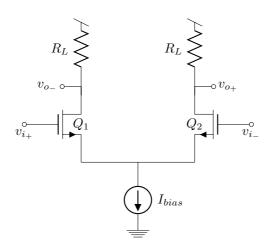

#### 2.3.1 Differential input stage

A differential input stage with MOSFET-transistors loaded by  $Z_L$  is shown in figure 2.6.

The small signal analysis of the circuit in figure 2.6 is found in every textbook concerning design of analog integrated circuits and will only be summarised shortly [11, 17]. Because of symmetrical branches there will be  $\frac{I_{bias}}{2}$  in each branch, and the small signal gain of the differential input stage at low frequencies is similar to that of a common source stage and is seen in equation (2.23).

Figure 2.6: Differential input stage

$$A_{0} = \frac{\left(v_{o_{+}} - v_{o_{-}}\right)}{\left(v_{i_{+}} - v_{i_{-}}\right)} = g_{m}\left(r_{o}||R_{L}\right)$$

$$(2.23)$$

The load  $R_L$  is often realised by an active load, such as a current mirror.

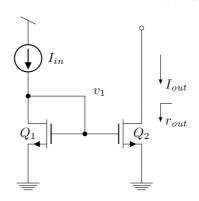

#### 2.3.2 Current mirrors

Figure 2.7 show a simple current mirror with NMOS-transistors, chosen because most equations in this chapter is based on NMOS-operation for simplicity. A current mirror is characterised by a relatively low input impedance,  $\frac{1}{g_{m_1}}$ , and a high output impedance,  $r_{out} = r_{ds_2}$ , which is given by equation (2.11).

Figure 2.7: A CMOS current mirror.

By assuming that both  $Q_1$  and  $Q_2$  are in the active region and strong inversion

their drain currents can be described by the square law voltage-current relationship given in (2.4). As  $V_{gs_{Q_1}} = V_{gs_{Q_2}} = v_1$ , the relationship between  $Q_1$ s drain current,  $I_{in}$ , and  $Q_2$ s drain current  $I_{out}$  is expressed in equation (2.24).

$$\frac{I_{out}}{I_{in}} = \frac{\left(\frac{W}{L}\right)_2}{\left(\frac{W}{L}\right)_1} = \frac{S_2}{S_1}$$

(2.24)

This equation show that the output current is related to the input current by aspect ratios, and is decided solely by transistor geometries [11, 17]. The transistor aspect ratios  $\frac{W}{L}$  are often abbreviated by S.

One way of using the current mirror is to load the differential stage shown in figure 2.6 in order to convert to a single ended output. The current mirror needed to load the differential input needs to be realised by PMOS-transistors. Also the bias voltage  $I_{bias}$  from figure 2.6 is often fed to the differential input from the current source using current mirrors.

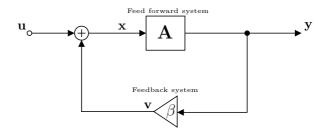

#### 2.4 Feedback

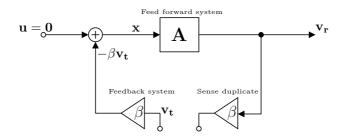

Feedback is a central concept in electronics and crucial to this project. Feedback is often applied when regulation of some system is needed, and can be either positive or negative. Negative feedback is when a part of the output is removed from the input, making some correction. Positive feedback is when a part of the output is added to the input. Figure 2.8 show a block diagram of a general feedback system. In figure 2.8,  $\mathbf{u}$  is the input of the whole system,  $\mathbf{x}$  is the input to the feed forward

Figure 2.8: General feedback system

system, **A** represents some gain in the *feed forward system*,  $\beta$  is the feedback factor of the feedback system, **v** is the feedback signal and **y** is the output of the whole system. If **v** is negative it will be subtracted from the input, and we have negative feedback. A feedback system is often characterised by its *closed loop gain* and *open loop gain*. To find the closed loop gain for the general feedback system in figure 2.8 we can find its transfer function  $\frac{\mathbf{y}}{\mathbf{u}}$ . Let us consider the feedback as negative, namely the signal **v** is negative. The output is sensed by the feedback system, and sent back to the input. This gives  $\mathbf{v} = \beta \mathbf{y}$ . As  $\mathbf{v}$  is negative, we can write  $\mathbf{x} = \mathbf{u} - \mathbf{v} = \mathbf{u} - \beta \mathbf{y}$ . With  $\mathbf{x}$  being the input to the feed forward system,  $\mathbf{y} = \mathbf{A}\mathbf{x}$ , we get  $\mathbf{y} = \mathbf{A}(\mathbf{u} - \beta \mathbf{y})$ . Solving this equation results in the closed loop gain of the general feedback system and is given in equation (2.25)

$$\frac{\mathbf{y}}{\mathbf{u}} = \frac{\mathbf{A}}{1 + \beta \mathbf{A}} \tag{2.25}$$

Figure 2.9 show the necessary configuration for calculation of open loop gain. To calculate the open loop gain, or loop gain, we set all independent signal sources to our system to zero, which in our case means  $\mathbf{u} = 0$ . Then we break the loop, and apply a test signal  $\mathbf{v}_t$  at the point were the loop was broken, and observe the returned value  $\mathbf{v}_r$  at the output of the feed forward system. In practice the feedback network will have finite I/O–impedances, so the output should also be loaded by the same impedance as seen at the input of our test signal. This is illustrated with the *sense duplicate* block in figure 2.9 which is a duplicate of the feedback system itself. However, for out calculation now, we will assume an ideal network, so that the sense duplicate does not load the output of our system.

Figure 2.9: Configuration for calculating open loop gain of a feedback system

From figure 2.9 we see that  $\mathbf{v_r} = \mathbf{A}\mathbf{x}$ . As we also assume negative feedback in this case, we get  $\mathbf{x} = -\beta \mathbf{v_t}$ . The resulting expression for loop gain is given in equation (2.26).

$$LG = -\frac{\mathbf{v}_r}{\mathbf{v}_t} = \beta \mathbf{A} \tag{2.26}$$

Consider an amplifier with finite gain A. Whithout feedback, amplifier characteristics such as gain, I/O-impedances and linearity may be very unpredictable. Amplifiers are built using MOSFET-transistors, which are inherently nonlinear devices suffering from unpredictabilities due to many different sources of variations which will be explained later. By using feedback, the amplifiers performance can be stabilised and improved. If LG >> 1, equation (2.25) can be simplified to  $\frac{1}{\beta}$ , which may be more predictable than the amplifier gain if  $\beta$  is set by passive elements. This will often reduce the gain but also it make the gain more constant, reducing nonlinear distortion. By choosing the right feedback topology, one can control the input and output impedances, and also extend the bandwidth of the amplifier.

When using feedback, one should always be concerned by the stability of the feedback system. Negative feedback will always be stable. However, if the feedback network is frequency dependent there might be a phase shift turning the negative feedback positive, resulting in unstable feedback. By looking at figure 2.9 and equation (2.26), one can see that if the loop gain LG becomes negative it will be added to the input, and not subtracted. In this case the feedback will be postive and potentially unstable, which may cause oscillations. Stability of such a system with positive feedback can be obtained by keeping the loop gain below unity. These observations form the base of two properties that describes the stability of a frequency dependant system, namely phase- and gain margin. One can determine if a system is stable based on the closed loop transfer function, and if its poles and zeros are located in the left half plane of the s-plane. However, this may often be complex to analyse. The more simple method determines the phase margin PM based on the loop gain frequency respons. For a frequency dependent loop gain  $LG(s) = A(s)\beta$ , the system is stable if the open loop phase response  $\angle LG(\omega_t) > -180^\circ$ , where  $\omega_t$  is the unity gain angular frequency of the loop gain. This term results in the phase margin definition (2.27).

$$PM = \angle LG\left(\omega_t\right) + 180^{\circ} \tag{2.27}$$

Phase margin defines the additional phase shift needed to obtain instability at the unity gain frequency.

Gain margin (GM) is found where the open loop phase shift has reached  $-180^{\circ}$ ,  $\angle LG(\omega) = -180^{\circ}$  and can be defined as (2.28).

$$GM = 0 - LG(\omega_{-180^{\circ}}) \tag{2.28}$$

Gain margin tells us how much the signal is dampened at the point in frequency where the feedback becomes positive. If the gain margin is positive, the loop gain is less than one and we still have a stable system.

### 2.5 Sources of variation in integrated circuits

Transistor technology is continuously scaling down in size to fit more devices into a single chip, and thus achieve more processing power per area resulting in increased performance for modern integrated circuits. There are three main goals motivating transistor scaling: 1) Decreasing transistor gate delay, and thereby increasing the operating frequency; 2) Increasing transistor density; 3) Reducing the energy per operation in order to save power [7, 8]. As a result of technology scaling, one can reduce the supply voltage without lowering the operation frequency, and have a quadratic reduction in power. However, certain limitations arise as process technology reaches atomic levels, and one of the main challenges is variation in the threshold voltage [5]. The threshold voltage does not scale proportionally to transistor size and supply voltage, causing small variations in threshold votage to result

in a large impact on performance. For example, by looking back at equation (2.5) one can see that even with  $V_{gs} = 0$  there will be some leakage current exponentially dependant on  $V_{tn}$ . This leakage current increases with decreasing  $V_{tn}$ , which will increase the static power consumption. Along with technology scaling there are continuous innovation being done in the manufacturing processes to overcome the challenges of variation, however the manufacturing can never be completely accurate. Therefore one of the biggest source of these variations may be in the manufacturing process. As a transistors parameters are solely decided by physical quantities of which today are in the sizes of a few nanometers it is not possible to manufacture these 100% precisely. Other variations may origin from degradation of the device over time, or from temperatures influencing the characteristics of the materials in which the device lies.

#### 2.5.1 Process variation

Process variations are variations occurring due to imperfect manufacturing. These variations are spatially correlated and are common to devices within the same area. This means you may observe different process variations between wafers, but also between areas within the same wafer. Process variations occur because it is impossible to maintain the same conditions, e.g. temperature, silicon purity, etc. when manufacturing integrated circuits. Process variations are gaussian distributed, and the expected transistor behavior can be defined as the mean value. Random variations can be seen as fluctuations around this mean, while process variations will change the mean value itself. Random variations will be covered in the next section. To model process variations the production foundries provide different simulation models of the transistors based on measurements to model both typical and various worst case scenarios known as corners. This give circuit designers the possibility to create robust designs capable of maintaining performance over different process corners. Often one may have to add extra overhead in the form of auxiliary circuits to handle these variations, or one must increase device sizes which increases area and may increase power consumption. For this project there will be utilised corner models provided for commercially available 28nm UTBB FDSOI transistors to model process variation. Figure 2.10 depict the spread in saturation current between the different corners, where T is for typical, S is for slow, F is for fast and A is for alternative. The first letter in each denomination describes NMOS corners and the second is for PMOS.

#### 2.5.2 Random process variation

Random process variation, also known as mismatch, is variation between two identically matched and identically used devices fabricated under the same conditions. As the performance of analog integrated circuits is often based on ratios between devices, it is very important to characterise how mismatch affect these ratios. Two

Figure 2.10: Illustration of spread between corners.

of the most important sources of mismatch are threshold voltage variation and  $\beta$  variation, with  $\beta = \mu_i C_{ox}$ . Random variation is gaussian distributed and the variance in threshold voltage  $V_{t0}$  and  $\beta$  for two identical devices is given in equation (2.29a) and (2.29b) respectively.

$$\sigma^2 (V_{t0}) = \frac{A_{V_{t0}}^2}{WL} + S_{V_{t0}}^2 D^2$$

(2.29a)

$$\frac{\sigma^2(\beta)}{\beta^2} = \frac{A_{\beta}^2}{WL} + S_{\beta}^2 D^2$$

(2.29b)

In (A.9), D is the distance between the two identical devies, W and L are device dimensions and A and S are proportionality constants [11, 24]. Two very common building blocks in analog integrated circuits, and also this project, are current mirrors and differential input pairs. Current mirrors have the same  $V_{gs}$ , and at zero input the differential pair also have equal  $V_{gs}$ . Because of being biased with the same gate-source voltage, current mismatch in current mirrors and differential pairs can be expressed by equation (2.30).

$$\left(\frac{\sigma\left(\Delta I_D\right)}{I_D}\right)^2 = \left(\frac{g_m}{I_D}\right)^2 \sigma^2\left(\Delta V_{t0}\right) + \frac{\sigma^2\left(\beta\right)}{\beta^2} \tag{2.30}$$

By assume closely spaced devices,  $D \approx 0$ , and inserting (A.9) in (2.30) we obtain an expression for current mismatch in a current mirror (2.31).

$$\left(\frac{\sigma\left(\Delta I_{D}\right)}{I_{D}}\right)^{2} = \frac{1}{WL} \left[A_{V_{to}}^{2} \left(\frac{g_{m}}{I_{D}}\right)^{2} + A_{\beta}^{2}\right]$$

(2.31)

From equation (2.31) we see that mismatch in threshold voltage is the dominant, and that current mismatch is largest when transistors are operated in weak inversion, i.e. high  $\frac{g_m}{I_D}$ . So, in order to achieve high accuracy in current mirrors, operating devices in strong inversion is prefered at the cost of a higher saturation voltage. Whereas for a differential input pair, the mismatch is measured as an offset between the inputs and is given by equation (2.32).

$$\sigma^{2}(V_{OS}) = \frac{\sigma^{2}(\Delta I_{D})}{g_{m}^{2}} = \frac{1}{WL} \left[ A_{V_{t0}}^{2} + \left(\frac{I_{D}}{g_{m}}\right)^{2} A_{\beta}^{2} \right]$$

(2.32)

And from this equation it can be seen that by biasing the differential input pair with a current and operation the transistors in weak inversion, the offset variance due to variations in  $\beta$  is reduced and  $V_{t0}$ -variations becomes dominant. The threshold voltage variations is therefore very important in analog circuits.

#### 2.5.3 Temperature variation

Non-ideal conditions of circuit manufacturing is not the only source of variation that may seriously impact circuit performance. Characteristics inherent to the materials that transistors are made of are dependent on temperature, where two of the most important parameters for transistor operation are carrier mobility  $\mu$ and threshold voltage  $V_{t0}$ . As transistor density on a single die has increased dramatically, the heat generation becomes severe and may impact performance dramatically [7, 8]. From section 2.2 it is clear that these two parameters are involved in almost all aspects of analog circuit performance. Both carrier mobility and threshold voltage decrease with increasing temperature, and their dependence of temperature is modelled by equations (2.33a) and (2.33b) respectively.

$$\mu_0(T) = \mu_0(T_0) \left(\frac{T_0}{T}\right)^{k_1}$$

(2.33a)

$$V_{t0}(T) = V_{t0}(T_0) + \alpha_{V_{t0}}(T - T_0)$$

(2.33b)

In (2.33),  $T_0$  is the reference temperature,  $k_1$  is a fitting constant in the range of 1-2 in room temperatures, T is the actual temperature and  $\alpha_{V_{t0}} = \frac{\delta V_{t0}}{\delta T}$  is a negative constant [25, 26].

# 3 Design

The motive behind the circuitry designed in this project is to improve stability and performance of some main functionality carried out by more vital circuitry. Therefore this additional circuitry can be considered overhead, where stability and increased performance is traded for increased power consumption and area. As area has a tendency to increase with complexity, low power and low complexity has been the priority when designing these circuits. All circuits were designed in a commercially available 28nm–FDSOI technology, and circuit design was performed with Cadence Virtuoso. As leakage currents in the bulk 2.2.2 are critical to the performance of bulk biasing, a layout was made of both amplifier and ring oscillator to have an extended verification of these effects. These layouts were made in correspondence with design rules provided by the manufacturer, and passed Layout versus Schematic (LVS) test and Design Rule Check (DRC) performed with Calibre from Mentor Graphic.

## 3.1 Compensation of process and temperature variations

From section 2.5.1 we defined process variations as fluctuations of a mean value that represents transistor behavior, e.g. threshold voltage. When adding temperature variations to the corners representing worst case mean values, circuits are really at the edge of their operational limit. In this section, we will address these types of variations, and try to compensate these variations so that all corners operates close to the typical mean value for a wide temperature range. As we see in equation (3.20), ring oscillators depend strongly upon paramaters such as threshold voltage. From equation (2.33b) we know that the threshold voltage change with temperature. Section 2.2.2 also demonstrate that the threshold voltage may be sensitive to process variations, as it is based on physical properties in the transistor. We can therefore expect that the oscillation frequency of a ring oscillator will change dramatically over different process corners and temperature. Equation (2.19) show that the threshold voltage in FDSOI-transistors can be modulated by applying voltage to the bulk of the transistor  $V_{bs}$ . Therefore, in this first section we will utilise body biasing to compensate for process and temperature variations in a ring oscillator.

#### 3.1.1 Variation sensing and compensation

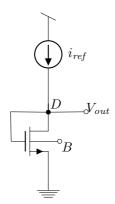

Variation sensing is done by monitoring the voltage drop over a diode connected mosfet transistor. A diode connected transistor is shown in figure 3.1, and is configurated as a transistor with its gate and drain tied together while source is shorted to ground, which gives  $V_{GS} = V_{DS} = V_{out}$ . This is a quite common configuration for generation of reference voltages [11].

Figure 3.1: Diode connected transistor.

The voltage drop over the diode connected transistor is decided by the reference current applied to it and intrinsic parameters of the transistor, where more current translates to more voltage. An expression for the voltage over the diode in weak inversion is given by equation (3.1) and is derived from the current equation of a transistor in weak inversion given by (2.5). As  $V_{eff} = V_{gs} - V_{tn}$ , the drain current equation is solved for the diode connected transistor in figure 3.1 with respect to  $V_{qs}$  and we obtain

$$V_{gs} = V_{out} = V_{tn} + nV_T \ln\left(\frac{I_{ref}}{I_{D0}\left(\frac{W}{L}\right)}\right)$$

(3.1)

This expression (3.1) show the output voltage dependence on drain current and threshold voltage. n is given in equation (2.21) and  $V_T = \frac{kT}{q}$  is the thermal voltage. If the diode connected transistor is biased in strong inversion, we can solve equation (2.4) and get the following expression for  $V_{out}$  (3.2).

$$V_{gs} = V_{out} = V_{tn} + \sqrt{\frac{2i_{ref}}{\mu_n C_{ox} \frac{W}{L}}}$$

(3.2)

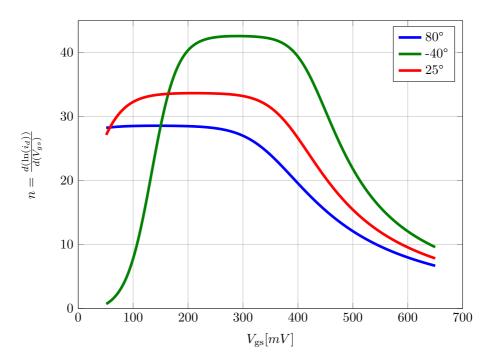

However, when sensing the threshold voltage, a reference current  $i_{ref}$  is chosen so that  $V_{eff} = 0$  and the voltage voltage drop over the diode is  $V_{out} \approx V_{tn}$  at room temperatures. This means that the diode connected transistor can be assumed to operate in moderate inversion, where none of the equations above (3.1) (3.2) are valid. Figure 3.2 show a plot of the subthreshold slope  $n = \frac{d(\log(i_d))}{d(V_{gs})}$  versus gate–source voltage.

Figure 3.2: Derivative of logarithmic drain current versus  $v_{as}$

The plateau where n is approximately constant depicts weak inversion operation, where the current exhibits an exponential relationship to the voltage. From simulations, threshold voltage for an LVT–NMOS is shown to be between approximately 350mV-430mV depending on transistor size. By looking at figure 3.2 we see that in this voltage range, transistor have just exited weak inversion, and the assumption of moderate inversion seems accurate. There are no very accurate equations, that the author is aware of, modelling transistor behavior in moderate inversion. Existing equations for moderate inversion are interpolations between weak and strong inversion operation. One equation for  $V_{gs}$  is given in [27] and is an interpolation between equations for weak and strong inversion based on the EKV–transistor model assuming forward current. This approximate interpolated equation describing  $V_{out}$  for the diode connected transistor is given in equation (3.3).

$$V_{out} = V_{tn} + 2V_T \ln \left( e^{\sqrt{\frac{I_{ref}}{2n\beta_n V_T^2 \left(\frac{W}{L}\right)}}} - 1 \right)$$

(3.3)

In (3.3),  $\beta_n = \mu_n C_{ox}$ . In order to get  $V_{out} \approx V_{tn}$ , the diode must be biased with a current  $I_{ref}$  such that the second term in equation (3.3) is cancelled. This occurs for a current such that  $e^{\sqrt{\frac{I_{REF}}{2n\beta_n V_T^2} (\frac{W}{L})}} = 2$ , as  $\ln(1) = 0$ , which leads to an expression

for the reference current in (3.3) needed to achieve  $V_{out} \approx V_{tn}$ , and is given in equation (3.4).

$$i_{ref} = 2\ln\left(2\right)^2 n\mu_n C_{ox}\left(\frac{W}{L}\right) V_T^2$$

(3.4)

Temperature dependencies for  $V_{tn}$  and  $\mu_n$  is given in section 2.5.3, and they are both decreasing with temperature. Equation (2.33a) give the following expression for the temperature dependency of mobility,  $\mu_0 (T_0) \left(\frac{T_0}{T}\right)^{k_1}$ , and from [28] we have that the factor  $k_1 \approx 1.4$  for SOI-transistors with thin silicon channels. It can therefore be assumed that the temperature dependency of the current in equation (3.4) is positive, and that for temperatures  $\pm 60^{\circ}C$  around room temperatures a PTAT current bias can be applied to the diode connected transistor to approximately cancel the second term in equation (3.3).

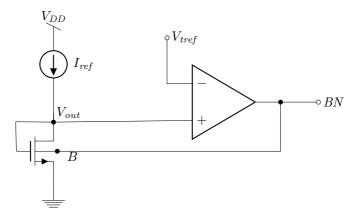

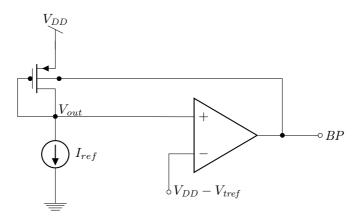

The voltage  $V_{out}$  will be measured by an amplifier as shown in figure 3.3 and compared to a reference voltage  $V_{tref} = V_{tn}$ , that should be equal to the typical case threshold voltage. In an ideal scenario with no variations, the output voltage is equal to the threshold voltage  $V_{out} = V_{tref}$ , and the output voltage of the amplifier is BN = 0. If the threshold voltage suffers from variations, leading to  $V_{out} \neq V_{tref}$ , the amplifiers output voltage will change in order to modulate the threshold voltage via the feedback loop through the diode connected transistors bulk according to equation (2.19).

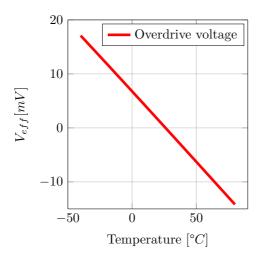

Figure 3.4 show the change in  $V_{\text{EFF}}$  for the diode connected transistor, with threshold voltage compensation, from  $-40^{\circ}C$  to  $80^{\circ}C$ . Reference current  $I_{ref}$  is constant and adjusted so that  $V_{out} \approx V_{tn} \Rightarrow V_{eff} \approx 0$  at room temperature. The plot clearly show that  $V_{eff}$  decreases with temperature, and by assuming that the threshold voltage is compensated for temperature variations, it is reasonable to believe that the second term in equation (3.3) decreases with temperature for constant  $I_{ref}$ . From this we can expect that a reference current  $I_{ref}$  as given in (3.4), which is increasing with temperature, will approximately cancel the second term in (3.3) in agreement with the previous discussion.

Assuming the bias current is correctly adjusted as discussed above, the voltage BN at the amplifier output will be able to compensate for approximately all process and temperature variations influencing the threshold voltage of transistors matched in size with the diode connected transistor of figure 3.3. This compensation scheme

Figure 3.3: NMOS threshold compensation circuit. [29]

may therefore be efficient in systems containing a large number of matched transistors, such as digital systems, and its efficiency will be tested out on a thirteen stage inverter based ring oscillator. Figure 3.5 depicts the circuit model for compensating variations in PMOS-transistors.

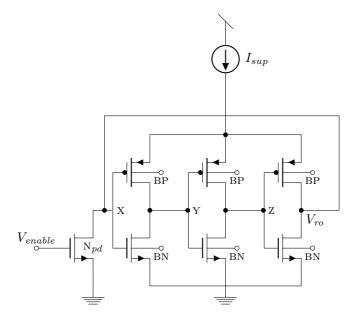

### **3.2 PTAT** Current Reference

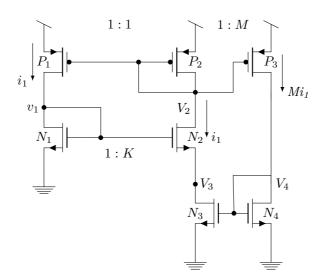

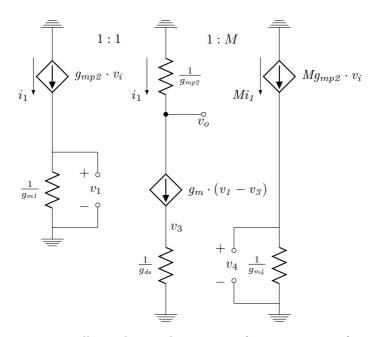

To realise a low power current reference capable to supply the compensation circuitry with currents in the magnitude of nano amperes it is favourable to use transistors operating in weak inversion as current sources. A simple architecture achieving this with weak inversion transistors was presented already in 1977 [19]. However, this design relies on a resistor to degenerate the source of a weak inversion transistor. As the system presented in this project should focus on keeping circuit area at a minimum, the resistor was replaced by a transistor operating in the triode region. This resistorless current reference architecture was presented earlier in [30] in is shown in figure 3.6.

In figure 3.6 the PMOS-transistors form current mirros with ratios 1:1 between P2 and P1, and 1:M between P2 and P3. Based on current mirror accuracy given by (2.30), all transistors are saturated and operated in strong inversion, forcing equal currents,  $i_1$ , in all branches multiplied by the mirror ratios according to (2.24). Current mirror transistors N1 and N2 should be operated in weak inversion, with an aspect ratio for N2 that is K-times largen than N1. N3 operates in triode region with a low drain-source voltage and therefore replaces the resistor in [19]. The diode connected transistor N4 is saturated and generates a bias voltage  $V_4$  to keep transistor N3 in triode region.

If we first look at the current reference core and consider N3 as a constant resistor.

Figure 3.4:  $V_{eff}$  dependency on temperature variation with constant  $I_{ref}$ .

We have  $V_{g_{N1}} = V_{g_{N2}} = V_1$  and  $V_{g_{P1}} = V_{g_{P2}}$ . Because N1 and N2 both are in weak inversion their drain current can be described by (2.5), and the source voltage of N2,  $V_3$ , can be expressed as shown in equation (3.5).

$$V_3 = V_T \ln\left(\frac{S_{N2}S_{P1}}{S_{N1}S_{P2}}\right) \approx V_T \ln\left(K\right)$$

(3.5)

This equation (3.5) form the base of the PTAT current reference, as the thermal voltage  $V_T$  is proportional to temperature and multiplied by a constant which is decided by dimensions in the current mirror transistors,  $S_{N1}$ ,  $S_{N2}$ ,  $S_{P1}$  and  $S_{P2}$ . As long as N1 and N2 is kept in weak inversion,  $V_3$  is independent of current level.

Reference current  $i_1$  can now be defined by the resistance that is source degenerating transistor N2. This leads to  $i_1 = \frac{v_3}{R}$ , and with R being the equivalent resistance of transistor N3 in triode region given by equation (2.14)  $i_1$  is given by equation (3.6).

$$i_1 = n\mu_n C_{ox} S_{N3} \left( V_4 - V_{tn} - \frac{n}{2} V_3 \right) V_3 \tag{3.6}$$

Where n is for correction due to low drain-source voltage  $V_3$  over N3 [30]. From this equation we can see that  $V_4$ , which is the voltage over the diode connected transistor N4, decides the equivalent resistance of the triode transistor. This voltage is given by current through N4. This current is mirrored by P2 and P3 and is therefore equal to  $Mi_1$ . N4 is saturated and operating in strong inversion, so its drain current is expressed by the square law equation (2.4) and voltage  $V_4$  can be expressed as follows (3.7).

$$V_4 = V_{tn} + \sqrt{\frac{2Mi_1}{\mu_n C_{ox} S_{N_4}}}$$

(3.7)

Figure 3.5: PMOS threshold compensation circuit. [29]

By inserting this equation and equation (3.5) in (3.6) we obtain a new expression  $i'_1$  in equation (3.8).

$$i_{1}' = n\mu_{n}C_{ox}S_{N3}\left(\sqrt{\frac{2Mi_{1}}{\mu_{n}C_{ox}S_{N4}}} - \frac{n}{2}V_{T}\ln\left(K\right)\right)V_{T}\ln\left(K\right)$$

(3.8)

As we can see, the reference current is now expressed by a bit more complex equation. This comes from adding the network of triode and bias transistors to realise a resistor. From [30] we have a closed form solution for equation (3.8) which is given in equation (3.9).

$$i_1 = n^2 \mu_n C_{ox} V_T^2 K_{eff} \tag{3.9}$$

where

$$K_{eff} = \left(K_2 - 0.5 + \sqrt{K_2 \left(K_2 - 1\right)}\right) \ln^2\left(K\right)$$

(3.10a)

$$K = \frac{S_{N2}S_{P1}}{S_{N1}S_{P2}}, K_2 = \frac{S_{N3}M}{S_{N4}}$$

(3.10b)