# A Fully Differential Front End Charge Sampling Amplifier for Medical Ultrasound Imaging in 28nm FD-SOI Technology

Endre Larsen

Master of Science in Electronics Submission date: June 2015 Supervisor: Trond Ytterdal, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# **Problem Description**

Downscaling of CMOS technology provides opportunities for energy efficient electronic circuits consuming small areas. However the scaled down technology entails challenges in designing analog circuits. New analog circuits must be designed to maintain high performance in scaled down technologies with low supply voltages. The main goal of this thesis is to design a front-end LNA in 28nm FD-SOI CMOS technology for a IVUS system. The amplifier should sample and amplify the signal from a capacitive micromachined ultrasound transducer adding minimum noise and distortion. The thesis should include:

- A fully differential topology.

- Sampling at 64MHz.

- Schematic and layout design in 28nm FD-SOI CMOS technology.

- Verification of performance.

- Comparison with existing attempts.

Assignent given 19. January 2015 Supervisor: Trond Ytterdal, IET Co-supervisor: Carsten Wulff, IET

## Summary

New generations of ultrasound imaging will contain thousands of receive and transmit elements in a single probe. This leads to challenges in analog front-end circuits concerning low power, low noise, low area consumption and high linearity.

This thesis presents the design and analysis of a fully differential charge sampling amplifier, CSA, in 28nm FD-SOI CMOS technology with a capacitive micromachined ultrasonic transducer, CMUT, model as source. The proposed CSA is intended as a frontend readout LNA for IVUS systems interfaced with an ADC for high accuracy digital conversion.

The readout of the CMUT is done by connecting the two CMUT terminals to the positive and negative input nodes of the proposed CSA, reading the current from both terminals and giving a differential input signal to the CSA. This way second harmonic destortion is improved.

A capacitive parasitic extraction is done and results from simulation of the layout with parasitic extraction are presented as final results.

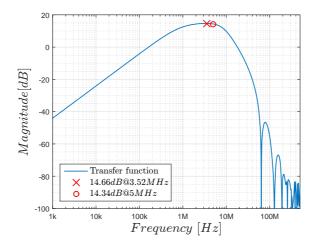

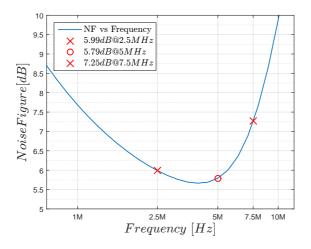

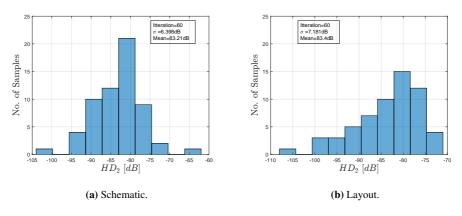

The proposed CSA achieves a bandwidth of 7.9MHz around a center frequency of 5MHz with a gain at centerfrequency of 14.34dB with a CMUT as source and a sampling frequency of 64MHz. High linearity of  $HD_2$ =-83dB, a relatively low power consumption of 110.6 $\mu$ W, an input impedance of 3.1 $k\Omega$  and a noise figure, NF, of 5.79dB was achieved with an area consumption of 39.8×70.3 $\mu$ m<sup>2</sup>.

# Sammendrag

Nye generasjoner av ultralyd avbildnings utstyr vil inneholde tusenvis av mottakere og sender komponenter inne i en ultralyd probe. Dette fører med seg utfordringer i analoge kretser vedrørende lav effekt, lav støy, lavt areal forbruk og høy linearitet.

Denne oppgaven presenterer designet av en fullt differensial ladning samplings forsterker, CSA, i 28nm FD-SOI CMOS teknologi med en kapasitiv mikromaskinert ultrasonic transduser, CMUT. Den foreslåtte CSA er tenkt som en front-end utlesnings lav-støy forsterker for et IVUS system tilkoblet en ADC for høy nøyaktighets digital konvertering.

Utlesningen fra CMUTen blir gjort ved å koble de to terminalene til CMUTen til den negative og positive inngangen til den foreslåtte CSA, slik at strømmen blir lest av fra begge terminalene og dermed gir et differensielt CSA inngangssignal. På denne måten blir andre harmonisk forvrengning forbedret.

En ekstraksjon av parasitisk kapasitanse er gjort og resultater fra simulasjoner av utlegget med disse parasittene er presentert som de endelige resultater.

Den foreslåtte CSA oppnår en båndbredde på 7.9MHz rundt en senterfrekvens på 5MHz med et gain ved senterfrekvens på 14.34dB med en CMUT som kilde og en sampling frekvens på 64MHz. Høy linearitet på  $HD_2$ =-83dB, en relativt lav effektforbruk på 110.6 $\mu$ W en inngangs impedanse på 3.1 $k\Omega$  og en logaritmisk støy faktor på 5.79dB ble oppnådd med et areal forbruk på 39.8×70.3 $\mu$ m<sup>2</sup>.

# Preface

First and foremost I would like to thank my supervisors Professor Trond Ytterdal and post doc. Carsten Wulff. Their deep knowledge of analog design, positive appearence and guidance along this thesis has been of great value for me and made an exiting task even more intriguing.

I would also like to thank my office companions Harald Garvik, Erlend Strandvik and Thomas Hanssen Nornes for their interest in exchanging knowledge and for a good office environment with many laughs.

# Table of Contents

| Pro | oblem   | Description                                       | i    |

|-----|---------|---------------------------------------------------|------|

| Su  | mmai    | 'y                                                | ii   |

| Sai | mmer    | ndrag                                             | iii  |

| Pro | eface   |                                                   | iv   |

| Ta  | ble of  | Contents                                          | vii  |

| Lis | st of T | ables                                             | ix   |

| Lis | st of F | 'igures 2                                         | xiii |

| Ab  | brevi   | ations                                            | xiv  |

| 1   | Intro   | oduction                                          | 1    |

|     | 1.1     | Main Contributions                                | 2    |

|     | 1.2     | Thesis outline                                    | 2    |

| 2   | Theo    | bry                                               | 3    |

|     | 2.1     | IVUS                                              | 3    |

|     | 2.2     | CMOS Transistors                                  | 4    |

|     |         | 2.2.1 Fully Deplated Silicon on Insulator(FD-SOI) | 6    |

|     |         | 2.2.2 Mismatch and Variability                    | 6    |

|     | 2.3     | Amplifier                                         | 7    |

|     |         | 2.3.1 Operation Amplifier                         | 7    |

|     |         | 2.3.2 Class of Operation                          | 8    |

|     |         | 2.3.3 Inverter                                    | 9    |

|     |         | 2.3.4 Fully Differential Amplifier                | 10   |

|     |         | 2.3.5 Biasing                                     | 11   |

|     |         | 2.3.6 Common Mode Feedback                        | 12   |

|   | 2.4      | Dynamic Range                        |

|---|----------|--------------------------------------|

|   |          | 2.4.1 Linearity                      |

|   |          | 2.4.2 Noise                          |

|   | 2.5      | Charge Sampling 17                   |

|   | 2.6      | CMOS Switches                        |

|   | 2.7      | Layout                               |

|   | 2.8      | Figure of Merit                      |

|   | 2.9      | Computer Assisted Design 24          |

|   | 2.10     | Existing Work                        |

| • | <b>T</b> |                                      |

| 3 | -        | logy and Design 27                   |

|   | 3.1      | Specifications                       |

|   | 3.2      | Charge Sampling Amplifier System     |

|   |          | 3.2.1 CMUT model                     |

|   | 2.2      | 3.2.2 Charge Sampling Amplifier      |

|   | 3.3      | Noise Analysis of CSA with CMUT load |

|   | 3.4      | Design Methology                     |

|   |          | 3.4.1 Operational Amplifier          |

|   |          | 3.4.2 Common Mode Feedback Circuit   |

|   | ~ ~      | 3.4.3 Switches                       |

|   | 3.5      | Layout                               |

| 4 | Resu     | lts 45                               |

|   | 4.1      | Test Setup                           |

|   |          | 4.1.1 Small Signal Analysis          |

|   |          | 4.1.2 Large Signal Analysis 46       |

|   | 4.2      | Frequency Response                   |

|   | 4.3      | Biasing Verification                 |

|   | 4.4      | Noise Analysis                       |

|   | 4.5      | Mismatch Performance                 |

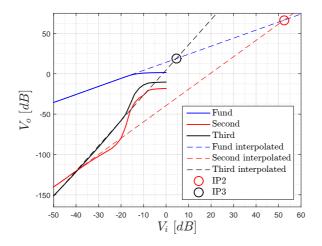

|   | 4.6      | IIP2 and IIP3                        |

|   | 4.7      | Process Variation Performance        |

|   | 4.8      | Ultrasound Pulse Test                |

|   | 4.9      | Results Summary                      |

|   |          |                                      |

| 5 | Disc     | ussion 59                            |

|   | 5.1      | Frequency Response                   |

|   | 5.2      | Noise                                |

|   | 5.3      | Mismatch Performance                 |

|   | 5.4      | IIP2 and IIP3 60                     |

|   | 5.5      | Process Variation                    |

|   | 5.6      | Ultrasound Pulse Test                |

|   | 5.7      | Operating point                      |

|   | 5.8      | Comperison with existing work        |

|   | 5.9      | Topology                             |

|   | 5.10     | Layout                               |

|   |          |                                      |

| 6 | Conclusion         6.1       Further Work                        | <b>65</b><br>66 |

|---|------------------------------------------------------------------|-----------------|

| A | Calculations A.1 Drain-to-Source Feedback Resistor Biasing       | <b>71</b><br>71 |

| B | Transfer function calculation of charge sampler with CMUT model  | 73              |

| С | Testbench         C.1       Ultrasound Pulse model and Waveforms | <b>75</b><br>77 |

| D | VerilogA Sample and Hold                                         | 79              |

| E | Clock Phase Logic                                                | 81              |

# List of Tables

| 3.1 | Specified goals.                                               | 27 |

|-----|----------------------------------------------------------------|----|

| 3.2 | CMUT model values.                                             | 29 |

| 3.3 | Clock signal duration and capcitor size.                       | 33 |

| 3.4 | Sizes of transistors in the OpAmp.                             | 40 |

| 3.5 |                                                                | 42 |

| 4.1 | The noise contributions from different circuit elements        | 48 |

| 4.2 | Mismatch performance.                                          | 49 |

| 4.3 | Performance of process variations.                             | 52 |

| 4.4 | Performance of process variations with adjusted supply voltage | 53 |

| 4.5 | Final results for the CSA                                      | 57 |

| 5.1 | Comparison with existing work.                                 | 62 |

# List of Figures

| 2.1  | Signal path for one transducer element in a IVUS system            |    |  |  |  |

|------|--------------------------------------------------------------------|----|--|--|--|

| 2.2  | A catheter with transducers [13]                                   |    |  |  |  |

| 2.3  | Bulk-CMOS and FD-SOI [16]                                          |    |  |  |  |

| 2.4  | MOSFET inverter                                                    | 9  |  |  |  |

| 2.5  | Inverter class of operation [19]                                   | 9  |  |  |  |

| 2.6  | A differential amplifier and its output with even-order distortion | 10 |  |  |  |

|      | (a) Differential amplifier                                         | 10 |  |  |  |

|      | (b) Output signals with even order distortion                      | 10 |  |  |  |

| 2.7  | MOSFET inverter with drain-to-gate resistor feedback biasing       | 11 |  |  |  |

| 2.8  | Switched-Capacitor CMFB circuit [15]                               | 13 |  |  |  |

| 2.9  | Typical $V_o/V_i$ relationship [22]                                | 15 |  |  |  |

| 2.10 | Noise model MOSFET.                                                | 15 |  |  |  |

| 2.11 | Noise model for a resistor.                                        | 16 |  |  |  |

| 2.12 | Charge sampling circuit and clock phases                           | 17 |  |  |  |

|      | (a) Charge sampling                                                | 17 |  |  |  |

|      | (b) Clock phases                                                   | 17 |  |  |  |

| 2.13 | Charge sampling transfer function.                                 | 18 |  |  |  |

|      | (a) Without magnitude degrading from hold-phase                    | 18 |  |  |  |

|      | (b) With magnitude degrading from hold-phase                       | 18 |  |  |  |

| 2.14 | SNR versus input signal frequency.                                 | 19 |  |  |  |

|      | (a) SNR versus input signal frequency.                             | 19 |  |  |  |

|      | (b) SNR versus frequency showing the -3dB passband                 | 19 |  |  |  |

| 2.15 |                                                                    | 20 |  |  |  |

|      | (a) NMOS switch.                                                   | 20 |  |  |  |

|      | (b) Transmission gate.                                             | 20 |  |  |  |

|      | (c) Bootstrapped switch.                                           | 20 |  |  |  |

| 2.16 | Relative resistance in the three different types of switches.      | 21 |  |  |  |

|      | (a) NMOS switch.                                                   | 21 |  |  |  |

|      | (b) Transmission gate                                              | 21 |  |  |  |

|      | (c) Bootstrapped switch.                                           | 21 |  |  |  |

|      |                                                                    |    |  |  |  |

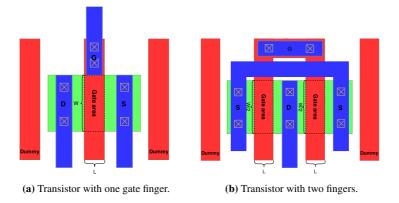

| 2.17 | Green=active area, Red=polysilicon, Blue=Metal 1 and Yellow=Via hole.            | 22  |

|------|----------------------------------------------------------------------------------|-----|

|      | (a) Transistor with one gate finger                                              | 22  |

|      | (b) Transistor with two fingers                                                  | 22  |

|      | Layout pattern to give equal process variation for matched transistors           | 23  |

| 2.19 | Analog CMOS IC design tradeoffs                                                  | 24  |

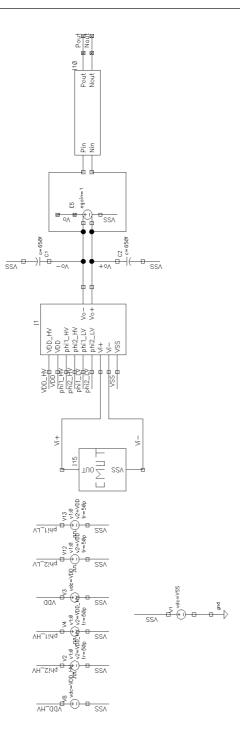

| 3.1  | The proposed fully differential charge sampling amplifier                        | 28  |

| 3.2  | CMUT small signal model                                                          | 28  |

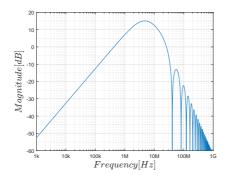

| 3.3  | Transfer function of the CMUT model.                                             | 30  |

| 5.5  | (a) CMUT current transfer function.                                              | 30  |

|      | (b) CMUT voltage transfer function                                               | 30  |

| 3.4  | A single ended active charge sampling amplifier.                                 | 31  |

| 3.5  | Charging duration plotet against -3dB frequency.                                 | 31  |

| 3.6  | Clock phases for the charge samling amplifier.                                   | 32  |

| 3.7  | Transfer function of CMUT and CS.                                                | 33  |

| 3.8  | Noise Contributions in a CSA with CMUT source.                                   | 34  |

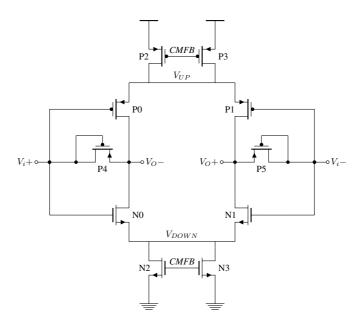

| 3.9  | Fully Differential Inverter Based Amplifier.                                     | 36  |

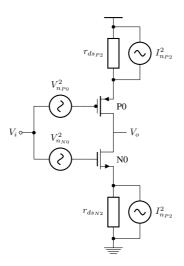

|      | The noise model of the left half side of the OpAmp.                              | 37  |

|      | Influence of nonidealities in OpAmp                                              | 38  |

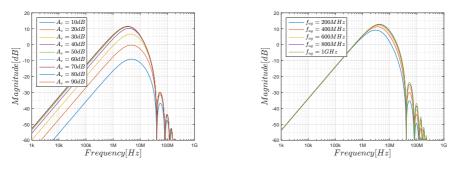

| 5.11 | (a) System transfer function for different OpAmp gain                            | 38  |

|      | (b) System transfer function for different $f_{uq}$                              | 38  |

| 3 12 | Schematic of the CMFB circuit used in this work. $\dots \dots \dots \dots \dots$ | 40  |

|      | Layout pattern of the OpAmp transistors.                                         | 42  |

|      | Picture of one unit capacitor.                                                   | 43  |

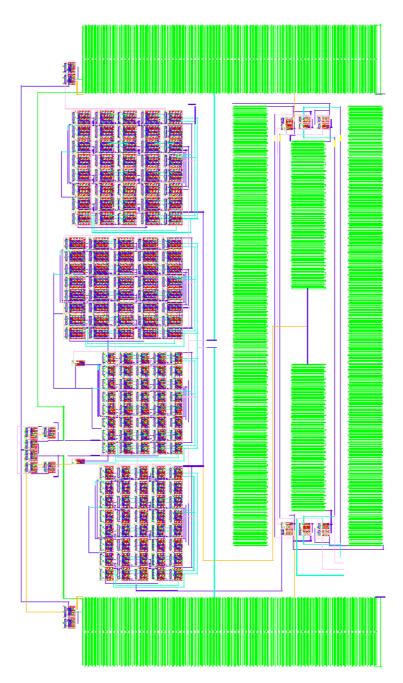

|      | Picture of the circuit layout.                                                   | 44  |

| 0110 |                                                                                  | • • |

| 4.1  | Resulting transfer function of the CSA with CMUT model as source                 | 46  |

| 4.2  | The noise figure plotted against frequency                                       | 48  |

| 4.3  | HD2 Monte Carlo result after 60 iterations.                                      | 49  |

|      | (a) Schematic                                                                    | 49  |

|      | (b) Layout                                                                       | 49  |

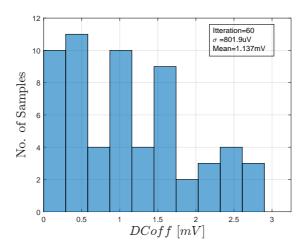

| 4.4  | Monte Carlo result of differential output offset.                                | 50  |

| 4.5  | Plot of the input output characteristics.                                        | 51  |

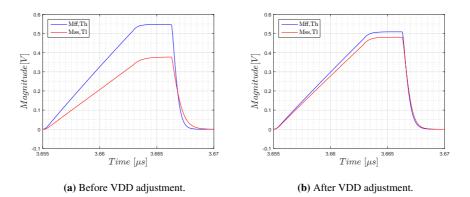

| 4.6  | CSA output signal over corners.                                                  | 52  |

|      | (a) Before VDD adjustment.                                                       | 52  |

|      | (b) After VDD adjustment.                                                        | 52  |

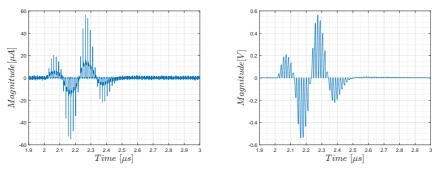

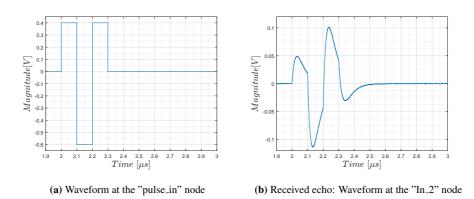

| 4.7  | Input and output ultrasound signal                                               | 54  |

|      | (a) The current signal obtained at the CSA input                                 | 54  |

|      | (b) The voltage at the CSA output                                                | 54  |

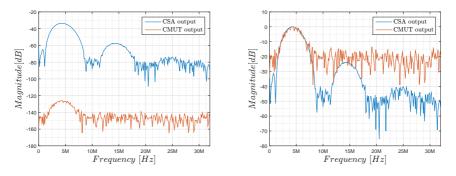

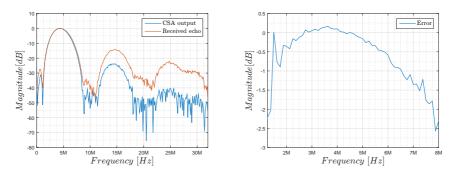

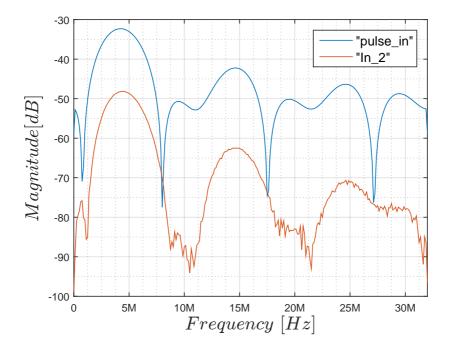

| 4.8  | The normalized signal spectrums of CSA input and output ultrasound signal.       | 55  |

|      | (a) Spectrum of the input current and output voltage of the CSA                  | 55  |

|      | (b) Normalized plot of the frequency spectrum                                    | 55  |

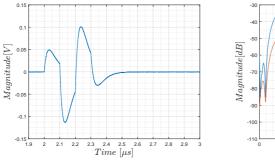

| 4.9  | The received echo waveform.                                                      | 55  |

|      | (a) The received echo waveform.                                                  | 55  |

|      | (b) The spectrum of the echo waveform and the CSA output voltage.                | 55  |

| 4.10 | Comparison of the echo spectrum and the CSA output spectrum                      | 56  |

|      |                                                                                  |     |

|                          | (a)<br>(b)                                 | Normalized spectrums of received echo and CSA output The difference between the spectrums | 56<br>56                               |

|--------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------|

| A.1                      | MOSF                                       | ET inverter with feedback biasing resistor.                                               | 71                                     |

| C.1<br>C.2<br>C.3<br>C.4 | Ultraso<br>Wavefo<br>(a)<br>(b)<br>Spectro | atbench used under simulations.                                                           | 76<br>77<br>77<br>77<br>77<br>77<br>78 |

| E.1                      | A poss                                     | ible circuit implementation to generate reset and charge phases                           | 81                                     |

# Abbreviations

| ADC    | = | Analoge to Digital Converter                   |

|--------|---|------------------------------------------------|

| CMFB   | = | Common Mode Feedback                           |

| CMOS   | = | Complementary Metal-Oxide-Semiconductor        |

| CMUT   | = | Capacitive Micromachined Ultrasound Transducer |

| CSA    | = | Charge Sampling Amplifier                      |

| CT     | = | Continous-Time                                 |

| DR     | = | Dynamic Range                                  |

| DT     | = | Discrete-Time                                  |

| DSP    | = | Digital Signal Processing                      |

| EDA    | = | Electronic Design Automation                   |

| F      | = | Noise Factor                                   |

| FD-SOI | = | Fully Depleted Silicon On Insulator            |

| FFT    | = | Fast Fourier Transform                         |

| IVUS   | = | Intravascular Ultrasound                       |

| LNA    | = | Low Noise Amplifier                            |

| MEMS   | = | Micro-Electro-Mechanical Systems               |

| NF     | = | Noise Figure                                   |

| OpAmp  | = | Operational Amplifier                          |

| SNR    | = | Signal-to-Noise Ratio                          |

| SoC    | = | System on a Chip                               |

| UTBB   | = | Ultra-Thin Body and Burid oxide                |

| VGA    | = | Variable Gain Amplifier                        |

|        |   |                                                |

# Chapter

# Introduction

Ultrasound is a popular tool for medical professionals in diagnosing and examinations inside the body. Ultrasound has the benefit over other medical imaging types in form of cost, that it can provide real-time images and it does not use ionizing radiation which may be harmful. There are several types of ultrasound techniques developed over the years like 2D-mode, Doppler ultrasonography and harmonic imaging. These techniques have different properties suited for different applications [1].

A type of ultrasound imaging technique is Intravascular ultrasound, IVUS, where a catheter with a ultrasound probe is led into the veins to be able to image the inside of the vein and locating problems such as plaque. The ultrasound transducers used for IVUS purpose need to be small and Capacitive Micromachined Ultrasound Transducers, CMUT, have proven to be a good alternative compared to the piezoelectric transducer for this purpose. CMUTs does not only have the advantage of modest size but can also be integrated on silicon in the same process as the CMOS circuitry. [2].

Modern nanoscale CMOS technology have also made it possible to implement relatively sophisticated logic in a small area. This opens the possibility to perform some of the digital processing, DSP, directly in the ultrasound probe itself which leads to less data transmission out of the probe and hence more elements can be put in the transducer array. This again gives an opportunity for 3D ultrasound imaging. [3].

Although digital circuits benefits from shrinking technology like lower power consumption, higher performance and less area consumption, analog circuitry does not have these same benefits. Nanoscale technology does often tolerate less supply voltage than larger technology. Because the relationship between signal-to-noise ratio and powerconsumtion includes voltage headroom the power consumption must be increased to maintain a certain level of accuracy [4]. This is a issue for IVUS since the power consumtion must be kept low so the temperature is held under a maximum limit. Also the intrinsic gain suffers from shrunk technology [5], [6]. This gives challenges in designing low power high performance analog circuitry like front end low noise amplifiers, LNA.

When a ultrasound echo is received at the transducer the signal may be very weak. For an analog-to-digital converter, ADC, to be able to convert it to a digital signal the received signal needs to be amplified to a certian level without adding to much noise or distortion to the signal. The front-end LNAs performance is of utmost importance because the loss in signal here have a large impact on the rest of the system. The resulting image resolution will never be better than the signal achieved after the LNA.

There are two main methods of reading the signal from a transducer, voltage- and current readout can be realized both in continuous time or discrete time. By using discrete time i.e. doing the sampling in the pre-amplifier LNA the power consumption can be reduced compared to using a continuous time pre-amplifier LNA and sampling the signal in a subsequent block [7]. For a discrete time LNA circuit a current mode amplifier is intriguing since this will avoide the problems with linear settling which may set high demands to speed in the operational amplifier, OpAmp [8].

Further more the use of second harmonic imaging to improve the image clearity, contrast and details[1] sets high demands to low second harmonic destortion, HD2.

Sevral approaches have been made to solve the CMUT readout challenge with many different topologies like continuous time LNA [9]–[11], voltage mode sampling LNA [12] and current mode charge sampling LNA [7], [12].

In this work a the main focus has been the design of a fully-differential charge-sampling low noise amplifier in 28nm FD-SOI UTBB to see if placing the CMUT element between the two input terminals could reduce the second harmonic distortion compared to previous attempts. Complete schematic design and layout of the schematic has been made. And simulations and verification of this design has been performed using EDA tools.

### **1.1 Main Contributions**

The main contributions in this work is the design and verification of a front-end fullydifferential charge-sampling low noise amplifier for CMUT elements which contains:

- a fully-differential inverter-based amplifier with drain-to-gate feedback biasing in 28nm FD-SOI UTBB

- a discrete time CMFB circuit

- a highly linear charge sampling amplifier

- schematic and layout of the final charge sampling amplifier

- simulation and verification of layout with parasitic extraction in EDA tools

### 1.2 Thesis outline

The thesis is oulined as follows. Chapter 2 presents background theory used in the design. This includes general theory about transistors, amplifiers, noise, linearity and layout. In chapter 3 the design is presented with decisions explained based on theory from chapter 2 and specified goals. Chapter 4 presents verifications and results of the design. In chapter 5 the results are analyzed, discussed and compared to existing work. Finaly, in chapter 6, a conclusion is made based on the results and discussion.

# Chapter 2

# Theory

### 2.1 IVUS

IVUS is a medical imaging methology where a catheter with a ultrasound probe attached at the tip is used to see from the inside of a blood vessels. By using IVUS one could take ultrasound images from the inside of the body which in many situations are preferred to traditional ultrasound images.

Piezoelectric elements have been the preferred way to generate and detect ultrasound throughout the history. The reason is that the electric field strength needed has been to high for the capacitive mikromachined ultrasonic transducer, CMUT. However the last decades advences in microelectromechanical systems, MEMS, technology has made it possible to make CMUTs that are compatible with piezoelectric transducers. CMUTs also offers improved bandwidth, ease of fabrication of large arrays and integrations with electronics [2].

CMUTs can be produced in common CMOS prosesses and is therefore cheaper and the CMUT with its electronics can be made more compact with individual connections through wafer, therefore more transducer elements can be put in a given area. This makes CMUTs suitable for small ultrasound probes like in IVUS. CMUTs also provide wide bandwidth with a flat frequency response in the band. This gives the possibility to use imaging techniques such as harmonic imaging. Usually in harmonic imaging the transmitter frequency is set to  $\frac{2}{3}$  of the senter frequency and the receiver frequency is set to  $\frac{4}{3}$ . This requires a flat frequency responce in a wide band and therefore CMUTs are suited. [2]. Second harmonic imaging is popular because it gives higher resolution in the resulting images than reading the receiving fundamental frequency. The reason is that tissue is nonliear and will distort the reflected signal. And so, by reading the fundamental frequency details may be lost [1].

In IVUS high-frequency and miniature probes are vital. Therefore CMUTs are well suited due to their sizes and high-frequency capabilities.

A CMUT consists of a metalized membrane, which is the top electrode, suspended above a heavily doped silicon substrate, which is the bottom electrode. The CMUT is therefor a two-port device with the two electrodes as terminals.

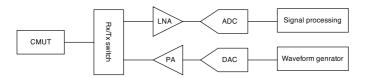

In figure 2.1 the system is shown for the signal chain for one transducer. It consists of the CMUT, a RX/Tx-switch and in the receiving path a LNA and a ADC. The signal processing logic is commen for all transducers. In the transmitting path there is a power amplifier, a DAC and a waveform generator. In a transducer array used in a probe there

Figure 2.1: Signal path for one transducer element in a IVUS system.

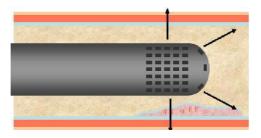

might be several thousand individual transducers as shown in 2.2 with several sub-circuits for each transducer. Therefore it is important that the area consumption of each sub-circuit is small. Also the power consumption of every sub-circuit will be multiplied with the total number of transducers and therefore must be kept low to reduce the radiated heat which may heat up the blood in the veins.

Figure 2.2: A catheter with transducers [13].

### 2.2 CMOS Transistors

CMOS technology is primarily developed for digital circuitry which benefits from shrunked technology due to lower supply voltage, less area consumption and less parasitics which makes power consumption lower [5]. To decrease cost from production it is desirable to design both digital and analog circuitry in the same technology so that only one technology is needed in the production process of system-of-a-chip, SoC [6].

There are some benefits of shrinking technology regarding analog circuits as well. For instance smaller gate area leads to decreased parasitic capacitance. This makes it easier to achieve higher bandwidths.

However the scaling of technology will not scale all parameters accordingly. For all practical purposes the transconductance will stay independent of technology node [14]. But the intrinsic gain of a transistor given in (2.1), decreases and the treshold voltage does

not scale down according to the supply voltage tolerated as technology is scaled down.

$$InrinsicGain = \frac{g_m}{g_{ds}} \tag{2.1}$$

Other non-idealities will, as sizes are decreased, have greater influence as well. To prevent unwanted circuit behavior after production non-idealities like high-field and short-channel effects as well as other effects like channel length modulation and mobility degradation [15] is important effects that should be considered in the design.

CMOS transistors are described by several behavior parameters. The most important parameters are threshold voltage  $V_{th}$  (2.2), drain current,  $I_D$  (2.3), transconductance  $g_m$  (2.4), drain source resistance  $r_{ds}$  (2.5), gate width W and gate length L.

$$V_{th} = V_{th-0} + \gamma (\sqrt{V_{SB} + 2\Phi_F} - \sqrt{2\Phi_F})$$

(2.2)

$$I_D = \frac{1}{2}\mu C_{ox} \frac{W}{L} (V_{GS} - V_{th})^2 [1 + \lambda (V_{DS} - (V_{GS} - V_{th}))]$$

(2.3)

$$g_m = \mu C_{ox} \frac{W}{L} (V_{gs} - V_{th}) \tag{2.4}$$

$$r_{ds} = \frac{1}{\lambda I_{D-sat}} \cong \frac{1}{\lambda I_D}$$

(2.5)

in equation (2.4)-(2.5)  $\mu$  is the carrier mobility in bulk,  $C_{ox}$  is the gate capacitance per area,  $\lambda$  is the output impedance constant,  $\gamma$  is the body effect parameter and  $2\Phi_F$  the surface inversion potential.  $V_{DS}$  is the drain-source voltage and  $V_{GS}$  the gate-source voltage.

The effective voltage  $V_{eff} = V_{GS} - V_{th}$  gives an indication of the transistors transconductor efficiency given by (2.6)

$$\frac{g_m}{I_D} = \frac{2}{V_{eff}} \tag{2.6}$$

The ratio  $\frac{g_m}{I_D}$  is valid for both strong- and weak inversion operation. The equation (2.3) is only valid in the strong inversion area where  $V_{eff}$  is relatively large. But as  $V_{eff}$  is decreased, and falls below approximately 100mV [15], to increase the trans-conductor efficiency, the transistors enters weak inversion region where equation (2.3) is no longer valid. The equation to describe the current in weak inversion is given in (2.7)

$$I_{D_{WI}} \cong I_{D_0} \left(\frac{W}{L}\right) e^{\frac{V_{eff}}{nV_T}}$$

(2.7)

where  $I_{D_0}$  is the current when  $V_{eff} = 0$ ,  $V_T$  is the thermal voltage and n is the slope factor.

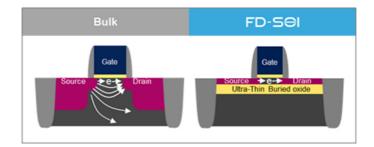

#### 2.2.1 Fully Deplated Silicon on Insulator(FD-SOI)

As transistors are scaled down the channel gate area is decreased. This reduces the gatecontrol, making the transistor to have poorer performance. Because of this unwanted tendency fabrication plants tries to decrease gate leakage and lack of gate-control by adding additional layers in different materials under manufacturing. Production then becomes more complex and thus more expensive. UTBB FD-SOI is a technology developed to counteract this tendency [16]. It uses a thin layer of insulator under the channel, as shown in figure 2.3, which makes doping of the channel, as used in bulk CMOS, unnecessary. This gives less channel leakage and thus the channel can be made shorter, giving faster

Figure 2.3: Bulk-CMOS and FD-SOI [16].

transistors. Two types of PMOS and NMOS, with different threshold voltages, are also offered by the FD-SOI technology. Low threshold voltage, LVT, transistors gives high performance and regular threshold voltage, RVT, transistors gives low power consumption.

### 2.2.2 Mismatch and Variability

After production transistors in a circuit may have slightly different performance than intended while design. After the manufacturing the transistor sizes and dopance may have changed because the fabrication plant cannot be perfectly accurate and so small deviations will accure. For instance the produced layout mask may have some diviation from the designed mask and also when masks are put on the top of each other they may not line up perfectly. An other sources to difference between design and manufactured circuit is scattering from well edges under ion implantation [15].

This mismatch and variability may in some circuits have great influence on performance. In circuits where two or more transistors needs to be equal or exactly scaled to each other small deviations in size may even make the circuit to not work at all if not accounted for during design. An example of such a circuit is the differential input pair. In a differential pair the output value should be zero if  $V_{gs}$  at the two input transistors are equal. If the threshold voltages differes in the two transistors equal  $V_{gs}$  will not give zero in output value because  $V_{eff}$  now differes. This leads to an offset. Also the trans-conductor effeciency will be different at each side leading to possible distortion. The offset variation in a differential pair is given in (2.8) [15].

$$\sigma^{2}(V_{OS}) = \frac{\sigma^{2}(\Delta I_{D})}{g_{m}^{2}} = \frac{1}{WL} \left[ A_{Vt0}^{2} + \left(\frac{I_{D}}{g_{m}}\right)^{2} A_{\kappa'}^{2} \right]$$

(2.8)

where  $A_{Vt0}$  and  $A_{\kappa'}$  is proportionally constants.  $V_t$  is the threshold voltage and  $\kappa' = \mu_n C_{OX}(W/L)$ .

As seen from the equation (2.8) to reduce the influence of mismatch one can increase the transistor area and the tranc-conductor efficiency  $\frac{g_m}{I_p}$ .

Because there is no need to dope the channel in FD-SOI transistors, unlike conventional planar bulk CMOS, there will be less variation in production than conventional CMOS transistors [17]. For this reason less margin is needed in a circuit design to obtain high yield after production, and thus the ciruit can be made more current efficient and area efficient while obtaining the specifications.

### 2.3 Amplifier

#### 2.3.1 Operation Amplifier

An operation amplifier, OpAmp, is an generic form of multipurpose amplifiers used mostly for small signal operations. An OpAmp can be design for many different applications and are characterized by several properties.

The gain in a single point of the  $V_o/V_i$  characteristic is called the small signal gain, as given in (2.9). For large signals the amplifier may enter compression and this is considered in the large signal gain given in (2.10)

$$A_{ss} = \frac{\partial V_o}{\partial V_i} \tag{2.9}$$

$$A_{ls} = \frac{V_o}{V_i} \tag{2.10}$$

If the OpAmp is loaded with a capacitor the transfer function will have a low pass characteristics given by (2.11)

$$|A(f)| = \frac{G_m R_{out}}{\sqrt{(2\pi f R_{out} C_L)^2 + 1}}$$

(2.11)

where  $G_m$  is the transconductance,  $R_{out}$  is the output resistance and  $C_L$  is load capacitor. From (2.11) it's seen that the DC-gain becomes (2.12)

$$A_{DC} = G_m R_{out} \tag{2.12}$$

the OpAmp unity gain frequency,  $f_{ug}$ , is (2.13)

$$f_{ug} = \frac{G_m}{2\pi C_L} \tag{2.13}$$

and the -3dB bandwidth,  $f_{-3dB}$ , is given by (2.14)

$$f_{-3dB} = \frac{1}{2\pi R_{out} C_L}$$

(2.14)

In discrete time applications the settling time characteristics is also important. The settling time is defined as the time OpAmp uses to reach a output value within a certain accuracy compared to the correct value.

The settling time can be divided into two periodes, slew rate and linear settling [18]. The duration of the slew rate periode is dependent of the maximum current the output of the OpAmp can deliver and the load capacitance as given in equation (2.15). The slew rate is signal dependent and is therefore a non-linear effekt that may lead to distortion.

$$SR = \frac{I_{out_{max}}}{C_L} \tag{2.15}$$

The linear settling periode is dependent of the OpAmp  $f_{ug}$  and the accuracy of which the output have to settle. Linear settling is given by (2.16)

$$t_{set} = -\tau ln\left(\frac{Err}{100\%}\right) \tag{2.16}$$

where  $\tau$  is the OpAmp time constant related to  $f_{ug}$  by (2.17) and Err is the accuracy in percent.

$$\tau = \frac{1}{2\pi f_{ug}} \tag{2.17}$$

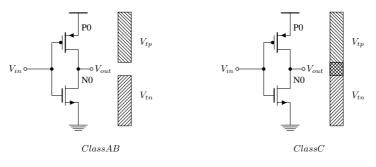

#### 2.3.2 Class of Operation

The four main classes of linear amplifier operation are class A, AB, B and C. Class A achives highest linearity, but will also have the highest power consumption since there always will be a static current to keep the transistor in active region and far from cut-off. To increase efficiency the transistors can be biased into class B. In this case the one transistor, in a push-pull configuration, will be turned off while the other is conducting. This will ideally remove the static current, but it also means that the transistors must operate in the nonlinear region between cut-off and active region which gives poor linearity. To avoid this the transistors can be biased between class A and class B called class AB. In class AB a small static current are allowed to increase linearity. Here the transistors will overlap in the region the transitors are nonlinear. This improves the linearity but at the cost of higher static current consumption. Class C means biasing the transistor lower, further than class B, which makes even lower linearity performance but also lower power consumption.

A push-pull class AB configuration like an inverter will have better slew rate performance than a class A common source configuration amplifier because there is no current source limiting the maximum peak output current.

### 2.3.3 Inverter

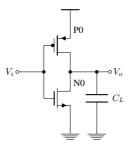

A CMOS inverter, depicted in 2.4, is a building block originally intended as a logical port. It consists of two complementary transistors, one PMOS and one NMOS, both connected in a common source configuration.

Figure 2.4: MOSFET inverter.

Because both the PMOS and the NMOS are active transistors the transconductance from both contribute to the total transconductance and the inverter will have higher total transconductance than other single stage configuration amplifiers like the common source. With twice the  $G_m$ , assuming  $g_{mn} = g_{mp}$ , and the same output resistance as a common source, the gain, given by (2.18), is twice a high. The unity-gain frequency also doubles with the same load (2.19). This makes inverter to have twice the trans-conductor efficiency,  $\frac{g_m}{I_D}$ , as a common source amplifier.

$$A_{v} = \frac{v_{o}}{v_{i}} = -G_{m} \times R_{out} = -(g_{mn} + g_{mp}) \times (r_{dsn} || r_{dsp})$$

(2.18)

$$f_{ug} = f_{-3dB} \times A_v = \frac{G_m}{2\pi C_L} = \frac{g_{mn} + g_{mp}}{2\pi C_L}$$

(2.19)

Biasing can be challanging with the inverter since the PMOS and NMOS will both work as active transistors but in opposite direction, they works as a push-pull configuration. The class of operation will depend on the threshold voltage and the supply voltage as shown in figure 2.5.

Figure 2.5: Inverter class of operation [19].

The class of operation is AB as long as  $V_{sup} \ge V_{thn} + V_{thp}$  and class C if  $V_{sup} < V_{thn} + V_{thp}$  as shown in figure 2.5. As one enters deeper into class AB the trans conductor efficiency increases as  $V_{eff}$  decreases and  $\frac{g_m}{I_D}$  increases. A drawback by pushing the inverter far into class AB is that, to maintain the current needed to keep a sufficient slew rate at large output swings, the transitor sizes must be increased. The increased sizes will increase the parasitics in the transistors which may decrease the intrinsic cut-off frequency,  $f_T$  of the amplifier.

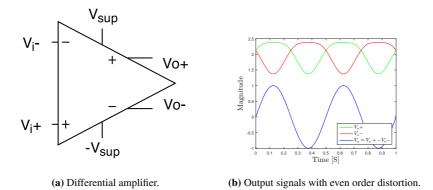

#### 2.3.4 Fully Differential Amplifier

A fully differential amplifier is an amplifier where both input and output have two terminals as shown in figure 2.6(a). It senses the voltage different between the input ports, multiplies this different with the gain A and produces a differential output (2.20). If balanced input signals is applied the even order harmonic distortion, generated by the amplifier, will be canceled as seen from (2.29) where all terms with power of even order will be canceled shown in 2.6(b).

$$V_o = (V_{o+} - V_{o-}) = A(V_{i+} - V_{i-})$$

(2.20)

Figure 2.6: A differential amplifier and its output with even-order distortion.

The voltage of which the output signals  $V_o$ + and  $V_o$ - swings around is called the output common mode voltage given by (2.21). In the same way there is an input common mode voltage. The common mode output voltage vary with the input common mode voltage and therefore a additionally circuit is needed called a common mode feedback. The purpose of this circuit is to keep the output common mode voltage at a specified level usually midway between the rail voltages.

$$V_{CM_o} = \frac{V_{o+} + V_{o-}}{2} \tag{2.21}$$

If the input signals is not perfectly balanced and the amplifier do not have infinitely high common mode rejection ratio, CMRR, the even order distortion is not completely canceled. CMRR is the rejection the amplifier have from a common mode input voltage variation to an output differential voltage variation. The common mode input to differential output voltage gain,  $A_{CM}$  can be added to equation (2.20) as shown in (2.22).

$$V_o = A(V_{i+} - V_{i-}) + A_{CM} \left(\frac{V_{i+} + V_{i-}}{2}\right)$$

(2.22)

CMRR can now be find by (2.23).

$$CMRR = \frac{A}{A_{CM}} = 20\log\frac{A}{A_{CM}}dB$$

(2.23)

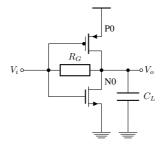

### 2.3.5 Biasing

An inverter as shown in figure 2.4 needs to be biased so that the point of operation on the input node is at the point where the gain,  $f_{ug}$  and linearity is at its highest. The output should also be in the middel of the rails to give maximum output swing. If both input and output point of operation is at the same voltage level a bias scheme called *drain-to-gate feedback resistor biasing* [20] shown in 2.7 can be used.

Figure 2.7: MOSFET inverter with drain-to-gate resistor feedback biasing.

In the topology the DC operating point at the input is set by the output operating point. The gate of the PMOS and NMOS are high impedance nodes at low frequencies so very little DC current flows through  $R_G$ , which makes both PMOS and NMOS to be diode connected transistors at low frequency. Therefore the transistors are self biased into active region. The biasing scheme set a limitation of the output swing because the transistors will leave the active region [21]. The minmum output voltage is given by (2.24) and the maximum voltage by (2.25).

$$V_{out_{min}} \approx \frac{V_{DD} - V_{SS}}{2} - V_{Tn} \tag{2.24}$$

$$V_{out_{max}} \approx \frac{V_{DD} - V_{SS}}{2} + V_{Tp} \tag{2.25}$$

As seen from equation (2.24) and (2.25) this topology is not suited for curcuits where the supply voltage is much larger than the threshold voltage. In modern nanoscale CMOS technology however the supply voltage is usually around 1V or lower and hence this bias scheme is suitable.

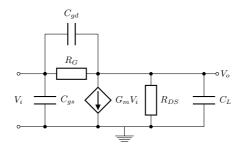

The drain-to-gate feedback resistor will lower the output resistance because it will act as a parallel connection with  $R_{DS}$  to virtual ground. A lower output resistance will lead to lower gain according to (2.18). To find the influence the drain-to-gate feedback resistor has on the gain and bandwidth some calculation can be performed. The calculations together with a small signal equivalent can be found in Appendix A.1 and the resulting equations is shown in (2.26) for gain and the transfer function in (2.27)

$$A_{DC} = -\frac{G_M R_{DS} - \frac{R_{DS}}{R_G}}{1 + \frac{R_{DS}}{R_G}}$$

(2.26)

$$|A_{AC}|^{2} = \frac{(\omega R_{DS} C_{gd})^{2} + \left(G_{M} R_{DS} - \frac{R_{DS}}{R_{G}}\right)^{2}}{(\omega R_{DS} (C_{L} + Cgd))^{2} + \left(1 + \frac{R_{DS}}{R_{G}}\right)^{2}}$$

(2.27)

It is seen from equation (2.26) that  $R_G$  will have a great influence on the DC-gain for small values of  $R_G$  because the second term in the numerator will be subtracted from the first term and the denominator will be large. However if  $R_G$  is kept at a high value then the influence will be negligible. The frequency response is given in (2.27) and in (2.28) it is solved for a gain of one to see the influence of  $R_G$  to the  $f_{ug}$ .

$$f_{ug} = \frac{1}{2\pi} \sqrt{\frac{G_M^2}{C_L^2 + 2C_L C_{gd}} - \frac{G_M}{2R_G (C_L^2 + 2C_L C_{gd})}}$$

(2.28)

Equation (2.28) shows that for large values of  $R_G$  the first term under the root sign will dominate and the  $f_{ug}$  will be almost identical to the frequency without  $R_G$ . However for small values the second term will dominate and the  $f_{ug}$  will be zero. One reason is that the gain will be lower and at some point even under one.

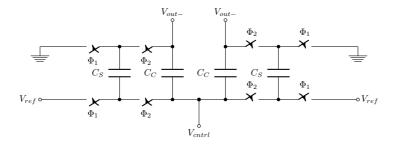

#### 2.3.6 Common Mode Feedback

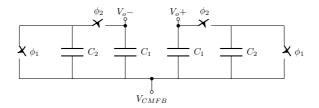

To control the common mode voltage of a fully-differential OpAmp some circuitry is needed. This kind of circuitry is called common-mode feedback, CMFB. The CMFB circuit finds the middle voltage between the two differential signals and compare it to a desired voltage and forces the two voltages to be equal. CMFB circuits can be implemented as both continous-time circuits or as switched-capacitor circuits. Continous-time CMFB has limitations in maximum swing and are hard to design linear over a large voltage swing which again limits the OpAmp output swing. It will also, for most topologies, use static power. Switched capacitor CMFB are most suited for discret time circuits because the switching may leed to clock feedtrough glitches in the output signal of a continous-time.

circuit. Also if large capacitors is needed in the switched capacitor CMFB the amplifier load is increased resulting in a need for higher current delivery demands from the amplifier. An example of a switched-capacitor CMFB circuit [27] is shown in 2.8.

Figure 2.8: Switched-Capacitor CMFB circuit [15].

The operation is as follows. The capacitors  $C_C$  provides a AC feedback path from the amplifier output nodes to a control node in the amplifier. The common mode gain is high, but the differential gain is kept low, idealy zero. This way the common mode can be be controlled to a constant value and the CMFB circuit will have little effect on the amplifier differential gain. Since DC voltage is blocked by  $C_C$  the capacitors  $C_S$  and the switches is needed to set the CMFB DC level.  $C_S$  provides a voltage drop over  $C_C$  that gives the desired common-mode output.

### 2.4 Dynamic Range

An important property of an amplifier used for high accuracy applications is dynamic range, DR. DR gives the ratio between the smallest and largest signal that the amplifier can handle. In the lower end DR is limited by noise and in the upper end by linearity.

### 2.4.1 Linearity

In a linear amplifier the output signal should be a exact replica of the input signal only with higher amplitude. But there are limitation due to non-idealities that will change the signal somewhat on its way through the amplifier. These limitations are among others compression due to limitation in supply headroom and non-linear  $I_o/V_i$  characteristics.

#### **Harmonic Distortion**

If a sinusoidal signal is applied to a nonlinear system, the system will generate harmonic frequency components such that the output signal will have a frequency component as the input signal,  $f_{in}$ , but also components at  $nf_{in}$  (n=2,3,4...). If the input signal of the nonlinear system is  $v_{in}(t)$  and the output is  $v_o(t)$ , then the output signal can be expressed as the Taylor series expansion shown in (2.29) [15].

$$v_o(t) = a_1 v_{in}(t) + a_2 v_{in}^2(t) + a_3 v_{in}^3(t) + a_4 v_{in}^4(t) + \dots$$

(2.29)

where  $a_1$  is the term of the fundamental frequency and  $a_2$ ,  $a_3$  and  $a_4$  is the terms of second-, third- and fourth-order harmonic distortion.

If  $v_{in}(t)$  is given by (2.30)

$$v_{in}(t) = A\cos(\omega t) \tag{2.30}$$

then the output signal is approximated by (2.31)

$$V_{o}(t) = a_{2}\frac{1}{2}A^{2} + (a_{1}A + a_{3}\frac{3}{4}A^{3})cos(\omega t) + a_{2}\frac{1}{2}A^{2}cos(2\omega t) + a_{3}\frac{1}{4}A^{3}cos(3\omega t) + ...$$

=  $H_{D_{0}} + H_{D_{1}}cos(\omega t) + H_{D_{2}}cos(2\omega t) + H_{D_{3}}cos(3\omega t) + ...$

where  $H_{D_0}$  is the DC component and  $H_{D_1}$ ,  $H_{D_2}$  and  $H_{D_3}$  are the amplitudes of the fundamental, second- and third- harmonic components. From this the second- and third-harmonic distortion ratios can be found by (2.32) and (2.33)[15]

$$HD_2 = \frac{H_{D_2}}{H_{D_1}} = \frac{a_2 \frac{1}{2}A}{a_1 + a_3 \frac{3}{4}A^2} \stackrel{\frac{3}{4}a_3 A^3 \ll a_1 A}{=} \left(\frac{a_2}{a_1}\right) \left(\frac{A}{2}\right)$$

(2.32)

$$HD_{3} = \frac{H_{D_{3}}}{H_{D_{1}}} = \frac{a_{3}\frac{1}{4}A^{2}}{a_{1} + a_{3}\frac{3}{4}A^{2}} \stackrel{\frac{3}{4}a_{3}A^{3}}{=} \left(\frac{a_{3}}{a_{1}}\right) \left(\frac{A^{2}}{4}\right)$$

(2.33)

In a fully differential system with perfectly balanced input signals, the even order terms in (2.31) will be canceled and so the evenorder distortion will be suppressed.

A measure for all the harmonics compared to the fundamental frequency is total harmonic distortion, THD. THD is the sum of all harmonics divided by the fundamental tone in decibel [15] as shown in (2.34)

$$THD = 10\log\left(\frac{H_{D_2}^2 + H_{D_3}^2 + H_{D_4}^2 + \dots}{H_{D_1}^2}\right)$$

(2.34)

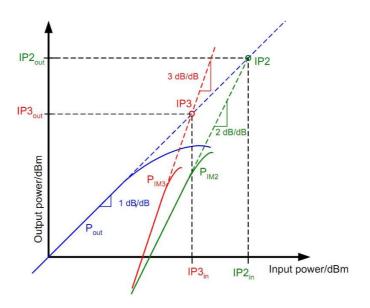

#### Second- and Third-Order Intercept Point (IP2,IP3)

As the input signal of an amplifier increases the output signals fundamental and harmonic components will increase. The fundamental component will be much larger than the hamonics for small input signals and the harmonics will also be below the noisfloor and, hence, not be visible in the fast fourier transform, FFT, spectrum of the output signal. But as the input signal increases the harmonics will arise above the noise floor and increase faster than the fundmental component. When the input signal gets larger the output will be limited by the maximum swing of the amplifier and so the slope will flatten out and no longer be linear. If the linear slope of the fundamental and the third harmonic component would continue infinitely they would at some point intercept as shown in 2.9. This intercept point is called Third-Order Intercept Point or IP3. The second-order intercept point is the intercept point between the fundamental and the second harmonic component. These points can be measured as terms of the input signal, IIP2 and IIP3, or as terms of the output signal, OIP2 and OIP3.

Figure 2.9: Typical  $V_o/V_i$  relationship [22].

### 2.4.2 Noise

#### **Types of Noise**

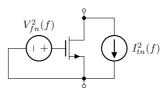

The most dominant types of noise in a CMOS transistor are flicker noise and thermal noise. Thermal noise occurs due to the channel resistance. In figure 2.10 the thermal noise is modeled as a current source,  $I_{tn}^2(f)$ . A simple model for the thermal noise is given in expression (2.35), where T is the temperature in Kelvin, k is Boltzman's constant and  $g_m$  is the transistors transconductanse. More advanced models are obtained in [23]. The flicker noise,  $V_{fn}(f)$ , is given approximately by (2.36) where L is the transistor length, W the width, K is a constant dependent on device properties, f is frequency and  $C_{ox}$  is the gate capacitance per area. Flicker noise is the noise type that dominates at low frequencies [15].

Figure 2.10: Noise model MOSFET.

$$I_{tn}^2(f) = 4kT\left(\frac{2}{3}\right)g_m\tag{2.35}$$

$$V_{fn}^2(f) = \frac{K}{WLC_{ox}f}$$

(2.36)

The input referred noise is given by (2.37) and is obtained by referring both noise sources of 2.10 to the gate.

$$V_i^2(f) = 4kT\left(\frac{2}{3}\right)\frac{1}{g_m} + \frac{K}{WLC_{ox}f}$$

(2.37)

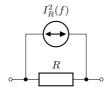

The noise in a resistor can be modeled as a current shown in figure 2.11

Figure 2.11: Noise model for a resistor.

and the noise current is given by equation (2.38)

$$I_R^2(f) = \frac{4kT}{R} \tag{2.38}$$

#### **Noise Figure**

Noise factor, F(f), is a measure to tell how much the signal to noise ratio, SNR, is reduced through a circuit. When calculating noise factor noise spectral density at a particular frequency, *spotnoise*, is used. Since the signal and the noise from the source both are amplified by the circuits gain, the output signal will be the input signal times the gain, and so can be replaced in the equation by a gain factor. The noise, however, is amplified, but in addition the noise from the circuit itself is added to the total output noise. The noise factor is thus the ratio of the total noise, input noise plus circuit noise, to the noise that would appear if the circuit was noiseless. If all noise is referred to the circuit input node the expression of F(f) becomes (2.39). Noise figure, NF(f) is the noise factor, F(f), in decibel as shown in (2.40) [15].

$$F(f) = \frac{V_{n_{source}}^2(f) + V_{n_{circuit}}^2(f)}{V_{n_{source}}^2(f)} = 1 + \frac{V_{n_{circuit}}^2(f)}{V_{n_{source}}^2(f)}$$

(2.39)

$$NF(f) = 10\log_{10}[F(f)]dB = 10\log_{10}\left[1 + \frac{V_{n_{circuit}}^2(f)}{V_{n_{source}}^2(f)}\right]dB$$

(2.40)

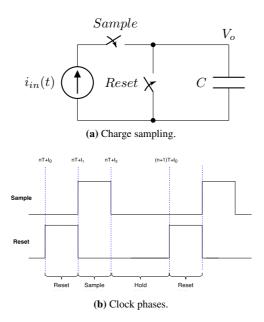

## 2.5 Charge Sampling

In applications when the signal from the source is a current, i.e. when the source impedance is high, a charge sampling circuit will be more suited than a voltage sampling circuit. Also, charge-sampling is a attractive alternative over voltage-sampling circuits for high speedapplications because the signal is processed in the current domain and in this way avoiding voltage settling.

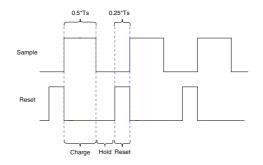

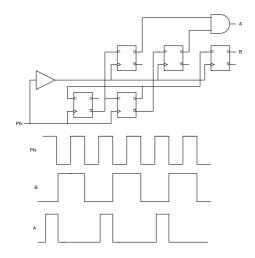

A simplified charge sampling circuit is shown in figure 2.12(a). It consists of two switches and a sampling capacitor. The process is composd of three phases: charging-, holding and reset phase shown in figure 2.12(b). The operation is as follows, first the reset-switch resets the capacitor, then the sampling-switch closes and lets current flow from the source and charge the capacitor. After a specified charge time the sampling switch is opened and the charge is held until the reset switch is closed and the process is repeted. The equation for the output node is given in 2.41 for  $t \in [nT + t_1, nT_{t2}]$ . The frequency domain transfer function is derived in [8] and is given in equation (2.42).

Figure 2.12: Charge sampling circuit and clock phases.

$$v_o(nT + t_2) = \frac{1}{C} \int_{nT + t_1}^{nT + t_2} i(t)dt$$

(2.41)

$$V_o(f) = \frac{\Delta t}{C} \left( \sum_{i=-\infty}^{\infty} I(f - if_s) sinc(\pi \Delta t(f - if_s)) \right) \Delta t_h sinc(\pi \Delta t_h f)$$

(2.42)

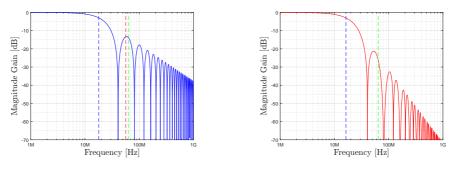

Figure 2.13(a) shows (2.42) plotted with normalized magnitude, i=0 and with the magnitude degrading from  $\Delta t_h$  is excluded. The sampling frequency,  $f_s = \frac{1}{T_s}$ , is set to 64MHz, chargetime is set to  $0.5T_s$  and reset to  $0.25T_s$ . Figure 2.13(b) is the normalized plot of (2.42) with magnitude degrading including.

(a) Without magnitude degrading from hold-phase.

(b) With magnitude degrading from hold-phase.

Figure 2.13: Charge sampling transfer function.

The blue vertical lines marks the -3dB point, which is at  $\frac{0.14}{\Delta t}$ , the green lines marks the sampling frequency,  $f_s$ , and the red line marks the senter frequency of the first side lobe. For very high speed applications this side lobe can be used as passband. An important property of charge sampling is that the -3dB bandwidth is decided by the duration of  $\Delta t$ . Since the duration of  $\Delta t$  is not directly dependent of technology the technology can be selected to fulfill other specifications.

The plots in figure 2.13 is normalized and the magnitude will depend on the duration of the charge phase. If  $\Delta t = 0.5$  only 50% of the signal is charged into the capacitor and so the magnitude will be 6dB lower than if all the signal had been charged into the capacitor.

A critical limitation of high-speed sampling is clock jitter. Clock jitter is the variation in rising or falling clock edges in time. If a clock edge shold rise at the time T it will, in a realized clock generator, infact rise at  $T \pm \delta t$  where  $\delta t$  is a small random number. The clock jitter is introduced by device noise and phase noise of oscillator [24]. This means that the sampling time is not at the exact point it was intended, and with a varying input signal, the sampled value becommes somewhat larger og smaller than the correct value. For charge sampling the signal to jitter noise ratio is given by (2.43) [25]

$$SNR = 10\log\left(\frac{\left(\sin\left(\frac{\omega\Delta t}{2}\right)\right)^2}{\left(\sin\left(\frac{\omega\delta t_0}{2}\right)\right)^2 + \left(\sin\left(\frac{\omega\delta t_0}{2}\right)\right)^2}\right)$$

(2.43)

Where  $\delta t_0$  and  $\delta t_1$  is the jitter error in rising and falling clock edges of the charging clock.

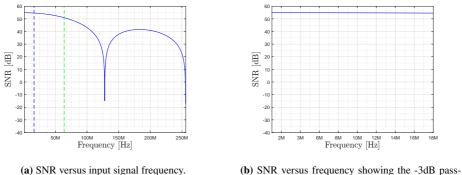

Figure 2.14 shows a plot of SNR versus input frequency with  $\delta t_0 = \delta t_1 = 10ps$ , charging periode  $\Delta t = 0.5 \frac{1}{f_s}$  and  $f_s = 64MHz$ .

band.

Figure 2.14: SNR versus input signal frequency.

It is seen from figure 2.14 that the error due to jitter in a charge sampling circuit is almost independent of frequency in the passband which, for some applications, is advantageous.

The noise in charge sampling circuits is due to switches, the noise from input and the total output noise is given in equation (2.44) [8]

$$e_v^2 = \frac{kT}{C} \left( \frac{2\Delta t}{R_S C} + e^{-\frac{2\Delta t}{R_{eq}C}} \right)$$

(2.44)

where  $R_S$  is the source resistance,  $R_{eq}$  is the parallel connection between the source resistance and the off resistance in the reset switch,  $R_{eq} = R_S ||R_{off}$ . If  $R_{off} \gg R_S \Rightarrow R_{eq} \approx R_s$  (2.44) becommes (2.45)

$$e_v^2 = \begin{cases} \frac{kT}{C} & \text{if} 2\Delta t \ll R_S C\\ \frac{kT}{C} \left(\frac{2\Delta t}{R_S C}\right) & \text{if} 2\Delta t \gg R_S C \end{cases}$$

(2.45)

which states that the noise will be near  $\frac{kT}{C}$  if  $2\Delta t \ll (R_S C)$  i.e. when the source impedance is high, the integration capacitor is large and the charging duration is short.

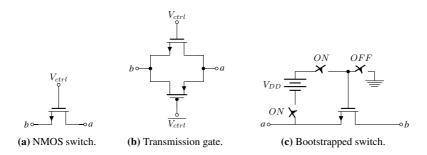

### 2.6 CMOS Switches

CMOS switches can be implemented as a single NMOS transitor, shown in figure 2.15(a), a transmissiongate with a NMOS and a PMOS in parallell, shown in figure 2.15(b) or as a bootstraped switch, shown in figure 2.15(c).

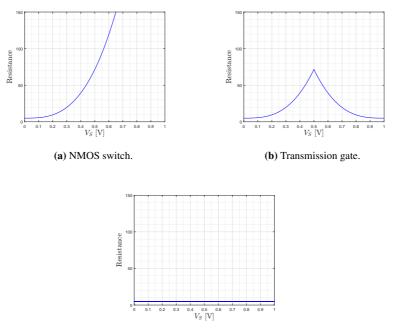

The simplest switch is a single NMOS transistor where input and output is the drain and source nodes and the control port is the gate node. The NMOS switch is limited by the voltage level at input and output. If the source node is near upper rail  $V_{GS}$  will be small and may be to low to turn the switch on. Also if the voltage level on the source node varies over a large voltage range the on-resistance, shown in figure 2.16(a) will vary which in some applications cannot be tolerated. To give the switch less variation in on-resistance a PMOS can be put in parrallel which will have lower resistance for high input and output voltage levels. But it increases complexity because a inverted version of the control signal is needed. Another drawback with transmissiongates is the increased impedance when input and output voltagelevel is halfway between the rails compared to high or low voltage levels as shown in figure 2.16(b). If the supply voltage is low the switch may even be completely off for the voltage region midway between the rails.

Figure 2.15: Three implementations of CMOS switches.

A way to improve this performance is the use of bootstrapped switches. This type off switch keeps the  $V_{GS}$  voltage constant for all voltage levels at input/output ports by the introduction of a voltage source between Source and Gate of the transistor. The common way to implement this voltage source is by a capacitor which is charge to VDD. Although constant on-resistance, a bootstrapped switch requires more transistors and a capacitor making them more complicated than other types of switches [26].

(c) Bootstrapped switch.

Figure 2.16: Relative resistance in the three different types of switches.

If the voltage level at the source of the switch is low and the voltage swing is low usally NMOS switches is used due to lowest complexity, lowest area and low noise performance. For nodes with large voltage swings the bootstrapped switch has the best performance due to the constant ON-reistance, but because of complexity and size transmissiongates are sometimes preferred.

An unwanted effect introduced by the use of transistor switches is charge injection. When the transistor is turned off the charge in the channel will flow out through the source and drain nodes of the transistor. The amount of channel charge in a transistor with  $V_{DS} = 0$  is given by [15]

$$Q_{ch} = WLC_{OX}V_{eff} \tag{2.46}$$

The expression in (2.46) indicates that small transitors will give less charge injection and large  $V_{eff} = V_{GS} - V_{th}$  will give more charge injection. As (2.46) is dependent of  $V_{eff}$  the charge injection is dependent on the voltage level of the source node and, thus, signal dependent.

# 2.7 Layout

An integrated circuit is produced in several steps dependent of technology and number of layers in the prosess. To be able to build up an integrated circuit at a fabrication plant masks that blocks areas of the circuits at different stages in the process steps must be made. These mask will determind the geometry of the final chip and it's the designers responsibility to create the geometry of these masks. The process of defining the geometry of these masks is called layout.

The masks must meet certain requirements or layout design rules which aims to compensate for the mask misalignment that may occur in production. As an example there is a rule that limits the minimum space between the drain and source contacts to the gate polysilicon. This way they will not overlap and shorts between gate and drain or source are avoided.

The rules are stricter for layout of analog circuitry than digital circuitry. The reason is that analog circuits are more sensitive to parasitics as capacitance and higher resitance in connections between layers than modeled under design. The latter can be solved by using more via connections. Also transistors for analog circuits are usually much wider than in digital circuits. Therefore the number of gate fingers are increased. To make transistors more square-shaped and compact they can be realized by using more fingers. A transitor with one finger is shown in 2.17(a) and a transistor with two fingers is shown in 2.17(b).

Figure 2.17: Green=active area, Red=polysilicon, Blue=Metal 1 and Yellow=Via hole.

The dummy polystrips in figure 2.17 are added to give transistors junctions equal surroundings and this way the surroundings will have less effect on the transistor performance.

If some transistors need to be matched to others, as the case for a differential pair, then the transistor should be build up with a number of unit sized transistors in parallel. These transistors should be laid out in a pattern so that production variation over the die area have the same influence on all the unit transistors. For instance if a differential pair, consisting of transistor A and B, is divided into unit transistors a pattern that give both A and B almost equal variation is by the pattern in figure 2.18.

| Α | В | В | Α |

|---|---|---|---|

| В | Α | Α | В |

Figure 2.18: Layout pattern to give equal process variation for matched transistors.

An other advantage of using M-factor is lower series resistance and lower junction capacitance, but due to routing the parasitic capacitance will increase. Because some circuitry is very sensitive to parasitic effects it is important to locate the nodes in the circuit which is most critical for parasitics and take extra care at these nodes in the layout.

In modern design tools built-in functions that will give warnings is the layout don't meet the design rules, there are tools for checking that all design rules are fulfilled and tools to compare the layout to the schematic so that all transistors are included, that they have the right sizes and that they are correctly connected to each other. Parasite capacitance, resistance and conductance can also be extracted from the layout to model more non-idealities that will arrise after production. This can help the designer in find bad layout choices and correct them before production.

#### 2.8 Figure of Merit

Figure of Merit, or FoM, is a measure to be able to compare different designs in different technologies. Dependent of application the FoM should include specifications as, power consumption, bandwidth, gain, noise performance, linearity performance and area consumption. A commonly used FoM for low power, low voltage amplifiers [14] is (2.47).

$$FoM = \frac{P}{DR^2 f} \tag{2.47}$$

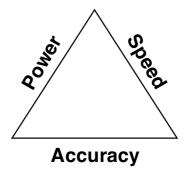

In design of analog integrated CMOS circuits there are trade offs so that a circuit can achieve the specifications with sevral solutions. Figure 2.19 shows the three tradeoffs power, speed and accuracy. A circuit can be made accurate and fast by increasing  $g_m$  and add capacitance. However to drive the capacitance a larger bias current is needed and, hence, high power consumption. High speed and low power can be achieved by using low capacitance and biasing the transistor in weak inversion.

For the case of low-noise front-end amplifiers important spesifications are gain bandwidth, noise factor, linearity and for IVUS ultrasound probes the area should be small. Also, like for all integrated circuits the power consumption should be kept as low as possible. In second order harmonic imaging the most critical distortion term is the second hormonic distortion and higher order distortion terms are not as important. The common way to specify the noise of a LNA is the noise faktor, F, and therefor it should be included in the FoM. The bandwidth is also important and can be tarded for power or area and

Figure 2.19: Analog CMOS IC design tradeoffs.

should be included. Therefore a suitable FoM for a LNA amplifier for second-harmonic imaging is (2.48)

$$FoM_{LNA} = \frac{P_{tot}A_{tot}HD_2F}{BW}$$

(2.48)

In equation (2.48)  $P_{tot}$  is the total power consumption,  $A_{tot}$  is total area consumption,  $HD_2$  is the second harmonic component, F is the noise factor and BW is the -3dB bandwidth. The lower value of  $FoM_{LNA}$  the better.

### 2.9 Computer Assisted Design

The behavior of transistors are very complex and include many higher order effects which may have great influence in a circuit design. Therefore advanced models, which tries to include as many of these effects as possible are developed through the years. As computers becommes faster and more powerfull more complex models can be used to describe transistors. Therefore modern design is done with sophisticated software, with tools to ease development and assure quality. Simulators are used to check the behavior of circuits where parasitic effects are modeled in circuit elements.

A circuit design is usually first simulated in a schematic representation. However this schematic does not take into account all parasitics and interconnects between different wires and circuit elements that is placed near each other. Therefore some effects that will occur in the fabricated circuit will not appear in the schematic simulations. After layout it is possible, with CAD tools, to extract these parasitics, but if the ciruit is large it may take some time to find areas where parasitics is causes errors. For this reason it is good practice to divide the schematic into many smaller subcircuits and do layout and simulation of these separately. This eases the search for errors and saves time.

Circuit performance may also deviate from simulated after production due to productions variations. Such variation may be mask misalignment and dopence variations. The fabrication plant can provide a statistical model for the variation and this model can be used for example in a Monte Carlo simulation. This simulation will do a number of spesified iterations picking out random parameters from this model each iteration. The result will be an statistical model of the circut performance after production.

# 2.10 Existing Work

There are many exiting low noise amplifiers for CMUT readout both in voltage and current mode and in both continuous time, CT, and discrete time, DT, domain. Solutions with and without variable gain amplifiers,VGA, and in different technologies. There are several solutions like single-ended-to-differential CT VGA [10], [11], [28], solutions with single-ended-to-differential DT VGA[29], single ended CT amplifiers[21] and single ended charge sampling amplifiers [7]. These solutions are made for different CMUT sizes with different senter frequencies intended for different IVUS solutions and so have different specifications.

There are also a difference in the load for the LNAs mentioned above as not all are intended for a system with in-probe DSP.

Interesting comparative work is found in [10], [28]. [28] because it acheives the lowest FoM of the work found and [10] because it uses the same technology.

# Chapter 3

# Topology and Design

The goal of this work is to design a discrete-time low noise amplifier for a IVUS system. The source for the LNA is a CMUT transducer and the load is ADC in the next stage.

The design focus is to obtain low harmonic distortion and low noise performance to obtain a high resolution outputsignal. Low power consumption is also of importance to reduce the radiated heat.

In the design matlab will be used to model behavior. Cadence Virtuoso will be used for schematic and layout design and spectre for simulations.

# 3.1 Specifications

The goal specification are given in table 3.1

| Parameters                  | Goal            |

|-----------------------------|-----------------|

| $V_{dd}$                    | $\leq 1 V$      |

| $V_{ss}$                    | 0 V             |

| $HD_2$                      | <-74 $dB$       |

| Center frequency, $f_C$     | 5 MHz           |

| Bandwidth (-3dB) $f_{-3dB}$ | 5 MHz           |

| Power Consumption           | Low as possibel |

| Noise figure, NF            | <3 dB           |

Table 3.1: Specified goals.

The supply voltage given in table 3.1 is set to one voltage to ensure that the maximum input voltage of the ADC is not exceeded. In second harmonic imaging the important distortion term is the second harmonic. To achieve a high resolution in the digital signal used for DSP, without distortion the HD2 goal is set to -74dB. The center frequency of the intended CMUT is 5MHz obtained from the model 3.2.1. And the -3dB bandwidth of the system should be at least 100% of the center frequency which correspond to 5MHz from

2.5MHz to 7.5MHz. The bandwidth is intended to enable the use of harmonic imaging as described in section 3.2.1 in the theory. In front-end receiver LNA it is important to not add to much noise to the signal. Usally the signal-to-noise ratio, SNR, at the LNA output should not be reduced with more than 3dB compared with the SNR at the LNA input. In other words, the added noise from the LNA should be less than the source noise. Therefore the noise figure, NF, should be less than 3dB.

There is no specified gain but to have some gain the CSA will be designed to have a gain around 15dB. The gain will be adjusted to improve other specifications and my be lower or higher than 15dB in the final design.

The LNA should be fully differential and designed in 28nm UTBB FD-SOI technology.

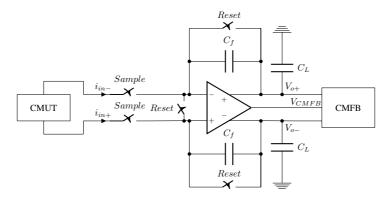

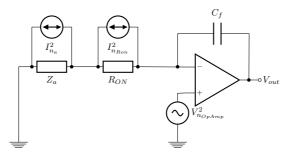

#### 3.2 Charge Sampling Amplifier System

The proposed charge sampling amplifier with the CMUT model is shown in figure 3.1

Figure 3.1: The proposed fully differential charge sampling amplifier.

It consists of the CMUT model placed between the input nodes, the sampling and reset switches, an OpAmp, a feedback capacitor, the load capacitor, which models the DAC of the proceeding SAR ADC, and a CMFB circuit. Design of all blocks will be described in following sections.

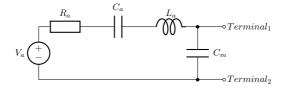

#### 3.2.1 CMUT model

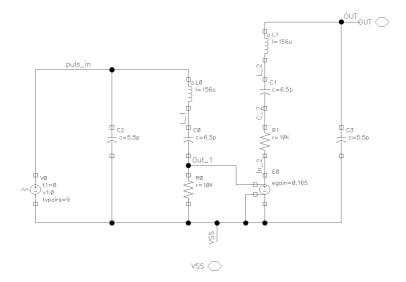

An electrical small signal equivalent circuit of a CMUT element is shown in figure 3.2

Figure 3.2: CMUT small signal model.

where  $R_a$  represents the coupling of acoustic waves between the water in front of the CMUT and the CMUT itself.  $C_a$  represents the mechanical stiffness of the mambrane and  $L_a$  represents the mass of the membrane and some of the water outside the mambrane.  $C_m$  represents the CMUT capacitance which is the capacitance measured between the two CMUT electrodes [7].

In table 3.2 the component values for the CMUT model are given [30], [31].

| Component | Value       |

|-----------|-------------|

| $R_a$     | $10k\Omega$ |

| $C_a$     | 6.5 pF      |

| $L_a$     | $156 \mu H$ |

| $C_m$     | 5.5 pF      |

Table 3.2: CMUT model values.

The center frequency for this CMUT model is the frequency at which the imaginary part of  $C_a$  and  $L_a$  cancels each other as shown in (3.1).

$$\left|\frac{1}{j\omega C_a}\right| = |j\omega L_a| \tag{3.1}$$

If this equation is rearranged center frequency is found in (3.2)

$$f_C = \frac{1}{2\pi} \sqrt{\frac{1}{L_a C_a}} = 4.9981 MHz \approx 5 MHz$$

(3.2)

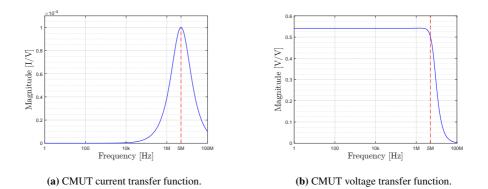

In figure 3.3 the transfer functions of the CMUT model is plotted. 3.3(a) shows the transfer function when current mode readout circuitry is used. In ideal current mode amplifiers the input impedance is zero and so the parallel capacitor  $C_m$  is shorted and the equation is given in (3.3). In figure 3.3(b) the voltage transfer is plotted where the voltage is measured over  $C_m$  and voltage readout is assumed where the input impedance of the amplifier is infinitely high. The voltage transfer function is given in (3.4).

Figure 3.3: Transfer function of the CMUT model.

As seen from 3.3 an ideal voltage readout circuit gives an asymetric characteristic around 5MHz. Also almost half the signal is lost due to current flowing into  $C_m$  while in an ideal current readout the all the current will flow into the amplifier. The transfer function of an ideal current readout circuit shows a peak magnitude at 5MHz, where  $Z_{C_a}$  equals  $Z_{L_a}$ , and the characteristic is symmetric around the center frequency.

$$|H_I(f)| = \left|\frac{I_i(f)}{V_o(f)}\right| = \frac{2\pi f C_a}{\sqrt{(2\pi f R_a C_a)^2 + (1 - (2\pi f)^2 C_a L_a)^2}}$$

(3.3)

$$|H_V(f)| = \left|\frac{V_i(f)}{V_o(f)}\right| = \frac{1}{\sqrt{(2\pi f R_a Cm)^2 + (1 + \frac{C_m}{C_a} - (2\pi f)^2 C_m L_a)^2}}$$

(3.4)

The high source impedance of the CMUT at 5MHz,  $R_a$ , and the transfer function shown in 3.3 makes the current mode amplifier topology most suited as the LNA for this CMUT model and was for this reason chosen.

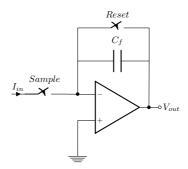

#### 3.2.2 Charge Sampling Amplifier

A current mode topology was chosen for reasons discussed above. The specification also stated that the amplifier should be in discrete time domain. An attractive topology is charge sampling [8]. In addition to relaxed speed demands in the OpAmp, charge sampling lowers the requirements to the sampling switches, compared to voltage sampling, because the voltage at the input node will be almost constant. A single ended charge sampling circuit is shown in 3.4 which consists of an OpAmp, an integrating capacitor,  $C_f$ , and two switches for charging- and reset phase.

Figure 3.4: A single ended active charge sampling amplifier.

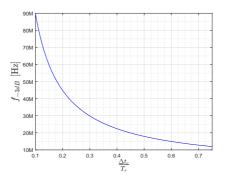

Except for the amplifier, the adjustable parameters in a charge sampling amplifier are the capacitor  $C_f$ , the sampling frequency,  $f_S$ , the charging duration,  $\Delta t_C$ , and the hold duration,  $\Delta t_H$ .