# Implementing a Time Management Unit for the OR1200 Processor.

Kyrre Erlend Aspelund Gonsholt Lars Ødegaard

Electronics System Design and InnovationSubmission date:July 2014Supervisor:Bjørn B. Larsen, IETCo-supervisor:Amund Skavhaug, ITK

Norwegian University of Science and Technology Department of Electronics and Telecommunications

| Title:   | Implementing a Time Management Unit for the OR1200 Processor |

|----------|--------------------------------------------------------------|

| Student: | Kyrre E. A. Gonsholt, Lars Ødegaard                          |

#### Problem description:

The project will focus on implementing a time management unit to improve the realtime capabilities of the OR1200 OpenRISC processor. The implementation will be based on previous implementations of hardware based TMUs, but will be implemented as an integrated part of the processor's internal registers. The TMU will have to be able to work with an existing operating systems scheduler.

This should be verified by hardware simulation, firmware testing and software testing through an existing operating system. The final solution should run on an FPGA.

The project should also consider the usefulness of an hardware solution to the time management problem associated with scheduling.

Responsible professor: Supervisor: Bjørn B. Larsen Amund Skavhaug ii

### Abstract

This thesis presents a Time Management Unit (TMU) that provides assistance to the scheduler and the interrupt handling of a real-time operation system. The unit provides functionality for monitoring task execution time and a mechanism for signalling when a task depletes its resources. This applies to both regular tasks and the handling of sporadic events. By putting the TMU inside a processor core, it has a more predictable impact on the overhead related to task switching.

The implemented TMU is tested as a stand-alone unit with a hardware testbench, and then integrated into the OpenRISC 1000 based OR1200 processor as special purpose registers. The behaviour of OR1200 is verified through hardware simulation, using compiled software as input. The Or1ksim instruction-set simulator is modified to include the TMU functionality, which provides a reference point for the behaviour of the altered processor.

The real-time operating system FreeRTOS is adapted to utilize the functionality of the TMU. Its behaviour is verified through simulation on Or1ksim, simulated hardware and execution on a Cyclone V FPGA.

Analysis of runtime statistics shows that the module is working as expected through all phases of verification, and that it can increase determinism, reliability and user control. Tests have shown that the TMU is able to recover a faulting task from spin-locks and aid in fail-soft operations for software faults. By placing the TMU inside the processor core, a fixed overhead of 131 cycles is achieved during a context switch when no caches are used. iv

# Sammendrag

Denne oppgaven presenterer en tidsovervåkingsenhet (TMU) som assisterer tidsplanleggeren og avbruddshåndteringen i et sanntids-operativsystem. Enheten har funksjonalitet for å overvåke kjøretiden til prosesser og signalere prosessoren når en prosess bruker opp sine tildelte ressurser. Dette gjelder både vanlige prosesser og sporadiske hendelser. Ved å plassere TMUen inne i en prosessor får man en mindre, og mer forutsigbar innvirkning på tidstillegg under bytting av prosesser.

Den implementerte TMUen har blitt testet som en enkeltstående enhet med en testbenk, og deretter integrert inn i den OpenRISC 1000-baserte OR1200 prosessoren som spesial-register. Oppførselen til OR1200 er verifisert av maskinvare-simulering med kompilert programvare som inngangsstimuli. Instruksjonssett-simulatoren Or1ksim er modifisert til å inkludere TMU-funksjonaliteten, som gir et referansepunkt for oppførselen til den modifiserte prosessoren.

Sanntids-operativsystemet FreeRTOS er tilpasset for å kunne ta i bruk funksjonaliteten til TMUen. Oppførselen til FreeRTOS er verifisert ved bruk av instruksjonssettsimulatoren, maskinvare-simuleringer og kjøring på en FPGA.

Analyse av kjøretidsstatistikk viser at enheten fungerer som forventet gjennom alle faser av verifikasjon, og at den øker determinismen, stabiliteten og brukerens kontroll over systemet. Tester har vist at TMUen gjør det mulig å gjenopprette prosesser som har feilet fra en spinn-lås og assisteres i mykfeil-operasjoner for programvarefeil. Ved å plassere TMUen inne i en prosessorkjerne ble det oppnådd en fast tilleggstid på 131 klokkesykler under et kontekstbytte, når det ikke brukes hurtigminne. vi

# Preface

This thesis is the final part of our graduate degree at the department of Electronics and Telecommunications at the Norwegian University of Technology and Science.

The work cover many different areas within digital hardware design, computer architecture and real-time systems programming, this thesis is therefore a collaboration between two students. Both of us are studying digital systems design at the department of Electronics and Telecommunications.

We would like to thank our supervisors Amund Skavhaug, who gave us this assignment and provided guidance and advice throughout the work on this project, and Bjørn B. Larsen who has guided us through the work on this project and through writing the final report.

Trondheim, 29th June, 2014

Kyrre Gonsholt

Lars Ødegaard

viii

# Table of Contents

| Ta       | ble c        | of Cont           | tents                        | xii           |

|----------|--------------|-------------------|------------------------------|---------------|

| Li       | st of        | Figure            | es                           | xiv           |

| Li       | st of        | Tables            | 3                            | xvi           |

| Li       | st of        | $\mathbf{Listin}$ | gs x                         | viii          |

| 1        | Intr<br>1.1  | oducti<br>Motiva  |                              | <b>1</b><br>1 |

|          | 1.1<br>1.2   |                   | contributions                | 1             |

|          | $1.2 \\ 1.3$ |                   | e of the report              | $\frac{1}{2}$ |

| <b>2</b> | Bac          | kgrour            | nd                           | 3             |

|          | 2.1          | Opera             | ting system                  | 3             |

|          |              | 2.1.1             | Real-time operating systems  | 3             |

|          |              | 2.1.2             | Scheduling                   | 4             |

|          |              | 2.1.3             | Processes                    | 5             |

|          |              | 2.1.4             | Exceptions and interrupts    | 9             |

|          | 2.2          | OR120             | 00                           | 11            |

|          |              | 2.2.1             | Overview                     | 13            |

|          |              | 2.2.2             | CPU                          | 13            |

|          |              | 2.2.3             | Caches and memory management | 15            |

|          |              | 2.2.4             | Registers                    | 15            |

|          |              | 2.2.5             | Functional operation         | 16            |

|          |              | 2.2.6             | Exception handling           | 16            |

|          |              | 2.2.7             | External communication       | 18            |

| 3        | Desi         | 0                 | d implementation of the TMU  | 19            |

|          | 3.1          |                   | al description of a TMU      | 19            |

|          | 3.2          | Previo            | us work with a TMU           | 20            |

|          |            | 3.2.1   | On-Line Execution time limiting, 2005                                                                                                 |

|----------|------------|---------|---------------------------------------------------------------------------------------------------------------------------------------|

|          |            | 3.2.2   | A TMU for real-time systems, 2008                                                                                                     |

|          |            | 3.2.3   | Functional specification for a TMU, 2010                                                                                              |

|          |            | 3.2.4   | Hardware implementation of a TMU, 2010 20                                                                                             |

|          | 3.3        | Design  | n of the TMU                                                                                                                          |

|          |            | 3.3.1   | Possible implementations placements                                                                                                   |

|          |            | 3.3.2   | Chosen design 22                                                                                                                      |

|          |            | 3.3.3   | Requirements                                                                                                                          |

|          | 3.4        | Impler  | nentation $\ldots \ldots 22$ |

|          |            | 3.4.1   | Required signals for the TMU                                                                                                          |

|          |            | 3.4.2   | HDL design                                                                                                                            |

|          |            | 3.4.3   | The internals of the TMU                                                                                                              |

|          |            | 3.4.4   | TMU register details                                                                                                                  |

|          |            | 3.4.5   | Operation                                                                                                                             |

|          | 3.5        |         | testbench                                                                                                                             |

|          | 3.6        |         | s of TMU testbench                                                                                                                    |

|          | 0.0        | 3.6.1   | Discussion of the results                                                                                                             |

|          |            | 0.0.1   |                                                                                                                                       |

| <b>4</b> | Inte       |         | g the TMU in OR1200 49                                                                                                                |

|          | 4.1        | Integra | ation into the OR1200 processor $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 49$                                   |

|          |            | 4.1.1   | Modifications to the SPRS module                                                                                                      |

|          |            | 4.1.2   | Modifications to exception module                                                                                                     |

|          |            | 4.1.3   | Modifications to the configuration module                                                                                             |

|          |            | 4.1.4   | Modifications to top level modules                                                                                                    |

|          |            | 4.1.5   | Additions to the configuration file                                                                                                   |

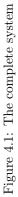

|          | 4.2        | Setting | g up the complete system                                                                                                              |

|          | 4.3        | Setting | g up simulation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $54$                                                            |

|          | 4.4        | OR120   | 00 tests                                                                                                                              |

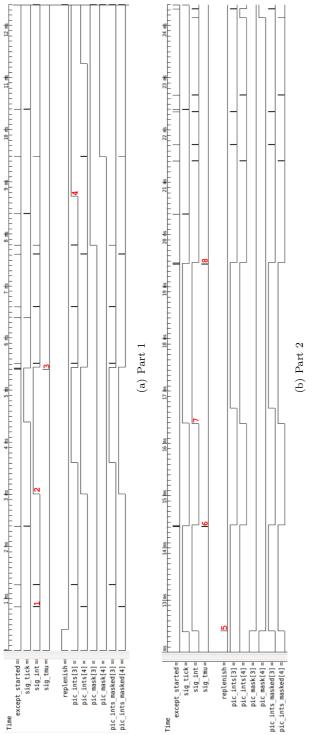

|          |            | 4.4.1   | Full TMU test                                                                                                                         |

|          | 4.5        | Result  | s of the OR1200 tests $\ldots \ldots 57$   |

|          |            | 4.5.1   | Discussion of the results                                                                                                             |

|          | 4.6        | Using   | the TMU                                                                                                                               |

|          |            | 4.6.1   | Task time counting                                                                                                                    |

|          |            | 4.6.2   | Counting interrupts                                                                                                                   |

| _        | 0.1        |         |                                                                                                                                       |

| 5        |            | ksim    | 63                                                                                                                                    |

|          | 5.1        |         | $\begin{array}{cccc} \text{im description} & \dots & $                |

|          |            |         | Downloading, installing and running                                                                                                   |

|          |            | 5.1.2   | Modules                                                                                                                               |

|          |            | 5.1.3   | Running Or1ksim as debug server                                                                                                       |

|          |            | 5.1.4   | Orksim structures                                                                                                                     |

|          |            | 5.1.5   | Or1ksim behavior                                                                                                                      |

|          | <b>_</b> - | 5.1.6   | Exceptions in Or1ksim                                                                                                                 |

|          | 5.2        |         | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                  |

|          |            | 5.2.1   | Exception handling                                                                                                                    |

|          |            | 5.2.2   | SPR                                                                                                                                   |

|   |      | 5.2.3 Programmable interrupt controller | 7  |

|---|------|-----------------------------------------|----|

|   |      | 5.2.4 Time management module            | 8  |

|   |      | 5.2.5 Interrupt generator               | '1 |

|   | 5.3  | TMU driver                              | 2  |

|   | 5.4  | Verifying Or1ksim                       | 2  |

|   |      | 5.4.1 TMU driver                        | 2  |

|   |      | 5.4.2 TMU behavior                      | 4  |

|   | 5.5  | Discussion                              | 7  |

| 6 | Free | eRTOS 7                                 | 9  |

|   | 6.1  | FreeRTOS description                    | 9  |

|   |      | 6.1.1 Introduction                      | 9  |

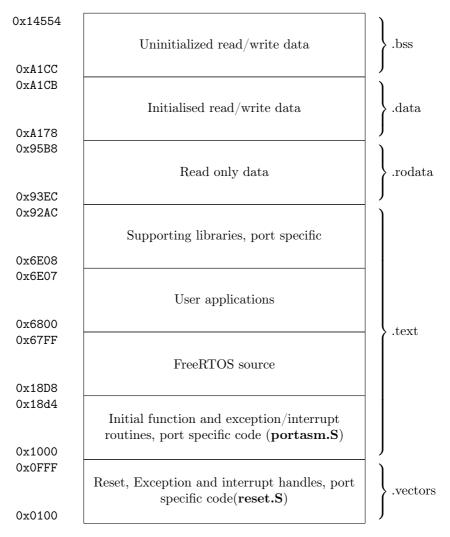

|   |      | 6.1.2 Memory layout                     | 9  |

|   |      | 6.1.3 Naming conventions in FreeRTOS 8  | 0  |

|   |      | 6.1.4 Task                              | 0  |

|   |      | 6.1.5 Exceptions and interrupts         | 4  |

|   |      | 6.1.6 Scheduler                         | 6  |

|   |      | 6.1.7 Context switch                    | 7  |

|   | 6.2  | FreeRTOS modifications                  | 0  |

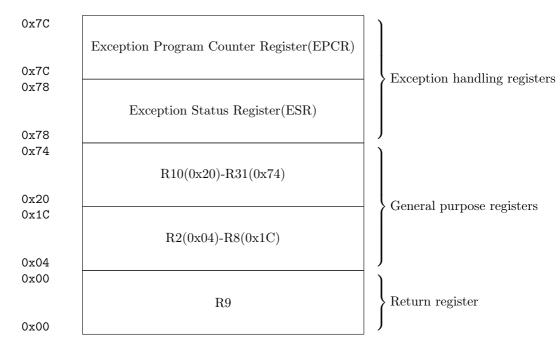

|   |      | 6.2.1 Context layout                    | 0  |

|   |      | 6.2.2 xTMUStruct                        | 1  |

|   |      | 6.2.3 Task control block                | 2  |

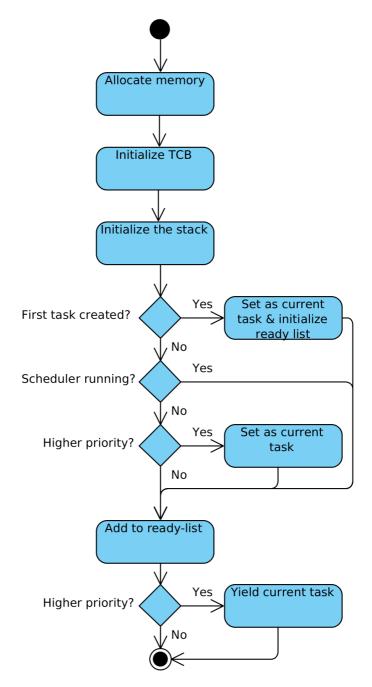

|   |      | 6.2.4 Task creation                     | 2  |

|   |      | 6.2.5 TMU exception handling            | 3  |

|   |      | 6.2.6 Critical sections                 | 7  |

|   | 6.3  | Setting up FreeRTOS to use the TMU      | 7  |

|   | 6.4  | Verifying FreeRTOS                      | 8  |

|   | 6.5  | Discussion                              | 0  |

| 7 | Test | ing the full system 10                  | 3  |

|   | 7.1  | Equipment                               | 3  |

|   | 7.2  | Resource usage                          | 3  |

|   | 7.3  | TMU functionality test                  | 5  |

|   |      | 7.3.1 Test setup                        | 15 |

|   |      | 7.3.2 Results                           | 6  |

|   | 7.4  | Overhead                                |    |

|   |      | 7.4.1 Testing TMU overhead 11           |    |

|   |      | 7.4.2 Overhead test results             |    |

|   | 7.5  | Processor utilization                   |    |

|   |      | 7.5.1 Expected results                  |    |

| 8 | Dise | cussion 12                              | 3  |

| - | 8.1  | TMU implementation and integration      | _  |

|   | 8.2  | Functionality test                      |    |

|   | 8.3  | Overhead test results   12              |    |

|   | 8.4  | Processor utilisation                   |    |

|    | 8.5                    | Real-time effects                            | 126   |

|----|------------------------|----------------------------------------------|-------|

| 9  |                        | clusion                                      | 129   |

|    | 9.1                    | Further work                                 | 130   |

| Bi | bliog                  | raphy                                        | 132   |

| A  | ppen                   | dix                                          | Ι     |

| A  | $\mathbf{T}\mathbf{M}$ | U verilog code                               | Ι     |

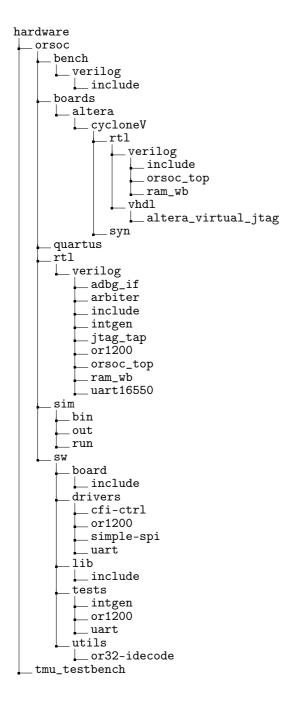

| в  | Fold                   | ler layout                                   | XI    |

|    | B.1                    | Test results                                 | XII   |

|    | B.2                    | Hardware files                               | XIII  |

|    | B.3                    | Or1ksim files                                |       |

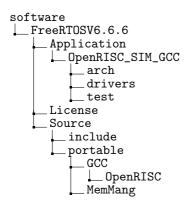

|    | B.4                    | Software files                               | XVI   |

| С  | Full                   | system setup X                               | VII   |

|    |                        | Simulation                                   |       |

|    | -                      | C.1.1 Tools                                  |       |

|    |                        | C.1.2 TMU testbench                          |       |

|    |                        | C.1.3 Full system tests                      |       |

|    | C.2                    | Compiling for FPGA                           |       |

|    | C.3                    | Uploading and running programs on the system |       |

|    |                        | Building and running Or1ksim                 |       |

|    | C.5                    |                                              |       |

| D  | Or1                    | ksim testing X                               | XIII  |

|    | D.1                    | 5                                            | XXIII |

|    | D.2                    | FreeRTOS test                                |       |

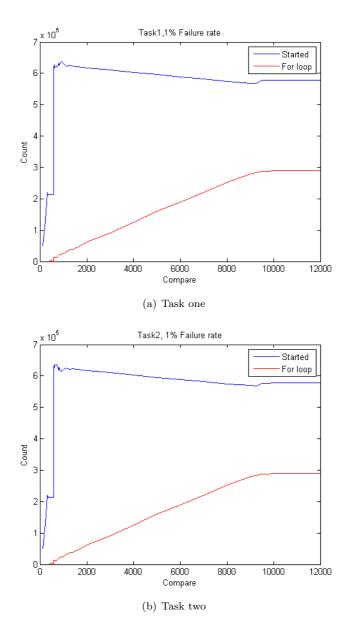

|    | D.3                    | Processor utilisation Figures                |       |

|    |                        | Processor utilisation results                |       |

# List of Figures

| 2.1  | Example of Process Control Block                                                                                                              |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2  | Process state transitions                                                                                                                     |

| 2.3  | Process Control Block in Memory                                                                                                               |

| 2.5  | Interrupt handling 12                                                                                                                         |

| 2.6  | Interrupt Sequence                                                                                                                            |

| 2.7  | OpenRISC 1200 architecture 14                                                                                                                 |

| 2.8  | OR1200 CPU block diagram                                                                                                                      |

| 3.1  | Illustration of the TMU and connected modules                                                                                                 |

| 3.2  | SPR operation                                                                                                                                 |

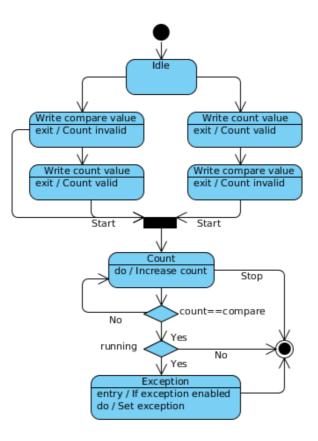

| 3.3  | Couting task time                                                                                                                             |

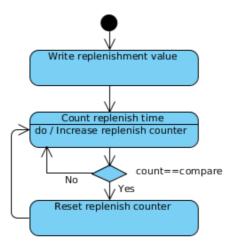

| 3.4  | Counting interrupt replenishment                                                                                                              |

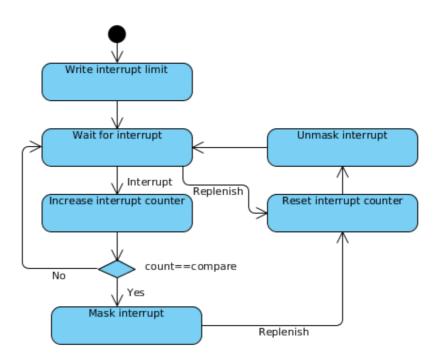

| 3.5  | Counting interrupts 35                                                                                                                        |

| 3.6  | Loading a value into replenishment register                                                                                                   |

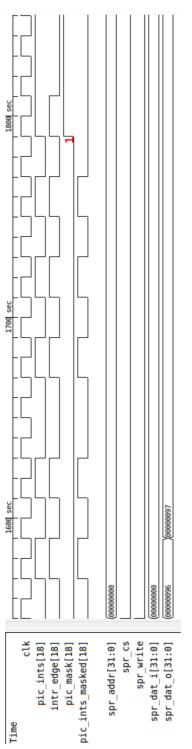

| 3.7  | Masking an interrupt                                                                                                                          |

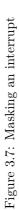

| 3.8  | Replenishment of the interrupt counter                                                                                                        |

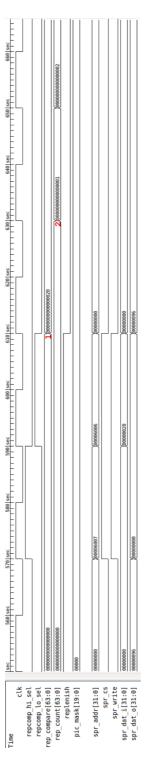

| 3.9  | Loading values for task execution time counting                                                                                               |

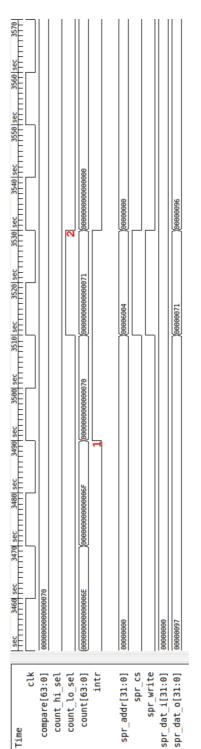

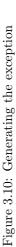

| 3.10 | Generating the exception                                                                                                                      |

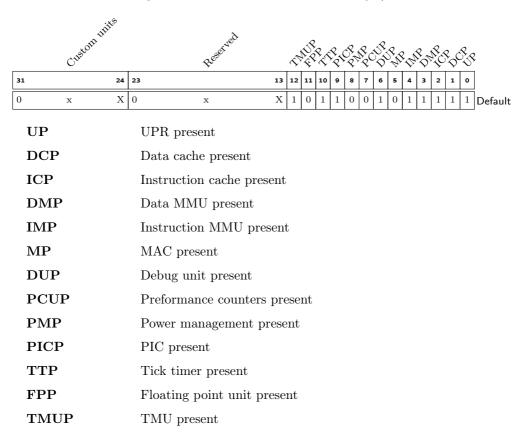

| 4.1  | The complete system                                                                                                                           |

| 4.2  | Makefile simulation flow                                                                                                                      |

| 4.3  | Key events from the TMU full test                                                                                                             |

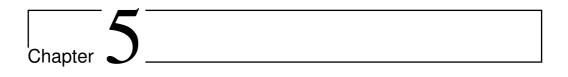

| 5.1  | exec_main                                                                                                                                     |

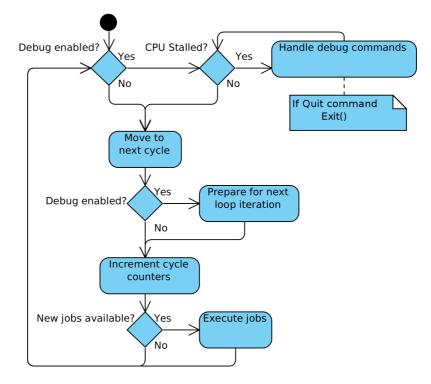

| 5.2  | except_handle                                                                                                                                 |

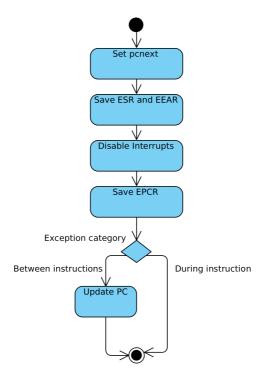

| 5.3  | $\operatorname{tmu}_{\operatorname{main}}$                                                                                                    |

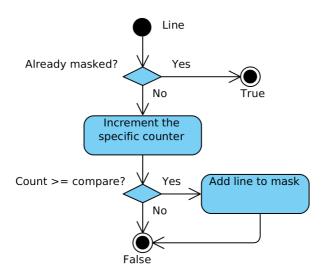

| 5.4  | $\mathbf{tmu\_int\_filter} \dots \dots$ |

| 6.1  | Example of FreeRTOS memory layout                                                                                                             |

| 6.2  | Context layout                                                                                                                                |

| 6.3  | Task Create         85                                                                                                                        |

|      |                                                                                                                                               |

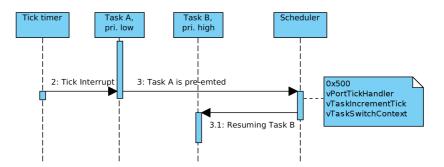

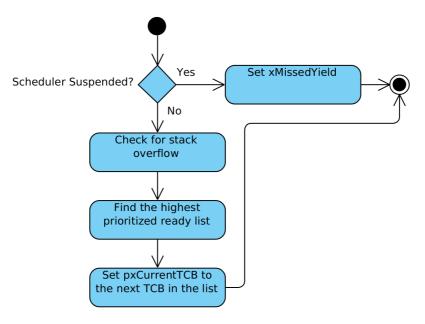

| $\begin{array}{c} 6.5 \\ 6.6 \end{array}$ | Path of the external interrupt in FreeRTOSTick timer exception sequencevTaskSwitchContextModified context layout | 87<br>89   |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------|

| $7.2 \\ 7.3$                              | Cyclone V GX starter kit                                                                                         | 116<br>119 |

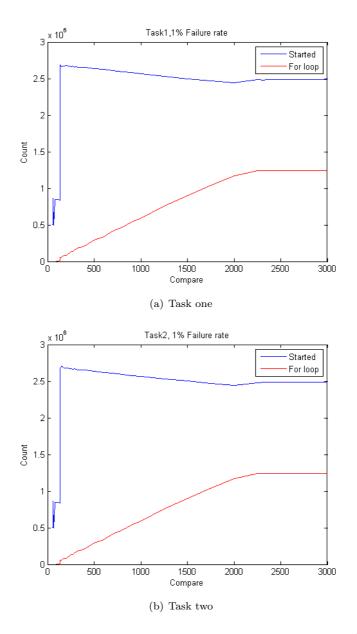

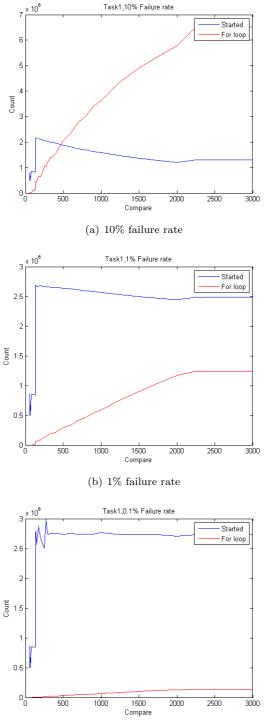

| D.1                                       | Task 1 started versus time spent in the for loop, all failure rates, Or1ksim                                     | XXVII      |

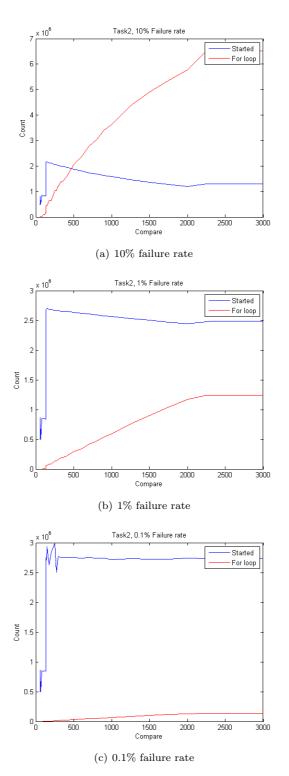

D.2 Task 2 started versus time spent in the for loop, all failure rates, Or1ksim XXVIII

# List of Tables

| $2.1 \\ 2.2 \\ 2.3$ | OR1200 execution times16Exceptions in OR120017Wishbone signals18 |

|---------------------|------------------------------------------------------------------|

| 3.1                 | Spr signals                                                      |

| 3.2                 | TMU system signals                                               |

| 3.3                 | TMU register list                                                |

| 3.4                 | Logic function for TMU features                                  |

| 3.5                 | Tests performed by the TMU testbench                             |

| 4.1                 | Paramters for the TMU                                            |

| 4.2                 | Tests performed by the SoC testbench                             |

| 4.3                 | Tests performed by the SoC testbench for the TMU 57              |

| 4.4                 | Parameters for the full TMU test                                 |

| 4.5                 | TMU full test events    59                                       |

| 5.1                 | A selection of variables and structures in Or1ksim               |

| 5.2                 | Configurable variables for the TMU in the <b>config</b> -struct  |

| 5.3                 | Configurable variables for the TMU in <b>sim.cfg</b>             |

| 5.4                 | Configurable variables in <b>sim.cfg</b>                         |

| 5.5                 | Functions available in the TMU driver and description            |

| 5.6                 | TMU driver special cases tests                                   |

| 5.7                 | Task timer tests   75                                            |

| 5.8                 | Interrupt filter tests                                           |

| 6.1                 | Naming conventions in FreeRTOS 80                                |

| 6.2                 | Excerpt of TCB from task.h 82                                    |

| 6.3                 | Parameters for vTaskCreate                                       |

| 6.4                 | <b>xTMUStruct</b>                                                |

| 7.1                 | TMU resource usage                                               |

| 7.2        | Test parameters                                                                                                                   | 106   |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|

| 7.3        | Icarus verilog result, 200 ticks                                                                                                  | 107   |

| 7.4        | Or1ksim test results, with TMU and critical section                                                                               | 107   |

| 7.5        | Or1ksim test results, with TMU, without critical section                                                                          | 108   |

| 7.6        | Or1ksim test results, without TMU and critical section                                                                            | 109   |

| 7.7        | Or1ksim result, second round: TMU disabled, short interrupt period, 20                                                            |       |

|            | 000 ticks                                                                                                                         | 109   |

| 7.8        | Or1ksim result: TMU disabled, short interrupt period, <i>PICSR</i> write back                                                     |       |

|            | moved, 20 000 ticks                                                                                                               | 110   |

| 7.9        | Or1ksim result, second round: TMU enabled, short interrupt period, 20                                                             |       |

|            | 000 ticks                                                                                                                         | 110   |

| 7.10       | Or1ksim test results, without TMU and critical section, longer minimal                                                            |       |

|            | interrupt time-out                                                                                                                | 110   |

| 7.11       | FPGA test results, with TMU and critical section                                                                                  | 111   |

| 7.12       | FPGA test results, with TMU, without critical section                                                                             | 111   |

| 7.13       | FPGA test results, without TMU and critical section                                                                               | 112   |

| 7.14       | FPGA test results, without TMU and critical section, longer minimal                                                               |       |

|            | interrupt time-out                                                                                                                | 112   |

| 7.15       | Overhead test parameters                                                                                                          | 113   |

|            | Execution time analysis for the overhead loop                                                                                     | 114   |

|            | Overhead test results                                                                                                             | 115   |

|            | Overhead test results                                                                                                             | 115   |

|            | Instructions per functions                                                                                                        | 117   |

|            | Processor utilization results, Or1ksim                                                                                            | 118   |

| 7.21       | Processor utilization results, FPGA                                                                                               | 120   |

| D 1        | Processon utilization regults Task 1 100 failure rate Ortheirs                                                                    | XXIX  |

|            | Processor utilisation results, Task 1, 10% failure rate, Or1ksim Processor utilisation results, Task 2, 10% failure rate, Or1ksim |       |

| D.2<br>D.3 | Processor utilisation results, Task 2, 10% failure rate, Or1ksim Processor utilisation results, Task 1, 1% failure rate, Or1ksim  |       |

| D.3<br>D.4 | Processor utilisation results, Task 1, 1% failure rate, Or1ksim                                                                   |       |

| D.4<br>D.5 | Processor utilisation results, Task 2, 1% failure rate, Or1ksim                                                                   |       |

| D.5<br>D.6 | Processor utilisation results, Task 1, 0.1% failure rate, Or1ksim                                                                 |       |

| -          | Processor utilisation results, Task 2, 0.1% failure rate, FPGA                                                                    |       |

|            | Processor utilisation results, Task 1, 1% failure rate, FPGA                                                                      |       |

| D.8        | r to cessor utilisation results, Task 2, 170 failure rate, rrGA                                                                   | ΛΛΛ 1 |

# Listings

| 3.1  | TMU module declaration                                            |

|------|-------------------------------------------------------------------|

| 3.2  | Read and write SPR                                                |

| 3.3  | Setting operation modes                                           |

| 3.4  | Implementation of count and compare registers                     |

| 3.5  | Implementation of replenishment count                             |

| 3.6  | Implementation of interrupt count                                 |

| 3.7  | Masking interrupts                                                |

| 4.1  | Writing TMU exception bit in SR                                   |

| 4.2  | Decoding TMU exception                                            |

| 4.3  | Decoding TMU exception                                            |

| 4.4  | Additionds to <b>0r1200</b> cpu                                   |

| 5.1  | Results from the TMU driver test on Or1ksim                       |

| 5.2  | Results from the TMU task timer test on Or1ksim                   |

| 5.3  | Results from the TMU interrupt filter test on Or1ksim, state zero |

| 5.4  | Results from the TMU interrupt filter test on Or1ksim, state one  |

| 5.5  | Results from the TMU interrupt filter test on Or1ksim, state two  |

| 6.1  | portSAVE CONTEXT-macro                                            |

| 6.2  | portRESTORE CONTEXT-macro                                         |

| 6.3  | xTMUStruct                                                        |

| 6.4  | pdExceptionCode                                                   |

| 6.5  | _except_f00                                                       |

| 6.6  | vPortTMUExceptionHandler                                          |

| 6.7  | portRESTART_TMU                                                   |

| 6.8  | $portSTART_T\overline{M}U$ , starts the TMU                       |

| 6.9  | portSTOP $\overline{T}MU$ , stops the TMU                         |

| 6.10 | portSAVE CONTEXT                                                  |

| 6.11 | portRESTORE CONTEXT                                               |

| 6.12 | $\operatorname{tmu}$ except                                       |

|      | Excerpt from vTaskResumeAll, line 1097-1099 in task.c             |

| 6.14 | Results from the FreeRTOS test on Or1ksim                         |

| 6.15 | Results from the FreeRTOS test on Or1ksim                         |

| 7.1    | Overhead test function loop assembly 1 | 114   |

|--------|----------------------------------------|-------|

| 7.2    | Overhead test function loop C          | 114   |

| listin | $ m mgs/or 1200\_tmu.v$                | Ι     |

| D.1    | Results from the TMU test on Or1ksim X | XXIII |

D.2 Results from the FreeRTOS test on Or1ksim

#### LISTINGS

# Abbreviation

- **ALM** Adaptive Logic Module

- $\label{eq:cpu} \textbf{CPU} \quad \text{Central Processing Unit}$

- $\textbf{DTLB}\ \text{Data TLB}$

- **EEAR** Exception Effective Address Register

- **ELF** Executable and Linkable Format

- **EPCR** Exception Program Counter Register

- **ESR** Exception Status Register

- $\label{eq:FIFO} First-In-First-Out$

- FPGA Field Programmable Gate Array

- **FPP** Fixed Priority Preemptive

- **GPR** General Purpose Register

- **HDL** Hardware Descriptive Language

- **ISA** Instruction Set Architecture

- **ITLB** Instruction TLB

- **LED** Light Emitting Diode

- LIFO Last-In-First-Out

- LRU Least-Recently Used

- LSU Load/Store Unit

- LUT Look-Up Table

- **MAC** Multiplier Accumulator

- **MMU** Memory Management Unit

- $\ensuremath{\mathsf{MUX}}$  MultipleXer

- **OS** Operating System

- **PC** Program Counter

- **PC** Process Control Block

- **PIC** Programmable Interrupt Controller

- $\ensuremath{\mathsf{PICSR}}$  PIC Status Register

- **PSW** Program Status Word

- **PTE** Page Table Entry

- **RMS** Rate Monotonic Scheduling

- **RSP** Remote Serial Protocol

- ${\sf RTOS}\,$  Real-Time Operating System

- **SPR** Special Purpose Register

- **TCB** Task Control Block

- **TLB** Translation Look-aside Buffer

- **TMU** Time Management Unit

- **UART** Universal Asynchronous Receiver/Transmitter

- **UPR** Unit Present Register

- **USB** Universal Serial Bus

- **VR** Version Register

- $\ensuremath{\mathsf{WCET}}$  Worst Case Execution Time

### | Chapter

# Introduction

# 1.1 Motivation

In a real-time system the correct behaviour of a task is dependent on both the logic result of its computation and the time of which the result arrives[1]. Failure to meet a deadline can in some cases have very severe consequences, thus the quality of a real-time system is highly dependent on its timing capabilities.

Scheduling of tasks in real-time systems is usually dependent on the worst-case execution time (WCET) of that task[13], but finding this measure may in some cases be very challenging. The average execution time will often be much smaller then WCET, and by scheduling tasks based on the worst-case situation the processor utilization will be poor. If scheduling is based on the average execution time, deadlines may be lost in cases where a task overruns this time. By using execution time control, less conservative budgets than WCET can be used and the overruns can be handled dynamically. To allow for this option, a unit in the system has to provide information about the elapsed time of the running tasks and interrupt the processor when an overrun has to be handled.

This thesis will present a solution for a unit designed to monitor task execution time called Time Management Unit (TMU) implemented in hardware as a part of an OR1200 processor. The unit will measure the execution time of running tasks and measure the arrival interrupts. By implementing a TMU inside a processor core it is believed that a smaller and more predictable overhead than a bus implementation can be achieved.

# **1.2** Main contributions

The main contributions from this thesis is the design and implementation of a TMU as a part of the OR1200 processor, modifying the OpenRISC ISA simulator Or1ksim to include this TMU and modifying FreeRTOS to take advantage of the functionality provided by the TMU.

Tests are provided to verify the behaviour of the TMU as a stand-alone unit, as a part

of the processor and as a part of Or1ksim. The modified FreeRTOS is tested through Or1ksim, and is then executed on a computer system, containing the modified OR1200, on an FPGA.

The complete system is tested through FreeRTOS on both Or1ksim and on an FPGA. Test were included to verify the behaviour of the TMU as well as demonstrates some of the features it provides.

# 1.3 Outline of the report

The first chapter is an introduction chapter containing information about the report. After the introduction, relevant background theory necessary to understand the report is presented. Chapters 3 to 6 outlines the development of different parts of the system, where:

Chapter 3 describes the functionality, development and testing of the TMU.

- **Chapter 4** describes the integration of the TMU into a larger system, and the testing of this system.

- **Chapter 5** describes the operation and modifications to the instruction set simulator for the OpenRISC architecture.

- Chapter 6 describes the operation and modifications done to the real-time operating system FreeRTOS.

Chapter 7 describes the testing of the full system, using the modified processor core and the adapted version of FreeRTOS, it also presents the results from these performed in the different environments. Chapter 8 has a discussion of the implementation and test results of the whole system. The final chapter concludes this thesis, and provides some points for further work on this subject.

Each of the development chapters starts with a short introduction and summary. Throughout the thesis a lot of results and decisions are presented as the report progress, smaller discussions surrounding these will be done where the result or decision is presented. Larger discussions will be made at the end of the chapter. Chapter 2

# Background

# 2.1 Operating system

This section will to give the reader an understanding of the basic principles relied on in the chapter describing FreeRTOS.

An Operating system(OS) is the collection of software that provides a layer of abstraction between user applications and hardware. It manages resources and provides services like memory management, scheduling and input/output-control. [14, ch.2.1].

#### 2.1.1 Real-time operating systems

For real-time systems, the correctness of the results depends not only on the logical result, but also at which time the result arrives [14, p.463]. The degree of how dependant a task is on timing is divided into two categories, hard and soft real-time tasks. For hard realtime tasks the deadline is essential, a missed deadline can have fatal consequences for the system. Soft real-time tasks on the other hand, relates to preferred deadlines, missing one is not severe, but there should still be made an effort to schedule the task within its deadline. Real-time tasks have another characteristic, whether it is periodic or aperiodic. Periodic tasks has a period of time in which they must be scheduled, or scheduled an exact number of units apart. Aperiodic tasks has an absolute time which they must start or finish before. A real-time operating system (RTOS) can be described with having unique requirements in five general areas [14, p.463]

#### Determinism

Determinism refers to what degree an OS performs operations at specific times, or within time intervall. Like issuing or acknowledging an interrupt.

#### Responsiveness

Related to determinism, but is rather a measure of how long, from acknowledging, it takes to handle the event.

#### User control

How much control does the user have over aspects like scheduling and memory.

Normally a standard OS allows for much less user control than an RTOS.

#### Reliability

Errors in a real-time systems can end in degraded functionality and performance, while for a standard OS it might be solved by simply rebooting, which may not be an option for an RTOS.

#### Fail-soft operation

To which degree can the system fail to preserve as much capability and data as possible.

To meet these requirements an RTOS usually include the following [14, p.465]:

- Fast task switch

- Small size

- Low response time for external events

- Multitasking, with synchronization tools like semaphores, signals and events

- Use of special sequential files for fast data storage

- Preemptive scheduling based on priority

- Functionality for task delay

- Special alarms and time-outs

The most important part for an RTOS is the scheduler. Real-time scheduling is explained shortly.

### 2.1.2 Scheduling

In general the term scheduling is used for the division of resources over a period of time[12]. Two main categories of scheduling types are :

#### **Pre-emptive:**

A task can and will be switched out for a higher prioritized task should one become available.

#### **Co-operative:**

Tasks are responsible for themselves releasing control of the processor.

#### Scheduler in Real-time operating systems

For real-time scheduling Stallings[14, p.467] lists four approaches:

#### Static table-driven:

Performing scheduling analysis prior to runtime, the resulting table decides the scheduling order.

#### Static priority-driven preemptive:

Performing a scheduling analysis prior to runtime and assigning priorities, which is used to determining execution order during runtime.

#### Dynamic planning-based:

Scheduling analysis is done during runtime, new tasks are only accepted for execution if there is sufficient resources available.

#### 2.1. OPERATING SYSTEM

#### Dynamic best effort:

All tasks are accepted, the system tries to meet all deadlines and aborts tasks with missed deadlines.

The different approaches are used in different scheduling policies. The scheduling policy used in FreeRTOS is known as Fixed Priority Preemptive Scheduling(FPP), this falls under the *static priority-driven preemtive*-approach. During implementation the user performs an analysis of which priority each task should have. This is very similar to Rate Monotonic Scheduling(RMS). RMS is basically assigning priorities to task disproportional to their period, low period - high priority [14, p.472]. This policy also provides a way of analysing the the schedulability of a set of tasks. This is done by calculating the combined processor utilization of the set of tasks over a period. This relies on good estimates of a tasks execution time and period. It can be shown that the set of *n* tasks are schedulable within a period if the combined processor utilization is below  $n(2^{1/n} - 1)$  over the same period.

One of the most basic scheduling policies is the round robin scheduler. Here processes are given resources in the order at which they arrive, first-in-first-out(FIFO)[14]. Each process will receive a pre-determined amount of time, regardless of the actual runtime needed by the process. When its timing budget is depleted, a clock interrupt will trigger a context switch to the next process in the queue. The switched out process then enters the back of the ready/blocked queue. FPP is very similar to round robin, the difference is that for FPP the task with the highest priority gets control of the CPU next.

#### 2.1.3 Processes

The following section is based on chapter 3 in Operating Systems: Internals and Design Principles by William Stallings [14].

A process is defined by Stallings as "The entity that can be assigned to and executed on a processor", among other definitions. This entity is a collection of data and instructions used to describe itself and its behaviour, this may contain the following:

#### Identifier:

A unique identifier for the process.

State:

Showing the current state of the process.

Priority:

Priority of the process.

#### **Program Counter:**

The address of the next instruction to be executed.

#### Memory pointers:

Pointers to the location of instructions, data and shared data allocated to the process.

#### Context data:

Data present in the processor's registers during execution.

#### I/O Status:

Includes current I/O requests and accessible I/O devices/files.

| Identifier             |

|------------------------|

| State                  |

| Priority               |

| Program Counter        |

| Memory Pointers        |

| Context Data           |

| I/O Status             |

| Accounting Information |

|                        |

|                        |

Figure 2.1: Example of Process Control Block

#### Accounting Information:

May include information such as processor time, real-clock time, time limits and other tracing information.

All this information is gathered in a data structure called process control block, Figure 2.1. This block contains enough information about the process to allow it to be interrupted and resumed later as if the interrupt never occurred. This is what allows for multiprocessing systems. When an interrupt arrives, the context data and program counter are saved in their respective memory locations and the state of the process is updated to blocked or ready. At this point it is the operating systems job to load a new process onto the processor.

#### **Process States**

This section is a summary of information relevant to this thesis, for the full explanation of all states and transitions refer to chapter 3.2-4 in the Operating Systems-textbook by William Stallings [14].

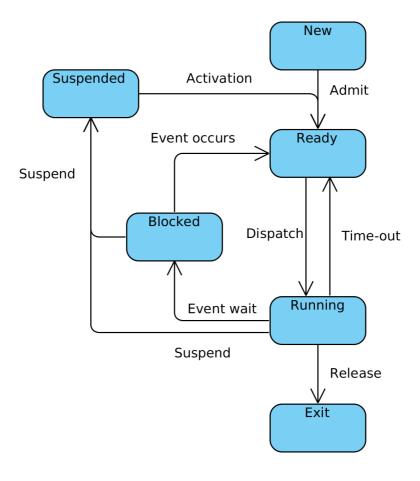

During the life cycle of a process it may go through multiple states, new, ready, running, blocked and exit. These states are organized by different lists managed by the operating system. When a process is created it is added to the new-list, once the operating system decides it has sufficient resources available to accommodate an extra process, the process will be added to the ready-list. The different states and what they represent is listed below, Figure 2.2 shows the transitions between the states.

#### New:

Process control block is initialized and the process is ready to enter the main execution loop, *ready-running*.

#### 2.1. OPERATING SYSTEM

#### Ready:

The process is ready to enter the execution state, Running.

#### **Running**:

Indicates that the process is currently executing on a processor.

#### Blocked:

The process is waiting on an event such as timing-event, I/O- or file-access

## Suspended:

The process is placed outside main execution loop, waiting for some event or resources becoming available.

#### Exit:

Indicates that the process is terminated and awaiting cleanup.

Figure 2.2: Process states transitions, based on [14, Fig.3.9]

### **Process Creation**

Creating a process can be done through the following steps, but not strictly locked to the following order [14, p.156]:

- 1. Assign a unique identifier.

- 2. Allocate memory to hold the new process.

- 3. Initialize the process control block.

- Setting the program counter to the start of the program's instructions

- Set Priorities and resource rights

- Set stack pointers to the correct memory area

- Set the process state

- 4. Add the process to the necessary lists and data structures

### **Process Switching**

There are multiple mechanics within an operating system that may force a process switch [14, p.157].

#### Timing interrupt:

If there is a time budget in place, the operating system may decide that the currently running process has exceeded its time limit and therefore want to switch process.

#### I/O interrupt:

Upon handling an interrupt, a higher priority task may have been unblocked. After switching back from the interrupt the OS will load the higher prioritized task, assuming pre-emptive kernel and no temporary raised priority levels.

#### Process yielding:

A process can issue commands that directly or indirectly forces a process switch, yielding or issuing a request to another process or I/O-device, thus blocking itself.

When a process switch is initiated an operating system follows these steps to switch out the currently executing process[14, p.159]:

- 1. Save the current context, including the program counter and other registers.

- 2. Update the process control block that is currently loaded on the processor. Setting the new state, and explaining the reason for this process to leave the running state and accounting information.

- 3. Add the process to the correct queue(*ready/blocked/suspended/exit*)

- 4. Select the next process

- 5. Update the selected process control block, including setting the state to running.

- 6. If required, update memory management structures.

- 7. Restore the context: Setting the program counter and registers to the values from the time this process was switched out of the running state.

#### Memory

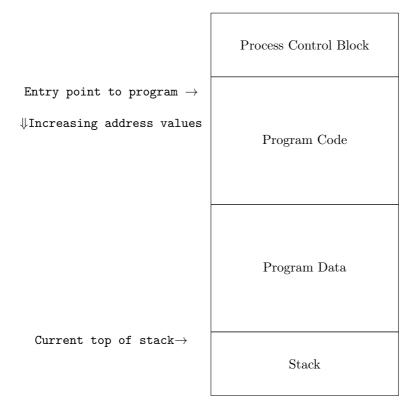

For the programmer the memory layout of a process can be seen as something like Figure 2.3. The layout in physical memory may differ, depending on the memory placement

Figure 2.3: Process Control Block in Memory, based on [14, Fig.7.1]

algorithms used [14, ch.7.2-4]. The figure shows the process control block followed by the program code, program data and finally the process stack. The program code contains the binary code for all the instructions in the order of execution. Program data contains all variables and structures. The stack is a first-in-last-out (FILO) data structure which is used to allocate local variables, and grows in respect to function calls and returns [8, p.A-27]. Depending on the architecture a stack may grow upwards or downwards, meaning new elements will have a higher or lower address related to the stackpointer. Local variables are stored with an offset to the stack pointer.

#### 2.1.4 Exceptions and interrupts

The terminology exception and interrupt are not used consistently throughout litterature, in this thesis these definitions will be primarily used:

#### Exception:

An internal event inside the CPU.

#### Interrupt:

Figure 2.4: S

imple instruction cycle with interrupt]Simple instruction cycle with interrupt, based on [14, Fig.1.7]

An external event which signals the CPU.

Typical interrupts would be environmental events, a UART module signalling that it is done with the transfer. Examples of exceptions are errors in alignment, meaning the CPU is trying to read/write to some address that is not a power of two or suitable for the data size.

Hennessy and Patterson lists these qualities an exception/interrupt can have [8, p.C-44]:

#### Synchronous vs. asynchronous:

If the exception occurs at the same time during execution, assuming the same data and memory layout, then the exception is synchronous, otherwise it is asynchronous. Asynchronous events can be handled after the current instruction, thus they are easier to handle.

#### User requested vs. coerced:

User requested exceptions are predictable in nature. Coerced are exceptions from some module that is not directly under the users control.

#### User maskable vs. user nonmaskable:

If an interrupt can be masked by a user task, it is user maskable. The effect of this is whether or not the hardware will respond to signals from the masked source.

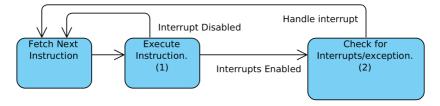

#### Within vs. between instructions:

Wheter or not an exception prevents the completion of the current instruction(1), or is recognized between instructions(2). Figure 2.4 shows a simplified model of the instruction cycle.

#### Resume vs. terminate

If the exception/interrupt causes the current  $\rm program/process$  to terminate or allows it to continue after handling the event.

#### Handling Exceptions and Interrupts

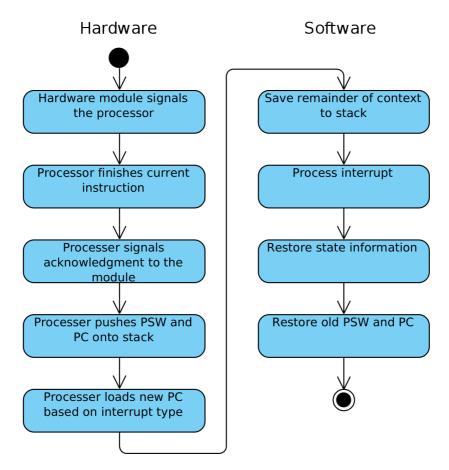

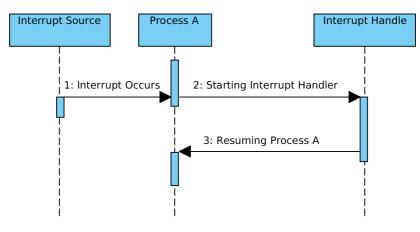

During the normal execution of a task an interrupt may occur. Figure 2.6 shows Process A in normal execution until an interrupt source requires handling. The interrupt source

#### 2.2. OR1200

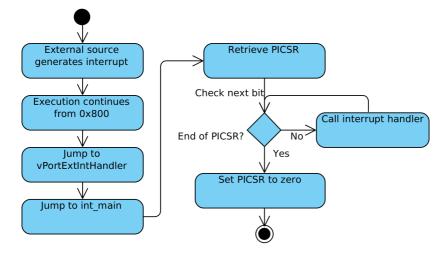

does this by e.g. setting a bit in a status register. If interrupts are enabled, the CPU will check this register during the instruction cycle, Figure 2.4. The interrupt raised in Figure 2.6 is registered in step two in the instruction cycle. The interrupt is handled through the following steps [14, p.39], Figure 2.5:

- 1. Interrupt source signals the processor.

- 2. The processor finishes the current instruction before responding.

- 3. The processor checks the status registers to determine if there has been issued an interrupt. It also checks which source generated the interrupt and sends an acknowledgement so that the source can remove its signal.

- 4. The processor prepares itself to execute the interrupt handler. It starts with saving the information that is needed to resume the currently running process from the point the interrupt occurred. The minimum information required is the program status word (PSW)<sup>1</sup> and program counter. These can be stored on a control stack.

- 5. The program counter is set to the start of the operating systems interrupt routine, either a specific PC for that specific interrupt handler or a generic handler which in turn may call a specific routine.

- 6. The instruction cycle continues, fetching the instruction at the new PC.

- 7. The first instructions in the interrupt routine must save the registers and other essential information about the last process to the stack. The stack pointer is updated and the program counter is set to the code handling the actual interrupt.

- 8. Depending on the interrupt source this may be a user defined function or a predefined routine inside the operating system.

- 9. Upon completing the interrupt service, the register values of the last process will be restored from stack.

- 10. And finally the PSW and program counter is retrieved from the stack. This allows for the interrupted process to start from the point of interrupt as if nothing happened.

An exception is handled very much in the same way, the difference is exceptions usually have specific operating system routines unlike interrupts which usually shares one or more generic routines.

# 2.2 OR1200

The processor core which will host the TMU is the OpenRISC 1000 based OR1200. This processor was chosen because it is an open-sourced and free processor, and it is supported by the GCC compiler. It also has support for programmable interrupts, 32-bit

$<sup>^1{\</sup>rm The}$  PSW contains status information about the current process e.g. status register, memory usage information, condition codes.

Figure 2.5: Interrupt handling, based on [14, Fig.1.10]

Figure 2.6: Interrupt Sequence

instructions and can be programmed on an FPGA. More details about the choice of the hardware platform can be found in the preliminary study for this thesis[6].

This section is a summary of the most relevant information found in the OpenRISC 1200 IP Core specification[9].

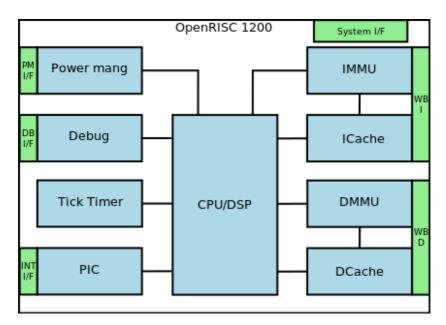

#### 2.2.1 Overview

The OR1200 processor is an implementation of the OpenRISC 1000 architecture[9]. It is a 32-bit scalar RISC processor with Harvard microarchitecture, five stage pipeline and virtual memory support. The processor implements the ORBIS32 instruction set.

It has separate Memory Management Units (MMU) for instructions and data, as well as separate instruction and data caches. Both the instruction and data caches are 1-way direct-mapped of 8KB, with 16-byte line size.

The core also contains a power management unit, a tick timer, a programmable interrupt controller and a debug unit. An illustration of the architecture of the OR1200 is shown in Figure 2.7

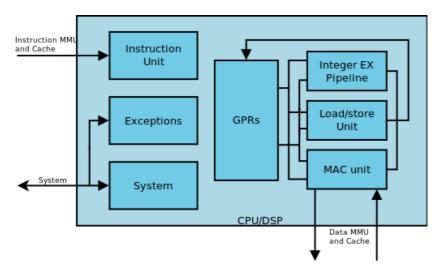

### 2.2.2 CPU

The central processing unit of the OR1200 contains the following:

- Instruction unit

- Exception unit

- System unit

- General purpose registers

- Integer execution pipeline unit

- Multiplier accumulator (MAC) unit

- Load/Store unit

Figure 2.7: OpenRISC 1200 architecture

Figure 2.8: OR1200 CPU block diagram

#### 2.2. OR1200

**Instruction unit** The Instruction Unit implements the basic instruction pipeline. It has a line to the instruction MMU and cache units, and is able to execute conditional branch and unconditional jump statements.

**GPR** The general purpose register(GPR) file is implemented as two synchronous dualport memories. It has a capacity of 32 words, where one word is 32 bit.

**Load/Sore unit** The Load/Store unit is responsible for all data transfers between the GPRs, the data cache and memory. It implements all load/store instructions in hardware, has an address entry buffer and the units operation is pipelined.

**Integer EX** The Integer Execution Pipeline performs 32-bit integer instructions. It handles arithmetic, compare, logical and rotate/shift instructions.

${\bf MAC}~$  The Multiplier Accumulator (MAC) unit is fully pipelined and executes DSP MAC operations that are 32x32 bit with 48-bit accumulator.

**System unit** The system unit is responsible for connecting all signals of the CPU that are not connected through other interfaces. it also contains some special purpose registers.

**Exceptions** The Exceptions unit in the CPU generates core exceptions, i.e. external interrupts and internal errors.

# 2.2.3 Caches and memory management

Since the OR1200 has a Harvard architecture, it has separate caches and MMUs for instructions and data. But as both the instruction- and data-caches and MMUs are implemented in the same manner, the are described only once.

**Caches** The default implementation of the caches are 8KB, 1-way direct mapped cache. The directory is physically addressed and it has a least-recently used (LRU) replacement policy.

**MMUs** The memory management units enables the OR1200 to provide a virtual memory management scheme. Both the instruction and data MMUs are by default implemented as 1-way, direct mapped hash-based translation look-aside buffers (TLB), with a page size of 8KB.

# 2.2.4 Registers

### $\mathbf{SPRs}$

In OR1200 special purpose registers are divided into 32 different groups. The register address consists of a 5-bit group address and 11-bit register index. A complete list of the registers in OR1200 can be found in [9, table 17]. If accessible, the special purpose

| Instruction group | Clock Cycles to Execute |

|-------------------|-------------------------|

| Arithmetic        | 1                       |

| Multiply          | 3                       |

| Compare           | 1                       |

| Logical           | 1                       |

| Rotate and Shift  | 1                       |

| Others            | 1                       |

Table 2.1: OR1200 execution times

registers can be written to with the  $1.mfspr^2$  and  $1.mtspr^3$  instructions. When reading from a register that is not implemented 1.mfspr will return zero. Writing to a register that is not implemented will have no effect.

#### GPRs

OR1200 has 32 general-purpose 32-bit registers, labelled R0-R31. Some of these registers have reserved functionality; R0 is fixed to zero, and has to be initialized by software. R1 is the stack pointer, R2 is the frame pointer and R9 is the link register. A complete list of the GPRs is found in the OpenRISC 1000 architecture manual [3, table 16-4].

#### 2.2.5 Functional operation

During operation, the **Instruction Unit** will generate the effective address of an instruction and fetch instructions from the instruction cache. The instruction memory management unit then translates this into a physical address. Based on the type of instruction, it is forwarded to the corresponding execution unit; load/store, integer execution or MAC.

Most of the instructions in OR1200 is executed on a single cycle. Table 2.1 shows the executions time for different instruction types.

#### 2.2.6 Exception handling

Exceptions in OR1200 are handled precisely, meaning that all instructions up until the start of an exception are valid, instructions in the program flow after the start of an exception are discarded and the causing instruction's address is saved in Exception Program Counter Register (EPCR), the current value of SR is stored in Exception Supervision Register(ESR), if a memory related exception is raised the effective address of the instruction is stored in Exception Effective Address Register(EEAR). A list of all the exceptions handled by OR1200 is shown in Table 2.2.

<sup>&</sup>lt;sup>2</sup>move from special-purpose register

<sup>&</sup>lt;sup>3</sup>move to special-purpose register

| Type         | Vector offset | Pri. | Conditions                             |

|--------------|---------------|------|----------------------------------------|

| Reset        | 0x100         | 1    | HW or SW reset                         |

| Bus error    | 0x200         | 4/9  | Attempt to access invalid address      |

| Data page    | 0x300         | 8    | No matching PTE in page table for      |

| fault        |               |      | load/store operations                  |

| Instruction  | 0x400         | 3    | No matching PTE in page table for      |

| page fault   |               |      | instruction fetch                      |

| Tick timer   | 0x500         | 12   | Tick timer interrupt asserted          |

| Alignment    | 0x600         | 6    | Load/store to unaligned location       |

| Illegal in-  | 0x700         | 5    | Illegal instruction in the instruction |

| struction    |               |      | stream                                 |

| External in- | 0x800         | 12   | External interrupt asserted            |

| terrupt      |               |      |                                        |

| DTLB Miss    | 0x900         | 7    | No matching entry in DTLB              |

| ITLB Miss    | 0xa00         | 2    | No matching entry in ITLB              |

| Range        | 0 xb 00       | 10   | Caused by certain flags in SR          |

| System call  | 0xc00         | 7    | System call initiated by SW            |

| Floating     | 0 x d 0 0     | 11   | Caused by floating point instruc       |

| point        |               |      | tions                                  |

| Breakpoint   | 0xe00         | 7    | Hardware breakpoint                    |

Table 2.2: Exceptions in OR1200

| Common signals | Description                                  |  |

|----------------|----------------------------------------------|--|

| clk_i          | Clock input                                  |  |

| rst_i          | Reset signal input                           |  |

| dat_i          | Data in                                      |  |

| dat_o          | Data out                                     |  |

| tgd_i          | Data tag type input                          |  |

| $tgd_o$        | Data tag type output                         |  |

| Master signals | Description                                  |  |

| ack_i          | Acknowledge signal from slave                |  |

| cyc_o          | Cycle output, indicates a cycle in progress  |  |

| stall_i        | Indicates slave is stalled                   |  |

| err_i          | Slave indicates abnormal cycle termination   |  |

| rty_i          | Slave indicates that cycle should be retried |  |

| sel_o          | Slave select signal                          |  |

| $stb_o$        | Strobe output                                |  |

| we_o           | Write enable                                 |  |

Table 2.3: Wishbone signals

#### 2.2.7 External communication

OR1200 uses a Wishbone interface for both data and instructions. Wishbone is an interconnection architecture for portable intellectual property (IP) cores developed by the OpenCores community.

The Wishbone used by OR1200 is shown in Table 2.3, and is taken from the Wishbone specification by OpenCores[11]. Only the signals for the master is shown here, but all connected slaves has a corresponding input/output port.

During operation a read or write through the Wishbone protocol requires three clock cycles[11], and the valid data is placed on the output on the last positive clock edge.

# Chapter 3

# Design and implementation of the TMU

This chapter presents the Time Management Unit (TMU). In the first section the purpose and responsibilities of the unit are described, in the second section some previous implementations are reviewed. Based on the previous work, a specification for the internal unit is devised and some alternative placements are examined. The third and fourth section describes the design requirements and development process of the TMU, and the fifth section presents a testbench for the designed TMU as a stand-alone unit and the results of these tests are shown in the sixth section.

# 3.1 General description of a TMU

A TMU in a real-time system provides aid in solving two problems. It measures the execution time of a normal task and signal if a task exceeds its budget, hence enable for more optimistic scheduling budgets. And it aids in controlling the time spent handling interrupts.

For counting the execution time of normal tasks, the TMU have to be told when the task starts executing and when it is stopped. It also have to know the time-limit for the running task. If a task then reaches its limit, the TMU will generate an exception so that other tasks can get runtime, and possibly correct the faulting task.

For monitoring time spent handling interrupts, there are two main approaches. Either count the actual time spent handling an interrupt in the same manner as with regular tasks, or count the number of arrived interrupts during a time frame. Both of these have its advantages and disadvantages. If the execution time is counted some overhead will be added for loading, starting and stopping the TMU, which could be critical in the handling of interrupts. One also have to address the problem of which process will be charged for the overhead in masking out the active interrupt. If the number of arrived interrupts are counted, the time it takes to handle a specific interrupt will be unknown if the user does not know the execution time of the interrupt service routine. But with this approach, counting and masking interrupts can be performed with zero overhead.

# 3.2 Previous work with a TMU

This section present some of the previous work that was studied for this thesis, and provided the base for the implementation of the TMU.

#### 3.2.1 On-Line Execution time limiting, 2005

In [13] Håvard Skinnemoen and Amund Skavhaug proposes a hardware counter with nanosecond precision in systems with variable CPU clock frequencies. This counter has 64-bits and would act as a wall-clock time-keeper, and by adding an execution time counter one can achieved a deferrable server scheduling approach. The counting of interrupt execution time can be done with one counter or with a separate counter for each interrupt line. The counting of task execution time is done with one counter register, where the counter value is saved and restored as a part of the task context.

In addition the paper specifies a method for avoiding the "babbling idiot problem", by counting the arrival of events instead of execution time for interrupts.

#### 3.2.2 A TMU for real-time systems, 2008

The master thesis by Bjørn Forsmann describes the implementation of a TMU for the LEON3 processor as a peripheral bus unit[4]. The thesis also discusses different possible solutions for the placement of the unit, where the alternatives to a bus implementation is either as a coprocessor or inside the processor as a register.

This unit has a count, limit and control register for counting task execution time, and a count, limit, period and control register for each interrupt line for interrupt execution time counting. Forsmann modified the real-time operating system eCos to incorporate the TMU functionality, and values for count and compare are loaded as part of the running context.

#### 3.2.3 Functional specification for a TMU, 2010

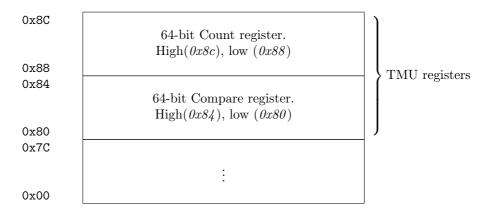

Kristoffer Gregersen and Amund Skavhaug presented a functional specification for a bus implementation of a TMU in 2010[7]. This paper proposed a simple unit with 64-bit count and compare registers, and swap register. In this specification, the count and compare values are loaded during a context switch or handling interrupts. Hence the implementation of the TMU itself is a simple counter with support for atomic swapping of registers. The specification was tailored for the work being done in implementing the Ada Ravenscar profile for the Atmel AVR architecture.

#### 3.2.4 Hardware implementation of a TMU, 2010

In his master thesis Stian Søvik improved the functional specification by Skavhaug and Gregertsen and implemented a TMU as a bus unit inside the Atmel AVR UC3

microcontroller[15]. In addition to the count and compare registers, Søvik introduced a status and control register. The implemented module also adhered to the behaviour of similar modules inside the UC3.

Values for the TMU registers are loaded as a part of the running context, and the overhead added by the TMU is dependent on the availability of the bus. The minimum overhead caused of the TMU during a context switch is claimed to be 28 clock cycles.

# 3.3 Design of the TMU

As described by Bjørn Forsmann in his master thesis, a possible placement for the TMU is inside the CPU[4]. He discarded this as a to intrusive implementation, but mentioned that it could possibly be much faster than a bus implementation. Implementing the TMU internally in the OR1200 CPU core was the focus of this thesis.

#### 3.3.1 Possible implementations placements

There are multiple solutions as to where to place the TMU inside the OR1200 core, and how it should communicate with the rest of the processor. Three different positions has been examined, all of which have pros and cons.

In the register file The TMU can be placed as a separate module inside the register file module. This would result in some extra addressable registers, but it would be faster because the load/store unit could write values to the TMU directly. The problem with this implementation is the width of the addresses for the registers, which is five bits and able to address 32 registers. To solve this problem at least one bit has to be added to the register operand address-width and some of the custom instructions could be used to load and store the TMU registers. Using custom instructions would also require logic for decoding these instructions.

This solution is highly intrusive and adds the need for a lot of modifications to exiting modules, mainly in the **register file**, **load/store unit**, **instruction decode unit** and **control unit**.

As a part of the GPRs Instead of adding the TMU as a separate module, it could be possible to reserve some of the existing general purpose registers to serve as TMU registers. This would remove the need for additional bits in register addresses, but would result in fewer registers available for general use. Depending on the number of interrupt lines, one could end up using all of the general purpose registers to count interrupts. To make sure that these registers are never used for anything other than TMU functionality the compiler tool chain have to be modified.

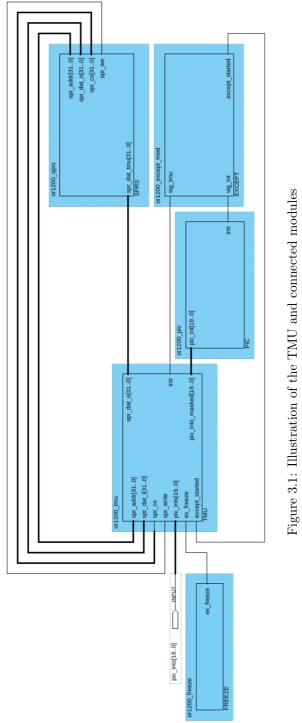

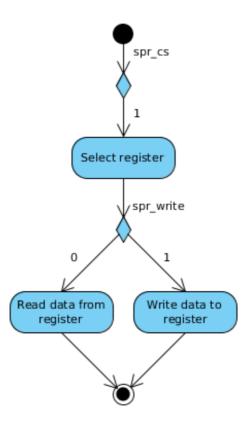

As special purpose registers The TMU could be implemented as a separate module inside the processor and have all registers be addressed as special purpose registers. As compared to the other possibilities, it would be easier to load and store values in the module since there are already several modules that uses the SPR interface inside the processor. But reading and writing values would have to be done with two instructions, resulting in a larger overhead than a GPR implementation.

### 3.3.2 Chosen design

Of the three alternatives, the chosen solution is the one that utilizes special purpose registers. This alternative was chosen because it minimizes the need to make large modifications to the existing modules and makes it possible to have the TMU as a separate and independent unit. It also makes communication with the module simple, because the existing interface for special purpose registers is used for reading and writing all data. Implementation of the TMU as a separate module corresponds well to the way the rest of OR1200 is written, with a module for a specific functionality[9]. The added overhead of one extra instruction for reading or writing registers in the module, as compared to an implementation directly in the register file, is acceptable.

#### 3.3.3 Requirements

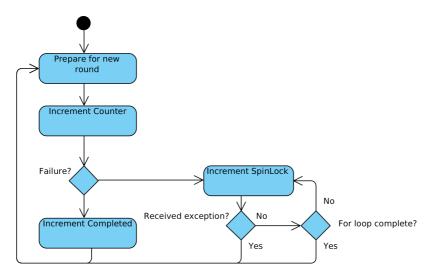

The requirements for the TMU implemented for the OR1200 processor is based on the article by Skinnemoen and Skavhaug[13] and Bjørn Forsman's master thesis[4]. The design of the unit should be as simple as possible, but still allow the user full control control over the operation. One of the main problems in counting execution time for both tasks and interrupts is defining the moment the counter should start and stop. The start and stop point for each counter decides which task should be charged with the overhead of switching tasks, or if any task should be charged.