## Transaction Level Modeling of a PCI Express Root Complex

Even Låte

Electronics System Design and Innovation Submission date: June 2014 Supervisor: Snorre Aunet, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

## **Project Assignment**

### **Candidate name:** Even Låte **Assignment title:** Transaction Level Modelling of a PCI Express Root Complex

#### **Assignment text:**

Model a Peripheral Component Interconnect(PCIe) Root Complex (RC) with respect to important performance metrics such as latency, bandwidth and jitter.

An RC serves as a bridge between PCI and QuickPath Interconnect(QPI) for Intel architectures.

PCIe is a packet-based, serial interconnect standard that is widely deployed in workstation for it's attractive bandwidth capabilities. QPI is also a packetbased communication standard that is used internally in the RC between the "I/O hub" and Intel's "Unicore".

I/O-traffic is on most modern systems said to be I/O coherent, that is, I/O transactions work on concert wit the cache coherency of the CPU-memory interconnect. PCIe has the ability to avoid the coherency(NoSnoop), to relax the ordering between transactions(RO). PCIe also has provisions for placing/reading data directly from the host caches, through TLP processing hints(TPH), which is formerly known as direct cache transfer. All these, can if used correctly, increase the performance of the communication architecture.

The main focus of the assignment is to create a high level model of an RC and CPU/memory complex in order to provide performance simulation of a PCIe device in a relevant environment, with respect to latency, bandwidth and jitter. The model can be correlated with real hardware, using a PCIe tracer to observe the characteristics of traffic of traffic on a real hardware platform. This in combination to selected traffic scenarios is well suited to correlate the model.

Assignment Proposer: Responsible Professor: Supervisor: Håkon Bugge, ORACLE Snorre Aunet, NTNU Morten Schanke, ORACLE

### Abstract

PCI Express(PCIe) is a packet-based, serial, interconnect standard that is widely deployed within servers and workstations for it's attractive performance capabilities. A platform that has a PCIe architecture also includes a PCIe Root Complex(RC) for linking the PCIe device-tree to the host CPU and memory.

During the design-phase of a PCIe endpoint-device it is highly desired to conduct computer aided simulations of the device in a relevant environment. Having a simulation software that can be applied early and iteratively in the design-phase enables engineers to tweak the product without realization of hardware. Causing a great reduction in the number of physical prototypes required before mass production.

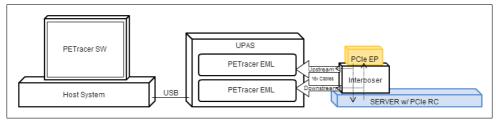

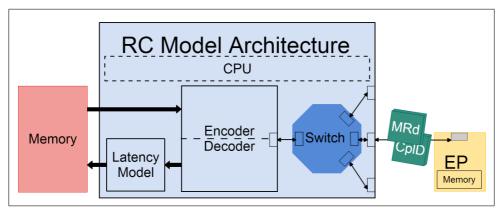

In this thesis a transaction level model(TLM) of a PCIe RC was assembled using SystemC, with a focus on latency and jitter as performance parameters. The model gives the Application Specific Integrated Circuit(ASIC) developers at Oracle a timing accurate alternative to the existing processor emulator(QEMU) that is used for the same purpose. To correlate the RC TLM with real hardware, a PCIe protocol analyzer from LeCroy was utilized. Traffic between a first generation PCIe endpoint-device and a SUN FIRE X4170 M3 server was traced.

The RC TLM was made in a modular manner allowing support for other micro-architectures through insertions of trace files. The recorded traces between requests and completions were processed and inserted directly into a delay database within the RC model, to ensure high correlation between the RC TLM and the real hardware. A simple model of a PCIe endpoint-device was implemented to serve as a suitable test-environment.

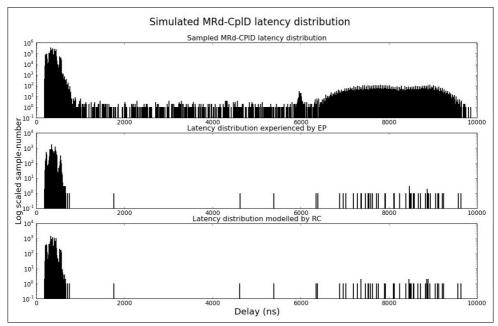

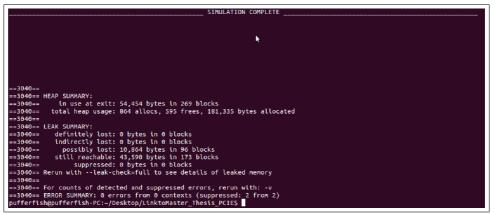

The functionality and the hardware realisticness of the RC model was successfully tested with targeted transaction scenarios. A simulated latency distribution of 15000 packets, proved to fit the latency distribution that was randomly drawn in the RC TLM. Only a small amount of negligible delay anomalies from imperative switch cycles were found.

The PCIe RC TLM is close to optimal for modeling latency and jitter using a database of targeted trace calbrations. The principle of modeling delays in an RC TLM using latency databases, was found to be a favorable alternative to the constant delay nature of the QEMU test-environment.

## Preface

This thesis is submitted to the Department of Electronics and Telecommunications at NTNU to complete a Master of Science degree in electronics; digital circuit design.

The assignment proposal originated through a meeting with Oracle in late November, 2013. The work on the thesis was initiated the 20th of January 2014, and was concluded the 16th of June the same year.

The intention of this assignment is to contribute to Oracle's existing ASIC test-environment by creating a transaction level model of a PCIe root complex for more hardware realistic performance simulations.

I would like to express my gratitude to; Morten Schanke and Håkon Bugge from the Oracle Corporation and professor Snorre Aunet from NTNU, for their support throughtout these 21 weeks. I would also like to thank Oracle and its employees at Skullerud for including me in their work towards designing ASICs for the new generation of enterprise data-centers.

Trondheim, 2014-06-16

Even Låte

## Contents

| Pr | Project Assignment i |         |                                                              |    |

|----|----------------------|---------|--------------------------------------------------------------|----|

| Pr | eface                | e       |                                                              | v  |

| 1  | Intr                 | oducti  | ion                                                          | 1  |

|    | 1.1                  | Motiv   | ration                                                       | 1  |

|    | 1.2                  | Thesi   | s Overview                                                   | 3  |

| 2  | The                  | oretica | al Background                                                | 5  |

|    | 2.1                  | PCI E   | xpress                                                       | 6  |

|    |                      | 2.1.1   | The PCIe Evolution                                           | 6  |

|    |                      | 2.1.2   | The PCIe System Architecture                                 | 9  |

|    |                      | 2.1.3   | The PCIe Topology                                            | 22 |

|    |                      | 2.1.4   | PCIe Packet Sending Example                                  | 26 |

|    | 2.2                  | PCIe I  | Related Performance Metrics                                  | 28 |

|    |                      | 2.2.1   | Bit Rate / Bandwidth                                         | 28 |

|    |                      | 2.2.2   | Latency and Jitter/Packet Delay Variation(PDV)               | 29 |

|    | 2.3                  | Root    | Complex Emulation with QEMU                                  | 33 |

|    | 2.4                  | Syster  | mC                                                           | 35 |

|    | 2.5                  | The L   | eCroy PCIe Gen. 1 Trace System                               | 38 |

| 3  | Met                  | hodolo  | ogv                                                          | 41 |

|    | 3.1                  |         | ion of Approach                                              | 42 |

|    |                      | 3.1.1   | Deciding on the Architectural Structure of the PCIe RC Model | 42 |

|    |                      | 3.1.2   | Model Approach for Delay Correctness                         | 43 |

|    | 3.2                  | Imple   | ementation of the RC model                                   | 44 |

|    |                      | 3.2.1   | Implementing the TLP C++ class                               | 44 |

|    |                      | 3.2.2   | Implementing the PCIe Encoder/Decoder Socket Module .        | 47 |

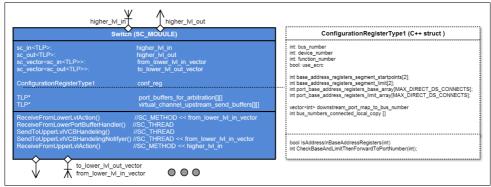

|    |                      | 3.2.3   | Implementing the PcieSwitch Module                           | 48 |

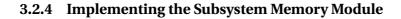

|    |                      | 3.2.4   | Implementing the Subsystem Memory Module                     | 50 |

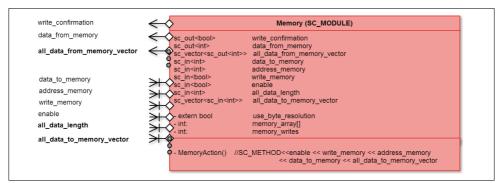

|    |                      | 3.2.5   | Implementing the RC Module.                                  | 51 |

|    | 3.3                  |         | rming traces on relevant HardWare                            | 54 |

|    |                      | 3.3.1   | Setting up the Trace Hardware and the Trace Software         | 54 |

|    |                      | 3.3.2   | Performing the Tracing                                       | 55 |

|    |                      | 3.3.3   | Converting the Trace Data to Text Delay Coloumns             | 56 |

|                                            |      | 3.3.4 Linking the Delay Model and the Trace Data                 | 57  |

|--------------------------------------------|------|------------------------------------------------------------------|-----|

| 3.4 Creating a test-environment for the RC |      |                                                                  | 59  |

|                                            |      | 3.4.1 Constructing the PCIe endpoint model                       | 59  |

|                                            |      | 3.4.2 Interconnecting modules creating a complete system         | 60  |

|                                            |      | 3.4.3 Creating the Program Interface in sc_main.cpp              | 61  |

|                                            | 3.5  | Testing the PCIe RC Model                                        | 62  |

|                                            |      | 3.5.1 System functionality                                       | 62  |

|                                            |      | 3.5.2 Valgrind Memory Leak Check for Runability                  | 71  |

| 4                                          | Res  | ults                                                             | 73  |

|                                            | 4.1  | Packet Tracing                                                   | 73  |

|                                            |      | 4.1.1 The PETracer Recordings                                    | 73  |

|                                            |      | 4.1.2 The Generated Delay File for the RC Model                  | 74  |

|                                            | 4.2  | Functionality Test-Results of the RC                             | 77  |

|                                            |      | 4.2.1 Functional Accuracy                                        | 77  |

|                                            |      | 4.2.2 Delay Model Accuracy                                       | 92  |

| 5                                          | Disc | cussion                                                          | 95  |

|                                            | 5.1  | Analyzing the PCIe Trace Recordings                              | 95  |

|                                            |      | 5.1.1 The Recorded MRd-CplD Latency Distribution                 | 96  |

|                                            |      | 5.1.2 The Delta Delay Extraction tool                            | 96  |

|                                            | 5.2  | Analyzing the RC TLM                                             | 97  |

|                                            |      | 5.2.1 Implementing the RC TLM                                    | 97  |

|                                            |      | 5.2.2 Testing The Functionality                                  | 101 |

|                                            | 5.3  | Using the RC model for performance testing of EPs                | 105 |

|                                            |      | 5.3.1 Deciding on the PCIe performance criteria                  | 106 |

|                                            |      | 5.3.2 Implementing a TLM of the EP                               | 106 |

|                                            |      | 5.3.3 Running the Performance Simulations                        | 107 |

|                                            |      | 5.3.4 Evaluation of the RC TLM as a Tool for Performance Testing | 108 |

|                                            | 5.4  | Future Work                                                      | 109 |

| 6                                          | Con  | clusion                                                          | 111 |

| Re                                         | fere | nces                                                             | 115 |

| A                                          | Acro | onyms                                                            | 119 |

| B                                          |      | Tool for Converting Exported Trace Files                         | 121 |

|                                            |      |                                                                  |     |

| С                                          | Pytl | hon Script for Plotting of Latency Distributions                 | 125 |

| D | D PCIe Traffic Trace Summaries                                       |                   |  |

|---|----------------------------------------------------------------------|-------------------|--|

|   | D.1 Summary of Trace Iteration 1                                     | 128               |  |

|   | D.2 Summary of Trace Iteration 2                                     | 132               |  |

|   | D.3 Summary of Trace Iteration 3                                     | 136               |  |

| E | Simulation Output Format<br>E.1 Root Complex Completes a MRd Request | <b>141</b><br>141 |  |

| F | Valgrind Test for Program Runability                                 | 145               |  |

## List of Figures

| 1.1 MSI Z77 requiring Intel Ivy Bridge for PCIe gen 3 support[38]     | 1  |

|-----------------------------------------------------------------------|----|

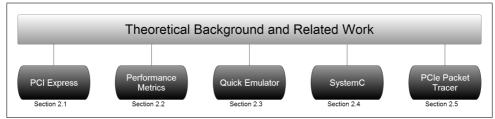

| 2.1 Overview of the theory sections in this thesis                    | 5  |

| 2.2 The PCIe logo by the PCI-SIG [26]                                 | 6  |

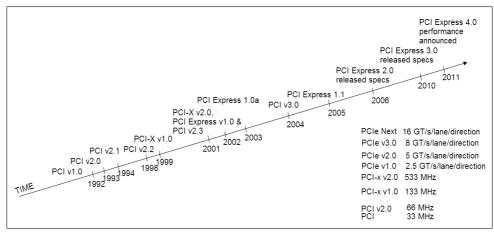

| 2.3 The evolution of the PCI and PCIe generations from 1992 until now | 7  |

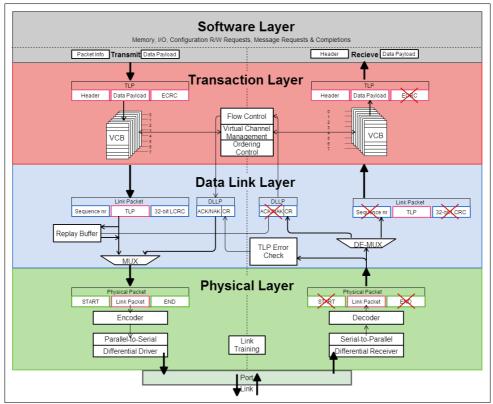

| 2.4 Two PCIe devices communicating with TLPs and DLLPs                | 9  |

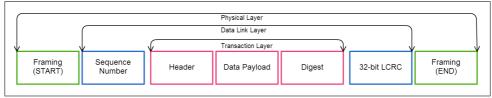

| 2.5 The TLP and it's layer-targeted segments 1                        | 10 |

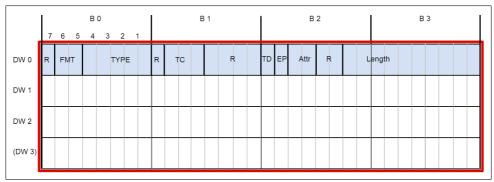

| 2.6 The generic TLP header 1                                          | 10 |

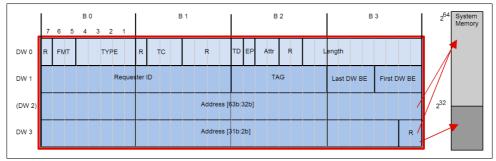

| 2.7 The memory request header 3DW & 4DW                               | 12 |

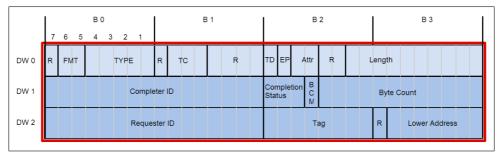

| 2.8 The completion header 1                                           | 13 |

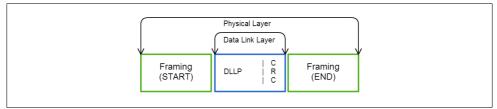

| 2.9 The structure of the data link layer packet 1                     | 13 |

| 2.10 The layered structure of the PCIe protocol stack 1               | 15 |

|                                                                       | 15 |

|                                                                       | 15 |

|                                                                       | 17 |

| 2.14 The data link layer of the PCIe Protocol 1                       | 19 |

|                                                                       | 20 |

|                                                                       | 22 |

| L                                                                     | 23 |

| 1                                                                     | 25 |

| 1                                                                     | 26 |

|                                                                       | 27 |

|                                                                       | 30 |

|                                                                       | 30 |

|                                                                       | 31 |

|                                                                       | 32 |

| 0 1 1                                                                 | 33 |

|                                                                       | 34 |

|                                                                       | 34 |

|                                                                       | 35 |

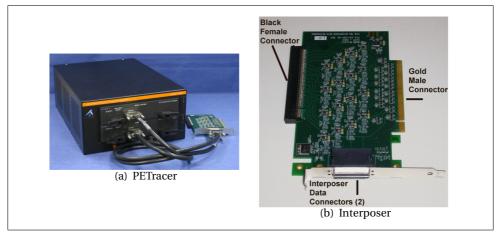

|                                                                       | 38 |

|                                                                       | 39 |

| 2.31 A hardware setup for the protocol analyzer                       | 39 |

xii

| 3.1  | Outline of the project workflow                                     | 41 |

|------|---------------------------------------------------------------------|----|

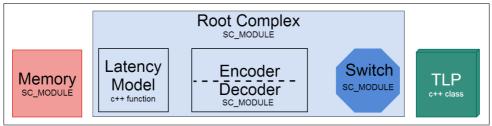

| 3.2  | Structural overview of the RC TLM                                   | 42 |

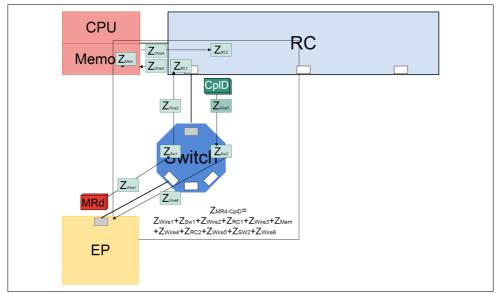

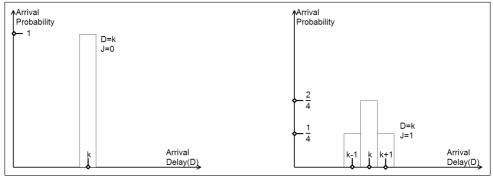

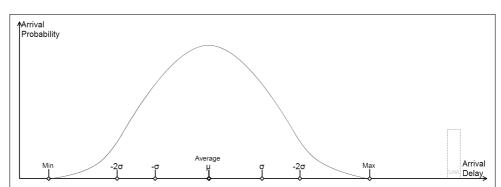

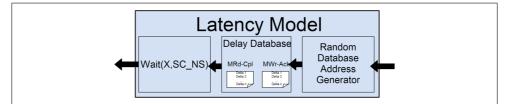

| 3.3  | A realistic delay model                                             | 43 |

| 3.4  | Modules, classes and functions of the RC TLM                        | 44 |

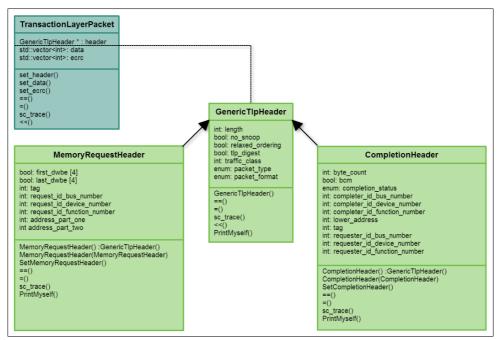

| 3.5  | A class diagram of the TLP and its header structure                 | 45 |

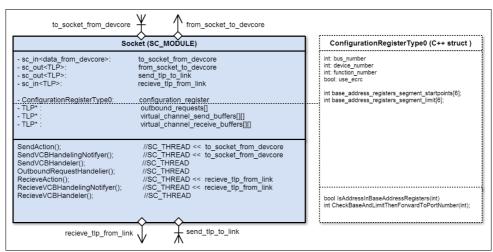

| 3.6  | A module diagram of the PCIe protocol stack                         | 47 |

| 3.7  | A module diagram of the PCIe packet switch                          | 48 |

| 3.8  | A module diagram of the host memory                                 | 50 |

| 3.9  | A module diagram of the RC TLM                                      | 51 |

| 3.10 | Trace setup at Oracle's test lab                                    | 54 |

| 3.11 | OFED comand for executing an application on the PCIe EP             | 56 |

| 3.12 | Snippet of raw packet flow between the PCIe EP and the RC           | 56 |

| 3.13 | Snippet of TLP-only flow between the PCIe EP and the RC             | 57 |

| 3.14 | Example of TLP Traffic extracted to Text                            | 58 |

| 3.15 | The Text Format Required by the RC Delay Model                      | 58 |

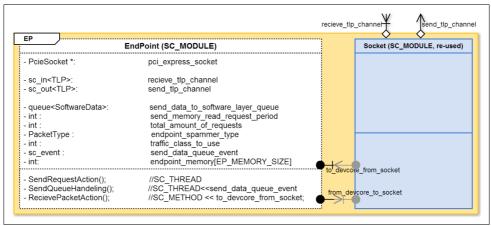

| 3.16 | A module diagram of the PCIe EP TLM                                 | 59 |

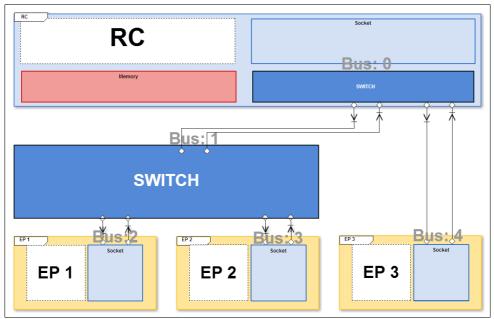

| 3.17 | A module diagram of the complete test system                        | 60 |

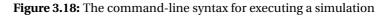

| 3.18 | The command-line syntax for executing a simulation                  | 62 |

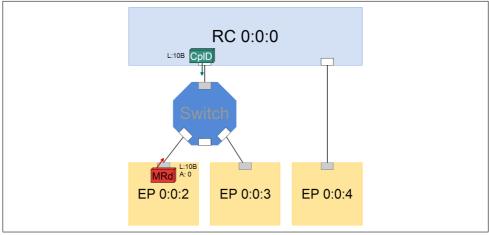

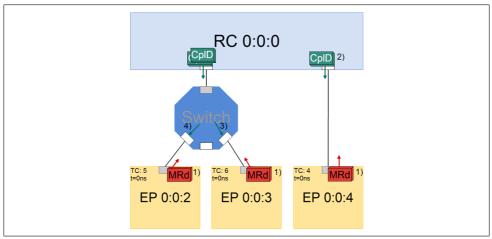

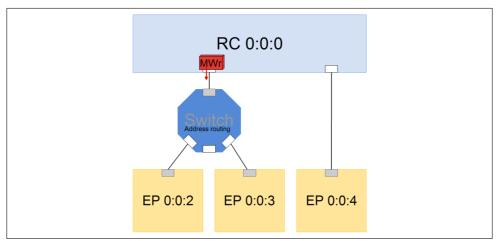

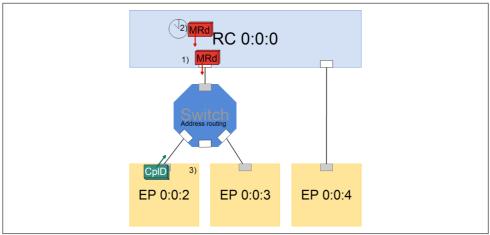

| 3.19 | Testing a single MRd from EP:002 to the RC                          | 64 |

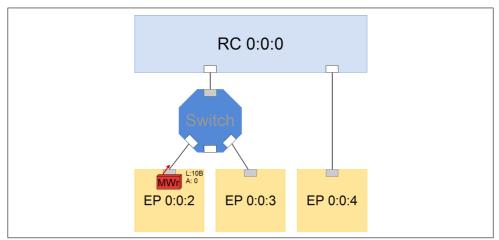

| 3.20 | Testing a single MWr from EP:002 to the RC's system memory          | 64 |

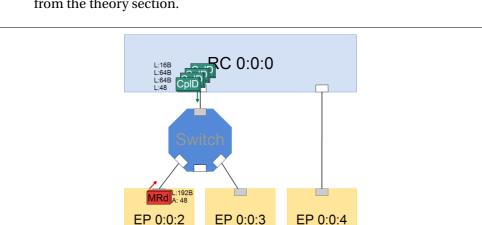

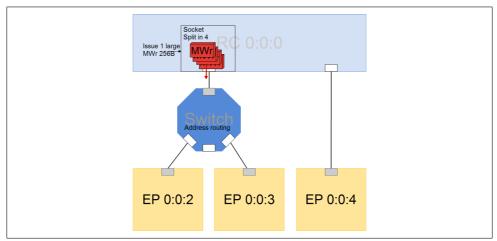

| 3.21 | Testing a single MRd from EP:002 to the RC, RCB exceeded            | 65 |

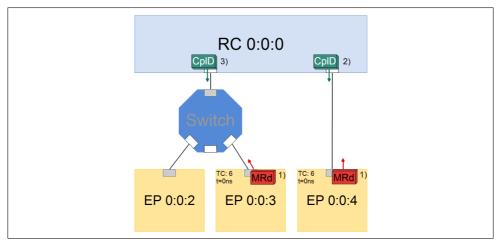

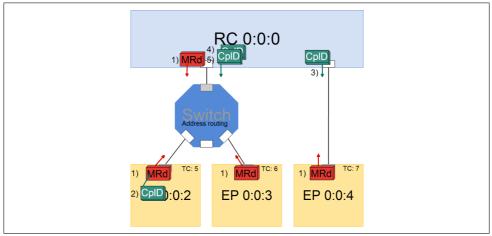

| 3.22 | Testing 2 simultaneous requests, switching cycles are illustrated . | 65 |

| 3.23 | Testing the virtual channel buffer arbitration                      | 66 |

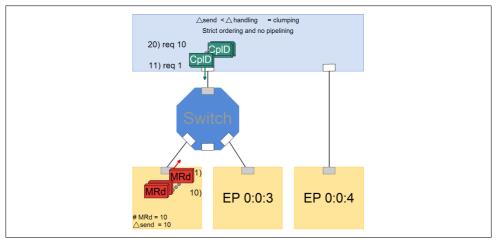

| 3.24 | Testing rapidly sent requests                                       | 66 |

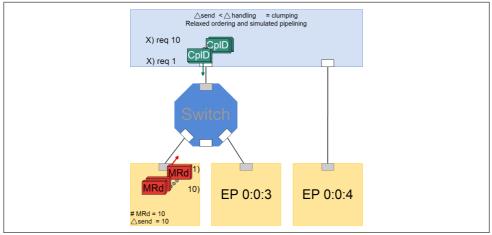

| 3.25 | Testing rapidly sent requests, RC relaxed ordering                  | 67 |

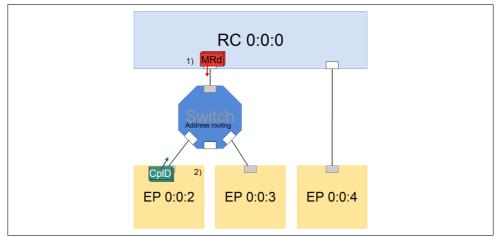

| 3.26 | Testing RC's ability to issue requests, in this case a simple MRd   | 68 |

| 3.27 | Testing RC's ability to issue a simple MWr request                  | 68 |

| 3.28 | Testing the RC's ability renew lost requests                        | 69 |

| 3.29 | Testing the maximum payload size restriction with a memory write    | 69 |

| 3.30 | Testing bidirectional MRd traffic                                   | 70 |

| 3.31 | Testing bidirectional MWr traffic                                   | 70 |

| 3.32 | A realistic PCIe scenario, computation is outsourced to the EP      | 71 |

| 3.33 | The command-line syntax for a Valgrind execution                    | 71 |

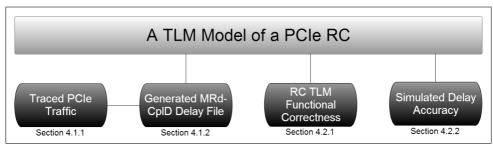

| 4.1  | Overview of the result sections in this chapter                     | 73 |

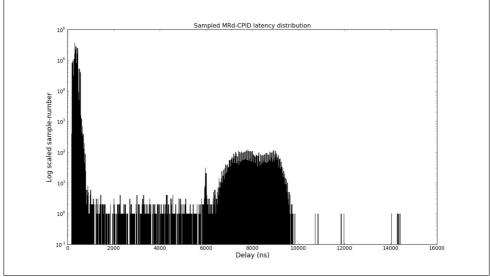

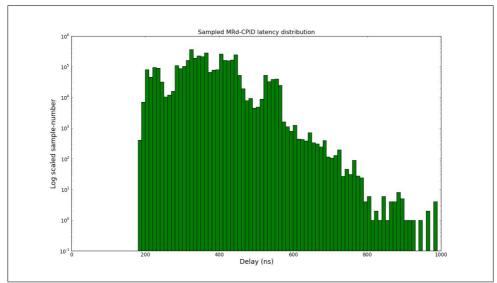

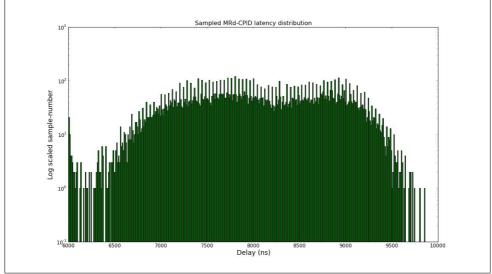

| 4.2  | A histogram of the total amount of traced delays                    | 74 |

| 4.3  | The first sub distribution in figure 4.2, heavy-tailed              | 75 |

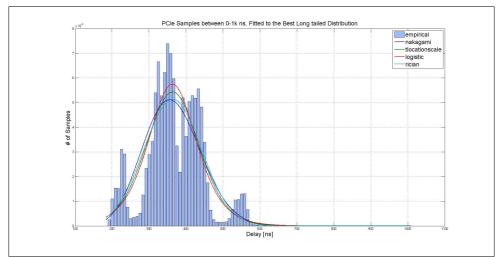

| 4.4  | Fitting a probability distribution to the first sub distribution    | 75 |

| 4.5  | The last sub distribution in figure 4.2, bell shape                 | 76 |

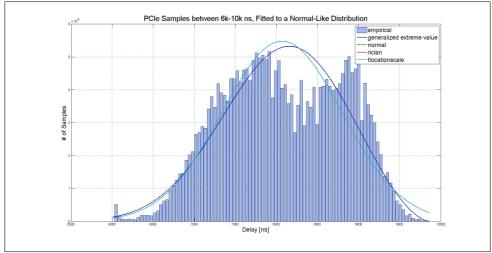

| 4.6  | Fitting a probability distribution to the last sub distribution     | 76 |

| 4.7  | The summary of the output.txt file generated by a single simulated  |    |

|      | MRd request from EP 2:0:0                                           | 78 |

|      |                                                                     |    |

| 4.8        | The summary of the output.txt file generated by a single simulated      |          |

|------------|-------------------------------------------------------------------------|----------|

|            | MWr request from EP 2:0:0                                               | 79       |

| 4.9        | The summary of a large MRd request, prooving the RCB function-          |          |

|            | ality                                                                   | 80       |

| 4.10       | Simulation log file that illustrates the imperative delta delay con-    |          |

|            | sumed by switch modules                                                 | 81       |

| 4.11       | Simulation log file that illustrates the packet priority of the system, |          |

|            | EP 4:0:0 is handled first because of the delta delay in the switch      | 82       |

| 4.12       | Simulation log file from a simulation with multiple MRd requests        |          |

|            | sent with low periodicity, illustrates clumping in the RC               | 83       |

| 4.13       | Simulation log file from a simulation with multiple MRd requests        |          |

|            | sent rapidly, multitasking in the RC resolves the clumping              | 84       |

| 4.14       | Simulation log of the Root Complex using address routing to route       |          |

|            | a single MRd package downstream to its reciever                         | 85       |

| 4.15       | Simulation log of the Root Complex using address routing to route       |          |

|            | a single MWr package downstream to its reciever                         | 86       |

| 4.16       | Simulation log of the Root Complex using address routing to route       |          |

|            | a single MRd package downstream to its reciever                         | 87       |

| 4.17       | Simulation log of the Root Complex sending a single MWr request         |          |

|            | for a large amount of data, being limited by the max payload at-        |          |

|            | tribute                                                                 | 88       |

| 4.18       | Simulation log of a simulation where all devices are requesters and     |          |

| 4.10       | potentially completers                                                  | 89       |

| 4.19       | Simulation log of a simulation where all devices requests memory        | 0.0      |

| 4 00       | writes to the other devices                                             | 90       |

|            | Simulation log of a realistic PCIe system scenario                      | 91       |

|            | Simulation log of 15000 packets over 1 ms                               | 92<br>93 |

| 4.22       | Correlation between sampled and simulated latency distributions         | 93       |

| 5.1        | Topics of discussion and their sections in this chapter                 | 95       |

| 5.2        | Mixture probability distribution function of the MRd-CplD delays        | 98       |

| 5.3        | A blue print of a generic EP TLM to ensure RC TLM compatibility         | 107      |

| <b>P</b> 1 |                                                                         | 1 4 5    |

| F.1        | Summary log for a valgrind run, no definitely lost memory               | 145      |

xiv

## List of Tables

| 2.1 | Paralell bus structures, frequencies, transfer rates and io ports [3] | 7  |

|-----|-----------------------------------------------------------------------|----|

| 2.2 | The PCIe Transaction types                                            | 9  |

| 2.3 | The generic header fields of the TLP, explained                       | 11 |

| 2.4 | The memory-request header specific fields, explained                  | 12 |

| 2.5 | The completion-header specific fields, explained                      | 14 |

| 3.1 | The settings used for a trace recording                               | 55 |

| 4.1 | TLP-type trace statistics summary for all 3 trace iterations          | 74 |

| 4.2 | General statistics for the recorded traces                            | 74 |

# CHAPTER **L**

### 1.1 Motivation

Figure 1.1: MSI Z77 requiring Intel Ivy Bridge for PCIe gen 3 support[38]

Today's industry shows an increasing trend towards large data-centers and databases. Internet traffic is expected to increase exponentially as the introduction of Internet Protocol version 6(IPv6) allows the Internet of Everything(IoE) to be created. Cisco estimated that around 50 billion devices will be connected to the Internet in 2020 as a result of ipv6 and the IoE [7]. All these devices generate massive amounts of data that requires processing, communication and storage. Organizations manage more data, with greater speed and from more sources than ever before.

Larger IT-based companies desire to ease the job of the average IT-technician by acquiring hardware and software solutions that are able to virtually tie machines together. They want to fuse many sparse databases into few virtual ones that are easily manageable. This demand creates a market for virtual, secure and high performance database solutions. Oracle's ASIC-department at Skullerud in Oslo works to satisfy the need for quicker transfer of data between devices. They are part of Oracle's global R&D team with a focus on communication between the internal processing units of server systems. The ASICs utilize communication protocols such as PCI Express(PCIe) and Infiniband to move data from one processing unit to another due to their attractive transfer rates.

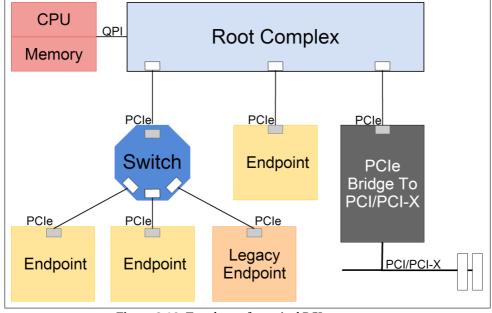

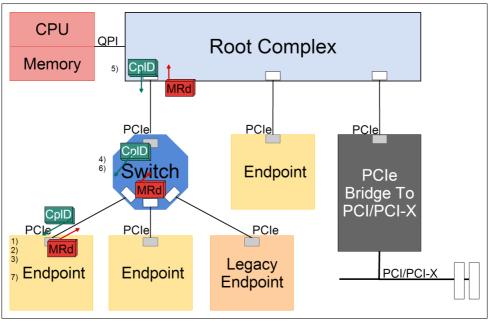

PCIe is a packet-based, serial, interconnect standard. It is widely deployed and has a bright future as a communication infrastructure for peripheral units in computers. Figure 1.1 shows a MSI Z77 motherboard, incorporating a third generation PCIe slot. PCIe devices communicate with other devices, in a switch based tree structure. A common PCIe topology contains a root complex(RC), several Endpoints(EPs) and optional switches. The RC is the logic structure that interconnects the CPU, the memory and the PCIe Tree containing the system I/O. The EPs are I/O devices that are connected to the branches of the PCIe tree, an example would typically be a graphics controller. The switches allow data transactions between devices by applying packet switching on behalf of the RC or EPs in the PCIe tree.

It is crucial to map system performance when developing PCIe hardware, both during the design process, and afterwards for marketing purposes. Teledyne Lecroy and Agilent deliver solutions for protocol analyzation of PCIe Hardware. Physical test instruments are able to interpose PCIe Traffic and to record detailed packet information that can be used to analyze performance of realized PCIe EPs. However, it is also desired to simulate device performance during the design-phase of a PCIe device, prior to hardware manufacturing. Simulations allow tweaking of hardware in front of realization, which is valuable with respect to design-cost and performance due to a reduction of prototypeiterations. Computer aided simulations are easily configured and allows for optimization of parameters such as buffer sizes, algorithms and other system variables. The result is that latency, jitter and packet congestion are reduced, maximizing the bandwidth and the quality of service(QoS) of the final product.

To perform software simulations of PCIe express EPs, a model of the RC, and models of the EPs are required. Oracle's ASIC-branch in Oslo and in California have until now been using QEMU for environment modeling during hardware simulations. QEMU is a generic open source machine emulator and virtualizer, that includes an emulated CPU with an RC and a memory system. Some problems with QEMU as a RC simulator is that it is not cycle accurate, propagation delays are not included in round-time latencies and there is no model for jitter included in the round-time latencies. Another factor is that it contains a lot of excess functionality that is not necessary from a PCIe-ASIC developer's point of view. There is a need for a new tool that fills these gaps.

This thesis involves the creation of an accurate and purpose specific alterna-

tive to the already existing PCIe simulation environment QEMU. A transaction level model(TLM) of a PCIe RC is to be created. Accuracy of the model should be ensured by correlating it to real PCIe hardware through protocol analyzations of a relevant server platform.

### **1.2 Thesis Overview**

The successive chapters delve into and analyze the creation of a transaction layer model of a PCIe RC. Each chapter is marked with a black rectangle in the upper right corner of the page. On the very same page an illustration is given describing the contents of the chapter's child sections. An overview of the paper, chapter by chapter, is given below:

Chapter 2 provides background information on theory regarding terms and concepts that will come in handy throughout the paper. The chapter begins with a detailed overview of PCI Express protocol. In-depth knowledge of PCIe is required to understand the nature of a PCIe RC. PCIe related performance metrics are also explained. Theoretical performance-limits of a PCIe system are seldom achieved, the actual performance of the system is dependent on a wide specter of system variables. Terms such as bit-rate, net bit-rate, peak bit-rate, bandwidth, throughput and latency are elucidated. The chapter then moves on to describing the QEMU software. Basic knowledge of the transaction-level modeling language, SystemC, is summarized to ease the understanding of the implementation. The benefits of using SystemC compared to other modeling languages are also explained. The Final section of the theoretical background chapter covers PCIe protocol analyzing. Both software and hardware components of the trace instruments are introduced to draw a picture of the packet tracing process.

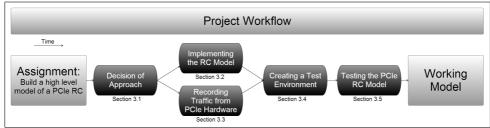

Chapter 3 covers the methodology of this thesis, that is basically the workflow for the entire design process of designing an RC TLM. The first section covers the decision phase of the structural architecture of the RC model. The following section describe the selection of a modeling language for implementation of the model. The workflow of the software implementation is described, including the design of internal modules, classes and functions used within the TLM. This chapter also describes the process of obtaining traffic information from recording traffic on real, first generation PCIe hardware. The data achieved from the protocol analyzer is merged with the RC's delay model to create a realistic delay model of the root complex. The latter sections of chapter 3 presents the implementation of a compatible TLM of a PCIe EP, test and verification of the RC model are also outlined.

Chapter 4 presents illustrations of the results from the PCIe traffic record-

ings from the LeCroy protocol analyzer. The remaining section of this chapter will list the test-results achieved from testing the software model, both with respect to functionality and timing accuracy. The result chapter will consist of several windows containing exported text-files from test-runs of the model. It could be advantageous to read this chapter electronically as text out-puts are more easily interpreted with search functions.

Chapter 5 brings out the discussion of the results. The created software model of the PCIe Root complex is analyzed to map whether the model is an adequate option to simulation using QEMU. Requirements for use are also discussed, these are; compatible implementation of an EP TLM in SystemC and instantiation of all the components in the complete simulation environment. The chapter covers several topics, all attempting to answer the question: Is the RC TLM's functionality better than that of the QEMU emulator with respect to hardware realisticness? Topics that are covered are: functional adequacy, simplifications of the software implementation, future work of the model and challenges faced during implementation.

Chapter 6 is the conclusion chapter, it contains answers to the questions discussed throughout this thesis. Will the work carried out in this thesis benefit Oracle in the form of a platform that has the potential to reduce development costs and improve the final performance of their PCIe ASICs?

Acronyms used in this thesis are listed in appendix **??**. For readers who find the implementation of an RC TLM interesting, the appendixes can provide essential details for the software made for this assignment. Some basic examples of program output from the RC system-model are attached in the appendix. The c++ script for converting exported files and the python script for plotting latency distributions are to be found. The trace files them selves are not included as they are in the gigabyte size-range, however summaries of them are attached. The Code itself for the RC TLM, can be found on Git-Hub at the location specified in [10].

## CHAPTER 2

## **Theoretical Background**

Figure 2.1: Overview of the theory sections in this thesis

The purpose of this chapter is to introduce several important concepts and terms that are used in the modeling approach of the RC and in the discussions throughout this thesis. Figure 2.1 shows the outline of this chapter. The PCI Express section is the most weighted one in this chapter, this section gives a detailed overview of the transaction layer nature of the PCIe Architecture. PCI Express relevant performance metrics are also discussed in this chapter to reason for the modeling approach of the Root Complex. A section is dedicated to explain the Quick EMUlator software currently used by Oracle. The event driven nature of the SystemC modeling language is covered in its own section to ease reading of the model and to ease the understanding of the diagrams found in the methodology chapter. Finally, the hardware that is used for recording of PCI Express Root Complex.

### 2.1 PCI Express

Figure 2.2: The PCIe logo by the PCI-SIG [26]

The Peripheral Component Interconnect Express standard is officially abbreviated PCIe. It is a serialized, point to point, connection-standard developed by the Peripheral Component Interconnect-Special Interest Group (PCI-SIG). It is a packet-based interconnect that allows peripherals to communicate with other devices by the use of differential signaling. The peripherals that are interconnected in a third generation PCIe system are achieving transfer rates of up to 8(GT/s) billion transfers per second, per lane, per direction. This corresponds to a raw bit rate total of 16(GB/s) billion bytes per second, per direction, for a 16-lane PCIe slot. These terms and metrics are described in detail later in this chapter.

PCIe is applied in technologies such as personal computers, servers, embedded computing and communication platforms. The most commonly known field of application for PCIe architectures is as interconnections between CPUs and graphics cards within personal computers. The system host writes data to the memory that is adjacent to the graphic accelerator. Once the data transfer is complete, the host issues a kernel call to provide the graphics processing unit(GPU) with data processing instructions. A completed outsourced computation is written back to the host once it is complete. Whenever graphics cards desire to fetch data from CPU-adjacent memory, or write data to it, they have to consult with the PCIe controller first, also known as the Root Complex(RC).

### 2.1.1 The PCIe Evolution

In the early computer-days around 1970, before the old PCI standard was invented, data was transfered using serial connections. Computers assembled data-packets and sent them serially from device to device, one packet at a time. As time went by, serial connections proved to be slow despite their reliable and robust nature. To cope with the steep speedup of computers, scientists began to develop parallel structures for communication, oblivious to the fact that they

Figure 2.3: The evolution of the PCI and PCIe generations from 1992 until now

were stepping into a design-architecture with less potential for performance. This increasing trend gave birth to the PCI bus which was introduced 1992 as shown in the time line in figure 2.3. For years the 32 bit PCI bus was the most convenient manner to connect sound, video and network cards to a mother-board.

| Bus Type     | Clock Frequency   | Peak Bandwidth  | #Card Slots |

|--------------|-------------------|-----------------|-------------|

| PCI 32-bit   | 33 MHz            | 133 MBytes/sec  | 4-5         |

| PCI 32-bit   | 66 MHz            | 266 MBytes/sec  | 1-2         |

| PCI-X 32-bit | 66 MHz            | 266 MBytes/sec  | 4           |

| PCI-X 32-bit | 133MHz            | 533 MBytes/sec  | 1-2         |

| PCI-X 32-bit | 266 MHz effective | 1066 MBytes/sec | 1           |

| PCI-X 32-bit | 266 MHz effective | 2131 MBytes/sec | 1           |

Table 2.1: Paralell bus structures, frequencies, transfer rates and io ports [3]

Incremental improvements of bus transfer speeds were achieved by increasing bus clock frequencies. The PCI theoretically support 32 devices connected to each bus. Increasing the bus frequency in parallel bus architectures turned out to drastically reduce the number of feasible electrical loads. This is because the method for detecting bus devices rely on the reflection of a driven test signal to locate the termination of the bus. The more devices connected to the bus, the longer it takes for the signal to be reflected. The total time it takes from the signal is set to the reflection arrives must be less than the clock period to for the signal to reach a device before bus evaluation.

Higher requirements to data-transfer rates together with the electrical load barrier was why PCI-X was introduced. The multi-drop parallel bus began to replace the PCI, however it was only a temporarily solution as computers grew more and more powerful. Table 2.1 reflects this phenomenon, increasing the frequency for a given architecture implies reducing the number of card slots per bus, both for PCI and PCI-X. The electrical load barrier created yet again a need for a new, revolutionary design approach. Computer scientists were forced to re-think fundamental concepts as they were facing a physical barrier.

Research advancements in the field of dividing, labeling and re-assembling packets as well as improvements in electrical hardware components for differential signaling, re-introduced the trend of serial data transfers. Interconnect research had again turned towards high speed serial communication which gave birth to PCIe, a serialized packet-based communication protocol. PCIe 1.0 was introduced in 2002 as a third generation I/O bus. Today, high speed interconnects such as USB and Firewire and PCIe are all built on the serial data transfer principle. PCIe kept the strong features of PCI, and improved the weak ones, the serial transfer approach, makes it technically speaking, not a bus. The predecessors of PCIe are referred to as true buses, they are constructed with physically adjacent rails for parallel data transfer. PCIe on the other hand side, has a structure that resembles a serial network connection. It mimics PCI even though it communicates using a packet based protocol. The resemblance to PCI ease the task of migrating PCI devices to PCIe, create bridges between the two, and removes the need to change software during a migration.

The PCIe bus is said to be categorized as a third generation bus out of three generations:

- The first generation of buses consists of multiple purpose specific busstandards, all with dedicated tasks to be assembled into a larger system. One bus for is dedicated for memory, one for peripherals and so. Many smaller systems are built together to create a larger computer system. Examples of first generation buses are: ISA, EISA, VESA and Micro channel buses.

- The second generation of buses are known for using two layers of connection. The CPU and the memory are connected to the north-bridge, and the peripheral devices are connected to the south-bridge, the two modules are interconnected with an internal bus structure. Examples of second generation bus standards are: PCI, AGP, PCI-X.

- Third generation buses are flexible with respect to the number of physical connected devices to the system. This makes them suitable for use internally in computer systems connecting computing nodes together. The third generation of buses behave like networks rather than bus standards.

Figure 2.4: Two PCIe devices communicating with TLPs and DLLPs

### 2.1.2 The PCIe System Architecture

### **PCIe Units of Transaction**

This section covers the system architecture of PCIe, starting from the bottom up with the units of transactions first, then the device layers and finally the coarse grained system topology. PCIe is as mentioned above a packet based communication protocol. There are two packet types flowing on the links between PCIe devices. These are the transaction layer packets(TLPs) and the data link layer packets(DLLPs) shown in figure 2.4. The DLLPs are used for Link management functions, for transferring data between devices that help maintain connection statuses and to provide information about reception of TLPs. Examples of such functions are ACK/NAK handshakes, exchange of flow control details and power management features. The TLPs are the larger communication units that are used for the transactions themselves. That includes memory actions, io actions, configuration of PCI devices and for messaging and event reporting. The TLPs are explained in detail below as these are essential for the creation of an RC TLM.

### **The Transaction Layer Packet**

The 15 transaction layer PCIe transactions are listed in table 2.2 in 5 categories.

| Category      | TLP Types                   | Acronym | Posted or Non-Posted |

|---------------|-----------------------------|---------|----------------------|

| Memory        | Memory Read Request         | MRd     | Non-Posted           |

|               | Memory Read Lock Request    | MRdLk   | Non-Posted           |

|               | Memory Write Request        | MWr     | Posted               |

| IO            | IO Read Request             | IORd    | Non-Posted           |

|               | IO Write Request            | IOWr    | Non-Posted           |

| Configuration | Config Type 0 Read Request  | CfgRd0  | Non-Posted           |

|               | Config Type 0 Write Request | CfgWr0  | Non-Posted           |

|               | Config Type 1 Read Request  | CfgRd1  | Non-Posted           |

|               | Config Type 1 Write Request | CfgWr1  | Non-Posted           |

| Message       | Message Request             | Msg     | Posted               |

|               | Message Request W/Data      | MsgD    | Posted               |

| Completion    | Completion                  | Cpl     | -                    |

|               | Completion W/Data           | CpID    | -                    |

|               | Completion-Locked           | CplLk   | -                    |

|               | Completion-Locked W/Data    | CplDLk  | -                    |

The requests can be split into two types, posted transactions and non-posted transactions. The non-posted transactions are those that expect TLP answers in return of a request, typically memory read requests that expect a completion TLP containing the requested data. The posted transactions are those that do not expect a reply such as memory write requests. Writes are satisfied once the data is written to the specified system memory address. Non-Posted requests are handled as a split transactions, freeing the bus while waiting for an answer. This is an automatic feature as a result of the packet based nature of PCIe.

Figure 2.5: The TLP and it's layer-targeted segments

The TLP is consists of the 7 main segments shown in figure 2.5. The header of the TLP is assembled in the transaction layer of the sender, and disassembled in the transaction layer of the receiver. The transaction layer section of the TLP is encapsulated with sequence numbers, error checks and start-stop indications on its way down towards the egress port. These encapsulations are upon reception of the packet, peeled off like onion-shells in their respective abstraction layers. When the packet arrives at the software layer of it's destination, only the payload and the header remains.

Figure 2.6: The generic TLP header

The header segment of the TLP shown in figure 2.5, consists of 3 or 4 Double Words(DW). The data payload is up to 1024 DW data payload and the optionally ECRC segment is 1 DW. The 15 various types of TLPs listed in table 2.2 are distinguished from each-other by differences in the byte-fields within the header of the packet. The structure of the header varies for the different TLP types, which is represented with the white fields in figure 2.6. The light blue fields are

| Header field       | Explanation                                                                |

|--------------------|----------------------------------------------------------------------------|

| Reserved (R)       | The reserved fields are all reserved for header recognition, they are      |

|                    | all set to 0's during TLP construction. Recent patches to the PCIe         |

|                    | structure use some of the reserved fields for extra attributes such as     |

|                    | extended tags, and TLP hints [18] [40].                                    |

| Format (Fmt)       | The format of the TLPFmt are used to tell whether a data payload is        |

|                    | present in the TLP or not, it is also used for information about the       |

|                    | length of the header itself, if it is 3 DWs or if it is 4 DWs.             |

| Traffic Class(TC)  | The Traffic class is the priority of the TLP, it tells what priority based |

|                    | virtual channel buffer it is to be put in at forwarding and handel-        |

|                    | ing. The higher the number the higher is the priority, TC can be a         |

|                    | number from 0 to 7.                                                        |

| TLP Digest (TD)    | TLP digest tells whether the 1DW optional ECRC section of the TLP          |

|                    | is present or not, the receiver of the packet must check the ECRC          |

|                    | field if it is.                                                            |

| Poisoned Data (EP) | If this bit is high, the TLP is consdered to be invalid. The transaction   |

|                    | is allowed to complete normally.                                           |

| Attributes (Attr)  | The attributes of the header tells whether to <b>Relax Ordering (RO)</b>   |

|                    | or to use strict ordering when transfering the packet. The attributes      |

|                    | also tell whether to set No Snooping (NS) for the transaction, mean-       |

|                    | ing that no cache coherency issues exist regarding this TLP. The sys-      |

|                    | tem is allowed to skip snooping to ensure cache coherency thus in-         |

|                    | creasing the system performance.                                           |

| Length             | The Length field indicates the size of the data payload in given in        |

|                    | DW, maximum payload size is 1024DW as the field is 10 bits long.           |

Table 2.3: The generic header fields of the TLP, explained

generic, they are common for nearly all packet types. Each generic type field is explained further in detail in table 2.3.

The header types for memory requests packets and completion packets are explained in this paper as these are vital for an RC TLM. The type specific fields for MRd an MWr are shown in figure 2.7. Equally, Cpl and CplD header fields are described in figure 2.8. Explanations for the memory request packets are found in table 2.4 and completion header explanations are given in table 2.5. The gray rectangle next to the memory request header represents 32bit addressing vs 64 bit addressing in system memory, the 3 dw memory request header can only access the darker shade of gray, the bottom 4 GB of PCIe system memory. Please refer to the PCI e system manual [3] for explanation of the remaining header types for the packets listed in 2.2

To further understand the packet structures and the intention behind the packet types, a deeper look into the layered structure of the PCIe protocol is necessary as the DLLPs originate in the data link layer, and the TLPs originate in the transaction layer of PCIe devices.

| Memory Header<br>field                    | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Last DW Byte En-<br>able                  | Last DW Byte Enables consist of four bits that indicate what bytes<br>that are included in the last DW of the payload, this field is needed<br>as the address field is DW alligned.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| First DW Byte En-<br>able<br>Requester ID | First DW Byte Enables works in a similar fashion to Last DW BE, it<br>tells what bytes to include in the first DW of the data payload.<br>The requester ID tells the completer of the memory request who the<br>requester is, so that a completion packet may be returned. The re-<br>quester ID is the device ID of the requester, described by a bus num-<br>ber from 0 to 255, a device number from 0 to 31, and a function<br>number from 0 to 7. Completion packets for memory requests are<br>returned using ID routing                                                                                                                                            |

| Tag                                       | The Tag of the memory request is a water-stamp that is put on a non-<br>posted request packet to ID outstanding requests that are issued<br>by a requester. By default a device may only have 32 outbound re-<br>quests at a time. The completion packet to the request is also water-<br>stamped with the same tag, so that the request can be removed from<br>the outbound buffer in the transaction layer of the receiver. Recent<br>changes to this parameter is explained in [40], the change is called<br>extended tags, allowing 256 outbound requests.                                                                                                           |

| Address                                   | The address field of the memory request header provides the sys-<br>tem memory address for the requested memory action. The entire<br>PCIe system is given different segments of the 64 bit available sys-<br>tem memory address space, this allows for address routing to be<br>used when routing packets between PCIe devices. The address field<br>is either 1 DW or 2 DWs, depending on the addressing type indi-<br>cated in the format of the header. If the header is 3 DW in total, only<br>the lower 4 GB might be addressed. The lowest 4 bits of the address<br>forces the memory to be double word aligned, creating the need for<br>the byte enable fields. |

Table 2.4: The memory-request header specific fields, explained

### The Data Link Layer Packet

The DLLPs originate in the data link layer of a transmitter and are terminated in the data link layer of a receiver. The DLLPs are used for management of the PCIe

Figure 2.8: The completion header

Figure 2.9: The structure of the data link layer packet

links by sending ACK/NAK packets, power management information, and to exchange credits that are used for flow control of virtual channel buffers. ACKs and NAKs are the DLLPs that are used for acknowledging successful receptions of TLPs, and for reporting faults in transactions. When a DLLP is sent down to the physical layer, extra sections marking the start and the end of the packet to be transmitted are added. This is illustrated in figure 2.9, note that the outer segments are equal to the outer physical segments of the TLP. The DLLP is not explained in detail here as the RC TLM is to be made in a higher abstraction level.

### **PCIe Device Layers**

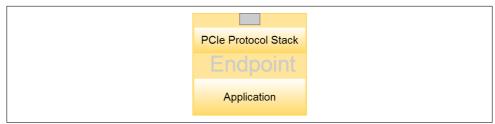

Figure 2.10 shows a PCIe device and its device layers put together in a lego-like structure to form the PCIe Protocol stack. Each layer is described below with extra effort is put into the the higher abstraction layers. The importance of the paragraphs are reflected in their lengths.

### Software Layer

The software layer is where the device's system logic lies. It is the software application running on hardware on top of the PCIe protocol stack. For an RC TLM this would be the root complex core logic, and for an endpoint this would be the endpoint core logic. The top section of figure 2.10 shows that the all layers are divided into a transmit side and a receive side, even the software layer is

| Completion<br>Header field     | Explanation                                                                                                                                                                                                                                                                                                                |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Completer ID                   | The completer ID tells the receiver of the completion package, who<br>sent it, this has no purpose for routing the packet, however it might<br>come in handy when debugging packet traffic.                                                                                                                                |

| Competion Status               | The Completion status in the header marks whether the completion package is the result of a successfull completion or not.                                                                                                                                                                                                 |

| Byte Count Modi-<br>fied (BCM) | The BCM field is only set to 1 by PCI-x completers, it indicates<br>whether the Byte Count field tells the receiver of the packet the<br>number of bytes in the first transfer payload rather than the remain-<br>ing payload.                                                                                             |

| Byte Count                     | The Byte Count reflects the remaining number of bytes until the re-<br>quest that was the origin of the completion is satisfied, this counter<br>includes the payload of the current completion packet. The field is<br>usefull when multiple completion packets are returned to one re-<br>quest.                         |

| Requester ID                   | The Requester ID field in the completion packet represents the de-<br>vice ID of the requester that originated the completion packet, the<br>request field is used for routing the completion packet back to the<br>correct requester by using ID Routing.                                                                 |

| Tag                            | The Tag of the completion packet is equal to the tag of the corre-<br>sponding request packet, the tag is used by the receiver of the com-<br>pletion packet to remove the request from the outbound request<br>buffer to prevent further re-playing if requests.                                                          |

| Lower Address                  | The Lower address of the completion header represents the lower<br>7 bits of the address for the first byte of data returned that was re-<br>turned to a reader. The lower address is used for determining the<br>next legal Read completion boundary for large read requests as a<br>precaution to cache line alignments. |

Table 2.5: The completion-header specific fields, explained

slightly divided. Whenever the device core decides to send a packet on the PCIe link, the transmit side of the software layer sends the necessary information to build that packet, down to the transaction layer. The information needed to build a TLP includes TLP-type, address, data, amount of data to be transfered, traffic class and more. The receive side of the device core is responsible for receiving data that has made its way up to the transaction layer, this data includes most data in the normal TLP core except from the ECRC field which is removed by the transaction layer.

### **The Transaction Layer**

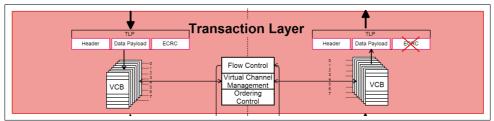

The transaction layer is responsible for generating outbound traffic and for decoding inbound TLP traffic. The transaction layer is as shown in figure 2.12 also bipartite like the software layer. One part is transmitting, it generates the outbound TLP headers and assembles the TLP cores on behalf of the software

Figure 2.10: The layered structure of the PCIe protocol stack

Figure 2.11: The software layer of the PCIe Protocol

Figure 2.12: The transaction layer of the PCIe Protocol

layer, data payload is encapsulated within the header and an end-to-end cyclic redundancy check field (ECRC). The packets created are then placed in transmitbuffers to be forwarded down to the data link layer. The receiving part of the transaction layer receives packets from the data link layer and places them in receive buffers for handling. When TLPs are picked out for handling they are first checked for CRC errors based on the optional ECRC section of the TLP, if there are none, the packets are stripped for their ECRC field and the resulting information is forwarded to the software-layer together with the data payloads of the transactions.

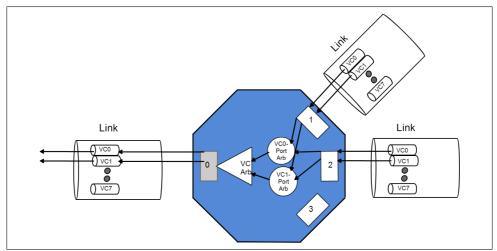

The transmit and receive buffers in the transaction layer are known as virtual channel buffers(VCBs). There is one transmit and one receive buffer for each traffic class. The 8 VCBs are shown in figure 2.12. All TLPs are marked with a traffic class, a number between 0 and 7, as explained in section 2.1.2. The traffic class is the priority number of the packet, and depending on what TC number the packet has, the packet is put into different buffers with different priorities. The higher the traffic class the higher is the priority of the buffer arbitration. The buffers with higher priorities are cleared at quicker rates than the buffers with low priorities. Quality of Service (QoS) is also ensured by having a credit based flow control to avoid buffer overflow for the VCBs. A virtual channel send buffer is not allowed to be handled unless the credit-status of that specific virtual channel buffer says so. A TLP will only be transmitted if the transmitter knows for sure that the receiver has buffer space to accept the transmitted TLP. The credits represents buffer-space, and they are updated through data link level packets that are sent periodically between devices. The DLLPs are responsible for updating the credit information.

Whenever the transaction layer receives a completion TLP from another device, the tag of the TLP is associated with the tags of previously sent non-posted requests that are stored in an outbound request buffer. The packet is rejected if tag is nowhere to be found in the outbound request buffer. The request stored in the outbound request buffer is removed whenever a completion is received that matches the tag of the stored request. If the request is lost, the packet is replayed after a specified time out period.

Configuration is only covered partly in this assignment as a performance based device simulation targets an already configured PCIe System. A device's configuration registers are associated with the transaction layer of the each device function, a device may have up to 8 functions. Each device function implements a set of configuration registers. The registers are configurable and are used to store system settings such as address maps, device IDs, link capabilities and other system information that needs to be accessed in runtime. Each PCIe device has a set of Configuration registers that are initialized during system boot up by the RC in runtime software. The transaction layer and the software layer access the configuration registers in runtime when sending and receiving packets. The configuration registers are set during system configuration with configuration packets from the PCIe RC.

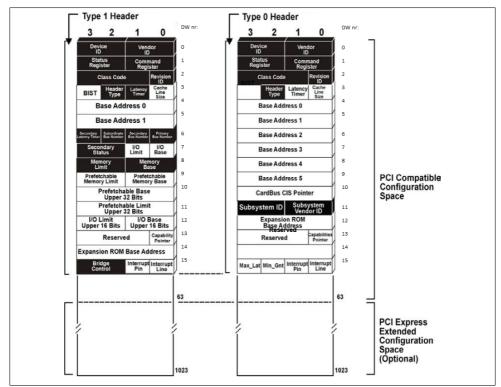

As figure 2.13 shows, the PCIe device's configuration register contains a 256

Figure 2.13: Type 1 and type 0 configuration register headers[3]

byte PCI compatible fraction that includes device ID, base addresses and such. The remaining 3840 bytes of the configuration register is dedicated to PCIe configurations, they includes virtual channel capabilities to support QoS and other optional PCIe specific extended capability registers. PCI does not support QoS in the same degree as PCIe does.

There are two different configuration spaces, these are the type 0 and type 1 headers shown in figure 2.13. All devices that require system memory, IO, or memory mapped IO target addresses implements Base Address registers (BARs). Type 0 registers have 6 BARs and are the non-bridge/non-switch format, meaning that endpoints use type 0 configuration registers. Type 1 configuration registers have 2 bars and are used for forwarding packets in switches and bridges. These registers contain unique segments of the system memory address space. The device that owns the BARs, also owns the segment in the system memory and is allowed to respond as a completer whenever requests that are address routed, target an address in this segment. 2 adjacent base address registers may be used to create the support for 64 bit addressing.

**Transaction Layer rules for building and decoding TLPs.** 6 Important rules for assembling data from the software layer into transaction layer packets and dissembling TLPs that are recieved form the data link layer are given below:

- Completions may be broken into multiple packets, however the total payload has to be equal to the size of the original request and each completion have to be returned in an increasing address-order. Completions from multiple requests are on the other hand not allowed to be merged such that several requests give one large completion.

- The read completion boundary (RCB) ensures that single memory read request results in several completions. Each intermediate transaction must end with naturally aligned 64 or 128 bytes address boundaries. Only the Root complex is able to have a read completion boundary on 64 bytes or 128 bytes, all other PCIe devices have an RCB equal to 128 bytes. The RCB is a direct result of the cache line size used in memory systems. PCIe performance is thus related to cache-lines. An example containing multiple completions as a result of one memory read request for 192 bytes from address nr. 0x10030 is given here:

- 1. 0x10030 -> 0x1003F (0x10 bytes)<br/>(16bytes, resulting address pointer is dividable by rcb = 0x40 (64)

- 2. 0x10040 -> 0x1007F (0x40 bytes)<br/>(64bytes) resulting address pointer is dividable by rcb = 0x40 (64)

- 3. 0x10080 -> 0x100BF (0x40 bytes)(64bytes) resulting address pointer is dividable by rcb = 0x40 (64)

- 4. 0x100C0 -> 0x100EF (0x30 bytes)(48 bytes)resulting address pointer is not dividable by rcb = 0x40(64)

- Multiple completions as the results of RCB splitting of a single request are allowed to be combined into one completion if the completions that arrived at the egress port queue first have to await sending due to port arbitration delays. If multiple completions are ready for sending, they might as well be combined into one TLP embodiment as long as they satisfy the maximum payload size [8].

- Any completion with a completion status other than "successfull completion" will terminate the transaction. A completion without any corresponding request in the outbound request buffer will be handled as an error as they are not expected.

- The maximum payload per TLP is for requests, limited by the value of the Max\_Payload\_size register located in the device's control register. If it crosses this upper limit, then it is considered a malformed TLP, and is

rejected by the receiver. A large max\_payload size allows for system communication with less overhead. But it also has its disadvantages of more packet congestion due to full buffers, a detailed description for setting the optimal maximum payload value is given in [25]. The total PCIe system is limited by its weakest components, if a system has a component with a maximum payload of 128 bytes while all other components have 256 bytes, the entire system will be configured by the RC to use 128 bytes.

• Header lengths and ECRC lengths are not included in the length-fields of headers, only data payload is included in this information. Receivers must check that the length field corresponds to the data that is transferred, if it does not match, then the TLP is considered to be malformed. The length field has a double word resolution, byte resolution on reads and writes is achieved with the last and first dw-byte enable bits.

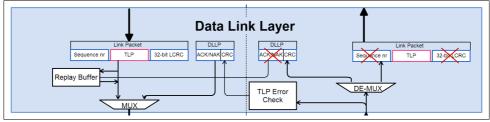

#### The Data Link Layer

Figure 2.14: The data link layer of the PCIe Protocol

The main function of the data link layer is to ensure data integrity in packets when transmitting and receiving TLPs. The DLLPs are assembled and dissembled in the data link layer. If TLP-CRC errors are detected in a receiver's data link layer, then a NAK DLLP is sent back to the transmitter of the TLP to let it know that an error has occurred and the packet-sending needs to be replayed. The ACK-NAK protocol together with the automatic replay functionality of the data link layer provides a very high probability that the TLP will make it to its final destination unscrambled. Such a feature is ideal for server systems that require low error rate and high availability.

Flow control of the system is ensured using DLLPs. The status of the virtual channel buffers of the transaction layer is updated by periodically sending VC credit information between interconnected devices.

In addition to sending separate data link layer packets, the data link layer also concatenates a sequence ID and a LCRC field to each TLP received from the transaction level for further forwarding. The sequence id is used to identify packets in the replay buffer with incoming ACK/NAK DLLPs, and the LCRC field is used for deciding whether to return an ACK or a NAK DLLP to the sender.

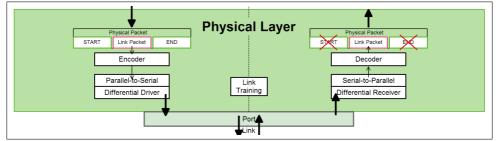

#### The Physical Layer

Figure 2.15: The physical layer of the PCIe Protocol

The layer that has direct contact with other PCIe devices is called the physical layer. This is the final layer that the packet has to pass through for it to leave the PCIe device, or the first layer that an incoming packet will face. The physical layer forwards both DLLPs and TLPs, to which it adds start of packet and end of packet indicators. There are two levels in the physical layer, one is the logical part and one is the electrical part of the layer. The first one processes the packets before sending them, to or from the physical electrical part, depending on the traffic direction. The physical electrical part is the analog interface for the physical layer to the link.

The packets leaving the Physical layer towards the egress port are converted to a serial bit-stream before they are sent out on the wire lanes. All PCIe packets are encoded using a 8/10 bit encoding, meaning that 2 extra bits are added per 8 bits of TLP or DLLP data. These 2 redundant bits are used for embedding a clock into the serial bit stream, removing the need for a clock tree.

A PCIe link between two devices that deploys the PCIe architecture is either of type 1x, 2x, 4x, 8x, 16x or 32x. The type number denote the number of twodirectional lanes that exists in the connection link between the two devices. The more lanes implemented on a link, the faster a packet is transmitted, thus the greater the bandwidth of the link. A lane consists of four signal-wire pairs, two wires for each transfer-direction. Each of these signal-wire pairs use differential signaling to achieve transfer rates of up to 2.5 GT/s for PCIe gen1, 5 GT/s for PCIe gen2, 8 GT/s for PCIe gen 3, and an announced transfer rate of 16 GT/s for the future PCIe gen 4. One wire in the pair represents a positive differential terminal, and the other wire represents the negative terminal. Whenever the voltage difference between the two terminals is positive a logical 1 is interpreted by the receiver, and whenever the difference is negative a logical 0 is received. The differential pair is in its high-impedance tristate condition or idle-state whenever the voltage difference is 0. A signal event is triggered whenever the peak to peak voltage difference is between 800mV and 1200 mV.

# 2.1.3 The PCIe Topology

Figure 2.16: Topology of a typical PCIe system

Figure 2.16 shows the component structure of a typical PCIe system. Endpoint devices and switches are connected to the memory and the CPU via the module known as the Root Complex. Whenever the CPU desires to communicate with peripherals, it performs transactions via the RC. Same goes for the endpoints, whenever they want to access data that is located in the subsystem memory next to the CPU, they have to send request TLPs to the root node in the PCIe tree for handling.

# The Root Complex (RC)

The RC interconnects the CPU and the memory to the PCIe switch fabric. It is similar to the host bridge for PCI. The RC is a critical component in the PCIe topology as it serves as the root node for the hierarchical PCIe tree, connecting the tree to the host CPU and Memory. An RC includes multiple components such as a memory interface and a processor interface for single CPUs or multiple CPUs. The CPU and the memory are connected to the RC using local bus architectures in a manner that allows the root complex to send transaction requests to PCIe devices on behalf of the CPU. The RC is also able to perform DMA, freeing the CPU as an intermediary, accessing the host memory directly.

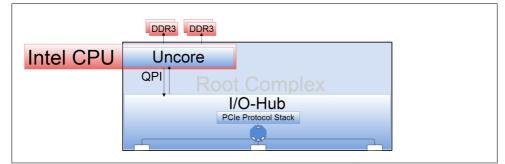

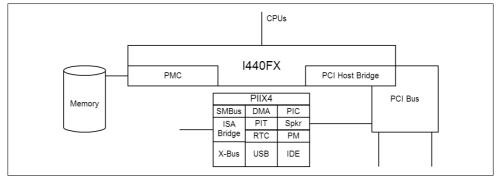

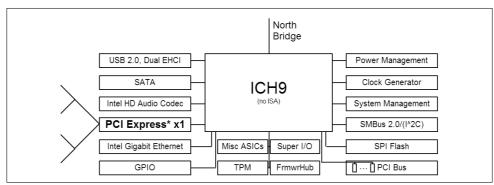

The buses that connects the PCIe tree to the CPU are company specific because the RC is built into the chip-set for the CPU. Intel CPUs have been using

Figure 2.17: The PCIe multiport RC

the bus architecture known as the front side bus (FSB) for a couple of decades. The FSB in Xeon and Itanium was replaced by the QuickPath Interconnect (QPI) [16] [28] for newer Intel micro-architectures such as Nehalem, Westmere and Xeon arriving after Xeon Bloomfield, starting in 2008-2009. The QPI is displayed in figure 2.17. It is a point to point packet based interconnect located within the Root complex, interconnecting the I/O Hub and the Uncore [12] [31] of recent Intel architectures.

The root complex is in addition to serving as a bridge between peripherals and core logic, also responsible for controlling hot plug of new PCIe devices, configuration, power management, interrupts involving the CPU, error detection and for reporting system messages. As explained earlier, each PCIe device contains configuration registers, these configuration registers are set by the root complex during system initialization and hot plug using configuration packets. The configuration registers contain data required to route packets to their appropriate destination. All PCIe devices in a system are initialized with device IDs consisting of bus numbers, device number and function numbers. The device IDs are used for ID routing by marking the packets with the corresponding sender or receiver.

There is only one RC in a PCIe network, and it is always initialized with the device ID; bus nr: 0, device nr: 0 and function nr 0. It can have one or several PCIe devices connected to it, either directly or indirectly via switches. Several connections directly to the RC requires that a switch is implemented as an internal submodule. All PCIe packet-traffic heading towards the RC is considered to move upstream, and all traffic moving away from the RC is considered to move downstream.

Multi-port PCIe RCs have the same requirements as a switch with respect to arbitration and timing requirements. Arbitration algorithms, and timing requirements are not defined in detail in PCIe RC specs, so these are vendor specific.However, a PCIe RC realization must satisfy all the paragraphs in the checklist given in [35] in order to be a valid PCIe RC. For this thesis however, only a delay-based model is to be provided, so the checklist is only relevant as theoretical background information.

**Snooping** A phenomenon called snooping plays an important role on RC performance, and thus the PCIe system performance. All memory accesses to a PCIe system memory complex are considered cache-able by the host at any time. This means that the CPU continuously stores copies of system memory in its caches. An EP requesting memory access to a system memory segment will experience a wait period for the RC to search in processor caches for copies of the memory segment. The CPU might have modified local copies with the intention to update the memory location. If this is the case, then the requesting EP will have to await the memory update before it is allowed to access the memory. The RC's cache check, filters out violations of cache coherency. Cache coherency is crucial, yet time consuming. The time it takes to snoop the CPU cache is bounded below a maximum limit, but it is still not predictable, largely influencing the Jitter of the MRd-CpID completion delay. [22]

A way to prevent system jitter from snooping is to dedicate uncacheable areas of system memory. In this way the CPU will avoid caching those areas. A second way is to have the software layer to set the "No Snoop" attribute in the TLP as described in 2.1.2. This causes the host to skip snooping regardless of its previous instructions, it can only be done when the software guarantees that the memory segment is nowhere to be found in the CPU cache. The requester knows that this will not cause any conflicts. For high priority virtual channels that requires isochronous paths, jitter can be avoided by setting configuring the RC to reject all incoming Snooping transactions on that channel. All packets that does not have the "No Snoop" attribute set might be rejected.

**Relaxed Ordering** A phenomenon called Ordering also plays an important role on RC performance. It is often beneficiary to have a strict ordering of packets that have data dependencies or memory location dependencies. A typical example would be a movie stream, you want packets to arrive in the order of the movie. However, a strict ordering of packets is not always needed. Successive transactions that do not have dependencies between each-other might allow a relaxed ordering of the transfers. Forcing ordering of packets that are independent can cause large loss of bandwidth, packets may clump up waiting for their predecessor to be sent. Instead the packets are allowed to jump the queues, and to be sent once they are ready. Relaxed ordering is set by setting the attribute in the TLP Header called "Relaxed Ordering" as described in 2.1.2.

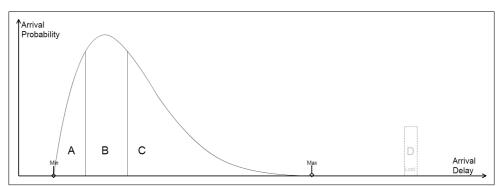

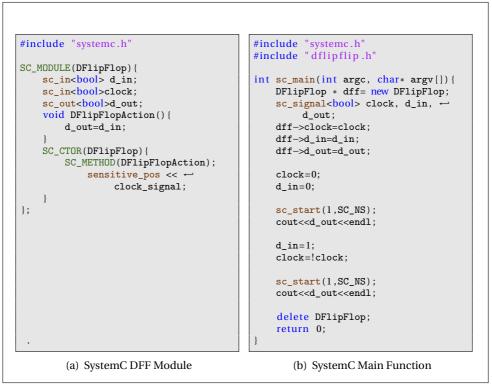

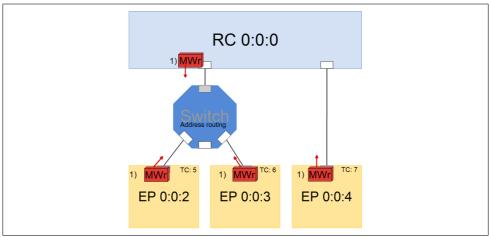

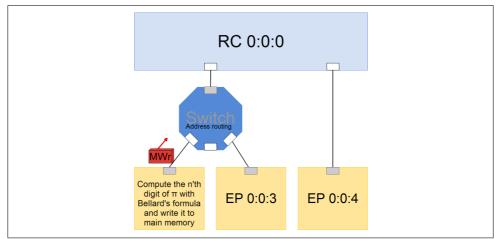

**TLP Hints, Direct Cache Transfer** A new feature for PCIe Generation 3 is the phenomenon of TLP Hints. It turns out play an important role on RC perfor-