# Scalable FPGA fabric for parallelising 2D-surface trajectory cost calculations

Design and Evaluation of Application and Hardware

### Dibyajyoti Jana

Embedded Computing Systems Submission date: June 2014 Supervisor: Kjetil Svarstad, IET Co-supervisor: Geir Åge Noven, Kongsberg Defence Systems

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# **Project Assignment**

#### **Candidate Name:**

Dibyajyoti Jana

#### **Assignment Title:**

Scalable Fabric for parallelizing 2D Trajectory Cost Calculations – Design and Evaluation of Application and Hardware

#### **Assignment Text:**

Many practical applications need to evaluate the quality of many trajectories on a two dimensional map, based on some static or slowly changing cost functions, e.g. topographic elevation, or weather conditions. Such applications would benefit from a hardware accelerator, that can parallelize and perform these cost computations efficiently. The present work proposes a scalable hardware design for such an accelerator, that is amenable to FPGA implementation.

The present work is the continuation of the work done in the previous semester (autumn 2013), where a SystemC model was developed for the proposed design. The tasks in the present semester (spring 2014) are to aim at developing on that model in two directions – one towards a higher level of abstraction involving development of an application to utilize the proposed accelerator and evaluate the effectiveness of the design. The other direction of development was to use the SystemC model as a reference to define detailed hardware and software architecture of the design and implement them. However, the time available would not be sufficient to complete all of these tasks. So, the target would be to finish the higher-level system evaluation and demonstration including an application and incorporate the findings in the detailed design, and to finish a significant part of the implementation task and qualifying it, while drawing up plans and directions for the future work, necessary to finish them.

#### **Assignment Proposer/Co-supervisor:**

Geir Åge Noven, Kongsberg Gruppen ggnoven@gmail.com

#### Supervisor:

Prof. Kjetil Svarstad, IET, NTNU

### Abstract

One way of simplifying two dimensional trajectory cost computation is to partition the 2D domain (i.e. the "map") into a grid of unit squares, and approximate the cost functions by constants within these sub-domains (called "map segments"), and similarly replace the trajectory by a piece-wise linear approximation, and accumulate the contribution of each map segment by using the constant cost functions of that segment and the length (and possibly direction) of the trajectory there, which are also easily computed because of the piece-wise linear approximation.

In hardware, the map segments can be naturally mapped onto a 2D array of processing nodes connected by a network-on-chip (NoC), where each node contains the cost data for the corresponding map segment, and can compute its local cost-contribution and add that into a data field of a packet, representing a trajectory, and pass it on to a neighbor, so that the packet traverses a path in the NoC that matches the trajectory, it represents. If the packet starts its journey through the network with a properly initialized data-field (unually 0), then after it finishes its journey and the final processing node adds its contribution to the field, it contains the cost of that trajectory. This architecture is scalable, and provides parallelization of computation, but has its draw-backs.

Because the communications between the nodes must occur in all possible directions (to model all possible directions of the trajectory), deadlocks are a real possibility. One way of detecting probable deadlocks is by detecting no progress within a timeout interval. They can then be resolved by dropping a waiting packet. But it is important to communicate the packet dropping to the external application. An auxiliary low band-width NoC, called the injection-ejection network (IENW), is planned to be used for this purpose, along with the main network, called computation network (CNW). IENW is also designed to be used to carry the packets into the correct start-point and carry out from the end-points in the processing array, reducing the CNW loading. Another problem is that the size of the hardware processing array is now connected to the map divisions, which makes reuse of hardware difficult. It may also be hard for applications to exploit the hardware optimally when it is too highly parallel, because then the application will have to produce packets at a high throughput. These problems are solved by letting more than one map segment be mapped onto the same processing node, using a structured approach introduced in Section 1.3.1.

In the previous semester a SystemC design was developed to model this hardware accelerator. In the present semester, a high level C model incorporating an external application and a high level model of the accelerator was developed to study its performance at the highest possible level in order to demonstrate the effectiveness of the design as well as to provide design guidelines for application development, e.g. how to ensure the best utilization of the hardware from the application perspective, how to accommodate the property of packet-dropping in the accelerator, etc. This activity successfully demonstrates the existence of practical applications that can benefit from this design, thereby demonstrating its utility.

In the present semester, a detailed micro-architecture of the communication infrastructure involving the CNW and IENW was developed and implemented in Verilog RTL. This was used for synthesis and timing, targeting a Xilinx Virtex7 FPGA. The results showed that a practical processing array of size 8x8 processing nodes can be comfortably accommodated, at a clock speed of about 245 MHz. These findings provide another level of confirmation of the feasibility of the design. The accelerator would also contain processors and the software running on these processors in order to implement the cost computation algorithm, packet routing, etc. These could not be implemented due to lack of time, but some guidelines for their development have been worked out. During the synthesis, the processors were replaced by a standard Microblaze micro-controller system for area estimation [15], assuming that they would have similar area. Thus the feasibility and utility of the design have been convincingly demonstrated, and its development has been placed on a clearly defined track.

### Preface

This thesis is submitted to the Norwegian University of Science and Technology in partial fulfillment of the requirements for the European Masters in "Embedded Computer Systems" (EMECS) degree. This work has been executed during spring semester 2014 at the Department of Electronics and Telecommunication, NTNU, Trondheim, under the supervision of Prof. Kjetil Svarstad, and joint-supervision of Geir Åge Noven, Kongsberg Gruppen.

# Acknowledgement

I would like to thank Geir Åge Noven for his problem proposal and suggestions about the basic system architecture. I would like to thank both Prof. Kjetil Svarstad and Geir Åge Noven for their help, reviews and feed-backs, provided to me continually during the entire period of this activity involving literature survey, design and implementation. I would also like to extend special thanks to Tore Barlindhaug for his kind help with the tool licenses and computation resources necessary for synthesis and simulation of the designed hardware.

# **Table of Contents**

| 1. Introduction and Motivation                      | 1  |

|-----------------------------------------------------|----|

| 1.1 Problem Description                             | 1  |

| 1.2 Proposed Algorithm                              | 2  |

| 1.3 Proposed System Design                          | 3  |

| 1.3.1 Map Folding                                   | 5  |

| 1.3.2 Processing Nodes                              | 6  |

| 1.4 Methodology                                     | 6  |

| 1.5 Present Contributions                           | 7  |

| 2. Previous Work                                    | 9  |

| 2.1 Communication Infrastructure                    | 9  |

| 2.2 Processing Node Hardware                        | 11 |

| 2.3 Communication Protocols                         | 12 |

| 2.4 Modeling and Simulation                         | 13 |

| 2.5 Conclusion                                      | 14 |

| 3. Application: Theory and Research                 | 15 |

| 3.1 Motion and Trajectory Planning                  |    |

| 3.2 Trajectory Optimization Problems                |    |

| 3.3 Parallelization of Optimization Algorithms      |    |

| 3.3.1 Genetic Algorithm                             |    |

| 3.3.2 Simulated Annealing                           |    |

| 3.4 Different Implementation Options                |    |

| 3.5 Conclusion                                      |    |

| 4. Application: Design                              |    |

| 4.1 Hardware Modeling                               |    |

| 4.2 Application Implementing Simulated Annealing    |    |

| 4.3 Application Implementing Genetic Algorithm.     |    |

| 4.3.1 Algorithm Description                         |    |

| 4.3.2 Application Design                            |    |

| 4.3.3 Potential Simulation Deadlock and Resolution  |    |

| 4.3.4 Hardware Modeling – Packet Dropping Rate      | 30 |

| 4.3.5 HW and SW Modeling – Dispatch Rate Adaptation |    |

| 4.4 Conclusion                                      |    |

| 5. Application: Simulation and Evaluation           |    |

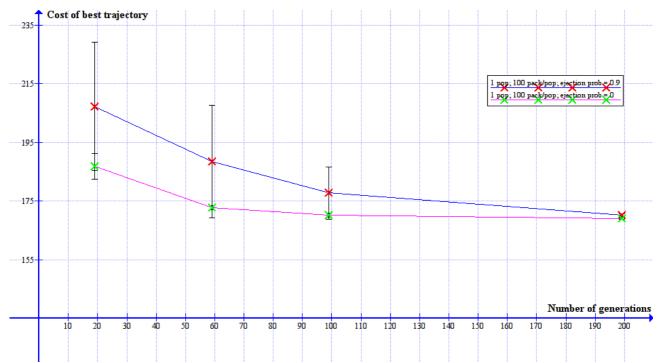

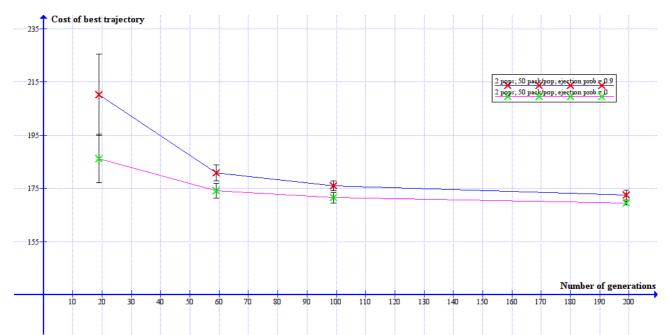

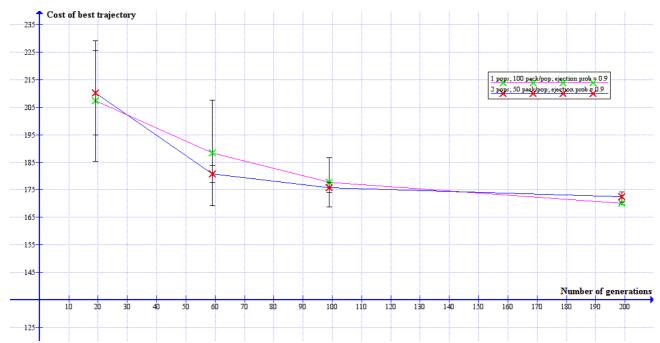

| 5.1 Comparison of SA and GA                         |    |

| 5.2 SystemC Simulation                              |    |

| 5.3 Influence of Packet-dropping                    |    |

| 5.4 Influence of Dispatch Rate Adaptation           |    |

| 5.5 Conclusion                                      |    |

| 6. Hardware: Design – Micro-architecture            |    |

| 6.1 CNW Node Architecture                           |    |

| 6.1.1 Memory Mapping                                |    |

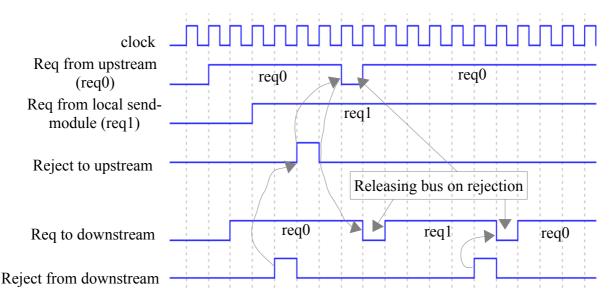

| 6.1.2 CNW Bus Protocol                              |    |

| 6.1.3 Internal Bus Protocol                         |    |

| 6.1.4 FIFO-Controller                               |    |

| 6.1.5 Send-list                                     |    |

| 6.1.6 Send-module                                   |    |

| 6.1.7 Data Consistency of Shared Resources.         |    |

| 6.2 IENW Architecture.                              |    |

|                                                     |    |

| 6.2.1 IENW Node Architecture                    | 56 |

|-------------------------------------------------|----|

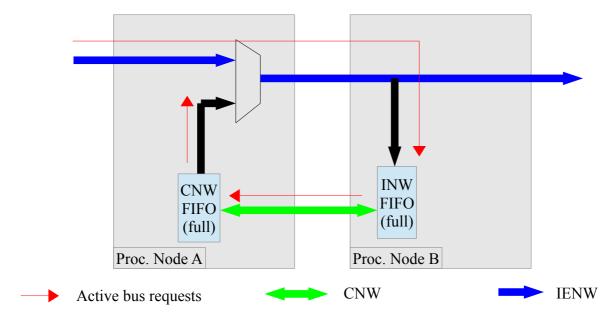

| 6.2.2 Deadlock Avoidance                        | 57 |

| 6.2.3 IENW Protocol.                            | 59 |

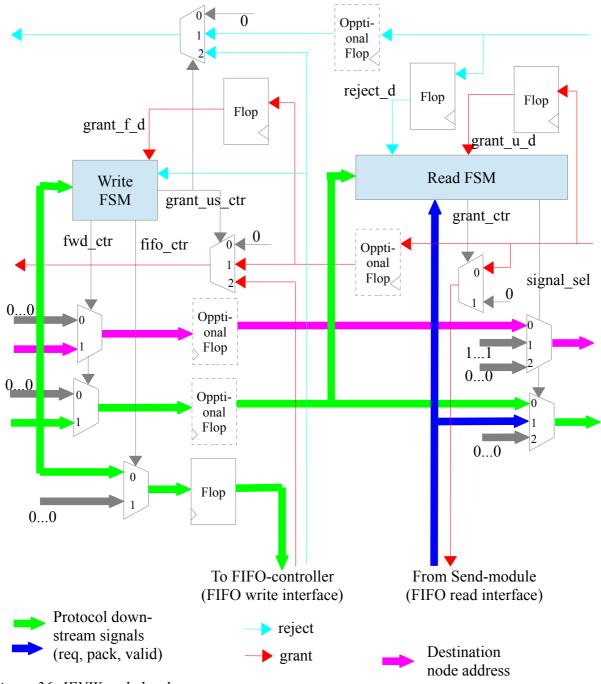

| 6.2.4 IENW Control Logic                        | 60 |

| 6.3 Processing Node Software                    | 63 |

| 6.3.1 Virtual Map Records                       | 64 |

| 6.4 Conclusion                                  | 64 |

| 7. Hardware: Verification                       | 65 |

| 7.1 Design Requirements and Covering Test-Cases | 65 |

| 7.2 Details of Test-Cases                       | 67 |

| 7.3 Conclusion                                  |    |

| 8. Hardware: Synthesis and Evaluation           | 73 |

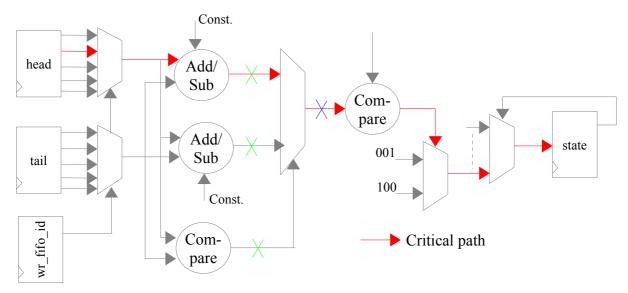

| 8.1 Performance Bottleneck and Resolution       | 73 |

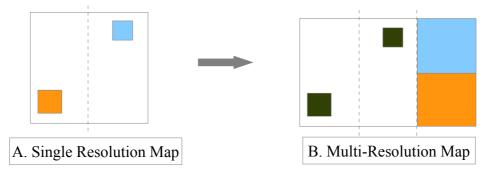

| 8.2 Hardware Resource Usage (Single Node)       |    |

| 8.3 Hardware Evaluation: Multi-node             |    |

| 8.4 Conclusion                                  |    |

| 9. Discussion and Conclusion                    |    |

| 9.1 Accelerator Model                           |    |

| 9.2 Application                                 |    |

| 9.3 Implementation                              |    |

| 9.3.1 Model-Implementation Differences          |    |

| 9.4 Conclusions                                 |    |

| 10. Further Work                                |    |

| Reference                                       |    |

| Appendix A. Guide to Codes                      |    |

| A.1 High Level C Model                          |    |

| A.2 Verilog RTL Design                          |    |

| A.3 SystemC Model                               |    |

| Appendix B. Selected Simulation Data            | 94 |

# List of Terminology

| 2D           | Two Dimensional                                                                                                                                          |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| CNW          | Computation Network                                                                                                                                      |

| FTR          | Flight Trajectory Record – a packet that contains the details of a trajectory, and is passed around in the NoC fabric to calculate the trajectory cost.  |

| GA           | Genetic Algorithm                                                                                                                                        |

| GPU          | Graphics Processing Unit                                                                                                                                 |

| HW           | Hardware                                                                                                                                                 |

| IENW         | Injection-extraction Network                                                                                                                             |

| Мар          | The 2D surface on which the trajectories are defined                                                                                                     |

| Map Segment  | Each element of the grid of rectangular subareas with approximately constant cost-function, in which a map is divided for the simplicity of calculation. |

| PN           | Processing node, i.e. a node of the NoC fabric where all computations are performed – both for the communication and cost calculation                    |

| RADAR        | RAdio Detection And Ranging                                                                                                                              |

| SA           | Simulated Annealing                                                                                                                                      |

| SAM          | Surface-to-Air Missile                                                                                                                                   |

| SW           | Software                                                                                                                                                 |

| Terrain Data | The approximate cost function values associated with a map segment                                                                                       |

| Trajectory   | A directed path on a 2D surface                                                                                                                          |

| UAV          | Unmanned Aerial Vehicle                                                                                                                                  |

| VMR          | Virtual Map Record – a packet that is used to configure the terrain data in the system                                                                   |

# **Chapter 1**

### **Introduction and Motivation**

Many practical problems involve calculating costs of trajectories on a two-dimensional (2-D) map. The map may be a usual geographical map, or some other problem may be transformed into an equivalent form for easier visualization and solution. The cost may also be of different kinds. The simplest of them is the length of the trajectory. However, many more complicated costs may be defined, e.g. the distance traversed along a trajectory on a geographical terrain (with uneven topographic elevations), or to accumulate all positive differences in altitude in the direction of motion along the trajectory and to discard the negative ones. This is generally difficult to solve analytically, but to a cyclist, this would be a measurement of the effort she would require to spend to traverse this trajectory. Costs may also be a linear combination of different factors, e.g. weather situations at different locations on the map, or threat from enemy positions in case of a military application, etc. It is, however, often possible to reduce all such contributing factors into one scalar (e.g. weather condition) and one vector (e.g. terrain gradient) component, as long as the operations performed on them are linearly combinable. The present work proposes a way to perform such trajectory cost computations efficiently, and develops a hardware that implements this approach. This hardware then may be used as a hardware accelerator for any application that needs to perform such 2-D trajectory cost computations efficiently.

### **1.1 Problem Description**

Trajectory costs, as described above, can normally be represented as line integrals (or sums of line integrals) of some cost function along piecewise differentiable trajectories. As mentioned above, one simple example would be to calculate the length, L, of a trajectory, T, on a 2D map. This can clearly be evaluated as the line-integral,  $L = \int 1.dt$ , where the cost-function is a constant scalar,

1. Another such scalar cost function, f(x,y) defined for Cartesian co-ordinates, could be the inverse of the velocity attained by an all-terrain vehicle (ATV) at different locations on a geographic plane, depending on the nature of the soil there, e.g. whether it is firm, loose, sandy, muddy, etc. In such a case, the line-integral,  $\int f(x, y) dt$  evaluates the time taken by the vehicle to traverse the

trajectory, and this will be its cost.

However, it is possible to also have vector cost functions. Let  $\vec{\nabla}(x, y)$  be defined to be the gradient at the co-ordinates (x,y) on a topographical map of a geographical region. The lineintegral,  $\Delta_h = \int_T \vec{\nabla}(x, y) \cdot d\vec{t}$  in this case computes the difference in elevation of the start and end

points of the trajectory, and may be defined as the cost of this trajectory, though there may exist easier ways of computing this quantity than by evaluating a line integral.

Some other trajectory costs may be harder to express as line integrals, e.g. the problem, mentioned at the beginning, of estimating a cyclist's effort to traverse a trajectory in a topographically uneven area. This can be evaluated only as a summation of line-integrals along segments of the trajectory. In order to solve this problem, the trajectory has to be divided into two sets of segments, say S<sub>u</sub>, the uphill set and  $S_d$ , the downhill set, where  $S_u = \{T_1, T_2, ..., T_n\}$ , such that at every point on each of these segments, the condition  $(\vec{\nabla} \cdot \vec{e_T}) > 0$ , where  $\vec{e_T}$  is the unit tangent vector along the direction of the trajectory at that point (assuming a piecewise differentiable trajectory), is satisfied. All other segments of the trajectory make up the set S<sub>d</sub>. Then, the estimate of the cyclist's effort may be represented as  $E_c = \sum_{p=1}^n \int_{T_p} \vec{\nabla}(x, y) \cdot d\vec{t}$ . The gradient may still be regarded as the costfunction, though with constrained applicability.

Another cost, relatively difficult to formulate, is the distance traversed along a trajectory on a geographical terrain with uneven topographical elevations. The x-component of the gradient, say

$\nabla_x$  is the rate of change of elevation at a location in the x direction. If we define  $g_x = \sqrt{1 + \nabla_x^2}$ it provides the local ratio of actual distance traversed on the topographical map to the displacement along the x-direction. Similarly, the y-component of gradient,  $\nabla_y$  may be used to define  $g_y = \sqrt{1 + \nabla_y^2}$ . Now, defining a vector function on the 2D map,  $\vec{g}(x, y) = g_x \cdot \vec{i} + g_y \cdot \vec{j}$ , where  $\vec{i}$ and  $\vec{j}$  are respectively the unit vectors along the x and y directions, the line-integral,  $d = \int_T \vec{g}(x, y) \cdot d\vec{i}$  yields the actual distance traversed on the local geographical topography by

following a trajectory, T, <u>directed only towards positive x and y directions</u> at every point (if it is differentiable at that point) on it. Similar expressions can be formulated for other orientations of the trajectory. Just like in the case of the cyclist's effort, a general trajectory can then be divided into segments, each of which lends itself to application of one of these formulae, and the results of these line-integrals can then be summed up to derive the total distance traversed on the geographical terrain following the trajectory.

It is possible to also have costs which do not involve line-integrals, but are defined by extrema of a cost-function along it. Using the previous examples of topographic maps, it may be the highest elevation of a point on the trajectory, or the steepest gradient along it. It is also possible to define the overall cost of a trajectory to be a (linear) combination of the basic costs of the types explained above. A road-builder, for example, would define the overall cost of the proposed lay-out of a road (represented as a trajectory for our purpose) depending on its length, its maximum steepness, maximum curvature, how long a vehicle would take to traverse it, etc.

As this discussion shows, the computation of trajectory costs may often be quite complicated, even though required in many applications. Hence it was felt that an efficient way to perform this task would be quite beneficial. Therefore, the aim was to define an efficient algorithm for estimating such trajectory costs, and develop a hardware system that can implement it efficiently at a high through-put, which would require parallelization. In order to enable rapid prototyping and deployment, an FPGA implementation is expected to be ideal. In order to exploit the full flexibility offered by FPGA's, the design is required to be scalable, so that it can be easily adapted to changing system requirements, whether involving change in complexity of the problem, or the throughput requirements.

### **1.2 Proposed Algorithm**

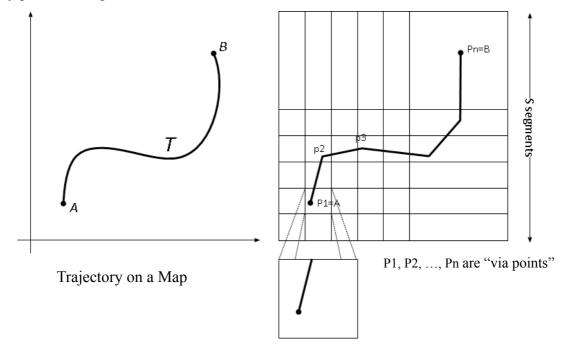

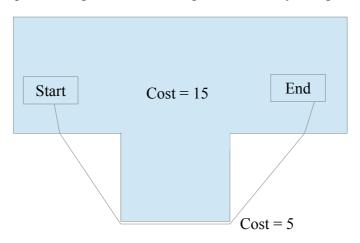

As explained above, the cost of a trajectory can often be modeled as the line integral of a costfunction, or a linear combination of the line integrals of multiple cost-functions. In order to estimate the line-integral, the map is proposed to be divided up into an SxS unit square grid, and the costfunction(s) is/are assumed to be constant over each square, called a "map segment". The trajectory is similarly represented by a piece-wise linear approximation defined by the end-points (termed "via-points") of each of these linear segments in their proper order, as shown on Figure 1. The contribution of each map segment to the overall trajectory cost can then be computed as the product of the length of the part of the trajectory in that map segment and the value of the cost-function(s) (evaluated along the direction of the trajectory in case of a vector cost-function) in that map segment. As explained above, the cost-functions are assumed to be constant over the whole map segment, but in case of a vector cost-function, its value along the direction of the trajectory may change if a via-point is encountered inside a map segment, and the trajectory direction changes at that point. This has also to be taken care of during the cost computation. The total cost of a trajectory can then be estimated by summing up the cost contributions of all map segments, that the trajectory passes through.

Figure 1: "Map" divided into segments and piecewise linear approximation of trajectory

An analogous approach can be utilized to evaluate the costs which are defined as extrema along the trajectory. In this case, instead of adding up the contributions from the various map segments that the trajectory passes through, they can be compared and the require minimum or maximum can be accepted as the cost. Because the extremum-type and the line-integral-type problems both have naturally analogous solutions, and because most of the useful costs are expected to be of the line-integral type, the discussion will henceforth primarily refer only to that. However, the analogous operations for the extremum-type cost can always be derived easily from it.

This algorithm is also effective at tackling the cost computations that involve segmentation of the trajectory, as was required for the last to examples in Section 1.1, because trajectory-segmentation is used as one of its basic steps.

#### **1.3 Proposed System Design**

In order to perform the above-mentioned computations efficiently, one natural solution envisioned was to use an SxS 2-D array of processing nodes connected with each other through a network-onchip (NoC) of mesh topology, where the 2-D processing array maps directly onto the 2-D "map segment" grid described above with 1-to-1 mapping between the processing arrays and the map segments, each processing node containing the (locally constant approximate) values of the costfunction(s) in the corresponding map segment, and capable of computing the contribution of the local map segment to the total cost of a trajectory. When computing the cost of a trajectory, the trajectory can be defined as an ordered list of via-points, as described above, encased in a packet, which can be passed inside the NoC from processing node to processing node along a path that maps to the trajectory concerned, while each processing node encountered on the path adds its cost contribution to a data field in the packet. The routing decision at each processing node can be taken based on the via-list. The data field in the packet is initialized to 0 before it starts its journey in the NoC, and it contains the computed cost of the trajectory when the packet reaches its destination processing node, and the destination has added its cost contribution to the said data field.

Being a NoC-centric design, the system is easily scalable (i.e. more nodes can be added easily). Also, it is easy to see that all communications are local between neighboring processing nodes, as the trajectories are continuous. Still it is a problem that the processing array size is determined by the size and the granularity of division of the target map, thus limiting the scope of usage of the hardware for widely varying maps. This design may also struggle to maintain good hardware loading. The loading of a processing node is defined as the proportion of time it is "active", i.e. it spends performing useful calculations on a packet, e.g. routing or cost computation, and the over-all hardware loading is defined as the average loading of all the processing nodes. Defining  $P_n$  to be the n-th processing node, and the total number of nodes in the processing array to be N, let us define:

$A_n(t) = 0$  if  $P_n$  is inactive at time t = 1 if  $P_n$  is active at time t

From this, the hardware loading (HL), as defined above, can be formulated as:

$$HL = \frac{1}{N} \sum_{n=0}^{N} \left( \frac{1}{T} \int_{0}^{T} A_{n}(t) \, dt \right)$$

where T = the period of use of the hardware. This expression may be alternatively written as:

$$HL = \frac{1}{T} \int_{0}^{T} \left( \frac{1}{N} \sum_{n=0}^{N} A_{n}(t) \right) dt$$

which can be interpreted as the average proportion of the "active" processing nodes in the processing array.

In order to make a rough estimation of the HL, let us assume that every packet under processing inside the processing array is always active, i.e. being processed by one node or another, and that each processing node can process only one packet at a time. Then, HL is also the ratio of the average number of active packets to total number of processing nodes in the array. If, the average latency of a packet inside the hardware (i.e. the time required to complete its cost computation) be T<sub>1</sub>, and one new packet is assumed to be launched for computation at an interval of T<sub>1</sub>, then in the first T<sub>1</sub> interval of the execution, the hardware receives (T<sub>1</sub>/T<sub>1</sub>) packets, but likely does not produce any output packet. But, after that in every T<sub>1</sub> time interval it receives a new packet and produces one new output on average, thus reaching a stochastic steady-state. In this steady-state, then, the number of active packets inside the hardware can be estimated as (T<sub>1</sub>/T<sub>1</sub>). If the map is divided into an SxS grid, and accordingly a processing array of size SxS is used, then N=S<sup>2</sup>, and  $HL=T_1/(S^2, T_1)$ .

Assuming that the map area is selected near-optimally, i.e. the map-area chosen contains very little area beyond what is required to represent the trajectories, the smallest length of a trajectory would be close to S. On the other hand, the maximum length possible for a straight-line trajectory is  $\sqrt{2S}$ . So, if the trajectories under consideration are relatively well-behaved, i.e. not with too many bends, their length will also be in the order of S (say, below 3S or 4S). Thus, it is clear that the average trajectory length is of the order of S, and the packet computation latency is expected to be proportional to the trajectory length. Hence, it is reasonable to assume that  $T_1 = \alpha S$ , where  $\alpha$  is a constant. This may be used to rewrite  $HL = \alpha/(S.T_t)$ . This means that with increasingly finer division of the map (i.e. increasing S), in order to maintain constant HL, the T<sub>t</sub> has to be reduced proportionately. It also means, of course, adding more processing nodes into the hardware, which is a problem in itself. Even the required reduction of T<sub>t</sub> is expected to be a problem, as the application

that would use the proposed hardware for accelerating its trajectory cost calculation, would ideally prefer to not have to change its own throughput with the changes in map division granularity, which may be required for proper accuracy of the cost computation.

The afore-mentioned two problems (modifying hardware and modifying application throughput) associated with the proposed hardware structure can be solved by allowing multiple map segments to be mapped onto the same processing node. An intelligent and simple way of achieving this, while maintaining the desirable quality of keeping all communications local, is by introducing the concept of logically folding the map, as explained below.

#### **1.3.1 Map Folding**

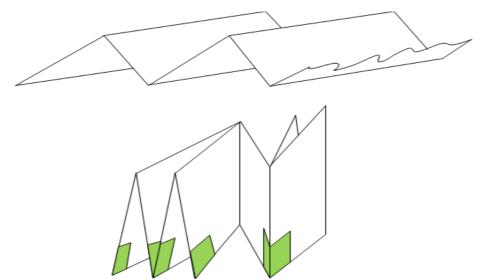

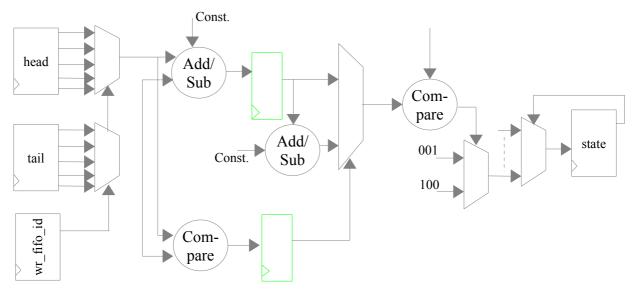

The idea is to define a "logical folding" of the map along each axis as shown on Figure 2 when defining the mapping of map segments to the processing nodes. In this scheme, all the map segments that end up coinciding after the folding, are mapped on to the same processing node. For example, if there are 12 map segments (0...11) along the X-axis, and if only 2 folding layers are used along this axis, then the map segments (0...5) coincide on (11...6) respectively, and the processing array requires only 6 nodes along the X-axis, where node 0 processes map segments 0 and 11, node 1 processes map segments 1 and 10, etc. The same map may be folded along the Xaxis using 3 folding layers, and then, map segments (0...3), (7...4) and (8...11) coincide respectively. It requires a processing array of 4 nodes along the X-axis, where node 0 processes map segments 0, 7 and 8; node 1 processes map segments 1, 6 and 9, and so on. The same idea is applicable also along the Y-axis. Thus, a 12x12 map after folding with 3x3 layers (i.e. 3 layers due to folding along X-axis and 3 layers due to folding along Y-axis, yielding total 9 layers) will have map segments (0,0), (0,7), (0,8), (7,0), (7,7), (7,8), (8,0), (8,7) and (8,8) coinciding and being processed by the processing node (0,0) in a processing array of size 4x4. The folding does not change the logical representation of the map, map data or the trajectories. It only modifies the mapping of the map segments onto the processing nodes, the mapping thus becoming many-to-one.

*Figure 2: Folding the map. Top: Folding along one axis only. Bottom: Folding along both axes – the green map segments all map to the same processing node.*

This mapping mechanism ensures that different map resolutions and map sizes may be computed using the same processing array. It also ensures that the map segments which are neighbors on the map, are mapped either onto the same or neighboring processing nodes, preserving the property that all communications in the hardware are local. This also ensures that increasing map resolution (i.e. allowing finer division) would increase the packet latency in the hardware, allowing the application to increase the interval between the packets it launches to the hardware in order to maintain the same level of loading. This relaxes the timing requirements on the application and should be easier to implement. If the application needs to be made oblivious of the resolution change, that may also be achieved by using a hardware "packet launching" mechanism, that can take care of this, instead of the application. But this has to be decided on the basis of specific system requirements on a case by case basis, and is thus not considered further in this work.

#### **1.3.2 Processing Nodes**

As explained before, the NoC fabric connects the processing nodes, that perform at least two important tasks - the cost computation, as well as routing calculation, determining in which of the four possible directions each packet has to be routed from the present node. The routing calculation algorithm is expected to be fixed, allowing a packet to follow a path in the processing array, that traces the trajectory in the map specified by the packet's via-list. Thus it can possibly be implemented as a hardware component. However, the cost computation must be reconfigurable, with many different kinds of possible operations, including but not limited to the ones explained in the Section 1.1. In order to ensure the best reconfigurability, the cost computation algorithm is best implemented as a software running on a small microprocessor. These calculations also require the length, and possibly the direction of the trajectory in the present map segment. These data can be computed as byproducts of the routing calculation. Hence, the cost computation and the routing computation are expected to be quite closely related. So, it is decided, as an initial design decision to implement both of them in software running in the present processing node. Therefore, every processing node may be thought of consisting of a communication node, that handles the communication requirements of the NoC, and a microprocessor, which performs the routing and cost computations.

### **1.4 Methodology**

The outline of the basic concepts described so far was available as a part of the project proposal, including the key algorithmic concept of map folding. The ultimate aim of the work was to study the proposed hardware solution in further detail, and implement it. The work would have a hardware design in RTL, and possibly a prototype in FPGA as its final result. Additionally, it would be useful to develop an example application, that can use this hardware as a hardware accelerator to accelerate its trajectory cost computations while exploiting the hardware optimally, in order to evaluate and demonstrate the efficacy of the design.

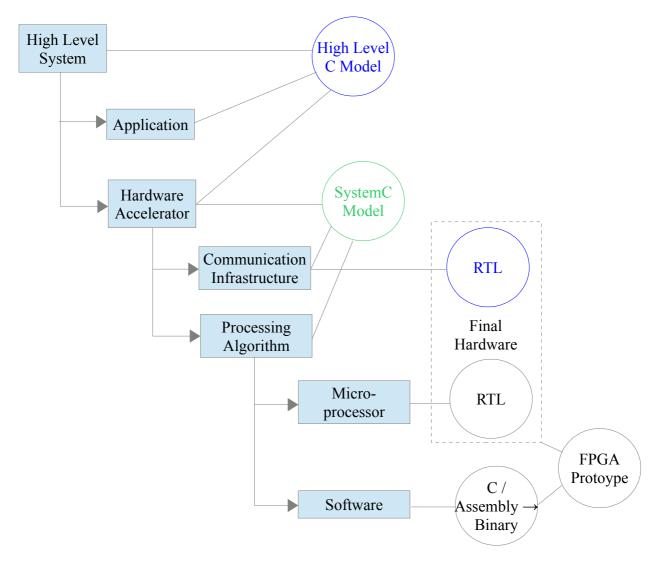

In order to smoothen the design of the "hardware accelerator", i.e. the hardware processing node array connected through a NoC as described above, the hardware-software co-design approach was followed, in which the accelerator system was first modeled in SystemC including both the hardware structure as well as the software to be run on the microprocessor in each processing node. The data gathered from the simulations of this model would be used in two ways. Firstly, an even higher level design would be developed in C-language that models a system comprising an external application and the hardware accelerator. This design can be simulated to understand the mutual influences between the application and the accelerator designs, whereby constraints can be formulated for future application designs and requirements can be generated for the hardware design. Secondly, the micro-architecture of the hardware accelerator, consisting of the communication infrastructure (NoC and communication nodes) and the algorithm to compute both cost and routing, implemented as a software running on a processor, as described in Section 1.3.2, would be worked out, and both hardware and the software components of it would be designed and implemented. Each of these tasks again involve further partitioning and micro-architecture

definition, implementation, verification and performance evaluation. The designs are different levels of abstraction are also mutually interdependent. Simulations of the higher level models help evaluate architecture level decisions, while data received from the evaluation of the lower level models help to fine-tune the higher-level models. Thus, the whole design involves intimated feed-back between the three levels of abstraction used (high-level C model, SystemC model, HW/SW implementation), and may potentially involve some iterations because of that. The whole scope of the work can be described in a graphical format as on Figure 3.

*Figure 3: Scope of work in the whole project from system definition to HW/SW. The fields in blue mark the principal contributions in the present semester*

### **1.5 Present Contributions**

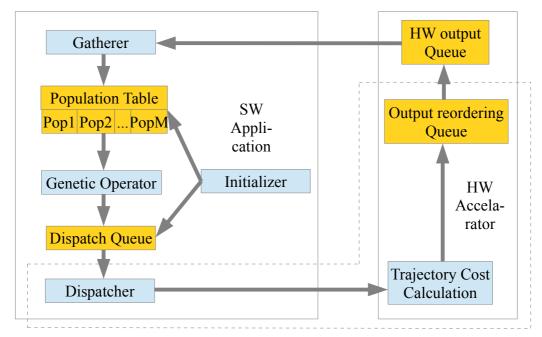

The previous section describes the different stages of the whole project. In the previous semester (Autumn 2013), the main activity was to define and simulate the SystemC model (marked in green on Figure 3) to evaluate the hardware accelerator. The relevant findings from this work will be summarized in Chapter 2. The main activities in the present semester (Spring 2014) have been:

1. the development of the high level C-model consisting of an example application and a model of the hardware accelerator and simulating it to evaluate the system, and

2. the development and implementation of the communication infrastructure in RTL.

These have been marked in blue on Figure 3. The details of the contributions made in the present semester will be described in the Chapters 3-8, as listed below:

- Chapter 3 describes the motivation and preparation behind the choice of the high level application, supported by extensive literature survey.

- Chapter 4 describes the development of the high level C model, including both an application and a model of the hardware accelerator.

- Chapter 5 describes the evaluation of the system, both through simulating the high level C model, as well as the SystemC model developed last semester and described in Chapter 2.

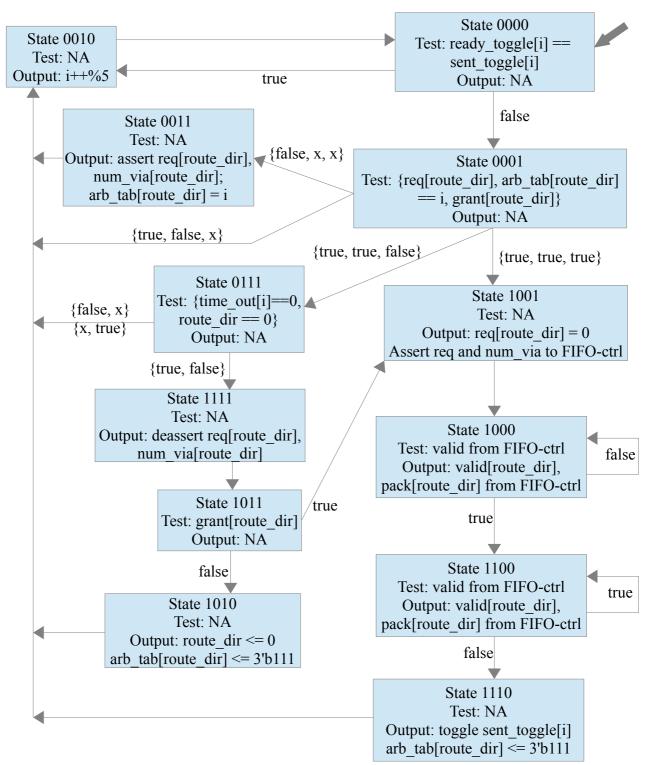

- Chapter 6 describes the hardware architecture of the accelerator, clearly distinguishing the communication infrastructure from the processor, and then describes the micro-architecture of the communication infrastructure in detail. This has been implemented in Verilog RTL.

- Chapter 7 outlines the verification strategy of the hardware. All the described test-cases have been implemented in Verilog testbenches and used to unit-test the design. However, only completely directed testing was used, and thus the coverage is expected to be low. But it provides a comprehensive description of the various functional requirements to be satisfied, and guidelines for testcases to test them. This can be easily developed to execute fully fledged verification.

- Chapter 8 describes the performance analysis of the design through synthesis and timing.

Thus, in this semester, on one hand, the high level C model has developed and simulated, and on the other the complete hardware for the communication infrastructure has been implemented in Verilog and evaluated for performance, and unit-tested to ensure that it is free of obvious bugs. But it cannot yet be certified as completely bug-free as the verification was not comprehensive.

The next chapters summarize and discuss the findings from the previous chapters (Chapter 9) and discuss the possible direction of future work (Chapter 10) to finish the project by completing the verification of the hardware implemented this semester, by designing and implementing the processor (if not using a standard processor off-the-shelf), by implementing the software, and finally by prototyping the whole HW/SW of the accelerator on an FPGA. These could not be attempted in this semester due to paucity of time, though Section 6.3 does provide a brief guideline for the software development, and synthesizable RTL for the communication infrastructure has been developed, and is ready to be used in prototyping.

# **Chapter 2**

### **Previous Work**

As preparation for implementing the hardware accelerator proposed in Chapter 1, a top level system architecture was first worked out and modeled in SystemC and simulated in order to evaluate its feasibility and quality in terms of various system performance parameters. This activity was executed during the autumn semester 2013, and [11] is the project report for it. Some of the work in the present semester (spring 2014), to be described in the present document, uses the findings reported in [11] as its starting point and design constraints. Hence, the relevant findings and design decisions described in [11] are being summarized and catalogued with proper references in this chapter, so as to place the present activity in its proper context.

### **2.1 Communication Infrastructure**

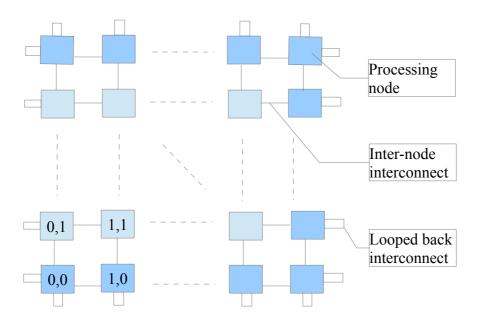

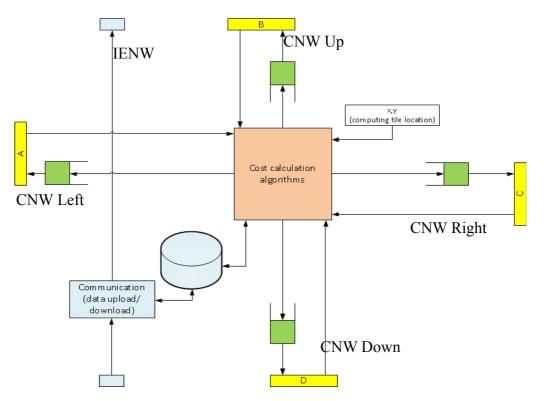

As described in Chapter 1, the hardware accelerator is made up of a 2-dimensional grid of "processing nodes", connected to each other through a network-on-chip, where each processing node is associated to one or a set of "map segments" and performs the trajectory cost calculation for that/those specific segment(s). Refer to Figure 4. Each trajectory cost calculation problem is represented by a packet (called flight trajectory record, FTR) that is passed along the processing array in the required order, while each node incrementally adds its contribution of the cost to the packet, and the calculation finishes when the packet reaches its destination.

Figure 4: Mesh NoC Topology proposed for CNW

The map folding strategy described in Section 1.3.1 implies that a processing node at the edge of the processing array may be associated to multiple neighboring map segments. When a trajectory passes between such map segments, the "looped back interconnects" as shown above may be utilized to route the corresponding computation packet from the corresponding processing node back to itself.

#### **CNW Routing**

The network-on-chip involved in thus transporting the FTR packets has been termed "computation network" (CNW). As is clear from Section 1.3.1, the mapping of the "terrain data map" onto the processing array is performed in such a fashion that any pair of neighboring map segments either map onto the same processing node, or onto a pair of neighboring processing nodes. Also, because the trajectories are assumed to be continuous, it follows that all packet exchanges are limited between neighboring processing nodes. However, when a trajectory enters as well as exits a map segment very close to one of its vertices (or when the trajectory passes from one segment to one of its diagonally neighboring segments exactly through their common vertex), the calculation may be somewhat sped up by routing the corresponding packet <u>diagonally</u> and accepting a cruder cost approximation of the short omitted segment using the cost function of one of its computing neighbors. The support of "diagonal routing" introduces some cases where the inter-node communication is no more local, rather goes through the intermediary of exactly one node, which is a neighbor to both the source node and the diagonally located destination node. To make things easier, the switching mechanism in this case has been taken to be "store-and-forward" (SAF).

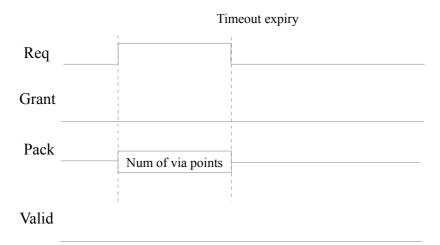

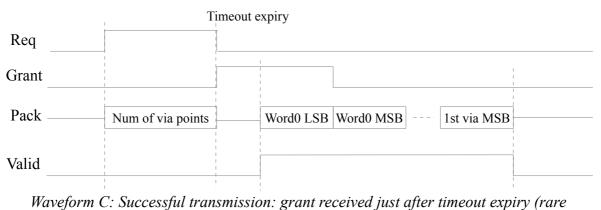

#### **CNW Deadlock Resolution**

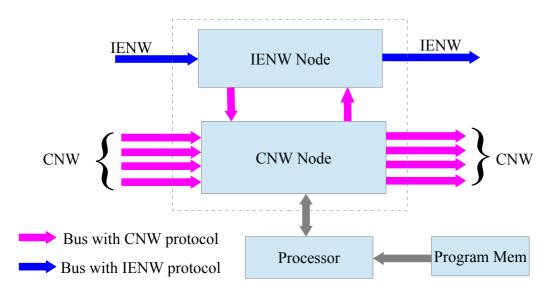

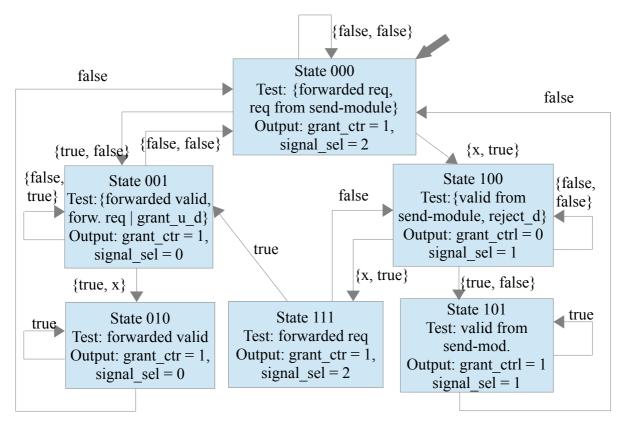

It is to be notes, however, that the trajectories may involve any kind of turns and twists, thus making it imperative that the CNW be able to route packets in all possible directions. As explained in Sections 2.5 and 4.1.3 in [11], this is expected to lead to unavoidable deadlock situations in the network. Hence, a deadlock-resolution strategy was developed to solve this problem. The strategy is based on a deadlock-timeout counting. Each time a processing node tries to pass on a packet to its next neighbor, it initiates a timeout counter, and if the packet cannot be successfully sent out within this period, a deadlock is assumed to have been detected, and the corresponding packet is "dropped" from processing. If the external application requires, it can relaunch the computation of those "dropped" packets later on. But in order for this to happen, the external application needs to be informed of the identity of the dropped packets. Therefore, a mechanism is required for a processing node to communicate this information outside the hardware accelerator, when it is already facing a deadlock in the CNW. In order for this to happen reliably, a secondary low-bandwidth deadlock-free network-on-chip, called the "injection-ejection network" (IENW) was envisioned to connect all the nodes in addition to CNW.

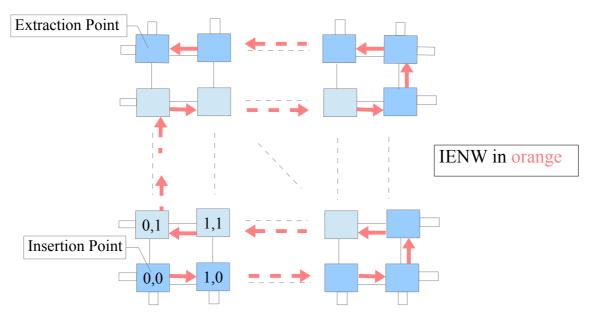

#### IENW

IENW doubles in for transporting the FTR packets from the external application to the first processing node inside the hardware accelerator, and also from the last node out of the hardware back to the application. Different possible topologies for IENW were discussed and compared in Section 4.2 in [11]. During the course of the work in the present semester, however, a quite different topology was developed and implemented as described in Section 6.2/Figure 35 of the present document. All in all, however, the existence of the IENW ensures that all packets launched by the external application reaches the respective first processing node, and all packets ejected by the hardware, whether because of a detected deadlock or because the computation was finished for it, are transported back to the application. As explained above, the IENW was, however, expected to be simple and low-bandwidth, and thus occupied a lower priority in the design task. Thus the SystemC model developed in last semester did not try to model it accurately, and instead used a very simple replacement as described in Section 6.2/Figure 14 of [11], concentrating instead on modeling the CNW and the processing nodes.

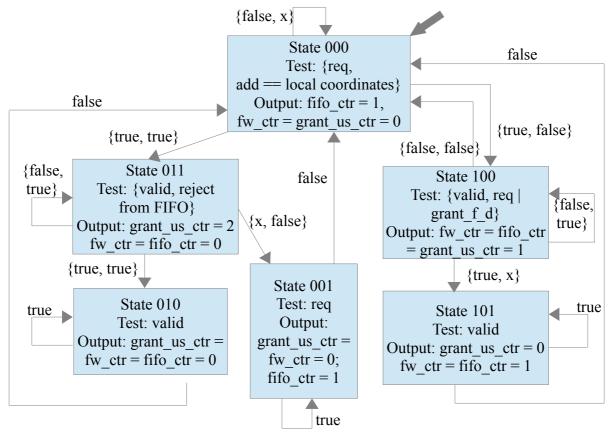

### 2.2 Processing Node Hardware

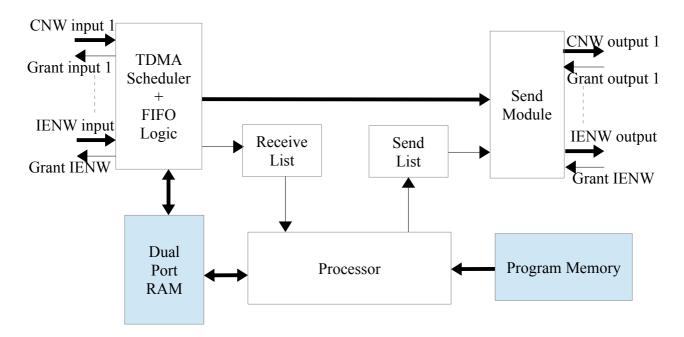

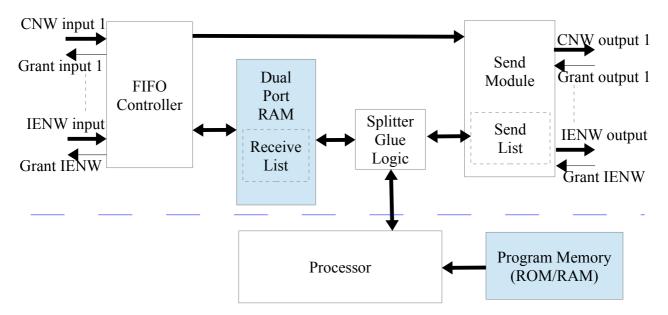

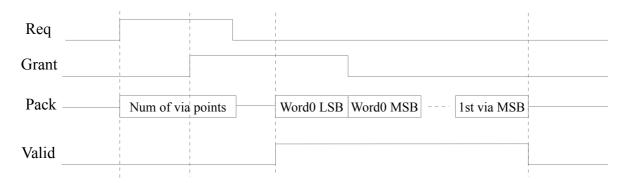

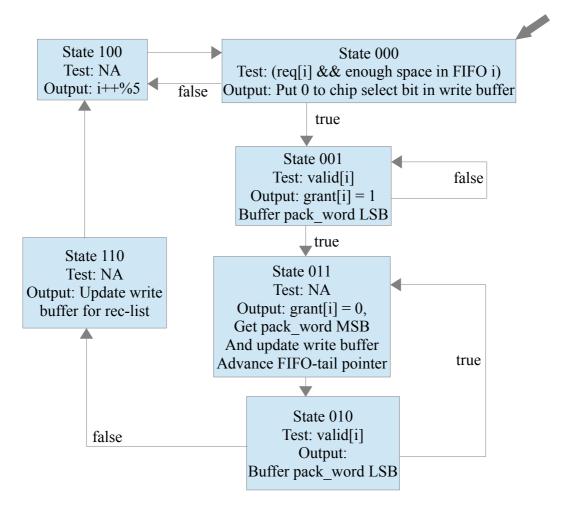

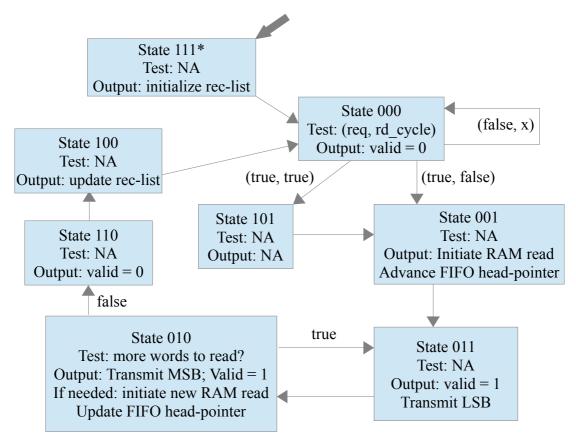

The basic structure of the processing node was taken to be made up of the logic required to communicate over CNW and IENW, as well as the logic required to execute the cost calculation. Thus the basic logical structure of the node was envisioned as below on Figure 5, where FIFO's were instantiated on the CNW output interfaces. FIFO's could alternatively be instantiated on the input interfaces.

Figure 5: Logical structure of processing node with FIFO on the output

#### **RAM Optimization**

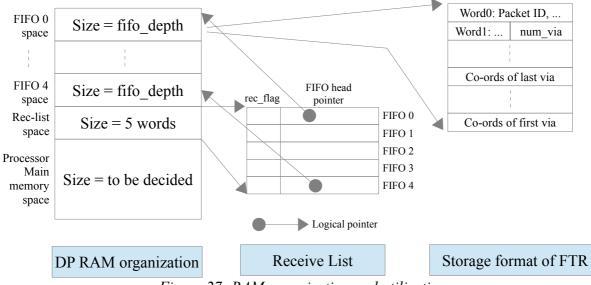

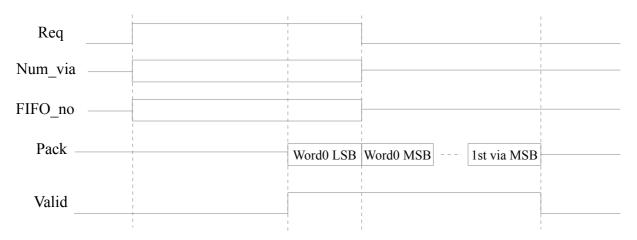

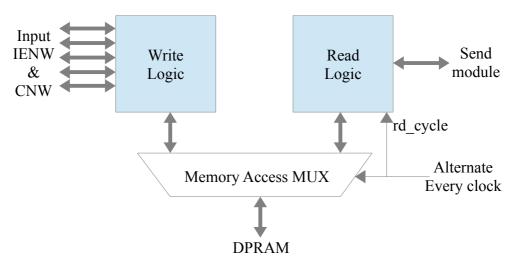

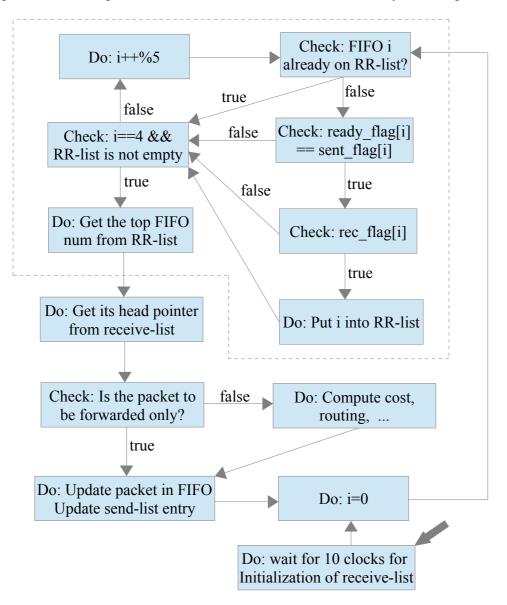

A direct hardware implementation of this architecture is, however, deemed to be inefficient in terms of memory usage, especially if targeting an FPGA implementation, as each FIFO needs its own associated memory, but FPGA's only have a limited number of block RAM's to efficiently implement that. Thus, it was decided to merge the RAM's of the FIFO's as well as the data memory of the processor into one physical dual port RAM. This way, the required number of RAM's per processing node is minimized. At the same time, this also eliminated any requirement of copying the FTR data from the FIFO's into the processor data memory. However, it was noticed that this is much easier to implement if the FIFO's are instantiated on the input CNW/IENW interface rather than the output interface, because the knowledge of the correct output interface for a packet presupposes the completion of the local routing calculation, which may actually be performed by the processor, and thus requiring the storage of the packet in the data memory. If the FIFO's are placed on the output, then the packet will need to be copied into the correct FIFO (which may share the same memory, but will likely have its own separate address space) after the completion of the routing calculations, thus introducing extra delay. If the FIFO's are introduced on the inputs, on the other hand, then there is no such copying involved. The sharing of memory among different FIFO's, however, can be achieved only at the expense of a reduced data transfer rate, as only one FIFO can be read/written in any clock-cycle, thus giving rise to a TDMA-like scheduling of the RAM access for the different FIFO's. This was, however, expected to be a reasonable limitation, because the data availability rate is expected to be determined by the much lower throughput of the processor, which is required to perform fairly complex tasks of arbitration, routing, cost computation, etc. The resultant micro-architecture of the processing node (ignoring the difference between IENW and CNW) is shown on Figure 6 below.

Figure 6: Micro-architecture of Processing Node (with FIFO on input)

The "TDMA scheduler+FIFO logic" block interfaces with the input CNW/IENW ports and writes the incoming packets into the dual port RAM, implementing the FIFO's. It also reads out the packets and sends them to the send-module on request, in order for the packets to be sent out to the next downstream node or to be ejected through the IENW. The processor can manipulate the packets in situ inside the dual port RAM, to be implemented as a block RAM, in case of an FPGA implementation. The "Receive List" data-structure is used by the FIFO-Logic to communicate availability of packets in the FIFO to the processor. Similarly, the "Send List" data-structure is used by the processor to communicate the completed packet. This design, after some minor modifications, has been used as a starting point for further development and implementation of the hardware in the present semester, as has been explained in Chapter 6.

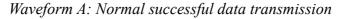

### **2.3 Communication Protocols**

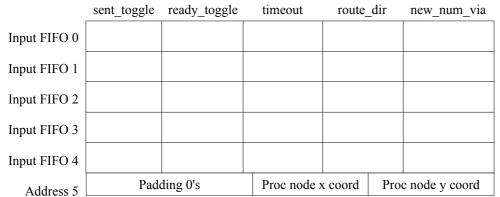

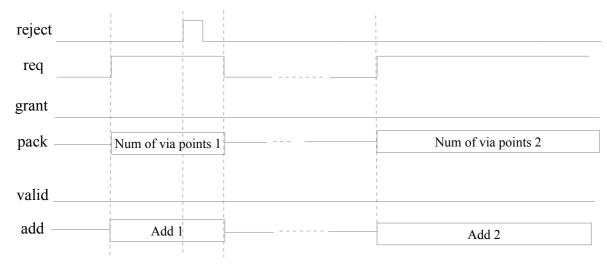

Packet level protocols for the communication were also worked out in the work described in [11]. As described in Section 5.2 of [11], two kinds of packets were planned for – Virtual Map Records (VMR) and Flight Trajectory Records (FTR). VMR is used to load the map data into the processing nodes, whereas FTR is used to represent a trajectory in the map, and is manipulated by the processing array to compute the associated cost. A list of the required fields in these packets has been presented in the afore-mentioned section. These structures have been found to be adequate during the work performed in this semester, but a couple of restrictions have been imposed on them:

1. The least significant 2 bytes of the 2nd (4 byte-)word of an FTR has to be the num\_via (i.e. via-list size) field.

2. The hardware treats VMR packets the same way as FTR's. Hence, the least significant 2 bytes of the 2nd (4 byte-)word of a VMR packet has to equal the size of the packet in words minus the size of FTR header in words, allowing the hardware to calculate the packet size correctly.

Apart from the packet structure, a routing calculation algorithm was also developed, and presented in Section 4.1.4 of [11] for CNW.

### 2.4 Modeling and Simulation

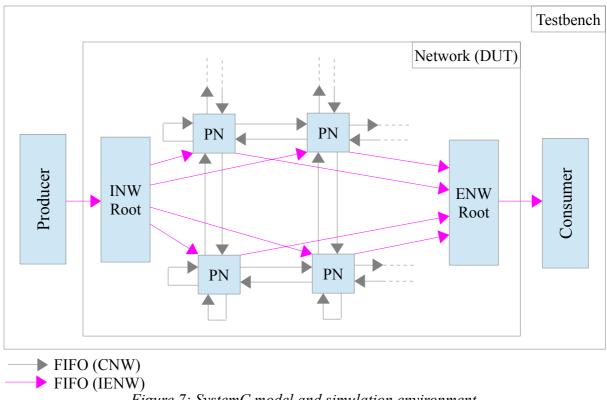

The design described above was modeled in SystemC, as described in Chapter 6 of [11]. Some simplifications were made for the ease of implementation, when they were not expected to influence the system behavior significantly, e.g. the IENW was implemented as two rooted trees of height 1, and the FIFO's were instantiated between the processing nodes, instead of inside as the connecting elements. The resultant structure is shown on Figure 7.

Figure 7: SystemC model and simulation environment

This model was used to thoroughly evaluate many performance parameters of the system, and the results have been presented in Chapter 7 of [11]. The results were consistent with the design expectations, including the fact that the folding concept introduced in Section 1.3.1 does ensure good utilization of the hardware resources when computing costs of random trajectories. Some of the important characteristics of the system as designed and validated by simulation are as follows:

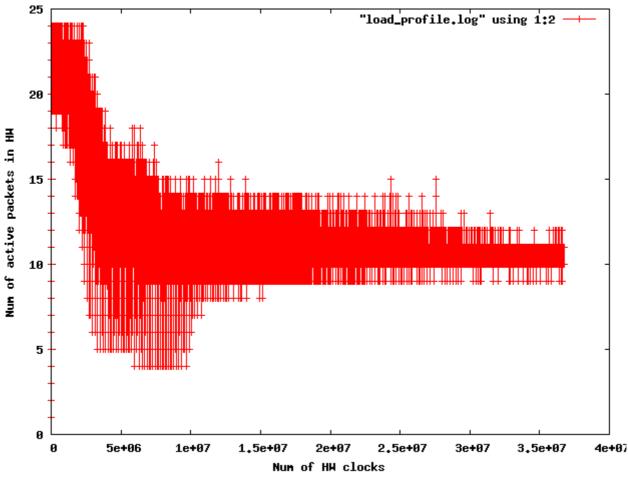

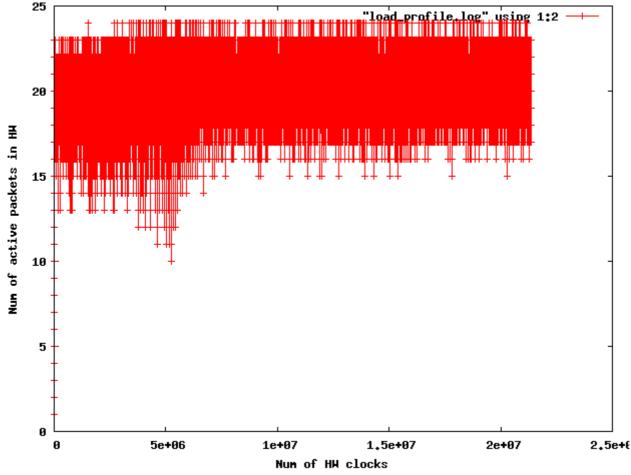

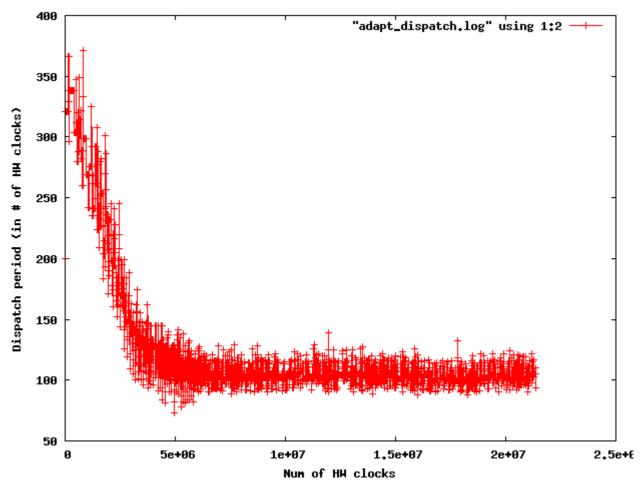

1. When the incoming packet characteristics (e.g. trajectory length, number of via points, etc.) remain statistically stable (e.g. when the packets are completely random), the system seems to have a maximum supported throughput. When packets are fed in at a higher rate than that, many packets are ejected to approximately maintain this saturation throughput of successfully computed output packets (Figure 18 of [11]). So the hardware may be thought of as behaving statistically like a pipeline with initiation interval given by this saturation

throughput.

- 2. It is hard to predict the computation latency of an individual packet inside the hardware, as it depends on factors like presence and number of other packets in the different nodes it visits, and whether they have arbitration and routing conflicts with this packet, etc. However, the latency also includes a trajectory-length dependent component, which is easier to estimate.

- 3. Because of the unpredictable latency, and also because the time interval between the incoming packets is usually much smaller than the average latency (in order to exploit the "pipelining" effect described above), the order of completion of packet computation is unpredictable.

- 4. Not all packets that are launched for computation may finish successfully. Some may be "dropped"/"ejected" in order to solve possible CNW deadlocks, as described above in Section 2.1. As expected, the packet dropping becomes significant when the input throughput exceeds the maximum supported throughput, and statistically increases linearly after that.

Any application that would use the proposed hardware as an accelerator for its trajectory cost calculations must be aware of and accommodate this system behavior.

# **2.5** Conclusion

It can be concluded that the work from the last semester (autumn 2013) led to a good high level understanding of the expected behavior of the design under development, and it also provided guidelines to further work. While a significant part of the design work has been further developed leading to the hardware implementation in RTL in this semester (Chapter 6), it has also been used to develop a higher level C-model, with help from additional SystemC simulations (Section 5.2) to help in developing and evaluating an application (Chapter 4). The following Chapters 3-5 provide an overview of what kinds of applications may possibly use the proposed hardware as an accelerator, describe a simple application, explain the motivation behind it, and demonstrate that it is indeed possible to use the proposed hardware efficiently with a carefully designed application. This exercise provides useful data about factors to be considered in both application development as well as hardware development. Chapters 6-8, on the other hand, describe a hardware implementation based on the findings of last semester as explained in this chapter, as well as with guidance from the application development. Hence the present work may legitimately be viewed as the continuation of the work done last semester and described in [11].

# Chapter 3

# **Application: Theory and Research**

As explained in Chapter 1, the system under consideration is envisioned to be used as a hardware accelerator for computing trajectory costs over a 2-dimensional domain. Evidently, such a hardware will be useful to speed up applications which require computation of many 2D trajectory costs. One obvious application would be the determination of the optimal trajectory between two points on a map under different constraints and cost functions using heuristics that need to evaluate the costs of many different trajectories. The literature was surveyed to find out the state-of-the-art techniques in the relevant field of motion and trajectory planning, Cf. [1] – [10].

### 3.1 Motion and Trajectory Planning

Motion and trajectory planning, as discussed in [1], is a vast field of investigation with numerous practical applications, e.g. finding the best or a feasible trajectory between two points on a geographical 2D map under different constraints. The quality of the trajectory may be decided, e.g. by its length, or the time consumed to traverse it by a given vehicle, or the energy expended in doing so, etc. The constraints may be environmental, e.g. the terrain may have obstacles, or it may derive from the degrees of freedom of movement, the body under motion possesses, e.g. human beings can control their speed and direction of motion in all possible directions on a 2-D surface, i.e. they have 2 degrees of freedom of translational motion – along the two perpendicular Cartesian axes on the 2-D surface, and 1 degree of freedom of rotational motion around the axis perpendicular to the surface. A car, on the other hand, can only accelerate or decelerate along the front-rear axis, and turn left-right around the vertical axis, and thus has 2 degrees of freedom. These two kinds of planning problems are described respectively as holonomic - having full control over motion in all directions – and nonholonomic problems, which concern less controllable bodies or vehicles. In either case, the motion (i.e. speed or direction) of a moving body can be altered in a specific way by applying a specific "control input" (e.g. turning the steering wheel or stepping on the gas or brake pedal of a car) for a specified amount of time. The solution of a motion planning problem is thus given by an ordered set of {control input, duration} pairs. In order to optimize a trajectory, it is often required to first solve a feasible motion planning problem, and then use trajectory planning techniques to optimize the resulting trajectory.

[2] proposes an efficient algorithm for finding a feasible solution to a nonholonomic motion planning problem. Explained in terms of a geographical terrain, the problem is to find a feasible trajectory for a nonholonomic body to move from one point to another on a 2-D surface under environmental constraints like obstacles. The heuristics first divides up the terrain coarsely into a rectangular grid of subsections, and searches for a feasible trajectory from the given start point, assuming that the control input changes at most one time in every map segment. It builds a search tree using constrained depth-first search (i.e. the depth difference between the search tree leaves is below a specified constraint at all points) while satisfying all nonholonomic constraints. The terrain divisions are made finer in stages, i.e. control inputs are allowed to change more frequently, if it is necesary to find a solution. This approach finds feasible, but not optimal, trajectories as can be seen on Figure 8.

Figure 8: Example solution trajectory for a feasible nonholonomic motion planning problem in 2-D under presence of obstacles. Ref [2]

### **3.2 Trajectory Optimization Problems**

Some optimal trajectory planning problems have been discussed in [3]–[6]. [3] presents a detailed modeling of radar cross sections of unmanned aerial vehicles (UAV), hostile air defense systems involving RADARs and surface-to-air missiles (SAM), and aircraft controls. It then goes on to plan the motion and the trajectory of such a UAV that has to fly into an area under air defense coverage with known RADAR locations and go from one given point to another, while minimizing its probability of getting shot down. The UAV may have other "mission tasks" specified as a list of flyby points along with the times of arrival at those points. The algorithm characterizes the location and movement of the UAV on the map as either unthreatened or threatened, and tries to minimize the time spent under high threat.

[6] describes another military application where the task is to plan the motion of a UAV to follow a target while there are threats from known RADAR locations on the map. The proposed algorithm tries to keep the UAV within a defined proximity radius of the target as long as possible. Under some circumstances, e.g. in order to avoid some threat on the map, it may have to move so far away from the target that its sensors cannot track the target any more. In such cases it tries to estimate the trajectory of the target and tries to meet it at a point on this estimated trajectory in future. If the target remains undetected for a specified time-out, the UAV returns to base avoiding the threats. This involves an online alogirthm with dynamic inputs about the target's motion, as well as changes in the threat map.

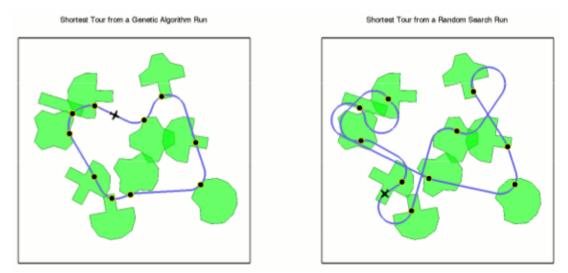

[4] presents another UAV motion planning problem, but now for reconnaissance missions without threat. It has to photograph some given targets in a terrain. Assuming that the UAV always flies on a plain at constant altitude, the areas on this plain from where various targets are photographable are polygons, as the terrain may hide the objects from specific locations. The algorithm proposes a way to find out the optimal trajectory to visit all the polygons and then come back to the initial point. This is a variant of the traveling salesman problem, called Polygon-Visiting Dubin's Traveling Salesman Problem, where the UAV has been modeled as Dubin's vehicle, i.e. a vehicle that only goes forward and turns left/right in an arc. An illustrative solution for such a problem, as computed by a genetic algorithm is shown below:

Figure 9: Example solution for finding the shortest trajectory of a Dubin's vehicle visiting all the green polygons and coming back to its source – as computed by a genetic algorithm. Ref [4].

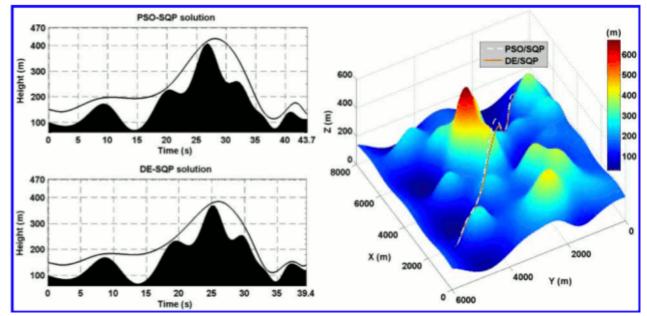

[5] discusses a general aircraft trajectory optimization problem, relevant to both military and civilian applications. It provides a detailed 6 degrees of freedom (DOF) aircraft motion model, viz. translation along the 3 Cartesian axes and rotations around them, with a 4-DOF control model: throttle (1-axis translation), and elevator, aileron and rudder providing control on the 3 rotation axes. It then determines a point to point trajectory on a given terrain to optimize one of the 3 parameters (or a linear combination of them): minimize time of flight, minimize energy expended in flight or maximize time within a given elevation over the terrain – the last one is motivated by requirements to avoid detection by RADAR. There may or may not be threats present on the map. Figure 10 presents two example solutions found for a purely time-optimization problem using this algorithm but two different optimization heuristics:

Figure 10: Example solution trajectories for a flight time optimization problem for an airplane flying over a 3-D terrain – using two different optimization heuristics – PSO-SQP and DE-SQP. Ref [5]

The algorithms in [3]–[5] can be regarded generally as composed of a system model, a formulation of the problem as a static motion optimization problem on a known map, and then executing the optimization. Different papers employ different optimization algorithms, e.g. [3] uses Matlab fminimax() function, [4] uses a genetic algorithm, and [5] uses a number of advanced optimization algorithms, e.g. Particle Swarm Optimization – Sequential Quadratic Programming (PSO-SQP) and Differential Evolution – Sequential Quadratic Programming (DE-SQP) combinations. [6] also involves the similar setup of modeling, stating the optimization problem and applying optimization. While modeling and problem statement is a design decision for all of these algorithms, the optimization has to be run for each problem configuration, and in case of [6] it has to be done online in real time in a possibly changing threat map. This means, it is crucial to accelerate the optimization process to make the implementation of these algorithms feasible. The optimization problems generally involve evaluating the cost or fitness of many different trajectories. Thus it is expected that it is useful to design a hardware accelerator that can parallelize and speed up this cost calculation, and the proposed hardware in the present work may indeed fill in this requirement.

# **3.3 Parallelization of Optimization Algorithms**

One key factor that influences the performance of such a hardware accelerator is the degree of parallelizability of the implemented optimization algorithm itself. Two well-known and widely used optimization algorithms are simulated annealing (SA) and genetic algorithms (GA), the latter one has in fact been used in [4]. In order to find out a practical application suitable for the hardware under development, the literature was surveyed to find out ways to parallelize these algorithms.

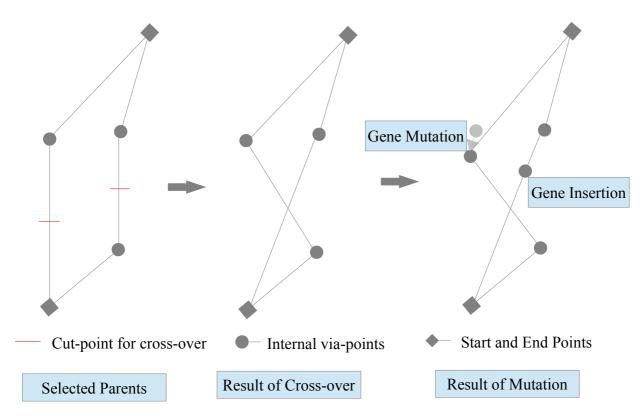

### 3.3.1 Genetic Algorithm

Genetic algorithm (GA) is an iterative optimization heuristic based on the principles of natural selection and biological evolution. In case of biological organisms, the principle of natural selection states that in each generation, the fitter individuals have higher reproductive success and pass on their genes, and thus tend to produce a fitter next generation, where the fitness is evaluated with respect to the environment the population lives in. Thus, it is expected that after the elapse of an appropriate number of generations, the population contains individuals very close to the fittest possible organisms for that particular ecological environment. In terms of the general optimization problem, the fitness to the environment is emulated by a fitness function of a candidate solution, which acts as the analogue of an individual organism. Just like in the case of the biological population, the evolution progresses by deriving new generations of a population of candidate solutions. Each solution is encoded as a "chromosome" containing multiple "genes". The reproductive success of the organisms is paralleled by a "parent selection strategy", and sexual reproduction is imitated by a cross-over operation, akin to the same phenomenon in biological meiosis cell division, that generates the gametes, the basic cells involved in sexual reproduction. In more concrete terms, in genetic algorithm, the cross-over is applied on two "parent" chromosomes to derive two "child" chromosomes by exchanging some genes between the two parent chromosomes. Biological mutation may also be emulated in the GA by inducing small perturbations in the chromosome structure. The algorithm can also incorporate other optional operations.

[7] provides a general survey of various parallel GA implementations. It divides them into 3 main groups:

1. **Single population master-slave:** A "master" process maintains the population of solutions globally and perform the genetic operations on them, e.g. cross-over and mutation. However, the evaluation of the fitness of different solutions is distributed over multiple parallel processes.

- 2. Single population fine grained: There is a global population, but each process treats only one (or a small number of) individual solutions, and there is no global master. The individuals are assumed to be connected with each other through a topology in a connected graph usually same as the connection topology of the parallel computer, that the computation is running on. Parent selection and cross-over are localized, i.e. each process can only interact with its neighbours.

- 3. **Multiple population coarse grained:** In this approach, each process treats a separate population, and applies GA on it independently to evolve it. Only occasionally, some individuals "migrate" between the processes allowing exchange of information among them.

It can be observed that if an application is developed that uses GA to optimize 2-D trajectories, then the hardware structure proposed in Chapters 1 and 2 can be used to accelerate any of these parallelization approaches, as long as the hardware is used only to accelerate the computation of the fitness of the candidate solutions.

#### **3.3.2 Simulated Annealing**

Simulated annealing is another popular iterative optimization heuristics, based on the physical phenomenon of annealing in metals. This involves heating the material to a temperature above a critical temperature and then cooling it slowly so that the crystal structure inside always remains at thermal equilibrium. When the metal is thus brought to room temperature, its crystal structure assumes the lowest possible energy state, being the most regular possible, avoiding internal stress and lattice defects. This process is paralleled in the domain of general optimization algorithms by drawing an analogue of the general solution quality function to the physical energy function, and by defining a gradually diminishing temperature at each iteration which determines the degree of acceptable "disorder" in the solution. In each iteration, the present solution is slightly perturbed and its energy-function is evaluated. This is accepted as the new solution if it has a lower energy than the previous solution. Even if its energy is higher, it may still be accepted probabilistically, depending on the exact amount of energy increase and the iteration-temperature (i.e. acceptable degree of disorder). Smaller increases have higher probability of being accepted if the iteration temperature remains fixed, and higher iteration temperature allows higher probability of acceptance when the energy-increase is same. The basic algorithm is completely specified by defining an energy function, a cooling schedule and an acceptance criterion. The last is often defined as an exponential function producing the probability of acceptance (PA) of a new solution as

$PA = 1 \quad if M > 1$ = M otherwise where  $M = e^{(-\Delta E/T)}$  $\Delta E = Increment of energy$ T = Iteration temperature

[8] discusses some strategies to parallelize simulated annealing (SA). This paper proposes the following approaches:

- 1. **Asynchronous (AS):** This is parallelization of the multi-start approach, i.e. independent runs of the SA algorithm with different random initial solutions are executed in parallel by multiple processes, and the best solution is chosen at the end.

- 2. Synchronous with occasional solution exchange (SOS): Similar to AS, but after some specified number of iterations, all the solutions are gathered by a master process, and some genetic operations (e.g. cross-over) and selection are applied on them to form a new solution population, and SA is again applied on them in a distributed manner for the specified

number of iterations, before gathering the population in the master again and repeating the process. The annealing temperature is globally managed at each synchronization at the master. This approach is a combination of SA and GA.

- 3. Synchronous with occasional enforcement of best solution fixed interval (SOEB-F): In this approach, all processes start with the same random initial solution and temperature. Like in SOS, all the results are gathered by a master after a specified number of iterations in each process, and then the best solution from the population is chosen for further SA iterations to be done parallelly on the distributed processes. The temperature is controlled globally at each synchronization step, like in SOS.

- 4. Synchronous with occasional enforcement of best solution varying interval (SOEB-V): Like SOEB-F, all processes start with the same initial condition and temperature, and apply the SA algorithm independently. However, each process controls its own annealing temperature, and communicates its result to the master when a specified temperature reduction has been achieved. When the master has received results from all parallel processes, it chooses the best one from them and broadcasts it to all processes for further processing till all of them reach the next temperature target. The process is repeated. In this process, all the processes are synchronized when they are at the same temperature.

- 5. **Highly coupled synchronous approach (HCS):** All processes start with the same random initial solution and the same temperature. The results are reported back to the master after each iteration in each process. Additionally, each process is allowed to perturb only one axis/variable of the solution in each iteration. The master then chooses the best solution after perturbation, and integrates other less performing perturbations into it as long as that improves the solution. Then, each process receives this composite solution and gets an axis/variable specified, on which to perform the perturbation in the next iteration. This approach has a very high communication overhead on a traditional parallel computer.

- 6. **Modified highly coupled synchronous approach (MHCS):** In order to reduce the communication overhead in HCS, the synchronization/merging of solutions is performed only at an interval of a specified number of iterations, yielding the MHCS algorithm.

These methods are then benchmarked in [8] with respect to a standard suit of test functions. MHCS was found to be the best performing in terms of speed and quality of result for most kinds of problems. AS was found to be the usually the worst performing.

[9] proposed two parallel SA implementations. The first of them, viz. "Clustering algorithm" is in essence same as the SOEB-F from [8], except that the initial solutions for the different processes are different. The second algorithm is called "Genetic clustering algorithm", and it uses a genetic algorithm to find a population of good solutions, which are then used as the initial solution for the "clustering algorithm" mentioned above.

[10] is a highly theoretical paper that explores the Markov process based optimization heuristics, e.g. SA and GA, and explores their relationships. It proposes a "Parallel simulated annealing" algorithm by performing the perturbations in parallel and then choosing the best among them using an acceptance probability. This seems similar to SOEB algorithms from [8], assuming that the synchronization is performed after every iteration. The paper then introduces the "Massively parallel simulated annealing". This is exactly same as the AS algorithm from [8]. This algorithm is then extended by defining a "parallel neighbourhood model", where the processes are assumed to be connected to each other in a defined topology in a connected graph like in the case of "single population fine grained" parallel GA described in [7]. A "parallel neighborhood algorithm" has been defined on this topology that allows interaction between the neighboring processes, just like in the corresponding GA schemes, allowing improvement of the solution population as a whole.

# **3.4 Different Implementation Options**

The parallel algorithms described in [7] - [10] have been discussed for shared or distributed memory processors. When these approaches are applied to solve the trajectory planning problems, as described in [3] - [6], some challenges are faced. Because a realistic map of, e.g. terrain elevation, threat location, etc. is difficult to store in a compact representation (e.g. as analytical functions), these data are in general memory intensive. This leads to the following challenges in different parallelization approaches:

- 1. **Shared memory:** In case of parallel shared memory processors (e.g. GPU using global memory), though the map data may be shared, because of the parallel execution of different processes dealing with different trajectories, a lot of memory access conflicts are generated. This leads to memory bandwidth bottleneck.

- 2. **Distributed memory:** In this case, two different approaches can be taken:

- (a) **Data duplication:** In this approach the map data is duplicated in the locally accessible memory of each processor. However, this is expected to be quite expensive in terms of memory requirements.

- (b) **Data fragmentation:** In this approach, the map data is divided up into smaller fragments, each of which is stored in a small memory, local to a processor. Then the cost calculation for each trajectory can be accomplished by communicating between these processors, each computing the cost of its local part of the trajectory. This, however, assumes that the overall cost of a trajectory can be determined by (linear or some other analytical) combination of the costs of the individual trajectory segments. This way, only one copy of the map data is needed to be stored, and because it is distributed in many memories, there is no memory bandwidth limitations either. However, this improvement comes at an increased cost of communication between the processors, which is expected to be acceptable as all communications take place between neighbors.

It is apparent that the data duplication approach may be suitable for distributed systems with lot of memory but relatively slow communication, e.g. computing clusters. The data fragmentation approach would be more suitable for systems with low amount of memory, but relatively faster communication, e.g. a network-on-chip connecting an array of on-chip processor cores.

As explained above, all three approaches have their own advantages and disadvantages. For the offline optimization problems described in [3] - [5], probably any of these three parallelization techniques can be applied. The on-line optimization problem, discussed in [6], however, probably needs an energy-efficient low-memory on-chip solution, e.g. a GPU-based (shared memory) or a NoC-based (fragmented distributed memory) solution. The present work aims to realize this last solution: a NoC-based "fragmented" distributed memory system for parallelization of these trajectory optimization problems.

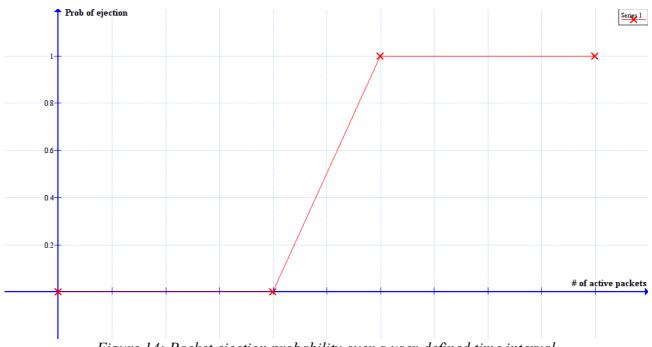

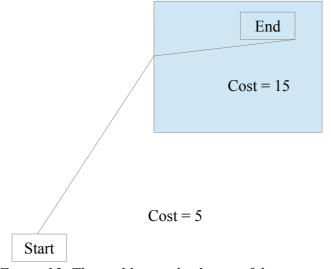

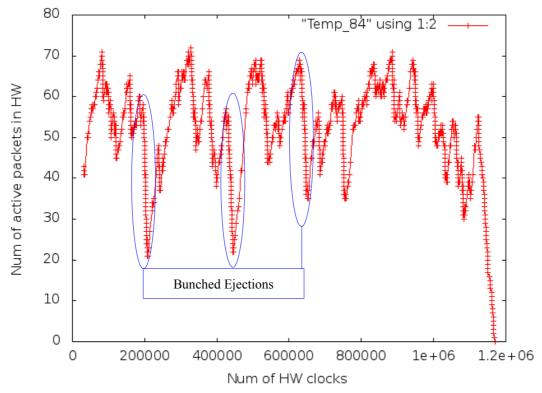

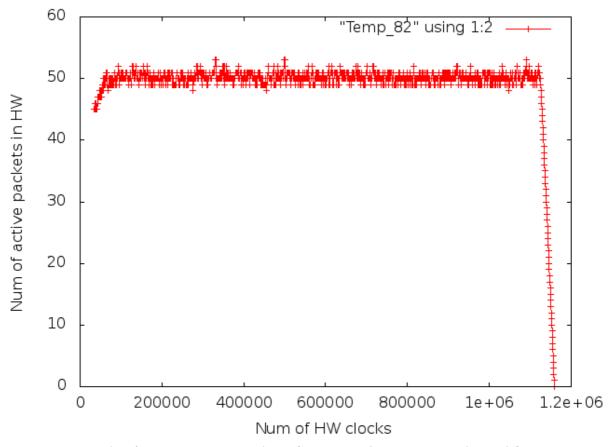

# **3.5** Conclusion