# Fine-Grained ASIP Power Gating

Gate-level study of the break-even point for fine-grained power gating

Anja Niedermeier

Master of Science in ElectronicsSubmission date:September 2009Supervisor:Kjetil Svarstad, IETCo-supervisor:Frank Bouwens, IMEC-NL

Norwegian University of Science and Technology Department of Electronics and Telecommunications

## **Problem Description**

In a not too distant future, millions of tiny, invisible, self-sufficient, and communicating wireless sensors will assist our daily lives and improve the quality of life. Such wireless sensor nodes (WSN) consist out of components such as a radio for communication, sensors, and a processor for on-node processing of the data. The WSNs use scavenged energy harvested from the environment to avoid dependency of a depleting battery. The scavenged energy, however, is neither high nor continuous and requires that the aforementioned components are highly optimized for low energy consumption.

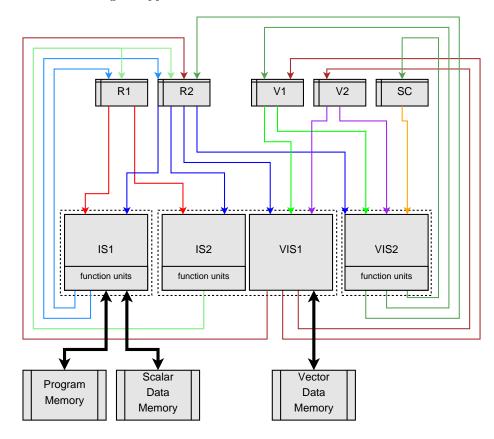

The application specific instruction set processors (ASIP) developed at Holst Centre / IMEC-NL are targeting high processing power (> 100MIPS) with a minimum amount of power (under 100uW) in the domains of biomedical and wireless communication. This requires high optimizations for both dynamic and static power. The ASIPs consist out application specific issue slots, function units, register files and/ or memories, which remain unused for other algorithms. Since leakage becomes significant if not dominant with the upcoming technologies, it is desirable to switch off unused resources at a fine-grained level.

The purpose of this thesis is to optimize a wireless communication processor for energy consumption without loss of performance by using power shut-off techniques applied to the data path of the processor. The ultra wide band processor is available as a reference generated with Target® and TSMC 90nm technology. Based on preliminary findings of simulations the processor will be optimized for energy wherever possible using fine-grained hardware techniques supported by software.

Specific tasks which are to be performed during this assignment include a detailed research of methods for power-off techniques; the results are analyzed and compared in terms of a multiissue VLIW-processor. Based on these findings, a power-off scheme is proposed and implemented on the architectural level. Finally, the scheme is analyzed and qualified to determine the realistic power consumption benefit for the system.

Assignment given: 09. March 2009 Supervisor: Kjetil Svarstad, IET

#### Abstract

Power consumption in portable electronic devices is a crucial design factor. While technology at 90 nm and above is still dominated by dynamic power, it is expected that leakage power will gain importance in sub-90 nm technologies. One commonly used technique to reduce leakage power is power gating, which is still an active research topic, especially on the fine-grained level.

The purpose of this thesis was to explore the impact of fine-grained power gating on the datapath of a VLIW processor. Also, a detailed analysis of the savings versus introduced overhead was performed to derive a generic formula for a quick estimation of the energy efficiency of power gating.

During the work, a work-flow to partition the system into power domains was developed. Furthermore, a verification method was implemented that validates whether a power gated resource is scheduled by the compiler or not. A configurable HSPICE simulation flow was implemented to determine how many power switches were required for a specific power domain as well as the energy consumption to switch a power domain on.

Two processors with different usage profiles, designed with the help of different tools, were investigated in this thesis. The processors were modified to support power gating, and, furthermore, a synchronous power manager was developed. After RTL-level verification of functional correctness, the resulting systems were synthesised and placed and routed for 100 Mhz with two different 90nm TSMC libraries (low power and general purpose) to evaluate the variation between different technology flavours. The results showed, that a large contributor to the energy overhead of power gating is the dynamic power of additionally required modules, e.g., the isolation cells at the output of a power domain and the power manager. Also it was proven that the power domains need a very low duty cycle in order to apply power gating efficiently.

It has been shown that the energy overhead for fine-grained power gating is significant and it is mainly caused by additional modules that have to be added to the system. Therefore, power gating can only be beneficial on designs with sufficient large power domains with a low duty cycle. However, it must be said that power is mainly consumed by the memories. Also, for 90 nm, leakage power is a rather small fraction of the total power consumption. The possible overall savings when focussing on the datapath are therefore very limited.

### Preface

Writing my Master Thesis in IMEC-NL was a great experience. I received very helpful support and guidance during my work and I also learned a lot about processor desing and low-power techniques. First of all, I would like to thank Frank Bouwens, who was my daily supervisor and a great guide through my thesis. Also he was very supportive in technical matters as well as he helped me organising the structure of my thesis. I also received great help from Jos Hulzink for the implementation of power gating in the processors itself. He also tought me a lot about ASIP design in general. A special thanks I want to give to Michael De Nil, who always helped me when I had problems with synthesis or place and route. Also, he always managed to give me new motivation when I was despairing of the tools. Also Ben Busze I would like to thank for his help with synthesis and place and route. For the circuit-level related topics I was involved in I received great help of Yu Pu, who showed me how to determine the power-on energy, and from Maryam Ashouei who helped me with question related to SPICE as well as with an estimation how many switches I needed. I would also like to thank Filipa Duarte for her help regarding academic writing. Finally, I would like to thank Jos Huisken and my professor Kjetil Svarstad for their guidance and support throughout my thesis.

After finishing my Thesis, I was encouraged to write a paper about my work. This paper was submitted to the Design, Automation, and Test in Europe (DATE) conference 2010. It can be found in the electronic appendix (filename article.pdf).

# Contents

| 1        |                   | roduction                                                     | 1               |

|----------|-------------------|---------------------------------------------------------------|-----------------|

|          | 1.1               | Related work                                                  | 1               |

|          | 1.2               | Approach, contribution of this work                           | 2               |

|          | 1.3               | Document structure                                            | 3               |

| <b>2</b> | Bac               | kground                                                       | 4               |

|          | 2.1               | Power consumption in CMOS                                     | 4               |

|          |                   | 2.1.1 Dynamic power consumption                               | 5               |

|          |                   | 2.1.2 Leakage power consumption                               | 5               |

|          | 2.2               | Power gating                                                  | 6               |

|          |                   | 2.2.1 Power domain                                            | 6               |

|          |                   | 2.2.2 Power switch                                            | 7               |

|          |                   | 2.2.3 Isolation                                               | 8               |

|          |                   | 2.2.4 State retention and restoration                         | 10              |

|          |                   | 2.2.5 Power manager                                           | 11              |

|          | 2.3               | Power aware compilation                                       | 11              |

|          |                   | 2.3.1 Method one: Post-processing                             | 12              |

|          |                   | 2.3.2 Method two: Smart scheduling                            | 13              |

| 3        | Ana               | lysis of the break-even point                                 | 15              |

| Ŭ        | 3.1               | Power profile of a power gated system                         | 15              |

|          | 3.2               | Energy consumption in the different states                    | 16              |

|          | 3.3               | Energy savings                                                | 17              |

|          | 3.4               | Energy overhead                                               | 18              |

|          | 3.5               | Derivation of the break-even point                            | 19              |

|          | 3.6               | Absolute energy savings                                       | 20              |

|          | 3.7               | Example for a power gating scheme                             | 20<br>21        |

| 4        | Ъ                 | 1 J-1                                                         | 23              |

| 4        | 4.1               | t <b>hodology</b><br>Tools used in this work                  | <b>23</b><br>24 |

|          | $\frac{4.1}{4.2}$ | Determination of power consumption values                     | $\frac{24}{24}$ |

|          | $\frac{4.2}{4.3}$ | · ·                                                           | 24<br>26        |

|          |                   | Resource utilisation over time                                |                 |

|          | 4.4               | Partitioning into Power Domains                               | 26              |

|          | 4.5               | Determination if state retention is required                  | 27              |

|          | 4.6               | Number of required switches                                   | 27              |

|          | 4.7               | Implementation of power gating                                | 29              |

|          | 4.8               | Verification that the system still works functionally correct | 30              |

|          | 4.9               | Evaluate energy savings                                       | 31              |

|    |            | 4.9.1Power-on /-off energy                                                                                             | $\frac{33}{36}$ |

|----|------------|------------------------------------------------------------------------------------------------------------------------|-----------------|

| -  | Ŧ          |                                                                                                                        |                 |

| 5  | -          | blementation of Power Gating                                                                                           | <b>38</b>       |

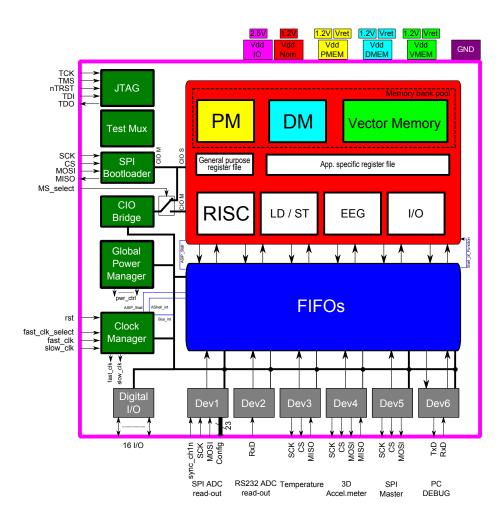

|    | 5.1        | Architecture description                                                                                               | $\frac{38}{38}$ |

|    |            | 5.1.1 Ultra wide band processor                                                                                        |                 |

|    | ۲ŋ         | 5.1.2 Biomedical DSP                                                                                                   | 40              |

|    | 5.2        | Partitioning into power domains                                                                                        | 41              |

|    |            | 5.2.1 UWB processor                                                                                                    | 42              |

|    | <b>۲</b> . | 5.2.2 Biomedical DSP                                                                                                   | 45              |

|    | 5.3        | Proposed power gating topology 1: HW based power manager                                                               | 47              |

|    |            | 5.3.1 HW implementation                                                                                                | 47              |

|    |            | 5.3.2 SW implementation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                 | 52              |

|    | 5.4        | Proposed power gating topology 2: SW based power manager                                                               | 55              |

|    |            | 5.4.1 Implementation on the UWB processor                                                                              | 55              |

|    |            | 5.4.2 Implementation on the Biomedical DSP                                                                             | 57              |

|    | 5.5        | CPF Flow                                                                                                               | 59              |

|    | ъ          |                                                                                                                        |                 |

| 6  |            | ults                                                                                                                   | 61              |

|    | 6.1        | UWB processor                                                                                                          | 61              |

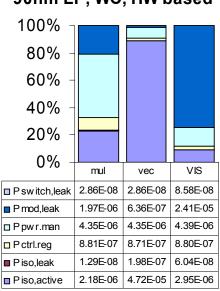

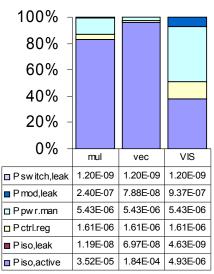

|    |            | 6.1.1 HW based power manager                                                                                           | 62              |

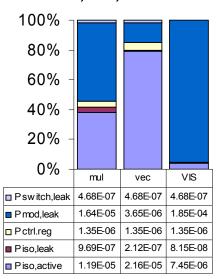

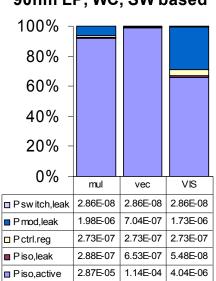

|    |            | 6.1.2 SW based power manager                                                                                           | 65              |

|    | 6.2        | Biomedical DSP                                                                                                         | 68              |

|    | 6.3        | Results from the spice simulations                                                                                     | 69              |

|    | 6.4        | Results for the break-even point                                                                                       | 70              |

|    | 6.5        | Detailed analysis of the break-even point for selected cases $% \mathcal{A} = \mathcal{A} = \mathcal{A} = \mathcal{A}$ | 71              |

|    | 6.6        | Absolute energy savings                                                                                                | 73              |

| 7  | Dis        | cussion                                                                                                                | 75              |

|    | 7.1        | UWB processor                                                                                                          | 75              |

|    |            | 7.1.1 HW based power manager                                                                                           | 75              |

|    |            | 7.1.2 SW based power manager                                                                                           | 78              |

|    | 7.2        | Biomedical DSP                                                                                                         | 79              |

|    | 7.3        | Results from the spice simulations                                                                                     | 80              |

|    | 7.4        | Comparison of the detailed versus the simplified formula for the                                                       | 00              |

|    | 1.1        | break-even point                                                                                                       | 81              |

|    | 7.5        | General analysis of the overhead                                                                                       | 81              |

|    | 1.0        | General analysis of the overhead                                                                                       | 01              |

| 8  | Fut        | ure work                                                                                                               | 83              |

| 9  | Cor        | nclusion                                                                                                               | 84              |

| Bi | ibliog     | graphy                                                                                                                 | 85              |

# List of Figures

| 2.1  | General power gating scheme                                                                      | 7   |

|------|--------------------------------------------------------------------------------------------------|-----|

| 2.2  | Header switch                                                                                    | 7   |

| 2.3  | Footer switch                                                                                    | 8   |

| 2.4  | Principle of an and-isolation cell                                                               | 9   |

| 2.5  | Principle of an or-isolation cell                                                                | 9   |

| 2.6  | State retention register                                                                         | 11  |

| 2.7  | Control sequence for a design without state retention                                            | 11  |

| 2.8  | Control sequence for a design with state retention                                               | 12  |

| 3.1  | Power dissipation of a non power-gated system                                                    | 16  |

| 3.2  | Power dissipation of a power gated system                                                        | 16  |

| 3.3  | Illustration of the absolute energy savings                                                      | 21  |

| 3.4  | Example of a power gated module where power gating makes sense                                   | 22  |

| 3.5  | Example of a power gated module where power gating does not                                      |     |

|      | makes sense                                                                                      | 22  |

| 4.1  | General power gating design flow                                                                 | 23  |

| 4.2  | Flow for the extraction of the power numbers                                                     | 25  |

| 4.3  | Flow for the determination of the resource usage over time                                       | 27  |

| 4.4  | Equivalent circuit for determination of required number of switches                              | 28  |

| 4.5  | Design implementation flow                                                                       | 30  |

| 4.6  | Flow for the verification that a resource is not used while it is                                |     |

|      | switched off                                                                                     | 32  |

| 4.7  | Spice model of the circuit                                                                       | 33  |

| 4.8  | Schmeatic of the power switch                                                                    | 34  |

| 4.9  | Spice model of the power gated block with a net of switches                                      | 35  |

| 4.10 | Spice simulation flow                                                                            | 35  |

| 5.1  | Overview of the UWB processor                                                                    | 39  |

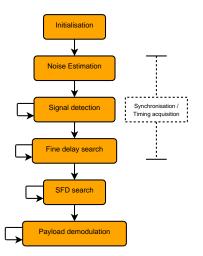

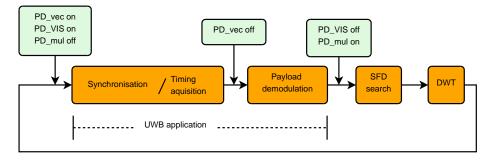

| 5.2  | States of the UWB application                                                                    | 40  |

| 5.3  | Biomedical DSP overview                                                                          | 41  |

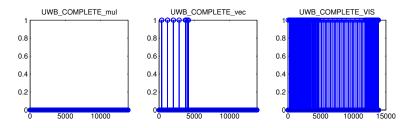

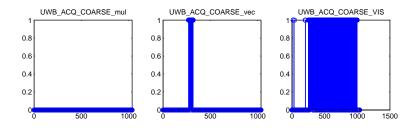

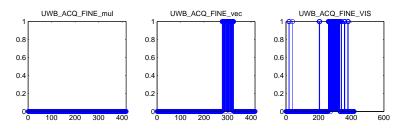

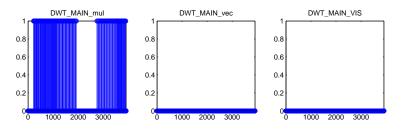

| 5.4  | Resource utilisation of the power domains during complete UWB algorithm                          | 42  |

| 5.5  | Resource utilisation of the power domains during signal detection                                | 44  |

| 0.0  | in UWB application                                                                               | 43  |

| 5.6  | Resource utilisation of the power domains during fine delay com-<br>pensation in UWB application | 43  |

| 5.7  | Resource utilisation of the power domains during complete DWT                                    | 10  |

| J. I | algorithm                                                                                        | 43  |

|      | 0                                                                                                | - 5 |

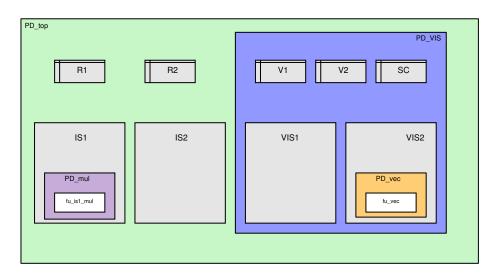

| 5.8 Power Domains in the UWB processor               | 44 |

|------------------------------------------------------|----|

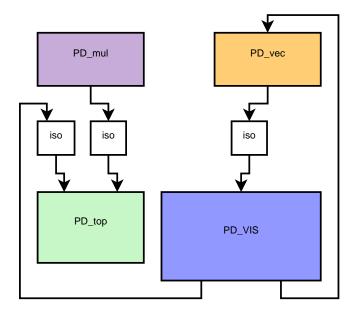

| 5.9 Isolation scheme for the UWB processor           | 45 |

| 5.10 Possible power off scheme for the UWB processor | 45 |

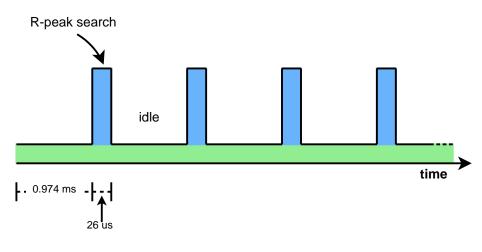

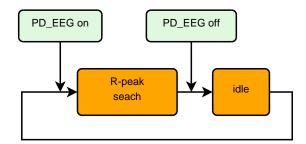

| 5.11 EEG algorithm                                   | 46 |

| 5.12 EEG power off scheme                            | 46 |

|                                                      | 47 |

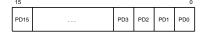

| 5.14 Power Gating Control Register                   | 48 |

| 5.15 Block diagram of power gating control unit      | 52 |

|                                                      | 53 |

|                                                      | 55 |

|                                                      |    |

|                                                      | 62 |

|                                                      | 63 |

|                                                      | 64 |

| 6.4 Results for G, WC, SW in [J]                     | 65 |

|                                                      | 66 |

|                                                      | 67 |

|                                                      | 68 |

|                                                      | 71 |

|                                                      | 72 |

|                                                      | 72 |

|                                                      | 72 |

|                                                      | 73 |

# List of Tables

| 2.1 | Truth table of an and-isolation cell                               | 9  |

|-----|--------------------------------------------------------------------|----|

| 2.2 | Truth table of an or-isolation cell                                | 9  |

| 5.1 | Power domains in the UWB processor                                 | 44 |

| 5.2 | Bit configuration for the control register                         | 56 |

| 6.1 | Results of the spice simulations                                   | 69 |

| 6.2 | Results of the break-even point of the UWB processor               | 70 |

| 6.3 | Results of the break-even point of the biomedical DSP              | 70 |

| 6.4 | Results for the possible absolute energy savings in the biomedical |    |

|     | DSP                                                                | 74 |

# List of Abbreviations

| ALU                    | Arithmetic Logic Unit                          |  |  |

|------------------------|------------------------------------------------|--|--|

| ASAP                   | As Soon As Possible                            |  |  |

| ASIP                   | Application Specific Instruction set Processor |  |  |

| CPF                    | Common Power Format                            |  |  |

| CPU                    | Central Processing Unit                        |  |  |

| DFVS                   | Dynamic Frequency and Voltage Scaling          |  |  |

| DSP                    | Digital Signal Processor                       |  |  |

| DWT                    | 0 0                                            |  |  |

| ECG                    | ${ m Electrocardiogram}$                       |  |  |

| EEG                    | Electroencephalogram                           |  |  |

| G                      | General purpose                                |  |  |

| GIDL                   | Gate Induced Drain Leakage                     |  |  |

| HDL                    | Hardware Description Language                  |  |  |

| $\mathbf{H}\mathbf{W}$ | HardWare                                       |  |  |

| I/O                    | $\operatorname{Input}/\operatorname{Output}$   |  |  |

| ILP                    | Instruction Level Parallelism                  |  |  |

| IP                     | Intellectual Property                          |  |  |

| IPC                    | Instructions issued Per Cycle                  |  |  |

| $\mathbf{LP}$          | Low Power                                      |  |  |

| $\mathbf{MAC}$         | Multiply ACcumulate                            |  |  |

| $\mathbf{MLV}$         | Minimum Leakage Vector                         |  |  |

| P&R                    | Place and Route                                |  |  |

| PD                     | Power Domain                                   |  |  |

| $\mathbf{RBB}$         | Reverse Body Biasing                           |  |  |

| RISC                   | Reduced Instruction Set Computer               |  |  |

| $\mathbf{RTL}$         | Register Transfer Level                        |  |  |

| $\mathbf{SDF}$         | Standard Delay Format                          |  |  |

| $\mathbf{SFD}$         | Start Frame Delimiter                          |  |  |

| $\mathbf{SR}$          | State Retention                                |  |  |

| $\mathbf{SW}$          | $\operatorname{SoftWare}$                      |  |  |

| $\mathbf{TC}$          | Typical Case                                   |  |  |

| TSMC                   | Taiwan Semiconductor Manufacturing Company     |  |  |

| VCD                    | Value Change Dump                              |  |  |

| $\mathbf{VHDL}$        | Very high speed integrated circuits HDL        |  |  |

| VLIW                   | Very Long Instruction Word                     |  |  |

| WC                     | Worst Case                                     |  |  |

### Chapter 1

### Introduction

Due to downscaling of technology, portable embedded systems have gained increasing popularity. Besides multimedia applications, like mobile music or gaming devices, a promising field of application is in the medical sector [1], [2]. As these systems usually are battery-powered or even use energy scavenging [3], optimisation of power consumption is crucial in order to meet the strict energy constraints.

While power consumption was historically dominated by dynamic switching power, leakage power consumption has gained more and more impact in both absolute numbers [4] as well as in power consumption per area [5] in the sub-90 nm technologies. One promising method to save leakage power is power gating [6, ch. 4], [7, ch. 10], i.e. shutting off unused blocks while they are not used.

Power gating is nowadays a commonly used technique for power management on system level [8] [9], i.e. switching off complete components of a chip like a processor or memory banks. However, it is still an active research topic on a more fine grained level like on the datapath of a processor.

#### 1.1 Related work

In [10], an exploration of the potential of power gating applied on the level of execution units in the datapath is performed. Also, an analytical equation for the break-even point is derived. For the estimation, the authors use a state-of-the-art superscalar processor model which they calibrate against a pre-RTL processor model. In their analysis for the break-even point they assume the power consumed by the switch to be the only source of the energy overhead. They conclude that for an idle period of 10 cycles, power gating can bring benefits.

The authors of [4] also perform an analysis of the break-even point for power gating. They include, besides the power switch, also additionally required decap area in their model. They conclude that the overhead which is caused by additional dynamic power consumed by the switch and the additional decap is too high for 130 nm technology, but they assume that for future technology it will bring benefits.

In [11], an implementation methodology for power gating and an analysis of the overhead are presented. The authors base their methodology on exploiting existing clock-gating control signals which they assume to be present in the design. Based on the clock-gating domains, they provide an algorithm to partition the system automatically into power domains. Also the control signals for power gating are derived from the clock-gating control. In their analysis of the overhead, they only consider the power switch. They applied their methodology on a 32-bit RISC embedded CPU and performed synthesis and place and route (P&R). Afterwards they performed power analysis by using Toshiba 90nm device models. They conclude that significant amounts of leakage power can be saved at a reasonable area penalty.

In [12], a more detailed analysis of power gating than in the previous papers is presented. The authors base their trade-off analysis on five factors, namely performance degradation, sleep transistor size, leakage power savings, power mode transition time and power mode transition energy. They implement a power gated design with 65 nm STMicroelectronics technology and present power numbers extracted after place and route. They conclude that they can achieve up to 75 % leakage power savings.

All of the previously presented publications have in common that they do not consider the energy consumed by the isolation cells at the boundary of a power domain. Neither, any statements are given regarding the energy consumption of additional modules, like a power manager.

#### 1.2 Approach, contribution of this work

The hypothesis of this work is that applying power gating in the datapath of a processor can lead to energy savings. Also, it is expected that the overhead of power gating is not only determined by the energy to switch a power domain on, like concluded in previous publications on power gating, but also by additionally required modules like isolation cells.

The purpose of this thesis is therefore an exploration of the impact of power gating in the data path of a processor. Henceforth, a detailed analysis of the break-even point of power gating is derived to evaluate if power gating could bring benefits. Furthermore, a method to partition a processor into power domains, followed by the implementation and evaluation of power gating is proposed. Finally, an analysis of the main challenges of fine grained power gating in the datapath is given. The analysis was based on power figures obtained from a post-P&R netlist for 90 nm TSMC.

The procedure for implementing power gating was as follows: After a careful analysis of the power consumption of the blocks in the datapath and their duty cycle, the system is partitioned into power domains. In order to determine both the powering-on time and energy, spice simulations are performed. Further spice simulations were performed to identify the number of required power switches. Following, power gating was integrated into the design using the Common Power Format (CPF) [13]. The resulting system was synthesised and placed and routed using the Cadence Design Tools [14]. Afterwards, the power consumption was analysed using PrimeTime from Synopsis [15]. The obtained power numbers were used for the final analysis to determine whether energy could be saved by using power gating.

#### **1.3** Document structure

The remainder of this report is structured as follows: In chapter 2, the background for power consumption in CMOS circuits is described including a brief overview of power saving techniques. Then, in chapter 3 a detailed analysis of the benefits and costs of power gating is performed. In chapter 4, the methodology which is used in this work is explained. In chapter 5, the implementation of power gating is described. The results are presented in chapter 6, followed by a discussion in chapter 7. A short overview of possible future work is given in chapter 8. Finally, the conclusions are drawn in chapter 9.

### Chapter 2

### Background

In this chapter, the background theory of this work is explained. First, an introduction to the different sources of power dissipation in CMOS circuits, including a brief overview of power reduction techniques, is given in section 2.1. As power gating is primarily used in this work, the principles of power gating are explained in section 2.2. Finally in section 2.3, an overview of leakage power aware compliation techniques is given.

#### 2.1 Power consumption in CMOS

The average power dissipation in CMOS devices  $(P_{avg})$  can be described by the following equation [16], [17]:

$$P_{avg} = P_{short} + P_{dynamic} + P_{leak} = \frac{\beta}{12} \cdot (V_{dd} - 2V_T)^3 \cdot \frac{\tau}{T} + \alpha C_L V_{dd}^2 f + I_{leak} V_{dd}$$

(2.1)

$P_{short}$  is caused by short circuit currents that occur when both the NMOS and PMOS transistor in a CMOS cell are in their conductive state for a short time during transitions.  $\beta$  is the gain factor of a MOS transistor,  $V_T$  is the threshold voltage,  $\tau$  is the rise or fall time of a signal, T is the period time of a signal and  $V_{dd}$  is the supply voltage [18].

$P_{dynamic}$  represents the dynamic power due to switching activity in the circuit. It is determined by the node transition factor  $\alpha$ , the load capacitance  $C_L$ , the clock frequency f and  $V_{dd}$ .

$P_{leak}$  represents the leakage power consumption and is a product of the leakage current  $I_{leakage}$  and  $V_{dd}$ .

#### 2.1.1 Dynamic power consumption

Dynamic power is caused by charging and discharging of node capacitances in the design. To minimise dynamic power consumption, several techniques are available. In the following, an overview of the most common techniques is given.

One approach is dynamic frequency and voltage scaling (DFVS). The principle is to lower the voltage and/ or frequency of a design to a level that the circuit just remains functional and reaches its timing constraints ([7], [19, ch. 4]). This is also supported by several application compilers, like presented in [20], [21] or [22].

Another technique is *clock gating*, which is applied to idle blocks of the design ([6, ch. 2], [23]. In order to reduce switching power dissipation caused by the clock, which can be up to 50 percent of the total power consumption, the clock is turned off for blocks that are not performing any useful task.

Usually, several modules share a common input source, typically a register or a memory. When the inputs of a module are changing, but the output is not needed, it is performing redundant computation during which dynamic power is consumed. In order to prevent that, the inputs of a module can be isolated using *operand isolation* [24].

Minimising the switching capacitance is another method. Hereby the switching activity or the capacitive load is reduced by several optimisation techniques, like described in for example [19, ch. 7] or [25].

Besides the mentioned methods, there are further optimisation techniques, a good summary can be found in [26] and [27]. Several methods which focus on software optimisation techniques for low power are presented in [28].

#### 2.1.2 Leakage power consumption

According to [16], there are five major sources of leakage current, namely subthreshold current, gate leakage, pn-junction leakage, Gate Induced Drain Leakage (GIDL) and Punchthrough. Of those, leakage due to subthreshold current, which is flowing between the source and the drain when the transistor is in the subthreshold region (i.e. when the gate voltage is below the threshold voltage), has the highest impact. This current is also strongly depending on the temperature the circuit is operating at, it increases with higher temperatures [29]. A detailed analysis of leakage power can also be found in [30], [31] and [32].

While the total power consumption was historically dominated by dynamic power, leakage power gains more and more impact in sub-90nm designs [5]. Therefore, optimisation methods that focus on leakage power minimisation become of increasing interest in addition to methods for minimisation of dynamic power dissipation.

One method to reduce leakage power is *reverse body biasing (RBB)*, as explained for example in [7], [30] and [33]. The principle is to apply a deep reverse body bias during standby to increase the threshold voltage and thus force the transistor into the off region to reduce subthreshold leakage. Leakage power consumption of a gate is depending on its input vector [34]. Another method to minimise the leakage power when a module is idle, is called *minimum leakage vector (MLV)*. The principle is to shift the input vector which causes the least leakage current into the module whenever it is idle. A method to determine the MLV for a given combinational logic, including a short review of related methods, is presented in [35].

A popular technique for leakage power reduction is *power gating*, also called *power shut-off*. In the remainder of this report, the term *power gating* will be used. The basic principle of this method is to disconnect idle blocks from the supply voltage, as described in more detailed in the next section.

#### 2.2 Power gating

Power gating relies on switching off idle blocks in the design, thus saving leakage power. A very good overview can be found in [6] and [7].

There are two basic design approaches for power gating ([7, ch. 10.3.4.1]). One is the coarse-grained approach, in which complete blocks are switched off. An illustrating example for a system with coarse grained power gating could be a wireless sensor node ([36]) which consists of a microprocessor, a sensor and a radio. Power gating could be applied to the radio whenever no communication is needed. Or, the sensor is powered down as long as data is transmitted.

The other approach is fine-grained power gating, where individual modules within a block can be switched off while keeping other modules switched on at the same time. Fine-grained power gating could be applied to a processor with several dedicated modules, for example one multiplier and one multiplyaccumulate (MAC) unit. Whenever the multiplier is used, the MAC-unit could be powered down or vice versa.

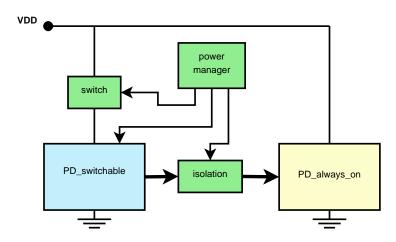

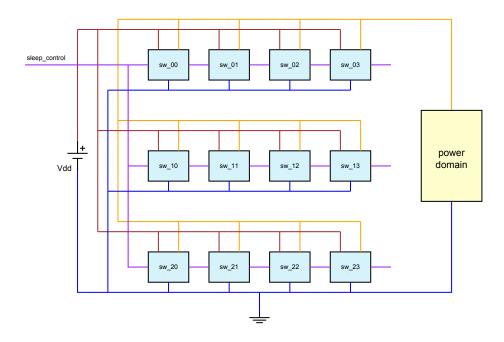

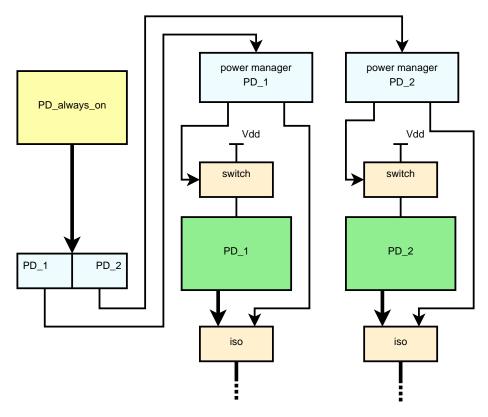

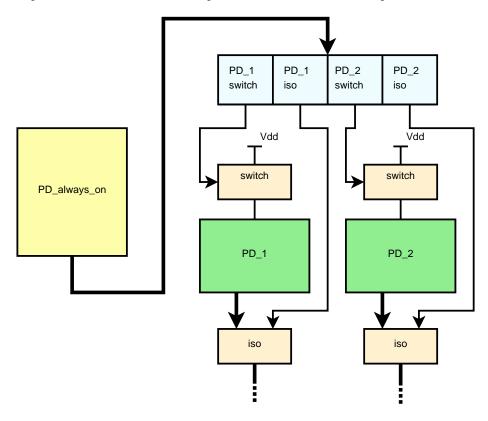

A general overview of a power gated system is illustrated in Figure 2.1. A part of the system which is in one switchable power domain is represented by  $PD\_switchable$ . Its output signals are connected to another power domain  $(PD\_always\_on)$ , which is an always-on domain in this example. It can be seen, that the outputs are isolated to prevent unknown signals propagating through the design when  $PD\_switchable$  is switched off. Also, a power switch is inserted between the voltage supply VDD and the power domain. Furthermore, a power manager is integrated into the system to control the power gating related cells.

In the coming sections, the individual parts of the scheme and the general considerations for power gating will be described in more detail.

#### 2.2.1 Power domain

A part of a design which is connected to the same power supply is called a *power domain*. When no power gating is used, the complete design is in the same, always-on, power domain. When power power gating is used, usually several power domain are present in the design. In Figure 2.1, all modules that are contained in the power domain  $PD_{always_on}$  are connected to the

Figure 2.1: General power gating scheme

supply voltage VDD which is always on. All modules which belong to the power domain *PD\_switchable* are connected to VDD through a switch, hence they are connected to an own power supply.

#### 2.2.2 Power switch

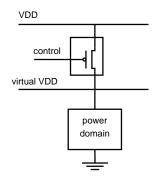

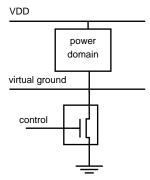

To cut off the power supply of a power domain, a sleep-transistor which is controlled like a switch is used. There are two possibilities to cut off the power supply of a power domain. Either, a header or a footer switch is used as depicted in Figure 2.2 and Figure 2.3, respectively. The header switch is placed between the supply voltage and the power domain, thus introducing a virtual voltage supply. The footer switch is placed between the power domain and ground, thus introducing a virtual ground. In Figure 2.1, a header switch is used. An overview of the advantages and disadvantages of both approaches is given in [6, ch. 5.1].

Figure 2.2: Header switch

The insertion of power switches influences the system's behaviour in multiple ways, namely rush-in current, area overhead and voltage drop.

Figure 2.3: Footer switch

When a module is powered on after a sleep period, a sudden *rush-in current* is introduced. This current affects the power-on energy significantly and causes noise in the circuit. It can be controlled by connecting the power switches in a daisy-chain configuration, so that they are turned on one after another and so limit the current flow ([37]).

Power switches also introduce *area overhead* to the design which translates into a higher total power consumption. Several approaches to reduce this area overhead have been proposed, for example to connect the power switches in a cluster ([38]) or in a distributed network ([39]).

Another important factor is the *voltage drop* over the switch during active mode, if it is too high, the required frequency cannot be reached which leads to timing problems. The voltage drop is related to the number of power switches and their size [40].

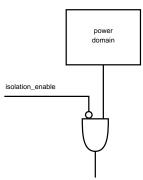

#### 2.2.3 Isolation

Interfaces between power gated domains and other domains, in Figure 2.1 between  $PD\_switchable$  and  $PD\_always\_on$  have to be taken special care of. When a power domain is shut off, its output signals are floating, i.e. it is not known which value they have. In order to prevent unknown values propagating through the design, the output signals of the power domains have to be isolated. Therefore, the outgoing signals have to be forced to either  $\theta$  or 1 by using special isolation cells.

When output signals of switched-off power domains are forced to zero, an isolation cell like in Figure 2.4 is used. As long as the power domain is switched on, *iso* is low. As soon as it is switched off, *iso* becomes high to enforce the output of the isolation cell to be low. The truth table can be found in Table 2.1.

Figure 2.4: Principle of an and-isolation cell

| Data | iso | Out |

|------|-----|-----|

| 1    | 0   | 1   |

| 0    | 0   | 0   |

| x    | 1   | 0   |

Table 2.1: Truth table of an and-isolation cell

When the output signals are forced to one, an isolation cell like in Figure 2.5 is used. The truth table is shown in Table 2.2.

Figure 2.5: Principle of an or-isolation cell

| Data | iso | Out |

|------|-----|-----|

| 0    | 0   | 0   |

| 1    | 0   | 1   |

| х    | 1   | 1   |

Table 2.2: Truth table of an or-isolation cell

Another consideration is whether the isolation cells should be placed at the output of the power domain, in Figure 2.1  $PD\_switchable$ , or at the input of the next module, which is using the output signals of the power gated module as inputs, in Figure 2.1  $PD\_always\_on$ .

In terms of functionality, there is no difference, but as one power domain usually provides input values to multiple modules, there is more area overhead when the signals are isolated at their destination. Furthermore, analysis and verification is simplified when signals are isolated at their output. In Figure 2.1, the isolation cells are placed at the output of the power domain.

Introducing isolation cells can also affect the timing of the design and therefore the maximum achievable frequency. It can occur that due to isolation cells the timing of a path cannot be reached anymore. Hence this path becomes a critical path. This can lead to additionally required buffers or faster cells in the path, increasing power consumption. Moreover, synthesis and layout tools are more restricted in performing design optimisation.

#### 2.2.4 State retention and restoration

When registers are shut off, they lose their internal state. When the stored value still has to be present after a shutdown period, the register's state can be retained or restored.

State retention (SR) can be implemented by three methods:

- 1. Software based, where the value of the register which is to be switched off is written to an external memory or another register which remains switched on.

- 2. Exploiting already existing scan chains by shifting the scan registers as scan-in-testing while the outputs are routed to an external memory during the power-down sequence.

- 3. Usage of special state retention flip flops which are capable of saving the internal state during. power-down

A detailed comparison between the methods can be found in [6, ch. 5.3]. In this work, the focus is explicitly on SR registers.

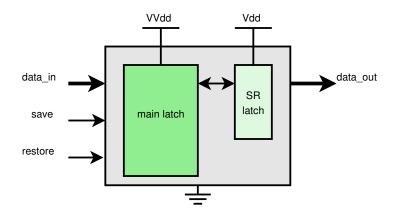

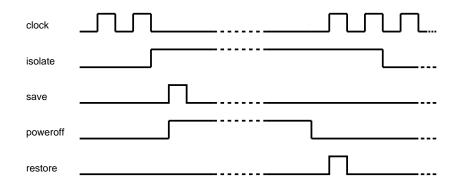

A state retention register is a special register that contains, in addition to the normal functionality, a shadow register which can retain the state during shut off. A schematic can be seen in Figure 2.6. This type of SR registers has two latches, a main latch for the active mode which is connected to the virtual voltage supply,  $VV_{dd}$ , and a SR latch which dissipates less leakage power than the main latch which is connected to an always-on voltage supply ( $V_{dd}$ ). Before a SR register is shut off, the *save* signal has to be set in order to transfer the stored value from the main latch into the SR latch. At wakeup, the *restore* signal has to be set so that the data is written back.

An advantage of state retention cell compared to the other state retention methods is that the design and the design flow itself does not have to be changed, apart from assigning the *save* and *restore* signals properly. A drawback is, that the retention cells have area overhead, typically 20% or more ([6]) and require additional control signals. To avoid the use of control signals, a sense-amplifierbased state retention flip flop is proposed in [41]. The presented design has a retention time in the range of milliseconds and a small area overhead. The

Figure 2.6: State retention register

rather long retention time, however, makes these SR registers less suitable for fast power-gating.

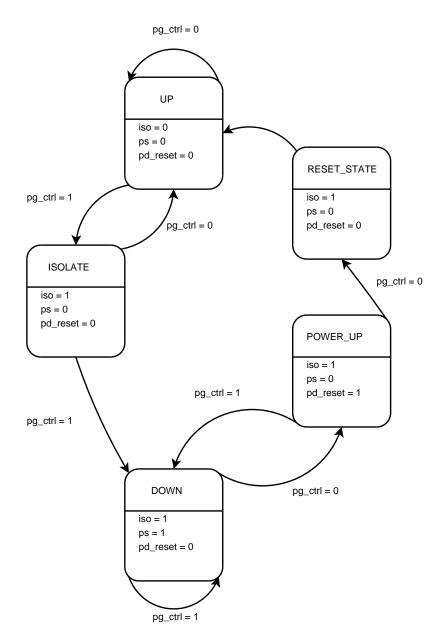

#### 2.2.5 Power manager

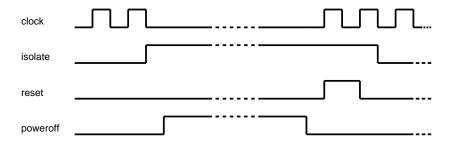

The power manager is in charge of providing the control signals to the power switches, isolation cells, and, if present, to the SR registers. It can be implemented as a dedicated hardware module or in software. In Figure 2.1, the power manager is implemented in hardware. The control sequence for a system without SR can be seen in Figure 2.7. When registers are included in the power domain, a reset signal has to be provided before de-isolation to set the registers in the power domain in a known state. The control sequence for a system with SR can be seen in Figure 2.8.

Figure 2.7: Control sequence for a design without state retention

#### 2.3 Power aware compilation

The compiler has a large influence on the power efficiency of an application. Considering power gating, it is relevant in which cycle a resource is used and how long its idle periods are. Usually, the compiler has a lot of freedom how to

Figure 2.8: Control sequence for a design with state retention

schedule as it is only constrained by data flow and control demands. That can lead to inefficient resource usage in terms of idleness.

In the following section the different principles of leakage power aware compilation are explained. Basically, there are two principles:

- 1. Post-processing: The program code is scheduled first before a post-processing algorithm is executed to analyse the generated assembly code for possibilities to shut off certain blocks. Then, power gating instructions are inserted into the assembly code.

- 2. Smart scheduling: Already during the initial scheduling phase, the idle periods of functional unit are increased without affecting the performance. This is achieved by smart mapping of the instructions to the hardware.

#### 2.3.1 Method one: Post-processing

In [42], a patent is filed for automatic scheduling of power gating instructions. The principle is to translate the high-level code into assembly, followed by an analysis of the dataflow and utilisation of hardware-blocks. Based on the results, power-gating instructions are inserted into the code. In a next step, power gating instruction are merged together if possible in order to minimse instruction execution power. To determine possible savings, the leakage energy of the block is traded off against the energy required to fetch and decode a power-gating instruction. Other overhead is not considered in this approach.

In [43], several compiler techniques for power aware scheduling are described. It covers both dynamic and static power minimisation. Power gating awareness is reached by inserting power-off and power-on instructions into the assembly code.

The authors of [44] first compare hardware-based methods to analyse the resource utilisation with compiler based methods. They draw the conclusion that the compiler based methods are suited better as a compiler has an overview of the total dataflow, the hardware based methods require a certain history to base assumptions on. Then they describe their compiler approach, which starts with an initial scheduling of the code, followed by a partitioning of the program into hot and cold blocks. Afterwards, an analysis of the utilisation of these blocks is performed. Based on a power model which considers expected idle time, power-on and power-off energy, the compiler inserts power-off and power-on instructions into the code.

In [45], a similar approach like in [44] and [42] is described. The program is scheduled first, then a data flow diagram is set up. Based on that, the compiler inserts power gating instructions into the code. Their power model takes the power-off and power-on energy into account.

All presented methods have the drawback that they do not consider the additional energy overhead which is introduced into the system due to power-gating related cells like power switches or isolation cells. Also they give the compiler during the initial scheduling all freedom. No consideration is made of possibilities to select different function units in instruction level parallelism (ILP) or delay instructions in order to leave a module switched off longer without influencing the functionality.

#### 2.3.2 Method two: Smart scheduling

In [46], a scheduling method which increases the idle time of function units is described. The idea behind the method is that if a resource has a longer continuous idle period, it can be shut off. The approach is to schedule in a way that functional units are used in blocks. However, this method does not consider ILP.

In [47], a scheduling approach for clustered VLIW architectures is described. The principle is as follows: Whenever a functional unit is idle for one clock cycle, it is marked as sleeping. During scheduling, when there is more than one functional unit of the desired type, the one which has slept for the longest time is selected by the compiler to compensate for the wakeup-energy. The energy model that is used in this work to determine the break-even point trades off the leakage energy of the functional unit with the energy required to power it on.

Another method is developed in [48], in which a loop scheduling is described where resources are rescheduled to better locations to increase idle periods in other resources.

In [49], the authors present another leakage energy aware scheduling method, which has the focus on the utilisation of arithmetic logic units (ALUs) in loops. First they identify all the loops in the program, then they analyse the critical, most executed block in each loop. Within this block, they analyse how many ALUs are necessary, they call it instructions issued per cycle (IPC). After analysis, the program is rescheduled with the previously determined subset of ALUs. This could cause a overhead due to increased execution time when there were more ALUs necessary in the non-critical blocks of the loop then in the critical block. The scheduling algorithm therefore has to take the energy overhead caused by that into account and make sure that the savings due to shut-off ALUs are larger than the energy overhead. After rescheduling is complete, power-off and power-on instructions are inserted before and after the loops to shut off the unused ALUs. The authors base their trade-off on the leakage energy that could be saved versus the energy overhead due to switching on a function unit and the additional energy required for extra required execution cycles. Energy overhead caused by other power gating related cells that have to be added to the design, like isolation cells, they do not consider.

### Chapter 3

# Analysis of the break-even point

An important task within this thesis was the evaluation whether applying power gating to a system can bring benefits. The analysis is presented in this chapter.

The chapter is organised as follows: First, the power dissipation characteristics of a system that uses power gating is described in section 3.1. In section 3.2, the energy consumption in the different states of a processor is analysed. In section 3.3, the savings are explained, followed by an analysis of the energy overhead in section 3.4. Afterwards, the break-even point for power gating based on the findings is derived in section 3.5. Finally, two example power profiles of power gated systems are illustrated in section 3.7.

#### 3.1 Power profile of a power gated system

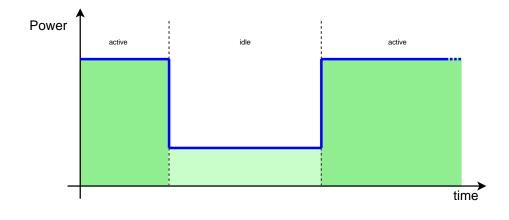

A digital system like a processor is usually not constantly active. It has periods where computations are performed followed by idle periods. A schematic of an example power profile of a system is illustrated in Figure 3.1. During *active*, the system is performing useful tasks. The power consumption is illustrated as an average over the complete active period. Afterwards, the system is not performing any useful tasks, i.e. it is idle. The power consumption during that period is determined by the leakage power consumption of the system, assumed that the clock is stopped, i.e. that clock gating is applied.

In Figure 3.2, the power consumption characteristics of a system that uses power gating is depicted. At  $t_{idle}$ , the system has finished the active state and is switched off. The switching off process is finished at  $t_{off}$ . Then, the system remains switched off until  $t_{sleep}$ . At that moment, it is switched on again. At  $t_{on}$ , it is again fully functional. The individual components of the power consumption will be explained in the remainder of this chapter.

Figure 3.1: Power dissipation of a non power-gated system

Figure 3.2: Power dissipation of a power gated system

#### 3.2 Energy consumption in the different states

The total energy consumption of a power gated system is composed of the energy which is consumed by the power domain and the energy which is consumed by the additional power gating related modules. The modules which are constantly active, like a power manager, are consuming energy all the time  $(E_{add.modules})$ . The energy consumption of the remaining components depends on the state of the processors.

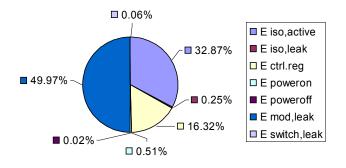

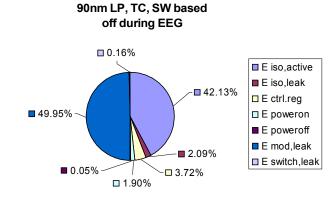

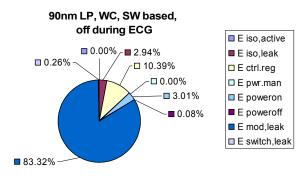

During  $t_{active}$ , the system is in its active state. The energy in this state is consumed by the power domain  $(E_{mod,active})$ , the isolation cells  $(E_{iso,active})$  and the

SR registers which consume more energy than regular registers ( $\Delta E_{SR,active}$ ).

At  $t_{idle}$ , the system has finished the active state and goes immediately to the idle state by switching off the clock. At the same time it is powered off. The powering off process takes place until  $t_{off}$ . During that time, the power domain still leaks but the leakage energy of the power domain  $(E_{mod,leak,on})$  is converging to the off-level.

Then, the system remains switched off during  $t_{down}$ . The energy which is consumed depends on the leakage of the power switch(es) ( $E_{switch,leak}$ ), the leakage of the isolation cells ( $E_{iso,leak}$ ) and the leakage of the SR registers ( $E_{SR,leak}$ ).

At  $t_{sleep}$ , the power domain is switched on again. The switching-on process takes until  $t_{on}$ . The energy which is consumed during that period is the leakage energy of the power domain  $(E_{mod,leak,on})$  and the additional energy required to switch the power domain on  $(E_{poweron})$ . Afterwards, the system is fully functional.

#### 3.3 Energy savings

The energy savings are defined as the amount of energy that is saved when power gating is applied to a system. In Figure 3.2, it is represented by the blue areas.

The energy savings of a power gated module are determined by two factors:

- 1.  $E_{mod,leak}$ , the energy which the module would consume during the idle period if it was not switched off. It is determined by the leakage power of the power domain  $(P_{mod,leak})$  multiplied by time the module is switched off  $(t_{down})$ .

- 2.  $E_{powerdown}$ , which is the difference between the leakage energy the power domain would normally consume during powering off (between  $t_{idle}$  and  $t_{off}$ ) and the energy which is still consumed ( $E_{mod,leak,on}$ ). That implies that from the moment the power-down signal is given, energy is saved.

Both contributors can be combined to the total energy savings  $E_{savings}$ :

$$E_{savings} = E_{mod,leak} + E_{powerdown}$$

$$= P_{mod,leak} \cdot t_{down} + E_{powerdown}$$

(3.1)

For future analysis, the equation is rewritten to

$$E_{savings} = \alpha \cdot t_{down} + \varphi \tag{3.2}$$

with  $\alpha = P_{mod,leak}$  and  $\varphi = E_{powerdown}$ .

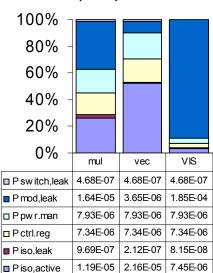

#### 3.4 Energy overhead

The energy overhead is defined as the additional energy consumption of a system due to the required components for power gating. In Figure 3.2, the overhead is represented by the pink, purple, and orange areas. The energy overhead can be divided into four subgroups, namely

- 1.  $E_{overhead,down}$ , the additional energy which is consumed while the power domain is switched off. It is represented by the purple areas.

- 2.  $E_{overhead,active}$ , the additional energy which is consumed while the power domain is active. It is represented by the pink areas.

- 3. *E*<sub>overhead,always</sub>, the additional energy which is consumed during the total run-time. It is represented by the dark orange area.

- 4.  $E_{poweron}$ , which is required to power a module back on after it has been switched off. It is represented by the light orange area.

$E_{overhead,down}$  is determined by the leakage power of the power switch(es)  $(P_{switch,leak})$ , the leakage power of the isolation cells  $(P_{iso,leak})$ , the leakage power of the SR registers  $(P_{SR,leak})$ , and the time during which the power domain is switched off  $(t_{down})$ . The equation for  $E_{overhead,down}$  is as follows:

$$E_{overhead,down} = E_{switch,leak} + E_{iso,leak} + E_{SR,leak}$$

$$= t_{down} \cdot (P_{switch,leak} + P_{iso,leak} + P_{SR,leak})$$

(3.3)

$E_{overhead,active}$  depends on the energy consumed by the isolation cells during active mode ( $P_{iso,active}$ ), the additional power consumed by the SR registers compared to what regular registers would consume during active mode ( $\Delta P_{SR,active}$ ), and the time during which the power domain is active ( $t_{active}$ ). The equation for  $E_{overhead,active}$  is as follows:

$$E_{overhead,active} = E_{iso,active} + \Delta E_{SR,active}$$

$$= t_{active} \cdot (P_{iso,active} + \Delta P_{SR,active})$$

(3.4)

$E_{overhead,always}$  is caused by always-on components that have to be added to the design in order to enable power gating, as for example control registers or a power manager. Their power consumption ( $P_{add.modules}$ ) and the total run time, ( $t_{total}$ ) determine the total energy consumption. Summarising,  $E_{overhead,always}$ is defined as follows:

$$E_{overhead, always} = t_{total} \cdot P_{add.modules} \tag{3.5}$$

$E_{poweron}$  is determined by the number and size of the power switches and the size of the power domain.

To evaluate the impact of the power gating related cells and components introduced in section 2.2, a short summary is given below which of the energy overhead components they influence.

- Power switches. They leak when the power domain is switched off, they therefore have an impact on  $E_{overhead,down}$ .

- Isolation cells. One factor is the energy they consume while the power domain is active. Whenever the output of the power domain switches, the isolation cells have to switch as well. This influences  $E_{overhead,active}$ . The other factor is the leakage energy consumed by the isolation cells while the power domain is switched off. That has an impact on  $E_{overhead,down}$ .

- SR registers. During active mode of the power domain, they introduce a certain energy overhead, namely the difference in energy consumption compared to regular registers. This influences  $E_{overhead, active}$ . The leakage energy during of the SR registers the period the power domain is switched off impacts  $E_{overhead,down}$ .

- Additional modules, like a power manager or function units. As they are switched during the complete run-time, they influence  $E_{overhead, always}$ .

Summarising, the energy overhead can be written as follows:

-

-

$$E_{overhead} = E_{overhead,down} + E_{overhead,active} + E_{overhead,always} + E_{poweron}$$

$$= t_{down} \cdot (P_{switch,leak} + P_{iso,leak} + P_{SR,leak})$$

$$+ t_{active} \cdot (P_{iso,active} + \Delta P_{SR,active})$$

$$+ t_{total} \cdot P_{add.modules}$$

$$+ E_{poweron}$$

(3.6)

For simplicity's sake for the final analysis, the individual factors are merged, which leads to the following equation:

$$E_{overhead} = t_{down} \cdot \beta + t_{active} \cdot \gamma + t_{total} \cdot \delta + \epsilon \tag{3.7}$$

-

with  $\beta = P_{switch, leak} + P_{iso, leak} + P_{SR, leak}, \gamma = P_{iso, active} + \Delta P_{SR, active}, \delta =$  $P_{add.modules}$  and  $\epsilon = E_{poweron}$ .

#### 3.5Derivation of the break-even point

Building on the above analysis of the savings and the overhead, an analytical equation can be derived for the minimum percentage of time that the module has to be switched off in order to gain energy savings, i.e. the break-even point. Energy is saved when the energy savings exceed the energy overhead:

$$E_{savings} > E_{overhead}$$

(3.8)

By using the above definitions for the savings and the overhead, and expressing  $t_{active}$  with  $t_{total} - t_{down}$ , a condition for the minimum down time  $t_{down,min}$  can be found:

$\alpha \cdot t_{down,min} + \varphi > \beta \cdot t_{down,min} + \gamma \cdot t_{active} + \delta \cdot t_{total} + \epsilon$   $t_{down,min} (\alpha - \beta) - \gamma (t_{total} - t_{down,min}) > \delta \cdot t_{total} + \epsilon - \varphi$   $t_{down,min} (\alpha - \beta + \gamma) > t_{total} (\gamma + \delta) + \epsilon - \varphi$   $t_{down,min} > \frac{\epsilon - \varphi + t_{total} (\gamma + \delta)}{\alpha - \beta + \gamma}$ (3.9)

Some of the factors of the above analysis can be omitted because they are neglegible, namely the leakage power of the switch  $(P_{switch,leak})$ , the leakage power of the isolation cells  $(P_{iso,leak})$ , the energy to switch a power domain on after it has been switched off  $(E_{poweron})$  and the energy which is saved during powering down before reaching the lowest energy state  $(E_{powerdown})$ . This will be shown in the results section (chapter 6). Then, the condition for  $t_{down,min}$  is not longer depending on the total run time but can be expressed percentage-wise with reference to  $t_{total}$ :

$$\frac{t_{down,min}}{t_{total}} > \frac{P_{iso,active} + \Delta P_{SR,active} + P_{add.modules}}{P_{iso,active} + \Delta P_{SR,active} + P_{leak,mod} + P_{SR,leak}}$$

(3.10)

Using the previously definitions for  $\alpha$ ,  $\gamma$  and  $\delta$  and defining  $\beta' = P_{SR,leak}$ , the equation can be written as follows:

$$\frac{t_{down,min}}{t_{total}} > \frac{\gamma + \delta}{\gamma + \alpha + \beta'} \tag{3.11}$$

where  $\alpha = P_{leak,mod}$ ,  $\beta' = P_{SR,leak}$ ,  $\gamma = P_{iso,active} + \Delta P_{SR,active}$  and  $\delta = P_{add.modules}$

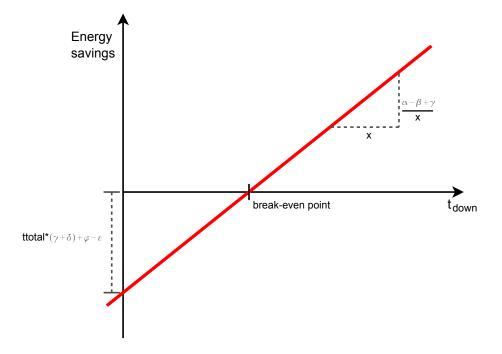

#### 3.6 Absolute energy savings

For the calculation of the absolute energy savings, the break-even point is a first indication. After the break-even point for a given system has been calculated, it can be determined whether the system can be switched off for a sufficient long time in order to gain energy savings. When this is the case, it also has to be calculated how big the total energy savings are. This is done the following way:

The absolute savings are the difference between the possible energy savings and the introduced overhead:

$$E_{savings,tot} = E_{savings} - E_{overhead} \tag{3.12}$$

Using the definitions for  $\alpha$ ,  $\beta$ ,  $\gamma$  and  $\delta$ , the equation can be rewritten:

$$E_{savings,tot} = E_{savings} - E_{overhead}$$

=  $\alpha \cdot t_{down} + \varphi - (t_{down} \cdot \beta + t_{active} \cdot \gamma + t_{total} \cdot \delta + \epsilon)$

=  $t_{down} \cdot (\alpha - \beta + \gamma) - t_{total} \cdot (\gamma + \delta) + \varphi - \epsilon$  (3.13)

An illustration can be seen in Figure 3.3. The slope of the line is determined by the term  $\alpha - \beta + \gamma$ , the offset is determined by  $t_{total} \cdot (\gamma + \delta) + \varphi - \epsilon$ . The bigger  $\alpha$ , i.e. the leakage power of the power domain, the bigger is the steepness of the line, i.e. the energy savings.

Figure 3.3: Illustration of the absolute energy savings

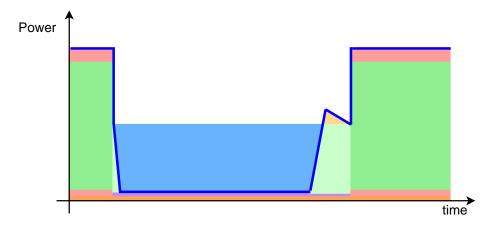

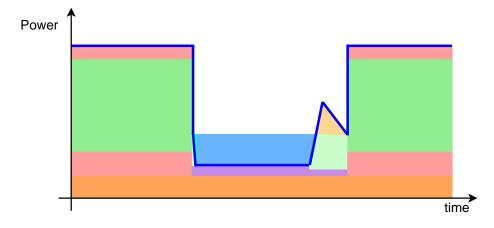

#### 3.7 Example for a power gating scheme

To illustrate the power characteristics of power domains, two examples are illustrated. The first example depicts the power consumption scheme of a power domain where power gating leads to energy savings, the second example shows a power domain where power gating leads to extra energy consumption. Both examples are for illustration purposes and not based on numbers obtained from experiments. The color scheme corresponds to the color scheme used in Figure 3.2.

In Figure 3.4 the power characteristics of a power domain which can be switched off for a significant amount of time is displayed. It can be seen that the leakage

energy (blue) of the power domain is relatively high and the introduced overhead (orange, pink, purple) rather low. Therefore, power gating is justified in this system.

Figure 3.4: Example of a power gated module where power gating makes sense

As a counterexample, in Figure 3.5 the power power distribution of another power domain is shown. There it can be seen, that the introduced energy overhead, especially caused by additional modules and the isolation cells, is larger than the savings, which implies that power gating is not efficient in this case.

Figure 3.5: Example of a power gated module where power gating does not makes sense

### Chapter 4

## Methodology

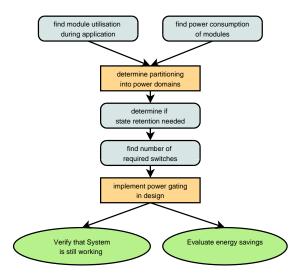

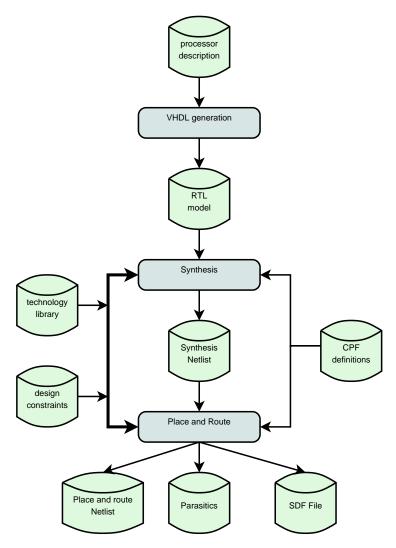

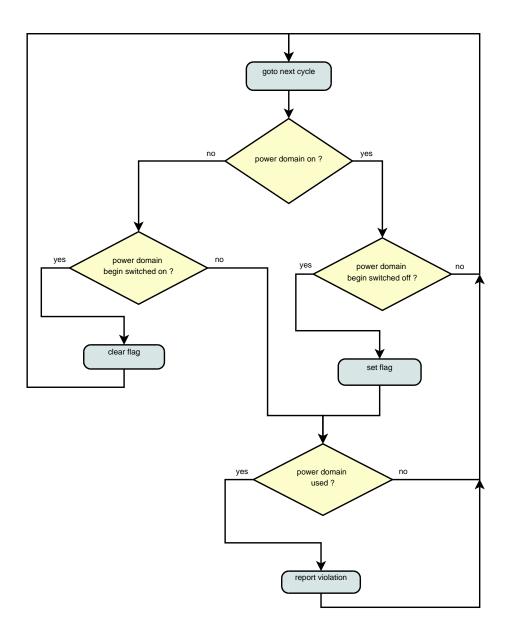

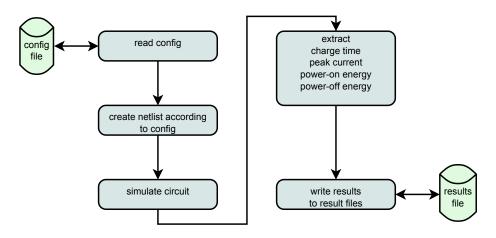

In this chapter, the methodology that has been developed and used during this work is explained. It is a design flow that can be applied to a system, in this work a processor, to implement fine-grained power gating. In Figure 4.1, an overview is depicted. In the flow, the system is partitioned into power domains, then power gating is implemented into the design. Finally, a verification is performed to prove that the system is still functionally correct, furthermore, the energy savings are evaluated.

Figure 4.1: General power gating design flow

The chapter is organised as follows: In section 4.1, the tools that were used during this work are introduced. In section 4.2, the methodology to obtain power consumption values is described. In section 4.3, it is explained how the module utilisation is determined. Based on those section, the partitioning into power domains is described in section 4.4. Afterwards, the method to determine if state retention (SR) is required in section 4.5 is presented. A description how the number of required power switches can be identified is presented in section 4.6. In section 4.7, the workflow for implementing power gating into a design on RTL level is described. In section 4.8 it is explained how it can be verified that the system still is functionally correct. Finally, the evaluation of energy savings is explained in section 4.9.

#### 4.1 Tools used in this work

In this section, a brief introduction of the tools that were used in this work is given.

- Target IP Designer [50], a tool for the design of application specific instruction set processors (ASIP). It uses a high-level description language (nML, [51, ch. 4]) to specify the functionality and architecture of the desired processor. From this description, synthesisable HDL code and a compiler are generated. Also, a cycle-accurate and instruction-accurate simulator are provided that can be used for verification and debug purposes. A typical design flow for the design of a processor with Target IP Designer is presented in [52].

- Silicon Hive's Hive Logic [53], also a tool for the design of ASIPs. Like in Target, the architecture of the desired processor is described in a Silicon Hive proprietary description language called TIM (The Incredible Machine). From the description, the HDL code, compiler and simulator are generated. A description of the design flow of Hive Logic can be found in [54].

- The Cadence [14] design tools, including NCSim (for rtl- and netlist simulations), RTL Compiler (for synthesis) and Encounter (for place and route).

- PrimeTime [55] from Synopsis [15], used for the extraction of power numbers after layout.

- HSPICE [56] from Synopsis, used for circuit-level simulations required to obtain accurate numbers for the analysis.

- Matlab from MathWorks [57], used for plots.

- tcl, a scripting language used for automation of design processes or simulations.

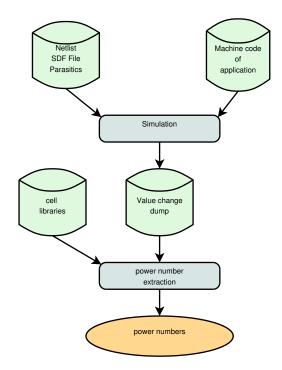

#### 4.2 Determination of power consumption values

For extraction of power numbers, the flow which is depicted in Figure 4.2 was used. Initially, a netlist after place and route and a SDF (standard delay format) [58] file which defines the delays of each gate in the design is required, i.e. the complete design flow from RTL to layout has to be executed (refer section 4.7). A simulation has to be executed with a realistic application to obtain the switching activity. During simulation, a VCD (value change dump) file is generated containing the switching activity of all signals and nodes. This file is

Figure 4.2: Flow for the extraction of the power numbers

then used to extract power numbers with primetime. The power consumption is broken down into *static power* which consists of mainly subthreshold leakage, *internal power* which is consumed within the boundaries of a cell including power due to charging and discharging of internal capacitances and short circuit currents, and *switching power* which is caused by charging and discharging of load capacitances at the output of a cell.

When the power consumption of all modules is known, the main consumers of leakage power have to be identified, as the focus is on leakage power consumption is this work. For this purpose, a tcl-script was written which produced a report with the required information at a glance. In the script, the modules of interest are defined and then the power concumption report generated by PrimeTime is scanned for these modules. Then, the power numbers are written out and the leakage power consumption related to the total leakage power consumption is calculated. The script can be found in the electronic appendix (filename get\_power\_numbers.tcl), a code snippet for the calculation of the relative leakage power consumption of a module can be found in Listing 4.6.

```

1 # get total leakage power as reference

2 if {[string match ${top_module_name} [lindex $words 0]] == 1} {

3 set total_leakage [lindex $words 3]

4 }

5

6 if {[string match ${module_name} [lindex $words 0]] == 1} {

7 set rel_leakage [expr [lindex $words 4]/$total_leakage*100]

9 puts $rel_leakage

9 }

```

Code Snippet 4.1: Extract relative leakage power consumption of report file

### 4.3 Resource utilisation over time

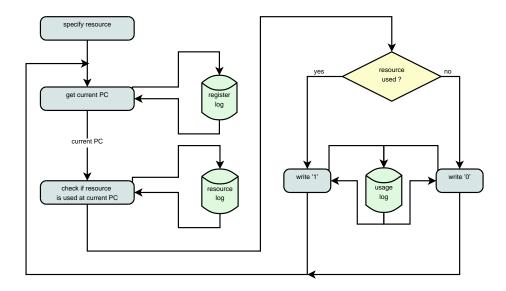

The complete flow to determine the resource utilisation over the complete runtime of the application is illustrated in Figure 4.3.

When the power consumption of the resources is known, it has to be determined if they have sufficient idle periods where they can eventually be switched off. For this purpose, a script was written during this thesis that could provide this information. For this script, the following information is required: First it has to be determined which resources are used for which instruction (where one instruction represents all operations used during one cycle). The second information is the sequence in which the instructions are executed during the complete run-time of the application.

For this purpose, Target IP Designer provides useful features. One is a mechanism that gives information about resource usage for each instruction. The desired resources that are to be monitored have to be specified and the result will be information about which instruction requires the desired resource. The result will be saved in a *resource usage file*. Another useful feature is that a log file of the register content is generated for the complete run-time with the corresponding program counter (PC) value. The result is stored in a *register log file*.

These two files can be exploited to find the utilisation of specific resources over time. The register log file is parsed for the value of the program counter which is also listed in the resource usage file. If a specific resource is used for the specific program counter, a '1' is saved in a *result file*, otherwise a '0'. A code snippet for the explained procedure is shown in Code Snippet 4.4. The complete scripts can be found in the electronic appendix (folder resource usage).

Code Snippet 4.2: Link resource usage file with register log file

This result file can be used in Matlab to plot the usage over time for an easy overview, the matlab script can be found in the electronic appendix (filename plot\_usage.m).

# 4.4 Partitioning into Power Domains

In this section, the steps that are required to divide a system into different power domains are explained. The modules with a significant leakage power consumption should be considered as possible power domains. Also, it is important how the modules are utilised during the application. For an initial partitioning of the system, modules with similar utilisation profiles and a relatively high leakage power consumption should be grouped into power domains. However,

Figure 4.3: Flow for the determination of the resource usage over time

the final partitioning requires good knowledge of the system and the executed application.

# 4.5 Determination if state retention is required

When the power domains are determined, it has to be decided whether state retention (SR) is required. When a power domain contains registers, it has to be analysed if their internal state has to be retained during shutdown. For example, a power domain can contain registers that are used to store temporary variables of the application. When this power domain is switched off during the the execution of the application, it is most likely that the state has to be retained. However, when a power domain contains registers that are of a special type, for example vector registers, it can be different. A possible use-case is that an application consists of different function calls. Only one of the functions requires the presence of vector registers, otherwise they are not needed. Then, the state does not have to be retained.

In the end, extensive knowledge of the system and the application is required to determine if state retention is required or not. As it was described in chapter 3, SR registers also come with a certain overhead. For the final decision, several possibilities should be evaluated.

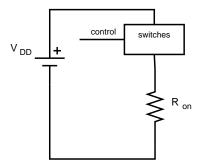

# 4.6 Number of required switches

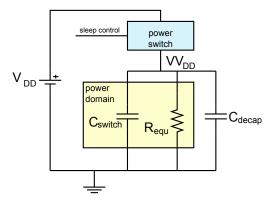

An important issue for power gating is the number of required power switches for a power domain. It has to be ensured that the voltage drop over the switches is low enough that the timing constraints can still be reached. For that purpose, the circuit is modelled as shown in Figure 4.4.  $R_{on}$  is the equivalent resistance of the power domain in active mode.

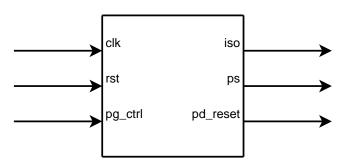

Figure 4.4: Equivalent circuit for determination of required number of switches