### Wideband Efficiency in a Class-F Power Amplifier

Andreas Berg Stenstrøm

Electronics System Design and Innovation Submission date: June 2014 Supervisor: Morten Olavsbråten, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

## **Problem Description**

Assignment title: Wideband Efficiency in a Class-F Power Amplifier

In many radio systems the efficiency of the power amplifier is extremely important. When a power amplifier is driven near its maximum output power, it will generate higher order harmonic frequency components. A way to increase the efficiency in the amplifier is to tune these components to a desired outcome. In class-F and class- $F^{-1}$ , also called harmonic tuned power amplifiers, the impedance of these components are tuned at the output of the amplifier. This will adjust the shape of the current and voltage, making the amplifier as efficient as possible.

The tasks of this assignment are:

- Study the principles of class-F and class-F<sup>-1</sup> power amplifiers.

- Learn to use electronic design automation software (Agilent ADS).

- Design and characterize a power amplifier with high efficiency over a relatively large bandwidth.

- Tune the harmonic impedances using load pull, to get as high efficiency as possible in the bandwidth.

- Manufacture one or more prototypes.

- Measure and characterize the amplifiers.

Specifications:

| Center frequency $(f_0)$ | 2.4 GHz                       |

|--------------------------|-------------------------------|

| Bandwidth (3 dB)         | 1.2 GHz                       |

| Output Power $(P_{out})$ | > 40 dBm within the bandwidth |

| Gain                     | > 12 dB within the bandwidth  |

| Input Match $(S_{11})$   | < -10 dB within the bandwidth |

| Efficiency               | as high as possible           |

Supervisor: Morten Olavsbråten Issued at: Department of Electronics and Telecommunications, NTNU, Norway

### Summary

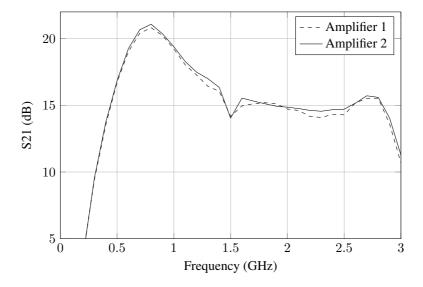

In this thesis, the design of a class-F/F<sup>-1</sup> amplifier with high efficiency in a 1.2 GHz bandwidth and center frequency at 2.4 GHz is presented. The harmonic tuning is done by using a CAD load pull test bench in Agilent ADS. The optimal impedances at  $f_0$ , and at the harmonics  $2f_0$  and  $3f_0$ , which gives the best performance is found by using the test bench. These impedances are realized in matching networks with passive components, microstrip lines and open circuit stubs. Two identical amplifiers were manufactured and characterized with small signal, large signal and two tone measurements. The design is based around a Cree 10 W GaN HEMT transistor and printed on a FR-4 substrate.

Simulations using the lossless load pull test bench resulted in a drain efficiency higher than 80% and PAE higher than 75% through the bandwidth while the output power was larger than 10 W with a maximum of 11.9 W. This is the optimal performance of the amplifier and set the impedances to obtain in the matching networks.

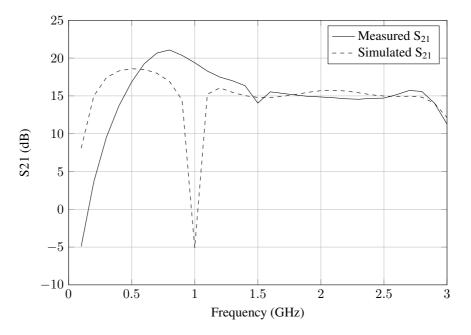

The final design with realized matching networks resulted in a decrease in efficiency of 5-15% and an increase in output power by about 0.5 dBm while operating at the 1 dB compression point. The decreased efficiency is due to imperfect matching and loss in components and microstrip lines. In the simulations, the amplifier achieved a 3 dB bandwidth of 1.8 GHz in the small signal gain.

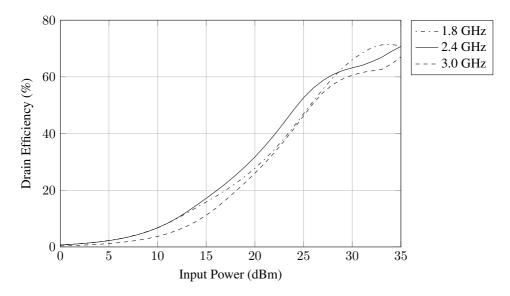

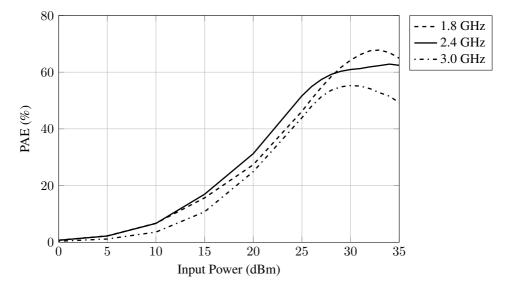

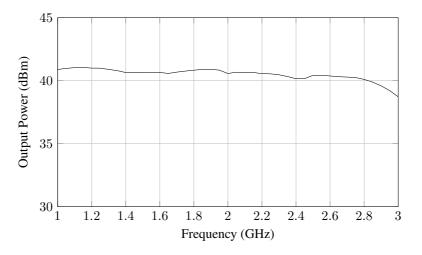

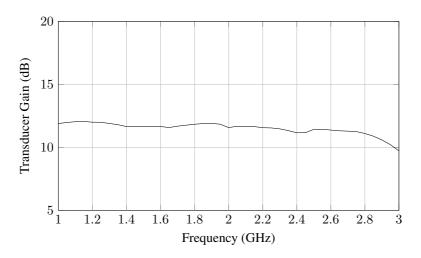

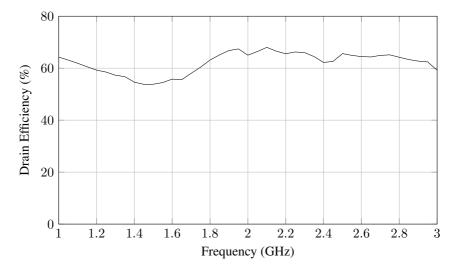

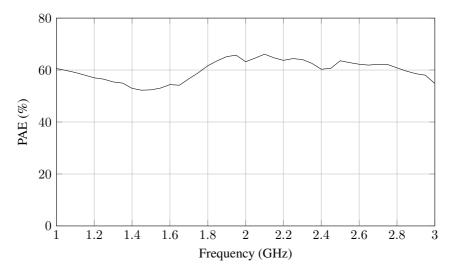

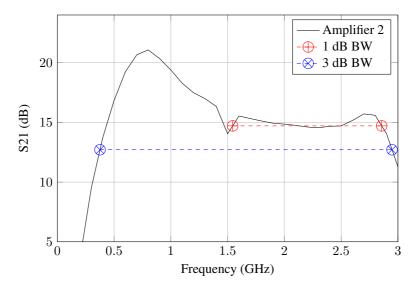

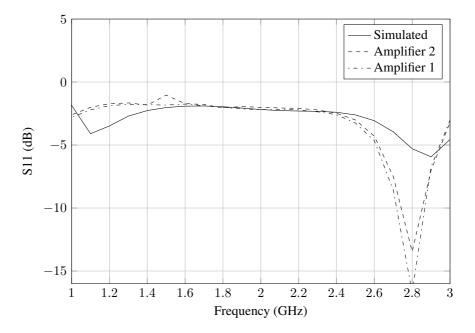

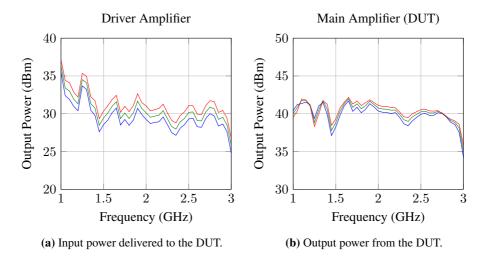

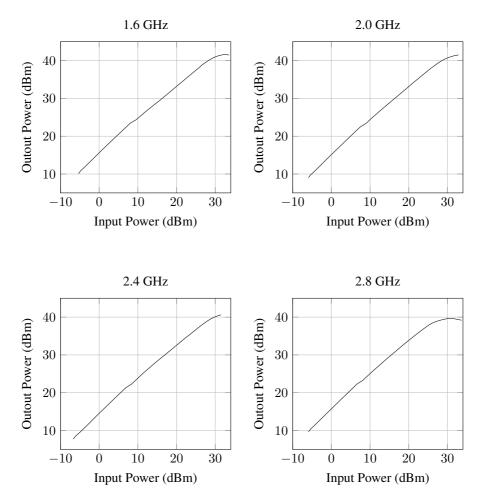

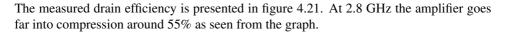

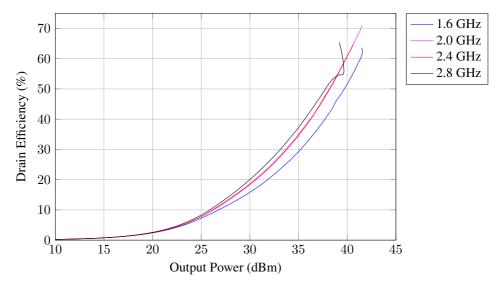

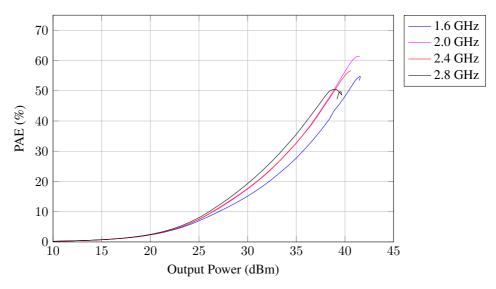

The measurements concluded that the most optimal bandwidth of operation is from 1.6 - 2.8 GHz, a 200 MHz shift from the bandwidth given in the assignment. The measurements results show a drain efficiency from 55-66% in the bandwidth and a PAE higher than 50%, delivering an output power of 14.2 W operating at 1 dB compression. The measured 3 dB bandwidth of the amplifier was 2.57 GHz.

The measured results are good as power amplifiers covering large frequency bands rarely has good efficiency throughout the whole bandwidth. Possible applications include cognitive radio transceivers, radios which use frequency hopping or as a buffer amplifier for lab purposes.

## Sammendrag

I denne oppgaven presenteres en metode for design av en klasse- $F/F^{-1}$  effektforsterker med senterfrekvens på 2.4 GHz og høy virkningsgrad i en båndbredde på 1.2 GHz. Dette gjøres ved å utføre harmonisk tilpasning ved hjelp av en "load pull" testbenk i simuleringsprogrammet Agilent ADS for radiosystemer. De optimale impedansene ved  $f_0$  og de harmoniske komponentene ved  $2f_0$  og  $3f_0$  som vil gi de beste resultatene kartlegges ved bruk av testbenken. Disse impedansene blir deretter realisert i tilpasningsnettverk ved bruk av passive komponenter og transmisjonslinjer. To like forsterkere ble produsert og deretter karakterisert ved bruk av småsignal-, storsignal- og totonemålinger. Forsterkeren er designet rundt en Cree 10W GaN HEMT transistor og frest ut på et FR-4 substrat.

Simuleringene utført med de tapsfrie "load pull" testbenkene gir en "drain efficiency" høyere enn 80% og PAE høyere en 75%, samt utgangseffekt høyere enn 10 W i hele båndbredden med en maks uteffekt på 11.9 W. Dette er den optimale ytelsen til forsterkeren med tanke på virkningsgrad.

Det endelige designet med realiserte tilpasningsnettverk resulterte i en 5-15% nedgang i virkningsgrad og en økt utgangseffekt med gjennomsnittlig 0.5 dBm mens forsterkeren opererer ved 1 dB kompresjon. Den lavere virkningsgraden kan skyldes feil i tilpasningen av nettverkene med de optimale impedansene, samt tap i passive komponenter og transmisjonslinjer. Den simulerte 3 dB båndbredden i småsignal gain var 1.8 GHz.

Resultatet av målingene konkluderte med at den mest optimale båndbredden er fra 1.6 - 2.8 GHz, dette er en 200 MHz forflytning i båndet. Målingene resulterte i en "drain efficiency" mellom 55-66% og en PAE høyere enn 50% samtidig som den maksimale utgangseffekten var på 14.2 W ved 1 dB kompresjon. Forsterkeren oppnådde en målt 3 dB båndbredde på 2.57 GHz.

Forsterkeren oppnådde god virkningsgrad som ikke er vanlig i konvensjonelle effektforsterkere med like stor båndbredde. Mulige bruksområder for forsterkeren er kognitive radioenheter, radioer som benytter frekvenshopping og bruk til laboratorieformål som en driverforsterker.

## Preface

This thesis is submitted in partial fulfillment of the requirements for the degree of master of science (MSc) at the Department of Electronics and Telecommunications, Norwegian University of Science and Technology (NTNU). The work was carried out in the period January to June 2014.

#### Acknowledgment

I would like to thank my supervisor, Associate Professor Morten Olavsbråten, for his valuable input and help with this thesis. His commitment and passion for the topic of RF power amplifiers combined with enthusiasm has been a source of motivation during my work on this thesis. I would also like to thank PhD cand. Dragan Mitrevski for help with my measurements as well as head engineer Terje Mathisen for his help with the production of the PCB. Finally, a special thanks to my friends and fellow students for valuable input and insight during this period.

Trondheim, Norway, June 2014. Andreas Berg Stenstrøm

## Table of Contents

| Su | ımma                                                      | у                                                                                                                                                                                                                                                     | i                                                                    |

|----|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Sa | mme                                                       | drag                                                                                                                                                                                                                                                  | ii                                                                   |

| Pr | eface                                                     |                                                                                                                                                                                                                                                       | iii                                                                  |

| Та | ble of                                                    | Contents                                                                                                                                                                                                                                              | vii                                                                  |

| Li | st of I                                                   | igures                                                                                                                                                                                                                                                | X                                                                    |

| Li | st of ]                                                   | ables                                                                                                                                                                                                                                                 | xi                                                                   |

| Ał | obrevi                                                    | ations                                                                                                                                                                                                                                                | xii                                                                  |

| 1  | Intr                                                      | duction                                                                                                                                                                                                                                               | 1                                                                    |

| 2  | The                                                       | •                                                                                                                                                                                                                                                     | 3                                                                    |

|    | <ul><li>2.1</li><li>2.2</li><li>2.3</li><li>2.4</li></ul> | S Parameters2.1.1Gain2.1.2Stability2.1.3MatchingPower Amplifiers2.2.1Efficiency2.2.2Linearity2.2.3Amplifiers Classes2.2.4Class-F Amplifier2.2.5Load and Source PullGaN Transistor Technology2.4.1Large Signal Simulations2.4.2Optimization Algorithms | 3<br>4<br>5<br>6<br>8<br>8<br>10<br>11<br>14<br>14<br>14<br>15<br>15 |

|    |                                                           | 2.4.3 Load-Pull Test Bench                                                                                                                                                                                                                            | 16                                                                   |

|       | 2.5   | Measurements                        | 17  |

|-------|-------|-------------------------------------|-----|

|       |       | 2.5.1 Network Analyzer              | 17  |

|       |       | 2.5.2 Calibration                   | 17  |

|       |       | 2.5.3 Measuring Power Amplifiers    | 18  |

|       |       | 2.5.4 Two-Carrier Characterization  | 18  |

|       |       |                                     |     |

| 3     | Desi  |                                     | 19  |

|       | 3.1   |                                     | 19  |

|       |       |                                     | 19  |

|       |       | 1                                   | 19  |

|       |       |                                     | 20  |

|       | 3.2   | 1 61                                | 20  |

|       | 3.3   | 0 0                                 | 21  |

|       |       |                                     | 21  |

|       |       |                                     | 24  |

|       |       | 3.3.3 Matching Networks             | 24  |

|       |       | 3.3.4 Realizing Test Bench Results  | 27  |

|       | 3.4   | Measurements                        | 29  |

|       |       | 3.4.1 Small Signal                  | 29  |

|       |       | 3.4.2 Large Signal                  | 31  |

|       | n     |                                     | ••• |

| 4     | Resi  |                                     | 33  |

|       | 4.1   |                                     | 33  |

|       |       |                                     | 33  |

|       |       | 8                                   | 36  |

|       | 4.0   | 1                                   | 40  |

|       | 4.2   |                                     | 42  |

|       |       | ε                                   | 42  |

|       |       | 4.2.2 Large Signal                  | 45  |

| 5     | Disc  | ssion                               | 51  |

| -     | 5.1   |                                     | 51  |

|       | 5.2   | 8                                   | 52  |

|       |       |                                     | 52  |

|       |       |                                     | 53  |

|       | 5.3   |                                     | 56  |

|       |       | 11                                  |     |

| 6     | Con   | usion                               | 57  |

|       | 6.1   | Further Work                        | 58  |

| Bi    | bliog | phy                                 | 59  |

| Ap    | opend | A - Test Bench Setup in Agilent ADS | П   |

| Ap    | opend | B - Schematic of the Final Design   | П   |

| -     | -     |                                     | IV  |

| · • ŀ | Pena  |                                     | - • |

| Appendix D - Measurement Pictures | V  |

|-----------------------------------|----|

| Appendix E - Matlab Code          | VI |

# List of Figures

| 2.1  | Generalized two-port network with source and load impedances. [4]              | 3         |

|------|--------------------------------------------------------------------------------|-----------|

| 2.2  | A general transistor amplifier circuit. [4]                                    | 4         |

| 2.3  | Comparison of different PA classes with respect to input signal overdrive      |           |

|      | and conduction angle. [8]                                                      | 7         |

| 2.4  | Two-tone intermodulation spectrum. [1]                                         | 9         |

| 2.5  | 1 dB compression point and third order intercept point (IP3) in log scale. [1] | 10        |

| 2.6  | I-V characteristic showing the bias point of different PA classes. [14]        | 10        |

| 2.7  | Resonators at the output to control the odd and even harmonics. [8]            | 12        |

| 2.8  | Ideal time domain current and voltage waveforms for class-F and class-         |           |

|      | $F^{-1}$ under equal biasing conditions and for same output power. [3]         | 12        |

| 2.9  | Load pull test bench block used in the simulations.                            | 16        |

|      |                                                                                |           |

| 3.1  | I-V characteristics of the Cree CGH40010 transistor with bias point and        | <u>01</u> |

|      | maximum current indicated.                                                     | 21        |

| 3.2  | Bias network schematic.                                                        | 22        |

| 3.3  | Attenuation of the RF signal to prevent leakage to the DC source               | 23        |

| 3.4  | Simulated reflection                                                           | 23        |

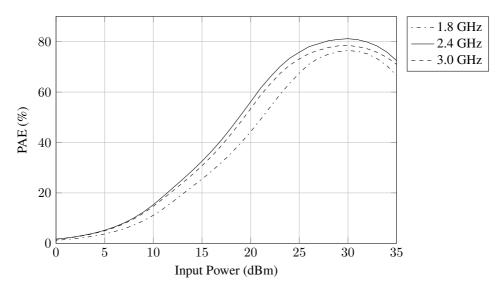

| 3.5  | Simulated stability factor $\mu$ before and after stabilization                | 24        |

| 3.6  | Using the test bench reversed to find optimal impedances for the source        |           |

|      | matching network.                                                              | 25        |

| 3.7  | Optimal source impedances for source and load matching networks with           |           |

|      | increasing frequency moving counterclockwise                                   | 26        |

| 3.8  | Comparison of the optimal impedances from the test bench and the real-         |           |

|      | ized network                                                                   | 28        |

| 3.9  | Comparison of the optimal impedances from the test bench and the real-         |           |

|      | ized network.                                                                  | 29        |

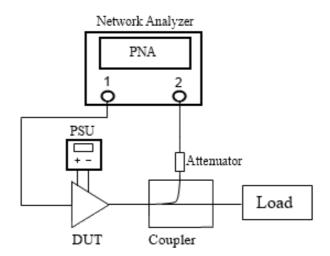

| 3.10 | Schematic for the small signal measurement setup.                              | 30        |

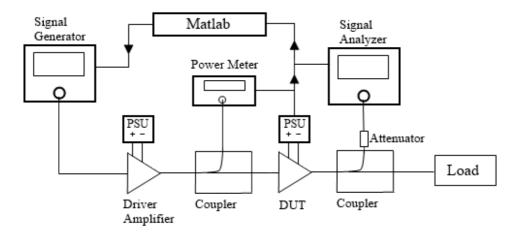

| 3.11 | Schematic for the large signal measurement setup                               | 31        |

|      |                                                                                | _         |

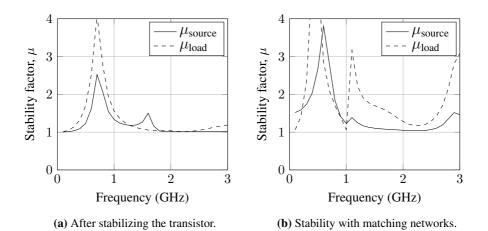

| 4.1  | Output power with lossless test benches                                        | 34        |

|      |                                                                                |           |

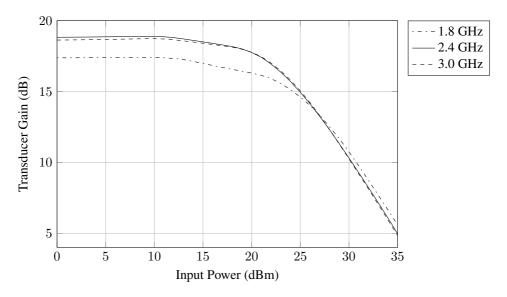

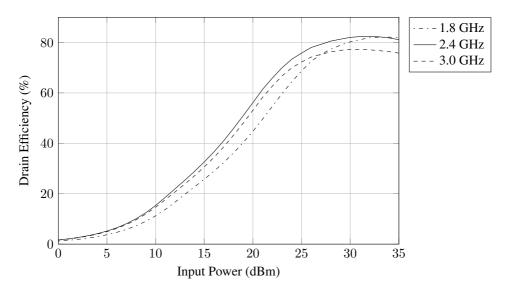

| 4.2  | Transducer power gain with lossless test benches.                                | 34 |

|------|----------------------------------------------------------------------------------|----|

| 4.3  | Drain efficiency with lossless test benches.                                     | 35 |

| 4.4  | Power added efficiency with lossless test benches.                               | 35 |

| 4.5  | Comparison of stability of the transistor and the stability of the final design. | 36 |

| 4.6  | Simulated small signal gain versus maximum available gain for the real-          |    |

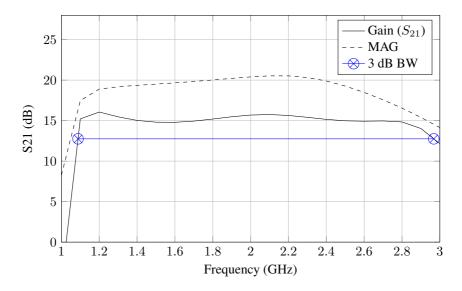

|      | ized matching networks.                                                          | 37 |

| 4.7  | Simulated output power of the final design.                                      | 37 |

| 4.8  | Simulated transducer power gain of the final design.                             | 38 |

| 4.9  | Simulated drain efficiency of the final design.                                  | 38 |

| 4.10 | Simulated power added efficiency of the final design.                            | 39 |

| 4.11 | Output power versus frequency at 1 dB compression.                               | 40 |

| 4.12 | Transducer power gain versus frequency at 1 dB compression                       | 40 |

|      | Drain efficiency versus frequency at 1 dB compression.                           | 41 |

| 4.14 | PAE versus frequency at 1 dB compression.                                        | 41 |

|      | Measured versus simulated small signal gain.                                     | 42 |

|      | Measured small signal gain for the two manufactured amplifiers                   | 43 |

| 4.17 | Measured gain with the 1 dB and 3 dB bandwidth indicated.                        | 43 |

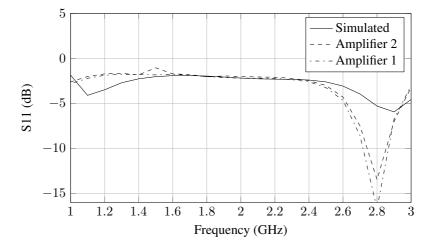

|      | Comparison of $S_{11}$ of the two manufactured amplifiers and the simulation.    | 44 |

| 4.19 | Comparison the output power of the driver and DUT versus frequency               | 45 |

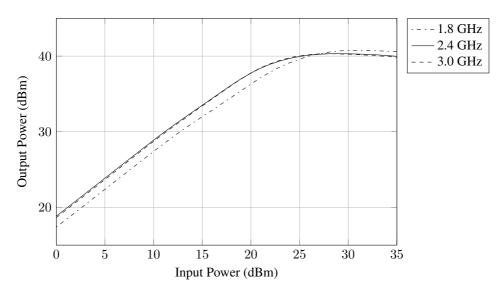

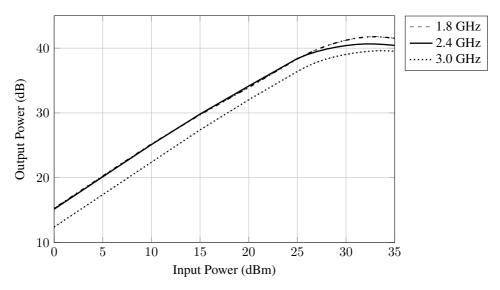

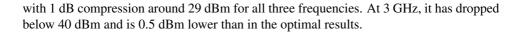

| 4.20 | Comparison of input power versus output power at different frequencies.          | 46 |

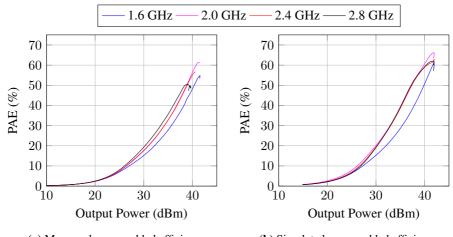

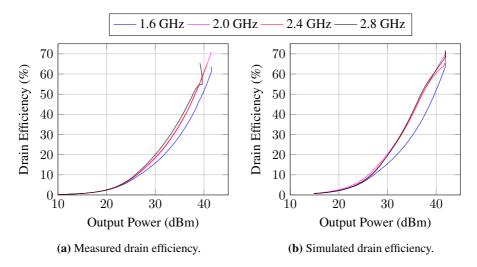

|      | Measures drain efficiency of the amplifier.                                      | 47 |

| 4.22 | PAE of the measured amplifier.                                                   | 47 |

| 4.23 | Measured transducer gain of the amplifier                                        | 48 |

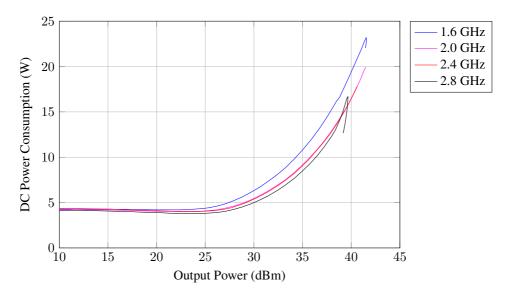

|      | DC power consumption of the measured amplifier.                                  | 48 |

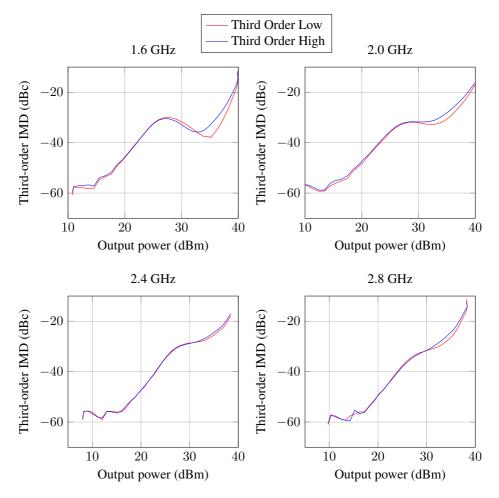

| 4.25 | Comparison of IMD at different frequencies                                       | 49 |

| 5.1  | Reflection $S_{11}$ of the measured amplifiers presenting a mismatch with sim-   |    |

|      | ulations                                                                         | 54 |

| 5.2  | Comparison of the measured and simulated power added efficiency                  | 55 |

| 5.3  | Comparison of the measured and simulated drain efficiency.                       | 55 |

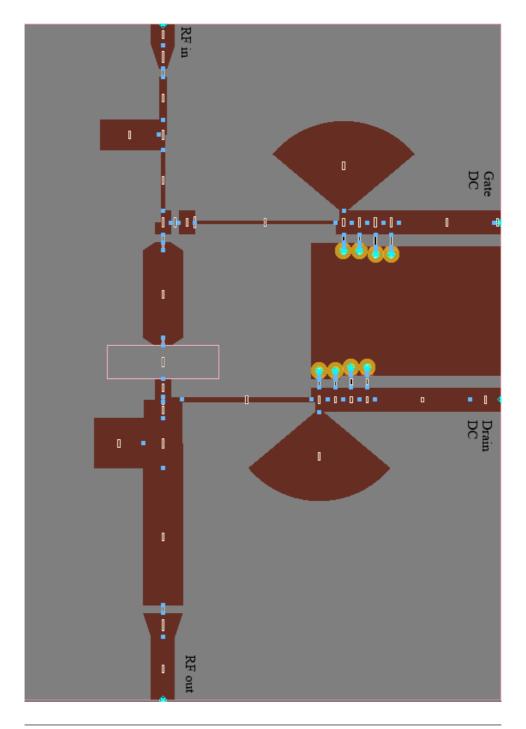

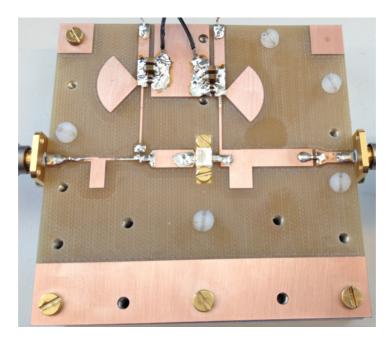

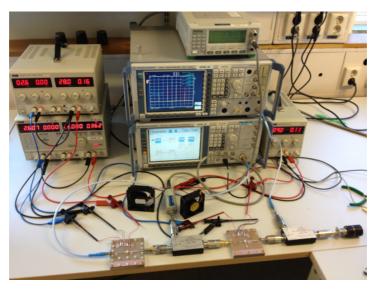

| D.1  | Finished PCB.                                                                    | v  |

| D.2  | Large signal and two tone measurement setup                                      | V  |

## List of Tables

| 1.1 | Specifications given in the assignment text for the thesis              | 2  |

|-----|-------------------------------------------------------------------------|----|

| 3.1 | FR4 Substrate Parameters.                                               | 20 |

| 3.2 | Optimization goal to match for maximum gain at the source matching net- |    |

|     | work                                                                    | 25 |

| 3.3 | Optimal impedances from load pull test bench simulations                | 26 |

| 3.4 | Optimization goals used when realizing the source matching network      | 27 |

| 3.5 | Overview of the small signal measurement equipment.                     | 30 |

| 3.6 | Overview of the large signal measurement equipment                      | 32 |

| 4.1 | Key parameters of the amplifier using the load pull test bench          | 36 |

| 4.2 | Key parameters of the simulated final design.                           | 39 |

| 4.3 | Key parameters of the amplifier measurements at 1 dB compression        | 50 |

## Abbreviations

| AM   | = | amplitude modulation              |

|------|---|-----------------------------------|

| ADS  | = | Advanced Design Systems           |

| DUT  | = | device under test                 |

| GaAs | = | Gallium Arsenide                  |

| GaN  | = | Gallium Nitride                   |

| GPIB | = | general purpose interface bus     |

| HB   | = | harmonic balance                  |

| HEMT | = | high electron mobility transistor |

| IMD  | = | intermodulation distortion        |

| MAG  | = | maximum available gain            |

| PA   | = | power amplifier                   |

| PAE  | = | power added efficiency            |

| PCB  | = | printed circuit board             |

| PM   | = | phase modulation                  |

| PNA  | = | programmable network analyzer     |

| RF   | = | radio frequency                   |

| RFPA | = | radio frequency power amplifier   |

| Si   | = | Silicon                           |

| SMA  | = | SubMiniature version A            |

| SMD  | = | surface mounted device            |

| SOLT | = | short-open-load-thru              |

| TRL  | = | thru-reflect-line                 |

| VNA  | = | vector network analyzer           |

|      |   |                                   |

# Chapter

## Introduction

The power amplifier (PA) is a critical component in a wireless communication system. It accounts for a significant portion of the costs in both development and production of radio equipment, making improved power amplifier architectures and design topologies desired in the industry. With later years rapid increase in the number of wireless communication systems, the already high linearity requirements the power amplifier must satisfy have become even tougher. In addition to linearity, requirements regarding power efficiency are also present for some applications. In portable devices it is the power amplifier that drains the battery the most, while in base station equipment the power amplifiers often require large and expensive cooling systems, increasing the running and total costs for the operator.

With the introduction of Gallium Nitride (GaN) high electron mobility transistors (HEMT) in the last decade, the problem of high efficiency operation seem to have a brighter future. The GaN HEMT technology provides some advantageous properties, such as increased power density, higher operating voltages, and improved thermal properties [6]. These properties combined allows for less complex designs, higher power efficiencies, and a reduced requirement for large cooling systems. A way to implement a design for high efficiency operation is to carry out load pull measurements to find the optimal operating conditions of the device.

To achieve high efficiency operation in power amplifiers, the transistor needs to be driven into nonlinear operation, which in turn will generate higher order harmonic frequency components in the output signal. The class-F amplifier is a reduced angle amplifier with load harmonic modulation control to shape the drain voltage in a way that it in theory does not overlap with drain current, thus greatly reducing the power dissipated in the amplifier which increases the efficiency. The theory on class-F operation is well explained by Cripps [1] and Raab [7].

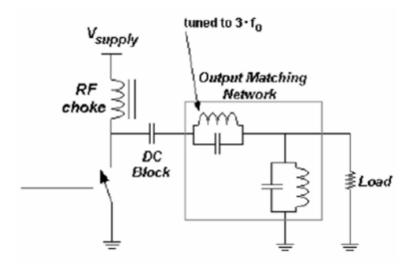

Design of a class-F amplifier involves matching network design at the fundamental frequency, and load harmonic tuning network design up to certain order harmonics. The common practice is to present a short circuit at the even order harmonics, and an open circuit at the odd order harmonic. In most cases only the second and third order harmonics are considered, since higher order harmonic control would lead to more complexity and possibly further loss [4].

In this thesis, the design of a class-F amplifier using a load pull test bench in microwave/RF CAD software will be performed. The load pull test bench will be used to find the optimal impedances, both for the source and load matching networks, to be realized using passive components and microstrip lines. This requires studying the principles of power amplifier classes F and  $F^{-1}$ , and design procedures of power amplifiers in CAD software Agilent ADS. The given specifications for the amplifiers are listed in table 1.1.

| Table 1.1: Specific | ations given in th | e assignment text for | the thesis. |

|---------------------|--------------------|-----------------------|-------------|

|---------------------|--------------------|-----------------------|-------------|

| Center frequency $(f_0)$ | 2.4 GHz                       |

|--------------------------|-------------------------------|

| Bandwidth (3 dB)         | 1.2 GHz                       |

| Output Power $(P_{out})$ | > 40 dBm within the bandwidth |

| Gain                     | > 12 dB within the bandwidth  |

| Input Match $(S_{11})$   | < -10 dB within the bandwidth |

| Efficiency               | as high as possible           |

# Chapter 2

### Theory

#### 2.1 S Parameters

The scattering matrix is a mathematical method that quantifies how RF energy propagates through a multi-port network. The S-matrix allows us to accurately describe the properties of very complex networks by viewing them as a simple box. For an RF signal incident on one port, some fraction of the signal is reflected, and some is scattered and exits other ports and some maybe lost to heat or radiation. The S-matrix for an N-port contains  $N^2$  coefficients called S-parameters, each one a complex value (magnitude and phase) representing a possible input-output path.

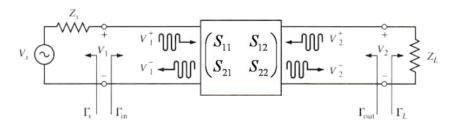

Figure 2.1: Generalized two-port network with source and load impedances. [4]

Figure 2.1 shows a generalized two-port network.  $S_{11}$  and  $S_{22}$  are the input/output reflection coefficients, while  $S_{12}$  and  $S_{21}$  are the forward/reverse voltage gain. If we assume that each port is terminated by an impedance  $Z_S = Z_L = Z_0$ , the network can be described as shown in equation 2.1 and 2.2. An expression for each of the parameters can be derived from these equations [4].

$$\begin{pmatrix} V_1^- \\ V_2^- \end{pmatrix} = \begin{pmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{pmatrix} \times \begin{pmatrix} V_1^+ \\ V_2^+ \end{pmatrix}$$

(2.1)

$$V_1^- = S_{11}V_1^+ + S_{12}V_2^+$$

$$V_2^- = S_{21}V_1^+ + S_{22}V_2^+$$

(2.2)

Figure 2.1 also displays the four reflection coefficients together with the two-port Sparameters. The reflection coefficient seen looking toward the load is

$$\Gamma_L = \frac{Z_L - Z_0}{Z_L + Z_0},$$

(2.3)

while the reflection coefficient looking toward the source is

$$\Gamma_S = \frac{Z_S - Z_0}{Z_S + Z_0},$$

(2.4)

where  $Z_0$  is the characteristic impedance reference for the s-parameters of the two-port network.  $\Gamma_{in}$  and  $\Gamma_{out}$  is the reflection seen from the matching networks looking toward the terminated network. With reference to figure 2.1 and equation 2.2 they are defined as

$$\Gamma_{in} = \frac{V_1^-}{V_1^+} = S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L} = \frac{Z_{in} - Z_0}{Z_{in} + Z_0},$$

(2.5)

and

$$\Gamma_{out} = \frac{V_2^-}{V_2^+} = S_{22} + \frac{S_{12}S_{21}\Gamma_S}{1 - S_{11}\Gamma_S} = \frac{Z_{out} - Z_0}{Z_{out} + Z_0},$$

(2.6)

S parameters are a vital instrument in understanding and designing RF circuits. It is used to describe gain, stability and matching. In CAD software the parameters are used in simulating small signal applications.

#### 2.1.1 Gain

Gain is defined as the amplifiers ability to increase the power or amplitude of a signal from the input to the output by adding energy to the signal from a power supply. For a power amplifier, there are three different definitions of gain, *Power Gain, Available Gain* and *Transducer Power Gain*.

Figure 2.2: A general transistor amplifier circuit. [4]

*Power Gain* is defined as the ratio of power dissipated in the load  $Z_L$  to the power delivered to the input of the two-port network and is not dependent on  $\Gamma_S$  [4]. It is defined as

$$G = \frac{P_L}{P_{in}} = \frac{|S_{21}|^2 (1 - |\Gamma_L|^2)}{(1 - |\Gamma_{in}|^2)|1 - S_{22}\Gamma_L|^2}.$$

(2.7)

Available Gain is defined as the ratio of the power available from the two-port network to the power available from the source. This assumes that both the source and load are conjugately matched and does not depend on  $\Gamma_L$  [4]. It is defined as

$$G_A = \frac{P_{avn}}{P_{avs}} = \frac{|S_{21}|^2 (1 - |\Gamma_S|^2)}{|1 - S_{11}\Gamma_S|^2 (1 - |\Gamma_{out}|^2)}.$$

(2.8)

*Transducer Power Gain* is defined as the ratio of the power delivered at the load to the power available from the source and is dependent on both source and load reflection coefficients [4]. Equation 2.9 shows the expression for the transducer power gain.

$$G_T = \frac{P_L}{P_{avs}} = \frac{|S_{21}|^2 (1 - |\Gamma_S|^2) (1 - |\Gamma_L|^2)}{|1 - \Gamma_S \Gamma_{in}|^2 |1 - S_{22} \Gamma_L|^2}$$

(2.9)

For a general transistor amplifier in figure 2.2 you can divide this expression into three parts.

$$G_S = \frac{1 - |\Gamma_S|^2}{|1 - \Gamma_S \Gamma_{in}|^2}$$

(2.10a)

$$G_0 = |S_{21}|^2 \tag{2.10b}$$

$$G_L = \frac{1 - |\Gamma_L|^2}{|1 - S_{22}\Gamma_L|^2}$$

(2.10c)

The three equations above show how the transducer power gain accounts for both source and load mismatch, as well as the transistor gain.

#### 2.1.2 Stability

Stability in an amplifier circuit is related to the risk of oscillations occurring at different frequencies. Oscillations can present in both large signal and small signal applications with varying effects, but are in both cases unwanted as it will cause problems in the amplifier. For a transistor amplifier circuit this can occur if either the input or output port impedance has a negative real part, i.e the reflection  $|\Gamma_{in}| > 1$  or  $|\Gamma_{out}| > 1$ . Since  $\Gamma_{in}$  and  $\Gamma_{out}$  depends on the source and load matching networks, the stability also depends on  $\Gamma_S$  and  $\Gamma_L$  from the matching networks. There are two main categories of stability, conditional and unconditional [4].

- Conditional stability: When the circuit presents a mismatch, making the stability condition  $|\Gamma_{in}| < 1$  and  $|\Gamma_{out}| < 1$  only valid for a certain range of load and source impedances. This condition is also referred to as potentially unstable.

- Unconditional stability: The stability condition  $|\Gamma_{in}| < 1$  and  $|\Gamma_{out}| < 1$  is valid for all passive source and load impedances (i.e  $|\Gamma_S| < 1$  and  $|\Gamma_L| < 1$ ) and the real part of the impedance is positive.

To determine if an amplifier circuit is stable, there are two tests used. One of these is the K- $\Delta$  test, where it can be shown that a device is unconditionally stable if "Rollet's Condition" is met. It is defined as

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{12}S_{21}|} > 1 , \qquad (2.11)$$

where

$$|\Delta| = |S_{11}S_{22} - S_{12}S_{21}| < 1.$$

(2.12)

If equations 2.11 and 2.12 are simultaneously satisfied, there is unconditional stability in the amplifier. It has to be regarded that since the source and load matching networks are generally frequency dependent, the stability has to be calculated for a wide frequency band to avoid oscillations. The K- $\Delta$  test has its shortcoming when it comes to comparing the relative stability of two or more devices because the magnitude of K does not indicate the margin of stability, just that it is stable. The other option is the  $\mu$  test. The advantage of this test is that it only dependent one parameter,  $\mu$ . It is defined as

$$\mu = \frac{1 - |S_{11}|^2}{|S_{22} - \Delta S_{11}^*| + |S_{12}S_{21}|} > 1$$

(2.13)

Where  $\mu > 1$  indicates unconditional stability. In addition, larger values of  $\mu$  implies a greater margin of stability [4].

#### 2.1.3 Matching

From equation 2.10 for a single stage amplifier we can se that if the source and load are matched to the characteristic impedance  $Z_0$ , the total gain of the amplifier would be the fixed gain of the transistor  $G_0 = |S_{21}|^2$ . So when designing an amplifier, the source and load matching,  $G_S$  and  $G_L$ , must be designed according to the application of the amplifier. For a power amplifier you want maximum gain in the source matching and maximum power transfer for the load matching.

With reference to figure 2.2, maximum gain and power transfer from the source matching network to the transistor will occur when the input impedance  $\Gamma_{in}$  seen by the transistor is conjugately matched with the impedance  $\Gamma_S$  from the source matching network.

$$\Gamma_{in} = \Gamma_S^* \tag{2.14}$$

For maximum power transfer at the output,  $\Gamma_L$  should be matched to provide as high  $P_{out}$  as possible.

$$\Gamma_{out} \Rightarrow max(P_{out}) \tag{2.15}$$

#### 2.2 **Power Amplifiers**

Power amplifiers (PA) are generally divided in two categories, linear and non-linear. Linear power amplifiers generate output power proportional to the input power, with a small amount of harmonics generated. Non-linear amplifiers operate near the cut-off region of the transistor which results in a large amount of harmonics generated together with the fundamental signal at the output. The result of the added harmonics is a non-linear relationship between the input power and output of the device.

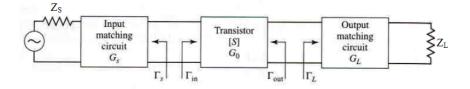

Figure 2.3: Comparison of different PA classes with respect to input signal overdrive and conduction angle. [8]

Linear and non-linear amplifiers can be further divided as biasing class and switching class. Linear class A, B, AB and C are classified based on their bias and conduction angle. The conduction angle is defined as the fraction of RF input drive signal where non-zero current is flowing through the device.

Switching amplifiers are implemented as high-efficiency PA's with true switching mode operation (class-D and E) at frequencies from VLF through lower VHF. The drain waveforms of these amplifiers are not sinusoidal, which means they will contain harmonics. Even class-B operation requires the presence of harmonics to produce the half-sinusoidal current waveforms. While the output network prevents the harmonics from reaching the load, it must allow their presence at its input. The harmonic frequency. If the output network does not permit any harmonic voltages or currents, only class-A operation which has low efficiency is possible. Chapter 2.2.3 and 2.2.4 will further explain the different classes of power amplifiers.

#### 2.2.1 Efficiency

The efficiency is one of the most important figure of merits describing the performance of a low-power amplifier and is often used in small signal amplifiers. Drain efficiency is defined as the ratio of the RF output power to the DC power dissipated in the amplifier.

$$\eta = \frac{P_{out}}{P_{DC}} \tag{2.16}$$

To increase efficiency, the amount of DC power consumed by the amplifier has to decrease while outputting the same amount of power. The power that is not converted to useful signal is dissipated as heat. Thus PA's that have low efficiency have high levels of heat dissipation, which is a limiting factor in many applications.

For large signal RF applications, the drain efficiency is no longer the most precise way to describe the efficiency. In this case equation 2.17 gives a more accurate description.

$$\eta_{\text{PAE}} = PAE = \frac{P_{out} - P_{in}}{P_{DC}} = \left(1 - \frac{1}{G}\right) \frac{P_{out}}{P_{DC}} = \left(1 - \frac{1}{G}\right)\eta \qquad (2.17)$$

Power Added Efficiency (PAE) takes into account the input RF power as it defines how efficiently the amplifier is able to convert DC power to RF power. The gain (G) in the equation above is the *power gain* of the amplifier.

#### 2.2.2 Linearity

Linearity in a RF amplifier can be described as the ability to increase the power level of an input signal without otherwise altering the content of the signal. The term linearity derives form an amplifier's linear relationship of input power to output power which, in an ideal amplifier, is directly related to the gain. One of the trade-offs in power amplifiers is between output power and bandwidth. Active devices are inherently limited in bandwidth by internal parasitic capacitance. That means that every transistor reaches a frequency at which signal gain drops to a point where it no longer useful as an amplifier. Smaller transistor geometries can lead to higher operating frequency, but this will result in a reduced current and power capacity.

To achieve good efficiency in an amplifier, linearity is the trade-off. When the amplifier is driven into compression it becomes nonlinear, which creates intermodulation distortion (IMD), also called harmonics, in the output signal. The IMD products that fall within the bandwidth of the signal will create distortion and have to be attenuated in the output network of the amplifier. A two-tone test is a common way to test linearity in amplifiers. A signal with two carriers (eq.2.18) is applied to the amplifier and can be described using the power series in equation 2.19. Note that the following equations assumes a weakly nonlinear amplifier, whose output and input voltage can be related using a standard power series [1].

$$v_{in}(t) = V_0(\cos\omega_1 t + \cos\omega_2 t) \tag{2.18}$$

$$v_{out} = a_0 + a_1 v_{in} + a_2 v_{in}^2 + a_3 v_{in}^3 + \dots$$

(2.19)

$$v_{out}(t) = a_0 + a_1 V_0 (\cos \omega_1 t + \cos \omega_2 t) + a_2 V_0^2 (\cos \omega_1 t + \cos \omega_2 t)^2 + a_3 V_0^3 (\cos \omega_1 t + \cos \omega_2 t)^3 + \dots$$

(2.20)

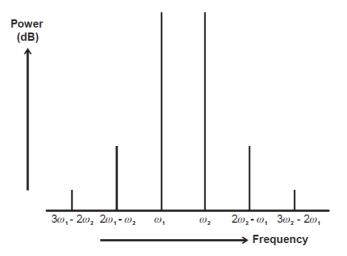

The resulting series in equation 2.20 shows the three first degrees of distortion. Each degree generates a number of distortion products, which have either the same or lower orders. The even order distortion terms will be well outside the band of the signal and are off less importance than the odd order products. Figure 2.4 illustrates that the products of most interest are the intermodulation products in the band because of their potentially disruptive effect on the signal. The third order products at frequencies  $2\omega_1 - \omega_2$  and  $2\omega_2 - \omega_1$  with amplitudes of  $a_2 \cdot V_0^2 = \frac{3}{4}$  also has a contribution of amplitude  $a_5 \cdot V_0^5 = \frac{25}{8}$  from the fifth degree term. The other large product comes from the fifth degree terms at  $3\omega_1 - 2\omega_2$  and  $3\omega_2 - 2\omega_1$  with amplitude  $a_5 \cdot V_0^5 = \frac{5}{8}$ . These products become dominant when the amplifier is operating in the compression or saturation region [1].

Figure 2.4: Two-tone intermodulation spectrum. [1]

The intermodulation product are dependent on frequency. The fifth order products is not affected by the third order nonlinearities, but the third order products are functions of both third- and fifth order (and higher) terms. This means that at low signal amplitudes, where the fifth order products can be neglected, the amplitude of the third order product is proportional to the third order term  $a_2 \cdot V_0^2$  of the input amplitude. With larger amplitudes, the fifth order products will be a factor and increase the third order product. Since it is difficult to change the amount of nonlinearities, distortion is most effectively minimized by optimizing the impedances seen by the distortion current sources.

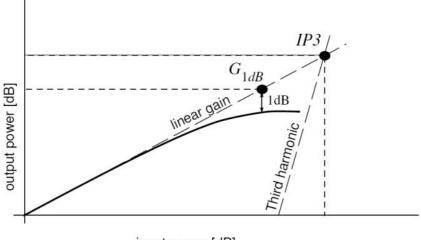

In all power amplifiers, the output level is a "compressive" or "saturating" function of the input level. The gain of the PA approaches zero for sufficiently high input levels. In RF circuits this effect is quantified by the 1 dB compression point, defined as the input signal level that causes the small-signal gain to drop by 1 dB. Figure 2.5 shows the 1 dB compression point as well as the third order intercept point, which is a fictitious point where the linear gain meets the linear line of the third order harmonic.

input power [dB]

Figure 2.5: 1 dB compression point and third order intercept point (IP3) in log scale. [1]

#### 2.2.3 Amplifiers Classes

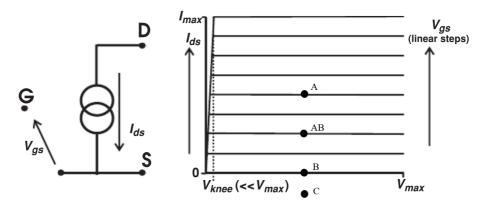

The different biasing points of the classes of power amplifiers are displayed using I-V characteristics in figure 2.6.

Figure 2.6: I-V characteristic showing the bias point of different PA classes. [14]

*Class-A* is a linear amplifier in the biasing class. The biasing point is in the middle of active region, ideally at  $\frac{1}{2}V_{max}$  and  $\frac{1}{2}I_{max}$ . The conduction angle is 360° which means that the transistor is turned on and conducting during the entire sinusoidal cycle. The class-A amplifier is most commonly used in small signal operation because of its simplicity and linear qualities. The maximum theoretical drain efficiency is 50% and is the lowest of the power amplifier classes. The low efficiency makes it unsuitable for high power applications as the high amount of power dissipated in the amplifier would generate too much heat.

*Class-AB* is a compromise between class-A and B in terms of efficiency and linearity. It is biased in the region between class-A and B and the conduction angle is  $180^{\circ}$ -  $360^{\circ}$  with a theoretical drain efficiency is between 50% - 78.5%. Conventional class-AB operation creates odd harmonics in the process of improving efficiency. Theoretically to increases efficiency all the way up to 78.5%, the device shall generate only even order harmonics as it will not create undesirable close-to-carrier intermodulation distortion.

*Class-B* operation is also determined by the biasing point, which is close to the cut-off region of the transistor. The conduction angle is  $180^{\circ}$  which means that conducts a half cycle of the input signal. The theoretical drain efficiency is 78.5% and much better than class-A. However, since the transistor generates higher order harmonics near cut-off the linearity is not good. Linearity can be improved by either using two transistors in a push-pull configuration or by controlling the harmonics using resonators.

*Class-C* is biased below the cut-off region with a conduction angle less than 180°. The transistor is biased such that under steady-state conditions no drain current flows. In order to survive class-C operation, the transistor should have a drain voltage breakdown that is at least three times the active devices own DC voltage supply. For this reason true class-C operation is not often used in solid-state at higher RF and microwave frequencies.

#### 2.2.4 Class-F Amplifier

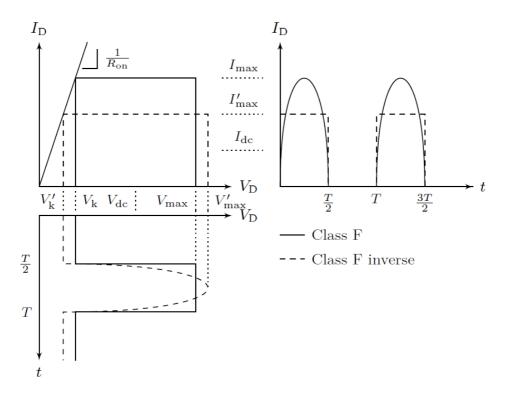

Class-F and  $F^{-1}$  amplifiers use harmonic tuning on the amplified signal (fig.2.7) to control the harmonic content of the drain-voltage or current-drain waveforms. The drain voltage waveform includes odd harmonics and approximates a square wave, while the drain current waveform includes even harmonics and approximates a half sine wave (fig.2.8). The harmonics contribute to flatten the waveforms which allows he majority of the drain current to flow when the drain voltage is low, reducing the power dissipation. Ideally, this leads to a power efficiency of 100% as these waveforms do not overlap at all, but since only a finite number of harmonics can be used in the generation of the waveforms, there will be some overlap between the current and voltage waveforms, and the power efficiency will decrease. In practical realization of microwave/RF class-F, normally only the first three harmonics are considered, as tuning higher harmonics does not yield a significant improvement in efficiency compared to the complexity of implementing it.

Figure 2.7: Resonators at the output to control the odd and even harmonics. [8]

Inverse class-F  $(F^{-1})$  is tuned to be short at odd harmonics and open at even harmonics which means that the drain current includes odd harmonics and approximates a square wave, and the drain voltage contains even harmonics and approximates a half sine-wave. It is important that the fundamental and second harmonic drain voltage is in-phase in order to properly shape the voltage waveform.

The efficiency of an ideal PA increased from 50% (Class-A) up to an ideal 100% depending on the amount of harmonics that can be controlled. In contrast to class-C, which also has a theoretical efficiency of 100%, the output power capability is also increased. Class-F is is one of the oldest techniques for improving efficiency of an RF PA, yet is still perhaps one of the least understood methods.

The ideal time domain current and voltage waveforms for class-F and  $F^{-1}$  are presented in figure 2.8.  $V_k$  denotes the knee voltage,  $V_{dc}$  the drain voltage bias and  $I_c$  the DC current and inverse class-F parameters are denoted with a prime (ex.  $I'_D$ ). The waveforms can be analyzed using their Fourier series expansion and for a class-F amplifier waveforms, which include the effect of the on-state resistance are given by [16]

$$I_D(\theta) = I_{max} \left[ \frac{1}{\pi} + \frac{1}{2} sin(\theta) - \frac{2}{\pi} \sum_{n=1}^{\infty} \frac{cos(2n\theta)}{4n^2 - 1} \right] \quad [A],$$

(2.21)

$$V_D(\theta) = V_{dc} - \frac{4(V_{dc} - V_k)}{\pi} \sum_{n=1}^{\infty} \frac{\sin((2n-1)\theta)}{2n-1} \quad [V],$$

(2.22)

where  $\theta = \omega t$  and  $\omega$  is the fundamental frequency of the desired output. For a class-F<sup>-1</sup> power amplifier, the Fourier series expansion of the waveforms are given by

$$I'_{D}(\theta) = \frac{I'_{max}}{2} \left[ 1 + \frac{4}{\pi} \sum_{n=1}^{\infty} \frac{\sin((2n-1)\theta)}{2n-1} \right] \ [A],$$

(2.23)

$$V_D'(\theta) = V_k' + (V_{max}' - V_k') \left(\frac{1}{\pi} - \frac{1}{2}sin(\theta) + \frac{2}{\pi}\sum_{n=1}^{\infty} \frac{cos(2n\theta)}{4n^2 - 1}\right) \quad [V],$$

(2.24)

where

$$V'_{max} = \pi V_{dc} - (\pi - 1)V'_k.$$

(2.25)

Using these equations, expressions for the output properties of each class (power efficiency, fundamental output power, etc) can be derived. In [16], equations are derived for the power efficiency, output power, and the load resistance, all as a function of the on–state resistance. The results show how the class- $F^{-1}$  mode amplifier outperforms the class-F mode amplifier with increasing on–state resistance.

#### 2.2.5 Load and Source Pull

Load/source pull consists of varying or "pulling" the load or source impedance seen by a device while measuring the performance. They are used to measure a device in actual operating conditions. This method is important for large signal, nonlinear devices where the operating point may change with power level or tuning. Load pull is not usually needed for linear devices, where performance with any load can be predicted from small signal S parameters [1].

The load pull systems is used to find optimum loading conditions experimentally, while physically changing load reflection coefficient  $\Gamma_L$  for the extraction of design parameters, such as output power, the DC to RF power conversion efficiency, the operating power gain, gain compression and the power added efficiency for transistor devices. It can thus be concluded that the load pull system or technique allow the analysis of active device performance under varying loading conditions and leading to the design of matching circuits [1].

#### 2.3 GaN Transistor Technology

Power amplifiers using Gallium Nitride (GaN) transistors are an active area of research. The performance of these transistors can be represented in terms of some important properties such as electron mobility, hole mobility, band gap and thermal conductivity. GaN has a wider band gap and a higher thermal conductivity than both Silicon (Si) and Gallium Arsenide (GaAs). These properties provides a relatively high power density, which has been shown to be one order of magnitude greater than its counterparts in Gallium Arsenide (GaAs) and Silicon (Si) [15]. Hence, for the same output power, a ten-time reduction of the size of the device can be realized using GaN HEMT technology.

A wider band gap allows the device to have a higher operating temperature and lower vulnerability to external noise such as shot noise because it requires more energy for the electrons to escape from the valence band to the conduction band. A wider band gap also provides a higher breakdown voltage and higher power density so that the transistor is able to output higher power in smaller physical size [6]. Over the last decade, GaN HEMTs have become more and more popular for microwave applications, and especially in base stations, where the properties of the GaN technology can be utilized to their full potential.

The 10W Cree GaN transistor used in this project operates at 28 V and up to 48 V. The higher efficiency that results from this high operating voltage reduces power requirements and simplifies cooling, an important advantage, since cost and weight of cooling systems is a significant fraction of the cost of a high power microwave transmitter.

#### 2.4 Agilent ADS

All the simulations were performed in Agilent Technologies simulation software Advanced Systems Design (ADS). Agilent ADS supports every step of the design process,

from schematic capture, layout, frequency-domain and time-domain circuit simulation, and electromagnetic field simulation. This allows the user to fully characterize and optimize a complete RF design within the same design tool. For small signal simulations a predefined design guide which simulates the s parameters, noise figure, stability, and group delay of any two-port network versus frequency.

#### 2.4.1 Large Signal Simulations

The large-signal simulations are performed in ADS using a method called "Harmonic Balance". Harmonic balance is a frequency-domain analysis technique for simulating nonlinear circuits and systems. It is well-suited for simulating analog RF and microwave circuits, since these are most naturally handled in the frequency domain. Harmonic balance simulation calculates the magnitude and phase of voltages or currents in a potentially nonlinear circuit which makes it possible to simulate circuits with multiple input frequencies. This includes intermodulation frequencies, harmonics, and frequency conversion between harmonics. Not only can the circuit itself produce harmonics, but each signal source can also produce harmonics or small signal sidebands. Designers are usually most interested in a systems steady-state behavior. Many high-frequency circuits contain long time constants that require conventional transient methods to integrate over many periods of the lowestfrequency sinusoid to reach steady state. Harmonic balance, on the other hand, captures the steady-state spectral response directly [9].

#### 2.4.2 Optimization Algorithms

The optimization algorithms used in Agilent ADS uses the least squares error function to calculate the error. The least-squares error function is calculated by evaluating the error for each specified goal at each frequency or power point individually. The magnitudes of these errors are then squared, and the squared magnitudes are then averaged over frequency or power. The three types of algorithms used were "Random", "Gradient" and Quasi-Newton".

The Random optimizer arrives at new parameter values by using a random-number generator by picking a number at random within a range. Starting from an initial set of parameter values for which the error function is known, a new set of values is obtained by perturbing each of the initial values, and the error function is re-evaluated. Then the error function is re-evaluated by reversing the algebraic sign of each parameter value perturbation. These two values, corresponding to positive and negative perturbations, are compared to the value at the initial point. If either value is less than the initial value, then the set of parameter values for which the error function has its least value becomes the initial point for the next iteration. If neither value is less than the initial value, then the initial point remains the same for the next iteration. Since random search uses a pseudo-random generator, the results can be different for two optimization procedures [10].

The Gradient optimizer arrives at new parameter values using the gradient information of the networks error function. The gradient of the error function indicates the direction to move a set of parameter values in order to reduce the error function. For each iteration, the error function and its gradient is evaluated at the initial point. Then the set of parameter values is moved in that direction until the error function is minimized. A single iteration usually includes many function evaluations and therefore, an iteration in the gradient search method takes much longer than the random search method [10].

The Quasi-Newton optimizer uses the second-order derivatives of the error function and the gradient to find a descending direction. The second-order derivatives are estimated by the Davidson-Fletcher-Powell (DFP) formula or its complement. Appropriately combined with the gradient, this information is used to find a direction and an inexact line-search is conducted. Much like the optimizers using the gradient search method, an iteration in the optimizers using the Quasi-Newton search method consists of many function evaluations. Therefore, a single iteration using the Quasi-Newton search method takes longer than an iteration in the optimizers using the Random search method [10].

#### 2.4.3 Load-Pull Test Bench

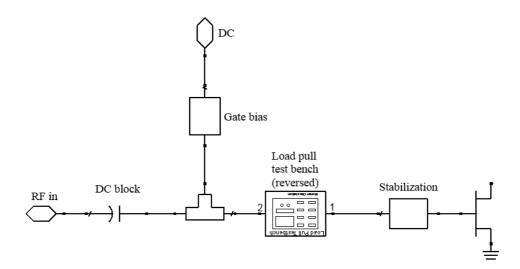

Figure 2.9: Load pull test bench block used in the simulations.

To tune the impedance at  $f_0$  and the harmonics at  $2f_0$  and  $3f_0$ , the load pull block in figure 2.9 was used in ADS. It is a load pull test bench made by Morten Olavsbråten, which allows the user to tune the impedances at  $f_0$ ,  $2f_0$  and  $3f_0$  individually without affecting each other. In normal load-pull techniques, these impedances are dependent of each other which makes tuning more complex. The test bench will interpolate between the frequencies specified and the harmonics, either using linear or cosinus interpolation. The user specifies the fundamental frequency, bandwidth of the baseband, and the reflection coefficients magnitude and phase for baseband,  $f_0$ ,  $2f_0$  and  $3f_0$ . It is designed to find the impedance at port 1 and should be placed at the drain of the transistor so that this impedance translates to  $\Gamma_L$  in a two-port network. The next step is to manually tune the values of the reflection coefficients while looking at the simulation of PAE, output power and transducer gain. The fundamental frequency  $f_0$  is tuned to achieve maximum output power, while  $2f_0$  and  $3f_0$  is tuned to achieve high efficiency (PAE).

#### 2.5 Measurements

The following section briefly presents measurement methods and uncertainties related to them.

#### 2.5.1 Network Analyzer

To measure the s-parameters of a device, a vector network analyzer (VNA) is used. This type of network analyzer consists of a sweep oscillator, a test set which includes two ports, a control panel, an information display and RF cables connected to the DUT. Each port of the test set includes dual directional couplers and a complex ratio measuring device.

Only perfect test equipment does not require some kind of correction. Imperfections exist in even the finest test equipment and cause less than ideal measurement results. Some of the factors that contribute to measurement errors are repeatable and predictable over time and temperature and can be removed, while others are random and cannot be removed. All measurement systems, including those employing network analyzers, can be affected by three types of measurement errors [11]:

- **Systematic errors:** Caused by imperfections in the test equipment and test setup. If these errors do not vary over time, they can be characterized through calibration and mathematically removed during the measurement process. Errors are typically caused by signal leakage, signal reflections, and frequency response.

- **Random errors:** Varies randomly as a function of time. Since they are not predictable, they cannot be removed by calibration. The main contributors to random errors are instrument noise and switch/connector repeatability.

- **Drift errors:** Occurs when a test systems performance changes after a calibration has been performed. They are primarily caused by temperature variation and can be removed by additional calibration and by having the test equipment in an environment with controlled temperature.

#### 2.5.2 Calibration

There are two basic types of calibration used to correct for systematic errors. The two types are SOLT (*short, open, load, thru*) and TRL (*thru, reflect, line*). The differences in the calibrations are related to the types of calibration standards they use and how these standards are defined. They each have their advantages, depending on frequency range and application.

SOLT calibration is the most widely used choice for coaxial measurements. *Short, open* and *load* calibration consists of two one-port impedance calibrations, while *thru* provides forward and reverse transmission and reflection measurements. It is easy to perform and is used in a broad variety of environments. It provides broadband calibrations, essentially from DC to the upper frequency limit of the connector type being used.

TRL calibration was developed for making accurate measurements of non-coaxial devices at microwave and millimeter-wave frequencies. It is commonly used for in-fixture and on-wafer environments.

#### 2.5.3 Measuring Power Amplifiers

With DUTs such as power amplifiers, the output power of the DUT may exceed the linear input range of the VNA. As an example, an amplifier has an output power of 20 W is measured on a VNA that has a limit of 0.2W at the test input port. Then a 20 dB attenuator between the amplifier output and test port 2 should be sufficient to prevent any overdrive, but using an attenuator creates a source of error. The reflection measurements will be affected as the signal passes the attenuator up to 3 times for a measurement. The attenuation in it self is removed in calibration, but every time the signal is attenuated it approaches the noise floor in the VNA which makes the measurement of  $S_{12}$  and  $S_{22}$  noise affected. By setting the analyzer to average the measurements by a high factor the results may be usable, but the process will become very time consuming [14].

#### 2.5.4 Two-Carrier Characterization

The two-carrier, or two-tone test is a convenient method of generating an amplitudemodulated carrier with essentially no distortion. Any attempt to create AM using some form of modulator runs into the problem that the signal will have distortion due to the nonlinearity of the modulator. In modern communications applications, the two-carrier test has been largely replaced by tests using the actual modulation system in use. This kind of testing is essential, both during development and in production, for determining specification compliance on a product and characterizing the amplifier.

Asymmetries in the amplitudes of upper and lower intermodulation distortion (IMD) products of power amplifiers are found when performing a two-tone test. This means that the IMD at  $2\omega_2 - \omega_1$  is different from the one at  $2\omega_1 - \omega_2$ . This type of asymmetry can create false results when measuring intermodulation ratios (IMR), third order intercept point (IP3) or other type of distortion figures of merit.

# Chapter 3

## Design

This chapter presents the design process and technology used in the amplifier. The technology used in simulations and on the PCB is presented with the key parts of the design following. The last section describes how the measurements were performed with a detailed overview of the setup.

#### 3.1 Design Technology

In this section, the design technology used in the simulations and on the PCB is presented. This includes a short overview of the transistor, the capacitors and resistors, and the substrate used.

#### 3.1.1 Transistor

The 10 W Cree CGH40010 transistor is an unmatched, gallium nitride (GaN) high electron mobility transistor (HEMT). It operates from a 28 volt rail, and offers a general purpose, broadband solution to a variety of RF and microwave applications. GaN HEMT offers high efficiency, high gain and wide bandwidth capabilities making the transistor ideal for both linear and nonlinear amplifier circuits.

#### 3.1.2 Passive components

Johanson Technology surface mounted (SMD) capacitors are used in the amplifier. The Multi-Layer High-Q gives an ultra-high Q performance, and exhibit NP0 temperature characteristics. NP0 refers to the shape of the capacitors temperature coefficient graph which is how capacitance changes with temperature. NP0 means that the graph is flat and the device is not affected by temperature changes. The size of the capacitors used is 1608 mm and has a rated maximum voltage of 250 VDC.

Murata SMD capacitors is used as DC-blocks and in the bias networks. They are general purpose ceramic capacitors with high dielectric constant type in a smaller size with a

higher capacitance value. The size of the capacitors used is 1608 and 3216 mm and has a rated maximum voltage of 50 VDC.

The resistors used were basic 1608 mm SMD following the E12 series where each succeeding resistor falls within the +/-10% of the previous value resulting in 12 values in logarithmic steps per decade.

#### 3.1.3 Substrate

The substrate used for the amplifier is FR-4 which is a composite material composed of woven fiberglass cloth with an epoxy resin binder that is flame resistant. FR-4 glass epoxy is a popular and versatile high-pressure thermoset plastic laminate grade with good strength to weight ratios. With near zero water absorption, FR-4 is most commonly used as an electrical insulator possessing considerable mechanical strength. The material is known to retain its high mechanical values and electrical insulating qualities in both dry and humid conditions. These attributes, along with good fabrication characteristics, lend utility to this grade for a wide variety of electrical and mechanical applications. The parameters used in the ADS simulations are shown in table 3.1.

Table 3.1: FR4 Substrate Parameters.

| Н                      | Er  | Mur | Cond              | Т                     | $tan(\delta)$ |

|------------------------|-----|-----|-------------------|-----------------------|---------------|

| $1.6\times 10^{-3}\;m$ | 4.4 | 1.0 | $5.96\times 10^7$ | $36 \times 10^{-6} m$ | 0.02          |

#### **3.2 DC-Bias operating point**

The quiescent operating point of a class-F amplifier must be close to the cutoff region in order to generate significant amounts of harmonics. The class-F amplifier is usually biased around a class-B or AB amplifier, which naturally causes the drain waveforms to be similar. The difference is that because of the harmonic control in class-F, it has a larger voltage swing and the same clipping of the drain current.

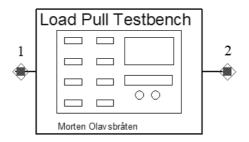

From the documentation of Cree's ADS model for the CGH40010 transistor [12], the valid range of gate voltage  $V_{GS}$  is from -1.5 V to -3 V and the pinch-off voltage is at -2.9 V. The valid range of drain voltage  $V_{DD}$  is from 28 V to 48 V. To find the operating point, a IV-Curve design guide for FET transistors available in ADS was used. The gate voltage  $V_{GS}$  was set to sweep from -1.5 V to -3 V and the drain voltage  $V_{DD}$  from 0 V to 48 V. The result of the simulation is presented in figure 3.1.

Figure 3.1: I-V characteristics of the Cree CGH40010 transistor with bias point and maximum current indicated.

The drain voltage was set to be 28 V and from the IV-characteristic a bias point at marker "Bias" was set. The result is an quiescent operating point at gate voltage  $V_{GS} = -2.8 V$  with resulting drain current  $I_{DS} = 163 mA$ . As seen from figure 3.1 the chosen bias point will result in a voltage swing from 28 V to 5 V with a maximum current of  $I_{DS_{max}} = 1.049 A$ .

## 3.3 Small Signal Design

S-parameter simulations are essential in characterizing the performance parameters of an amplifier, so the basic design of the circuit are characterized by using small signal simulations.

#### 3.3.1 Bias Network

With a chosen operating point, a basic design can be set up to stabilize and match the input of the transistor for maximum gain. The first step is to design the drain and gate bias networks. In an amplifier it is very important that the bias networks are designed to avoid leakage of RF signal into the bias network or unwanted DC components into the output signal which can cause oscillations. The main concern for this is in the drain bias because of the large amount of DC voltage applied. When looking from the circuit into the bias network you wish to see infinite impedance at the fundamental frequency, limiting the chance of leakage drastically.

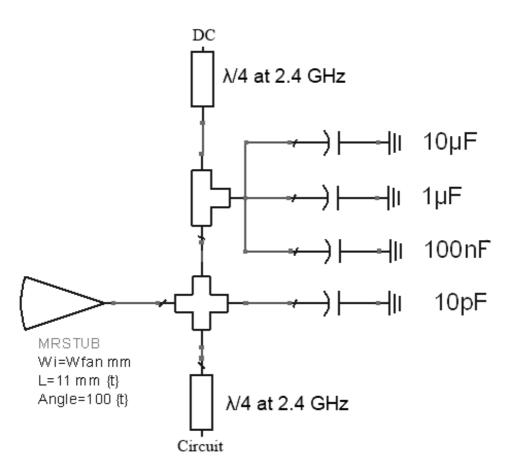

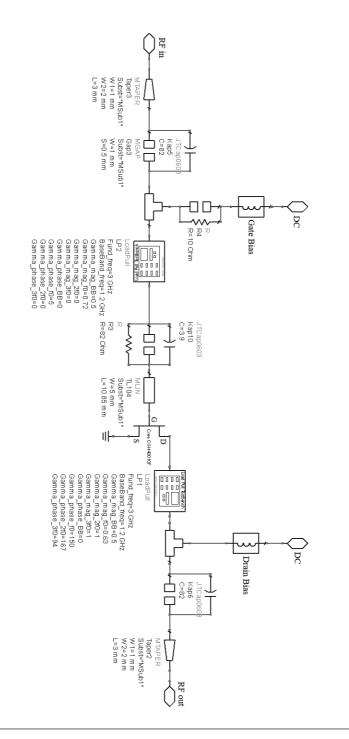

Figure 3.2: Bias network schematic.

Figure 3.2 shows the bias network at the drain of the amplifier. It is designed so that looking from the circuit you see infinite impedance, and at the base of the fan it sees a short circuit at the fundamental frequency.

The gate bias network is identical except for a resistor on the output to the circuit is added as recommended by Cree in the data sheet for the transistor [13] to help with stabilization. The capacitors at the base af the fan will help to suppress any RF signal from getting into the DC supply while providing high impedance at the drain/gate in order to maintain optimal in-band RF gain.

Figure 3.3: Attenuation of the RF signal to prevent leakage to the DC source.

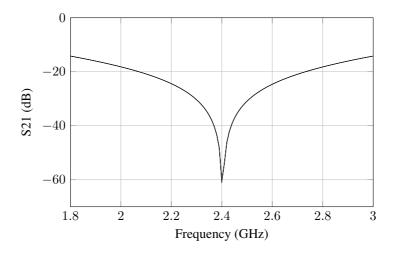

Figure 3.3 shows the attenuation through the bias from circuit to DC source. It is designed so that the maximum attenuation is at the center frequency with as high as possible attenuation towards the edges of the frequency band. This will prevent the RF signal from leaking into the DC source.

Figure 3.4: Simulated reflection

In figure 3.4, the reflection of the RF signal from the circuit is presented. The reflection should be as high as possible so the RF signal is prevented from leaking into the DC supply. Full reflection is when  $\Gamma = 1$  (0 dB).

#### 3.3.2 Stabilization

For stabilization at the gate of the transistor, a series-parallel RC network was inserted at the gate of the transistor along with a resistor at the base of the gate bias network (see appendix A). This is called a frequency selective method of stabilizing as this network will introduce loss at low frequencies ( $f < \frac{1}{BC}$ ).

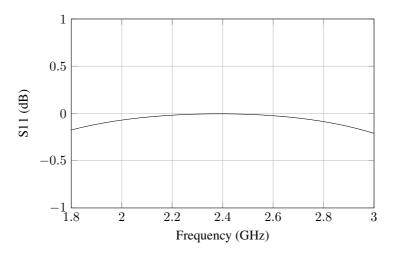

Figure 3.5: Simulated stability factor  $\mu$  before and after stabilization.

Figure 3.5b shows that the circuit meets the criteria of the  $\mu$ -test described in chapter 2.1.2 which states that  $\mu > 1$  indicates unconditional stability. The stability factor is very close to the limit from 2 - 3 GHz in  $\mu_{load}$  and does not indicate a good margin of stability. When inserting the matching networks, the margin is expected to improve.

#### 3.3.3 Matching Networks

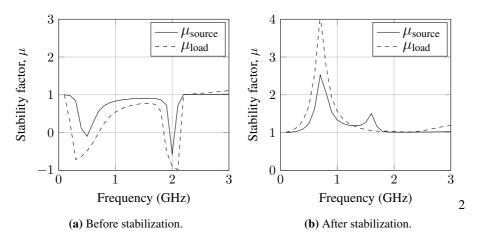

The first approach to designing the source matching network was a combination of microstrip lines and stubs to keep the network gain flat over the bandwidth and then inserting the load pull test bench presented in chapter 2.4.3 at the drain of the transistor to find the optimal load impedances. When tuning the impedances of the load matching network, the optimal impedance at the source will change slightly, creating the need to adjust the source matching impedance to achieve the best possible result. This was solved by inserting the test bench at the source instead of a realized network. The test bench had to be reversed so that port 1 is facing the transistor gate (fig.3.6). This created the possibility to do both load and source pull on  $\Gamma_S$  and  $\Gamma_L$  simultaneously to more efficiently find the optimal impedances.

Figure 3.6: Using the test bench reversed to find optimal impedances for the source matching network.

Figure 3.6 shows the test bench inserted before the stabilization network. The source test bench was optimized for maximum gain where  $\Gamma_{in} = \Gamma_S^*$ . The goals in table 3.2 were set to achieve this, where stability was set as the highest priority.

Table 3.2: Optimization goal to match for maximum gain at the source matching network.

|                             | Goal                  | Frequency range |

|-----------------------------|-----------------------|-----------------|

| Gain $(S_{21})$             | $\geq 15~\mathrm{dB}$ | 1.8-3 GHz       |

| Stability                   | > 1                   | 0.1-3 GHz       |

| Input Reflection $(S_{11})$ | $< -10 \ \mathrm{dB}$ | 1.8-3 GHz       |

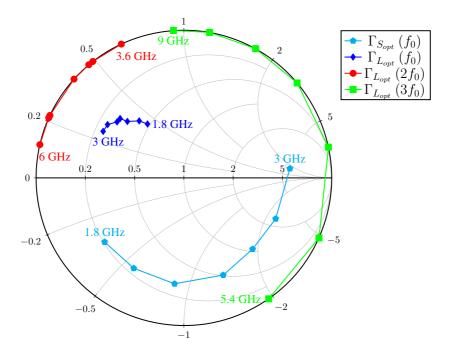

After obtaining a satisfying small signal results from the source test bench, the load test bench was inserted at the drain and the circuit could be further optimized using large signal harmonic balance simulations. Since the impedances found at the source should be the most optimal for the transistor, they were allowed only to move  $\pm 5\%$  in the optimization since it is expected that they will need to change a little as the load impedances changes. The test benches were set to tune  $\Gamma_S(f_0)$  and  $\Gamma_L(f_0)$  with optimization goals that will maximize gain and output power. With the fundamental frequency tuned to optimal impedances, the harmonics  $\Gamma_L(2f_0)$  and  $\Gamma_L(3f_0)$  were tuned to maximize PAE. These simulations were done for the bandwidth frequencies from 1.8 - 3 GHz with 200 MHz steps. The result are presented in table 3.3.

|           | Source                    |                           | Load                             |                                    |

|-----------|---------------------------|---------------------------|----------------------------------|------------------------------------|

| Frequency | $\Gamma_{opt}(f_0)$       | $\Gamma_{opt}(f_0)$       | $\Gamma_{opt} \left(2f_0\right)$ | $\Gamma_{opt} \left( 3f_0 \right)$ |

| 1.8 GHz   | $0.69\angle -141^{\circ}$ | $0.44\angle 124^{\circ}$  | 1∠115°                           | $1\angle -55^{\circ}$              |

| 2.0 GHz   | $0.7\angle -119^{\circ}$  | $0.49\angle 128^{\circ}$  | $1 \angle 128^{\circ}$           | $1\angle -24^{\circ}$              |

| 2.2 GHz   | $0.72\angle -95^{\circ}$  | $0.54\angle 135^{\circ}$  | 1∠130°                           | $1 \angle 12^{\circ}$              |

| 2.4 GHz   | $0.71\angle-68^{\circ}$   | $0.59 \angle 137^{\circ}$ | $1 \angle 138^{\circ}$           | $1 \angle 40^{\circ}$              |

| 2.6 GHz   | $0.67\angle-46^\circ$     | $0.59 \angle 140^{\circ}$ | $1 \angle 155^{\circ}$           | $1\angle 61^{\circ}$               |

| 2.8 GHz   | $0.68\angle -24^{\circ}$  | $0.63 \angle 145^{\circ}$ | $1 \angle 156^{\circ}$           | 1∠180°                             |

| 3.0 GHz   | $0.72\angle 5^{\circ}$    | $0.63\angle 150^{\circ}$  | $1\angle 167^{\circ}$            | $1\angle 94^{\circ}$               |

Table 3.3: Optimal impedances from load pull test bench simulations.

A representation of the impedances in table 3.3 are plotted in a Smith chart in figure 3.7. Both source and load impedances move counterclockwise with increasing frequency in the Smith chart. This is in theory impossible, but can be solved by either moving clockwise in loops or with a negative transmission line. The complexity of trying to implement negative transmission lines, which require a large network of capacitors and inductors, was decided as not necessary as the looping method is a better solution in this assignment.

Figure 3.7: Optimal source impedances for source and load matching networks with increasing frequency moving counterclockwise.

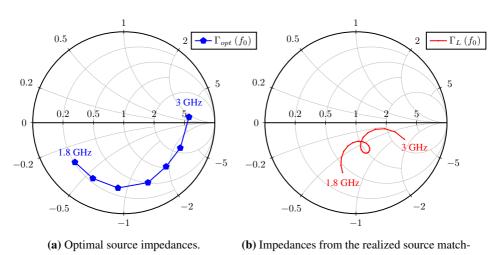

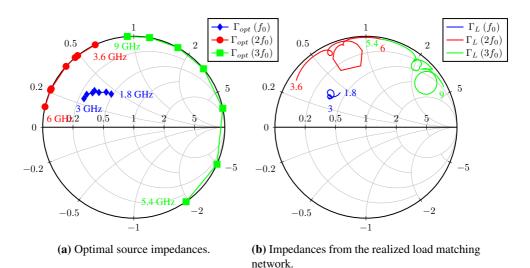

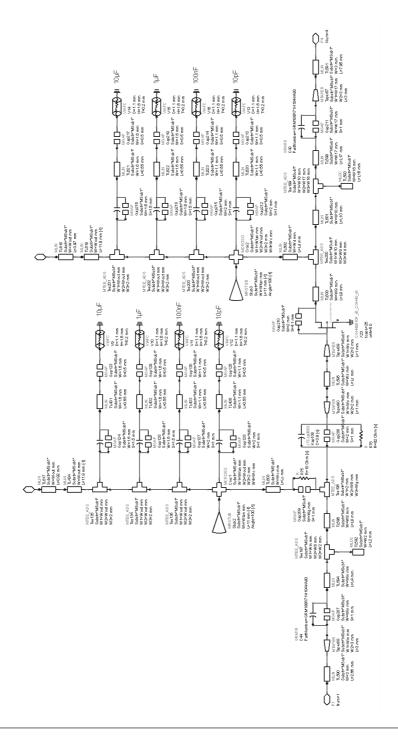

#### 3.3.4 Realizing Test Bench Results

With the optimal impedances for the two matching networks found, the process of realizing them in microstrip lines and passive components can be done. The source matching network is the easiest to match, as it only has to take into account the impedances at  $f_0$ . The impedances can be inputted as separate goals so that ADS can try to match each point exactly, but since a looping method must be used it will not be able to achieve perfect matching. By using each points gain circles it is easier to achieve better results as the simulation program can be set to try and match each point, for example within the circle with 1 dB loss in gain. A way to calculate the gain difference between the optimal impedance and the simulated is to use equations 2.9 and 2.10 in chapter 2.1.1. Equation 2.10a. shows the gain condition for the source matching network and together with the optimal impedances found in table 3.3 it can be used as a simulation goal in ADS. The expression will then be written as

$$G_S = \frac{1 - |\Gamma_S|^2}{|1 - \Gamma_{opt}^* \Gamma_S|^2} = \frac{1 - |S_{11}|^2}{|1 - \Gamma_{opt}^* S_{11}|^2},$$

(3.1)

where  $S_{11}$  is calculated continuously in ADS to match  $\Gamma_{opt}$ . Maximum gain is achieved when  $S_{11} = \Gamma_{opt}$  and the resulting expression will be

$$G_{S_{max}} = \frac{1 - |\Gamma_{opt}|^2}{|1 - \Gamma_{opt}^* \Gamma_{opt}|^2} = \frac{1}{|1 - \Gamma_{opt}|^2}.$$

(3.2)

By combining equation 3.1 and 3.2 the difference between the simulated gain and the optimal gain can be written as

$$\Delta G = \frac{G_S}{G_{S_{max}}} = \frac{1 - |S_{11}|^2}{|1 - \Gamma^*_{opt} S_{11}|^2} \cdot (1 - |\Gamma_{opt}|^2).$$

(3.3)

This makes it possible for ADS to continuously calculate the gain difference while simulating. By using equation 3.3 and creating an expression for each frequency of  $\Gamma_{opt}$  from table 3.3, the optimization goals in table 3.4 were used to create the matching network.

Table 3.4: Optimization goals used when realizing the source matching network.

|                                  | Goal               | Frequency range | Weight |

|----------------------------------|--------------------|-----------------|--------|

| $\Delta G$ (for each freq. step) | < -1  dB           | 1.8-3 GHz       | High   |

| Average $\Delta G$               | $= 0  \mathrm{dB}$ | 1.8-3 GHz       | Medium |

The "Average  $\Delta G$ " goal was added as a way to ensure an even error distribution as ADS tended to favor the points which were easier to match making the gain difference very high at other frequencies. After experimenting with different combinations of microstrip lines and open circuit stubs, the network that was chosen had the impedances presented in the Smith chart in figure 3.8b.

ing network.

Figure 3.8: Comparison of the optimal impedances from the test bench and the realized network.

Figure 3.8b illustrates the looping characteristics of the realized network. From the optimization in ADS it was found that each point could be matched individually, but it was not possible to get closer to the optimal impedances when matching all the points together. So the highest frequencies were prioritized, as this is where the gain is lowest and most vulnerable to a large gain difference. The result was an average gain difference of around 3 dB lower than the optimal case.