### Implementation of the Epileptic Seizure Prediction Algorithm on the SHMAC Platform

Sunniva Nergaard Berg

Electronics System Design and Innovation Submission date: June 2014 Supervisor: Per Gunnar Kjeldsberg, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

## **Problem Description**

Candidate name: Sunniva Nergaard Berg

**Thesis title:** Implementation of the Epileptic Seizure Prediction Algorithm on the SHMAC Platform

#### **Problem Description**

The Single-ISA Heterogeneous MAny-core Computer (SHMAC) is an ongoing research project within the Energy Efficient Computing Systems (EECS) strategic research area at NTNU. SHMAC is planned to run in an FPGA and be an evaluation platform for research on heterogeneous multi-core systems. Due to battery limitations and the so called Dark silicon effect, future computing systems in all performance ranges are expected to be power limited. The goal of the SHMAC project is to propose software and hardware solutions for future power-limited heterogeneous systems.

An existing algorithm for epileptic seizure prediction is going to be mapped on the SHMAC platform. An important part of this algorithm is calculation of a Short-Term maximum Lyapunov exponent (STLmax). There currently exist several versions of this STLmax calculation, both in Matlab and in C, and at different levels of optimization, e.g., floating point and fixed point versions.

The main parts of this assignment are as follows:

- Study the epileptic seizure prediction algorithm and its STLmax calculation.

- Study different approaches found in the literature for mapping of algorithms on heterogeneous platforms consisting of general processing units and hardware accelerators.

- Adapt the STLmax calculation to the SHMAC single instruction set architecture and run it on a general SHMAC processing tile.

- Select one or more kernels in the STLmax calculation and adapt the general processing tile for its efficient execution.

- Evaluate performance and energy gains achieved as well as area overhead.

Supervisor: Per Gunnar Kjeldsberg

## Abstract

This study concerns mapping of the Epileptic Seizure Prediction Algorithm to the SHMAC platform by analysing the algorithm and designing specialized hardware. The work is constituted through consideration of design approaches and variations within the different approaches and implementations of these designs. As the SHMAC platform uses the 32-bit floating point standard for number representations, the design approaches consists of either direct operations on floating point numbers or conversion from floating point to fixed point and operations with fixed point numbers within the module.

Two of the approaches in this study use the floating point and fixed point packages of VHDL and the *float* and *sfixed* types included in these packages, while the third uses standard VHDL and the *std\_logic\_vector* type. The approaches were analysed through simulation in *ISim* and synthesis using *Xilinx's XST*, and verified through a golden devicesimilar method.

The three approaches result respectively to each other as follows (these results assume utilization RAM resources in synthesis):

- Float package: Low design time, low speed, high area consumption.

- Fixed package: Low design time, medium speed, medium area consumption.

- Standard VHDL: High design time, high speed, low area consumption.

To conclude: standard VHDL appears to be the best choice due to the high speed and low area. It especially appears promising to keep to the standard VHDL as the *Xilinx* platform does not seem fully compatible with the float and fixed point packages. Therefore it seems more likely to avoid unexpected problems and incompatibility with the surrounding interface when the time comes for implementing the accelerator to the platform.

### Sammendrag

Denne avhandlingen omhandler implementering av "the Epileptic Seizure Prediction Algorithm" til SHMAC plattformen ved å analysere algoritmen og designe spesialisert hardware. Arbeidet er gjennomført ved å vurdere ulike fremgangsmåter for design og variasjoner innad i de ulike fremgangsmåtene samt implementering av disse designene. Ettersom SHMAC plattformen bruker 32-bit floating point standarden for nummerrepresentasjon, består fremgangsmåtene enten av direkte behandling av floating point tall eller konvertering fra floating point til fixed point og deretter behandling av fixed point tall innad i modulen.

To av fremgangsmåtene i denne avhandlingen bruker floating point og fixed point pakkene i VHDL samt *float-* og *sfixed-*typene inkludert i disse pakkene, mens den tredje bruker standard VHDL og *std\_logic\_vector-*typen. Fremgangsmåtene ble analysert ved simulering i *ISim* og syntetisert ved bruk av *Xilinxs XST* og verifisert ved å bruke en golden device-lik metode.

De tre fremgangsmåtene resulterte i det følgende, respektivt hverandre(resultatene antar utnyttelse av RAM ressursene ved syntese):

- Float package: Lav designtid, lav hastighet, høyt arealforbruk.

- Fixed package: Lav designtid, medium hastighet, medium arealforbruk.

- Standard VHDL: Høy designtid, høy hastighet, lavt arealforbruk.

For å konkludere: standard VHDL virker å være det beste valget, grunnet høy hastighet og lavt areal. Det virker særlig lovende å holde seg til standard VHDL ettersom *Xilinx* plattformen ikke virker fullstendig kompatibel med float og fixed point pakkene. Derfor virker det mer sannsynlig å unngå uventede problemer og inkompatibilitet med det omsluttende grensesnittet ved bruk av standard VHDL, når tiden kommer for implementering av akseleratoren til plattformen.

### Preface

This thesis constitutes the end of my Master of Science degree in Electronics at the Norwegian University of Technology and Science.

Throughout the work on this study, I have received a lot of great support from my supervisor Per Gunnar Kjeldsberg. I would like to thank him, saying that without his guidance, contributions and advice, this work would have been most challenging. I would also like to thank Håkon Wikene who helped me running of codes and profiling on the SHMAC platform, and the others working on SHMAC who have contributed expertise within their respective areas.

Sime N. Berg

Sunniva Nergaard Berg

## Contents

| A  | bstra                                         | $\mathbf{ct}$                                                                                                                                                                        | i                                                                                 |

|----|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Sa | mme                                           | endrag                                                                                                                                                                               | iii                                                                               |

| Pı | reface                                        | Э                                                                                                                                                                                    | $\mathbf{v}$                                                                      |

| Co | onter                                         | ıts                                                                                                                                                                                  | vi                                                                                |

| Li | st of                                         | Figures                                                                                                                                                                              | ix                                                                                |

| Li | st of                                         | Tables                                                                                                                                                                               | xi                                                                                |

| A  | bbrev                                         | viations                                                                                                                                                                             | xiii                                                                              |

| 1  | Intr                                          | oduction                                                                                                                                                                             | 1                                                                                 |

| 2  | The<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Fory and Related Work         SHMAC         Heterogeneous systems         Accelerators         Partitioning of Applications         Number representations         Lyapunov Exponent | <ol> <li>9</li> <li>11</li> <li>12</li> <li>15</li> <li>17</li> <li>20</li> </ol> |

| 3  | <b>Ana</b><br>3.1                             | Ilysis of the Lyapunov Exponent Calculation AlgorithmGeneral profiling                                                                                                               | <b>27</b><br>28                                                                   |

| 4  | 3.2<br>Imp                                    | System specific profiling                                                                                                                                                            | 29<br><b>35</b>                                                                   |

|    | 4.1<br>4.2                                    | Design                                                                                                                                                                               | 35<br>37<br>39<br>39<br>41                                                        |

| 5  | <b>Res</b><br>5.1                             | ults<br>Results from Simulation                                                                                                                                                      | <b>45</b><br>45                                                                   |

|              | 5.2  | Results post Synthesis                           | 48 |

|--------------|------|--------------------------------------------------|----|

|              |      | 5.2.1 Approach expansion package, floating point | 49 |

|              |      | 5.2.2 Approach expansion package, fixed point    | 49 |

|              |      | 5.2.3 Approach standard VHDL, fixed point        | 50 |

|              |      | 5.2.4 Power estimates                            | 51 |

| 6            | Disc | cussion                                          | 53 |

| 7            | Con  | clusion and Future work                          | 59 |

|              |      |                                                  |    |

| A            | Pro  | filing of C-similar Matlab-code                  | 61 |

| В            | Tim  | ing of most time consuming calculations          | 63 |

| С            | Dev  | iations                                          | 69 |

| D            | VH   | DL codes                                         | 75 |

|              | D.1  | Float approach                                   | 75 |

|              |      | D.1.1 Design 1                                   | 75 |

|              |      | D.1.2 Design 2                                   | 77 |

|              | D.2  | Fixed approach                                   | 79 |

|              |      | D.2.1 Design 1                                   | 79 |

|              |      | D.2.2 Design 2                                   | 81 |

|              | D.3  | Standard VHDL                                    | 82 |

| $\mathbf{E}$ | Veri | fication scripts                                 | 93 |

|              | E.1  | C-script calculation differences                 | 93 |

|              | E.2  | Matlab-script for sorting                        | 94 |

#### Bibliography

95

# List of Figures

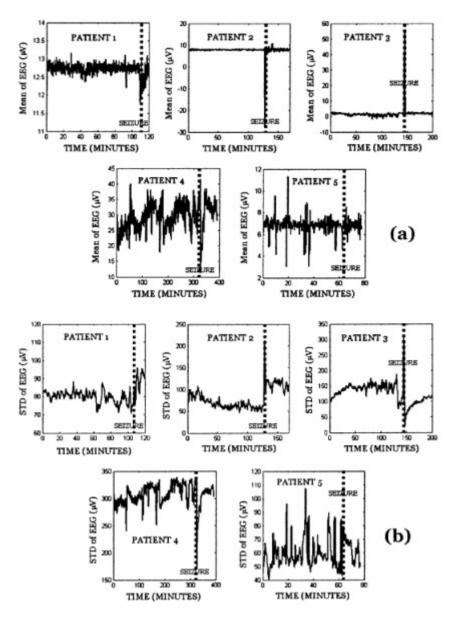

| 1.1  | 1 Mean value(a) and standard deviation(b) of EEG over time from 5 patients[1].<br>Vertical lines denote seizure onset.       |               |  |

|------|------------------------------------------------------------------------------------------------------------------------------|---------------|--|

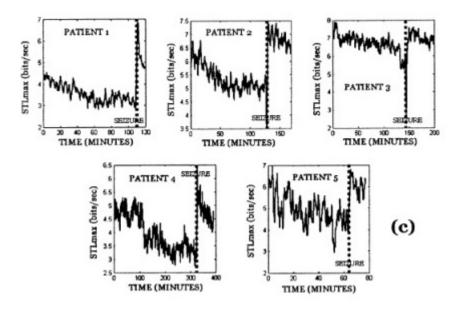

| 1.2  | $STL_{max}$ over time from 5 patients[1]. Vertical lines denote seizure onset.                                               | $\frac{2}{3}$ |  |

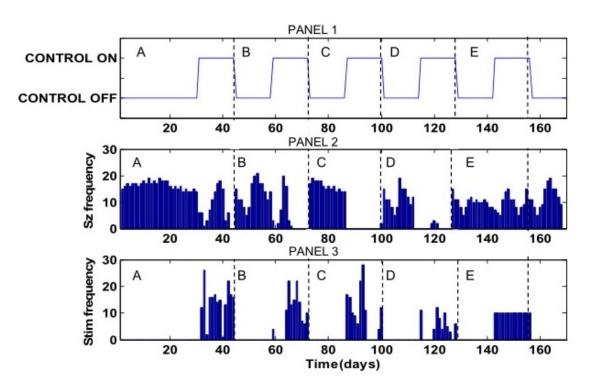

| 1.3  | Control of seizures in a rat using the epileptic seizure prediction algorithm                                                | 0             |  |

|      | and different schemes of stimuli via electrodes[2].                                                                          | 4             |  |

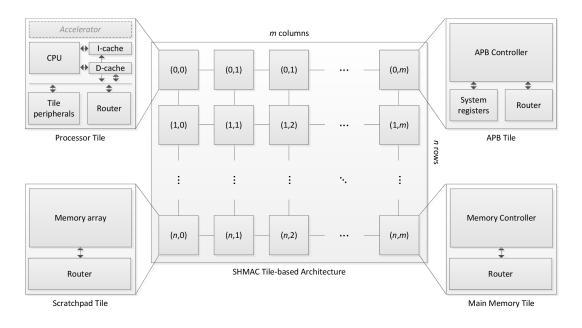

| 1.4  | The tile-based architecture of the SHMAC platform[3]                                                                         | 6             |  |

| 2.1  | FPGA                                                                                                                         | 10            |  |

| 2.2  | Amber Tile                                                                                                                   | 10            |  |

| 2.3  | Process execution tree                                                                                                       | 13            |  |

| 2.4  | Difference in execution on single and multi threaded CPUs (Figure inspired                                                   |               |  |

|      | from [4, p. 361])                                                                                                            | 13            |  |

| 2.5  | Effect of unrolling                                                                                                          | 14            |  |

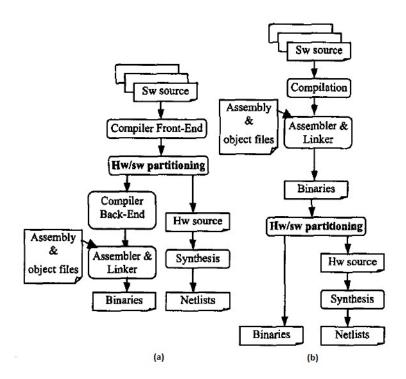

| 2.6  | (a) Source-based and (b) binary-based partitioning[5]                                                                        | 16            |  |

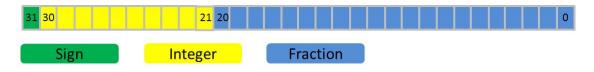

| 2.7  | How floating point numbers are represented                                                                                   | 17            |  |

| 2.8  | How fixed point numbers are represented                                                                                      | 18            |  |

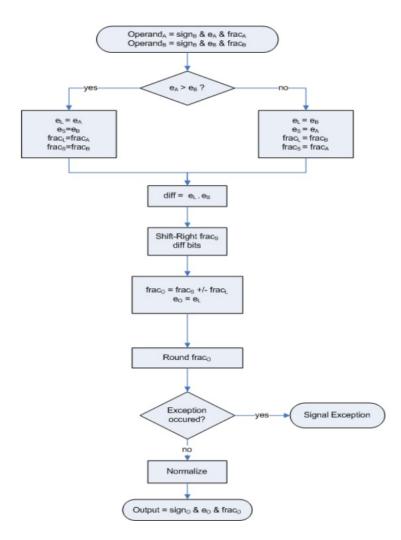

| 2.9  | Algorithm for addition/subtraction in FPU[6]                                                                                 | 19            |  |

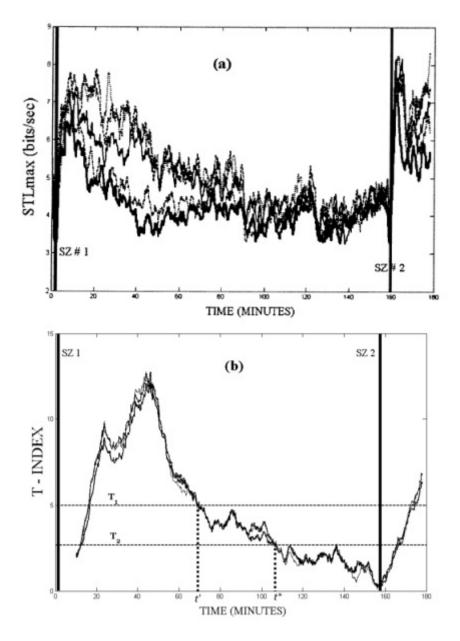

| 2.10 | (a) $STL_{max}$ values between two seizures. (b) T-index for the three most optimal groups of sites between two seizures[1]. | 22            |  |

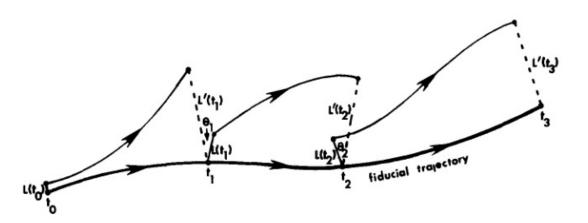

| 2.11 | Evolution of points along the fiducial trajectory for Lyapunov exponent calculation[7].                                      | 23            |  |

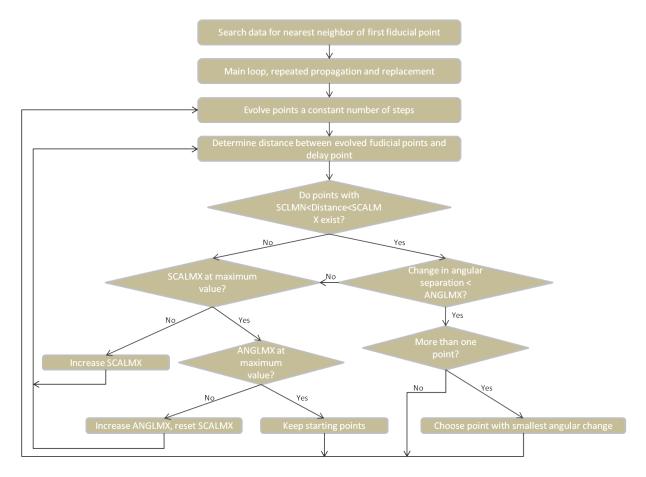

| 2.12 | Flowchart of algorithm for calculating Lyapunov exponents using fixed evolution time as described by Wolf <i>et al.</i> [7]  | 24            |  |

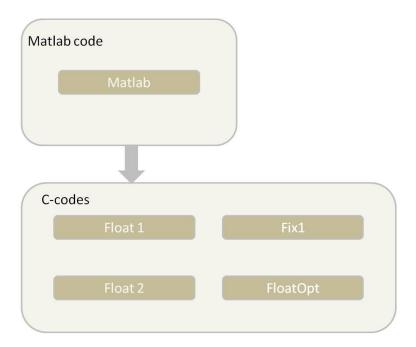

| 3.1  | Illustration of codes available for profiling.                                                                               | 27            |  |

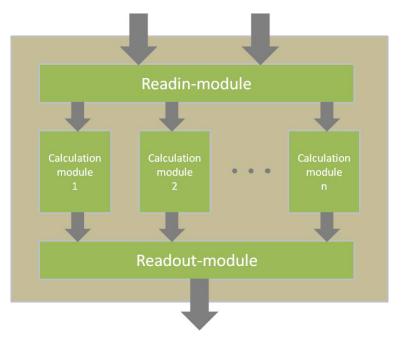

| 4.1  | Illustration of general module.                                                                                              | 37            |  |

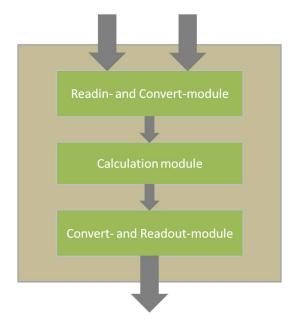

| 4.2  | Illustration of the module using standard VHDL.                                                                              | 40            |  |

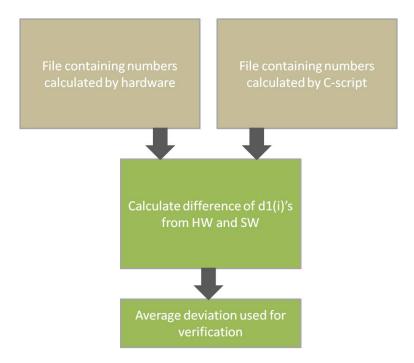

| 4.3  | Illustration of the technique used for verification.                                                                         | 42            |  |

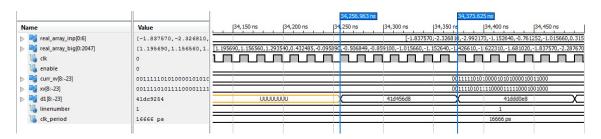

| 5.1  | Waveform from simulation of a module without (left) and with (right) <i>Read</i> -                                           | 17            |  |

| 5.2  | <i>out</i> -module                                                                                                           | 47<br>48      |  |

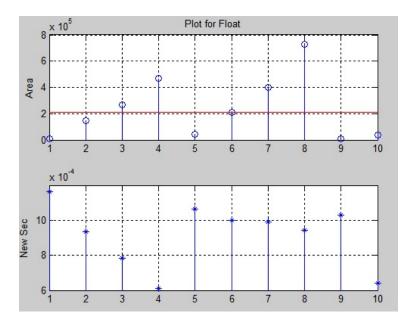

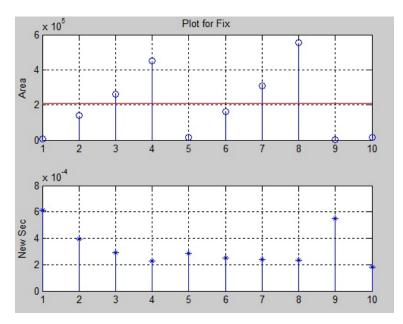

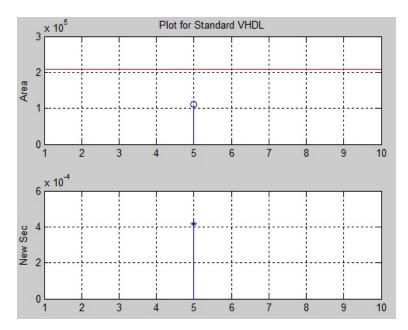

| 6.1  | Graph showing area and speed(in estimated new total runtime, new sec) of different design choices.                           | 54            |  |

| 6.2 | Graph showing area and speed(in estimated new total runtime, new sec)      |    |

|-----|----------------------------------------------------------------------------|----|

|     | of different design choices.                                               | 55 |

| 6.3 | Graph showing area and speed(in estimated new total runtime, new sec)      |    |

|     | of the approach implementing fixed point from std_logic_vector. $\ldots$ . | 56 |

## List of Tables

| 1.1                 | Dennadrian versus Post-Dennardian scaling [8]                                                                                      | 5               |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| $3.1 \\ 3.2 \\ 3.3$ | Profiling of Matlab code working on matricesMost run lines from Matlab profiling.Total execution time.                             | 28<br>29<br>30  |

| 3.4<br>3.5          | Cycles for instructions in Fix1 code if rewritten for integer utilization.<br>Addition and subtraction spend same amount of cycles | 30              |

| 3.6                 | milliseconds                                                                                                                       | $\frac{31}{31}$ |

| 4.1                 | Area and performance for float extension package approach                                                                          | 38              |

| 4.2                 | Area and performance for fixed extension package approach                                                                          | 39              |

| 4.3                 | Area and performance for standard VHDL fixed point approach                                                                        | 40              |

| 4.4                 | Deviation for float expansion package approach                                                                                     | 43              |

| 4.5                 | Deviation for fixed expansion package approach                                                                                     | 44              |

| 4.6                 | Deviation for standard VHDL approach                                                                                               | 44              |

| 5.1                 | Simulation time from float and fixed extension package approach, and the                                                           |                 |

|                     | standard VHDL approach                                                                                                             | 46              |

| 5.2                 | New timing for float extension package approach                                                                                    | 49              |

| 5.3                 | New timing for fixed extension package approach                                                                                    | 50              |

| 5.4                 | New timing for standard VHDL approach                                                                                              | 50              |

| 5.5                 | Table of power estimates                                                                                                           | 51              |

| 6.1                 | Table which compares qualities of the different approaches                                                                         | 57              |

| A.1                 | Profiling of C-syntax like Matlab code                                                                                             | 61              |

| B.1                 | Timing of most time consuming calculations, algorithm float $1 \ldots \ldots$                                                      | 63              |

| B.2                 | Timing of most time consuming calculations, algorithm float $2 \ldots \ldots$                                                      | 64              |

| B.3                 | Timing of most time consuming calculations, algorithm fix $1 \ldots \ldots$                                                        | 65              |

| B.4                 | Timing of most time consuming calculations, algorithm fix 1                                                                        | 66              |

| B.5                 | Timing of most time consuming calculations, algorithm no malloc                                                                    | 66              |

| B.6                 | Timing of most time consuming calculations, algorithm FloatOpt from fixed point experiences.                                       | 68              |

| C.1                 | Deviation for float extension package approach                                                                                     | 70              |

| C.2 | Deviation for float extension package approach | 72 |

|-----|------------------------------------------------|----|

| C.3 | Deviation for the approach using standard VHDL | 74 |

### Abbreviations

APB Advanced Peripheral Bus

$BRAM\,$ Block Random Access Memory

CPU Central Processing Unit

CSL Configurable System Logic

EEG Electroencephalogram

FPGA Field-Programmable Gate Array

FPU Floating Point Unit

ISA Instruction Set Architecture

ISE Instruction Set Extention

$ISEGEN\,$  ISE Generation

$L_{max}$  Maximum Lyapunov exponent

LUT LookUp Table

RAM Random Access Memory

RISC Reduced Instruction Set Computer

$SHMAC\,$ Single-ISA Heterogeneous MAny-core Computer

$STL_{max}$  Short-term maximum Lyapunov exponent

STP System ThroughPut

VHDL VHSIC Hardware Description Language

$VHSIC\,$  Very High Speed Integrated Circuit

$ZBT\,$ Zero Bus Turnaround

#### Chapter 1

### Introduction

The Single-ISA Heterogeneous MAny-core Cumputer, SHMAC, project is an ongoing research project at NTNU. This is planned to be a platform for evaluation of heterogeneous systems. The platform is continuously changing and evolving, i.e. increasing the quality of the system. As for the beginning of this project, there is for instance no hardware support for floating point numbers, which will prove crucial for the scope of this thesis, to map an epileptic seizure prediction algorithm to the SHMAC platform.

Epilepsy is a neurological disorder characterized by epileptic seizures. These seizures are results of a temporary electrical disturbance of the brain[1]. The seizures are followed by postictal slowing and disorganization of the EEG rhythm, and can incapacitate the patient during as well as after the seizure[9]. Epileptic seizures can, if not controlled, have a severe impact on the patients social, vocal and educational activities, and thereby reduce the patient's quality of life[2]. 1% to 2% of the world's population, at all ages, are affected by this disorder. It was previously believed that seizures occurred abruptly and could not be anticipated[2]. This, however, proved to be incorrect.

The algorithm proposed by Iasemidis *et al.* [1][9] aims to be able to predict an oncoming seizure and thus enable the possibility of implantable devices for diagnostic or therapeutic purposes. The epileptic seizure prediction suggested by Iasemidis *et al.*[1][2][9], use the EEG recordings of the brain and utilize these recordings to predict an oncoming seizure. These recording, however, does not change consistently across patients: Figure 1.1 illustrates EEG recordings before, during and after a seizure in five patients. For example, the mean recording shows an upward trend in Patient 4, but no significant trend is visible in the other patients before the seizure.

FIGURE 1.1: Mean value(a) and standard deviation(b) of EEG over time from 5 patients[1]. Vertical lines denote seizure onset.

This inconsistency applies to all cases, before, during and after the seizure, across all five patients. Because of this inconsistency, an other measure called Short-term maximum Lyapunov exponent,  $STL_{max}$ , is introduced.  $STL_{max}$  exponents quantify the rate of production/destruction of information within short periods of time (here 10.24s) of EEG measurements[1]. Looking at the  $STL_{max}$  values in Figure 1.2 for the same patients in the same timespan, it is obvious that  $STL_{max}$  values change consistently across patients. All the  $STL_{max}$  values are higher after than before the seizure, indicating that  $STL_{max}$  values can be used for seizure prediction.

FIGURE 1.2:  $STL_{max}$  over time from 5 patients [1]. Vertical lines denote seizure onset.

A brain in a normal state is characterized by chaos, i.e. that measurements of production or destruction of information in different brain sites are incoherent. These measurements are carried out by calculating Lyapunov exponents of the system, in this case the nonlinear, dynamical system - the brain. Lyapunov exponents are amongst the most important measures of the dynamics of a linear or nonlinear system[2]. These exponents measure average information flow in bits per second. Positive exponents indicate generation of information while negative exponents indicate destruction.

For a dynamical system to be chaotic, at least one of the system's Lyapunov exponents needs to be positive[2]. Due to this, the calculation of Lyapunov exponents is crucial to determine whether or not the system is chaotic in the epileptic seizure prediction algorithm. The calculation will be further elaborated in Chapter 2.

The algorithm has also been tested on rats, using electrodes implanted in their brains and stimulating the rats brains according to warnings issued by the prediction algorithm. Using different schemes of stimuli, the combination of the seizure prediction algorithm and electrical pulses to stimulate the brain seems promising, as illustrated in Figure 1.3.

FIGURE 1.3: Control of seizures in a rat using the epileptic seizure prediction algorithm and different schemes of stimuli via electrodes[2].

Schemes C and D in Figure 1.3 seem to reduce the numbers of seizures to zero for days at a time. The epileptic seizure prediction thus appears to be a useful application, and could possibly be used in human implants in the future. It is, however, important that implants are as energy efficient as possible, as changing batteries or harvesting energy inside the body is a challenging task.

The scope of this thesis is to map the epileptic seizure algorithm to the SHMAC platform. The Single-ISA Heterogeneous MAny-core Computer(SHMAC) platform, is as previously stated, an ongoing research project within the research initiative Energy Efficient Computing Systems(EECS) at the Faculty for Information Technology, Mathematics and Electrical Engineering, NTNU. SHMAC is planned to be an evaluation platform for research on heterogeneous multi-core systems. Heterogeneous systems are required partly due to the Dark Silicon effect.

As an important goal of the SHMAC platform also is to be energy efficient, implementing this algorithm to the SHMAC platform could be of beneficial use both for the purpose of implementing the algorithm itself, and to explore the efficiency attainable on the SHMAC platform. The future of electronic devices is expected to be power limited. This is both due to the limitation of batteries and the Dark silicon effect. The Dark Silicon effect comes from the breakdown of Dennardian scaling. Dennardian scaling used the concept of scaling the threshold voltage to improve energy efficiency. The formula for a chip's power consumption is shown in Table 1.1. As the power relates to the voltage squared, scaling the voltage will result in an improvement of  $S^2$  in energy efficiency.

The relationship between Dennardian scaling and Post-Dennardian scaling is exposed in Table 1.1. The scaling factor S comes from the ratio between the feature size of two processes, for example the ratio  $S = 1.4 \times$  for two processes of 32 and 22 nm[8]. Post-Dennardian scaling is also called leakage-limited scaling, and in that regime, one cannot exploit the fact that reduction in threshold voltage gives a reduction in operating voltage resulting in a  $S^2$  improvement of energy efficiency. This is what distinguishes Dennardian from post-Dennardian scaling, and is as shown in lines 4 through 6 in Table 1.1. This also causes the shortfall of  $S^2$  for each process generation. The percentage of chips that needs to be powered off, or dark, will thus increase.

| Scaling                                    |            |                 |  |

|--------------------------------------------|------------|-----------------|--|

| Transistor property                        | Dennardian | Post-Dennardian |  |

| $\Delta Quantity$                          | $S^2$      | $S^2$           |  |

| $\Delta Frequency$                         | S          | S               |  |

| $\Delta Capacitance$                       | 1/S        | 1/S             |  |

| $\Delta V_{dd}^2$                          | $1/S^{2}$  | 1               |  |

| $\Rightarrow \Delta Power = \Delta QFCV^2$ | 1          | $S^2$           |  |

| $\Rightarrow \Delta Utilization = 1/Power$ | 1          | $1/S^{2}$       |  |

TABLE 1.1: Dennadrian versus Post-Dennardian scaling [8]

The SHMAC platform is a tile-based architecture, illustrated in Figure 1.4. The interconnections are in a mesh grid, meaning that all tiles have connections to their north, east, south and west, excluding tiles at the boundaries.

FIGURE 1.4: The tile-based architecture of the SHMAC platform[3].

The platform supports tiles of types[3]:

- Processor tile

- Scratchpad tile

- Main Memory tile

- APB Interface tile

- Dummy tile

For this project, the processor tile is the relevant tile. A tile of this type primarily consists of a processor, caches, peripherals and a router, but can also be equipped with accelerators. Accelerators are execution units optimized for their task.

The idea with the SHMAC-project, is to reduce the Dark Silicon effect by two main strategies, of which exploiting a heterogeneous architecture is one. A heterogeneous architecture is an architecture consisting of different resources, each included to achieve higher performance or a more energy efficient system[10].

By including cores both for high performance and for energy efficiency, one can dynamically schedule a system to have high performance or low energy consumption[11]. Heterogeneous systems will be further discussed in Chapter 2. Another way of addressing

the problem of the Dark Silicon effect, is to add application specific elements, accelerators, to the architecture that are very energy efficient at their task, and can be turned off if their task does not occur. This will actually increase the heterogeneity of the system, and is as such not a completely different strategy compared to the utilization of a heterogeneous architecture. Accelerators will be further elaborated in Chapter 2. The objective of this study is to map the Epileptic Seizure Prediction Algorithm on the SHMAC Platform by examining the algorithm and investigate parts of the code that could benefit from the implementation of specialized hardware.

The remaining of the thesis is organized as follows. Chapter 2 will go into details regarding the SHMAC platform and related theory, calculation of the Lyapunov exponent, partitioning of applications, and number representations. Analysis of the codes are presented out in Chapter 3 including both general and system specific profiling. Chapter 4 concerns design approaches, data from synthesis and verification of designs. Results from simulation in *ISim* and post synthesis estimations are placed in Chapter 5 and the results and how they are affected by the synthesis results are discussed in Chapter 6. Chapter 7 contains suggestions for future work and the conclusion.

### Chapter 2

### Theory and Related Work

As stated in Chapter 1, two main ideas have been suggested to address the Dark Silicon effect on the SHMAC platform. One is implementing a heterogeneous system and the other is adding accelerators to the architecture, increasing its heterogeneity. This chapter will go more into detail about what heterogeneous systems and accelerators are and different ways to represent numbers, as well as the calculation of the Lyapunov exponents used in the algorithm related to this work.

#### 2.1 SHMAC

The SHMAC platform is, as previously stated, a research project at NTNU. The platform is planned to be an evaluation platform for research on heterogeneous multi-core systems. The platform's architecture is described in the following.

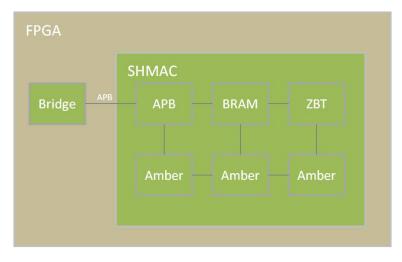

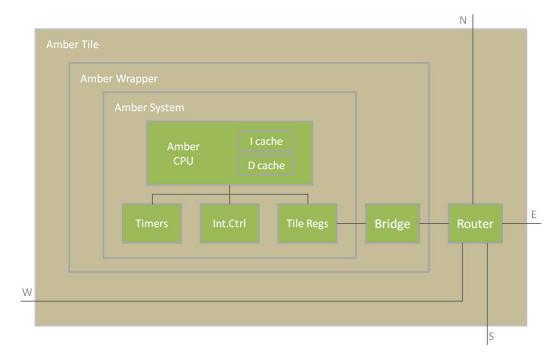

FIGURE 2.1: FPGA

As can be seen in Figure 2.1, the SHMAC platform consists of several tiles, here represented by APB, ZBT, BRAM and Amber tiles. The Amber tiles are equivalent to the processor tiles described in the project plan for the SHMAC project [3]. A lower level of abstraction than the Amber Tile is the Amber Wrapper. Illustrated in Figure 2.2, the wrapper excludes the router. Within the next level of abstraction from the Amber CPU wrapper, one finds the Amber system, which amongst other, contains the Amber CPU [12].

FIGURE 2.2: Amber Tile

The Amber processor core is a 32-bit RISC processor running at 60 MHz with a 5-stage pipeline, which is fully compatible with the ARM v2a ISA[12]. An important detail for this project is the delay of each instruction in the Amber core. As can be found in the reference manual for the Amber core[12], register based instructions are executed in one cycle, excluding instructions involving multiplication. Multiplication as well as multiply-accumulate operations take 34 clock cycles, making these operations obvious bottlenecks amongst the standard instructions. The multiplication on the Amber core uses the Booth algorithm[13], which is a small and slow implementation of a multiplier. The algorithm repeatedly adds one of two predetermined values to a product and then makes a rightward arithmetic shift on the product. The complete algorithm can be found in the Amber manual[12] or further reading in the article "A signed binary multiplication technique" by Booth[13].

#### 2.2 Heterogeneous systems

A heterogeneous system is a system consisting of different resources. Which, relating to the SHMAC platform, would say that the different tiles in the SHMAC platform can have different characteristics due to additional units on the tile, i.e. an accelerator, additional memory or other units not featured on a standard tile.

Heterogeneity can be classified in three classes. The weakest form for heterogeneity, is systems having the same ISA and micro architecture across the cores, only varying in clock frequency. Then there is a stronger form where the cores have the same ISA, but have different micro architectures. The strongest form of heterogeneity is systems which have both different ISAs and micro architectures. The SHMAC is Single-ISA, meaning that the different cores all implement the same instruction set architecture.

K. V. Craeynest and L. Eeckhout [11] present some results regarding homogeneous versus heterogeneous designs. Compared to homogeneous designs, heterogeneity yields a better performance, up to 32% of a weighted speed-up, STP. This increase comes from heterogeneous systems' ability to map jobs to cores most appropriate. As heterogeneous systems are more specialized than homogeneous, they are more complex, as the cores in homogeneous systems all contain of the same tiles, while the tiles within a heterogeneous system varies. This presumably makes a homogeneous system easier to implement.

The complexity of heterogeneous systems can, however, often be accounted for by the benefits regarding energy consumption and performance. When executing a program on a heterogeneous multi-core system, the program is divided into smaller parts, each executed on the most suitable core[14, p. 14], leading to speed-ups and/or less energy consumption.

#### 2.3 Accelerators

The fastest processors are considered to be very expensive, so splitting the application and dividing it to be performed on several smaller processors can be cheaper, even when considering the cost of assembling those components [4, p. 354]. In addition, some algorithms may not map well onto a CPU, and may as such be better executed on a specially designated processing element, such as an accelerator.

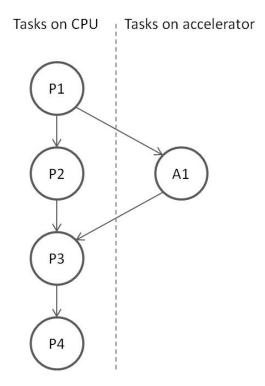

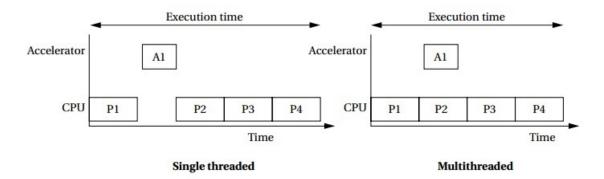

An accelerator is a processing element attached to the CPU bus [4, p. 357]. This is to be able to execute tasks quickly. The basic concern with accelerators is how much gain can be achieved. This depends in part on whether the system in which it is to be integrated is single threaded or multi threaded: does the CPU wait for the accelerator while it is operating, or does the CPU run with the accelerator running in the background? Figure 2.3 illustrates a tree of processes, where process A1 is executed on an accelerator whilst the other four processes are executed on the CPU. Figure 2.4 illustrates the difference in executing the sequence of processes from the process tree in Figure 2.3 on a single threaded and a multi threaded CPU, respectively.

FIGURE 2.3: Process execution tree

FIGURE 2.4: Difference in execution on single and multi threaded CPUs (Figure inspired from [4, p. 361])

A simple equation for the speed-up using an accelerator in a system is [4, p. 362]:

$$S = n(t_{CPU} - t_{accel}) = n[t_{CPU} - (t_{in} + t_x + t_{out})]$$

(2.1)

In this equation, n is the number of times the accelerated block is executed,  $t_{CPU}$  is the execution time of the function in software,  $t_{in}$  and  $t_{out}$  are the times spent reading and writing variables, and  $t_x$  is the execution time of the accelerator when all the data is available. From this, one can conclude that it is of greater value to accelerate a task which is executed a significant number of times. In a single threaded system, the total execution time is reduced by S, while it is more complex for multi threaded systems. In multi threaded systems, there are several execution paths. So, to find the total execution time, one have to find the longest path from the beginning to the end of the execution.

An example of targets that are executed a significant number of times, are the ones inside loops, especially nested loops. In this case loop unrolling is an interesting approach for an accelerator. In the case of double nested for-loops, loop unrolling can be done in more or less extensive ways, unrolling both the for-loops entirely, one entirely and the other partly, or both partly. Unrolling both loops to the fullest, will yield the highest performing hardware regarding speed, but also the most area consuming, and vice versa. It is therefore important to evaluate how the calculation speed and area of this specific hardware are influenced by different degrees of unrolling, to find a optimal solution.

Figure 2.5 illustrates how unrolling will affect the area and performance. By having no unrolling only one calculation module is needed. This means lower speed as the one module has to be run  $(sizeloop1) \times (sizeloop2) = n$  times, but it also means lower area consumption. By completely unrolling both for-loops, we would have the exact opposite situation; n parallel modules, high speed and large area consumption.

FIGURE 2.5: Effect of unrolling

Another aspect concerning accelerators is if they operate on a large amount of data. So, if this is the case, it can be beneficial to give it direct memory access. The accelerator can thus read and write data directly, not having the CPU as a shuttle between the accelerator and the memory. In that case, the CPU and accelerator can communicate through a shared memory. To decide if an accelerator is needed, the specific system needs to be analysed. Other issues in the system, such as moving data, may be a bottleneck. In that case the inclusion of an accelerator may not be as beneficial as intended[4, p. 357].

#### 2.4 Partitioning of Applications

Partitioning is a crucial aspect when one is to implement an accelerator to a system. The partitioning has a first order impact on the cost/performance of the final system[15] as it takes into account the gain and/or drawback of the resulting hardware or software blocks. The partitioning is, relating to this study, to map the Epileptic Seizure Prediction Algorithm partly onto an accelerator while the remaining code will run on the Amber CPU.

An approach to partitioning is the ISEGEN algorithm. This algorithm uses the Kernighan-Lin min-cut algorithm[16] for partitioning. The goal of Biswas *et al.*[17] is to make an iterative improvement technique to generate solutions close to the ones provided manually by expert designers. The algorithm starts with all nodes in either hardware or software and toggles each unmoved node from hardware to software or vice versa. For each toggled node, the gain function is computed to measure how the toggle affects the cost/performance of the system. The ISEGEN algorithm also takes into account how many outputs and inputs the resulting ISE will have. As an example, moving a node with one input and no output will increase the numbers of inputs and outputs of the ISE by one and zero, respectively.

A more straight forward approach is to examine the loop regions of a code and make the most time-consuming software into specialised hardware. Stitt and Vahid [5] applied such an approach by mapping critical loops of embedded applications to configurable system logic. They did, however, consider two different approaches to partitioning, sourcebased and binary-based. The two approaches are depicted in Figure 2.6.

FIGURE 2.6: (a) Source-based and (b) binary-based partitioning[5].

For area and power characteristics they used Xilinx VirtexE. For estimation of total power consumption, Equation 2.2 was applied:

$$TotalPower = \%SW \times P_{SW} + \%CSL \times (P_{CSL} + 0.25 \times P_{SW}) + InterconnectPower + QuiecentPower$$

$$(2.2)$$

$P_{CSL}$  is the power of the configurable system logic when it is active and  $P_{SW}$  is the power of the software when the microprocessor is active. It is also assumed that an inactive microprocessor uses  $\frac{1}{4}$  of the power used while being active. Stitt and Vahids approach include implementing blocks and replacing the corresponding software region by a handshaking behavior[5]. Determination of potential improvements was done by converting C-code for the previously mentioned critical loops into VHDL-code.

Stitt and Vahid extracted the parallelism of the C-code and created appropriate hardware[5]. The authors also suggest to implement techniques such as loop unrolling and pipelining to achieve a greater speed-up. For partitioning at source-level, Stitt and Vahid achieved an average speed-up of 1.5 times and energy savings of 27% compared to running the benchmarks in pure software.

#### 2.5 Number representations

Since the algorithm is written in C using float-numbers, the numbers being input to the accelerator will be represented in floating point. Floating point numbers have got this notation due to the fact that the decimal point is not set between a specific bitpair, but is floating. The Amber core uses the 32-bit format of the IEEE Standard 754 for Floating-Point. According to the IEEE Standard for Floating-Point Arithmetic, the standard representation of 32-bit floating-point numbers is as follows[18]:

- Bit 31: sign

- Bits 30-23: exponent

- Bits 22-0: significand/mantissa

The floating point standard also requires that the most significant '1' in the number to be represented is removed and made implicit. Therefore, when converting to or from floating point, one always have to take this implicit 1 into account. This means that a number represented by floating point has implicitly 24 bits for the mantissa, resulting in an accuracy of  $2^{-24} = 59.60 \times 10^{-9}$ .

FIGURE 2.7: How floating point numbers are represented.

Floating point numbers can according to the IEEE Standard 754 also use bit widths such as 64 and 128 bit. The decimal value of the floating-point numbers are calculated as in Equation 2.3:

$$decimal\_value = (-1)^{sign} * b^{exponent\_exponent\_bias} * (1 + significand)$$

(2.3)

The distinction between fixed and floating point numbers is that the fixed point has, as the name indicates, the decimal point at a fixed bit. To avoid erroneous calculations the user has to keep track of its location. The decimal point can be placed where desired, depending on the required size of the integer and accuracy of the fractional part. For example as illustrated in Figure 2.8: one bit is used for sign, 10 for the integer number and 21 for the fractional part. This means that the accuracy of numbers in this representation is  $2^{-21} = 476.83 \times 10^{-9}$ , and the integer part can be up to  $2^{10} - 1 = 1023$ .

FIGURE 2.8: How fixed point numbers are represented.

Conversion from the fixed point representation as presented in Figure 2.8 to the 32 bit floating point standard can be carried out in the following way:

Sign bit: no conversion, directly transfer.

Find number of bits required to represent the integer of the fixed point ↔ representation.

Add exponent base to find correct exponent in the floating point standard.

Shift fraction equal to number of bits so that the most significant bit of the ↔ integer is at index 21.

Remove most significant bit of integer.

LISTING 2.1: Conversion strategy floating point to fixed point

Doing operations on floating-point numbers is not straight forward. Jidan Al-Eryan implemented an FPU and documented it in an accompanying paper. He there added the algorithms for addition, subtraction, multiplication and division[6]. The addition and subtraction algorithm is depicted in Figure 2.9.

FIGURE 2.9: Algorithm for addition/subtraction in FPU[6].

Due to this, implementation of modules for addition/subtraction and multiplication would be necessary to directly work on the numbers sent from the CPU to the accelerator.

However, in VHDL there exists extension packages which include fixed point and floating point number-types, conversion from floating to fixed-point representations and vice versa[19][20][21]. These packages are:

- float\_pkg\_c.vhdl

- fixed\_pkg\_c.vhdl

- fixed\_float\_types\_c.vhdl

David Bishop states in "Floating point package user's guide", that the hardware of the fixed point can be almost 3X less than that of floating point[20]. He also says in the

fixed point guide, that because the fixed point is a step between integer math and floating point, it is almost as fast as the numeric\_std arithmetic of VHDL[21].

### 2.6 Lyapunov Exponent

Lyapunov exponents can be used to diagnose the dynamics in a chaotic system [7]. They quantify the average rate of separation for nearby trajectories[22]. For a system to be chaotic, it needs to contain at least one positive Lyapunov exponent. Lyapunov exponents measure the rate of creation or destruction of information in system processes, and are expressed in bits/s or bits/orbit[7].

The seizure algorithm uses short-term maximum Lyapunov exponents  $(STL_{max})$  which are more accurate than the traditional maximum Lyapunov exponents  $(L_{max})$ .  $STL_{max}$ profiles are created from recordings of EEG signals from different sites for 10 seconds, each recording site resulting in one  $STL_{max}$  estimation[2]. Progressive convergence of  $STL_{max}$  profiles is called dynamical entrainment [1][2][9]. The brain sites involved in measuring this dynamical entrainment are called critical sites, while the corresponding pairs of sites interacting are called critical pairs[2].

The selection of sites is however not straight forward, as the sites participating in the pre-ictal transition can vary from seizure to seizure even within the same patient. Iasemidis *et al.* [9] resolved this by selecting k critical sites after the occurrence of the first seizure. Their selection procedure leads to the selection of the k sites that were most entrained 10 minutes prior to the seizure as well as being disentrained postically. This procedure is then carried out after each seizure, and new critical sites are updated automatically for optimal prediction[9].

When it comes to determining entrainment amongst the detected critical electrode sites, the authors use a period of time in which the difference of the mean  $STL_{max}$  values of two sites are statistically estimated. They use 10 minute periods<sup>1</sup>, which include approximately 60  $STL_{max}$  values, and do the test at significance level  $\alpha = 0.01[9]$ . As the entrainment is calculated by comparing two sites, the pair T-statistic is used. The Tindex for electrode sites *i* and *j* in the epileptic seizure prediction algorithm is calculated as in Equations 2.4 to 2.8[1]:

<sup>&</sup>lt;sup>1</sup>denoted w(t)

$$L_{i}^{t} = \left\{ STL_{max_{i}}^{t}, STL_{max_{i}}^{t+1}, \dots, STL_{max_{i}}^{t+59} \right\}$$

(2.4)

$$L_{j}^{t} = \left\{ STL_{max_{j}}^{t}, STL_{max_{j}}^{t+1}, \dots, STL_{max_{j}}^{t+59} \right\}$$

(2.5)

$$D_{ij}^{t} = L_{i}^{t} - L_{j}^{t} = \left\{ d_{ij}^{t}, d_{ij}^{t+1}, \dots, d_{ij}^{t+59} \right\}$$

(2.6)

$$d_{ij}^{t'} = \left\{ STL_{max_i}^{t'} - STL_{max_j}^{t'} \right\}$$

$$(2.7)$$

$L_i$  and  $L_j$  are vectors of the 60  $STL_{max}$  values for the 10 minute period, and D is the distance between the electrode sites *i* and *j* at a time *t*. This results in Equation 2.8, the pair T-statistic:

$$T_{ij}^t = \frac{|\overline{D}_{ij}^t|}{\frac{\hat{\sigma}_d}{\sqrt{60}}} \tag{2.8}$$

The pair-T statistic shown in Equation 2.8 use  $\overline{D}_{ij}^{t}$  and  $\hat{\sigma}_{d}$  which are the sample average and standard deviation respectively. Significance level 0.01 means that the threshold value for disentrainment is  $T_{i,j} > T_{\frac{\alpha}{2},59} = T_{0.005,59} = 2.662$ . The choice of significance level is explained in Iasemidis *et al.* [1, p. 619].

The threshold value of T = 2.622 indicates, as mentioned, disentrainment of the sites. A second threshold has been introduced at significance level  $\alpha = 0.00001$ , this corresponds to a T-value of 5.000. Thus, there are two threshold values,  $T_1 = 5.000$  and  $T_2 = 2.662$ . A dynamical transition toward a seizure is recognized when the T-value transits from a value  $T > T_1$  at time  $t_1$  to a value  $T < T_2$  at a time  $t_2 > t_1$ . If this transition results from the initially selected sites, a warning of an impending seizure will be issued[9].

FIGURE 2.10: (a) $STL_{max}$  values between two seizures. (b) T-index for the three most optimal groups of sites between two seizures[1].

Figure 2.10 shows the T-index and  $STL_{max}$  between two seizures. The two solid vertical lines are seizure onset while the dashed lines indicate where the T-index crosses the two threshold values  $T_1$  and  $T_2$ . As Figure 2.10 depicts, the warning of an impending seizure will for these electrode sites and this seizure be issued about 55 minutes prior to the seizure.

The calculation of Lyapunov exponents in the Epileptic Seizure Prediction algorithm is carried out by expanding the EEG-signals into a m-dimensional<sup>2</sup> phase portrait with

$<sup>^2 \</sup>mathrm{In}$  this case 7-dimensional.

delay coordinates<sup>[7]</sup>:

$$\{x(t), x(t+T), \dots, x(t+[m-1]T)\}$$

(2.9)

where T is the delay time. At a time  $t_0$ , the nearest neighbour<sup>3</sup> to the initial point is located, and the distance  $x(t_0) - x(t)$  is denoted  $L(t_0)$ . After a constant propagation time, at time  $t_1$ , this distance will have evolved to  $L'(t_1)$ . At this point in time, a point to replace the evolved point is searched for to better meet the following criteria[7]:

- The distance between the new chosen point and the evolved fiducial point is small

- The angular separation between them is small

This procedure is then executed throughout the provided data, and at last the Lyapunov exponent is estimated by Equation 2.10[7]:

$$\lambda_1 = \frac{1}{t_M - t_0} \sum_{k=1}^M \log_2 \frac{L'(t_k)}{L(t_{k-1})}$$

(2.10)

FIGURE 2.11: Evolution of points along the fiducial trajectory for Lyapunov exponent calculation[7].

Figure 2.11 illustrates how the procedure of estimating Lyapunov exponents works, traversing the fiducial trajectory and choosing new points nearer the trajectory if the absolute value of the vector between two points becomes too large. It is then essential that the replacement point minimize both the distance between the new point and the fiducial trajectory as well as the angular separation, denoted  $\theta$  in Figure 2.11.

$^{3}$ Euclidean

FIGURE 2.12: Flowchart of algorithm for calculating Lyapunov exponents using fixed evolution time as described by Wolf *et al.*[7].

Figure 2.12 describes the algorithm for calculating Lyapunov exponents using the fixed evolution time program proposed by Wolf *et al.* [7]. As can be seen in Figure 2.12, the program contains a main loop where all the data is traversed. Inside the main loop, the distances between the evolved points are calculated. The goal is to find points as little separated as possible down to a lower threshold SCALMN<sup>4</sup>. The upper threshold for separation of points is SCALMX, and for angular separation, ANGLMX. All distances within the interval  $\langle SCALMN, SCALMX \rangle$  are examined and the new point is determined based on the angular separation. If no points in the interval exist, or the points within the interval have a too large angular separation, the upper threshold SCALMX is increased. This can be repeated a predetermined number of times. When SCALMX has been increased the maximum amount of times, and no points have been found to fit the criteria, ANGLMX is increased and SCALMX is reset to its initial value.

<sup>&</sup>lt;sup>4</sup>Lower threshold SCALMN is introduced due to noise considerations.

This procedure is repeated until ANGLMX and SCALMX are both at their maximum values. If no points satisfy the criteria, the initial evolved point of this time step<sup>5</sup> is kept. The exponent is then updated by adding the new points in the sum in Equation 2.10.

<sup>&</sup>lt;sup>5</sup>e.g.  $t_1$  in Figure 2.11

## Chapter 3

# Analysis of the Lyapunov Exponent Calculation Algorithm

There are several versions of the Lyapunov Exponent Calculation Algorithm. The initial ones are written in Matlab. Using Matlab is beneficial as matrices and matrix operations are heavily featured in the algorithm. From these initial versions, others have been developed by translating the codes to C-language. This evolution is illustrated in Figure 3.1.

FIGURE 3.1: Illustration of codes available for profiling.

To determine which blocks of the code that are the most computational demanding and thus good targets for acceleration, the codes need to be profiled. As the objective of this study is to map the algorithm to the SHMAC platform, the profiling is divided in two. First the Matlab code is profiled using the built-in tools of Matlab version R2013b. The data attained from the general profiling are then used as a pointer for the system specific profiling. This is done due to a necessity of narrowing down blocks to record time consumption of, when run on the SHMAC platform.

### 3.1 General profiling

The run time from the profiling in Matlab is shown in Table 3.1. This code uses a Csimilar syntax instead of exploiting the matrix operations available in Matlab. The datum in the first row of Table 3.1 is for calculating 3516 Lyapunov exponents. To calculate one exponent it thus takes an average of  $\frac{4975,14}{3516} = 1.42$  seconds, when run on a computer with 8GB RAM and 3.20GHz processor.

| Profiling in Matlab            |                  |  |

|--------------------------------|------------------|--|

| Code                           | Time             |  |

| For calculating 3516 exponents | 4975.142 seconds |  |

| For calculating one exponent   | 1.42 seconds     |  |

TABLE 3.1: Profiling of Matlab code working on matrices.

While looking into the profiling data, six lines stood out as the absolutely most run lines. This is illustrated in Table 3.2, where more time is spent on the top six lines than on the seventh. To make this profiling data more comparable with the system specific profiling, the data in Table 3.2 have been divided by 3516 to estimate run times per exponent. This is because the system specific profiling was run for calculation of one exponent. The raw data can be found in Appendix A. The information in Table 3.2 indicate that the vast majority of the execution time is spent on calculating d1partial, which corresponds to the code in Listing 3.1.

```

for k=1:7

for n=1:2008

d1partial=curr_xV(k)-xV(n+(k-1)*4);

d1partial=d1partial*d1partial;

d1(1,n) = d1(1,n)+d1partial;

end

end

```

|             | Most run lines from Matlab profiling                           |              |                 |  |  |

|-------------|----------------------------------------------------------------|--------------|-----------------|--|--|

| Line number | Code                                                           | Time in msec | % of total time |  |  |

| 156         | $d1 partial = curr_x V(k) - xV(n + (k - 1) * tau);$            |              |                 |  |  |

| 157         | d1 partial = d1 partial * d1 partial;                          |              |                 |  |  |

| 158         | d1(1,n) = d1(1,n) + d1partial;                                 | 742.19       | 52.35           |  |  |

| 334         | select = cv(n) + (k-1) * tau;                                  |              |                 |  |  |

| 335         | dot2partial(n) = dot2partial(n) + (diffpoint(k) * xV(select)); | 167.55       | 11.81           |  |  |

| 342         | dot2(i) = (dot2(i) * dot2(i))/(d1(cv(i)) * df);                | 33.51        | 2.36            |  |  |

| 361         | sub = fudpoint - xV(ind : tau : ind + xVexpanse)';             | 5.55         | 0.39            |  |  |

LISTING 3.1: Snippet of C-similar Matlab code

TABLE 3.2: Most run lines from Matlab profiling

The general profiling indicates that over 50% of the total execution time is spent in the code blocks described by row one in Table 3.2. As seen in Listing 3.1, these three code lines are inside a double nested for-loop. This indicates that is it possible to use the method of Stitt and Vahid (ref. Chapter 2 Section 2.4) and extract the parallelism of the C-code in the possible implementation of an accelerator.

### 3.2 System specific profiling

For the system specific profiling, four different versions of the Lyapunov Exponent Calculation algorithm were profiled. They were all based on the initial Matlab code as illustrated in Figure 3.1. The codes listed in the tables in this section are as follows:

- Float1: First translation from Matlab to C. Uses floating point.

- Float2: First revision of Float1. Uses floating point.

- Fix1: First translation to fixed point from floating point.

• FloatOpt: Floating point version with optimizations based on experiences from fixed point version, includes loop unrolling.

To determine which version of the algorithm to use for further reference, the execution times while running on the SHMAC platform were measured. This is important data for comparison with timing data after the implementation of an accelerator, as a goal is to run the algorithm within a time schedule of having 10.24 seconds to calculate 32 Lyaponov exponents, i.e.  $\frac{10.24}{32} = 0.32$  seconds per exponent. The total execution times per exponent are listed in Table 3.3.

| Comparison of execution time on the SHMAC platform |        |        |         |          |

|----------------------------------------------------|--------|--------|---------|----------|

| Code                                               | Float1 | Float2 | Fix1    | FloatOpt |

| Time in seconds                                    | 71.66  | 69.57  | 7935.48 | 52.46    |

TABLE 3.3: Total execution time

As can be seen from Table 3.3, the fixed point version of the algorithm spends a tremendous amount of time compared to the floating point versions. The algorithm for fixed point is more complicated than the floating point algorithms, as displayed in Table B.4. This is because the Fix1 version emulates fixed point by using floating point, which again is emulated in software on the SHMAC platform. However, if the Fix1 code is rewritten to utilize the integer compatible hardware on the SHMAC platform, the emulation of fixed point via floating point would be not be necessary. Håkon Wikene at the Department of Computer and Information Science, highlighted that the amount of cycles required for integer instructions are a lot lower than those required for floating point instructions. The differences in cycles are presented in Table 3.4.

| Change in cycles [float/integer]                              |  |  |          |  |

|---------------------------------------------------------------|--|--|----------|--|

| Add/sub Multiplication Division                               |  |  | Division |  |

| Emulating cycles/integer cycles $1000/17$ $3300/17$ $2500/17$ |  |  |          |  |

TABLE 3.4: Cycles for instructions in Fix1 code if rewritten for integer utilization.Addition and subtraction spend same amount of cycles.

This would presumably lead to a reduction in run time for the Fix1 code on the SHMAC platform.

| (           | Comparison of calculation times |           |              |           |

|-------------|---------------------------------|-----------|--------------|-----------|

| Code        | Float1                          | Float2    | Fix1         | FloatOpt  |

| d1partial1  | 223.27                          | 216.18    | 37,870.46    | 156.91    |

| d1 partial2 | 37,686.96                       | 36,488.21 | 6,393,424.96 | 26,464.31 |

| dot2partial | $14,\!535.65$                   | 14,057.00 | 918,770.47   | 14,475.42 |

| dot2        | 2777.12                         | 2777.06   | 504,950.10   | 20.63     |

TABLE 3.5: System specific profiling, calculation times for different code versions in milliseconds.

Table 3.5 compares the time it takes to run the calculations that stood out in the general profiling on the SHMAC platform. Based on the numbers in Table 3.3 and Table 3.5, the percentage of the total execution time spent in each of the calculations can be found. This further helps to illustrate where most of the execution time is spent, as shown in Table 3.6.

| Comparison of percentage of runtimes |        |        |        |          |

|--------------------------------------|--------|--------|--------|----------|

| Code                                 | Float1 | Float2 | Fix1   | FloatOpt |

| d1 partial 1                         | 0.31%  | 0.31%  | 0.48%  | 0.30%    |

| d1 partial 2                         | 52.59% | 52.45% | 80.57% | 50.45%   |

| dot2partial                          | 20.28% | 20.21% | 11.58% | 27.60%   |

| dot2                                 | 3.88%  | 3.99%  | 6.36%  | 0.04%    |

TABLE 3.6: System specific profiling, percentage of total runtime spent on calculations.

The calculations of d1partial in codes Float1 and Float2 are carried out as in Listing 3.2.

```

for (k=0; k < m; k++)

{

for (i=0; i < d1size; i++)

{

d1partial=curr_xV[k]-xV[i+k*tau];

d1partial=d1partial*d1partial;

d1[i] = d1[i]+d1partial;

}

}</pre>

```

```

LISTING 3.2: Snippet of C code calculation of d1partial

```

After analysis of the percentage of total time spent on the different blocks (ref. Table 3.6), two of the calculations stood out: d1partial2 and dot2partial, d1partial2 is more than twice as time consuming as dot2partial. Further, the codes for d1partial1 and d1partial2 are basically the same, only differing in starting value in their for-loops<sup>1</sup>. d1partial1 is the calculation of the first point, while d1partial2 is of the remaining 167. The time spent on calculating d1partial2 is therefore about 167 times greater than the time spent on calculating d1partial1.

Based on the data evolved from the analysis in this chapter and the aim of making the calculation of Lyapunov exponents faster than the previously mentioned time frame on the SHMAC platform, the timing results from the FloatOpt version is chosen as a reference for results after implementation of an accelerator. The FloatOpt version spends 16.8 seconds less time than the second fastest code. Without altering the SHMAC platform it takes minimum 52.46 seconds to calculate one Lyapunov exponent. It is necessary to decrease the run time for it to be applicable in the seizure prediction.

Due to the massive percentage of total execution time spent on calculating d1partial, this will be the first target for acceleration in the effort to speed up the code, with dot2partial as a possible extension.

The calculation of d1partial in FloatOpt differs from the others in that instead of having a double-nested for-loop, the outer loop, running from k = 0: 7, is unrolled. This loop unrolling is shown in Listing 3.3. Loop unrolling has also been exploited in the calculation of dot2partial in FloatOpt, illustrated in Listing 3.4. The two code excerpts in Listings 3.3 and 3.4 do look somewhat similar, enabling the opportunity to exploit this similarity to speed up the code even further than with just looking at d1partial. The calculation of dot2partial is, however, in a for-loop which varies in size, making it more challenging to implement.

<sup>&</sup>lt;sup>1</sup>Iterating from i = th : d1size and i = 0 : d1size, respectively.

```

for (i = 0; i < d1size; i++)

{

float d1temp = 0;

//Complete loop unroll of k-loop

d1partial=curr_xV[0]-xV[i+0*tau];

d1temp += d1partial*d1partial;

d1partial=curr_xV[1]-xV[i+1*tau];

d1temp += d1partial*d1partial;

d1partial=curr_xV[2]-xV[i+2*tau];

dltemp += dlpartial*dlpartial;

d1 partial = curr_x V[3] - xV[i+3*tau];

dltemp += dlpartial*dlpartial;

d1partial=curr_xV[4]-xV[i+4*tau];

d1temp += d1partial*d1partial;

d1partial=curr_xV[5]-xV[i+5*tau];

d1temp += d1partial*d1partial;

d1partial=curr_xV[6]-xV[i+6*tau];

d1temp += d1partial*d1partial;

d1[i] = d1temp;

```

}

#### LISTING 3.3: Snippet of calculation of *d1partial2* in FloatOpt

```

select=cv[i];

dot2partial=dot2partial+(diffpoint[0]*xV[select]);

select=cv[i]+tau;

dot2partial=dot2partial+(diffpoint[1]*xV[select]);

select=cv[i]+2*tau;

dot2partial=dot2partial+(diffpoint[2]*xV[select]);

select=cv[i]+3*tau;

dot2partial=dot2partial+(diffpoint[3]*xV[select]);

select=cv[i]+4*tau;

dot2partial=dot2partial+(diffpoint[4]*xV[select]);

select=cv[i]+5*tau;

dot2partial=dot2partial+(diffpoint[5]*xV[select]);

select=cv[i]+6*tau;

dot2partial=dot2partial+(diffpoint[6]*xV[select]);

```

#### LISTING 3.4: Snippet of calculation of *dot2partial2* in FloatOpt

This loop unrolling, extracting the parallelism of the C-code, is somewhat the same idea Stitt and Vahid exploited in their *Hardware/software partitioning of software binaries*. The replacement of software with hardware has, however, not yet been carried out in this case, and is therefore a natural next step in the process of speeding up the calculation.

## Chapter 4

## **Implementation and Verification**

The first step in discovering the benefits of implementing d1partial is to design the hardware module. One way to implement the d1partial is to make a multiply-accumulate module which is likely to enhance the run time of this calculation, especially if one utilizes pre-fetching of the data by having an own module for address calculation. However, due to the nature of the intended target, another approach is to unroll the nested for-loops. This would probably, contrary to a pure multiply-accumulate acceleration, lead to less cycles required to run the accelerator. An example of unrolling of the d1partial-calculation is shown in the FloatOpt code in Listing 3.3. The target for implementation takes, as displayed in Table 3.6, 50.45% of the execution time of the FloatOpt code. As stated in Chapter 3, a Lyapunov point is based on 32 simultaneous Lyapunov exponents, and the Lyapunov exponent is calculated based on a 10.24 second time window. This, together with the percentage of total execution time, means that the accelerator should spend less than  $0.50 \times \frac{10.24}{32} = 0.16$  seconds.

### 4.1 Design

Initially, when looking at the target, two options for the design were clear. The Ccodes which are going to work with the accelerator, operates on numbers represented in the floating point standard. Therefore, making an accelerator which takes in floating point numbers and operates on these was an option. Another option was conversion to fixed point and then operate directly on these. However, two other options appeared while learning about the fixed point package[19, p.283] and floating point package[19, p.284] of VHDL. This means that there are four different approaches to implementing the accelerator:

- Including separate modules for addition/subtraction and multiplication in the design using standard VHDL, floating point.

- Converting floating point input to std\_logic\_vectors and make logic from standard VHDL to assure the location of the decimal point, fixed point.

- Use functions and type included in the floating point package, floating point.

- Use functions and type included in the fixed point package. This package includes conversion from floating point to fixed. Fixed point.

The first option concerns the implementation of modules for doing floating point operations and directly operating on the data from the CPU using standard VHDL. This approach will however not be implemented, as it basically is like adding an FPU with little functionality to the design, and a full function FPU is currently being worked on by others on the SHMAC project. The second is about conversion from floating point to fixed point and uses the standard package of VHDL to implement the code and the necessary logic to keep track of the location of the decimal point. The third and fourth are somewhat similar in the description, as they both use expansion packages to VHDL, which includes types *float*, *sfixed* and *ufixed* and arithmetic operators for these types. Hence, the third and fourth approaches are to use these packages to make a floating-point and fixed-point implementation of the *d1partial* calculation, respectively.

The general structure of the design will however be somewhat equal for all approaches, and is illustrated in Figure 4.1. The actual implementations of all approaches are attached in Appendix D.

FIGURE 4.1: Illustration of general module.

#### 4.1.1 Approach expansion package, floating point

This approach uses the expansion package for floating point numbers and operators, such as +, -, \* and /. It has two 32-bit floating point input ports and a 32-bit floating point output port. The first design is a straight forward implementation of the C-code without any performance enhancements. After this, the technique used for increasing the performance is loop unrolling, as discussed in Chapter 2 Section 2.3. The unroll factors are for the k-loop either not unrolled or completely unrolled, due to the fact that it iterates over 7 numbers, and 7 is a prime number. Therefore, unrolling factor of 7 or none are the two available options whilst avoiding additional control for other unroll factors. For the *i*-loop, the factors are 2,4 or 8. Next possible unroll factor for the i-loop without making additional control logic is 251, as the number 2008 can be factorized to 2 \* 2 \* 2 \* 251 and 251 is a prime number.

Table 4.1 displays the synthesis data for the different designs. As exposed by the data, the designs utilize different unroll factors for k and i. Designs 1 through 8 in Tables 4.1 and 4.2 are as illustrated in Figure 4.1, with a *Readin*-module, one or several *Calculation*-module(s) and a *Readout*-module. Designs 9 and 10 are without inclusion of a *Readout*-module, and values are continuously read out as they are calculated.

| Designs: 207,360 Slice LUTs available on Virtex5 model |                   |             |                 |                       |

|--------------------------------------------------------|-------------------|-------------|-----------------|-----------------------|

| Design number                                          | Unroll factor k,i | #Slice LUTs | % of Slice LUTs | Maximum Frequency     |

| 1                                                      | None,0            | 9505        | 4%              | $15.565 \mathrm{MHz}$ |

| 2                                                      | None,2            | 144,056     | 69%             | $11.872 \mathrm{MHz}$ |

| 3                                                      | None,4            | 268,887     | 129%            | 9.682MHz              |

| 4                                                      | None,8            | 470,221     | 226%            | 9.495MHz              |

| 5                                                      | Full,0            | 40,558      | 19%             | 5.706MHz              |

| 6                                                      | Full,2            | 210,065     | 101%            | $5.061 \mathrm{MHz}$  |

| 7                                                      | Full,4            | 400,558     | 193%            | $4.595 \mathrm{MHz}$  |

| 8                                                      | Full,8            | 727,126     | 350%            | $4.556 \mathrm{MHz}$  |

| 9                                                      | None,0 w/o RO     | 6498        | 3%              | $15.617 \mathrm{MHz}$ |

| 10                                                     | Full,0 w/o RO     | 36,400      | 17%             | 6.341MHz              |

TABLE 4.1: Area and performance for float extension package approach

Design 1 is not at all unrolled, each of the d1[i]-s are calculated at separate clock cycles. This results in the hardware having just one calculation-module. The designs of Table 4.1 iterates first over i and then increments k and repeats. This makes the *Readout* module necessary; one needs to iterate through all ks, as the d1[i] calculation is dependent on each of the ks from 0 to 6. To save hardware area, this can be implemented differently, iterating firstly over k and then increment i. This means, that every seventh clock cycle, a value of the d1-vector is ready to be output. These can then be read into a vector in the C-code or to memory, and eliminate the necessity of saving the d1-vector until all 2008 calculations are done, which saves both area and cycles. Removing the *Readout* module does, however, eliminate the opportunity to have other unroll factors for i than 0, without implementing multiple output ports. There are therefore only two designs without *Readout* module, no unrolling, and full unrolling of k. Full unrolling of k will result in a d1-value on the output every clock cycle, while no unrolling will result in a value every seventh clock cycle.

The maximum frequencies of the floating point designs are low, indicating long critical paths. This can be explained by David Bishop's statement: "the hardware of the floating point can be up to  $3 \times$  more than that of the fixed point package" [20].

#### 4.1.2 Approach expansion package, fixed point

The fixed point approach uses the expansion package for fixed point numbers and operators, such as +, -, \* and /. It has two 32-bit floating point input ports and a 32-bit floating point output port, which makes it necessary to convert from floating point to fixed point and vice versa. This has also been included in the package, thus conversion to/from float/fixed is not a design issue. The designs 1 through 10 are otherwise carried out in the same way as those of the floating point approaches.

|               | Designs: 207,360 Slice LUTs available on Virtex5 model |             |                 |                       |

|---------------|--------------------------------------------------------|-------------|-----------------|-----------------------|

| Design number | Unroll factor k,i                                      | #Slice LUTs | % of Slice LUTs | Maximum Frequency     |