# Efficient Implementation of Cross-Correlation in Hardware

David Eirik Taylor

Electronics System Design and InnovationSubmission date:May 2014Supervisor:Kjetil Svarstad, IETCo-supervisor:Lloyd Clark, Atmel Norway AS

Norwegian University of Science and Technology Department of Electronics and Telecommunications

#### Abstract

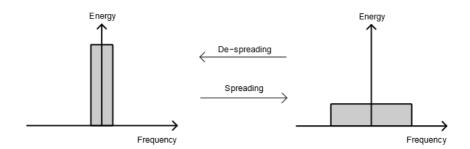

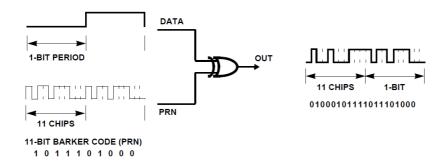

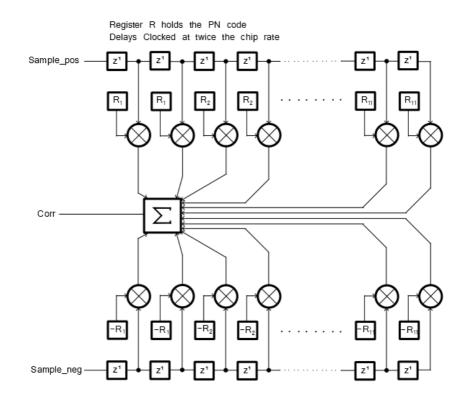

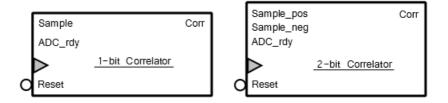

Low-area matched filter and correlator designs are explored in this thesis, for ADC resolutions of 1- and 2-bits. Correlators are used extensively in spread-spectrum communication technologies, where they serve as a means of detecting a known pseudo-random sequence (PN code). The correlator designs presented here are intended for direct-sequence spread spectrum (DSSS) radio, where the data to be sent is expanded using either the PN code, or the inverse of the PN code. The correlator or matched filter will then respond with a positive or negative peak when a data bit is detected.

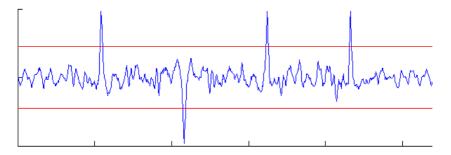

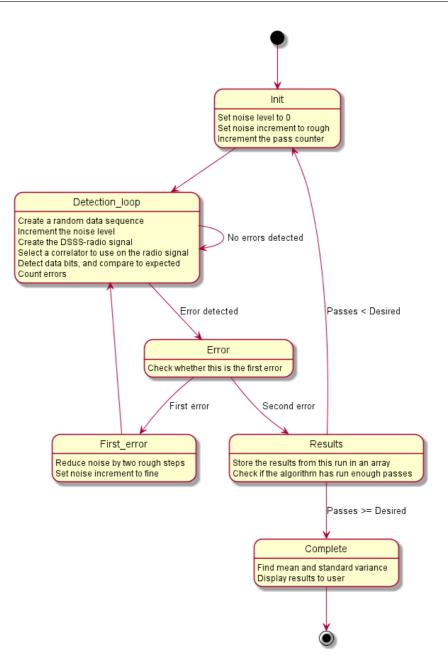

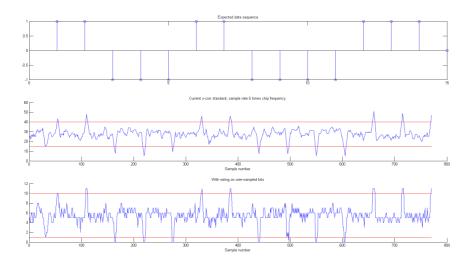

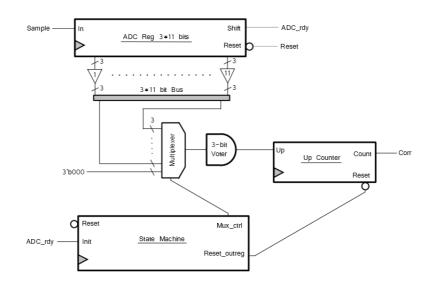

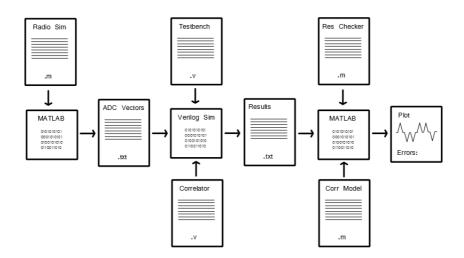

To test various correlator designs a testbench is developed in MATLAB, where a DSSS data sequence can be created and corrupted with an adjustable level of white Gaussian noise. The data stream with noise is filtered with an automatic gain stage, and sampled using an ADC of variable resolution and sampling rate. The sampled signal is then fed to a mathematical model of the given correlator design to see how it behaves. For an objective measure of performance in the presence of noise, a novel noise immunity test bench was developed, which subjects the correlator models to a signal with increasing levels of noise. The SNR where the correlator is no longer able to extract the correct data bits from the signal is considered the noise immunity level.

Several HDL matched filter designs are presented for both 1- and 2-bits of ADC resolution. The 1-bit matched filters are tested using the Barker-11 PN code, whereas the 2-bit correlators are tested using a 36 chip long chirp sequence. For both the 1- and 2-bit correlators, a specific design type using a multiplexed parallel counter was the most area efficient. A novel grouping correlator design is also presented for 2-bit operation, however the area required by this design is larger than that of the other designs. The results from the grouping design indicate that a significant reduction in dynamic power is present. In terms of power efficiency, the dual correlator designs. The design of parallel bit counters used in the matched filters are also presented, along with the area per bits required for each design.

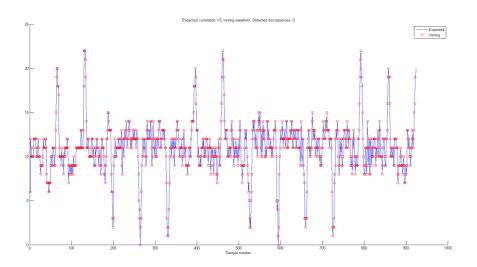

Verification of the designs is performed using mathematical correlator models, which are subjected to the same input as the Verilog modules. The results from these two tests are compared, and any discrepancies are reported to the user of the testbench. The mathematical and Verilog correlator models are fed with a simulated real-world input signal, which is essentially random noise for purposes of testing functionality.

#### Sammendrag

Temaet for denne masteroppgaven er implementasjon av matchetfiltre og korrelasjonsenheter med minimalt arealforbruk, og for ADC-oppløsninger på henholdsvis 1 og 2 bit. Korrelasjonsenheter brukes utbredt innen spreadspectrum kommunikasjonsteknologi, der de har som oppgave å oppdage en på forhånd kjent pseudotilfeldig sekvens (PN kode). Enhetene presentert her er utviklet for "direct-sequence spread spectrum" (DSSS) radio, der hvert enkelt databit representeres enten med PN koden, eller den inverse av PN koden, avhengig av verdien til databiten. Korrelasjonsenheten vil gi maksimalt eller minimalt utslag hver gang PN koden mottas, og disse utslagene kan leses av som de opprinnelige databitene.

For å teste støypåvirkning og andre faktorer på korrelasjonen ble en testbenk utviklet i MATLAB, der en DSSS datasekvens kan lages og ispes med et valgt nivå av Gaussisk hvit støy. Datastrømmen med støy blir så normalisert, og deretter samplet ved hjelp av en analog til digital konverter med justerbar oppløsning og samplingsrate. Det samplet signalet settes så inn i en matematisk modell av korrelasjonsenheten som testes for å se hvordan den oppfører seg. For å få et objektivt mål på evnen til å motstå støy ble det utviklet en støyimmunitetstestbenk, som tilfører et signal med stadig høyere støynivå til en korrelasjonsmodell. SNR-nivået der dataen i signalet ikke lenger tolkes riktig blir satt som støyimmuniteten til korrelasjonsmodellen.

Flere HDL matchetfilterdesign presenteres for både 1 og 2 bit med oppløsning. 1 bit matchetfilterene bruker Barker-11 sekvensen som PN kode, mens 2 bit enhetene bruker en 36 chip lang chirpsekvens. For både 1 og 2 bit enhetene var det et bestemt design som brukte en multiplexed parallellteller som var mest arealeffektiv. En original korrelasjonsenhet som grupperer ADC samples blir også presentert for 2 bit ADC oppløsning, og som viser en betydelig reduksjon i dynamisk strømforbruk. Strømforbruket til dual correlator designene viste en halvering i strømforbruket sammenlignet med de andre enhetene. Design av parallellbittellerne som brukes i korrelasjonsenheten blir også presentert, sammen med arealet per telte bit.

Designverifisering er gjort ved bruk av matematiske modeller, som utsettes for de samme inngangssignaler som Verilog modulene. Resultatene fra disse to testene sammenlignes, og forskjeller rapporteres til brukeren av testbenken. Både de matematiske og Verilogmodulene mates med en simulert DSSS signal, som for testformål er tilfeldig støy.

# Thesis Details

Candidate Name: David Eirik Taylor Assignment Title: Efficient Implementation of Cross-correlation in Hardware Supervisor: Kjetil Svarstad External Supervisor: Lloyd Clark, Atmel Norway AS

#### Problem description

Cross-correlation is a signal processing technique that is extremely useful in wireless receivers, radar, image recognition, and many other scenarios in which a pattern must be reliably detected in noise. This thesis would explore how to implement cross-correlation in hardware to minimize gate count and/or power consumption. Of special interest for this project are implementations in which the signal to be correlated is obtained from a low-resolution analog-to-digital converter with only one or two bits of output.

### Preface

This Master's thesis was written at the Norwegian University of Science and Technology (NTNU), under the department of Electronics and Telecommunications. It signifies the academic pinnacle of my time at University, and the final barrier before earning a Master of Science degree in Electrical Engineering.

I would like to thank my supervisor at NTNU, Professor Kjetil Svarstad, and my external supervisor at Atmel, Lloyd Clark, for always being available when required, and for providing valuable feedback during the course of this thesis. I would also like to thank my friends here in Trondheim for making these years the most fun in my life, and my parents for encouraging my pursuit of higher education.

David Eirik Taylor Trondheim, May 2014 Contents

# Contents

| Li            | st of                           | Figure                                             | es                                 | xi                               |

|---------------|---------------------------------|----------------------------------------------------|------------------------------------|----------------------------------|

| $\mathbf{Li}$ | st of                           | Tables                                             | s xi                               | iii                              |

| 1             | <b>Intr</b><br>1.1<br>1.2       | Contri                                             | ion and Motivation<br>ibution      | <b>1</b><br>1<br>2               |

| 2             | <b>Bac</b><br>2.1<br>2.2<br>2.3 | Digita<br>Direct                                   | nd Material<br>l cross Correlation | <b>3</b><br>3<br>4<br>7          |

| 3             | <b>Spe</b><br>3.1<br>3.2<br>3.3 | Radio<br>Correl                                    | ator Simulator                     | <b>9</b><br>10<br>11<br>12       |

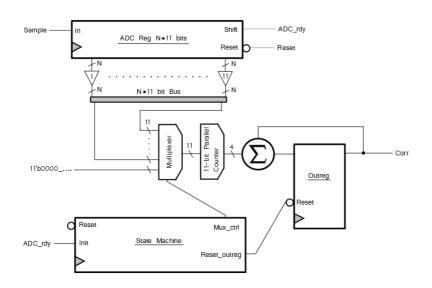

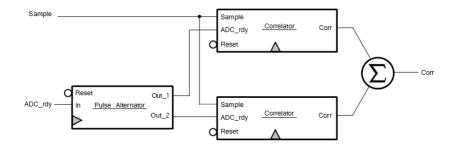

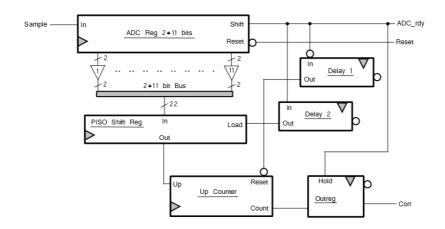

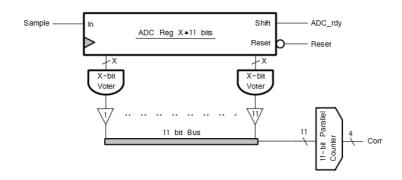

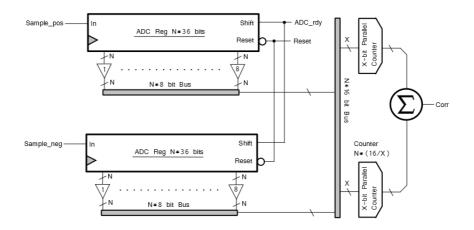

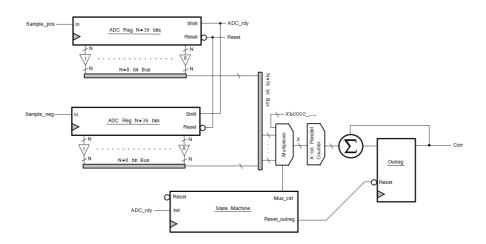

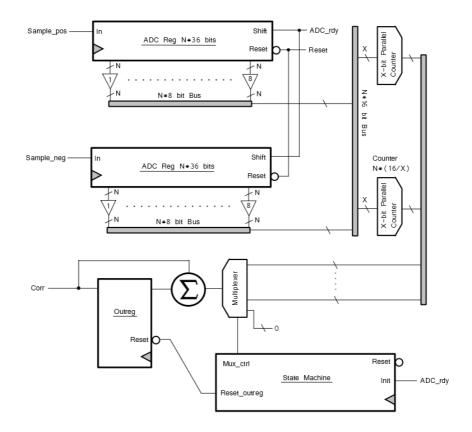

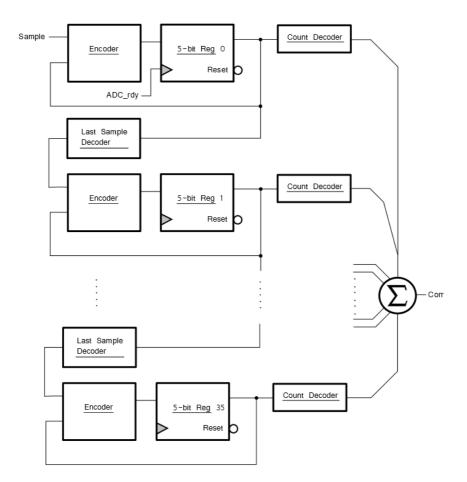

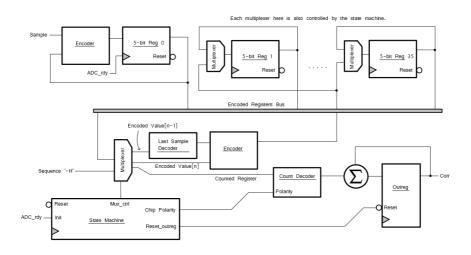

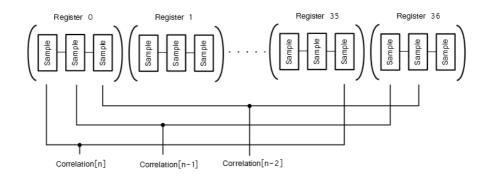

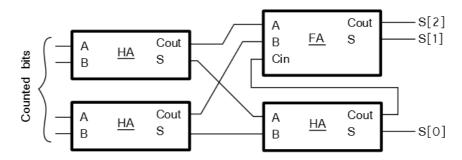

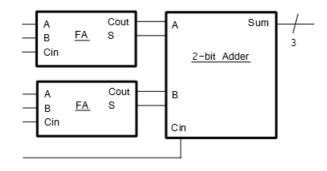

| 4             | <b>Arc</b><br>4.1<br>4.2        | One-b<br>4.1.1<br>4.1.2<br>Two-b<br>4.2.1          | it Correlator Implementation       | 15<br>16<br>22<br>27<br>28       |

|               | 4.3                             | 4.2.2<br>4.2.3<br>4.2.4<br>Hardw<br>4.3.1<br>4.3.2 | Multiplexed Sum Correlator         | 29<br>30<br>32<br>40<br>40<br>41 |

|                | 4.3.3                                                                                                                                                                                                                                     | Other Parallel Bit Counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | 4.3.4                                                                                                                                                                                                                                     | Majority Voters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Log            | ical Ve                                                                                                                                                                                                                                   | nrification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -              |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| -              |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0.2            |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <b>۲</b> 9     | 0.2.0                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| -              |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.5            | Verific                                                                                                                                                                                                                                   | ation of the Parallel Bit Counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $\mathbf{Res}$ | ults                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.1            | Paralle                                                                                                                                                                                                                                   | el Bit Counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.2            | 1-bit (                                                                                                                                                                                                                                   | Correlators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 6.2.1                                                                                                                                                                                                                                     | Area Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 6.2.2                                                                                                                                                                                                                                     | Noise Immunity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 6.2.3                                                                                                                                                                                                                                     | Operational Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 6.2.4                                                                                                                                                                                                                                     | Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 6.2.5                                                                                                                                                                                                                                     | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.3            | 2-bit (                                                                                                                                                                                                                                   | Correlators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 6.3.1                                                                                                                                                                                                                                     | Operational Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 6.3.2                                                                                                                                                                                                                                     | Area Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 6.3.3                                                                                                                                                                                                                                     | Noise Immunity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 6.3.4                                                                                                                                                                                                                                     | Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Dise           | cussion                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| • •            |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| • •            |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| • • -          |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.0            | Choice                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Con            | nclusio                                                                                                                                                                                                                                   | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8.1            | Future                                                                                                                                                                                                                                    | e Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

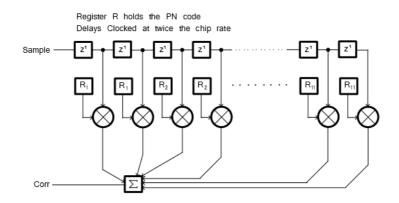

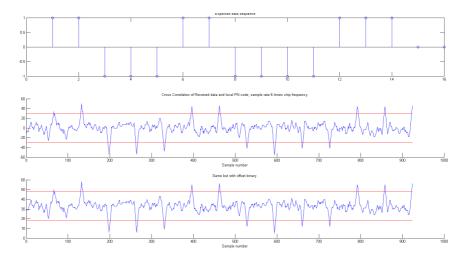

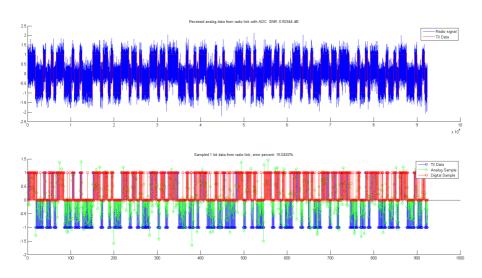

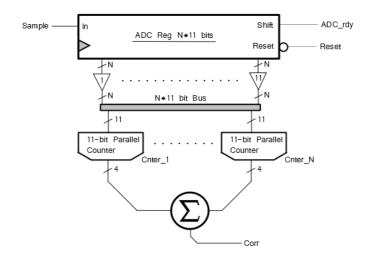

| Bib            | liograp                                                                                                                                                                                                                                   | bhy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |