# Trade-offs between Performance and Robustness for Ultra Low Power/Low Energy Subthreshold D flip-flops in 65nm CMOS

Magne Værnes

Master of Science in ElectronicsSubmission date:June 2013Supervisor:Snorre Aunet, IETCo-supervisor:Anders Hagen, Q-Free ASA

Norwegian University of Science and Technology Department of Electronics and Telecommunications

#### Abstract

The need for Ultra Low Power systems has increased with increasing number of portable devices. The maintenance costs of battery powered systems can be greatly reduced by improving the battery time, especially in places where battery replacement is hard or impossible. Implementation of subthreshold D flip-flops in layout is one step closer to having a subthreshold building block library. The task for this thesis is to implement D flip-flop blocks, which are highly suitable for subthreshold operation in layout. These are the PowerPC 603, C<sup>2</sup>MOS, a Classic NAND-based D flipflop, and two Minority3-based D flip-flops. The D flip-flops are first custom designed for 250mV in schematic at transistor level, and then implemented in layout. The implementation in layout focuses on high robustness against process variations, by using high regularity for the cost of area.

The D flip-flops are simulated in both schematic and layout, and the results are compared to each other and earlier results found in papers. The results show that the PowerPC 603 has the lowest PDP, the lowest power consumption, very low propagation delay, and an average relative standard deviation for delay. The  $C^2MOS$  has the lowest propagation delay, low power consumption and low PDP results. However, it has the highest relative standard deviation on delay. The Minority3-based D flip-flops have a very low relative standard deviation for delay, which makes them the most robust against process variations in this sense. However, they have the highest propagation delay, highest power consumption and PDP, and consumes the highest chip area. The Classic NAND-based D flip-flop has good PDP and power consumption results, but a high delay and average standard deviation for delay. Earlier papers show similar results for the  $C^2MOS$  and the PowerPC 603, but no results are found for the rest. Future work consists of implementing and testing forced-stacked blocks, body biasing, high threshold voltage transistors, and tape-out measurements.

## Preface

This Thesis is the finishing part of the degree Master of Science in Circuit and System design at the Department of Electronics and Telecommunication, Faculty of Information Technology, Mathematics and Electrical Engineering, at the Norwegian University of Science and Technology (NTNU). It is done in cooperation with Q-free ASA Trondheim, with Professor Snorre Aunet at NTNU and Anders Hagen from Q-free as supervisors, and Professor Trond Ytterdal at NTNU as cosupervisor. I chose low power design for my Thesis because I find it interesting, and because I believe it will be an important part of everyday electronics in the future. The task was challenging, and gave me valuable knowledge in subthreshold operation, IC-design at schematic and layout, process variations, D flip-flop functionality and more.

I will firstly like to thank my supervisor Professor Snorre Aunet for his help and guidance through the project. He has shown great interest to the task, and always been available for help in his office, on the phone or through email. Secondly, I would like to thank co-supervisors Anders Hagen and Trond Ytterdal for the help provided by working with my Thesis.

Third, I would like to thank my fellow students Joacim Dybedal, Jonathan Bjerkedok and Lars-Frode Schjolden at the study room for the support and the RC-helicopter flying in the breaks.

Forth, I would like to thank my family for their support.

Last, but not least, I would like to thank my partner Tuva for supporting me through the whole process.

## Contents

| 1                        | $\mathbf{Intr}$ | introduction 1   |                                                                                                                                                 |            |  |  |

|--------------------------|-----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

|                          | 1.1             | Overv            | iew of the Thesis                                                                                                                               | 2          |  |  |

| <b>2</b>                 | Pro             | blem I           | Description                                                                                                                                     | 3          |  |  |

| 3 Theoretical Background |                 |                  |                                                                                                                                                 | <b>5</b>   |  |  |

|                          | 3.1             | Subth            | reshold Operation                                                                                                                               | 5          |  |  |

|                          |                 | 3.1.1            | Subthreshold Delay                                                                                                                              | 6          |  |  |

|                          |                 | 3.1.2            | Subthreshold Power Consumption                                                                                                                  | 6          |  |  |

|                          |                 | 3.1.3            | Subthreshold Leakage Current                                                                                                                    | 7          |  |  |

|                          | 3.2             | Transi           | stor Matching                                                                                                                                   | 8          |  |  |

|                          | 3.3             | Robus            |                                                                                                                                                 | 8          |  |  |

|                          |                 | 3.3.1            | Temperature Variations                                                                                                                          | 8          |  |  |

|                          |                 | 3.3.2            | Process Variations                                                                                                                              | 9          |  |  |

|                          |                 | 3.3.3            | Well-Proximity-Effect                                                                                                                           | 9          |  |  |

|                          | 3.4             |                  | uilding Blocks                                                                                                                                  | 10         |  |  |

|                          |                 | 3.4.1            | Inverter                                                                                                                                        | 10         |  |  |

|                          |                 | 3.4.2            | Transmission Gate                                                                                                                               | 10         |  |  |

|                          |                 | 3.4.3            | Clocked Inverter                                                                                                                                | 10         |  |  |

|                          |                 | 3.4.4            | Minority3 Gate                                                                                                                                  | 10         |  |  |

|                          |                 | 3.4.5            | D-latches                                                                                                                                       | 11         |  |  |

|                          | 9.5             | 3.4.6            | The D flip-flop                                                                                                                                 | 14         |  |  |

|                          | 3.5             | -                | flop Design Structures                                                                                                                          | 15         |  |  |

|                          |                 | 3.5.1            | The Classic NAND-based D flip-flop                                                                                                              | 15         |  |  |

|                          |                 | 3.5.2            | Minority3-based D flip-flop $\dots \dots \dots$ | 15<br>16   |  |  |

|                          |                 | $3.5.3 \\ 3.5.4$ | $C^2MOS D$ flip-flop                                                                                                                            | $16 \\ 16$ |  |  |

|                          | 3.6             |                  | g and Delay                                                                                                                                     | 10         |  |  |

|                          | $3.0 \\ 3.7$    |                  | stor Layout                                                                                                                                     | 18         |  |  |

|                          | 5.7             | 3.7.1            | Substrate Connection                                                                                                                            | 18         |  |  |

|                          |                 | 3.7.1<br>3.7.2   | Dummy transistors                                                                                                                               | 18         |  |  |

|                          |                 | 3.7.2<br>3.7.3   | Design Rules                                                                                                                                    | 19         |  |  |

|                          |                 | 3.7.4            | Parasitic Extraction                                                                                                                            | 19         |  |  |

|                          |                 | 0.1.1            |                                                                                                                                                 | 10         |  |  |

| 4                        | Sele            | cting            | D flip-flop Implementation and Design in Schematics                                                                                             | <b>21</b>  |  |  |

|                          | 4.1             | Selecti          | ing D flip-flop Designs                                                                                                                         | 21         |  |  |

|                          |                 | 4.1.1            | Classic NAND-based D flip-flop                                                                                                                  | 21         |  |  |

|                          |                 | 4.1.2            | Minority3-based D flip-flop                                                                                                                     | 22         |  |  |

|                          |                 | 4.1.3            | Minority3-based D flip-flop without Set Input                                                                                                   | 22         |  |  |

|                          |                 | 4.1.4            | $C^2MOS D$ flip-flop                                                                                                                            | 22         |  |  |

|                          |                 | 4.1.5            | PowerPC 603 D flip-flop                                                                                                                         | 22         |  |  |

|                          | 4.2             |                  | ning Schematics for D flip-flop building blocks                                                                                                 | 23         |  |  |

|                          |                 | 4.2.1            | Sizing of Transistors                                                                                                                           | 23         |  |  |

|                          |                 | 4.2.2            | Deciding the Supply Voltage                                                                                                                     | 24         |  |  |

|                          |                 | 4.2.3            | Designing the Inverter                                                                                                                          | 24         |  |  |

|                          |                 | 4.2.4            | Designing the Clocked Inverter                                                                                                                  | 24         |  |  |

|          |                | 4.2.5 Designing the Transmission Gate                                                   | 25        |

|----------|----------------|-----------------------------------------------------------------------------------------|-----------|

|          |                | 4.2.6 Designing the Minority3-Gate                                                      |           |

|          |                | 4.2.7 Designing the Minority3-based NAND-gate                                           |           |

|          |                | 4.2.8 Designing the two-input NAND                                                      |           |

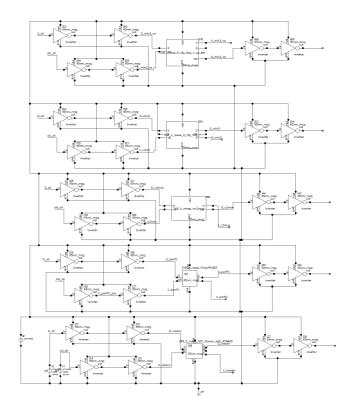

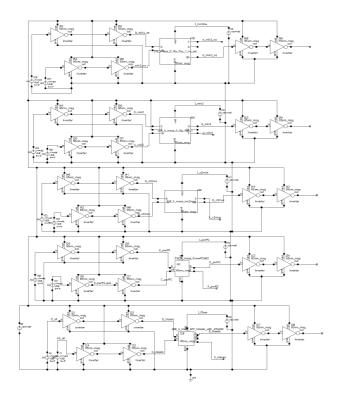

|          | 4.3            | Designing the Schematics for the D flip-flops                                           |           |

|          |                | 4.3.1 Designing the Classic NAND D flip-flop                                            |           |

|          |                | 4.3.2 Designing the Minority3 D flip-flop                                               |           |

|          |                | 4.3.3 Designing the Minority3 no-set D flip-flop                                        |           |

|          |                | 4.3.4 Designing the C <sup>2</sup> MOS D flip-flop $\ldots \ldots \ldots \ldots \ldots$ |           |

|          |                | 4.3.5 Designing the PowerPC 603 D flip-flop                                             |           |

|          |                | 4.3.6 D flip-flop Transistor Count                                                      |           |

|          | 4.4            | Modifying the Transistor Dimensions To Improve the Regularity .                         |           |

| <b>5</b> | Imp            | elementation in Layout                                                                  | 33        |

|          | $5.1^{-1}$     | Transistor Layout                                                                       | 33        |

|          |                | 5.1.1 Substrate Connection                                                              | 33        |

|          |                | 5.1.2 Parasitic Extraction                                                              | 33        |

|          |                | 5.1.3 nWell placement and sizing                                                        | 33        |

|          |                | 5.1.4 Regularity                                                                        | 34        |

|          |                | 5.1.5 Design Rules                                                                      | 35        |

|          | 5.2            | D Flip-Flop Implementation in Layout                                                    | 37        |

| 6        | Test           | tbenches                                                                                | 39        |

|          | 6.1            | Balancing Testbench                                                                     | 39        |

|          | 6.2            | The Delay Testbench                                                                     |           |

|          | 6.3            | The Power and PDP Testbench                                                             | 40        |

| 7        | $\mathbf{Sim}$ | ulations                                                                                | <b>43</b> |

|          | 7.1            | Transistor Layout                                                                       | 43        |

|          |                | 7.1.1 Parasitic Extraction                                                              | 43        |

|          |                | 7.1.2 nWell placement and sizing                                                        |           |

|          | 7.2            | D flip-flop functionality                                                               |           |

|          | 7.3            | Delay Simulation                                                                        | 43        |

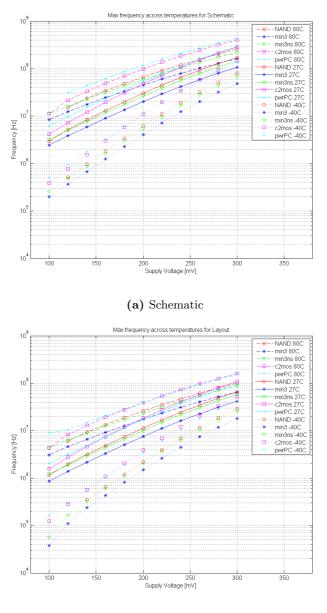

|          | 7.4            | Maximum D flip-flop frequency based on maximum delay                                    | 44        |

|          | 7.5            | Static Power Simulation                                                                 |           |

|          | 7.6            | Total Power Consumption                                                                 | 45        |

|          | 7.7            | Maximum Power Consumption                                                               |           |

|          | 7.8            | Power-Delay-Product                                                                     | 46        |

|          | 7.9            | Monte Carlo Delay Simulation                                                            | 46        |

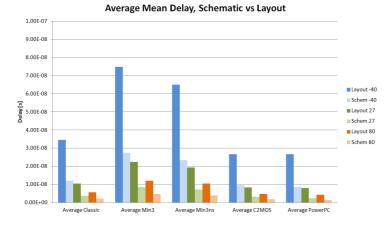

|          |                | 7.9.1 Average Mean Delay and Standard Deviation for Schematic<br>and Layout             | 47        |

|          |                | 7.9.2 Average Mean Delay for Schematic and Layout at different                          | TI        |

|          |                | Temperatures                                                                            | 47        |

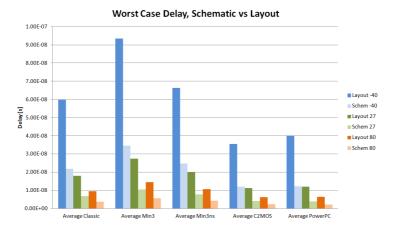

|          |                | 7.9.3 Worst Case Mean Delay for Schematic and Layout at dif-                            | -11       |

|          |                | ferent Temperatures                                                                     | 47        |

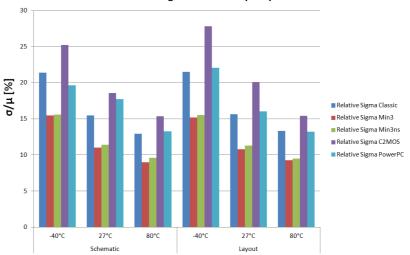

|          |                | 7.9.4 Relative Standard Deviation Comparison                                            | 47        |

|          | 710            | Running Simulations with OCEAN scripts                                                  | 47        |

|          | 1.10           |                                                                                         | -+1       |

|   | 7.11 | Simulation Input Signals                                       | 48  |

|---|------|----------------------------------------------------------------|-----|

| 8 | Res  | ults from Simulations                                          | 49  |

|   | 8.1  | Transistor Layout                                              | 49  |

|   |      | 8.1.1 Parasitic Extraction                                     | 49  |

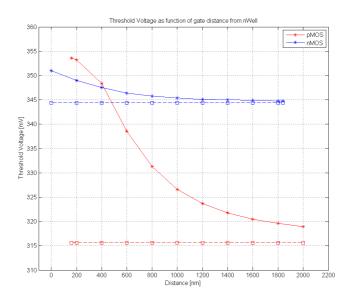

|   |      | 8.1.2 nWell Placement and Sizing                               | 50  |

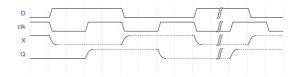

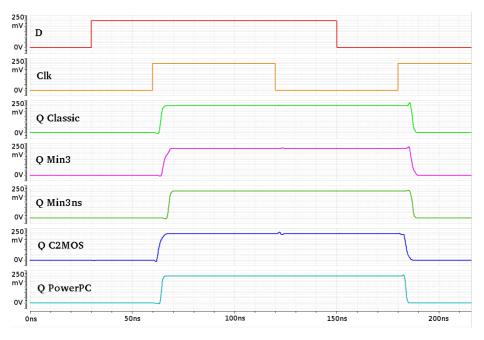

|   | 8.2  | D flip-flop functionality                                      | 51  |

|   | 8.3  | Delay Comparison of D flip-flops                               | 52  |

|   | 0.0  | 8.3.1 Master latch delay                                       | 52  |

|   |      | 8.3.2 Slave latch delay                                        | 58  |

|   |      | 8.3.3 Total D flip-flop delay                                  | 64  |

|   | 8.4  | Maximum D flip-flop frequency based on maximum delay           | 70  |

|   | -    | •                                                              |     |

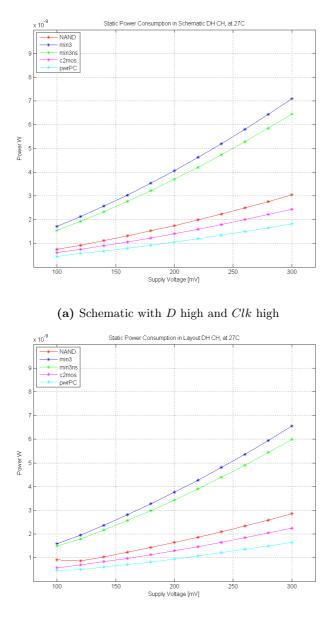

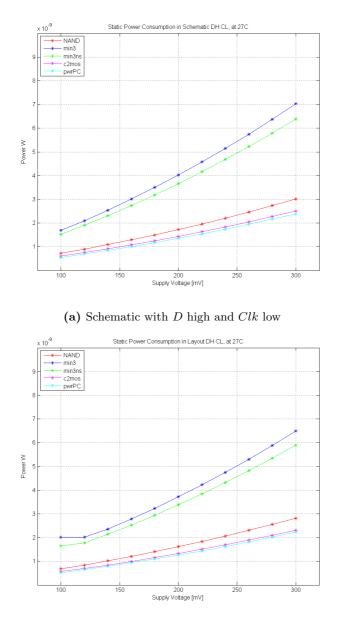

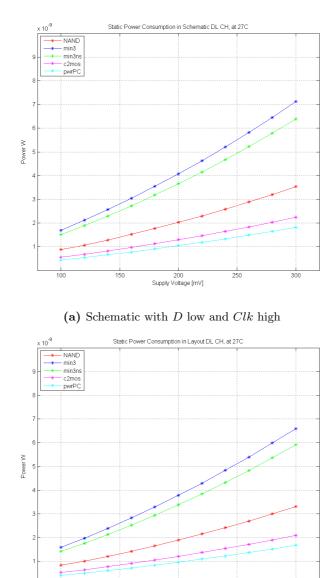

|   | 8.5  | Static Power Consumption                                       | 74  |

|   | 0.0  | 8.5.1 Static Power Comparison at Different Temperatures        | 78  |

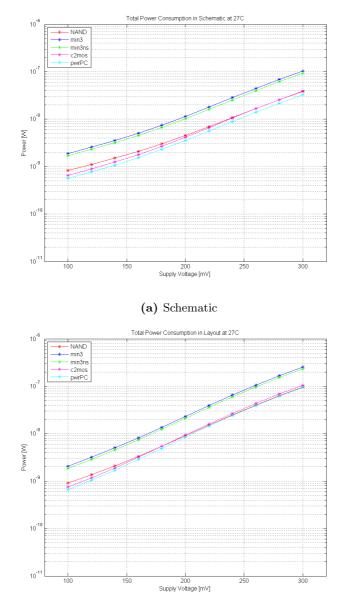

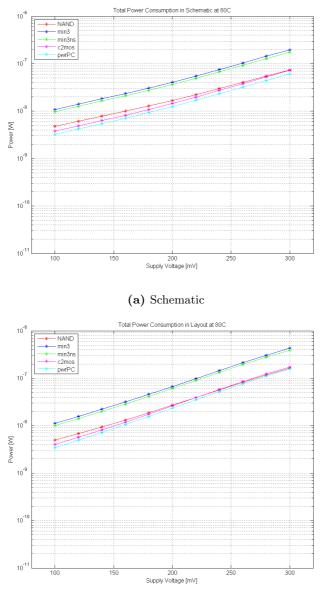

|   | 8.6  | Total Power Consumption                                        | 79  |

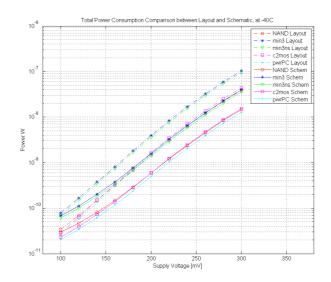

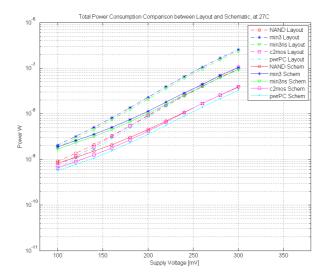

|   |      | 8.6.1 Total Power Consumption Schematic versus Layout Com-     |     |

|   |      | parison                                                        | 82  |

|   |      | 8.6.2 Total Power Consumption Temperature Comparison           | 84  |

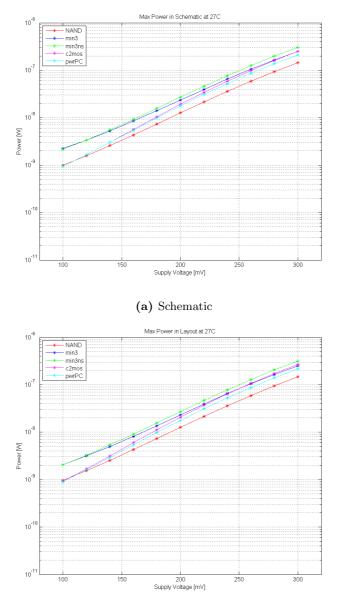

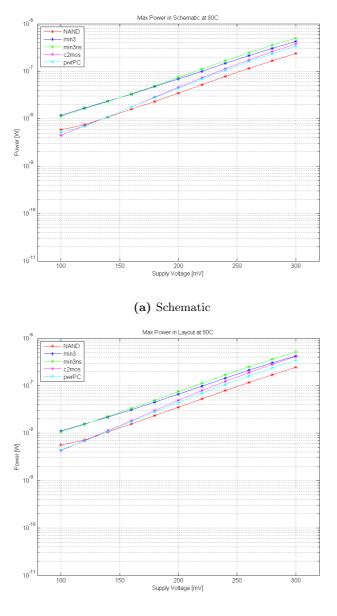

|   | 8.7  | Maximum Power Consumption                                      | 85  |

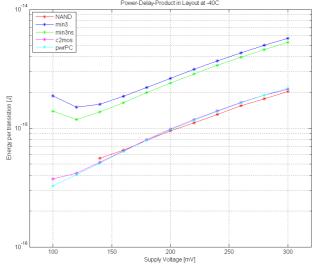

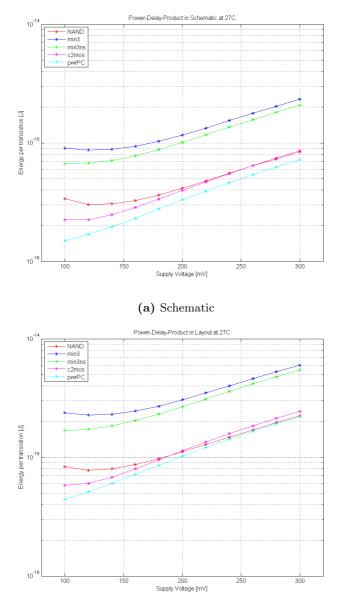

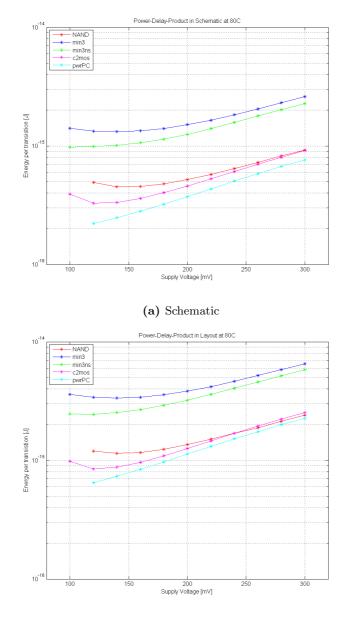

|   | 8.8  | Power-Delay-Product                                            | 88  |

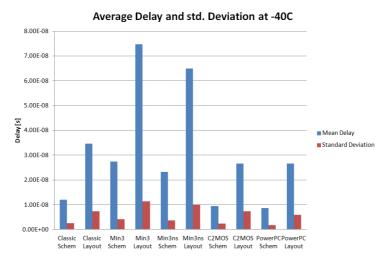

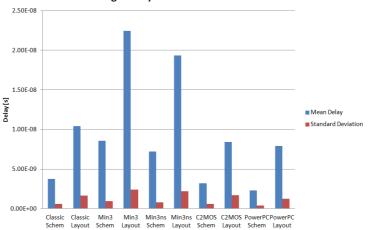

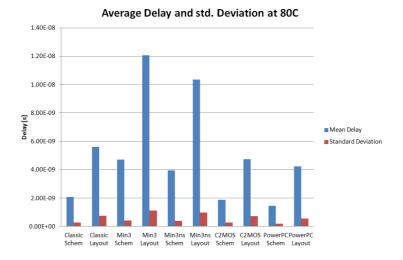

|   | 8.9  | Monte Carlo Delay Simulation                                   | 91  |

|   |      | 8.9.1 Average Mean Delay and Standard Deviation for Schematic  |     |

|   |      | and Layout                                                     | 91  |

|   |      | 8.9.2 Average Mean Delay for Schematic and Layout at different |     |

|   |      | temperatures                                                   | 92  |

|   |      | 8.9.3 Worst Case Mean Delay for Schematic and Layout at dif-   |     |

|   |      | ferent temperatures                                            | 93  |

|   |      | 8.9.4 Relative Standard Deviation Comparison                   | 94  |

| ~ | Б,   |                                                                | ~   |

| 9 |      |                                                                | 95  |

|   | 9.1  | Transistor Layout                                              | 95  |

|   |      | 9.1.1 Parasitic Extraction                                     | 95  |

|   |      | 9.1.2 nWell Placement and Sizing                               | 95  |

|   | 9.2  | D flip-flop functionality                                      | 96  |

|   | 9.3  | Delay Comparison of D flip-flops                               | 96  |

|   |      |                                                                | 96  |

|   |      |                                                                | 96  |

|   |      | 9.3.3 Total D flip-flop delay                                  | 97  |

|   | 9.4  | Maximum D flip-flop frequency based on maximum delay           | 98  |

|   | 9.5  | Static power consumption at different inputs                   | 98  |

|   |      | 9.5.1 Static power comparison at different temperatures        | 99  |

|   | 9.6  | Total power consumption                                        | 99  |

|   |      | 1 1                                                            | 99  |

|   |      | 9.6.2 Total Power Consumption Temperature Comparison           | 99  |

|   | 9.7  | Maximum Power Consumption                                      |     |

|   | 9.8  | Power-Delay-Product                                            |     |

|   | 9.9  | Monte Carlo Delay Simulation                                   |     |

|   | 0.0  |                                                                | LOT |

|              |      | 9.9.1  | Average Mean Delay and Standard Deviation for Schematic  |           |

|--------------|------|--------|----------------------------------------------------------|-----------|

|              |      |        | and Layout                                               | .01       |

|              |      | 9.9.2  | Average Mean Delay for Schematic and Layout at different |           |

|              |      |        | temperatures                                             | 02        |

|              |      | 9.9.3  | Worst Case Mean Delay for Schematic and Layout at dif-   |           |

|              |      |        | ferent temperatures                                      | 02        |

|              |      | 9.9.4  | Relative Standard Deviation Comparison                   |           |

|              | 9.10 | The T  | otal Results                                             | .03       |

| 10           | Con  | aludin | a Domonica 1                                             | 05        |

| 10           |      |        |                                                          |           |

|              | 10.1 | Improv | vements of the D flip-flops and Future Work              | .05       |

| $\mathbf{A}$ | Mor  | nte Ca | rlo Results 1                                            | 10        |

|              | A.1  | Monte  | Carlo Delay Data                                         | 10        |

|              | A.2  | Averag | ge Monte Carlo Delay Data                                | 16        |

|              |      |        | ve Sigma Results                                         |           |

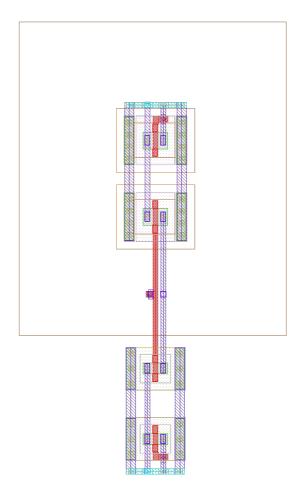

| в            | Lay  | out    | 1                                                        | 17        |

| -            | 200  |        | -                                                        |           |

| $\mathbf{C}$ | Sou  | rce Co | de 1                                                     | <b>26</b> |

|              | C.1  | Pythor | n Scripts                                                | 26        |

|              | -    |        | 1                                                        | -         |

## List of Figures

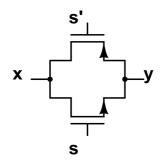

| 1  | Transmission Gate                                                           | 10              |

|----|-----------------------------------------------------------------------------|-----------------|

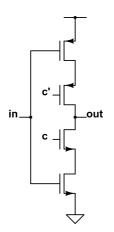

| 2  | The Clocked Inverter                                                        |                 |

| 3  | The Minority3 Gate                                                          | 12              |

| 4  | The NAND-coupled Minority3 Gate                                             | 12              |

| 5  | Gated D-latch symbol                                                        |                 |

| 6  | Logic Diagram for NAND-based D-latch                                        | 13              |

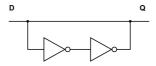

| 7  | Logic Diagram for inverter-based latch                                      | 13              |

| 8  | CMOS Diagram for inverter-based D-latch with Transmission Gates             |                 |

|    | [30]                                                                        | 13              |

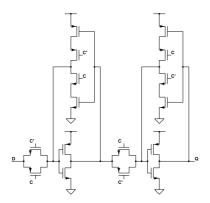

| 9  | CMOS Diagram for clocked inverter-based D-latch[30]                         | 14              |

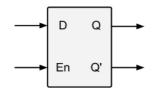

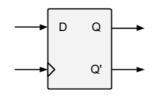

| 10 | The D flip-flop symbol                                                      | 14              |

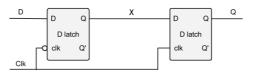

| 11 | Master-slave D flip-flop, Master latch to the left, and Slave latch         |                 |

|    | to the right                                                                | 15              |

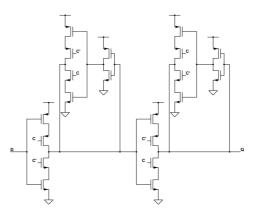

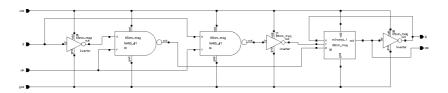

| 12 | Classic NAND-based D flip-flop [12]                                         | 15              |

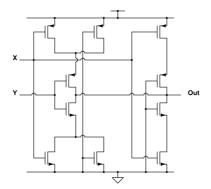

| 13 | Min3-based D flip-flop Schematics [8]                                       | 16              |

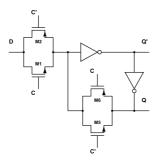

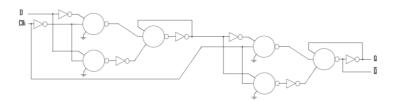

| 14 | $C^2MOS D$ flip-flop structure                                              | 16              |

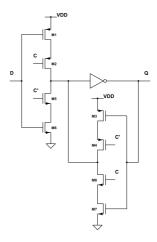

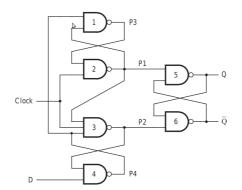

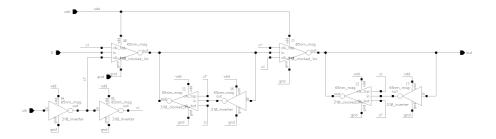

| 15 | The PowerPC 603 D flip-flop structure                                       | 17              |

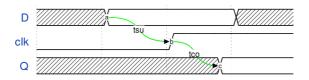

| 16 | The two delays in a waveform, where $t_{su}$ is the setup time, $t_{co}$ is |                 |

|    | the propagation delay $\ldots$                                              | 17              |

| 17 | Dummy transistors on the end of a pMOS transistor row                       | 19              |

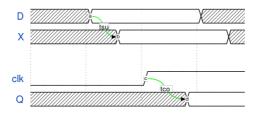

| 18 | Master-Slave D flip-flop with X node                                        | $\overline{23}$ |

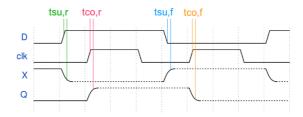

| 19 | Measurement of $t_{su}$ and $t_{co}$ , with the X node                      | 23              |

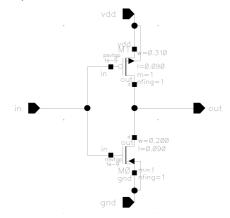

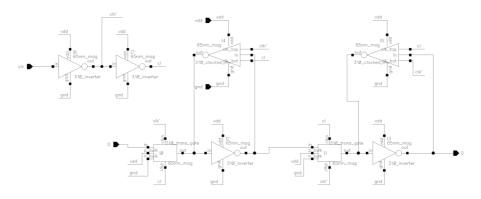

| 20 | Clocked Inverter schematics                                                 | 24              |

| 21 | Clocked Inverter schematics                                                 | 25              |

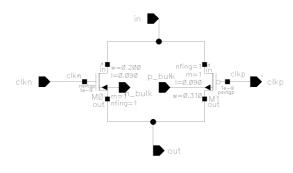

| 22 | Transmission Gate Schematics                                                | 25              |

| 23 | Minority3 Schematics                                                        |                 |

| 24 | Minority3 Schematics                                                        | 27              |

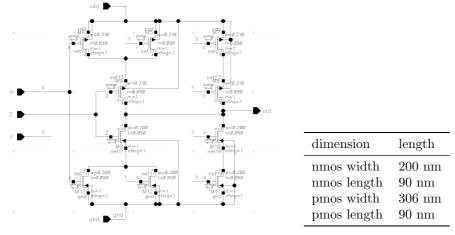

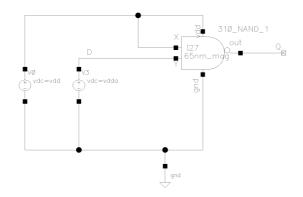

| 25 | Two-input NAND Schematics                                                   |                 |

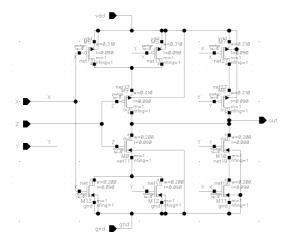

| 26 | Classic NAND D flip-flop Schematics                                         |                 |

| 27 | Minority3-based D flip-flop Schematics                                      |                 |

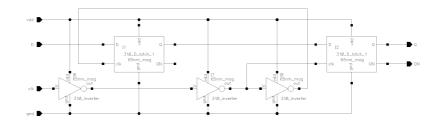

| 28 | Minority3-based D-latch Schematics                                          | 29              |

| 29 | Minority3-based no-set D flip-flop Schematics                               | 30              |

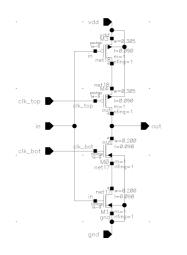

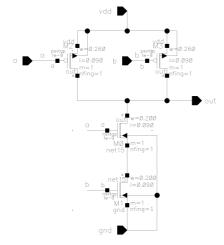

| 30 | $C^2MOS$ D flip-flop Schematics                                             | 30              |

| 31 | PowerPC 603 D flip-flop Schematics                                          | 30              |

| 32 | p-tap/n-tap connection                                                      | 33              |

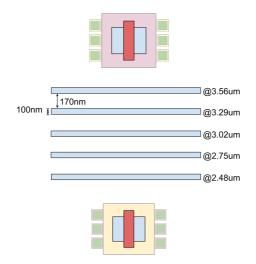

| 33 | Test circuit for comparing xRC and xACT 3D Parasitic Extraction             | 34              |

| 34 | Inverter layout for WPE simulation, nWell edge distance is $1\mu m$         |                 |

|    | from nMOS and pMOS                                                          | 35              |

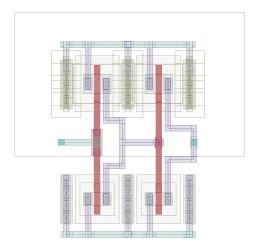

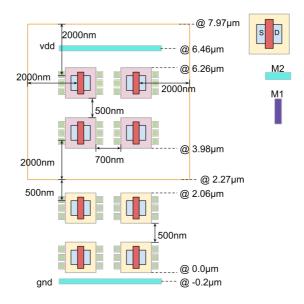

| 35 | Layout Placement, Distances and Positions                                   | 36              |

| 36 | Wire positions in Layout                                                    | 37              |

| 37 | The Balancing Testbench                                                     | 39              |

| 38 | The Delay Testbench                                                         | 40              |

| 39 | The power testbench                                                         | 41              |

| 40 | Delay testbench waveforms, tsu is setup time, tco is propagation            |                 |

|    | delay, r is rising edge, f is falling edge                                  | 44              |

| 41  | The power testbench waveforms                                                                        | 46       |

|-----|------------------------------------------------------------------------------------------------------|----------|

| 42  | WPE chart for inverter circuit, Dashed lines are the schematic                                       |          |

|     | threshold voltage                                                                                    | 50       |

| 43  | The confirmed functionality of the D flip-flops at $250mV,\!27^\circ C$                              | 51       |

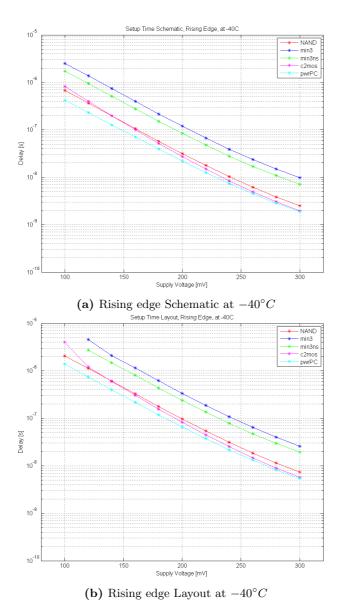

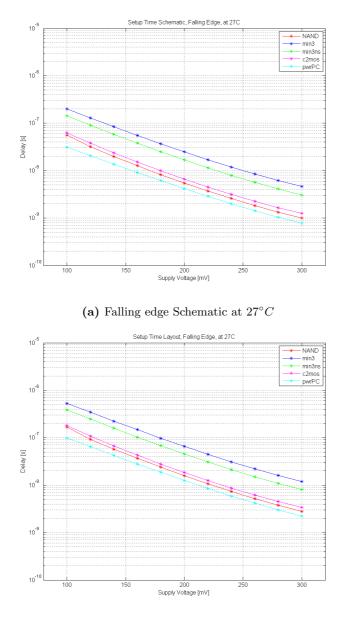

| 44  | Setup delay for schematic and layout at $-40^{\circ}C$ , Rising edge $\ldots$                        | 52       |

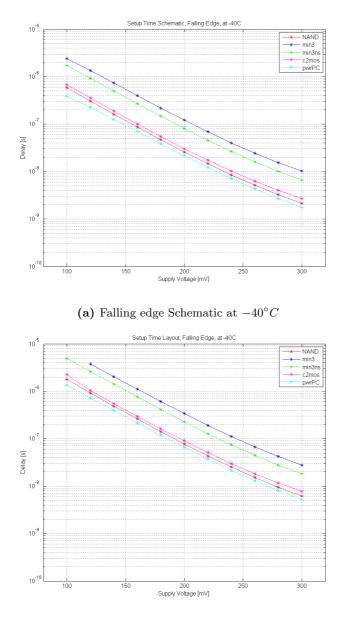

| 45  | Setup delay for schematic and layout at $-40^{\circ}C$ , Falling edge $\ldots$                       | 53       |

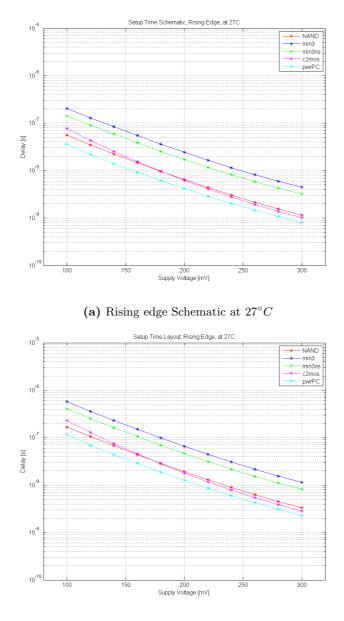

| 46  | Setup delay for schematic and layout at $27^{\circ}C$ , Rising edge $\ldots$                         | 54       |

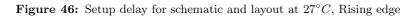

| 47  | Setup delay for schematic and layout at $27^{\circ}C$ , Falling edge $\ldots$                        | 55       |

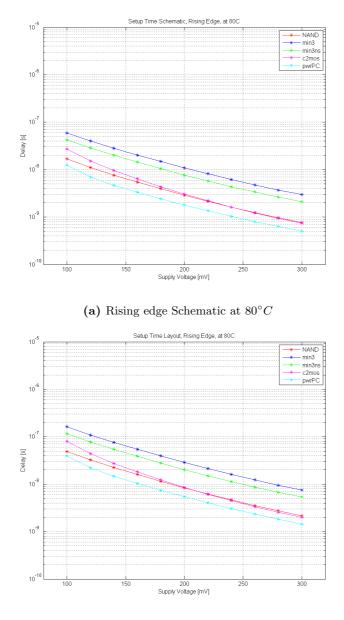

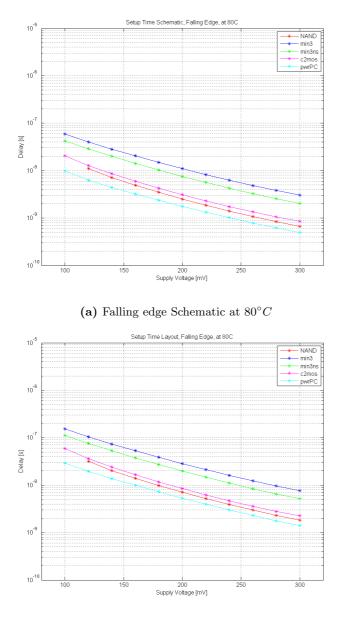

| 48  | Setup delay for schematic and layout at $80^{\circ}C$ , Rising edge $\ldots$                         | 56       |

| 49  | Setup delay for schematic and layout at $80^{\circ}C$ , Falling edge $\ldots$                        | 57       |

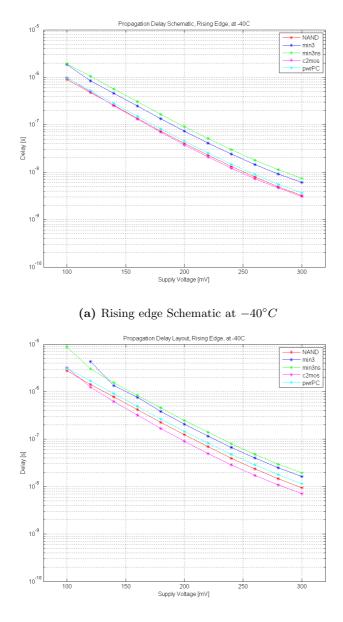

| 50  | Propagation delay for schematic and layout at $-40^{\circ}C$ , Rising edge                           | 58       |

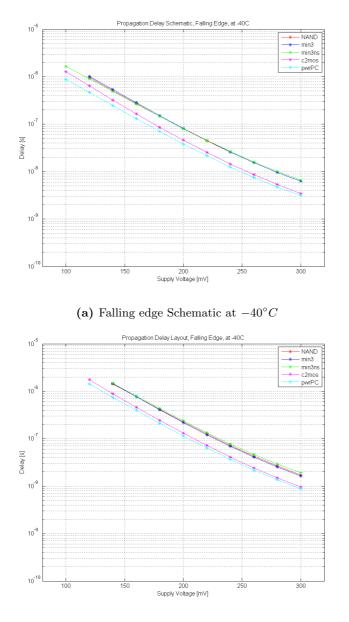

| 51  | Propagation delay for schematic and layout at $-40^{\circ}C$ , Falling edge                          | 59       |

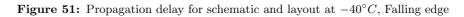

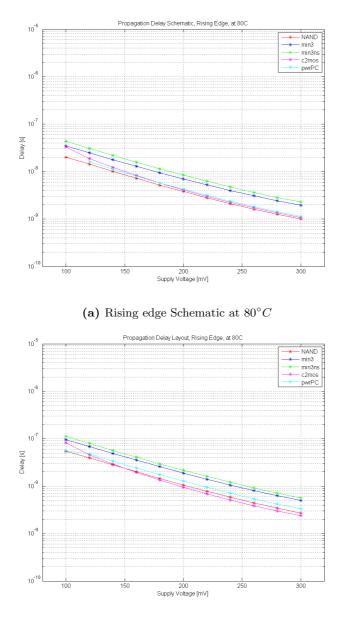

| 52  | Propagation delay for schematic and layout at $27^{\circ}C$ , Rising edge .                          | 60       |

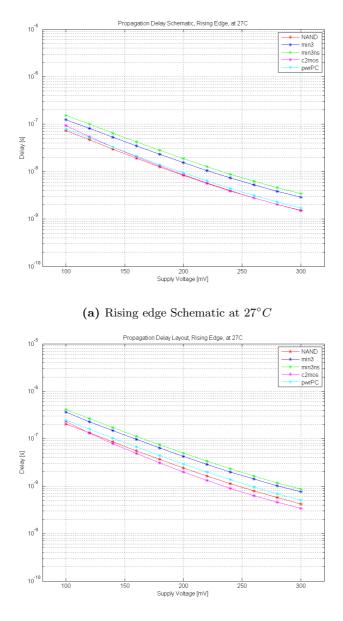

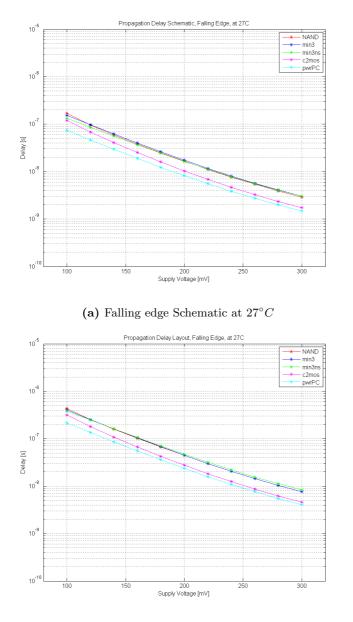

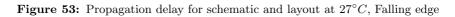

| 53  | Propagation delay for schematic and layout at $27^{\circ}C$ , Falling edge                           | 61       |

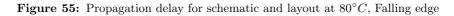

| 54  | Propagation delay for schematic and layout at $80^{\circ}C$ , Rising edge .                          | 62       |

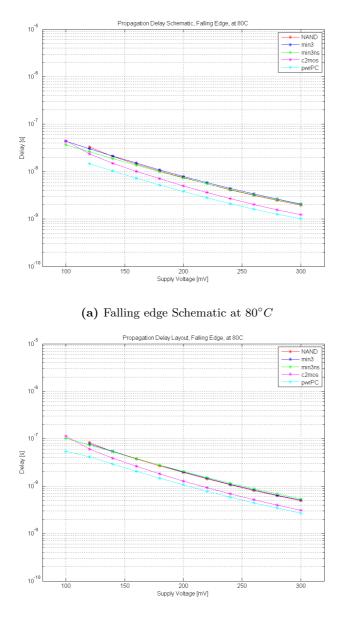

| 55  | Propagation delay for schematic and layout at $80^{\circ}C$ , Falling edge                           | 63       |

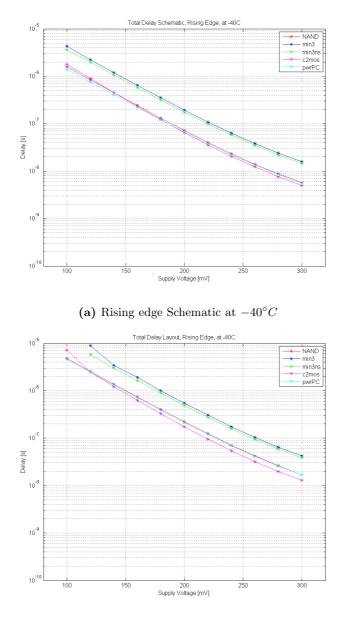

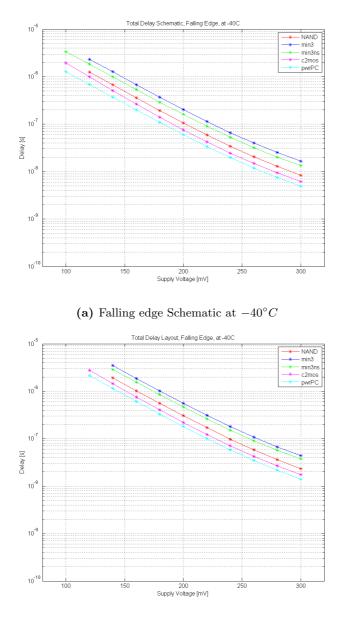

| 56  | Total delay for schematic and layout at $-40^{\circ}C$ , Rising edge                                 | 64       |

| 57  | Total delay for schematic and layout at $-40^{\circ}C$ , Falling edge                                | 65       |

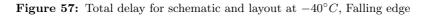

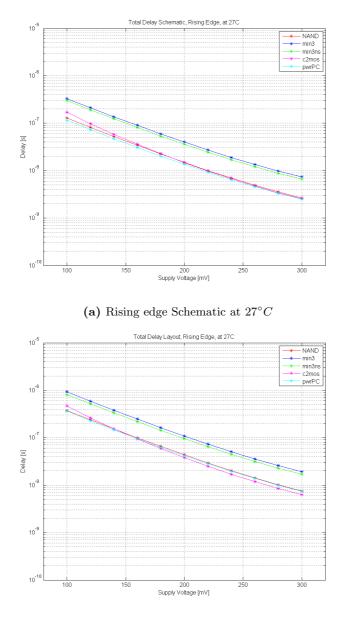

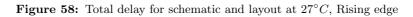

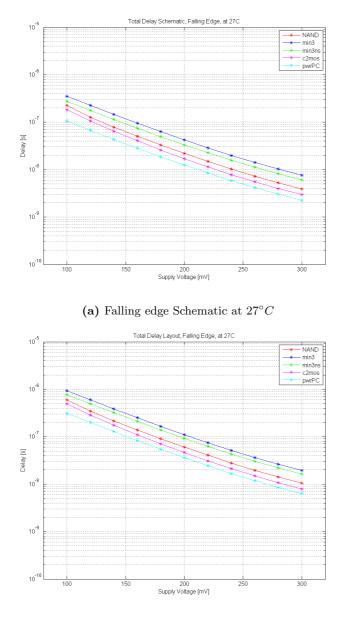

| 58  | Total delay for schematic and layout at $27^{\circ}C$ , Rising edge                                  | 66       |

| 59  | Total delay for schematic and layout at $27^{\circ}C$ , Falling edge $\ldots$                        | 67       |

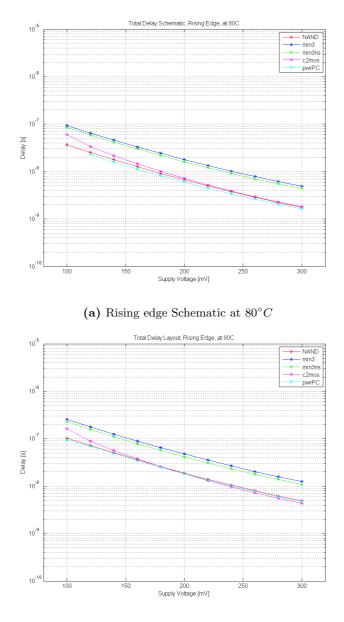

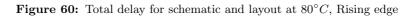

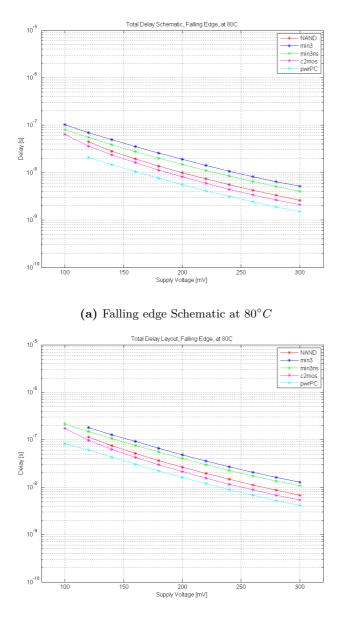

| 60  | Total delay for schematic and layout at $80^{\circ}C$ , Rising edge                                  | 68       |

| 61  | Total delay for schematic and layout at $80^{\circ}C$ , Falling edge                                 | 69       |

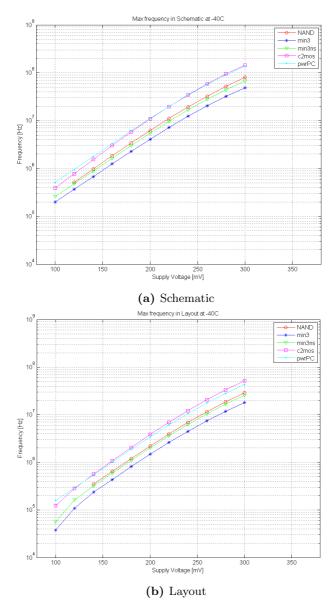

| 62  | Maximum frequency for all D flip-flops at $-40^{\circ}C$                                             | 70       |

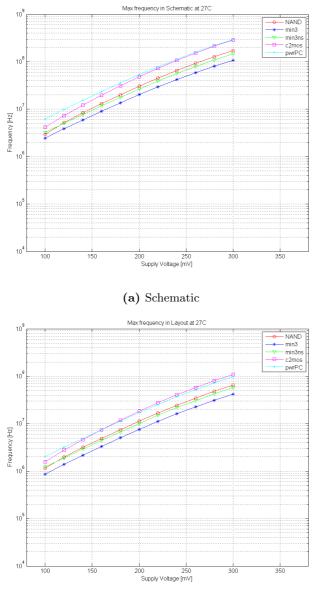

| 63  | Maximum frequency for all D flip-flops at $27^{\circ}C$                                              | 71       |

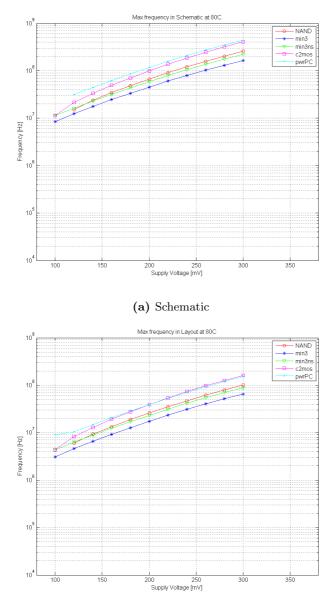

| 64  | Maximum frequency for all D flip-flops at $80^{\circ}C$                                              | 72       |

| 65  | Maximum frequency for all D flip-flops across temperatures                                           | 73       |

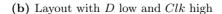

| 66  | Static Power Consumption for layout and schematic with $D$ high,                                     |          |

|     | $Clk$ high $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$          | 74       |

| 67  | Static Power Consumption for layout and schematic with $D$ high,                                     |          |

|     | Clk low                                                                                              | 75       |

| 68  | Static Power Consumption for layout and schematic with $D$ low,                                      |          |

|     | $Clk$ high $\ldots$ | 76       |

| 69  | Static Power Consumption for layout and schematic with $D$ low,                                      |          |

|     | Clk low                                                                                              | 77       |

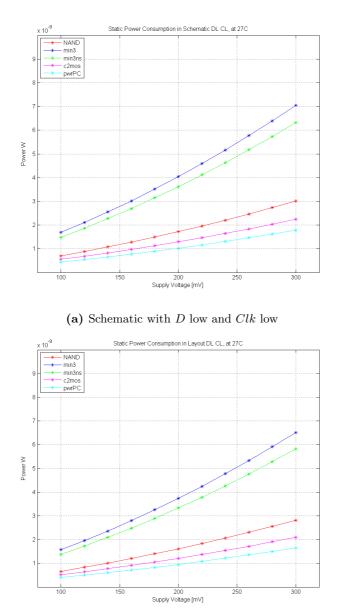

| 70  | Static Power Consumption DH CL at all temperatures                                                   | 78       |

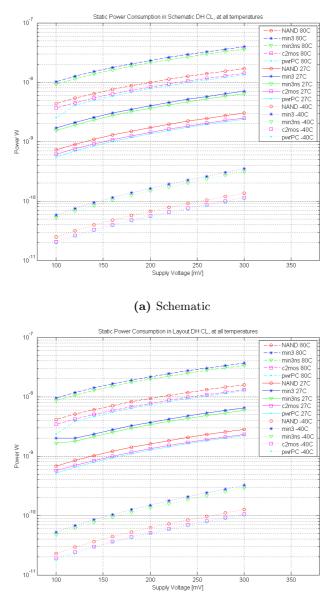

| 71  | Total Power Consumption at $-40^{\circ}C$                                                            | 79       |

| 72  | Total Power Consumption at $27^{\circ}C$                                                             | 80       |

| 73  | Total Power Consumption at $80^{\circ}C$                                                             | 81       |

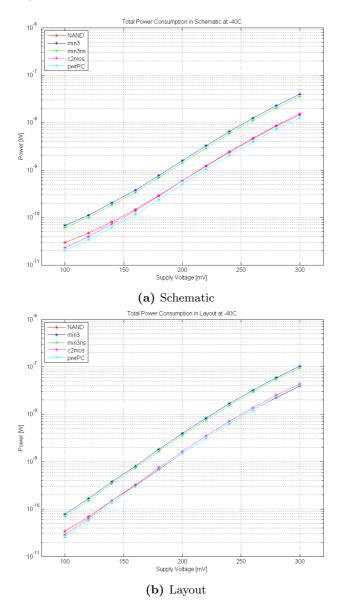

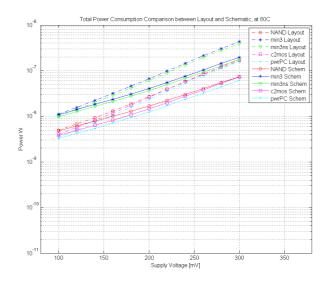

| 74  | Total Power Consumption Comparison between schematic and lay-                                        |          |

| • - | out at $-40^{\circ}C$                                                                                | 82       |

| 75  | Total Power Consumption Comparison between schematic and lay-                                        |          |

|     | out at $27^{\circ}C$                                                                                 | 83       |

| 76  | Total Power Consumption Comparison between schematic and lay-                                        | 00       |

| 10  | out at $80^{\circ}C$                                                                                 | 83       |

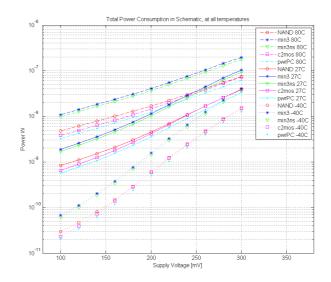

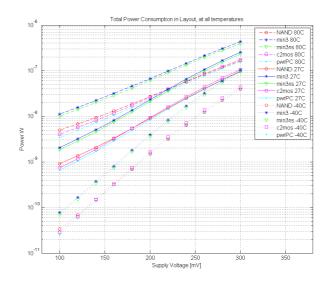

| 77  | Total Power Consumption Comparison between Temperatures for                                          | 00       |

| • • | schematic                                                                                            | 84       |

|     |                                                                                                      | <u> </u> |

| 78                                                                                                                                 | Total Power Consumption Comparison between Temperatures for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                                                                    | layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

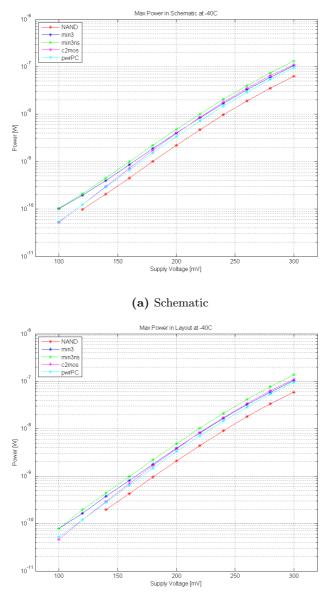

| 79                                                                                                                                 | Maximum Power Consumption at $-40^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 80                                                                                                                                 | Maximum Power Consumption at $27^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 81                                                                                                                                 | Maximum Power Consumption at $80^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 82                                                                                                                                 | Power-Delay-Product at $-40^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 83                                                                                                                                 | Power-Delay-Product at $27^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 84                                                                                                                                 | Power-Delay-Product at $80^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 85                                                                                                                                 | Monte Carlo Analysis Average Results and std. Deviation for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                                                                                                                    | schematic and layout at $-40^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 86                                                                                                                                 | Monte Carlo Analysis Average Results and std. Deviation for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                                                                                                                    | schematic and layout at $27^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 87                                                                                                                                 | Monte Carlo Analysis Average Results and std. Deviation for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                                                                                                                    | schematic and layout at $80^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 88                                                                                                                                 | Monte Carlo Analysis Average Results for schematic and layout . 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 89                                                                                                                                 | Monte Carlo Analysis Worst Case Results for schematic and layout 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 89<br>90                                                                                                                           | Monte Carlo Analysis Worst Case Results for schematic and layout 93<br>Relative Standard Deviation for all D flip-flops. The Y-value is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                                                                                                                                    | Monte Carlo Analysis Worst Case Results for schematic and layout 93<br>Relative Standard Deviation for all D flip-flops. The Y-value is<br>average Standard Deviation divided by the average Mean Delay . 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

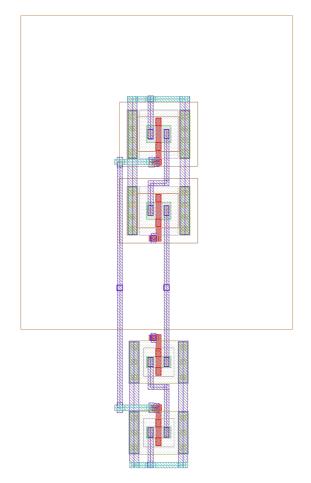

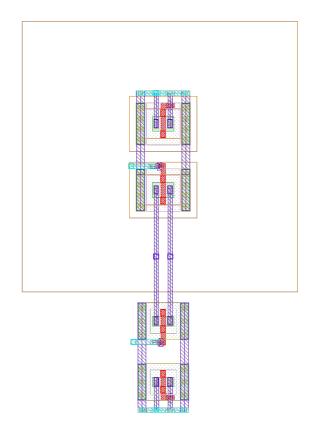

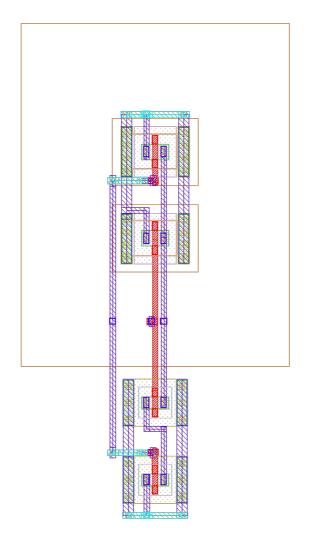

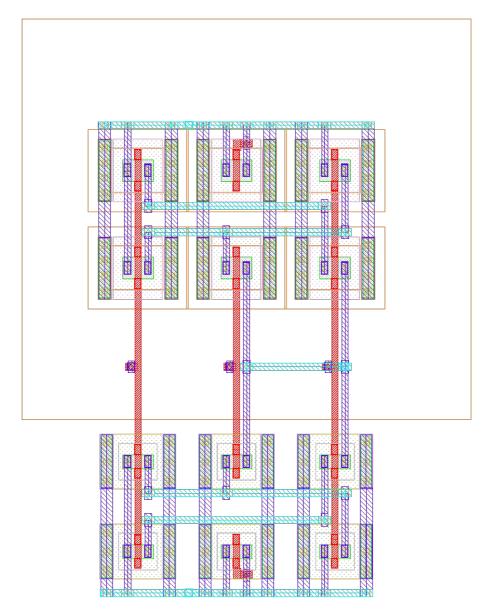

| 90<br>91                                                                                                                           | Monte Carlo Analysis Worst Case Results for schematic and layout 93<br>Relative Standard Deviation for all D flip-flops. The Y-value is<br>average Standard Deviation divided by the average Mean Delay . 94<br>The Inverter Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 90<br>91<br>92                                                                                                                     | Monte Carlo Analysis Worst Case Results for schematic and layout93Relative Standard Deviation for all D flip-flops. The Y-value isaverage Standard Deviation divided by the average Mean Delay94The Inverter Layout118The Clocked Inverter Layout119                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 90<br>91                                                                                                                           | Monte Carlo Analysis Worst Case Results for schematic and layout93Relative Standard Deviation for all D flip-flops. The Y-value is94average Standard Deviation divided by the average Mean Delay94The Inverter Layout118The Clocked Inverter Layout119The Transmission Gate Layout120                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 90<br>91<br>92<br>93<br>94                                                                                                         | Monte Carlo Analysis Worst Case Results for schematic and layout93Relative Standard Deviation for all D flip-flops. The Y-value isaverage Standard Deviation divided by the average Mean Delay94The Inverter Layout118The Clocked Inverter Layout119The Transmission Gate Layout120The Simple NAND Layout121                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 90<br>91<br>92<br>93                                                                                                               | Monte Carlo Analysis Worst Case Results for schematic and layout93Relative Standard Deviation for all D flip-flops. The Y-value isaverage Standard Deviation divided by the average Mean Delay94The Inverter Layout118The Clocked Inverter Layout119The Transmission Gate Layout120The Simple NAND Layout121The Minority3-gate Layout122                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 90<br>91<br>92<br>93<br>94                                                                                                         | Monte Carlo Analysis Worst Case Results for schematic and layout93Relative Standard Deviation for all D flip-flops. The Y-value is94average Standard Deviation divided by the average Mean Delay94The Inverter Layout118The Clocked Inverter Layout119The Transmission Gate Layout120The Simple NAND Layout121The Minority3-gate Layout123The Minority-based NAND-gate Layout123                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

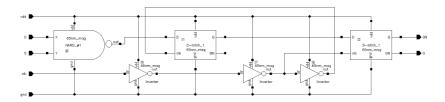

| 90<br>91<br>92<br>93<br>94<br>95                                                                                                   | Monte Carlo Analysis Worst Case Results for schematic and layout93Relative Standard Deviation for all D flip-flops. The Y-value is94average Standard Deviation divided by the average Mean Delay94The Inverter Layout118The Clocked Inverter Layout119The Transmission Gate Layout120The Simple NAND Layout121The Minority3-gate Layout122The Minority-based NAND-gate Layout123The Classic NAND D flip-flop Layout124                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| <ol> <li>90</li> <li>91</li> <li>92</li> <li>93</li> <li>94</li> <li>95</li> <li>96</li> </ol>                                     | Monte Carlo Analysis Worst Case Results for schematic and layout93Relative Standard Deviation for all D flip-flops. The Y-value is94average Standard Deviation divided by the average Mean Delay94The Inverter Layout118The Clocked Inverter Layout119The Transmission Gate Layout120The Simple NAND Layout121The Minority3-gate Layout122The Classic NAND D flip-flop Layout124The Minority-based D-latch Layout124                                                                                                                                                                                                                                                                                                     |  |  |  |  |

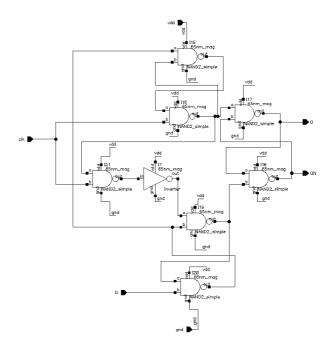

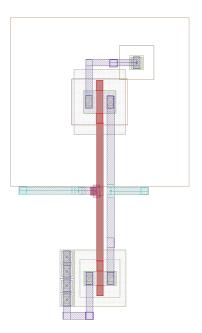

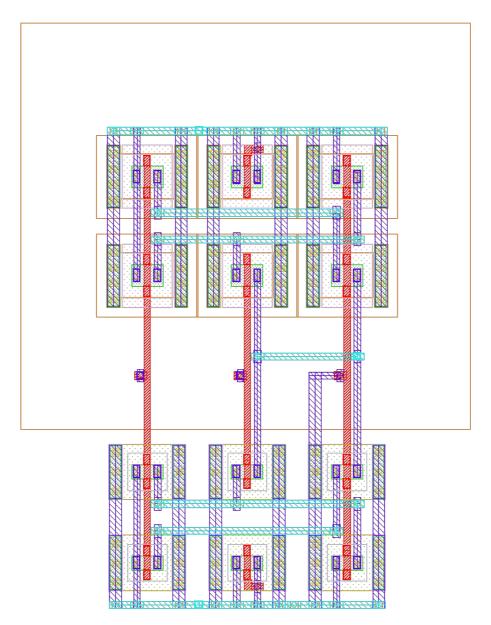

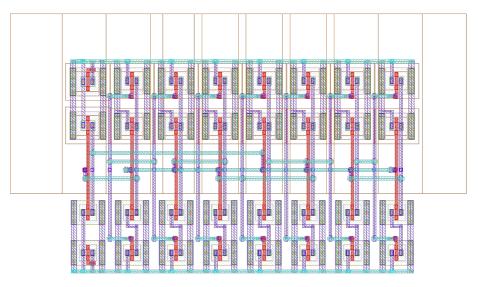

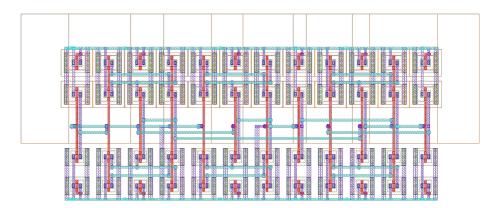

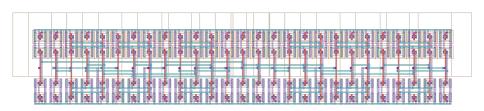

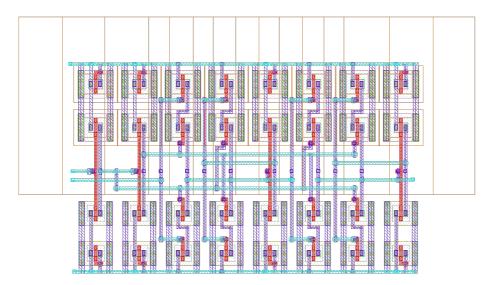

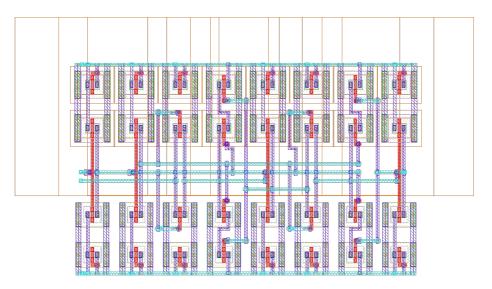

| <ul> <li>90</li> <li>91</li> <li>92</li> <li>93</li> <li>94</li> <li>95</li> <li>96</li> <li>97</li> <li>98</li> <li>99</li> </ul> | Monte Carlo Analysis Worst Case Results for schematic and layout93Relative Standard Deviation for all D flip-flops. The Y-value is94average Standard Deviation divided by the average Mean Delay94The Inverter Layout118The Clocked Inverter Layout119The Transmission Gate Layout120The Simple NAND Layout121The Minority3-gate Layout123The Classic NAND D flip-flop Layout124The Minority3-based D flip-flop Layout124                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 90<br>91<br>92<br>93<br>94<br>95<br>96<br>97<br>98<br>99<br>100                                                                    | Monte Carlo Analysis Worst Case Results for schematic and layout93Relative Standard Deviation for all D flip-flops. The Y-value is94average Standard Deviation divided by the average Mean Delay94The Inverter Layout118The Clocked Inverter Layout119The Transmission Gate Layout120The Simple NAND Layout122The Minority3-gate Layout123The Classic NAND D flip-flop Layout124The Minority3-based D flip-flop Layout124 |  |  |  |  |

| <ul> <li>90</li> <li>91</li> <li>92</li> <li>93</li> <li>94</li> <li>95</li> <li>96</li> <li>97</li> <li>98</li> <li>99</li> </ul> | Monte Carlo Analysis Worst Case Results for schematic and layout93Relative Standard Deviation for all D flip-flops. The Y-value is94average Standard Deviation divided by the average Mean Delay94The Inverter Layout118The Clocked Inverter Layout119The Transmission Gate Layout120The Simple NAND Layout121The Minority3-gate Layout123The Classic NAND D flip-flop Layout124The Minority3-based D flip-flop Layout124                                                                                                                                                                                                                                                                                                |  |  |  |  |

## List of Tables

|          |       | 11 |

|----------|-------|----|

|          |       | 19 |

|          |       | 24 |

|          |       | 25 |

| alance p | point | 26 |

|          |       | 26 |

|          |       | 27 |

|          |       | 27 |

| ics      |       | 31 |

|          |       | 31 |

|          |       | 32 |

|          |       | 38 |

| rements  | s .   | 45 |

| A        | ics   |    |

| 14 | Input Variables for the different Tests                                                                                                                                                                                                         |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 | Layout parasitics for test circuit using xRC extraction tool 49                                                                                                                                                                                 |

| 16 | Layout parasitics for test circuit using xACT 3D extraction tool $\therefore$ 49                                                                                                                                                                |

| 17 | Layout parasitics Simulation Results comparing the xRC and xACT                                                                                                                                                                                 |

|    | 3D extraction tools                                                                                                                                                                                                                             |

| 18 | Delay Comparison at $300 \text{mV}$ , $27^{\circ}C$ , Layout $\ldots \ldots \ldots 98$                                                                                                                                                          |

| 19 | Maximum Frequency of D flip-flops, $250mV$ supply voltage at                                                                                                                                                                                    |

|    | $27^{\circ}C$ Layout $\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$ |

| 20 | Total Power Consumption of D flip-flops, $250mV$ supply voltage                                                                                                                                                                                 |

|    | at 27°C Layout $\ldots \ldots 104$                                                                                                                   |

| 21 | Power-Delay-Product of D flip-flops, $250mV$ supply voltage at                                                                                                                                                                                  |

|    | $27^{\circ}C$ Layout $\hdots$                                                                                                                                                                                                                   |

| 22 | Transistor count in the current design, and the transistor count in                                                                                                                                                                             |

|    | the new proposed design, for the RX/TX-module $\ldots\ldots\ldots\ldots$ 106                                                                                                                                                                    |

| 23 | Monte Carlo Delay Results for Master latch, rising edge at $-40^{\circ}C$ 110                                                                                                                                                                   |

| 24 | Monte Carlo Delay Results for Master latch, falling edge at $-40^\circ C~110$                                                                                                                                                                   |

| 25 | Monte Carlo Delay Results for Slave latch, rising edge at $-40^\circ C$ . 111                                                                                                                                                                   |

| 26 | Monte Carlo Delay Results for Slave latch, falling edge at $-40^{\circ}C$ 111                                                                                                                                                                   |

| 27 | Monte Carlo Delay Results for Master latch, rising edge at $27^\circ C_{-}$ . 112                                                                                                                                                               |

| 28 | Monte Carlo Delay Results for Master latch, falling edge at $27^{\circ}C$ 112                                                                                                                                                                   |

| 29 | Monte Carlo Delay Results for Slave latch, rising edge at $27^\circ C_{-}$ 113                                                                                                                                                                  |

| 30 | Monte Carlo Delay Results for Slave latch, falling edge at $27^\circ C$ $$ . 113 $$                                                                                                                                                             |

| 31 | Monte Carlo Delay Results for Master latch, rising edge at $80^\circ C$ . 114                                                                                                                                                                   |

| 32 | Monte Carlo Delay Results for Master latch, falling edge at $80^{\circ}C$ 114                                                                                                                                                                   |

| 33 | Monte Carlo Delay Results for Slave latch, rising edge at $80^\circ C_{-}$ 115                                                                                                                                                                  |

| 34 | Monte Carlo Delay Results for Slave latch, falling edge at $80^\circ C$ $$ . 115 $$                                                                                                                                                             |

| 35 | Average Monte Carlo Delay Results, $\mu$ is mean delay, $\sigma$ is standard                                                                                                                                                                    |

|    | deviation $\ldots \ldots 116$                                                                                                                 |

| 36 | Relative Sigma Results                                                                                                                                                                                                                          |

## 1 Introduction

Ultra low power systems and circuits are getting more and more desired for applications where the power supply is limited. Battery supplied systems like pacemakers and subsea electronic equipment, where battery charging or battery replacement is hard or impossible, could have a great economic saving from improving the battery life time. With ultra low power systems, arises the possibility to use energy harvesting to power the devices. Energy harvesting is a technique to extract energy from external sources like heat, vibration, electromagnetic radiation and more, which could remove the need of batteries and greatly reduce the maintenance and battery cost.

Today there are many integrated-circuit building blocks for circuits operating in the super-threshold region. Super-threshold building blocks are well-tested and developed by large companies, and used in systems and circuits for many years. Subthreshold operation has recently become more popular as the need for battery powered systems has increased. Since the use of subthreshold design started relatively recent, there are not many well-tested and developed building blocks. Building blocks like the D flip-flop are much used in larger systems, and contributes a lot to the total system area. By creating robust D flip-flop building blocks, which are simulated on schematic and layout, the path to well-tested and reliable subthreshold building blocks shortens.

Some papers has been published which looks into different subthreshold D flip-flop implementations, but only with simulations on schematics like [6], [13] and [14]. In this Thesis, five known D flip-flop implementations will be custom designed for subthreshold operation, and simulated on Schematic and Layout. The transition from schematic to layout introduces many new non-idealities like parasitic capacitances, electric fields, mismatch from process variations, and more which affects the functionality of the circuit.

## 1.1 Overview of the Thesis

The chapters and appendixes contain the following:

- Chapter 1 contains the Introduction and motivation towards subthreshold design.

- Chapter 2 presents the Problem Description, and the tools and technology used.

- Chapter 3 presents all the theoretical background needed to fully understand the implementation and results.

- Chapter 4 explains the process of choosing D flip-flop structures and the procedure of the schematic design.

- Chapter 5 presents the layout implementation method and steps towards a highly regular design.

- Chapter 6 explains the different testbenches used to simulate both schematic and layout design.

- Chapter 7 explains the different simulation methods, tests, and input signals used.

- Chapter 8 presents the simulation results based on the tests described in Chapter 7.

- Chapter 9 discuss and compare the results to each other and to earlier results found in papers.

- Chapter 10 gives a summary of the results and discuss future work and improvements.

- Appendix A presents all Monte Carlo results.

- Appendix B shows the layout view of the D flip-flops.

- Appendix C presents the source code used to initiate simulations, and process results data.

## 2 Problem Description

The task is to implement D flip-flop structures which are highly suitable for subthreshold operation, and can be used as building block for greater design. The D flip-flops are custom designed in Schematics at transistor level, and implemented in layout by using techniques for high process variation robustness. The schematic and layout implementations are simulated to find delays, power consumption, PDP and susceptibility against process variations. These results are compared to find differences between schematic and layout implementations.

The tool used to implement both schematic and layout designs are Cadence Virtuoso Design Environment version IC6.1.5. The simulator used for both schematic and layout is the Cadence Virtuoso Spectre Circuit Simulator.

The transistor technology used is the STMircroelectronics 65nm SVTGP. The SVTGP is a standard threshold voltage general purpose transistor, as the name points out.

## 2 Problem Description

## 3 Theoretical Background

This Section contains the theory for understanding the basics in the design, layout, simulation and results chapters. First, subthreshold operation and difficulties around operating in that region, will be mentioned. Secondly, transistor matching, balancing and robustness will be described. Thirdly, the different D flip-flop functionality and design will be explained. At the end, timing and layout will be commented.

## 3.1 Subthreshold Operation

A MOS transistor is either n-channel or p-channel depending on the doping of the substrate and the doping of the Source and Drain terminals[18]. By applying a positive voltage to the gate of an n-channel MOS transistor, the gate attracts negative charge from the source and drain regions, creating a channel with mobile electrons connecting the source and the drain. By applying a sufficiently large gate-to-source voltage at the transistor, the p-region under the gate is changed to an n-channel, and is said to be inverted. The minimum gate-to-source voltage for this to happen is said to be the Threshold Voltage. The Threshold Voltage  $V_t$  of a MOS transistor is the gate-to-source Voltage where the concentration of electrons under the gate is equal to the concentration of holes in the substrate. Normally, a gate-to-source Voltage  $V_{GS}$  under the threshold voltage is said to cause the transistor to be turned off, since the current flow through the channel is significantly smaller than when applying a high voltage. However, this subthreshold current is still usable to create functional CMOS circuitry.

A MOS transistor is said to be in the subthreshold region or weak inversion when  $V_{GS} - V_t < -100mV$ . When operating in the subthreshold region, the current through the Drain terminal  $I_D$  should not be modelled by the square-law function. The subthreshold current is more accurately modelled by the exponential relationship. This approximation is shown in Equation 1 through Equation 4[31].

$$I_D = I_{D0} e^{\frac{V_G}{nU_T}} \left( e^{-\frac{V_S}{U_T}} - e^{-\frac{V_D}{U_T}} \right)$$

(1)

$$I_{D0} \sim \beta e^{\frac{V_{TH}}{nU_T}} \tag{2}$$

$$\beta = \mu C_{OX} \frac{W}{L} \tag{3}$$

The slope factor n is

$$n = 1 + \frac{\gamma}{2\sqrt{2\phi_F + V_S}} \tag{4}$$

$U_T$  is the thermal voltage,  $V_{TH}$  is the threshold voltage,  $\mu$  is the charge-carrier effective mobility,  $C_{OX}$  is the gate oxide capacitance per unit area, W and L is

the gate width and gate length of the MOS transistor.  $\gamma$  is the substrate factor,  $\phi_F$  is the Fermi potential in the substrate.

As the supply voltage is reduced, the current charging the switching capacitances is also reduced, causing an increased propagation delay through the logic, so the maximum frequency of the circuit is reduced. This reduction in maximum switching frequency is one of the main drawbacks with subthreshold operation as it limits the usage area, since many applications have real-time demands which needs high frequencies to be met.

#### 3.1.1 Subthreshold Delay